電流制限回路

【課題】ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い、出力トランジスタに対する電流制限回路を提供する。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

【解決手段】電流制限回路が、基準トランジスタと、基準トランジスタに所定の電流を流す電流源と、出力トランジスタがオンした時の両端の第1の電位差と基準トランジスタの両端の第2の電位差を比較する比較器であって、第1の電位差が第2の電位差よりも大きくなった場合に、出力トランジスタをオフするように制御する電流制限信号を出力する、比較器とを備える。基準トランジスタは、出力トランジスタとは素子サイズの異なる同型のトランジスタであり、基準トランジスタがオンした時のオン抵抗は、出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、基準トランジスタがオンするように基準トランジスタのゲートにバイアスがかけられている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、DC−DCコンバータにおいて、スイッチ素子が流す電流が所定の電流値以上となった場合にスイッチ素子をオフさせる電流制限回路に関する。

【背景技術】

【0002】

図2は、従来技術によるDC−DCコンバータ101の回路図である。図2に示すDC−DCコンバータ101は、スイッチ素子が流す電流値が所定の電流値以上となったことを検出すると、スイッチ素子をオフさせる従来のDC−DCコンバータの電流制限回路111を含む。

【0003】

図2に示すDC−DCコンバータ101は、スイッチ素子(出力トランジスタ)であるPMOS出力トランジスタM1と整流素子であるダイオードD1とを用いる降圧型のDC−DCコンバータである。PMOS出力トランジスタM1をスイッチング制御するDC−DCコンバータ制御回路110は、電流モード制御型のものである。PMOS出力トランジスタM1に流れる電流Ioutが所定の電流値以上となった場合に、DC−DCコンバータ制御回路110を介して、PMOS出力トランジスタM1をオフさせる電流制限回路111は、センス抵抗Rsen、PMOSセンストランジスタM2、基準抵抗Rref、定電流源I1、比較器2で構成されている。

【0004】

次に、図2に示す従来技術に係る電流制限回路111の動作について説明する。PMOS出力トランジスタM1とPMOSセンストランジスタM2とは、サイズ比がN:1で、半導体構造が同一のトランジスタである。ここで、PMOSセンストランジスタM2のオン抵抗Ron2は、センス抵抗Rsenよりも十分に大きい。このとき、PMOS出力トランジスタM1とPMOSセンストランジスタM2とに流れる電流の比は、1:1/Nになるので、PMOS出力トランジスタM1が流す電流をIout、電源Vinの電圧を「Vin」で表すと、ノードN1の電位Vsenは、以下の式[数1]で表される。この電位Vsenは、比較器2の反転入力端子の入力信号(電圧)となる。

[数1]

Vsen=Vin−Rsen×Iout/N

【0005】

また、基準抵抗Rrefに定電流源I1の定電流Irefが流れることで、ノードN2の電位Vrefは、以下の式[数2]で表される。この電位Vrefは、比較器2の非反転入力端子の入力信号(電圧)となる。

[数2]

Vref=Vin−Iref×Rref

【0006】

比較器2は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路110に入力されている。出力信号Vlimが“H”になると、RSフリップフロップ8にリセット信号が入力されて瞬時にPMOS出力トランジスタM1がオフされ、発振器12から次のセットパルスがRSフリップフロップ8に入力されるまでの間、PMOS出力トランジスタM1をオフさせることになる。

【0007】

ここでVsen=Vrefとなるときに、PMOS出力トランジスタM1に流れる電流をIlimとすると、Ilimは以下の式[数3]で表される。

[数3]

Ilim=Iref×Rref×N/Rsen

従って、定電流Iref、基準抵抗Rref、センス抵抗Rsen、及びサイズ比Nを調整することにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となったときにPMOS出力トランジスタM1をオフさせるように制御できる。

【0008】

図3は、従来技術による別のDC−DCコンバータ201の回路図である。図3に示すDC−DCコンバータ201は、図2に示すDC−DCコンバータ101と略同様のものであるが、図2に示す電流制限回路111とは異なる電流制限回路211を含む。

【0009】

図3に示す電流制限回路211は、基準抵抗Rref、定電流源I1、比較器1で構成されている。

【0010】

次に、図3に示す従来技術に係る電流制限回路211の動作について説明する。PMOS出力トランジスタM1が流す電流をIoutとし、PMOS出力トランジスタM1のオン抵抗をRon1とすると、ノードN1の電位Vsenは、以下の式[数4]で表される。この電位Vsenは、比較器2の反転入力端子の入力信号(電圧)となる。

[数4]

Vsen=Vin−Ron1×Iout

【0011】

また、基準抵抗Rrefに定電流源I1の定電流Irefが流れることでノードN2の電位Vrefは、以下の式[数5]で表される。この電位Vrefは、比較器2の非反転入力端子の入力信号(電圧)となる。

[数5]

Vref=Vin−Iref×Rref

【0012】

比較器1は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路210に入力されている。出力信号Vlimが“H”になると、RSフリップフロップ8にリセット信号が入力されて瞬時にPMOS出力トランジスタM1がオフされ、発振器12から次のセットパルスがRSフリップフロップ8に入力されるまでの間、PMOS出力トランジスタM1をオフさせることになる。

【0013】

ここで、Vsen=Vrefとなるときに、PMOS出力トランジスタM1に流れる電流をIlimとすると、Ilimは、以下の式[数6]で表される。

[数6]

Ilim=Iref×Rref/Ron1

従って、定電流Iref、及び基準抵抗Rrefを調整することにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となったときにPMOS出力トランジスタM1をオフさせるように制御できる。

【発明の概要】

【発明が解決しようとする課題】

【0014】

図2に示す従来技術に係る電流制限回路111は、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さく、且つ、基準抵抗Rrefとセンス抵抗Rsenの比が一定である」という条件を満たさなければならない。しかしながら、PMOSセンストランジスタM2のオン抵抗Ron2は、製造プロセス、温度、及び、電源電圧の変動によって大きく変動するため、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さい」という条件を満たすには、一般的にはセンス抵抗Rsenの値を極めて小さく設定する必要がある。

【0015】

センス抵抗Rsenの値が極めて小さく設定すると、電流制限がかかるべきときに(即ち、スイッチ素子を流れる電流が所定値に達したときに)、センス抵抗Rsenの両端に生じる電位差が小さくなる。そうすると、比較器2の出力が、比較器2のオフセット電圧のばらつきによる影響を大きく受ける、という問題が生じる。同時に、電流制限回路111は潜在的にノイズ耐性が低いという問題が生じる。

【0016】

比較器2のオフセット電圧のばらつきの影響に関してトリミング等によりその影響を無視できるようにしたとしても、センス抵抗Rsenにポリシリコンを抵抗素材として用いた場合は、センス抵抗Rsen若しくは基準抵抗Rrefの抵抗素子サイズが大きくなるという問題が生じる。また、メタルをセンス抵抗Rsenの抵抗素材として用いた場合には、基準抵抗Rrefの抵抗素材とは異なるものであるため、製造プロセスや温度などの変動の影響によって「Rref/Rsenが一定である」という条件を満たせない、という問題が生じる。

【0017】

このように、図2に示す従来技術に係る電流制限回路111は、潜在的にノイズ耐性が低いという問題を抱えており、且つ、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さく、且つ、基準抵抗Rrefとセンス抵抗Rsenの比が一定である」という条件を完全に満たすことは現実的には難しい。従って、図2に示す電流制限回路111は、実際には、相応の誤差を見込んで設計されている。

【0018】

また、図3に示す従来技術に係る電流制限回路211は、PMOS出力トランジスタM1のソース−ドレイン間の電位差を監視しているため、その電位差の絶対値は大きくなる。よって、そのノイズ耐性が向上すると共に、比較器2のオフセット電圧のばらつきの影響を受けにくくなることから制限電流値Ilimのばらつきも低減できる。しかしならが、図3に示す電流制限回路211では「Rref/Ron1が一定である」という条件の下で制限電流値Ilimが一定となるところ、製造プロセス、温度、電源電圧の変動によりオン抵抗Ron1は大きく変動する。従って、この条件を常に満たすことは困難であるという問題が生じる。

【0019】

上述の問題点を踏まえて、本発明は、ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い電流制限回路を提供することを目的とする。

【課題を解決するための手段】

【0020】

本発明は、上記の目的を達成するために為されたものである。本発明に係る、スイッチ素子である出力トランジスタに対する電流制限回路は、

基準トランジスタと、

前記基準トランジスタに所定の電流を流す電流源と、

前記出力トランジスタがオンした時の両端の第1の電位差と前記基準トランジスタの両端の第2の電位差を比較する比較器であって、前記第1の電位差が、前記第2の電位差よりも大きくなった場合に、前記出力トランジスタをオフするように制御する電流制限信号を出力する、比較器と

を備え、

前記基準トランジスタは、前記出力トランジスタとは素子サイズの異なる、半導体構造が同一のトランジスタであり、前記基準トランジスタがオンした時のオン抵抗は、前記出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、前記基準トランジスタがオンするように前記基準トランジスタのゲートにバイアスがかけられていることを特徴とする。

【発明の効果】

【0021】

本発明に係る電流制限回路は、スイッチ素子である出力トランジスタと半導体構造が同一でサイズ比の異なるトランジスタを基準トランジスタとして用いるので、温度、製造プロセス、及び電源電圧の変動が生じても制限電流値は変動することがなく、よって精度の高い電流制限を行うことができる。更に、本発明に係る電流制限回路は、出力トランジスタの両端に生じる電位差を監視しているため、ノイズや比較器のオフセット電圧のばらつきの影響を受けにくく、よって安定性のある電流制限を行うことができる。

【図面の簡単な説明】

【0022】

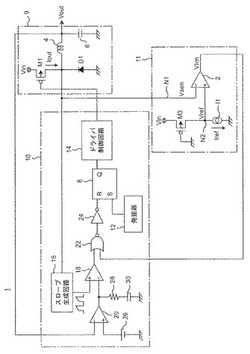

【図1】本発明の第1の実施形態に係るDC−DCコンバータの回路図である。

【図2】従来技術によるDC−DCコンバータの回路図である。

【図3】従来技術による別のDC−DCコンバータの回路図である。

【発明を実施するための形態】

【0023】

以下、図面を参照して、本発明に係る好適な実施形態を説明する。

【0024】

[第1の実施形態]

図1は、本発明の第1の実施形態に係るDC−DCコンバータ1の回路図である。第1の実施形態に係るDC−DCコンバータ1を構成する電流制限回路11は、スイッチ素子であるPMOS出力トランジスタM1と半導体構造が同一でサイズ比の異なる素子(PMOS基準トランジスタM3)を基準トランジスタとして用いるので、製造プロセス、温度、及び電源電圧の変動が生じたとしても制限電流値は変動しない。更に、電流制限回路11は、スイッチ素子(PMOS出力トランジスタM1)の両端に生じる電位差を監視しているので、比較器のオフセット電圧のばらつきやノイズの影響を受けにくい。

【0025】

第1の実施形態に係る電流制限回路及びそれを含むDC−DCコンバータに関する構成及び動作について、以下、説明する。

【0026】

1.DC−DCコンバータの構成

図1に示すDC−DCコンバータ1は、スイッチ素子(出力トランジスタ)であるPMOS出力トランジスタM1と整流素子であるダイオードD1とを用いる降圧型のDC−DCコンバータである。DC−DCコンバータ1は、主として、出力回路9、DC−DCコンバータ制御回路10、及び電流制限回路11により構成される。DC−DCコンバータ制御回路10は、電流モード制御型のものである。なお、図1に示すように、PMOS出力トランジスタM1は、PMOSトランジスタのハイ・サイド・スイッチ素子である。

【0027】

1.1.出力回路の構成

出力回路9はDC−DCコンバータ1の出力電圧を出力する回路であり、電源Vin、PMOS出力トランジスタM1、ダイオードD1、インダクタ4、及び、第1のキャパシタ6を含む。電源Vinの端子はPMOS出力トランジスタM1のソースに接続されている。PMOS出力トランジスタM1のドレインはダイオードD1のカソードに接続されている。ダイオードD1のアノードは接地に接続されている。更に、PMOS出力トランジスタM1のドレインとダイオードD1のカソードとが接続されるノードにはインダクタ4の一端が接続され、インダクタ4の他端は出力電圧Voutの端子に接続される。また、インダクタ4の他端と接地との間には第1のキャパシタ6が設けられている。

【0028】

PMOS出力トランジスタM1がオンであるとき、インダクタ4には電流が流れる。インダクタ4に流れる電流が増加すると、電源Vinの電圧と出力電圧Voutとの電位差に相当するエネルギがインダクタ4及び第1のキャパシタ6に蓄積される。後で説明する、PMOS出力トランジスタM1がオフの状態であるときには、インダクタ4及び第1のキャパシタ6に蓄積されたエネルギによる電流がダイオードD1を介して出力Voutに供給され、これによりDC−DCコンバータ1は継続して出力を行う。

【0029】

1.2.DC−DCコンバータ制御回路の構成

DC−DCコンバータ制御回路10は、スイッチ素子であるPMOS出力トランジスタM1のスイッチを行う駆動信号を制御する回路であり、ドライバ制御回路14、スロープ生成回路16、RSフリップフロップ8、発振器12、インバータ24、ノア回路22、PWMコンパレータ18、オペアンプ(誤差増幅器)20、電圧源26、抵抗28、及び、第2のキャパシタ30を含む。

【0030】

オペアンプ(誤差増幅器)20の反転入力端子には、出力回路9の出力電圧Voutが帰還電圧として入力される。オペアンプ(誤差増幅器)20の非反転入力端子には、電源源26による定電圧が入力される。オペアンプ(誤差増幅器)20は、電源源26による定電圧と出力回路9の出力電圧(帰還電圧)Voutとの差を増幅して出力する。オペアンプ(誤差増幅器)20の出力電圧は、抵抗28及び第2のキャパシタ30により構成される位相補償回路による位相補償を介して、PWMコンパレータ18の反転入力端子に入力される。

【0031】

スロープ生成回路16は、PMOS出力トランジスタM1のドレイン、ダイオードD1のカソード、及び、インダクタ4の一端が接続されるノードN1からの出力信号を入力する。スロープ生成回路16は、スロープ波(鋸波)を生成するスロープ生成部(図示せず)を有しており、上記のインダクタ4の一端が接続されるノードN1からの出力信号に対して、スロープ生成部により生成された固定スロープを重畳する。なお、スロープ生成回路16は、PWMコンパレータのオンデューティ比が50%以上のときに発生する、いわゆるサブハーモニック発振を防止するために設けられている。スロープ生成回路16からの出力信号は、PWMコンパレータ18の非反転入力端子に入力される。

【0032】

PWMコンパレータ18は、スロープ生成回路16からの出力信号(電圧)が、オペアンプ(誤差増幅器)20の出力信号(電圧)よりも高いとき、H信号を出力し、スロープ生成回路16からの出力信号(電圧)が、オペアンプ(誤差増幅器)20の出力信号(電圧)よりも低いとき、L信号を出力する。ここで、スロープ生成回路16は周期的なスロープ波(鋸波)を出力する。一方、(上記位相補償回路の作用も受ける)オペアンプ(誤差増幅器)20はほぼ一定の電圧を出力する。よって、スロープ生成回路16の出力する周期的なスロープ波が、オペアンプ(誤差増幅器)20の出力するほぼ一定の電圧よりも、周期的に高くなるときに、PWMコンパレータ18はH信号を出力する。

【0033】

PWMコンパレータ1の出力信号は、ノア回路22の一方の入力端子に入力するように構成されている。従って、PWMコンパレータ18の出力するH信号は、ノア回路22及びインバータ24を経由して、RSフリップフロップ8のリセット端子Rにリセット信号として入力される。これを受けて、リセットされたRSフリップフロップ8のQ出力にオフ信号が出力される。ドライバ制御回路14は、RSフリップフロップ8のQ出力を入力して、PMOS出力トランジスタM1のスイッチングに係る駆動信号を出力するように構成されている。よって、リセットされたRSフリップフロップ8のQ出力のオフ信号を受けたドライバ制御回路14は、即座にL信号を出力してPMOS出力トランジスタM1をオフさせる。

【0034】

従って、スロープ生成回路16の出力する周期的なスロープ波が、ほぼ一定の電圧(即ち、オペアンプ20の出力するほぼ一定の電圧)よりも周期的に高くなるとき、PMOS出力トランジスタM1がオフされることになる。このことにより、前述のサブハーモニック発振が防止される。

【0035】

RSフリップフロップ8のセット端子Sには、発振器12のセットパルスが入力するように構成されている。リセットされたRSフリップフロップ8は、発振器12のセットパルスにより再びセットされ、これによりRSフリップフロップ8のQ出力にオン信号が出力される。RSフリップフロップ8のQ出力のオン信号を受けたドライバ制御回路14は、即座にH信号を出力してPMOS出力トランジスタM1をオンさせる。このように、RSフリップフロップ8においては、PWMコンパレータ18の出力するH信号によるリセットと、発振器12のセットパルスによるセットとが、繰り返される。

【0036】

更に、DC−DCコンバータ制御回路10のノア回路22のもう一方の入力端子には、以下で説明する、電流制限回路11の比較器2の出力信号が入力するように構成されている。

【0037】

1.3.電流制限回路の構成

電流制限回路11は、スイッチ素子であるPMOS出力トランジスタM1に流れる電流が所定値以上となったことを検出すると、PMOS出力トランジスタM1をオフさせる信号をDC−DCコンバータ制御回路10(のノア回路22のもう一方の入力端子)に出力する回路であり、電源Vin、比較器2、PMOS基準トランジスタM3、及び、定電流源I1で構成されている。

【0038】

本実施形態では、PMOS基準トランジスタM3は、PMOS出力トランジスタM1と半導体構造が同一のものであり、PMOS出力トランジスタM1と素子サイズが異なる。PMOS出力トランジスタM1の方が、PMOS基準トランジスタM3よりも素子サイズが大きい。

【0039】

電源Vinの端子はPMOS基準トランジスタM3のソースに繋がっている。PMOS基準トランジスタM3のドレインは定電流源I1の一方の端子に繋がり、定電流源I1のもう一方の端子は接地に繋がっている。PMOS基準トランジスタM3のゲートには、接地電位の反転が繋げられている。即ち、スイッチ素子としてのPMOS基準トランジスタM3がオンとなるようにゲートはバイアスされている。

【0040】

比較器2の反転出力端子にはPMOS出力トランジスタのドレイン出力が入力するように、比較器2の非反転入力端子にはPMOS基準トランジスタM3のドレイン出力が入力するように、それぞれ、接続されている。比較器2の出力信号は、DC−DCコンバータ制御回路10のノア回路22の一方の入力端子に入力するように構成されている。

【0041】

2.本実施形態に係る電流制限回路の動作

第1の実施形態に係る電流制限回路10の動作、及び、それに関連するDC−DCコンバータ1の動作について述べる。

【0042】

電源Vinの電圧を「Vin」で表し、更に、スイッチ素子であるPMOS出力トランジスタM1に流れる電流をIoutとし、PMOS出力トランジスタM1のオン抵抗をRon1とすると、PMOS出力トランジスタM1のドレインに繋がるノードN1の電位Vsenは、以下の式[数7]で表される。この電位Vsenが、比較器2の反転入力端子の入力信号(電圧)となる。

[数7]

Vsen=Vin−Ron1×Iout

【0043】

また、PMOS基準トランジスタM3のオン抵抗をRon3とすると、PMOS基準トランジスタM3に定電流源I1の定電流Irefが流れることにより、PMOS基準トランジスタM3のドレインに繋がるノードN2の電位Vrefは、以下の[数8]で表される。この電位Vrefが、比較器2の非反転入力端子の入力信号(電圧)となる。

[数8]

Vref=Vin−Iref×Ron3

【0044】

よって、比較器2は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路10のノア回路24の一方の入力端子に入力されている。ここで、出力信号VlimがH信号になると、該H信号は、ノア回路22及びインバータ8を通過して、RSフリップフロップ8のリセット端子Rにリセット信号として入力される。これを受けて、リセットされたRSフリップフロップ8のQ出力にオフ信号が出力される。ドライバ制御回路14は、RSフリップフロップ8のQ出力を入力して、PMOS出力トランジスタM1のスイッチングに係る駆動信号を出力するように構成されている。よって、リセットされたRSフリップフロップ8のQ出力のオフ信号を受けたドライバ制御回路14は、即座にL信号を出力してPMOS出力トランジスタM1をオフさせる。

【0045】

発振器12から次のセットパルスがRSフリップフロップ8のセット端子Sに入力されるまでの間、PMOS出力トランジスタM1はオフとなる。従って、DC−DCコンバータ制御回路10は、RSフリップフロップ8において、PWMコンパレータ18の出力するH信号、及び、比較器2の出力する出力信号VlimのH信号によるリセットと、発振器12のセットパルスによるセットとが、繰り返されることになる。

【0046】

ここで、Vsen=VrefとなるときにPMOS出力トランジスタM1が流す電流をIlimとすると、[数7]及び[数8]により、Ilimは以下の式[数9]で表される。

[数9]

Ilim=Iref×Ron3/Ron1

【0047】

PMOS出力トランジスタM1とPMOS基準トランジスタM3とは半導体構造が同一の素子であるので、製造プロセスの変動や温度の変動があっても、「Ron3/Ron1」の値は一定となる。また、PMOS出力トランジスタM1がオンしているときのゲート−ソース電圧と、PMOS基準トランジスタM3のゲート−ソース電圧とは、いずれも「Vin」となるため、このことからも「Ron3/Ron1」の値は一定となる。従って、PMOS出力トランジスタM1とPMOS基準トランジスタM3のサイズ比が「N:1」(Nは1より大きい数)であるとすると、電流Ilimは以下の式[10]で表される。

[数10]

Ilim=Iref×N

【0048】

よって、定電流Irefとサイズ比Nとを調整することにより、電流Ilimを適宜調整できる。このことにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となった場合にPMOS出力トランジスタM1をオフさせる条件を、適切なものにすることができる。

【0049】

つまり、定電流Irefは、電源電圧の変動や温度の変動に依らず一定となるように設計することができ、製造プロセスの変動に対してもトリミングによる調整などによって一定とすることができる。また、サイズ比Nは、PMOS出力トランジスタM1とPMOS基準トランジスタM3のレイアウトを工夫することによって、そのばらつきを小さくすることができる。よって、本実施形態では、電源電圧、温度、及び製造プロセスにおいて変動が生じても、制限電流値Ilimを変動しないように構成できる。

【0050】

また、本実施形態では、PMOS出力トランジスタM1のソース−ドレイン間の電位差が監視されているので、PMOSセンストランジスタとセンス抵抗を用いてセンス抵抗の両端に生じる電位差を監視する従来技術の電流制御回路(図2参照)に比べて、電位差の絶対値は大きくなる。従って、本実施形態では、ノイズ耐性が向上すると共に、比較器のオフセット電圧のばらつきの影響を受けにくくなるため、制限電流値のばらつきを低減できる。

【0051】

3.まとめ

本実施形態に係る電流制限回路11では、PMOS出力トランジスタM1と半導体構造が同一のPMOS基準トランジスタM3を用いて、基準の電位Vrefを生成する。このような電流制限回路11を設けることにより、電源電圧、温度、及び、製造プロセスに変動が生じてもスイッチ素子が流す電流に対して高精度で制限を掛けることができる。また、スイッチ素子(PMOS出力トランジスタM1)の両端に生じる電位差を監視しているため、ノイズ耐性が高く、比較器のオフセット電圧のばらつきの影響を受けにくい。

【0052】

[その他の実施形態]

本発明は、前述の第1の実施形態のみに限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能である。

【0053】

前述の第1の実施形態は、PMOSトランジスタのハイ・サイド・スイッチ素子に対する電流制限回路であるが、本発明は、NMOSトランジスタのハイ・サイド・スイッチ素子の場合やNMOSトランジスタのロー・サイド・スイッチ素子に対しても、同様に適用できる。また、本発明は、MOSトランジスタではなく、バイポーラ・トランジスタにも同様に適用できる。すなわち、本発明は、様々なスイッチ素子に対する電流制限回路に広く適用可能である。

【符号の説明】

【0054】

1、101、201・・・DC−DCコンバータ、2・・・比較器、4・・・インダクタ、6・・・第1のキャパシタ、8・・・RSフリップフロップ、9・・・出力回路、10・・・DC−DCコンバータ制御回路、11・・・電流制御回路、12・・・発振器、14・・・ドライバ制御回路、16・・・スロープ生成回路、18・・・PWMコンパレータ、20・・・オペアンプ(誤差増幅器)、22・・・ノア回路、24・・・インバータ、26・・・電圧源、28・・・抵抗、30・・・第2のキャパシタ。

【先行技術文献】

【特許文献】

【0055】

本願発明の先行技術文献として、以下のものが挙げられる。

【特許文献1】特開2010−239832号公報

【特許文献2】特開2010−066984号公報

【技術分野】

【0001】

本発明は、DC−DCコンバータにおいて、スイッチ素子が流す電流が所定の電流値以上となった場合にスイッチ素子をオフさせる電流制限回路に関する。

【背景技術】

【0002】

図2は、従来技術によるDC−DCコンバータ101の回路図である。図2に示すDC−DCコンバータ101は、スイッチ素子が流す電流値が所定の電流値以上となったことを検出すると、スイッチ素子をオフさせる従来のDC−DCコンバータの電流制限回路111を含む。

【0003】

図2に示すDC−DCコンバータ101は、スイッチ素子(出力トランジスタ)であるPMOS出力トランジスタM1と整流素子であるダイオードD1とを用いる降圧型のDC−DCコンバータである。PMOS出力トランジスタM1をスイッチング制御するDC−DCコンバータ制御回路110は、電流モード制御型のものである。PMOS出力トランジスタM1に流れる電流Ioutが所定の電流値以上となった場合に、DC−DCコンバータ制御回路110を介して、PMOS出力トランジスタM1をオフさせる電流制限回路111は、センス抵抗Rsen、PMOSセンストランジスタM2、基準抵抗Rref、定電流源I1、比較器2で構成されている。

【0004】

次に、図2に示す従来技術に係る電流制限回路111の動作について説明する。PMOS出力トランジスタM1とPMOSセンストランジスタM2とは、サイズ比がN:1で、半導体構造が同一のトランジスタである。ここで、PMOSセンストランジスタM2のオン抵抗Ron2は、センス抵抗Rsenよりも十分に大きい。このとき、PMOS出力トランジスタM1とPMOSセンストランジスタM2とに流れる電流の比は、1:1/Nになるので、PMOS出力トランジスタM1が流す電流をIout、電源Vinの電圧を「Vin」で表すと、ノードN1の電位Vsenは、以下の式[数1]で表される。この電位Vsenは、比較器2の反転入力端子の入力信号(電圧)となる。

[数1]

Vsen=Vin−Rsen×Iout/N

【0005】

また、基準抵抗Rrefに定電流源I1の定電流Irefが流れることで、ノードN2の電位Vrefは、以下の式[数2]で表される。この電位Vrefは、比較器2の非反転入力端子の入力信号(電圧)となる。

[数2]

Vref=Vin−Iref×Rref

【0006】

比較器2は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路110に入力されている。出力信号Vlimが“H”になると、RSフリップフロップ8にリセット信号が入力されて瞬時にPMOS出力トランジスタM1がオフされ、発振器12から次のセットパルスがRSフリップフロップ8に入力されるまでの間、PMOS出力トランジスタM1をオフさせることになる。

【0007】

ここでVsen=Vrefとなるときに、PMOS出力トランジスタM1に流れる電流をIlimとすると、Ilimは以下の式[数3]で表される。

[数3]

Ilim=Iref×Rref×N/Rsen

従って、定電流Iref、基準抵抗Rref、センス抵抗Rsen、及びサイズ比Nを調整することにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となったときにPMOS出力トランジスタM1をオフさせるように制御できる。

【0008】

図3は、従来技術による別のDC−DCコンバータ201の回路図である。図3に示すDC−DCコンバータ201は、図2に示すDC−DCコンバータ101と略同様のものであるが、図2に示す電流制限回路111とは異なる電流制限回路211を含む。

【0009】

図3に示す電流制限回路211は、基準抵抗Rref、定電流源I1、比較器1で構成されている。

【0010】

次に、図3に示す従来技術に係る電流制限回路211の動作について説明する。PMOS出力トランジスタM1が流す電流をIoutとし、PMOS出力トランジスタM1のオン抵抗をRon1とすると、ノードN1の電位Vsenは、以下の式[数4]で表される。この電位Vsenは、比較器2の反転入力端子の入力信号(電圧)となる。

[数4]

Vsen=Vin−Ron1×Iout

【0011】

また、基準抵抗Rrefに定電流源I1の定電流Irefが流れることでノードN2の電位Vrefは、以下の式[数5]で表される。この電位Vrefは、比較器2の非反転入力端子の入力信号(電圧)となる。

[数5]

Vref=Vin−Iref×Rref

【0012】

比較器1は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路210に入力されている。出力信号Vlimが“H”になると、RSフリップフロップ8にリセット信号が入力されて瞬時にPMOS出力トランジスタM1がオフされ、発振器12から次のセットパルスがRSフリップフロップ8に入力されるまでの間、PMOS出力トランジスタM1をオフさせることになる。

【0013】

ここで、Vsen=Vrefとなるときに、PMOS出力トランジスタM1に流れる電流をIlimとすると、Ilimは、以下の式[数6]で表される。

[数6]

Ilim=Iref×Rref/Ron1

従って、定電流Iref、及び基準抵抗Rrefを調整することにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となったときにPMOS出力トランジスタM1をオフさせるように制御できる。

【発明の概要】

【発明が解決しようとする課題】

【0014】

図2に示す従来技術に係る電流制限回路111は、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さく、且つ、基準抵抗Rrefとセンス抵抗Rsenの比が一定である」という条件を満たさなければならない。しかしながら、PMOSセンストランジスタM2のオン抵抗Ron2は、製造プロセス、温度、及び、電源電圧の変動によって大きく変動するため、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さい」という条件を満たすには、一般的にはセンス抵抗Rsenの値を極めて小さく設定する必要がある。

【0015】

センス抵抗Rsenの値が極めて小さく設定すると、電流制限がかかるべきときに(即ち、スイッチ素子を流れる電流が所定値に達したときに)、センス抵抗Rsenの両端に生じる電位差が小さくなる。そうすると、比較器2の出力が、比較器2のオフセット電圧のばらつきによる影響を大きく受ける、という問題が生じる。同時に、電流制限回路111は潜在的にノイズ耐性が低いという問題が生じる。

【0016】

比較器2のオフセット電圧のばらつきの影響に関してトリミング等によりその影響を無視できるようにしたとしても、センス抵抗Rsenにポリシリコンを抵抗素材として用いた場合は、センス抵抗Rsen若しくは基準抵抗Rrefの抵抗素子サイズが大きくなるという問題が生じる。また、メタルをセンス抵抗Rsenの抵抗素材として用いた場合には、基準抵抗Rrefの抵抗素材とは異なるものであるため、製造プロセスや温度などの変動の影響によって「Rref/Rsenが一定である」という条件を満たせない、という問題が生じる。

【0017】

このように、図2に示す従来技術に係る電流制限回路111は、潜在的にノイズ耐性が低いという問題を抱えており、且つ、「センス抵抗RsenがPMOSセンストランジスタM2のオン抵抗Ron2に比べて十分に小さく、且つ、基準抵抗Rrefとセンス抵抗Rsenの比が一定である」という条件を完全に満たすことは現実的には難しい。従って、図2に示す電流制限回路111は、実際には、相応の誤差を見込んで設計されている。

【0018】

また、図3に示す従来技術に係る電流制限回路211は、PMOS出力トランジスタM1のソース−ドレイン間の電位差を監視しているため、その電位差の絶対値は大きくなる。よって、そのノイズ耐性が向上すると共に、比較器2のオフセット電圧のばらつきの影響を受けにくくなることから制限電流値Ilimのばらつきも低減できる。しかしならが、図3に示す電流制限回路211では「Rref/Ron1が一定である」という条件の下で制限電流値Ilimが一定となるところ、製造プロセス、温度、電源電圧の変動によりオン抵抗Ron1は大きく変動する。従って、この条件を常に満たすことは困難であるという問題が生じる。

【0019】

上述の問題点を踏まえて、本発明は、ノイズ耐性が高く、且つ、製造プロセス、電源、及び電源電圧が変動するような場合においても精度が高い電流制限回路を提供することを目的とする。

【課題を解決するための手段】

【0020】

本発明は、上記の目的を達成するために為されたものである。本発明に係る、スイッチ素子である出力トランジスタに対する電流制限回路は、

基準トランジスタと、

前記基準トランジスタに所定の電流を流す電流源と、

前記出力トランジスタがオンした時の両端の第1の電位差と前記基準トランジスタの両端の第2の電位差を比較する比較器であって、前記第1の電位差が、前記第2の電位差よりも大きくなった場合に、前記出力トランジスタをオフするように制御する電流制限信号を出力する、比較器と

を備え、

前記基準トランジスタは、前記出力トランジスタとは素子サイズの異なる、半導体構造が同一のトランジスタであり、前記基準トランジスタがオンした時のオン抵抗は、前記出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、前記基準トランジスタがオンするように前記基準トランジスタのゲートにバイアスがかけられていることを特徴とする。

【発明の効果】

【0021】

本発明に係る電流制限回路は、スイッチ素子である出力トランジスタと半導体構造が同一でサイズ比の異なるトランジスタを基準トランジスタとして用いるので、温度、製造プロセス、及び電源電圧の変動が生じても制限電流値は変動することがなく、よって精度の高い電流制限を行うことができる。更に、本発明に係る電流制限回路は、出力トランジスタの両端に生じる電位差を監視しているため、ノイズや比較器のオフセット電圧のばらつきの影響を受けにくく、よって安定性のある電流制限を行うことができる。

【図面の簡単な説明】

【0022】

【図1】本発明の第1の実施形態に係るDC−DCコンバータの回路図である。

【図2】従来技術によるDC−DCコンバータの回路図である。

【図3】従来技術による別のDC−DCコンバータの回路図である。

【発明を実施するための形態】

【0023】

以下、図面を参照して、本発明に係る好適な実施形態を説明する。

【0024】

[第1の実施形態]

図1は、本発明の第1の実施形態に係るDC−DCコンバータ1の回路図である。第1の実施形態に係るDC−DCコンバータ1を構成する電流制限回路11は、スイッチ素子であるPMOS出力トランジスタM1と半導体構造が同一でサイズ比の異なる素子(PMOS基準トランジスタM3)を基準トランジスタとして用いるので、製造プロセス、温度、及び電源電圧の変動が生じたとしても制限電流値は変動しない。更に、電流制限回路11は、スイッチ素子(PMOS出力トランジスタM1)の両端に生じる電位差を監視しているので、比較器のオフセット電圧のばらつきやノイズの影響を受けにくい。

【0025】

第1の実施形態に係る電流制限回路及びそれを含むDC−DCコンバータに関する構成及び動作について、以下、説明する。

【0026】

1.DC−DCコンバータの構成

図1に示すDC−DCコンバータ1は、スイッチ素子(出力トランジスタ)であるPMOS出力トランジスタM1と整流素子であるダイオードD1とを用いる降圧型のDC−DCコンバータである。DC−DCコンバータ1は、主として、出力回路9、DC−DCコンバータ制御回路10、及び電流制限回路11により構成される。DC−DCコンバータ制御回路10は、電流モード制御型のものである。なお、図1に示すように、PMOS出力トランジスタM1は、PMOSトランジスタのハイ・サイド・スイッチ素子である。

【0027】

1.1.出力回路の構成

出力回路9はDC−DCコンバータ1の出力電圧を出力する回路であり、電源Vin、PMOS出力トランジスタM1、ダイオードD1、インダクタ4、及び、第1のキャパシタ6を含む。電源Vinの端子はPMOS出力トランジスタM1のソースに接続されている。PMOS出力トランジスタM1のドレインはダイオードD1のカソードに接続されている。ダイオードD1のアノードは接地に接続されている。更に、PMOS出力トランジスタM1のドレインとダイオードD1のカソードとが接続されるノードにはインダクタ4の一端が接続され、インダクタ4の他端は出力電圧Voutの端子に接続される。また、インダクタ4の他端と接地との間には第1のキャパシタ6が設けられている。

【0028】

PMOS出力トランジスタM1がオンであるとき、インダクタ4には電流が流れる。インダクタ4に流れる電流が増加すると、電源Vinの電圧と出力電圧Voutとの電位差に相当するエネルギがインダクタ4及び第1のキャパシタ6に蓄積される。後で説明する、PMOS出力トランジスタM1がオフの状態であるときには、インダクタ4及び第1のキャパシタ6に蓄積されたエネルギによる電流がダイオードD1を介して出力Voutに供給され、これによりDC−DCコンバータ1は継続して出力を行う。

【0029】

1.2.DC−DCコンバータ制御回路の構成

DC−DCコンバータ制御回路10は、スイッチ素子であるPMOS出力トランジスタM1のスイッチを行う駆動信号を制御する回路であり、ドライバ制御回路14、スロープ生成回路16、RSフリップフロップ8、発振器12、インバータ24、ノア回路22、PWMコンパレータ18、オペアンプ(誤差増幅器)20、電圧源26、抵抗28、及び、第2のキャパシタ30を含む。

【0030】

オペアンプ(誤差増幅器)20の反転入力端子には、出力回路9の出力電圧Voutが帰還電圧として入力される。オペアンプ(誤差増幅器)20の非反転入力端子には、電源源26による定電圧が入力される。オペアンプ(誤差増幅器)20は、電源源26による定電圧と出力回路9の出力電圧(帰還電圧)Voutとの差を増幅して出力する。オペアンプ(誤差増幅器)20の出力電圧は、抵抗28及び第2のキャパシタ30により構成される位相補償回路による位相補償を介して、PWMコンパレータ18の反転入力端子に入力される。

【0031】

スロープ生成回路16は、PMOS出力トランジスタM1のドレイン、ダイオードD1のカソード、及び、インダクタ4の一端が接続されるノードN1からの出力信号を入力する。スロープ生成回路16は、スロープ波(鋸波)を生成するスロープ生成部(図示せず)を有しており、上記のインダクタ4の一端が接続されるノードN1からの出力信号に対して、スロープ生成部により生成された固定スロープを重畳する。なお、スロープ生成回路16は、PWMコンパレータのオンデューティ比が50%以上のときに発生する、いわゆるサブハーモニック発振を防止するために設けられている。スロープ生成回路16からの出力信号は、PWMコンパレータ18の非反転入力端子に入力される。

【0032】

PWMコンパレータ18は、スロープ生成回路16からの出力信号(電圧)が、オペアンプ(誤差増幅器)20の出力信号(電圧)よりも高いとき、H信号を出力し、スロープ生成回路16からの出力信号(電圧)が、オペアンプ(誤差増幅器)20の出力信号(電圧)よりも低いとき、L信号を出力する。ここで、スロープ生成回路16は周期的なスロープ波(鋸波)を出力する。一方、(上記位相補償回路の作用も受ける)オペアンプ(誤差増幅器)20はほぼ一定の電圧を出力する。よって、スロープ生成回路16の出力する周期的なスロープ波が、オペアンプ(誤差増幅器)20の出力するほぼ一定の電圧よりも、周期的に高くなるときに、PWMコンパレータ18はH信号を出力する。

【0033】

PWMコンパレータ1の出力信号は、ノア回路22の一方の入力端子に入力するように構成されている。従って、PWMコンパレータ18の出力するH信号は、ノア回路22及びインバータ24を経由して、RSフリップフロップ8のリセット端子Rにリセット信号として入力される。これを受けて、リセットされたRSフリップフロップ8のQ出力にオフ信号が出力される。ドライバ制御回路14は、RSフリップフロップ8のQ出力を入力して、PMOS出力トランジスタM1のスイッチングに係る駆動信号を出力するように構成されている。よって、リセットされたRSフリップフロップ8のQ出力のオフ信号を受けたドライバ制御回路14は、即座にL信号を出力してPMOS出力トランジスタM1をオフさせる。

【0034】

従って、スロープ生成回路16の出力する周期的なスロープ波が、ほぼ一定の電圧(即ち、オペアンプ20の出力するほぼ一定の電圧)よりも周期的に高くなるとき、PMOS出力トランジスタM1がオフされることになる。このことにより、前述のサブハーモニック発振が防止される。

【0035】

RSフリップフロップ8のセット端子Sには、発振器12のセットパルスが入力するように構成されている。リセットされたRSフリップフロップ8は、発振器12のセットパルスにより再びセットされ、これによりRSフリップフロップ8のQ出力にオン信号が出力される。RSフリップフロップ8のQ出力のオン信号を受けたドライバ制御回路14は、即座にH信号を出力してPMOS出力トランジスタM1をオンさせる。このように、RSフリップフロップ8においては、PWMコンパレータ18の出力するH信号によるリセットと、発振器12のセットパルスによるセットとが、繰り返される。

【0036】

更に、DC−DCコンバータ制御回路10のノア回路22のもう一方の入力端子には、以下で説明する、電流制限回路11の比較器2の出力信号が入力するように構成されている。

【0037】

1.3.電流制限回路の構成

電流制限回路11は、スイッチ素子であるPMOS出力トランジスタM1に流れる電流が所定値以上となったことを検出すると、PMOS出力トランジスタM1をオフさせる信号をDC−DCコンバータ制御回路10(のノア回路22のもう一方の入力端子)に出力する回路であり、電源Vin、比較器2、PMOS基準トランジスタM3、及び、定電流源I1で構成されている。

【0038】

本実施形態では、PMOS基準トランジスタM3は、PMOS出力トランジスタM1と半導体構造が同一のものであり、PMOS出力トランジスタM1と素子サイズが異なる。PMOS出力トランジスタM1の方が、PMOS基準トランジスタM3よりも素子サイズが大きい。

【0039】

電源Vinの端子はPMOS基準トランジスタM3のソースに繋がっている。PMOS基準トランジスタM3のドレインは定電流源I1の一方の端子に繋がり、定電流源I1のもう一方の端子は接地に繋がっている。PMOS基準トランジスタM3のゲートには、接地電位の反転が繋げられている。即ち、スイッチ素子としてのPMOS基準トランジスタM3がオンとなるようにゲートはバイアスされている。

【0040】

比較器2の反転出力端子にはPMOS出力トランジスタのドレイン出力が入力するように、比較器2の非反転入力端子にはPMOS基準トランジスタM3のドレイン出力が入力するように、それぞれ、接続されている。比較器2の出力信号は、DC−DCコンバータ制御回路10のノア回路22の一方の入力端子に入力するように構成されている。

【0041】

2.本実施形態に係る電流制限回路の動作

第1の実施形態に係る電流制限回路10の動作、及び、それに関連するDC−DCコンバータ1の動作について述べる。

【0042】

電源Vinの電圧を「Vin」で表し、更に、スイッチ素子であるPMOS出力トランジスタM1に流れる電流をIoutとし、PMOS出力トランジスタM1のオン抵抗をRon1とすると、PMOS出力トランジスタM1のドレインに繋がるノードN1の電位Vsenは、以下の式[数7]で表される。この電位Vsenが、比較器2の反転入力端子の入力信号(電圧)となる。

[数7]

Vsen=Vin−Ron1×Iout

【0043】

また、PMOS基準トランジスタM3のオン抵抗をRon3とすると、PMOS基準トランジスタM3に定電流源I1の定電流Irefが流れることにより、PMOS基準トランジスタM3のドレインに繋がるノードN2の電位Vrefは、以下の[数8]で表される。この電位Vrefが、比較器2の非反転入力端子の入力信号(電圧)となる。

[数8]

Vref=Vin−Iref×Ron3

【0044】

よって、比較器2は、Vsen>Vrefのときは、出力信号VlimにL信号を出力し、Vsen≦Vrefのときは、出力信号VlimにH信号を出力する。この出力信号Vlimは、DC−DCコンバータ制御回路10のノア回路24の一方の入力端子に入力されている。ここで、出力信号VlimがH信号になると、該H信号は、ノア回路22及びインバータ8を通過して、RSフリップフロップ8のリセット端子Rにリセット信号として入力される。これを受けて、リセットされたRSフリップフロップ8のQ出力にオフ信号が出力される。ドライバ制御回路14は、RSフリップフロップ8のQ出力を入力して、PMOS出力トランジスタM1のスイッチングに係る駆動信号を出力するように構成されている。よって、リセットされたRSフリップフロップ8のQ出力のオフ信号を受けたドライバ制御回路14は、即座にL信号を出力してPMOS出力トランジスタM1をオフさせる。

【0045】

発振器12から次のセットパルスがRSフリップフロップ8のセット端子Sに入力されるまでの間、PMOS出力トランジスタM1はオフとなる。従って、DC−DCコンバータ制御回路10は、RSフリップフロップ8において、PWMコンパレータ18の出力するH信号、及び、比較器2の出力する出力信号VlimのH信号によるリセットと、発振器12のセットパルスによるセットとが、繰り返されることになる。

【0046】

ここで、Vsen=VrefとなるときにPMOS出力トランジスタM1が流す電流をIlimとすると、[数7]及び[数8]により、Ilimは以下の式[数9]で表される。

[数9]

Ilim=Iref×Ron3/Ron1

【0047】

PMOS出力トランジスタM1とPMOS基準トランジスタM3とは半導体構造が同一の素子であるので、製造プロセスの変動や温度の変動があっても、「Ron3/Ron1」の値は一定となる。また、PMOS出力トランジスタM1がオンしているときのゲート−ソース電圧と、PMOS基準トランジスタM3のゲート−ソース電圧とは、いずれも「Vin」となるため、このことからも「Ron3/Ron1」の値は一定となる。従って、PMOS出力トランジスタM1とPMOS基準トランジスタM3のサイズ比が「N:1」(Nは1より大きい数)であるとすると、電流Ilimは以下の式[10]で表される。

[数10]

Ilim=Iref×N

【0048】

よって、定電流Irefとサイズ比Nとを調整することにより、電流Ilimを適宜調整できる。このことにより、PMOS出力トランジスタM1が流す電流が所定の電流値以上となった場合にPMOS出力トランジスタM1をオフさせる条件を、適切なものにすることができる。

【0049】

つまり、定電流Irefは、電源電圧の変動や温度の変動に依らず一定となるように設計することができ、製造プロセスの変動に対してもトリミングによる調整などによって一定とすることができる。また、サイズ比Nは、PMOS出力トランジスタM1とPMOS基準トランジスタM3のレイアウトを工夫することによって、そのばらつきを小さくすることができる。よって、本実施形態では、電源電圧、温度、及び製造プロセスにおいて変動が生じても、制限電流値Ilimを変動しないように構成できる。

【0050】

また、本実施形態では、PMOS出力トランジスタM1のソース−ドレイン間の電位差が監視されているので、PMOSセンストランジスタとセンス抵抗を用いてセンス抵抗の両端に生じる電位差を監視する従来技術の電流制御回路(図2参照)に比べて、電位差の絶対値は大きくなる。従って、本実施形態では、ノイズ耐性が向上すると共に、比較器のオフセット電圧のばらつきの影響を受けにくくなるため、制限電流値のばらつきを低減できる。

【0051】

3.まとめ

本実施形態に係る電流制限回路11では、PMOS出力トランジスタM1と半導体構造が同一のPMOS基準トランジスタM3を用いて、基準の電位Vrefを生成する。このような電流制限回路11を設けることにより、電源電圧、温度、及び、製造プロセスに変動が生じてもスイッチ素子が流す電流に対して高精度で制限を掛けることができる。また、スイッチ素子(PMOS出力トランジスタM1)の両端に生じる電位差を監視しているため、ノイズ耐性が高く、比較器のオフセット電圧のばらつきの影響を受けにくい。

【0052】

[その他の実施形態]

本発明は、前述の第1の実施形態のみに限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能である。

【0053】

前述の第1の実施形態は、PMOSトランジスタのハイ・サイド・スイッチ素子に対する電流制限回路であるが、本発明は、NMOSトランジスタのハイ・サイド・スイッチ素子の場合やNMOSトランジスタのロー・サイド・スイッチ素子に対しても、同様に適用できる。また、本発明は、MOSトランジスタではなく、バイポーラ・トランジスタにも同様に適用できる。すなわち、本発明は、様々なスイッチ素子に対する電流制限回路に広く適用可能である。

【符号の説明】

【0054】

1、101、201・・・DC−DCコンバータ、2・・・比較器、4・・・インダクタ、6・・・第1のキャパシタ、8・・・RSフリップフロップ、9・・・出力回路、10・・・DC−DCコンバータ制御回路、11・・・電流制御回路、12・・・発振器、14・・・ドライバ制御回路、16・・・スロープ生成回路、18・・・PWMコンパレータ、20・・・オペアンプ(誤差増幅器)、22・・・ノア回路、24・・・インバータ、26・・・電圧源、28・・・抵抗、30・・・第2のキャパシタ。

【先行技術文献】

【特許文献】

【0055】

本願発明の先行技術文献として、以下のものが挙げられる。

【特許文献1】特開2010−239832号公報

【特許文献2】特開2010−066984号公報

【特許請求の範囲】

【請求項1】

スイッチ素子である出力トランジスタに対する電流制限回路において、

基準トランジスタと、

前記基準トランジスタに所定の電流を流す電流源と、

前記出力トランジスタがオンした時の両端の第1の電位差と前記基準トランジスタの両端の第2の電位差を比較する比較器であって、前記第1の電位差が、前記第2の電位差よりも大きくなった場合に、前記出力トランジスタをオフするように制御する電流制限信号を出力する、比較器と

を備え、

前記基準トランジスタは、前記出力トランジスタとは素子サイズの異なる、半導体構造が同一のトランジスタであり、前記基準トランジスタがオンした時のオン抵抗は、前記出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、前記基準トランジスタがオンするように前記基準トランジスタのゲートにバイアスがかけられている

ことを特徴とする電流制限回路。

【請求項2】

接地電位を用いて前記基準トランジスタのゲートにバイアスがかけられている

ことを特徴とする請求項1に記載の電流制限回路。

【請求項3】

請求項1又は2に記載の電流制限回路を備えたことを特徴とするDC−DCコンバータ。

【請求項1】

スイッチ素子である出力トランジスタに対する電流制限回路において、

基準トランジスタと、

前記基準トランジスタに所定の電流を流す電流源と、

前記出力トランジスタがオンした時の両端の第1の電位差と前記基準トランジスタの両端の第2の電位差を比較する比較器であって、前記第1の電位差が、前記第2の電位差よりも大きくなった場合に、前記出力トランジスタをオフするように制御する電流制限信号を出力する、比較器と

を備え、

前記基準トランジスタは、前記出力トランジスタとは素子サイズの異なる、半導体構造が同一のトランジスタであり、前記基準トランジスタがオンした時のオン抵抗は、前記出力トランジスタがオンした時のオン抵抗の1/Nの大きさ(Nは1より大きい数)であり、更に、前記基準トランジスタがオンするように前記基準トランジスタのゲートにバイアスがかけられている

ことを特徴とする電流制限回路。

【請求項2】

接地電位を用いて前記基準トランジスタのゲートにバイアスがかけられている

ことを特徴とする請求項1に記載の電流制限回路。

【請求項3】

請求項1又は2に記載の電流制限回路を備えたことを特徴とするDC−DCコンバータ。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−62986(P2013−62986A)

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願番号】特願2011−201005(P2011−201005)

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年4月4日(2013.4.4)

【国際特許分類】

【出願日】平成23年9月14日(2011.9.14)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]