電流増幅半導体素子の駆動回路

【課題】 電流増幅半導体のベース電流をコレクタ電流に応じた必要最小限の値に制御するようにし、高速で低消費電力の電流増幅半導体素子の駆動回路を提供する。

【解決手段】 2個の直流電源の正側電源2の正極と負極の間に、チョッピング用スイッチング素子4とインダクタ6と被制御電流増幅半導体1のベース及びエミッタとの直列回路を接続するとともに、チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソード及び負側電源3の負極にアノードとなるようダイオード8を接続し、被制御電流増幅半導体のベースと負側電源の負極間に制御用スイッチング素子7を接続した回路構成をなし、被制御電流増幅半導体のコレクタ及びエミッタ間の電圧を検出し、被制御電流増幅半導体がオン状態時に、該電圧が準飽和電圧近辺の2値間になるようにチョッピング用スイッチング素子のオンオフ期間を制御する制御回路5を有する電流増幅半導体の駆動回路。

【解決手段】 2個の直流電源の正側電源2の正極と負極の間に、チョッピング用スイッチング素子4とインダクタ6と被制御電流増幅半導体1のベース及びエミッタとの直列回路を接続するとともに、チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソード及び負側電源3の負極にアノードとなるようダイオード8を接続し、被制御電流増幅半導体のベースと負側電源の負極間に制御用スイッチング素子7を接続した回路構成をなし、被制御電流増幅半導体のコレクタ及びエミッタ間の電圧を検出し、被制御電流増幅半導体がオン状態時に、該電圧が準飽和電圧近辺の2値間になるようにチョッピング用スイッチング素子のオンオフ期間を制御する制御回路5を有する電流増幅半導体の駆動回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はバイポーラトランジスタを初めとする電流増幅半導体をスイッチとして使用するインバータ回路等における該電流増幅半導体素子の駆動回路に関するものである。

【背景技術】

【0002】

電流増幅による半導体はベース(ゲート)から注入される少数キャリアにより、オン状態になるが、伝導度変調の効果により、オン電圧が極めて低いと言う特徴があり、大電流をスイッチングするインバータ回路等に使用されている。

【0003】

しかし、有限の増幅度によりベース(ゲート)に流し込む電流が大きく、このため制御電源が大型化したり、また、電流遮断(ターンオフ)時に、少数キャリアの過剰な蓄積を排出するための時間(ストレージタイム)が存在し、スイッチング周波数が制限される等の理由で、電圧駆動形の絶縁ゲート型バイポーラトランジスタ(IGBT )あるいはユニポーラで少数キャリアの無い、パワーMOS形電界効果トランジスタ(MOSFET)に取って代られているのが現状である。

【0004】

従来の電流増幅によるスイッチング半導体のベース(ゲート)駆動の基本回路として図8に示すものが知られている。

図8において、1は被制御電流増幅半導体で、ここではトランジスタで示す。2,3は直流電源、74,75はそれぞれオンおよびオフ用のスイッチング素子でトランジスタで示す。76はベース電流制限用の抵抗である。

【0005】

すなわち、直列に接続された2個の直流電源2,3とトランジスタ74,75からなるトーテンポール回路および抵抗76からなり、制御信号が印加されると、トランジスタ74がオンし、直流電源2から抵抗76を通してトランジスタ1のベース電流を流す。また、制御信号がオフすると、トランジスタ74がオフしてトランジスタ75がオンし、トランジスタ1のベース−エミッタ間に直流電源3の電圧を逆極性に加えて、少数キャリアを引き抜きターンオフさせ、トランジスタ1の順電圧阻止能力を回復させる。

【0006】

しかるに、図8に示す如きものは、抵抗76の抵抗値は直流電源2の電圧変動範囲の最小値、トランジスタ74のオン時コレクタ−エミッタ間電圧の最大値、トランジスタ1のベース−エミッタ間電圧の最大値および電流増幅率の最小値を考慮して、最大のコレクタ電流において決定されるため、それぞれの値が通常値の場合にはトランジスタ1のベース電流が不必要に多くなるのが通例であり、特にコレクタ電流が低い場合でも同じベース電流が流れてしまい、抵抗6に発生する損失が問題となったり、直流電源の容量が大きくなる欠点を有し、さらには過剰に蓄積されたキャリアによる動作周波数の制限が問題となっている。

【0007】

上述した欠点を補う手段として、後掲する発明人による既出願特許文献1(図9に基本回路を示す)に述べられているように、抵抗を無くしたり、部品のバラツキの影響を除去してベース電流を決定でき、電源電流をチョッピングすることで直流電源の容量を大幅に低減できる方法を提供できたが、最大コレクタ電流時に最小の増幅率でベース電流を決定しなければならない点は解決されていない。

【特許文献1】特公平7−28527号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

上述した図9の場合、直流電源2の電圧、トランジスタ4のオン時コレクタ−エミッタ間電圧、トランジスタ1のベース−エミッタ間電圧の変動等については解決されているが、想定される最大のコレクタ電流において、トランジスタ1の電流増幅率の最小値でベース電流を決定することは変わらず、相変わらず過剰なベース電流および過剰蓄積キャリアの問題は解決されていない。

【0009】

そこで、本発明は、上記問題点に鑑み、過剰な少数キャリアを蓄積させないように、必要最小限のベース(ゲート)電流を供給し、駆動電源の容量およびストレージタイムを低減できる電流増幅半導体の駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

以上のような目的を達成するために、被制御電流増幅半導体のベース(ゲート)に駆動電流を流す手段として、ターンオン初期およびターンオフ時の動作原理は特許文献1に示す従来例と同様であり、電流維持要素としてのインダクタとチョッピング用スイッチング素子を用いチョッピングのデューティサイクルを制御することで、損失無しで、通常オン電流を得るようにしていることも同じであるが、チョッピングデューティサイクルを制御するための制御目標が被制御電流増幅半導体のベース(ゲート)電流ではなく、被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧とし、被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧を想定される最大のコレクタ(ドレイン)電流における飽和電圧VCE(sat)、(VDS(sat))=VSに非常に近い、いわゆる準飽和状態の2値間(VHおよびVL)で制御するようにする。

【発明の効果】

【0011】

しかして、本発明は被制御電流増幅半導体を準飽和状態で駆動するため、駆動電流を必要最小とし、駆動電源の容量低減、ベース(ゲート)層に蓄積されるキャリアを最小とすることで、ターンオフ時間を低減でき、動作周波数の範囲を広げることができる。

【発明を実施するための最良の形態】

【0012】

以下、本願発明を実施例について図を参照しながら説明する。

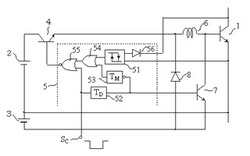

特許文献1に記載されている図では被制御素子をゲートターンオフサイリスタで示していたものを電流増幅半導体の一種であるトランジスタで書き改めたものを図9に示すが、本願発明の電流増幅半導体の駆動回路は基本的には同じである。全く異なるところは、ヒステリシスコンパレータをインダクタ電流ではなく、被制御電流増幅半導体のコレクタ−エミッタ間電圧で動作させるように改良したもので、図1に示す。

【0013】

図1図示の実施例は、図9図示の従来例と同一符号のものは機能を同じくするもので、1は被制御電流駆動半導体、2,3は直流電源、4はヒステリシスコンパレータ51の出力に応じてチョッピングするチョッピング用スイッチング素子、6は通常オン時に被制御電流増幅半導体の駆動電流を流し続けるための誘導エネルギー蓄積素子であるインダクタ、7は被制御電流増幅半導体のオンオフを制御するための制御用スイッチング素子、8はチョッピング用スイッチング素子4がオフしている期間にインダクタ電流をバイパスするダイオード、破線で囲った5はチョッピング用スイッチング素子4および制御用スイッチング素子7を制御する制御回路である。なお、本実施例では被制御電流増幅半導体1並びにスイッチ素子4,7をトランジスタで構成してある。

【0014】

該制御回路5において、51はヒステリシスコンパレータであり、被制御電流増幅半導体1のコレクタ−エミッタ間電圧が電圧値VL以下になると“Low”から “High”へ、VH以上になると“High”から“Low”となる信号を発生する、いわゆる、ヒステリシス動作を行う。52は被制御電流増幅半導体をターンオンするために、制御信号SCが “High”から“Low”への変化時点から時間TDだけ制御信号SCを遅らす遅延回路、53は遅延回路52の出力が“High”から“Low”への変化時点から時間幅TMのパルスを生成するモノマルチバイブレータ(以下「モノマルチ」という。)、54はヒステリシスコンパレータ51およびモノマルチ53の出力信号のOR論理信号を生成するOR回路、55は制御信号SCおよびOR回路54の出力信号のNOR論理信号を生成するNOR回路である。56は被制御電流増幅半導体1のオフ時にコレクタ−エミッタ間に印加される高電圧を阻止するためのダイオードである。

【0015】

かくのごとき構成の回路の動作を図3〜図5を用いて説明すると以下のごとくである。ここに、図3は被制御電流増幅半導体1をターンオンさせるにあたり、オーバードライブ電流の初期値となる尖頭値IPまでインダクタ電流を増大させる場合(時刻T0〜T1)の動作説明図を示す。図4は時刻T1の時点でIPとなったインダクタ6の電流がオーバードライブ電流として被制御電流増幅半導体1のベースに流入する場合(時刻T1〜T4)および定常状態においてインダクタ6の残留磁気エネルギーの放出により、インダクタ6の電流が被制御電流増幅半導体1のベースに流入する場合(時刻T5〜T6)の動作説明図を示す。図5は定常状態で、インダクタ6に磁気エネルギーを蓄積しながら、インダクタ6の電流が被制御電流増幅半導体1のベースに流入する場合(時刻T4〜T5)の動作説明図を示す。

【0016】

さて、被制御電流増幅半導体1をオンさせるために、図2に示す時刻T0で制御信号SCを“High”から“Low”にすると、遅延回路52の作用により制御用スイッチング素子7は時刻T1までの間(TD)オンを継続する。一方、モノマルチ53はトリガされていないので該出力は“Low”および 被制御電流増幅半導体1はオフ状態でコレクタ−エミッタ間電圧は高電圧でVH以上であるため、ヒステリシスコンパレータ51の出力も“Low”であり、OR回路54出力は“Low”になる。したがって、両入力が“Low”となるNOR回路55の出力は“High”となり、チョッピング用スイッチング素子4はオンし、図3の破線で示す経路で電流が流れる。すなわち、直流電源3→直流電源2→スイッチング素子4→インダクタ6→スイッチング素子7→直流電源3の経路で電流が流れる。この期間には、インダクタ6に直流電源2、3の合計電圧が印加されるので、その電流は急速に増大して行く。この電流が所望のオーバードライブ初期電流値IPとなるように、時間TDを決める。

【0017】

次に、図2の時刻T1で制御用スイッチング素子7がオフするために、インダクタ6に流れていた電流が被制御電流増幅半導体1のベースに転流する。一方、同時にモノマルチ53がトリガされるため、該出力が“High”となり、ヒステリシスコンパレータ51の出力に関係なくOR回路54の出力が“High”となる。したがって、NOR回路55出力は“Low”となり、チョッピング用スイッチング素子4もオフするため、インダクタ6の電流は図4に示す破線で示す経路に流れる。すなわち、直流電源3の負極→ダイオード8→インダクタ6→被制御電流増幅半導体1→直流電源3の正極の経路で電流が流れる。該電流は直流電源3に回生するため、インダクタ6の電流は減衰する。

【0018】

このように、制御用スイッチング素子7が高速でスイッチオフするため、被制御電流増幅半導体1のベースに急峻な立ち上がりを持ったオーバードライブ初期電流IPが流れるため、被制御電流増幅半導体1はターンオン遅れ(Td)が少なく、かつライズタイム(Tr)の短いターンオンが達成される。これにより、モノマルチ53が生成する時間TMより早く、被制御電流増幅半導体1のコレクタ−エミッタ間電圧は低下し、時刻T2でヒステリシスコンパレータ51の入力はVLに達し該出力は“High”となるが、モノマルチ53の出力は未だ“High”を継続しているので、電流経路に変化は無く、また、被制御電流増幅半導体1のベース電流も未だ大きく被制御電流増幅半導体1のベースは十分に駆動されており、被制御電流増幅半導体1は飽和状態の電圧降下(VS)となっている。

【0019】

インダクタ6の電流が減衰を継続し、被制御電流増幅半導体1を飽和状態に維持できなくなると、コレクタ−エミッタ間電圧が徐々に上昇して行き時刻T4でVHに達する。コレクタ−エミッタ間電圧がVHに達するとヒステリシスコンパレータ51の出力は“High”から“Low”になる。一方、この時点より前の時刻T3でモノマルチ53が“Low”となるように選定しており、時刻T4でOR回路54の両入力が“Low”となるため該出力は“Low”になる。これにより、NOR回路55の両入力も“Low”となるため該出力は“High”となり、再びチョッピング用スイッチング素子4がオンし、電流経路は図5のようになる。すなわち、直流電源2→スイッチング素子4→インダクタ6→被制御電流増幅半導体1→直流電源2の経路で電流が流れ、被制御電流増幅半導体1のベース電流に駆動電流の供給を継続しながら、インダクタ6に磁気エネルギーを蓄積して行く。

【0020】

したがって、インダクタ6の電流(=被制御電流増幅半導体1のベース電流)は増加して行き、これに伴い、被制御電流増幅半導体1のコレクタ−エミッタ間電圧は低下して行き、時刻T5でコレクタ−エミッタ間電圧は再びVLに達し、ヒステリシスコンパレータ51の出力は“Low” から “High”になりチョッピング用スイッチング素子4をオフさせ、図4の状態になりインダクタ6電流が減少し、時刻T6で時刻T4と同じ状態となる。以降、制御信号SCが“High”となるまで、この動作を繰り返す。

【0021】

次に、上述の通常時の動作について電流増幅半導体の出力特性を用いて説明する。図6はトランジスタについて、ベース電流をパラメータとしたコレクタ−エミッタ間電圧(VCE)とコレクタ電流(IC)の関係を示す出力特性の一例を示す。ここで、想定されるコレクタ電流の最大値を150Aとするとコレクタ−エミッタ間飽和電圧VSは0.36Vになる。コレクタ電流が100Aの時の説明をすると、この時のオン状態は図6の楕円で囲った部分になり、この部分をコレクタ−エミッタ間電圧(VCE)について拡大したものを図7に示す。

【0022】

図7は、前述したヒステリシスコンパレータ51の動作点を例えば、VL=0.4V、VH=0.5Vとなるように設定すると、ベース電流は図7の両端矢印で示すIHとILの間で制御されることを示している。これらのベース電流値は想定される最大電流時に必要とされたベース電流(図7に示すIB4)より大幅に少なくて良く、また、直流電源2、3から取り出す電流はチョッピング用スイッチング素子7のオン時のみ、つまり、直流電源2、3からの平均電流は(IH+IL)・D/2であるから、さらに小さくなる。ここでDはチョッピング用スイッチング素子7のオンデューティ比であり、D≒(E3+VBE)/(E2−VBE)〔E2は直流電源2の電圧、E3は直流電源3の電圧、VBEは被制御電流増幅半導体1のベース−エミッタ間電圧〕であるからE2をE3に比べ大きく設定すればオンデューティ比Dが小さくなり、さらに有利となる。また、インダクタ6の磁気エネルギーはチョッピング用スイッチング素子4がオフしている間は直流電源3に回生されるため、電源の容量が低減される。

【0023】

図2の時刻T7で制御信号SCが“Low” から “High”になり、他の如何なる条件に関わらず、NOR回路55の出力を“Low”にし、チョッピング用スイッチング素子4をオフさせ、同時に遅延回路52を“High”とし、制御用スイッチング素子7をオンさせる。これにより、直流電源3→被制御電流増幅半導体1のエミッタ→被制御電流増幅半導体1のベース→制御用スイッチング素子7→直流電源3の経路で電流を急峻に流し、被制御電流増幅半導体1のベース層に蓄積されたキャリアを放出させ、急速にターンオフさせる。

【0024】

加えるに、本願発明の構成により大きな機能が派生されることについて、以下に説明する。

交流および直流電動機を制御するスイッチング素子を使用したインバータやコンバータでは回転エネルギーを電源に回生する必要がある場合や、また通常の電源等に用いられるインバータやコンバータにおいても、スイッチング素子そのものの電圧は零ではあるが電流は流れず、該スイッチング素子と並列に接続されたフリーホィールダイオードに流れる状態が必ず存在する。

【0025】

このような状態の期間に該スイッチング素子には駆動電流を流すことは何ら意味がなく、無駄にエネルギーを浪費するだけとなる。このような状態で、負荷電流が極性反転して、スイッチング素子に電流が流れ始めようとして、スイッチング素子に電圧が印加始めた時に該スイッチング素子をオンさせれば良いことになる。

【0026】

しかるに、本願発明の構成では、図1には示していない並列ダイオードに電流が流れている時には上述したスイッチング素子である被制御電流増幅半導体1の電圧は零(実際はダイオードの電圧降下分、負となる)であるから、ヒステリシスコンパレータ51の出力は“High”となるから、OR回路54の出力も“High”となり、無条件にNOR回路55の出力を“Low”とするので、チョッピング用スイッチング素子4をオフさせるので、インダクタ6の残留磁気エネルギーが消失した後は被制御電流増幅半導体1のベース電流は流れなくなる。途中で負荷電流が極性反転し被制御電流増幅半導体1の電圧がVH以上になろうとすると、ヒステリシスコンパレータ51の出力は“Low”となり、モノマルチ53の出力は“Low” となっているためOR回路54の出力は “Low”となる。当然、この時には制御信号SCは“Low”であるからNOR回路55の出力は“High”となるので、チョッピング用スイッチング素子4をオンさせインダクタ6を通して、被制御電流増幅半導体1のベースに電流を流し始める、この時にはオーバードライブ電流は流れないが、被制御電流増幅半導体1のコレクタ(ドレイン)電流は零から流れ始めるので、その必要は無い。

【0027】

なお、制御回路5は図1に示したものに限定されるものではなく、チョッピング用スイッチング素子4および制御用スイッチング素子7が、図2に示した動作を行うものであればどのような構成のものであっても良く、チョッピング用スイッチング素子4および制御用スイッチング素子7をトランジスタの記号で示したが、これもスイッチング機能があるものならどのようなものでも良いことは言うまでもない。

【産業上の利用可能性】

【0028】

以上説明したように、本発明によれば、格別な構成により被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧の若干の上昇による犠牲はあるものの、他のスイッチ素子に比べ、もともと電流増幅半導体はオン電圧が非常に低いため、この不具合を埋め合わせて余りある効果をもたらすものであり、従来の駆動回路と比較して余り変わらない構成にて、ターンオン初期のオーバードライブ電流を流し、かつ、直流電源の電圧変動および各部品の特性のバラツキによっても変動させることなく、必要最低限の駆動電流を流すだけですむ駆動回路を提供でき、インバータやコンバータ等のパワーエレクトロニクス分野において実用上の利点が顕著な装置を提供できる。

【図面の簡単な説明】

【0029】

【図1】図1は本発明による基本回路構成を示す回路図である。

【図2】図2は被制御電流増幅半導体をオン・オフさせる動作を説明するタイムチャートである

【図3】図3は図2の時刻T0〜T1における図1の回路内の電流経路を示す図である。

【図4】図4は図2の時刻T1〜T4および時刻T5〜T6における図1の回路内の電流経路を示す図である。

【図5】図5は図2の時刻T4〜T5における図1の回路内の電流経路を示す図である。

【図6】図6は通常時のチョッピング状況を説明する電流増幅半導体出力特性の一例を示す図である。

【図7】図7は図6の楕円で囲った部分をコレクタ・エミッタ間電圧軸を拡大した図である。

【図8】従来の制御電流増幅半導体を駆動するための典型的な回路の基本図である。

【図9】特許文献1に採用した、特許登録済みの制御電流増幅半導体を駆動するための回路である。

【符号の説明】

【0030】

1 被制御電流増幅半導体

2,3 直流電源

4 チョッピング用スイッチング素子

5 制御回路

6 インダクタ

7 制御用スイッチング素子

8 ダイオード

51 ヒステリシスコンパレータ

52 遅延回路

53 モノマルチバイブレータ

54 OR回路

55 NOR回路

56 ダイオード

SC 制御信号

【技術分野】

【0001】

本発明はバイポーラトランジスタを初めとする電流増幅半導体をスイッチとして使用するインバータ回路等における該電流増幅半導体素子の駆動回路に関するものである。

【背景技術】

【0002】

電流増幅による半導体はベース(ゲート)から注入される少数キャリアにより、オン状態になるが、伝導度変調の効果により、オン電圧が極めて低いと言う特徴があり、大電流をスイッチングするインバータ回路等に使用されている。

【0003】

しかし、有限の増幅度によりベース(ゲート)に流し込む電流が大きく、このため制御電源が大型化したり、また、電流遮断(ターンオフ)時に、少数キャリアの過剰な蓄積を排出するための時間(ストレージタイム)が存在し、スイッチング周波数が制限される等の理由で、電圧駆動形の絶縁ゲート型バイポーラトランジスタ(IGBT )あるいはユニポーラで少数キャリアの無い、パワーMOS形電界効果トランジスタ(MOSFET)に取って代られているのが現状である。

【0004】

従来の電流増幅によるスイッチング半導体のベース(ゲート)駆動の基本回路として図8に示すものが知られている。

図8において、1は被制御電流増幅半導体で、ここではトランジスタで示す。2,3は直流電源、74,75はそれぞれオンおよびオフ用のスイッチング素子でトランジスタで示す。76はベース電流制限用の抵抗である。

【0005】

すなわち、直列に接続された2個の直流電源2,3とトランジスタ74,75からなるトーテンポール回路および抵抗76からなり、制御信号が印加されると、トランジスタ74がオンし、直流電源2から抵抗76を通してトランジスタ1のベース電流を流す。また、制御信号がオフすると、トランジスタ74がオフしてトランジスタ75がオンし、トランジスタ1のベース−エミッタ間に直流電源3の電圧を逆極性に加えて、少数キャリアを引き抜きターンオフさせ、トランジスタ1の順電圧阻止能力を回復させる。

【0006】

しかるに、図8に示す如きものは、抵抗76の抵抗値は直流電源2の電圧変動範囲の最小値、トランジスタ74のオン時コレクタ−エミッタ間電圧の最大値、トランジスタ1のベース−エミッタ間電圧の最大値および電流増幅率の最小値を考慮して、最大のコレクタ電流において決定されるため、それぞれの値が通常値の場合にはトランジスタ1のベース電流が不必要に多くなるのが通例であり、特にコレクタ電流が低い場合でも同じベース電流が流れてしまい、抵抗6に発生する損失が問題となったり、直流電源の容量が大きくなる欠点を有し、さらには過剰に蓄積されたキャリアによる動作周波数の制限が問題となっている。

【0007】

上述した欠点を補う手段として、後掲する発明人による既出願特許文献1(図9に基本回路を示す)に述べられているように、抵抗を無くしたり、部品のバラツキの影響を除去してベース電流を決定でき、電源電流をチョッピングすることで直流電源の容量を大幅に低減できる方法を提供できたが、最大コレクタ電流時に最小の増幅率でベース電流を決定しなければならない点は解決されていない。

【特許文献1】特公平7−28527号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

上述した図9の場合、直流電源2の電圧、トランジスタ4のオン時コレクタ−エミッタ間電圧、トランジスタ1のベース−エミッタ間電圧の変動等については解決されているが、想定される最大のコレクタ電流において、トランジスタ1の電流増幅率の最小値でベース電流を決定することは変わらず、相変わらず過剰なベース電流および過剰蓄積キャリアの問題は解決されていない。

【0009】

そこで、本発明は、上記問題点に鑑み、過剰な少数キャリアを蓄積させないように、必要最小限のベース(ゲート)電流を供給し、駆動電源の容量およびストレージタイムを低減できる電流増幅半導体の駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

以上のような目的を達成するために、被制御電流増幅半導体のベース(ゲート)に駆動電流を流す手段として、ターンオン初期およびターンオフ時の動作原理は特許文献1に示す従来例と同様であり、電流維持要素としてのインダクタとチョッピング用スイッチング素子を用いチョッピングのデューティサイクルを制御することで、損失無しで、通常オン電流を得るようにしていることも同じであるが、チョッピングデューティサイクルを制御するための制御目標が被制御電流増幅半導体のベース(ゲート)電流ではなく、被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧とし、被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧を想定される最大のコレクタ(ドレイン)電流における飽和電圧VCE(sat)、(VDS(sat))=VSに非常に近い、いわゆる準飽和状態の2値間(VHおよびVL)で制御するようにする。

【発明の効果】

【0011】

しかして、本発明は被制御電流増幅半導体を準飽和状態で駆動するため、駆動電流を必要最小とし、駆動電源の容量低減、ベース(ゲート)層に蓄積されるキャリアを最小とすることで、ターンオフ時間を低減でき、動作周波数の範囲を広げることができる。

【発明を実施するための最良の形態】

【0012】

以下、本願発明を実施例について図を参照しながら説明する。

特許文献1に記載されている図では被制御素子をゲートターンオフサイリスタで示していたものを電流増幅半導体の一種であるトランジスタで書き改めたものを図9に示すが、本願発明の電流増幅半導体の駆動回路は基本的には同じである。全く異なるところは、ヒステリシスコンパレータをインダクタ電流ではなく、被制御電流増幅半導体のコレクタ−エミッタ間電圧で動作させるように改良したもので、図1に示す。

【0013】

図1図示の実施例は、図9図示の従来例と同一符号のものは機能を同じくするもので、1は被制御電流駆動半導体、2,3は直流電源、4はヒステリシスコンパレータ51の出力に応じてチョッピングするチョッピング用スイッチング素子、6は通常オン時に被制御電流増幅半導体の駆動電流を流し続けるための誘導エネルギー蓄積素子であるインダクタ、7は被制御電流増幅半導体のオンオフを制御するための制御用スイッチング素子、8はチョッピング用スイッチング素子4がオフしている期間にインダクタ電流をバイパスするダイオード、破線で囲った5はチョッピング用スイッチング素子4および制御用スイッチング素子7を制御する制御回路である。なお、本実施例では被制御電流増幅半導体1並びにスイッチ素子4,7をトランジスタで構成してある。

【0014】

該制御回路5において、51はヒステリシスコンパレータであり、被制御電流増幅半導体1のコレクタ−エミッタ間電圧が電圧値VL以下になると“Low”から “High”へ、VH以上になると“High”から“Low”となる信号を発生する、いわゆる、ヒステリシス動作を行う。52は被制御電流増幅半導体をターンオンするために、制御信号SCが “High”から“Low”への変化時点から時間TDだけ制御信号SCを遅らす遅延回路、53は遅延回路52の出力が“High”から“Low”への変化時点から時間幅TMのパルスを生成するモノマルチバイブレータ(以下「モノマルチ」という。)、54はヒステリシスコンパレータ51およびモノマルチ53の出力信号のOR論理信号を生成するOR回路、55は制御信号SCおよびOR回路54の出力信号のNOR論理信号を生成するNOR回路である。56は被制御電流増幅半導体1のオフ時にコレクタ−エミッタ間に印加される高電圧を阻止するためのダイオードである。

【0015】

かくのごとき構成の回路の動作を図3〜図5を用いて説明すると以下のごとくである。ここに、図3は被制御電流増幅半導体1をターンオンさせるにあたり、オーバードライブ電流の初期値となる尖頭値IPまでインダクタ電流を増大させる場合(時刻T0〜T1)の動作説明図を示す。図4は時刻T1の時点でIPとなったインダクタ6の電流がオーバードライブ電流として被制御電流増幅半導体1のベースに流入する場合(時刻T1〜T4)および定常状態においてインダクタ6の残留磁気エネルギーの放出により、インダクタ6の電流が被制御電流増幅半導体1のベースに流入する場合(時刻T5〜T6)の動作説明図を示す。図5は定常状態で、インダクタ6に磁気エネルギーを蓄積しながら、インダクタ6の電流が被制御電流増幅半導体1のベースに流入する場合(時刻T4〜T5)の動作説明図を示す。

【0016】

さて、被制御電流増幅半導体1をオンさせるために、図2に示す時刻T0で制御信号SCを“High”から“Low”にすると、遅延回路52の作用により制御用スイッチング素子7は時刻T1までの間(TD)オンを継続する。一方、モノマルチ53はトリガされていないので該出力は“Low”および 被制御電流増幅半導体1はオフ状態でコレクタ−エミッタ間電圧は高電圧でVH以上であるため、ヒステリシスコンパレータ51の出力も“Low”であり、OR回路54出力は“Low”になる。したがって、両入力が“Low”となるNOR回路55の出力は“High”となり、チョッピング用スイッチング素子4はオンし、図3の破線で示す経路で電流が流れる。すなわち、直流電源3→直流電源2→スイッチング素子4→インダクタ6→スイッチング素子7→直流電源3の経路で電流が流れる。この期間には、インダクタ6に直流電源2、3の合計電圧が印加されるので、その電流は急速に増大して行く。この電流が所望のオーバードライブ初期電流値IPとなるように、時間TDを決める。

【0017】

次に、図2の時刻T1で制御用スイッチング素子7がオフするために、インダクタ6に流れていた電流が被制御電流増幅半導体1のベースに転流する。一方、同時にモノマルチ53がトリガされるため、該出力が“High”となり、ヒステリシスコンパレータ51の出力に関係なくOR回路54の出力が“High”となる。したがって、NOR回路55出力は“Low”となり、チョッピング用スイッチング素子4もオフするため、インダクタ6の電流は図4に示す破線で示す経路に流れる。すなわち、直流電源3の負極→ダイオード8→インダクタ6→被制御電流増幅半導体1→直流電源3の正極の経路で電流が流れる。該電流は直流電源3に回生するため、インダクタ6の電流は減衰する。

【0018】

このように、制御用スイッチング素子7が高速でスイッチオフするため、被制御電流増幅半導体1のベースに急峻な立ち上がりを持ったオーバードライブ初期電流IPが流れるため、被制御電流増幅半導体1はターンオン遅れ(Td)が少なく、かつライズタイム(Tr)の短いターンオンが達成される。これにより、モノマルチ53が生成する時間TMより早く、被制御電流増幅半導体1のコレクタ−エミッタ間電圧は低下し、時刻T2でヒステリシスコンパレータ51の入力はVLに達し該出力は“High”となるが、モノマルチ53の出力は未だ“High”を継続しているので、電流経路に変化は無く、また、被制御電流増幅半導体1のベース電流も未だ大きく被制御電流増幅半導体1のベースは十分に駆動されており、被制御電流増幅半導体1は飽和状態の電圧降下(VS)となっている。

【0019】

インダクタ6の電流が減衰を継続し、被制御電流増幅半導体1を飽和状態に維持できなくなると、コレクタ−エミッタ間電圧が徐々に上昇して行き時刻T4でVHに達する。コレクタ−エミッタ間電圧がVHに達するとヒステリシスコンパレータ51の出力は“High”から“Low”になる。一方、この時点より前の時刻T3でモノマルチ53が“Low”となるように選定しており、時刻T4でOR回路54の両入力が“Low”となるため該出力は“Low”になる。これにより、NOR回路55の両入力も“Low”となるため該出力は“High”となり、再びチョッピング用スイッチング素子4がオンし、電流経路は図5のようになる。すなわち、直流電源2→スイッチング素子4→インダクタ6→被制御電流増幅半導体1→直流電源2の経路で電流が流れ、被制御電流増幅半導体1のベース電流に駆動電流の供給を継続しながら、インダクタ6に磁気エネルギーを蓄積して行く。

【0020】

したがって、インダクタ6の電流(=被制御電流増幅半導体1のベース電流)は増加して行き、これに伴い、被制御電流増幅半導体1のコレクタ−エミッタ間電圧は低下して行き、時刻T5でコレクタ−エミッタ間電圧は再びVLに達し、ヒステリシスコンパレータ51の出力は“Low” から “High”になりチョッピング用スイッチング素子4をオフさせ、図4の状態になりインダクタ6電流が減少し、時刻T6で時刻T4と同じ状態となる。以降、制御信号SCが“High”となるまで、この動作を繰り返す。

【0021】

次に、上述の通常時の動作について電流増幅半導体の出力特性を用いて説明する。図6はトランジスタについて、ベース電流をパラメータとしたコレクタ−エミッタ間電圧(VCE)とコレクタ電流(IC)の関係を示す出力特性の一例を示す。ここで、想定されるコレクタ電流の最大値を150Aとするとコレクタ−エミッタ間飽和電圧VSは0.36Vになる。コレクタ電流が100Aの時の説明をすると、この時のオン状態は図6の楕円で囲った部分になり、この部分をコレクタ−エミッタ間電圧(VCE)について拡大したものを図7に示す。

【0022】

図7は、前述したヒステリシスコンパレータ51の動作点を例えば、VL=0.4V、VH=0.5Vとなるように設定すると、ベース電流は図7の両端矢印で示すIHとILの間で制御されることを示している。これらのベース電流値は想定される最大電流時に必要とされたベース電流(図7に示すIB4)より大幅に少なくて良く、また、直流電源2、3から取り出す電流はチョッピング用スイッチング素子7のオン時のみ、つまり、直流電源2、3からの平均電流は(IH+IL)・D/2であるから、さらに小さくなる。ここでDはチョッピング用スイッチング素子7のオンデューティ比であり、D≒(E3+VBE)/(E2−VBE)〔E2は直流電源2の電圧、E3は直流電源3の電圧、VBEは被制御電流増幅半導体1のベース−エミッタ間電圧〕であるからE2をE3に比べ大きく設定すればオンデューティ比Dが小さくなり、さらに有利となる。また、インダクタ6の磁気エネルギーはチョッピング用スイッチング素子4がオフしている間は直流電源3に回生されるため、電源の容量が低減される。

【0023】

図2の時刻T7で制御信号SCが“Low” から “High”になり、他の如何なる条件に関わらず、NOR回路55の出力を“Low”にし、チョッピング用スイッチング素子4をオフさせ、同時に遅延回路52を“High”とし、制御用スイッチング素子7をオンさせる。これにより、直流電源3→被制御電流増幅半導体1のエミッタ→被制御電流増幅半導体1のベース→制御用スイッチング素子7→直流電源3の経路で電流を急峻に流し、被制御電流増幅半導体1のベース層に蓄積されたキャリアを放出させ、急速にターンオフさせる。

【0024】

加えるに、本願発明の構成により大きな機能が派生されることについて、以下に説明する。

交流および直流電動機を制御するスイッチング素子を使用したインバータやコンバータでは回転エネルギーを電源に回生する必要がある場合や、また通常の電源等に用いられるインバータやコンバータにおいても、スイッチング素子そのものの電圧は零ではあるが電流は流れず、該スイッチング素子と並列に接続されたフリーホィールダイオードに流れる状態が必ず存在する。

【0025】

このような状態の期間に該スイッチング素子には駆動電流を流すことは何ら意味がなく、無駄にエネルギーを浪費するだけとなる。このような状態で、負荷電流が極性反転して、スイッチング素子に電流が流れ始めようとして、スイッチング素子に電圧が印加始めた時に該スイッチング素子をオンさせれば良いことになる。

【0026】

しかるに、本願発明の構成では、図1には示していない並列ダイオードに電流が流れている時には上述したスイッチング素子である被制御電流増幅半導体1の電圧は零(実際はダイオードの電圧降下分、負となる)であるから、ヒステリシスコンパレータ51の出力は“High”となるから、OR回路54の出力も“High”となり、無条件にNOR回路55の出力を“Low”とするので、チョッピング用スイッチング素子4をオフさせるので、インダクタ6の残留磁気エネルギーが消失した後は被制御電流増幅半導体1のベース電流は流れなくなる。途中で負荷電流が極性反転し被制御電流増幅半導体1の電圧がVH以上になろうとすると、ヒステリシスコンパレータ51の出力は“Low”となり、モノマルチ53の出力は“Low” となっているためOR回路54の出力は “Low”となる。当然、この時には制御信号SCは“Low”であるからNOR回路55の出力は“High”となるので、チョッピング用スイッチング素子4をオンさせインダクタ6を通して、被制御電流増幅半導体1のベースに電流を流し始める、この時にはオーバードライブ電流は流れないが、被制御電流増幅半導体1のコレクタ(ドレイン)電流は零から流れ始めるので、その必要は無い。

【0027】

なお、制御回路5は図1に示したものに限定されるものではなく、チョッピング用スイッチング素子4および制御用スイッチング素子7が、図2に示した動作を行うものであればどのような構成のものであっても良く、チョッピング用スイッチング素子4および制御用スイッチング素子7をトランジスタの記号で示したが、これもスイッチング機能があるものならどのようなものでも良いことは言うまでもない。

【産業上の利用可能性】

【0028】

以上説明したように、本発明によれば、格別な構成により被制御電流増幅半導体のコレクタ(ドレイン)−エミッタ(ソース)間電圧の若干の上昇による犠牲はあるものの、他のスイッチ素子に比べ、もともと電流増幅半導体はオン電圧が非常に低いため、この不具合を埋め合わせて余りある効果をもたらすものであり、従来の駆動回路と比較して余り変わらない構成にて、ターンオン初期のオーバードライブ電流を流し、かつ、直流電源の電圧変動および各部品の特性のバラツキによっても変動させることなく、必要最低限の駆動電流を流すだけですむ駆動回路を提供でき、インバータやコンバータ等のパワーエレクトロニクス分野において実用上の利点が顕著な装置を提供できる。

【図面の簡単な説明】

【0029】

【図1】図1は本発明による基本回路構成を示す回路図である。

【図2】図2は被制御電流増幅半導体をオン・オフさせる動作を説明するタイムチャートである

【図3】図3は図2の時刻T0〜T1における図1の回路内の電流経路を示す図である。

【図4】図4は図2の時刻T1〜T4および時刻T5〜T6における図1の回路内の電流経路を示す図である。

【図5】図5は図2の時刻T4〜T5における図1の回路内の電流経路を示す図である。

【図6】図6は通常時のチョッピング状況を説明する電流増幅半導体出力特性の一例を示す図である。

【図7】図7は図6の楕円で囲った部分をコレクタ・エミッタ間電圧軸を拡大した図である。

【図8】従来の制御電流増幅半導体を駆動するための典型的な回路の基本図である。

【図9】特許文献1に採用した、特許登録済みの制御電流増幅半導体を駆動するための回路である。

【符号の説明】

【0030】

1 被制御電流増幅半導体

2,3 直流電源

4 チョッピング用スイッチング素子

5 制御回路

6 インダクタ

7 制御用スイッチング素子

8 ダイオード

51 ヒステリシスコンパレータ

52 遅延回路

53 モノマルチバイブレータ

54 OR回路

55 NOR回路

56 ダイオード

SC 制御信号

【特許請求の範囲】

【請求項1】

直列に接続された2個の直流電源の正側電源の正極と負極の間に、チョッピング用スイッチング素子とインダクタと被制御電流増幅半導体のベース又はゲート、並びに、エミッタ又はソースとの直列回路を接続するとともに、前記チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソードおよび負側電源の負極にアノードとなるようダイオードを接続し、前記被制御電流増幅半導体のベース又はゲートと負側電源の負極間に制御用スイッチング素子を接続した回路構成をなし、

前記被制御電流増幅半導体のコレクタ又はドレイン、並びに、エミッタ又はソース間の電圧を検出し、前記被制御電流増幅半導体がオン状態時に、該電圧が飽和電圧より高い2値の電圧間になるように前記チョッピング用スイッチング素子のオンオフ期間を制御する制御回路を有することを特徴とした電流増幅半導体素子の駆動回路。

【請求項2】

前記被制御電流増幅半導体が、バイポーラトランジスタであることを特徴とする請求項1に記載の電流増幅半導体素子の駆動回路。

【請求項3】

前記被制御電流増幅半導体が、バイポーラ静電誘導トランジスタであることを特徴とする請求項1に記載の電流増幅半導体素子の駆動回路。

【請求項4】

前記インダクタが空芯であることを特徴とする請求項1から請求項3のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項5】

前記インダクタが鉄心入りであることを特徴とする請求項1から請求項3のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項6】

前記制御回路は、前記被制御電流増幅半導体のコレクタ−エミッタ間電圧が設定電圧値以下になるとヒステリシス動作を行うヒステリシスコンパレータを備えてあることを特徴とする請求項1から請求項5のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項7】

前記制御回路は、前記被制御電流増幅半導体をターンオンするために、制御信号の発振時間を遅らす遅延回路を備えてあることを特徴とする請求項1から請求項6のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項8】

前記制御回路は、前記遅延回路の出力の変化時点から時間幅のパルスを生成するモノマルチバイブレータを備えてあることを特徴とする請求項7に記載の電流増幅半導体素子の駆動回路。

【請求項9】

前記制御回路は、前記ヒステリシスコンパレータおよび前記モノマルチバイブレータの出力信号のOR論理信号を生成するOR回路を備えてあることを特徴とする請求項8に記載の電流増幅半導体素子の駆動回路。

【請求項10】

前記制御回路は、前記制御信号および前記OR回路の出力信号のNOR論理信号を生成するNOR回路を備えてあることを特徴とする請求項9に記載の電流増幅半導体素子の駆動回路。

【請求項1】

直列に接続された2個の直流電源の正側電源の正極と負極の間に、チョッピング用スイッチング素子とインダクタと被制御電流増幅半導体のベース又はゲート、並びに、エミッタ又はソースとの直列回路を接続するとともに、前記チョッピング用スイッチング素子とインダクタの接続点に該接続点側にカソードおよび負側電源の負極にアノードとなるようダイオードを接続し、前記被制御電流増幅半導体のベース又はゲートと負側電源の負極間に制御用スイッチング素子を接続した回路構成をなし、

前記被制御電流増幅半導体のコレクタ又はドレイン、並びに、エミッタ又はソース間の電圧を検出し、前記被制御電流増幅半導体がオン状態時に、該電圧が飽和電圧より高い2値の電圧間になるように前記チョッピング用スイッチング素子のオンオフ期間を制御する制御回路を有することを特徴とした電流増幅半導体素子の駆動回路。

【請求項2】

前記被制御電流増幅半導体が、バイポーラトランジスタであることを特徴とする請求項1に記載の電流増幅半導体素子の駆動回路。

【請求項3】

前記被制御電流増幅半導体が、バイポーラ静電誘導トランジスタであることを特徴とする請求項1に記載の電流増幅半導体素子の駆動回路。

【請求項4】

前記インダクタが空芯であることを特徴とする請求項1から請求項3のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項5】

前記インダクタが鉄心入りであることを特徴とする請求項1から請求項3のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項6】

前記制御回路は、前記被制御電流増幅半導体のコレクタ−エミッタ間電圧が設定電圧値以下になるとヒステリシス動作を行うヒステリシスコンパレータを備えてあることを特徴とする請求項1から請求項5のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項7】

前記制御回路は、前記被制御電流増幅半導体をターンオンするために、制御信号の発振時間を遅らす遅延回路を備えてあることを特徴とする請求項1から請求項6のいずれかに記載の電流増幅半導体素子の駆動回路。

【請求項8】

前記制御回路は、前記遅延回路の出力の変化時点から時間幅のパルスを生成するモノマルチバイブレータを備えてあることを特徴とする請求項7に記載の電流増幅半導体素子の駆動回路。

【請求項9】

前記制御回路は、前記ヒステリシスコンパレータおよび前記モノマルチバイブレータの出力信号のOR論理信号を生成するOR回路を備えてあることを特徴とする請求項8に記載の電流増幅半導体素子の駆動回路。

【請求項10】

前記制御回路は、前記制御信号および前記OR回路の出力信号のNOR論理信号を生成するNOR回路を備えてあることを特徴とする請求項9に記載の電流増幅半導体素子の駆動回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2009−17723(P2009−17723A)

【公開日】平成21年1月22日(2009.1.22)

【国際特許分類】

【出願番号】特願2007−178501(P2007−178501)

【出願日】平成19年7月6日(2007.7.6)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成21年1月22日(2009.1.22)

【国際特許分類】

【出願日】平成19年7月6日(2007.7.6)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]