電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチ素子、特にFET(電界効果トランジスタ)に流れる電流を検出する電流検出回路、および、この電流検出回路を用いたモータ制御装置に関する。

【背景技術】

【0002】

モータ制御装置には、インバータにより直流電圧を3相交流電圧に変換し、この3相交流電圧により3相交流モータ(3相ブラシレスモータや3相誘導モータ)を駆動するものがある(例えば、特許文献1を参照)。図5は、特許文献1に記載のモータ制御装置の構成図(特許文献1の図2)をそのまま示したものである。この図5に示すモータ制御装置は、6個のトランジスタQ1’〜Q6’で構成される3相ブリッジ回路と、制御回路CONTとからなるインバータ回路を用いて直流を交流に変換すると共に、出力電圧を制御して3相ブラシレスモータMの回転を制御するものである。このようなインバータ回路においては、過電流によるトランジスタの損傷、および過負荷によりモータの性能劣化などを防ぐことが必要になる。

【0003】

そこで、インバータの出力電流が過電流領域になったことを検出する回路を用いて、過電流発生時にトランジスタQ1’〜Q6’を一括オフ(すべてオフ)することによりモータ電流を遮断する方法が用いられている。この過電流を検出する代表的なものの1つに、インバータの3相ブリッジ回路の入力側(例えば、3相ブリッジ回路と電極(+)とを結ぶ直流電源線)に電流検出抵抗(または、分流器)を挿入し、その検出電圧を電流設定基準電圧と比較することにより過電流状態を検出する方法がある。また、例えば、ホール素子を内蔵するホールセンサをインバータの入力側(例えば、3相ブリッジ回路と電極(+)とを結ぶ直流電源線)に配置し、このホールセンサの出力電圧を電流設定基準電圧と比較することにより過電流状態を検出する方法がある。

【0004】

しかしながら、上記電流検出抵抗やホール素子を用いることはモータ制御装置(より正確には過電流保護回路)の小型化の要請に反し、また、これらの部品を使用することにより製品コストが上昇することになる。この問題に対処するために、上記特許文献1に記載のモータ制御装置では、FET(Field Effect Transistor)の導通タイミングにおけるオン電圧(電圧降下)を基に、FETに流れる電流を検出している。

【0005】

すなわち、図5に示す特許文献1に記載のモータ制御装置では、3相ブリッジ回路を、FETQ1’〜Q6を用いて構成し、モータMの第1相、第2相、第3相のモータ電流に比例するFETQ1’〜Q6のドレイン・ソース電圧VDS4,VDS5,VDS6を、各FETの導通タイミングに合わせてオンされる3個のスイッチAS1、AS2、AS3を介して、直列的に順次に検出する。そして、FETQ1’〜Q6’のドレイン・ソース電圧VDS4,VDS5,VDS6が電流設定基準電圧Vsを超えたときを過電流と判定して、制御回路CONTからの駆動情号を停止し、全てのFETをオフすることにより、過電流を流さないようにしている。

【0006】

なお、図6は、同じく上記特許文献1に記載された図(特許文献1の図1)をそのまま示した図であり、FETのドレイン・ソース間電圧VDSとドレイン電流IDの関係図である。この図に示すように、FETのゲート電圧VGをパラメータとすると、FETオン時のドレイン・ソース間の電圧降下VDSと、ドレイン電流IDとは、図に示すように、広い範囲に亘って直線的な比例関係を有する。しかもその傾斜は通常のトランジスタのそれに比べてかに緩やかであるため、ドレイン電流の変化に比例した十分大きなドレイン・ソース間電圧降下の変化を得ることができる。従って制御電流領域と過電流領域との間に大きな差をもたせることができるので、効果的な過電流の検出が可能である.

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−308420号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上述した特許文献1に記載のモータ制御装置では、モータ、トランジスタなどの過電流による損傷防止用過電流保護回路の小型化や、コストダウンを目的とし、ドレイン電流とドレイン・ソース間電圧圧降下とが広い範囲に亘って直線的関係にあるFETを用いると共に、このFETの動通タイミングに合わせてオンして、上記モータの各相電流に比例したドレイン・ソース間電圧降下を直列的に順次検出するスイッチ回路を設け、この回路の出力が設定基準電圧を越えたとき過電流と判定して上記制御回路への駆動信号の供給を停止しFETの電流遮断を行うようにしている。

【0009】

しかしながら、上記特許文献1に記載のFETのドレイン・ソース間電圧の検出による過電流保護回路にあっては、次のような問題点がある。すなわち、FETQ1’〜Q6’をプリント配線基板上に実装する構成においては、FETQ1’〜Q6’に流れる電流経路が配線パターンにより形成されることになる。したがって、直流電源の(−)端子を基準(回路グランド)として、FETQ4’〜Q6’のドレイン・ソース電圧(より正確には、ドレイン・回路グランド間電圧)を測定する場合には、配線パターンの抵抗による電圧降下分(オフセット)が含まれることになる。

【0010】

この場合、直流電源の(−)端子とトランジスタQ4’のソースとの間の配線パターンと、直流電源の(−)端子とトランジスタQ5’のソースとの間の配線パターンと、直流電源の(−)端子とトランジスタQ6’のソースとの間の配線パターンとの、それぞれ長さ(或いは幅、厚み)が異なることがある。このため、FETQ4’〜Q6’のドレイン・回路グランド間電圧には、配線パターンの抵抗値が異なることによる電圧差(電圧降下の差)が発生し、過電流の判定値がばらつくという問題がある。従って、配線パターンの抵抗のバラツキを考慮して、FETQ4’〜Q6’のドレイン・ソース間電圧を検出することが必要になる。

【0011】

本発明は、斯かる実情に鑑みなされたものであり、プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のドレインと回路グランド間の電圧降下VDGを基に検出する際に、FETの電流経路を形成する配線パターンの抵抗により発生するオフセット分を簡易な方法によりキャンセルして、FETのドレイン・ソース間の電圧降下(FETに流れる電流)を検出することができる、電流検出回路、および該電流検出回路を備えるモータ制御装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、上記課題を解決するためなされたものであり、本発明の電流検出回路は、プリント配線基板上に実装されるスイッチ素子の一方の入出力端子が、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記スイッチ素子に電流を供給する直流電源の負極側に接続されるとともに、前記スイッチ素子を制御する制御回路の回路グランドに接続される回路において、前記スイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなる抵抗直列回路を備え、前記抵抗直列回路においては、前記第1の抵抗の一端が前記スイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記スイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力することを特徴とする。

【0013】

また、本発明の電流検出回路は、前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定されることを特徴とする。

【0014】

また、本発明のモータ制御装置は、プリント配線基板上に実装されるスイッチ素子の3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置であって、前記直流電源から各スイッチ素子に流れる電流の電流経路が前記プリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各スイッチ素子と前記直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、前記下アーム側の対応するスイッチ素子の一方の入出力端子に接続され、他端が、前記プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記直流電源の負極側に接続されるとともに前記制御回路の回路グランドに接続されて構成されるモータ制御装置において、前記下アーム側のスイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記下アーム側の各スイッチ素子に対応して、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなるそれぞれの抵抗直列回路を備え、前記それぞれの抵抗直列回路においては、前記第1の抵抗の一端が対応するスイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記対応するスイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力することを特徴とする。

【0015】

また、本発明のモータ制御装置は、前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定されることを特徴とする。

【0016】

また、本発明のモータ制御装置は、前記下アーム側の各スイッチ素子に対応する第2の抵抗のそれぞれに並列に接続されるスイッチであって、前記下アーム側の対応するスイッチ素子の導通タイミングに合わせてオフし、前記対応するスイッチ素子の電流検出信号を当該スイッチ素子の導通時にのみ出力するスイッチを備えることを特徴とする。

【0017】

また、本発明のモータ制御装置は、前記下アーム側のスイッチ素子のオン時の電流検出信号が所定の過電流設定基準電圧を超えたときに過電流検出信号を出力する過電流検出回路と、前記過電流検出回路から過電流検出信号が出力された場合に、前記3相ブリッジ回路の各スイッチ素子のすべてをオフする過電流保護部と、を備えることを特徴とする。

【発明の効果】

【0018】

本発明の電流検出回路においては、スイッチ素子の一方の入出力端子と回路グランドとの間に接続される第1の抵抗と第2の抵抗とでなる抵抗直列回路を備え、この第2の抵抗と第1の抵抗の抵抗値の比(第2の抵抗/第1の抵抗)が、上記スイッチ素子のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定するとともに、第1の抵抗と第2の抵抗との接続点と回路グランドとの間の電圧をスイッチ素子に流れる電流の検出信号として出力する。

これにより、プリント配線基板上に搭載されるスイッチ素子に流れる電流を、スイッチ素子オン時のドレイン端子と回路グランド間の電圧降下を基に検出する際に、スイッチ素子の電流経路を形成する配線パターンの抵抗により発生するオフセット分を簡易な方法によりキャンセルして、スイッチ素子の一方の入出力端子と他方の入出力端子間電圧(スイッチ素子に流れる電流)を検出することができる。

【図面の簡単な説明】

【0019】

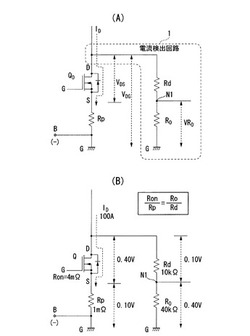

【図1】本発明の第1の実施形態に係わる電流検出回路を示す図である。

【図2】本発明の第2の実施形態に係わるモータ制御装置の構成を示す図である。

【図3】図2に示すモータ制御装置における電流検出回路の動作を説明するための図である。

【図4】FETに流れる電流(ドレイン・ソース間電圧VDS)の検出タイミングを示す図である。

【図5】特許文献1に記載のモータ制御装置の構成を示す図である。

【図6】FETのドレイン・ソース間電圧降下とドレイン電流の関係図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を添付図面を参照して説明する。

【0021】

[第1の実施形態]

図1は、本発明の第1の実施形態に係わる電流検出回路の構成を示す図である。この図1に示す回路おいては、電流検出対象となるFETQoはプリント配線基板上に実装され、また、直流電源装置(図示せず)の負極側に繋がる負極端子B(−)もプリント配線基板上に実装されている。そして、FETQoのソース端子Sは、このFETQoに流れる電流経路となる配線パターン(配線パターン抵抗Rpで示す経路)を介して、プリント配線基板上の負極端子B(−)に接続されるとともに、回路グランドGに接続されている。なお、FETQoは、図示しない制御回路(例えば、図2に示す制御部20等を参照)により、オン/オフ制御されるものである。

【0022】

図1に示すように、本実施形態の電流検出回路1は、抵抗分圧回路で構成され、この抵抗分圧回路は、検出部抵抗R1(第1の抵抗)とオフセット抵抗Ro(第2の抵抗)の直列回路で構成され、この検出部抵抗R1とオフセット抵抗Roとの接続点(ノードN1)から電流検出信号が出力される。

【0023】

この電流検出回路1は、FETQoに流れる電流(ドレイン電流ID)を、このFETQoのドレイン・ソース間電圧VDSを基に検出することを目的とする回路である。すなわち、図6に示すように、FETQoのドレイン・ソース間電圧VDS(電圧降下)は、ドレイン電流IDに比例する関係にあるので、このFETQoのドレイン・ソース間電圧VDS(電圧降下)を基に、FETQoに流れる電流(ドレイン電流ID)を検出する。

【0024】

ところで、図1に示す回路構成においては、FETQoのドレイン・ソース間電圧VDSを直接には測定せず、FETQoのドレイン端子Dと回路グランドGとの間の電圧VDGを測定している。このドレイン・回路グランド間電圧VDGには、FETQoのドレイン・ソース間電圧VDS(電圧降下=オン抵抗Ron×ドレイン電流ID)に加えて、配線パターン抵抗Rpによる電圧降下分がオフセットとして含まれる。従って、このドレイン・回路グランド間電圧VDGは、以下の式(1)のようになる。

【0025】

VDG=Ron×ID+Rp×ID・・・(1)

【0026】

この配線パターン抵抗(Rp)は、配線パターンの長さ・幅・厚みにより変化するため、オフセット分(Rp×ID)にはバラツキが発生する。このため、配線パターン抵抗Rpにより発生する電圧降下のオフセット分(Rp×ID)をキャンセルし、FETQoのドレイン・ソース間電圧VDS(=オン抵抗Ron×ID)を抽出する必要がある。

【0027】

そこで、本実施形態の電流検出回路では、FETQoのドレイン端子Dと、回路グランドGとの間に、抵抗分圧回路(検出部抵抗Rdとオフセット抵抗Roとで構成される抵抗直列回路)を挿入し、配線パターンの抵抗成分である配線パターン抵抗(Rp)による電圧降下分を、抵抗分圧回路を構成するオフセット抵抗Roにより分圧してオフセット分をキャンセルする。

【0028】

このために、FETQoのオン抵抗Ronと、配線パターン抵抗Rpと、オフセット抵抗Roと、検出部抵抗Rdの関係を以下のように定める。

【0029】

Ron:Rp=Ro:Rd・・・・(2)

すなわち、ドレイン電流IDが流れ電圧降下を発生させる側(抵抗Ronと配線パターン抵抗Rp側)の上下の抵抗値の比(Ron/Rp)に対して、抵抗分圧回路側(抵抗Rdと抵抗Ro側)の上下の抵抗値の比(Rd/Ro)が逆比になるようにする。すなわち、以下の関係になるようにする。

【0030】

Ron/Rp=Ro/Rd

【0031】

次に、具体的な数値の例を挙げて説明する。図1(B)は、配線パターン抵抗Rpにより発生する電圧降下(オフセット)をキャンセルする具体例について説明するための図である。この図に示すように、モータ電流を100Aとし、FETQoのオン抵抗Ronを4mΩ(Ron=4mΩ)とし、配線パターン抵抗Rpを1mΩ(Rp=1mΩ)とし、検出部抵抗(第1の抵抗)Rdを10kΩ(R1d=10kΩ)とし、オフセット抵抗(第2の抵抗)Roを40kΩ(Ro=40kΩ)とする。

【0032】

この場合は、ドレイン・回路グランド間電圧VDGは、0.50V(=100A×5mΩ)となる。すなわち、FETQoのオン抵抗Ronによる電圧降下が「0.40V(=100A×4mΩ)」となり、配線パターン抵抗Rpによる電圧降下が「0.10V(=100A×1mΩ)」となり、ドレイン・回路グランド間電圧VDGは、0.50Vとなる。

一方、抵抗分圧回路の検出電圧(ノードN1)の電圧VRo(抵抗Roの両端の電圧)は、ドレイン・回路グランド間電圧VDG(=0.50V)が抵抗分圧され、以下の式のようになる。

【0033】

VRo=0・50V×40kΩ/(10kΩ+40kΩ)=0.40V

【0034】

したがって、抵抗分圧回路の検出電圧(ノードN1)の電圧VRo(抵抗Roの両端の電圧)は、FETQoのドレイン・ソース間電圧VDS「0.40V(=100A×4mΩ)」と等しくなる。

【0035】

このように、ドレイン電流IDが流れ電圧降下を発生させる側の上下の抵抗値の比(Ron/Rp)に対して、抵抗分圧回路側の上下の抵抗値の比(Rd/Ro)が逆比になるように設定する(Ron/Rp=Ro/Rd)。すなわち、オフセット抵抗Roと検出部抵抗Rdとの抵抗値の比(Ro/Rd)を、FETQoのオン抵抗Ronと配線パターン抵抗Rpとの抵抗値の比(Ron/Rp)に一致するように設定する。これにより、配線パターン抵抗Rpにより発生する電圧降下分(オフセット)をキャンセルして、FETQoのドレイン・ソース間電圧VDSを検出することができる。

【0036】

なお、FETQoのオン抵抗Ronと、配線パターン抵抗Rpに対して、オフセット抵抗Roと、検出部抵抗Rdとは、十分大きな値に設定する。これは、オフセット抵抗Roと、検出部抵抗Rdの値が小さい場合は、このオフセット抵抗Roと検出部抵抗Rdとを通して流れる電流(FETQo側から分流する電流)が増大し、FETQoに流れる電流の検出誤差が増大するためである。

【0037】

[第2の実施形態]

次に、本発明の第2の実施形態として、上述した第1の実施形態の電流検出回路を、インバータにより3相交流モータを回転制御するモータ制御装置に用いた例について説明する。

【0038】

(モータ制御装置の構成についての説明)

図2は、本発明の実施形態に係わるモータ制御装置の構成を示す図である。図2に示すモータ制御装置10は、例えば、バッテリ(図示せず)を直流電源とし、このバッテリの直流電圧を交流電圧に変換して3相交流モータ(3相ブラシレスモータや3相誘導モータ)10を駆動する制御装置である。

【0039】

図2において、3相交流モータ(単に「モータ」とも呼ぶ)10は、例えば、エンジン(内燃機関)のスタータモータとなるモータである。この3相交流モータ10が、例えば、3相ブラシレスモータである場合は、このモータ10は、U、V、Wの各相コイル(鉄心に巻かれているコイル)を有するステータと、永久磁石からなるロータとで構成され、ステータには3相(U、V、W)のコイルが周方向に順番に巻装される。

【0040】

また、このモータ制御装置11内には、Nch型のMOSFET(Metal-Oxide Semiconductor Field-Effect Transistor)であるFETQ1〜Q6で構成される3相ブリッジ回路12が設けられている。この3相ブリッジ回路12は、FETQ1〜Q6がプリント配線基板上に実装されて構成されており、この3相ブリッジ回路12において、上アーム側のFETQ1、Q2、Q3のそれぞれのドレイン端子は、このFETQ1、Q2、Q3に流れる電流の電流経路となるそれぞれの配線パターンを介して、プリント配線基板上に設けられた正側電極端子A(+)に共通に接続されている。そして、この正側電極端子A(+)は、図示しない直流電源(例えば、バッテリ)の正電極に接続されている。

【0041】

また、下アーム側のFETQ4,Q5,Q6のそれぞれのソース端子は、このFETQ4,Q5,Q6に流れる電流の電流経路となるそれぞれの配線パターン(配線パターン抵抗Rp1,Rp2,Rp3で示す経路)を介して、プリント配線基板上に設けられた負電極端子B(−)に共通に接続されている。そして、このプリント配線基板上の負電極端子B(−)は、図示しない直流電源(例えば、バッテリ)の負電極に接続されており、また、この負電極端子B(−)は、後述する電流検出回路14や、過電流検出回路15や、制御部20などを構成する回路の基準電位(グランド)となる回路グランドGに接続されている。

【0042】

そして、3相ブリッジ回路12において、FETQ4のソース端子と負電極端子B(−)との間に挿入された抵抗Rp1は、FETQ4のソース端子と負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp1)を示している。また、FETQ5のソースと負電極端子B(−)との間に挿入された抵抗Rp2は、FETQ5のソースと負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp2)を示している。また、FETQ6のソースと負電極端子B(−)との間に挿入された抵抗Rp3は、FETQ6のソースと負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp3)を示している。

【0043】

なお、この配線パターン抵抗Rp1,Rp2,Rp3の抵抗値は、プリント配線基板上に実装されるFETQ1〜Q6の配置状況に応じて変化する。すなわち、配線パターン抵抗Rp1,Rp2,Rp3の抵抗値は、配線パターンの長さ(配線長)、幅、および厚みにより変化する。図2に示す例では、例えば、Rp1<Rp2<Rp3とする。すなわち、FETQ4のソース端子と負電極端子B(−)とを結ぶ配線パターンが最も短く、FETQ5のソース端子と負電極端子B(−)とを結ぶ配線パターンが次に長く、FETQ6のソース端子と負電極端子B(−)とを結ぶ配線パターンが最も長いものとする。

【0044】

そして、上アーム側のFETQ1のソース端子と、下アーム側のFETQ4のドレイン端子とが接続され、このFETQ1とQ4の接続点が、出力配線Luを介して3相交流モータ10のU相コイル端子に接続されている。また、上アーム側のFETQ2のソース端子と、下アーム側のFETQ5のドレイン端子とが接続され、このFETQ2とQ5の接続点が、出力配線Lvを介して3相交流モータ10のV相コイル端子に接続されている。

【0045】

また、上アーム側のFETQ3のソース端子と、下アーム側のFETQ6のドレイン端子とが接続され、このFETQ3とQ6の接続点が、出力配線Lwを介して3相交流モータ10のW相コイル端子に接続されている。なお、FETQ1〜Q6のそれぞれには、フライホイールダイオードDxが、図に示すようにカソードが(+)電極方向に、アノードが(−)電極方向となるように並列に接続されている。

【0046】

また、モータ制御装置11は、上アーム側のスイッチング素子(FET)Q1、Q2、Q3および下アーム側のスイッチング素子(FET)Q4、Q5、Q6をオン/オフ駆動するゲート信号を生成するゲート駆動回路(ドライバー回路)13を有している。上記のFETQ1〜Q6は、ゲート駆動回路13から出力されるゲート駆動信号により駆動され、このゲート駆動信号は、制御部(CPU等で構成される制御部)20から出力されるFET駆動信号を基にして生成される。

【0047】

制御部20は、FET駆動信号生成部21と、通電制御部22と、同期信号生成部23と、過電流保護部(過電流保護回路)24と、を有して構成される。通電制御部22は、3相交流モータ10を駆動するための通電信号を生成するための処理部である。この通電制御部22では、例えば、3相交流モータ10が低速で回転する場合において、180度の全通電期間中、120度の期間だけコイルに通電するようにして3相交流モータ10を駆動制御する。また、例えば、3相交流モータ10の高速回転時において、180°通電により、3相交流モータ10を駆動制御する。

【0048】

FET駆動信号生成部21は、通電制御部22により生成された通電信号に基づき、FETの駆動信号を生成し、このFETの駆動信号をゲート駆動回路13に出力する。このゲート駆動回路13は、FETのゲート駆動信号を生成するためのドライバー回路であり、このゲート駆動回路13から出力されるゲート駆動信号により、上記のFETQ1〜Q6をオン/オフ駆動する。

【0049】

また、同期信号生成部23は、後述するスイッチSW1,SW2,SW3をオン/オフ駆動する同期信号を生成する。また、過電流保護部24は、後述するコンパレータCP1、CP2、CP3、およびコンパレータCP4から過電流検出信号が入力されると、FET駆動信号生成部21を介してゲート駆動回路13を制御し、このゲート駆動回路13からFETQ1〜Q6を一括オフするゲート駆動信号を出力させる。

【0050】

(電流検出回路14についての説明)

上記構成において、本実施形態のモータ制御装置11では、FETQ4,Q5,Q6のドレイン・ソース間電圧(より正確にはドレイン・回路グランド間電圧)を検出することにより、FETQ4,Q5,Q6に流れる電流を検出する。このため、モータ制御装置11は、電流検出回路14を備えている。また、電流検出回路14により検出された電流信号を、所定の電流設定基準電圧と比較する過電流検出回路15を備えている。

【0051】

上記電流検出回路14においては、FETQ6のドレイン端子と回路グランドGとの間に、検出部抵抗R1とオフセット抵抗Ro1とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ6のドレインに抵抗R1の一端を接続し、この抵抗R1の他端を抵抗Ro1の一端に接続し、抵抗Ro1の他端を回路グランドGに接続する。また、抵抗R1と抵抗Ro1の接続点(ノードN1)とグランドGとの間にスイッチSW1を接続する。

【0052】

また、FETQ5のドレイン端子とグランドGとの間に、検出部抵抗R2とオフセット抵抗Ro2とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ5のドレイン端子に抵抗R2の一端を接続し、この抵抗R2の他端を抵抗Ro2の一端に接続し、抵抗Ro2の他端をグランドGに接続する。また、抵抗R2と抵抗Ro2の接続点(ノードN2)とグランドGとの間にスイッチSW2を接続する。

【0053】

同様にして、FETQ4のドレイン端子と回路グランドGとの間に、検出部抵抗R3とオフセット抵抗Ro3とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ4のドレイン端子に抵抗R3の一端を接続し、この抵抗R3の他端を抵抗Ro3の一端に接続し、抵抗Ro3の他端を回路グランドGに接続する。また、抵抗R3と抵抗Ro3の接続点(ノードN3)と回路グランドGとの間にスイッチSW3を接続する。

【0054】

上記構成において、スイッチSW1は、FETQ6がオフの場合はオンになり、FETQ6がオンになるタイミングでオフになる。すなわち、FETQ6がオンになり、モータ10のW相電流IwがFETQ6に流れる状態において、スイッチSW1をオフにする。これにより、FETQ6がオンになるタイミングで、FETQ6のドレインに発生する電圧(W相電流に比例する電圧)を抵抗R1とRo1とにより分圧し、ノードN1の電圧としてコンパレータCP1の一方の端子に入力することができる。

【0055】

また、スイッチSW2は、FETQ5がオフの場合はオンになり、FETQ5がオンになるタイミングでオフになる。すなわち、FETQ5がオンになり、モータ10のV相電流IvがFETQ5に流れる状態において、スイッチSW2をオフにする。これにより、FETQ5がオンになるタイミングで、FETQ5のドレインに発生する電圧(V相電流Ivに比例する電圧)を抵抗R2とRo2とにより分圧し、ノードN2の電圧としてコンパレータCP2の一方の端子に入力することができる。

【0056】

同様にして、スイッチSW3は、FETQ4がオフの場合はオンになり、FETQ4がオンになるタイミングでオフになる。すなわち、FETQ4がオンになり、モータ10のU相電流IuがFETQ4に流れる状態において、スイッチSW3をオフにする。これにより、FETQ4がオンになるタイミングで、FETQ4のドレインに発生する電圧(U相電流Iuに比例する電圧)を抵抗R3とRo3とにより分圧し、ノードN3の電圧としてコンパレータCP3の一方の端子に入力することができる。

【0057】

(配線パターン抵抗により発生するオフセットについての説明)

ところで、FETQ4,Q5,Q6は、同じ仕様(定格電流、耐圧、構造等が同じ仕様)のFET素子であり、そのオン抵抗Ronは同じ値(例えば、4mΩ)とみなすことができる。そして、そのドレイン・ソース間電圧VDSは、図6に示すように、流れるドレイン電流IDに比例する。このため、FETQ4,Q5,Q6に流れる電流を検出するには、それぞれのドレイン・ソース間電圧VDSを検出すればよいことになる。

【0058】

しかしながら、前述したように、FETQ4,Q5,Q6のそれぞれのソース端子と負電極端子B(−)との間には、配線パターン抵抗(Rp1,Rp2,Rp3)が介在する。従って、FETQ4,Q5,Q6に流れる電流を測定するために、それぞれのFETQ4,Q5,Q6のドレイン端子と回路グランドGとの間の電圧VDGを測定する場合は、配線パターン抵抗(Rp1,Rp2,Rp3)に起因するオフセット分が含まれることになる。

【0059】

例えば、FETQ6がオンの状態においてモータ電流Iwが流れると、FETQ6のドレイン端子と回路グランドGとの間に発生する電圧VDG6は、以下の式になる。

【0060】

VDG6=Iw×Ron+Iw×Rp3

【0061】

また、FETQ5がオンの状態においてモータ電流Ivが流れると、FETQ5のドレイン端子と回路グランドGとの間に発生する電圧VDG5は、以下の式になる。

【0062】

VDG5=Iv×Ron+Iv×Rp2

【0063】

また、FETQ4がオンの状態においてモータ電流Iuが流れると、FETQ4のドレイン端子と回路グランドGとの間に発生する電圧VDG4は、以下の式になる。

【0064】

VDG4=Iu×Ron+Iu×Rp1

【0065】

このように、FETQ4,Q5,Q6のドレイン・回路グランド間電圧は、ドレイン・ソース間電圧VDSに、配線パターン抵抗(Rp1,Rp2,Rp3)による電圧降下がオフセット分として加わることになる。このため、FETQ4,Q5,Q6のドレイン・ソース間電圧を求めるには、上記オフセット分をキャンセルする必要がある。

【0066】

そこで、本実施形態の電流検出回路14では、第1の実施形態で説明したように、配線パターンの抵抗(Rp1,Rp2,Rp3)による電圧降下分を、抵抗分圧回路を構成するオフセット抵抗(Ro1,Ro2,Ro3)により分圧してオフセットする。

【0067】

このために、FETQ4,Q5,Q6のオン抵抗Ronと、配線パターン抵抗(Rp1,Rp2,Rp3)と、オフセット抵抗(Ro1,Ro2,Ro3)と、検出部抵抗(R1,R2,R3)との関係を以下のように定める。

【0068】

すなわち、FETQ6については、FETQ6のオン抵抗Ronと、配線パターン抵抗Rp3と、FETQ6に対応する検出部抵抗R1と、オフセット抵抗Ro1とにおいて、

【0069】

FETQ6のオン抵抗Ron:配線パターン抵抗(Rp3)

=オフセット抵抗(Ro1):検出部抵抗(R1)

【0070】

となるように設定する。

【0071】

また、FETQ5については、FETQ5のオン抵抗Ronと、配線パターン抵抗Rp2と、FETQ5に対応する検出部抵抗R2と、オフセット抵抗Ro2とにおいて、

【0072】

FETQ5のオン抵抗Ron:配線パターン抵抗(Rp2)

=オフセット抵抗(Ro2):検出部抵抗(R2)

【0073】

となるように設定する。

【0074】

また、FETQ4については、FETQ4のオン抵抗Ronと、配線パターン抵抗Rp1と、FETQ4に対応する検出部抵抗R3と、オフセット抵抗Ro3とにおいて、

【0075】

FETQ4のオン抵抗Ron:配線パターン抵抗(Rp1)

=オフセット抵抗(Ro3):検出部抵抗(R3)

【0076】

となるように設定する。

【0077】

ただし、上記設定において、「オン抵抗Ron,パターン抵抗(Rp1,Rp2,Rp3)≪オフセット抵抗(Ro1,Ro2,R03),検出部抵抗(R1,R2,R3)」となるように設定する。すなわち、オフセット抵抗(Ro1,Ro2,R03)および検出部抵抗(R1,R2,R3)の抵抗値が、オン抵抗Ronおよびパターン抵抗(Rp1,Rp2,Rp3)の抵抗値よりも十分大きな値となるように設定する。

【0078】

次に、具体的な例について説明する。図3は、配線パターン抵抗Rp3により発生する電圧降下(オフセット)をキャンセルする具体例について説明するための図である。この図3に示すように、モータ電流(W相電流Iw)を100Aとし、FETQ4,Q5,Q6のオン抵抗Ronを4mΩ(Ron=4mΩ)とし、FETQ6の配線パターン抵抗Rp3を1mΩ(Rp3=1mΩ)とし、検出部抵抗R1を10kΩ(R1=10kΩ)とする。

【0079】

そして、オフセット抵抗Ro1なしとした場合(Ro1=∞)は、検出電圧(ノードN1の電圧)は、0.50V「=100A×5mΩ」となり、本来のドレイン・ソース間電圧VDS「0.40V(=100A×4mΩ)」に対して、検出誤差は+25%となる。

【0080】

一方、オフセット抵抗Ro1を40kΩ(Ro1=40kΩ)とした場合は、検出電圧(ノードN1の電圧)は、0.50V×40kΩ/50kΩ=0.40Vとなり、本来のドレイン・ソース間電圧VDS「0.400V(=100A×4mΩ)」に対して、検出誤差はほぼ0%となる。

【0081】

このように、ドレイン電流IDが流れ電圧降下を発生させる側の上下の抵抗の抵抗値の比(例えば、Ron/Rp3)に対して、抵抗分圧回路側の上下の抵抗の抵抗値の比(例えば、R1/Ro1)が逆比になるように設定する(Ron/Rp3=Ro1/R1)。すなわち、オフセット抵抗Ro1と検出部抵抗R1との抵抗値の比(Ro1/R1)を、FETQ6のオン抵抗Ronと配線パターン抵抗Rp3との抵抗値の比(Ron/Rp3)に一致するように設定する。これにより、例えば、配線パターン抵抗Rp3により発生する電圧降下分(オフセット)をキャンセルして、FETQ6のドレイン・ソース間電圧VDSを検出することができる。

【0082】

(過電流検出回路15の構成と過電流検出動作についての説明)

次に、過電流検出回路15の構成と動作について説明する。前述したように、電流検出回路14のノードN1は、コンパレータCP1の一方の入力端子(−)に接続され、また、コンパレータCP1の他方の入力端子(+)には、基準となる電流設定基準電圧VR1が入力される。このため、FETQ6の電流信号(ノードN1の電圧)が,電流設定基準電圧VR1より低い場合(過電流状態でない場合)は、コンパレータCP1の出力は、例えば、H状態となり、FETQ6の電流信号(ノードN1の電圧)が,電流設定基準電圧VR1よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0083】

また、電流検出回路14のノードN2は、コンパレータCP2の一方の入力端子(−)に接続され、コンパレータCP2の他方の入力端子(+)には、基準となる電流設定基準電圧VR2が入力される。このため、FETQ5の電流信号(ノードN2の電圧)が、電流設定基準電圧VR2より低い場合(過電流状態でない場合)は、コンパレータCP2の出力は、例えば、H状態となり、FETQ6の電流信号(ノードN2の電圧)が、電流設定基準電圧VR2よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0084】

同様にして、ノードN3は、コンパレータCP3の一方の入力端子(−)に接続され、コンパレータCP3の他方の入力端子(+)には、基準となる電流設定基準電圧VR3が入力される。このため、FETQ4の電流信号(ノードN3の電圧)が、電流設定基準電圧VR3より低い場合(過電流状態でない場合)は、コンパレータCP3の出力は、例えば、H状態となり、FETQ4の電流信号(ノードN3の電圧)が、電流設定基準電圧VR3よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0085】

また、電流検出回路14のノードN1は、アンプ(増幅器)AM11の一方の入力端子(+)に接続され、アンプAM11の他方の入力端子(−)には、アンプAM11の出力端子が接続される。これにより、アンプAM11はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN1から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0086】

また、電流検出回路14のノードN2は、アンプ(増幅器)AM12の一方の入力端子(+)に接続され、アンプAM12の他方の入力端子(−)には、アンプAM12の出力端子が接続される。これにより、アンプAM12はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN2から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0087】

同様にして、電流検出回路14のノードN3は、アンプ(増幅器)AM13の一方の入力端子(+)に接続され、アンプAM13の他方の入力端子(−)には、アンプAM13の出力端子が接続される。これにより、アンプAM13はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN3から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0088】

そして、アンプAM11の出力端子は抵抗R11を介してノードN4に接続され、アンプAM12の出力端子は抵抗R12を介してノードN4に接続され、アンプAM13の出力端子は抵抗R13を介してノードN4に接続される。これにより、アンプAM11と、アンプAM12と、アンプAM13の出力信号は、ノードN4においてワイヤードオアされる。このため、アンプAM11の出力信号と、アンプAM12の出力信号と、アンプAM13の出力信号のうちで最も信号レベルの高い信号(最も電圧レベルの高い信号)が

選択されてノードN4に現れる。

【0089】

このノードN4は、コンパレータCP4の一方の入力端子(−)に接続され、コンパレータCP4の他方の入力端子(+)には、基準となる電流設定基準電圧VR4が入力されている。このため、ノードN4の電圧が、電流設定基準電圧VR4より低い場合(過電流状態でない場合)は、コンパレータCP4の出力が、例えば、H状態となる。また、ノードN4の電圧が、電流設定基準電圧VR4よりも高くなる場合(過電流状態の場合)は、コンパレータCP4の出力が、例えば、L状態になる。

【0090】

従って、このアンプAM11,AM12,AM13とコンパレータCP4で構成される回路の系統では、ノードN1、ノードN2、ノードN3のいずれかの電圧が電流設定基準電圧VR4よりも高くなると(FETQ4,Q5,Q6のいずれかが過電流状態になると)、コンパレータCP4の出力が、例えば、L状態となる。

【0091】

このように、コンパレータCP1,CP2,CP3は、コンパレータCP1がFETQ6の過電流状態を検出し、コンパレータCP2がFETQ5の過電流状態を検出し、コンパレータCP3がFETQ4の過電流状態を検出するなど、個々のFETQ4,Q5,Q6の過電流状態を検出する。これに対して、アンプAM11,AM12,AM13とコンパレータCP4で構成される回路の系統では、FETQ4,Q5,Q6の過電流状態を一括して検出するものである。すなわち、アンプAMAM11,AM12,AM13とコンパレータCP4で構成される回路の系統は、コンパレータCP1,CP2,CP3を用いた過電流検出系統に対して、これを補完する予備の過電流検出系統として機能するものである。

【0092】

そして、コンパレータCP1,CP2,CP3、およびCP4の出力端子は信号線OCLに共通に接続されてワーヤードOR(オア)回路を構成している。このため、コンパレータCP1,CP2,CP3、およびCP4のいずれかの出力が、例えば、L状態になると、信号線OCLがL状態となり、このL状態の信号が過電流検出信号として制御部20に出力される。制御部20内の過電流保護部(過電流保護回路)24は、コンパレータCP1、CP2、CP3、およびコンパレータCP4から過電流検出信号(L状態の信号)が入力されると、FET駆動信号生成部21を介してゲート駆動回路13を制御し、このゲート駆動回路13からFETQ1〜Q6を一括オフするゲート駆動信号を出力させる。これにより、下アーム側のFETQ4,Q5,Q6のいずれかに過電流が流れる場合に、FETQ1〜Q6を一括オフし、FETQ1〜Q6を保護することができる。

【0093】

また、図4は、FETに流れる電流(ドレイン・ソース間電圧VDS)の検出タイミングを示す図である。この図4では、横方向に時間tの経過を示し、縦方向に、FETQnのドレイン・ソース間電圧VDSと、スイッチSWnのオン/オフ状態と、コンパレータCPnの入力電圧と、を並べて示したものである。

なお、この図4において、時刻t1は、FETQnがターンオンを開始する時刻を示し、時刻t1〜時刻t2までの期間ΔT1は、FETQnのタンーオン時間に応じて設けられる不感帯(電流検出を行わない期間)であり、時刻t3は、FETQnがターンオフを開始する時刻を示し、時刻t4はFETQnがターンオフを完了した時刻を示している。また、時刻t3から時刻t4までの期間ΔT2も、前述のΔT1と同様に、電流検出を行わない不感帯の期間である。

【0094】

図4に示すように、時刻t1以前のFETQn(例えば、FETQ6)がオフ(OFF)の状態においては、スイッチSWn(例えば、スイッチSW1)をオン(ON)状態にする。これにより、時刻t1以前には、コンパレータCpn(例えば、コンパレータCp1)に、FETQnの電流検出信号(例えば、ノードN1の電圧)が入力されないようにする。すなわち、コンパレータCpnの入力電圧を閾値(過電流設定基準電圧)以下にすることにより、コンパレータCpnにおいて過電流検出を行わないようにする。

【0095】

そして、時刻t1において、下アーム側のFETQn(例えば、W相のFETQ6)がターンオンを開始する。この時刻t1においてFETQnがターンオンを開始した後の時刻t2までの間は、スイッチSWn(例えば、スイッチSW1)のオン状態をそのまま保持し、時刻t2において、スイッチSWnをオフにする。

このようにスイッチSWnをオフにする際には、時刻t1よりΔT1だけ遅らせたタイミングの時刻t2で、スイッチSWnをオフにする。このように不感帯の期間ΔT1を設けることにより、FETQnがオンした後、FETQnに流れる電流が0から定常電流値まで立ち上がる過渡的な状態おいて発生する電流(例えば、過渡状態で発生する尖塔的なピーク電流等)を過電流として誤検出することを回避する。

【0096】

そして、時刻t2において、このスイッチSWnがオフになることにより、FETQnの電流検出信号(例えば、ノードN1の電圧)が、コンパレータCpn(例えば、コンパレータCP1)に入力され、FETQnに流れる電流の検出(過電流検出)が可能になる。これにより、FETQnに流れる電流が安定した時点で、コンパレータCpnは、FETQnに流れる電流(過電流)を検出することができる。

【0097】

そして、時刻t2において電流検出を開始した後、FETQnがターンオフを開始するタイミング(または、このターンオフを開始する直前のタイミング)である時刻t3(ターンオフ時刻t4よりも期間ΔT2だけ前の時刻t3)において、スイッチSWnをオンにする。このスイッチSWnがオンになることにより、時刻t3以降、コンパレータCpnに、FETQnの電流検出信号が入力されないようにする。すなわち、コンパレータCpnの入力電圧を閾値(過電流設定基準電圧)以下にし、コンパレータCpnにおいて過電流検出を行わないようにする。

このように期間ΔT2を設けることにより、FETQnがターンオフを開始した後、FETQnに流れる電流が定常電流から0に立ちさがるまでの過渡的な状態において流れる電流(例えば、過渡状態で発生する尖塔的なピーク電流等)を過電流として誤検出することを回避する。

【0098】

この図4のタイミングチャートに示すように、FETQnのオン期間中(時刻t1〜t4)において、不感帯(ΔT1およびΔT2)を設けて電流を検出することにより、FETQnに流れる電流が安定した時点で、このFETQnに流れる電流(過電流)を検出することができる。

【0099】

以上、本発明の実施形態について説明したが、ここで、本発明と上記実施形態における対応関係について補足して説明する。

すなわち、上記実施形態において、本発明における電流検出回路は、図1に示す電流検出回路1、および図2に示す電流検出回路14が対応し、本発明におけるモータ制御装置は、図2に示すモータ制御装置11が対応する。また、本発明における制御回路は、図2に示す制御部20、電流検出回路14、過電流検出回路15等が対応する。また、本発明における3相ブリッジ回路は、3相ブリッジ回路12が対応し、本発明におけるスイッチ素子は、図1に示すFET(Qo)および図2に示すFET(Q1〜Q6)が対応する。また、本発明におけるスイッチ素子のオン抵抗は、オン抵抗Ronが対応し、本発明における配線パターン抵抗は、図1に示す配線パターン抵抗Rpおよび図2に示す配線パターン抵抗(Rp1,Rp2,Rp3)が対応し、本発明における第1の抵抗は、図1に示す検出部抵抗Rdおよび図2に示す検出部抵抗(R1,R2,R3)が対応する。また、本発明における第2の抵抗は、図1に示すオフセット抵抗Roおよび図2に示すオフセット抵抗(Ro1,Ro2,Ro3)が対応する。

【0100】

また、本発明における過電流検出回路は、過電流検出回路15が対応し、本発明における過電流保護部は、制御部20内の過電流保護部24が対応する。また、本発明におけるスイッチは、スイッチSW1,SW2,SW3が対応する。また、本発明におけるスイッチ素子の一方の入出力端子は、図1に示すFET(Qo)のソース端子、または図2に示すFET(Q4,Q5,Q6)のソース端子が対応する。また、本発明におけるスイッチ素子の他方の入出力端子は、図1に示すFET(Qo)のドレイン端子、または図2に示すFET(Q4,Q5,Q6)のドレイン端子が対応する。

【0101】

(1)そして、上記実施形態において、電流検出回路1は、図1に示すように、プリント配線基板上に実装されるFET(Qo)のソース端子Sが、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子B(−)に接続され、該負電極端子B(−)はFET(Qo)に電流を供給する直流電源の負極側に接続されるとともに、FET(Qo)を制御する制御回路の回路グランドGに接続される回路において、FET(Qo)の導通時における電圧降下を基に、該FET(Qo)に流れる電流を検出する電流検出回路は、FET(Qo)のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗Rdと第2の抵抗Roとからなる抵抗直列回路を備え、上記抵抗直列回路においては、第1の抵抗Rdの一端がFET(Qo)のドレイン端子Dに接続され、他端が第2の抵抗Roの一端に接続され、第2の抵抗Roの他端が回路グランドGに接続され、第2の抵抗Roと第1の抵抗Rdとの抵抗値の比(第2の抵抗/第1の抵抗)が、FETの導通時のオン抵抗Ronと配線パターン抵抗Rpとの抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)の電圧であって回路グランドGに対する電圧VRoをFET(Qo)に流れる電流の検出信号として出力する。

【0102】

このような構成1の電流検出回路では、図1に示すように、FET(Qo)のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗Rdと第2の抵抗Roとで構成される抵抗直列回路を備える。そして、第2の抵抗Roと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターン抵抗Rpの抵抗値の比(Ron/Rp)に一致するように設定される。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

【0103】

これにより、プリント配線基板上に搭載されるFET(Qo)に流れる電流を、FET(Qo)のオン時のドレイン端子Dと回路グランドGとの間の電圧降下VDGを基に検出する際に、FET(Qo)の電流経路を形成する配線パターンの配線パターン抵抗Rpにより発生するオフセット分を容易にキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出することができる。このため、配線パターン抵抗Rpの影響をキャンセルして、FET(Qo)に流れる電流を検出することができる。

【0104】

(2)また、上記実施形態において、電流検出回路1は、FET(Qo)のオン抵抗Ronと配線パターン抵抗Rpの抵抗値に比べて、第1の抵抗Rdと第2の抵抗Roの抵抗値が、FET(Qo)に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される。

これにより、フセット抵抗Roと検出部抵抗Rdとを通して流れる電流を少なくすることができ、FET(Qo)に流れる電流の検出誤差を少なくすることができる。

【0105】

(3)また、上記実施形態において、モータ制御装置11は、図2に示すように、プリント配線基板上に実装されるFETの3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置11であって、直流電源から各FETQ1〜Q6に流れる電流の電流経路がプリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各FETQ4,Q5,Q6と直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、下アーム側の対応するFETQ4,Q5,Q6のソース端子Sに接続され、他端が、プリント配線基板上に設けられた負電極端子B(−)に接続され、該負電極端子B(−)は直流電源の負極側に接続されるとともに制御回路の回路グランドGに接続されて構成されるモータ制御装置において、下アーム側のFETQ4,Q5,Q6の導通時における電圧降下を基に、該FETに流れる電流を検出する電流検出回路14は、下アーム側の各FETQ4,Q5,Q6に対応して、FETQ4,Q5,Q6のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)とからなるそれぞれの抵抗直列回路を備え、上記それぞれの抵抗直列回路においては、第1の抵抗(R1,R2,R3)の一端が対応するFETのドレイン端子に接続され、他端が第2の抵抗(Ro1,Ro2,Ro3)の一端に接続され、第2の抵抗(Ro1,Ro2,Ro3)の他端が回路グランドGに接続され、第2の抵抗(Ro1,Ro2,Ro3)と第1の抵抗(R1,R2,R3)との抵抗値の比(第2の抵抗/第1の抵抗)が、対応するFETの導通時のオン抵抗(Ron)と配線パターン抵抗(Rp1,Rp2,Rp3)との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)との接続点の電圧であって回路グランドGに対する電圧を各FET(Q4,Q5,Q6)に流れる電流の検出信号として出力する。

【0106】

このような構成のモータ制御装置11では、図2に示すように、下アーム側のFET(Q4,Q5,Q6)の導通時における電圧降下を基に、該下アーム側のFET(Q4,Q5,Q6)に流れる電流を検出する電流検出回路14を備える。そして、電流検出回路14は、下アーム側の各FET(Q4,Q5,Q6)に対応して、それぞれが第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)とからなる抵抗直列回路(抵抗分圧回路)を備える。この抵抗直列回路(抵抗分圧回路)においては、第1の抵抗(R1,R2,R3)の一端が対応するFET(Q4,Q5,Q6)のドレイン端子Dに接続され、他端が第2の抵抗(Ro1,Ro2,Ro3)の一端に接続され、第2の抵抗(Ro1,Ro2,Ro3)の他端が回路グランドGに接続される。そして、第2の抵抗(Ro1,Ro2,Ro3)と第1の抵抗(R1,R2,R3)との抵抗値の比(例えば、第2の抵抗Ro1/第1の抵抗R1)が、対応するFET(Q4,Q5,Q6)の導通時のオン抵抗Ronと配線パターン抵抗(Rp1,Rp2,Rp3)との抵抗値の比(例えば、オン抵抗Ron/配線パターン抵抗Rp3)に一致するように設定され、第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)との接続点(ノードN1,N2,N3)の電圧であって回路グランドGに対する電圧をFET(Q4,Q5,Q6)に流れる電流の検出信号として出力する。

【0107】

これにより、モータ制御装置11では、プリント配線基板上に搭載されるFET(Q4,Q5,Q6)に流れる電流を、FET(Q4,Q5,Q6)のオン時のドレイン端子Dと回路グランドGとの間の電圧降下VDGを基に検出する際に、FET(Q4,Q5,Q6)の電流経路を形成する配線パターンの配線パターン抵抗(Rp1,Rp2,Rp3)により発生するオフセット分を容易にキャンセルして、FET(Q4,Q5,Q6)のドレイン・ソース間電圧VDSを検出することができる。このため、配線パターン抵抗(Rp1,Rp2,Rp3)の影響をキャンセルして、FET(Q4,Q5,Q6)に流れる電流を検出することができる。

【0108】

(4)また、上記実施形態において、モータ制御装置11は、FET(Q4,Q5,Q6)のオン抵抗(Ron)および前記配線パターン抵抗(Rp1,Rp2,Rp3)の抵抗値に比べて、第1の抵抗(R1,R2,R3)および第2の抵抗(Ro1,Ro2,Ro3)の抵抗値が、FET(Q4,Q5,Q6)に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される。

これにより、オフセット抵抗(Ro1,Ro2,Ro3)と検出部抵抗(R1,R2,R3)を通して流れる電流を少なくし、FET(Q4,Q5,Q6)に流れる電流の検出誤差を少なくすることができる。

【0109】

(5)また、上記実施形態において、モータ制御装置11は、下アーム側の各FET(Q4,Q5,Q6に対応する抵抗直列回路内の第2の抵抗(Ro1,Ro2,Ro3)のそれぞれに並列に接続されるスイッチ(スイッチSW1,SW2,SW3)であって、下アーム側の対応するFET(Q4,Q5,Q6)の導通タイミングに合わせてオフし、対応するFET(Q4,Q5,Q6)の電流検出信号を当該FETの導通時にのみ出力するスイッチ(スイッチSW1,SW2,SW3)を備える。

【0110】

これにより、FET(Q4,Q5,Q6)の電流検出信号を当該FETの導通時にのみ出力することができる。このため、FETがオフしている場合には、電流検出信号の出力を停止するので、他の相の電流検出信号にノイズ等の影響を与えることがなくなる。また、図4に示す特許文献1に記載のモータ制御装置では、アナログスイッチAS1,AS2,AS3が、信号の検出経路(FETのドレイン端子とアンプAMの入力端子を繋ぐ信号線の経路)に挿入されているため、このアナログスイッチAS1,AS2,AS3の内部インピーダンスにより電流検出信号が影響を受ける可能性があるが、図2に示す本実施形態のモータ制御装置11では、スイッチ(SW1,SW2,SW3)が信号の検出経路(FETのドレイン端子とコンパレータの入力端子を繋ぐ信号線の経路)に挿入されないため、信号の検出の際に、スイッチ(SW1,SW2,SW3)の内部インピーダンスによる影響を受けることがない。

【0111】

(6)また、上記実施形態において、モータ制御装置11は、下アーム側のFET(Q4,Q5,Q6)のオン時の電流検出信号が所定の過電流設定基準電圧(VR1,VR2,VR3,VR4)を超えたときに過電流検出信号を出力する過電流検出回路15と、過電流検出回路15から過電流検出信号が出力された場合に、3相ブリッジ回路12の各FET(Q1〜Q6)のすべてをオフする過電流保護部24と、を備える。

これにより、下アーム側のFET(Q4,Q5,Q6)のいずれかにおいて過電流状態が検出された場合に、3相ブリッジ回路12の各FET(Q4,Q5,Q6)のすべてを直ちに一括オフすることができる。このため、過電流によりFET(Q4,Q5,Q6)が損傷することを回避することができる。

【0112】

以上、本発明の実施の形態について説明したが、本発明の電流検出回路。およびモータ制御装置は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。また、本発明のスイッチ素子は、上述の図示例ではFETで示してあるが、スイッチ素子であればこれに限定されない。また、本発明のスイッチは、スイッチ素子であっても、アナログスイッチであっても良く、これに限定されない。

【符号の説明】

【0113】

1、14 電流検出回路、

10 3相交流モータ

11 モータ制御装置

12 3相ブリッジ回路

13 ゲート駆動回路

14 電流検出回路

15 過電流検出回路

20 制御部

21 FET信号生成部

22 通電制御部

23 同期信号生成部

24 過電流保護部

Q1,Q2,Q3 上アーム側のFET

Q4,Q5,Q6 下アーム側のFET

CP1,CP2,CP3,CP4 コンパレータ

Ron FETのオン抵抗

Rp1,Rp2,Rp3 配線パターン抵抗

Rd,R1,R2,R3 検出部抵抗(第1の抵抗)

Ro,Ro1,Ro2,Ro3 オフセット抵抗(第2の抵抗)

SW1,SW2,SW3 スイッチ

AM11,AM12,AM13 アンプ(増幅器)

【技術分野】

【0001】

本発明は、スイッチ素子、特にFET(電界効果トランジスタ)に流れる電流を検出する電流検出回路、および、この電流検出回路を用いたモータ制御装置に関する。

【背景技術】

【0002】

モータ制御装置には、インバータにより直流電圧を3相交流電圧に変換し、この3相交流電圧により3相交流モータ(3相ブラシレスモータや3相誘導モータ)を駆動するものがある(例えば、特許文献1を参照)。図5は、特許文献1に記載のモータ制御装置の構成図(特許文献1の図2)をそのまま示したものである。この図5に示すモータ制御装置は、6個のトランジスタQ1’〜Q6’で構成される3相ブリッジ回路と、制御回路CONTとからなるインバータ回路を用いて直流を交流に変換すると共に、出力電圧を制御して3相ブラシレスモータMの回転を制御するものである。このようなインバータ回路においては、過電流によるトランジスタの損傷、および過負荷によりモータの性能劣化などを防ぐことが必要になる。

【0003】

そこで、インバータの出力電流が過電流領域になったことを検出する回路を用いて、過電流発生時にトランジスタQ1’〜Q6’を一括オフ(すべてオフ)することによりモータ電流を遮断する方法が用いられている。この過電流を検出する代表的なものの1つに、インバータの3相ブリッジ回路の入力側(例えば、3相ブリッジ回路と電極(+)とを結ぶ直流電源線)に電流検出抵抗(または、分流器)を挿入し、その検出電圧を電流設定基準電圧と比較することにより過電流状態を検出する方法がある。また、例えば、ホール素子を内蔵するホールセンサをインバータの入力側(例えば、3相ブリッジ回路と電極(+)とを結ぶ直流電源線)に配置し、このホールセンサの出力電圧を電流設定基準電圧と比較することにより過電流状態を検出する方法がある。

【0004】

しかしながら、上記電流検出抵抗やホール素子を用いることはモータ制御装置(より正確には過電流保護回路)の小型化の要請に反し、また、これらの部品を使用することにより製品コストが上昇することになる。この問題に対処するために、上記特許文献1に記載のモータ制御装置では、FET(Field Effect Transistor)の導通タイミングにおけるオン電圧(電圧降下)を基に、FETに流れる電流を検出している。

【0005】

すなわち、図5に示す特許文献1に記載のモータ制御装置では、3相ブリッジ回路を、FETQ1’〜Q6を用いて構成し、モータMの第1相、第2相、第3相のモータ電流に比例するFETQ1’〜Q6のドレイン・ソース電圧VDS4,VDS5,VDS6を、各FETの導通タイミングに合わせてオンされる3個のスイッチAS1、AS2、AS3を介して、直列的に順次に検出する。そして、FETQ1’〜Q6’のドレイン・ソース電圧VDS4,VDS5,VDS6が電流設定基準電圧Vsを超えたときを過電流と判定して、制御回路CONTからの駆動情号を停止し、全てのFETをオフすることにより、過電流を流さないようにしている。

【0006】

なお、図6は、同じく上記特許文献1に記載された図(特許文献1の図1)をそのまま示した図であり、FETのドレイン・ソース間電圧VDSとドレイン電流IDの関係図である。この図に示すように、FETのゲート電圧VGをパラメータとすると、FETオン時のドレイン・ソース間の電圧降下VDSと、ドレイン電流IDとは、図に示すように、広い範囲に亘って直線的な比例関係を有する。しかもその傾斜は通常のトランジスタのそれに比べてかに緩やかであるため、ドレイン電流の変化に比例した十分大きなドレイン・ソース間電圧降下の変化を得ることができる。従って制御電流領域と過電流領域との間に大きな差をもたせることができるので、効果的な過電流の検出が可能である.

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開平4−308420号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

上述した特許文献1に記載のモータ制御装置では、モータ、トランジスタなどの過電流による損傷防止用過電流保護回路の小型化や、コストダウンを目的とし、ドレイン電流とドレイン・ソース間電圧圧降下とが広い範囲に亘って直線的関係にあるFETを用いると共に、このFETの動通タイミングに合わせてオンして、上記モータの各相電流に比例したドレイン・ソース間電圧降下を直列的に順次検出するスイッチ回路を設け、この回路の出力が設定基準電圧を越えたとき過電流と判定して上記制御回路への駆動信号の供給を停止しFETの電流遮断を行うようにしている。

【0009】

しかしながら、上記特許文献1に記載のFETのドレイン・ソース間電圧の検出による過電流保護回路にあっては、次のような問題点がある。すなわち、FETQ1’〜Q6’をプリント配線基板上に実装する構成においては、FETQ1’〜Q6’に流れる電流経路が配線パターンにより形成されることになる。したがって、直流電源の(−)端子を基準(回路グランド)として、FETQ4’〜Q6’のドレイン・ソース電圧(より正確には、ドレイン・回路グランド間電圧)を測定する場合には、配線パターンの抵抗による電圧降下分(オフセット)が含まれることになる。

【0010】

この場合、直流電源の(−)端子とトランジスタQ4’のソースとの間の配線パターンと、直流電源の(−)端子とトランジスタQ5’のソースとの間の配線パターンと、直流電源の(−)端子とトランジスタQ6’のソースとの間の配線パターンとの、それぞれ長さ(或いは幅、厚み)が異なることがある。このため、FETQ4’〜Q6’のドレイン・回路グランド間電圧には、配線パターンの抵抗値が異なることによる電圧差(電圧降下の差)が発生し、過電流の判定値がばらつくという問題がある。従って、配線パターンの抵抗のバラツキを考慮して、FETQ4’〜Q6’のドレイン・ソース間電圧を検出することが必要になる。

【0011】

本発明は、斯かる実情に鑑みなされたものであり、プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のドレインと回路グランド間の電圧降下VDGを基に検出する際に、FETの電流経路を形成する配線パターンの抵抗により発生するオフセット分を簡易な方法によりキャンセルして、FETのドレイン・ソース間の電圧降下(FETに流れる電流)を検出することができる、電流検出回路、および該電流検出回路を備えるモータ制御装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明は、上記課題を解決するためなされたものであり、本発明の電流検出回路は、プリント配線基板上に実装されるスイッチ素子の一方の入出力端子が、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記スイッチ素子に電流を供給する直流電源の負極側に接続されるとともに、前記スイッチ素子を制御する制御回路の回路グランドに接続される回路において、前記スイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなる抵抗直列回路を備え、前記抵抗直列回路においては、前記第1の抵抗の一端が前記スイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記スイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力することを特徴とする。

【0013】

また、本発明の電流検出回路は、前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定されることを特徴とする。

【0014】

また、本発明のモータ制御装置は、プリント配線基板上に実装されるスイッチ素子の3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置であって、前記直流電源から各スイッチ素子に流れる電流の電流経路が前記プリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各スイッチ素子と前記直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、前記下アーム側の対応するスイッチ素子の一方の入出力端子に接続され、他端が、前記プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記直流電源の負極側に接続されるとともに前記制御回路の回路グランドに接続されて構成されるモータ制御装置において、前記下アーム側のスイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記下アーム側の各スイッチ素子に対応して、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなるそれぞれの抵抗直列回路を備え、前記それぞれの抵抗直列回路においては、前記第1の抵抗の一端が対応するスイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記対応するスイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力することを特徴とする。

【0015】

また、本発明のモータ制御装置は、前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定されることを特徴とする。

【0016】

また、本発明のモータ制御装置は、前記下アーム側の各スイッチ素子に対応する第2の抵抗のそれぞれに並列に接続されるスイッチであって、前記下アーム側の対応するスイッチ素子の導通タイミングに合わせてオフし、前記対応するスイッチ素子の電流検出信号を当該スイッチ素子の導通時にのみ出力するスイッチを備えることを特徴とする。

【0017】

また、本発明のモータ制御装置は、前記下アーム側のスイッチ素子のオン時の電流検出信号が所定の過電流設定基準電圧を超えたときに過電流検出信号を出力する過電流検出回路と、前記過電流検出回路から過電流検出信号が出力された場合に、前記3相ブリッジ回路の各スイッチ素子のすべてをオフする過電流保護部と、を備えることを特徴とする。

【発明の効果】

【0018】

本発明の電流検出回路においては、スイッチ素子の一方の入出力端子と回路グランドとの間に接続される第1の抵抗と第2の抵抗とでなる抵抗直列回路を備え、この第2の抵抗と第1の抵抗の抵抗値の比(第2の抵抗/第1の抵抗)が、上記スイッチ素子のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定するとともに、第1の抵抗と第2の抵抗との接続点と回路グランドとの間の電圧をスイッチ素子に流れる電流の検出信号として出力する。

これにより、プリント配線基板上に搭載されるスイッチ素子に流れる電流を、スイッチ素子オン時のドレイン端子と回路グランド間の電圧降下を基に検出する際に、スイッチ素子の電流経路を形成する配線パターンの抵抗により発生するオフセット分を簡易な方法によりキャンセルして、スイッチ素子の一方の入出力端子と他方の入出力端子間電圧(スイッチ素子に流れる電流)を検出することができる。

【図面の簡単な説明】

【0019】

【図1】本発明の第1の実施形態に係わる電流検出回路を示す図である。

【図2】本発明の第2の実施形態に係わるモータ制御装置の構成を示す図である。

【図3】図2に示すモータ制御装置における電流検出回路の動作を説明するための図である。

【図4】FETに流れる電流(ドレイン・ソース間電圧VDS)の検出タイミングを示す図である。

【図5】特許文献1に記載のモータ制御装置の構成を示す図である。

【図6】FETのドレイン・ソース間電圧降下とドレイン電流の関係図である。

【発明を実施するための形態】

【0020】

以下、本発明の実施の形態を添付図面を参照して説明する。

【0021】

[第1の実施形態]

図1は、本発明の第1の実施形態に係わる電流検出回路の構成を示す図である。この図1に示す回路おいては、電流検出対象となるFETQoはプリント配線基板上に実装され、また、直流電源装置(図示せず)の負極側に繋がる負極端子B(−)もプリント配線基板上に実装されている。そして、FETQoのソース端子Sは、このFETQoに流れる電流経路となる配線パターン(配線パターン抵抗Rpで示す経路)を介して、プリント配線基板上の負極端子B(−)に接続されるとともに、回路グランドGに接続されている。なお、FETQoは、図示しない制御回路(例えば、図2に示す制御部20等を参照)により、オン/オフ制御されるものである。

【0022】

図1に示すように、本実施形態の電流検出回路1は、抵抗分圧回路で構成され、この抵抗分圧回路は、検出部抵抗R1(第1の抵抗)とオフセット抵抗Ro(第2の抵抗)の直列回路で構成され、この検出部抵抗R1とオフセット抵抗Roとの接続点(ノードN1)から電流検出信号が出力される。

【0023】

この電流検出回路1は、FETQoに流れる電流(ドレイン電流ID)を、このFETQoのドレイン・ソース間電圧VDSを基に検出することを目的とする回路である。すなわち、図6に示すように、FETQoのドレイン・ソース間電圧VDS(電圧降下)は、ドレイン電流IDに比例する関係にあるので、このFETQoのドレイン・ソース間電圧VDS(電圧降下)を基に、FETQoに流れる電流(ドレイン電流ID)を検出する。

【0024】

ところで、図1に示す回路構成においては、FETQoのドレイン・ソース間電圧VDSを直接には測定せず、FETQoのドレイン端子Dと回路グランドGとの間の電圧VDGを測定している。このドレイン・回路グランド間電圧VDGには、FETQoのドレイン・ソース間電圧VDS(電圧降下=オン抵抗Ron×ドレイン電流ID)に加えて、配線パターン抵抗Rpによる電圧降下分がオフセットとして含まれる。従って、このドレイン・回路グランド間電圧VDGは、以下の式(1)のようになる。

【0025】

VDG=Ron×ID+Rp×ID・・・(1)

【0026】

この配線パターン抵抗(Rp)は、配線パターンの長さ・幅・厚みにより変化するため、オフセット分(Rp×ID)にはバラツキが発生する。このため、配線パターン抵抗Rpにより発生する電圧降下のオフセット分(Rp×ID)をキャンセルし、FETQoのドレイン・ソース間電圧VDS(=オン抵抗Ron×ID)を抽出する必要がある。

【0027】

そこで、本実施形態の電流検出回路では、FETQoのドレイン端子Dと、回路グランドGとの間に、抵抗分圧回路(検出部抵抗Rdとオフセット抵抗Roとで構成される抵抗直列回路)を挿入し、配線パターンの抵抗成分である配線パターン抵抗(Rp)による電圧降下分を、抵抗分圧回路を構成するオフセット抵抗Roにより分圧してオフセット分をキャンセルする。

【0028】

このために、FETQoのオン抵抗Ronと、配線パターン抵抗Rpと、オフセット抵抗Roと、検出部抵抗Rdの関係を以下のように定める。

【0029】

Ron:Rp=Ro:Rd・・・・(2)

すなわち、ドレイン電流IDが流れ電圧降下を発生させる側(抵抗Ronと配線パターン抵抗Rp側)の上下の抵抗値の比(Ron/Rp)に対して、抵抗分圧回路側(抵抗Rdと抵抗Ro側)の上下の抵抗値の比(Rd/Ro)が逆比になるようにする。すなわち、以下の関係になるようにする。

【0030】

Ron/Rp=Ro/Rd

【0031】

次に、具体的な数値の例を挙げて説明する。図1(B)は、配線パターン抵抗Rpにより発生する電圧降下(オフセット)をキャンセルする具体例について説明するための図である。この図に示すように、モータ電流を100Aとし、FETQoのオン抵抗Ronを4mΩ(Ron=4mΩ)とし、配線パターン抵抗Rpを1mΩ(Rp=1mΩ)とし、検出部抵抗(第1の抵抗)Rdを10kΩ(R1d=10kΩ)とし、オフセット抵抗(第2の抵抗)Roを40kΩ(Ro=40kΩ)とする。

【0032】

この場合は、ドレイン・回路グランド間電圧VDGは、0.50V(=100A×5mΩ)となる。すなわち、FETQoのオン抵抗Ronによる電圧降下が「0.40V(=100A×4mΩ)」となり、配線パターン抵抗Rpによる電圧降下が「0.10V(=100A×1mΩ)」となり、ドレイン・回路グランド間電圧VDGは、0.50Vとなる。

一方、抵抗分圧回路の検出電圧(ノードN1)の電圧VRo(抵抗Roの両端の電圧)は、ドレイン・回路グランド間電圧VDG(=0.50V)が抵抗分圧され、以下の式のようになる。

【0033】

VRo=0・50V×40kΩ/(10kΩ+40kΩ)=0.40V

【0034】

したがって、抵抗分圧回路の検出電圧(ノードN1)の電圧VRo(抵抗Roの両端の電圧)は、FETQoのドレイン・ソース間電圧VDS「0.40V(=100A×4mΩ)」と等しくなる。

【0035】

このように、ドレイン電流IDが流れ電圧降下を発生させる側の上下の抵抗値の比(Ron/Rp)に対して、抵抗分圧回路側の上下の抵抗値の比(Rd/Ro)が逆比になるように設定する(Ron/Rp=Ro/Rd)。すなわち、オフセット抵抗Roと検出部抵抗Rdとの抵抗値の比(Ro/Rd)を、FETQoのオン抵抗Ronと配線パターン抵抗Rpとの抵抗値の比(Ron/Rp)に一致するように設定する。これにより、配線パターン抵抗Rpにより発生する電圧降下分(オフセット)をキャンセルして、FETQoのドレイン・ソース間電圧VDSを検出することができる。

【0036】

なお、FETQoのオン抵抗Ronと、配線パターン抵抗Rpに対して、オフセット抵抗Roと、検出部抵抗Rdとは、十分大きな値に設定する。これは、オフセット抵抗Roと、検出部抵抗Rdの値が小さい場合は、このオフセット抵抗Roと検出部抵抗Rdとを通して流れる電流(FETQo側から分流する電流)が増大し、FETQoに流れる電流の検出誤差が増大するためである。

【0037】

[第2の実施形態]

次に、本発明の第2の実施形態として、上述した第1の実施形態の電流検出回路を、インバータにより3相交流モータを回転制御するモータ制御装置に用いた例について説明する。

【0038】

(モータ制御装置の構成についての説明)

図2は、本発明の実施形態に係わるモータ制御装置の構成を示す図である。図2に示すモータ制御装置10は、例えば、バッテリ(図示せず)を直流電源とし、このバッテリの直流電圧を交流電圧に変換して3相交流モータ(3相ブラシレスモータや3相誘導モータ)10を駆動する制御装置である。

【0039】

図2において、3相交流モータ(単に「モータ」とも呼ぶ)10は、例えば、エンジン(内燃機関)のスタータモータとなるモータである。この3相交流モータ10が、例えば、3相ブラシレスモータである場合は、このモータ10は、U、V、Wの各相コイル(鉄心に巻かれているコイル)を有するステータと、永久磁石からなるロータとで構成され、ステータには3相(U、V、W)のコイルが周方向に順番に巻装される。

【0040】

また、このモータ制御装置11内には、Nch型のMOSFET(Metal-Oxide Semiconductor Field-Effect Transistor)であるFETQ1〜Q6で構成される3相ブリッジ回路12が設けられている。この3相ブリッジ回路12は、FETQ1〜Q6がプリント配線基板上に実装されて構成されており、この3相ブリッジ回路12において、上アーム側のFETQ1、Q2、Q3のそれぞれのドレイン端子は、このFETQ1、Q2、Q3に流れる電流の電流経路となるそれぞれの配線パターンを介して、プリント配線基板上に設けられた正側電極端子A(+)に共通に接続されている。そして、この正側電極端子A(+)は、図示しない直流電源(例えば、バッテリ)の正電極に接続されている。

【0041】

また、下アーム側のFETQ4,Q5,Q6のそれぞれのソース端子は、このFETQ4,Q5,Q6に流れる電流の電流経路となるそれぞれの配線パターン(配線パターン抵抗Rp1,Rp2,Rp3で示す経路)を介して、プリント配線基板上に設けられた負電極端子B(−)に共通に接続されている。そして、このプリント配線基板上の負電極端子B(−)は、図示しない直流電源(例えば、バッテリ)の負電極に接続されており、また、この負電極端子B(−)は、後述する電流検出回路14や、過電流検出回路15や、制御部20などを構成する回路の基準電位(グランド)となる回路グランドGに接続されている。

【0042】

そして、3相ブリッジ回路12において、FETQ4のソース端子と負電極端子B(−)との間に挿入された抵抗Rp1は、FETQ4のソース端子と負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp1)を示している。また、FETQ5のソースと負電極端子B(−)との間に挿入された抵抗Rp2は、FETQ5のソースと負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp2)を示している。また、FETQ6のソースと負電極端子B(−)との間に挿入された抵抗Rp3は、FETQ6のソースと負電極端子B(−)とを結ぶプリント配線基板上の配線パターンが有する抵抗成分(配線パターン抵抗Rp3)を示している。

【0043】

なお、この配線パターン抵抗Rp1,Rp2,Rp3の抵抗値は、プリント配線基板上に実装されるFETQ1〜Q6の配置状況に応じて変化する。すなわち、配線パターン抵抗Rp1,Rp2,Rp3の抵抗値は、配線パターンの長さ(配線長)、幅、および厚みにより変化する。図2に示す例では、例えば、Rp1<Rp2<Rp3とする。すなわち、FETQ4のソース端子と負電極端子B(−)とを結ぶ配線パターンが最も短く、FETQ5のソース端子と負電極端子B(−)とを結ぶ配線パターンが次に長く、FETQ6のソース端子と負電極端子B(−)とを結ぶ配線パターンが最も長いものとする。

【0044】

そして、上アーム側のFETQ1のソース端子と、下アーム側のFETQ4のドレイン端子とが接続され、このFETQ1とQ4の接続点が、出力配線Luを介して3相交流モータ10のU相コイル端子に接続されている。また、上アーム側のFETQ2のソース端子と、下アーム側のFETQ5のドレイン端子とが接続され、このFETQ2とQ5の接続点が、出力配線Lvを介して3相交流モータ10のV相コイル端子に接続されている。

【0045】

また、上アーム側のFETQ3のソース端子と、下アーム側のFETQ6のドレイン端子とが接続され、このFETQ3とQ6の接続点が、出力配線Lwを介して3相交流モータ10のW相コイル端子に接続されている。なお、FETQ1〜Q6のそれぞれには、フライホイールダイオードDxが、図に示すようにカソードが(+)電極方向に、アノードが(−)電極方向となるように並列に接続されている。

【0046】

また、モータ制御装置11は、上アーム側のスイッチング素子(FET)Q1、Q2、Q3および下アーム側のスイッチング素子(FET)Q4、Q5、Q6をオン/オフ駆動するゲート信号を生成するゲート駆動回路(ドライバー回路)13を有している。上記のFETQ1〜Q6は、ゲート駆動回路13から出力されるゲート駆動信号により駆動され、このゲート駆動信号は、制御部(CPU等で構成される制御部)20から出力されるFET駆動信号を基にして生成される。

【0047】

制御部20は、FET駆動信号生成部21と、通電制御部22と、同期信号生成部23と、過電流保護部(過電流保護回路)24と、を有して構成される。通電制御部22は、3相交流モータ10を駆動するための通電信号を生成するための処理部である。この通電制御部22では、例えば、3相交流モータ10が低速で回転する場合において、180度の全通電期間中、120度の期間だけコイルに通電するようにして3相交流モータ10を駆動制御する。また、例えば、3相交流モータ10の高速回転時において、180°通電により、3相交流モータ10を駆動制御する。

【0048】

FET駆動信号生成部21は、通電制御部22により生成された通電信号に基づき、FETの駆動信号を生成し、このFETの駆動信号をゲート駆動回路13に出力する。このゲート駆動回路13は、FETのゲート駆動信号を生成するためのドライバー回路であり、このゲート駆動回路13から出力されるゲート駆動信号により、上記のFETQ1〜Q6をオン/オフ駆動する。

【0049】

また、同期信号生成部23は、後述するスイッチSW1,SW2,SW3をオン/オフ駆動する同期信号を生成する。また、過電流保護部24は、後述するコンパレータCP1、CP2、CP3、およびコンパレータCP4から過電流検出信号が入力されると、FET駆動信号生成部21を介してゲート駆動回路13を制御し、このゲート駆動回路13からFETQ1〜Q6を一括オフするゲート駆動信号を出力させる。

【0050】

(電流検出回路14についての説明)

上記構成において、本実施形態のモータ制御装置11では、FETQ4,Q5,Q6のドレイン・ソース間電圧(より正確にはドレイン・回路グランド間電圧)を検出することにより、FETQ4,Q5,Q6に流れる電流を検出する。このため、モータ制御装置11は、電流検出回路14を備えている。また、電流検出回路14により検出された電流信号を、所定の電流設定基準電圧と比較する過電流検出回路15を備えている。

【0051】

上記電流検出回路14においては、FETQ6のドレイン端子と回路グランドGとの間に、検出部抵抗R1とオフセット抵抗Ro1とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ6のドレインに抵抗R1の一端を接続し、この抵抗R1の他端を抵抗Ro1の一端に接続し、抵抗Ro1の他端を回路グランドGに接続する。また、抵抗R1と抵抗Ro1の接続点(ノードN1)とグランドGとの間にスイッチSW1を接続する。

【0052】

また、FETQ5のドレイン端子とグランドGとの間に、検出部抵抗R2とオフセット抵抗Ro2とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ5のドレイン端子に抵抗R2の一端を接続し、この抵抗R2の他端を抵抗Ro2の一端に接続し、抵抗Ro2の他端をグランドGに接続する。また、抵抗R2と抵抗Ro2の接続点(ノードN2)とグランドGとの間にスイッチSW2を接続する。

【0053】

同様にして、FETQ4のドレイン端子と回路グランドGとの間に、検出部抵抗R3とオフセット抵抗Ro3とでなる抵抗直列回路(抵抗分圧回路)を挿入する。すなわち、FETQ4のドレイン端子に抵抗R3の一端を接続し、この抵抗R3の他端を抵抗Ro3の一端に接続し、抵抗Ro3の他端を回路グランドGに接続する。また、抵抗R3と抵抗Ro3の接続点(ノードN3)と回路グランドGとの間にスイッチSW3を接続する。

【0054】

上記構成において、スイッチSW1は、FETQ6がオフの場合はオンになり、FETQ6がオンになるタイミングでオフになる。すなわち、FETQ6がオンになり、モータ10のW相電流IwがFETQ6に流れる状態において、スイッチSW1をオフにする。これにより、FETQ6がオンになるタイミングで、FETQ6のドレインに発生する電圧(W相電流に比例する電圧)を抵抗R1とRo1とにより分圧し、ノードN1の電圧としてコンパレータCP1の一方の端子に入力することができる。

【0055】

また、スイッチSW2は、FETQ5がオフの場合はオンになり、FETQ5がオンになるタイミングでオフになる。すなわち、FETQ5がオンになり、モータ10のV相電流IvがFETQ5に流れる状態において、スイッチSW2をオフにする。これにより、FETQ5がオンになるタイミングで、FETQ5のドレインに発生する電圧(V相電流Ivに比例する電圧)を抵抗R2とRo2とにより分圧し、ノードN2の電圧としてコンパレータCP2の一方の端子に入力することができる。

【0056】

同様にして、スイッチSW3は、FETQ4がオフの場合はオンになり、FETQ4がオンになるタイミングでオフになる。すなわち、FETQ4がオンになり、モータ10のU相電流IuがFETQ4に流れる状態において、スイッチSW3をオフにする。これにより、FETQ4がオンになるタイミングで、FETQ4のドレインに発生する電圧(U相電流Iuに比例する電圧)を抵抗R3とRo3とにより分圧し、ノードN3の電圧としてコンパレータCP3の一方の端子に入力することができる。

【0057】

(配線パターン抵抗により発生するオフセットについての説明)

ところで、FETQ4,Q5,Q6は、同じ仕様(定格電流、耐圧、構造等が同じ仕様)のFET素子であり、そのオン抵抗Ronは同じ値(例えば、4mΩ)とみなすことができる。そして、そのドレイン・ソース間電圧VDSは、図6に示すように、流れるドレイン電流IDに比例する。このため、FETQ4,Q5,Q6に流れる電流を検出するには、それぞれのドレイン・ソース間電圧VDSを検出すればよいことになる。

【0058】

しかしながら、前述したように、FETQ4,Q5,Q6のそれぞれのソース端子と負電極端子B(−)との間には、配線パターン抵抗(Rp1,Rp2,Rp3)が介在する。従って、FETQ4,Q5,Q6に流れる電流を測定するために、それぞれのFETQ4,Q5,Q6のドレイン端子と回路グランドGとの間の電圧VDGを測定する場合は、配線パターン抵抗(Rp1,Rp2,Rp3)に起因するオフセット分が含まれることになる。

【0059】

例えば、FETQ6がオンの状態においてモータ電流Iwが流れると、FETQ6のドレイン端子と回路グランドGとの間に発生する電圧VDG6は、以下の式になる。

【0060】

VDG6=Iw×Ron+Iw×Rp3

【0061】

また、FETQ5がオンの状態においてモータ電流Ivが流れると、FETQ5のドレイン端子と回路グランドGとの間に発生する電圧VDG5は、以下の式になる。

【0062】

VDG5=Iv×Ron+Iv×Rp2

【0063】

また、FETQ4がオンの状態においてモータ電流Iuが流れると、FETQ4のドレイン端子と回路グランドGとの間に発生する電圧VDG4は、以下の式になる。

【0064】

VDG4=Iu×Ron+Iu×Rp1

【0065】

このように、FETQ4,Q5,Q6のドレイン・回路グランド間電圧は、ドレイン・ソース間電圧VDSに、配線パターン抵抗(Rp1,Rp2,Rp3)による電圧降下がオフセット分として加わることになる。このため、FETQ4,Q5,Q6のドレイン・ソース間電圧を求めるには、上記オフセット分をキャンセルする必要がある。

【0066】

そこで、本実施形態の電流検出回路14では、第1の実施形態で説明したように、配線パターンの抵抗(Rp1,Rp2,Rp3)による電圧降下分を、抵抗分圧回路を構成するオフセット抵抗(Ro1,Ro2,Ro3)により分圧してオフセットする。

【0067】

このために、FETQ4,Q5,Q6のオン抵抗Ronと、配線パターン抵抗(Rp1,Rp2,Rp3)と、オフセット抵抗(Ro1,Ro2,Ro3)と、検出部抵抗(R1,R2,R3)との関係を以下のように定める。

【0068】

すなわち、FETQ6については、FETQ6のオン抵抗Ronと、配線パターン抵抗Rp3と、FETQ6に対応する検出部抵抗R1と、オフセット抵抗Ro1とにおいて、

【0069】

FETQ6のオン抵抗Ron:配線パターン抵抗(Rp3)

=オフセット抵抗(Ro1):検出部抵抗(R1)

【0070】

となるように設定する。

【0071】

また、FETQ5については、FETQ5のオン抵抗Ronと、配線パターン抵抗Rp2と、FETQ5に対応する検出部抵抗R2と、オフセット抵抗Ro2とにおいて、

【0072】

FETQ5のオン抵抗Ron:配線パターン抵抗(Rp2)

=オフセット抵抗(Ro2):検出部抵抗(R2)

【0073】

となるように設定する。

【0074】

また、FETQ4については、FETQ4のオン抵抗Ronと、配線パターン抵抗Rp1と、FETQ4に対応する検出部抵抗R3と、オフセット抵抗Ro3とにおいて、

【0075】

FETQ4のオン抵抗Ron:配線パターン抵抗(Rp1)

=オフセット抵抗(Ro3):検出部抵抗(R3)

【0076】

となるように設定する。

【0077】

ただし、上記設定において、「オン抵抗Ron,パターン抵抗(Rp1,Rp2,Rp3)≪オフセット抵抗(Ro1,Ro2,R03),検出部抵抗(R1,R2,R3)」となるように設定する。すなわち、オフセット抵抗(Ro1,Ro2,R03)および検出部抵抗(R1,R2,R3)の抵抗値が、オン抵抗Ronおよびパターン抵抗(Rp1,Rp2,Rp3)の抵抗値よりも十分大きな値となるように設定する。

【0078】

次に、具体的な例について説明する。図3は、配線パターン抵抗Rp3により発生する電圧降下(オフセット)をキャンセルする具体例について説明するための図である。この図3に示すように、モータ電流(W相電流Iw)を100Aとし、FETQ4,Q5,Q6のオン抵抗Ronを4mΩ(Ron=4mΩ)とし、FETQ6の配線パターン抵抗Rp3を1mΩ(Rp3=1mΩ)とし、検出部抵抗R1を10kΩ(R1=10kΩ)とする。

【0079】

そして、オフセット抵抗Ro1なしとした場合(Ro1=∞)は、検出電圧(ノードN1の電圧)は、0.50V「=100A×5mΩ」となり、本来のドレイン・ソース間電圧VDS「0.40V(=100A×4mΩ)」に対して、検出誤差は+25%となる。

【0080】

一方、オフセット抵抗Ro1を40kΩ(Ro1=40kΩ)とした場合は、検出電圧(ノードN1の電圧)は、0.50V×40kΩ/50kΩ=0.40Vとなり、本来のドレイン・ソース間電圧VDS「0.400V(=100A×4mΩ)」に対して、検出誤差はほぼ0%となる。

【0081】

このように、ドレイン電流IDが流れ電圧降下を発生させる側の上下の抵抗の抵抗値の比(例えば、Ron/Rp3)に対して、抵抗分圧回路側の上下の抵抗の抵抗値の比(例えば、R1/Ro1)が逆比になるように設定する(Ron/Rp3=Ro1/R1)。すなわち、オフセット抵抗Ro1と検出部抵抗R1との抵抗値の比(Ro1/R1)を、FETQ6のオン抵抗Ronと配線パターン抵抗Rp3との抵抗値の比(Ron/Rp3)に一致するように設定する。これにより、例えば、配線パターン抵抗Rp3により発生する電圧降下分(オフセット)をキャンセルして、FETQ6のドレイン・ソース間電圧VDSを検出することができる。

【0082】

(過電流検出回路15の構成と過電流検出動作についての説明)

次に、過電流検出回路15の構成と動作について説明する。前述したように、電流検出回路14のノードN1は、コンパレータCP1の一方の入力端子(−)に接続され、また、コンパレータCP1の他方の入力端子(+)には、基準となる電流設定基準電圧VR1が入力される。このため、FETQ6の電流信号(ノードN1の電圧)が,電流設定基準電圧VR1より低い場合(過電流状態でない場合)は、コンパレータCP1の出力は、例えば、H状態となり、FETQ6の電流信号(ノードN1の電圧)が,電流設定基準電圧VR1よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0083】

また、電流検出回路14のノードN2は、コンパレータCP2の一方の入力端子(−)に接続され、コンパレータCP2の他方の入力端子(+)には、基準となる電流設定基準電圧VR2が入力される。このため、FETQ5の電流信号(ノードN2の電圧)が、電流設定基準電圧VR2より低い場合(過電流状態でない場合)は、コンパレータCP2の出力は、例えば、H状態となり、FETQ6の電流信号(ノードN2の電圧)が、電流設定基準電圧VR2よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0084】

同様にして、ノードN3は、コンパレータCP3の一方の入力端子(−)に接続され、コンパレータCP3の他方の入力端子(+)には、基準となる電流設定基準電圧VR3が入力される。このため、FETQ4の電流信号(ノードN3の電圧)が、電流設定基準電圧VR3より低い場合(過電流状態でない場合)は、コンパレータCP3の出力は、例えば、H状態となり、FETQ4の電流信号(ノードN3の電圧)が、電流設定基準電圧VR3よりも高くなる場合(過電流状態の場合)は、例えば、L状態になる。

【0085】

また、電流検出回路14のノードN1は、アンプ(増幅器)AM11の一方の入力端子(+)に接続され、アンプAM11の他方の入力端子(−)には、アンプAM11の出力端子が接続される。これにより、アンプAM11はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN1から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0086】

また、電流検出回路14のノードN2は、アンプ(増幅器)AM12の一方の入力端子(+)に接続され、アンプAM12の他方の入力端子(−)には、アンプAM12の出力端子が接続される。これにより、アンプAM12はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN2から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0087】

同様にして、電流検出回路14のノードN3は、アンプ(増幅器)AM13の一方の入力端子(+)に接続され、アンプAM13の他方の入力端子(−)には、アンプAM13の出力端子が接続される。これにより、アンプAM13はボルテージホロワ回路を構成する。このボルテージホロワ回路は、高入力インピーダンスかつ低出力ンピーダンスのバッファ回路として機能し、ノードN3から入力される電圧信号をバッファしてそのまま出力端子に出力する。

【0088】

そして、アンプAM11の出力端子は抵抗R11を介してノードN4に接続され、アンプAM12の出力端子は抵抗R12を介してノードN4に接続され、アンプAM13の出力端子は抵抗R13を介してノードN4に接続される。これにより、アンプAM11と、アンプAM12と、アンプAM13の出力信号は、ノードN4においてワイヤードオアされる。このため、アンプAM11の出力信号と、アンプAM12の出力信号と、アンプAM13の出力信号のうちで最も信号レベルの高い信号(最も電圧レベルの高い信号)が

選択されてノードN4に現れる。

【0089】

このノードN4は、コンパレータCP4の一方の入力端子(−)に接続され、コンパレータCP4の他方の入力端子(+)には、基準となる電流設定基準電圧VR4が入力されている。このため、ノードN4の電圧が、電流設定基準電圧VR4より低い場合(過電流状態でない場合)は、コンパレータCP4の出力が、例えば、H状態となる。また、ノードN4の電圧が、電流設定基準電圧VR4よりも高くなる場合(過電流状態の場合)は、コンパレータCP4の出力が、例えば、L状態になる。

【0090】

従って、このアンプAM11,AM12,AM13とコンパレータCP4で構成される回路の系統では、ノードN1、ノードN2、ノードN3のいずれかの電圧が電流設定基準電圧VR4よりも高くなると(FETQ4,Q5,Q6のいずれかが過電流状態になると)、コンパレータCP4の出力が、例えば、L状態となる。

【0091】

このように、コンパレータCP1,CP2,CP3は、コンパレータCP1がFETQ6の過電流状態を検出し、コンパレータCP2がFETQ5の過電流状態を検出し、コンパレータCP3がFETQ4の過電流状態を検出するなど、個々のFETQ4,Q5,Q6の過電流状態を検出する。これに対して、アンプAM11,AM12,AM13とコンパレータCP4で構成される回路の系統では、FETQ4,Q5,Q6の過電流状態を一括して検出するものである。すなわち、アンプAMAM11,AM12,AM13とコンパレータCP4で構成される回路の系統は、コンパレータCP1,CP2,CP3を用いた過電流検出系統に対して、これを補完する予備の過電流検出系統として機能するものである。

【0092】

そして、コンパレータCP1,CP2,CP3、およびCP4の出力端子は信号線OCLに共通に接続されてワーヤードOR(オア)回路を構成している。このため、コンパレータCP1,CP2,CP3、およびCP4のいずれかの出力が、例えば、L状態になると、信号線OCLがL状態となり、このL状態の信号が過電流検出信号として制御部20に出力される。制御部20内の過電流保護部(過電流保護回路)24は、コンパレータCP1、CP2、CP3、およびコンパレータCP4から過電流検出信号(L状態の信号)が入力されると、FET駆動信号生成部21を介してゲート駆動回路13を制御し、このゲート駆動回路13からFETQ1〜Q6を一括オフするゲート駆動信号を出力させる。これにより、下アーム側のFETQ4,Q5,Q6のいずれかに過電流が流れる場合に、FETQ1〜Q6を一括オフし、FETQ1〜Q6を保護することができる。

【0093】

また、図4は、FETに流れる電流(ドレイン・ソース間電圧VDS)の検出タイミングを示す図である。この図4では、横方向に時間tの経過を示し、縦方向に、FETQnのドレイン・ソース間電圧VDSと、スイッチSWnのオン/オフ状態と、コンパレータCPnの入力電圧と、を並べて示したものである。

なお、この図4において、時刻t1は、FETQnがターンオンを開始する時刻を示し、時刻t1〜時刻t2までの期間ΔT1は、FETQnのタンーオン時間に応じて設けられる不感帯(電流検出を行わない期間)であり、時刻t3は、FETQnがターンオフを開始する時刻を示し、時刻t4はFETQnがターンオフを完了した時刻を示している。また、時刻t3から時刻t4までの期間ΔT2も、前述のΔT1と同様に、電流検出を行わない不感帯の期間である。

【0094】

図4に示すように、時刻t1以前のFETQn(例えば、FETQ6)がオフ(OFF)の状態においては、スイッチSWn(例えば、スイッチSW1)をオン(ON)状態にする。これにより、時刻t1以前には、コンパレータCpn(例えば、コンパレータCp1)に、FETQnの電流検出信号(例えば、ノードN1の電圧)が入力されないようにする。すなわち、コンパレータCpnの入力電圧を閾値(過電流設定基準電圧)以下にすることにより、コンパレータCpnにおいて過電流検出を行わないようにする。

【0095】

そして、時刻t1において、下アーム側のFETQn(例えば、W相のFETQ6)がターンオンを開始する。この時刻t1においてFETQnがターンオンを開始した後の時刻t2までの間は、スイッチSWn(例えば、スイッチSW1)のオン状態をそのまま保持し、時刻t2において、スイッチSWnをオフにする。

このようにスイッチSWnをオフにする際には、時刻t1よりΔT1だけ遅らせたタイミングの時刻t2で、スイッチSWnをオフにする。このように不感帯の期間ΔT1を設けることにより、FETQnがオンした後、FETQnに流れる電流が0から定常電流値まで立ち上がる過渡的な状態おいて発生する電流(例えば、過渡状態で発生する尖塔的なピーク電流等)を過電流として誤検出することを回避する。

【0096】

そして、時刻t2において、このスイッチSWnがオフになることにより、FETQnの電流検出信号(例えば、ノードN1の電圧)が、コンパレータCpn(例えば、コンパレータCP1)に入力され、FETQnに流れる電流の検出(過電流検出)が可能になる。これにより、FETQnに流れる電流が安定した時点で、コンパレータCpnは、FETQnに流れる電流(過電流)を検出することができる。

【0097】

そして、時刻t2において電流検出を開始した後、FETQnがターンオフを開始するタイミング(または、このターンオフを開始する直前のタイミング)である時刻t3(ターンオフ時刻t4よりも期間ΔT2だけ前の時刻t3)において、スイッチSWnをオンにする。このスイッチSWnがオンになることにより、時刻t3以降、コンパレータCpnに、FETQnの電流検出信号が入力されないようにする。すなわち、コンパレータCpnの入力電圧を閾値(過電流設定基準電圧)以下にし、コンパレータCpnにおいて過電流検出を行わないようにする。

このように期間ΔT2を設けることにより、FETQnがターンオフを開始した後、FETQnに流れる電流が定常電流から0に立ちさがるまでの過渡的な状態において流れる電流(例えば、過渡状態で発生する尖塔的なピーク電流等)を過電流として誤検出することを回避する。

【0098】

この図4のタイミングチャートに示すように、FETQnのオン期間中(時刻t1〜t4)において、不感帯(ΔT1およびΔT2)を設けて電流を検出することにより、FETQnに流れる電流が安定した時点で、このFETQnに流れる電流(過電流)を検出することができる。

【0099】

以上、本発明の実施形態について説明したが、ここで、本発明と上記実施形態における対応関係について補足して説明する。

すなわち、上記実施形態において、本発明における電流検出回路は、図1に示す電流検出回路1、および図2に示す電流検出回路14が対応し、本発明におけるモータ制御装置は、図2に示すモータ制御装置11が対応する。また、本発明における制御回路は、図2に示す制御部20、電流検出回路14、過電流検出回路15等が対応する。また、本発明における3相ブリッジ回路は、3相ブリッジ回路12が対応し、本発明におけるスイッチ素子は、図1に示すFET(Qo)および図2に示すFET(Q1〜Q6)が対応する。また、本発明におけるスイッチ素子のオン抵抗は、オン抵抗Ronが対応し、本発明における配線パターン抵抗は、図1に示す配線パターン抵抗Rpおよび図2に示す配線パターン抵抗(Rp1,Rp2,Rp3)が対応し、本発明における第1の抵抗は、図1に示す検出部抵抗Rdおよび図2に示す検出部抵抗(R1,R2,R3)が対応する。また、本発明における第2の抵抗は、図1に示すオフセット抵抗Roおよび図2に示すオフセット抵抗(Ro1,Ro2,Ro3)が対応する。

【0100】

また、本発明における過電流検出回路は、過電流検出回路15が対応し、本発明における過電流保護部は、制御部20内の過電流保護部24が対応する。また、本発明におけるスイッチは、スイッチSW1,SW2,SW3が対応する。また、本発明におけるスイッチ素子の一方の入出力端子は、図1に示すFET(Qo)のソース端子、または図2に示すFET(Q4,Q5,Q6)のソース端子が対応する。また、本発明におけるスイッチ素子の他方の入出力端子は、図1に示すFET(Qo)のドレイン端子、または図2に示すFET(Q4,Q5,Q6)のドレイン端子が対応する。

【0101】

(1)そして、上記実施形態において、電流検出回路1は、図1に示すように、プリント配線基板上に実装されるFET(Qo)のソース端子Sが、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子B(−)に接続され、該負電極端子B(−)はFET(Qo)に電流を供給する直流電源の負極側に接続されるとともに、FET(Qo)を制御する制御回路の回路グランドGに接続される回路において、FET(Qo)の導通時における電圧降下を基に、該FET(Qo)に流れる電流を検出する電流検出回路は、FET(Qo)のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗Rdと第2の抵抗Roとからなる抵抗直列回路を備え、上記抵抗直列回路においては、第1の抵抗Rdの一端がFET(Qo)のドレイン端子Dに接続され、他端が第2の抵抗Roの一端に接続され、第2の抵抗Roの他端が回路グランドGに接続され、第2の抵抗Roと第1の抵抗Rdとの抵抗値の比(第2の抵抗/第1の抵抗)が、FETの導通時のオン抵抗Ronと配線パターン抵抗Rpとの抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)の電圧であって回路グランドGに対する電圧VRoをFET(Qo)に流れる電流の検出信号として出力する。

【0102】

このような構成1の電流検出回路では、図1に示すように、FET(Qo)のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗Rdと第2の抵抗Roとで構成される抵抗直列回路を備える。そして、第2の抵抗Roと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターン抵抗Rpの抵抗値の比(Ron/Rp)に一致するように設定される。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

【0103】

これにより、プリント配線基板上に搭載されるFET(Qo)に流れる電流を、FET(Qo)のオン時のドレイン端子Dと回路グランドGとの間の電圧降下VDGを基に検出する際に、FET(Qo)の電流経路を形成する配線パターンの配線パターン抵抗Rpにより発生するオフセット分を容易にキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出することができる。このため、配線パターン抵抗Rpの影響をキャンセルして、FET(Qo)に流れる電流を検出することができる。

【0104】

(2)また、上記実施形態において、電流検出回路1は、FET(Qo)のオン抵抗Ronと配線パターン抵抗Rpの抵抗値に比べて、第1の抵抗Rdと第2の抵抗Roの抵抗値が、FET(Qo)に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される。

これにより、フセット抵抗Roと検出部抵抗Rdとを通して流れる電流を少なくすることができ、FET(Qo)に流れる電流の検出誤差を少なくすることができる。

【0105】

(3)また、上記実施形態において、モータ制御装置11は、図2に示すように、プリント配線基板上に実装されるFETの3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置11であって、直流電源から各FETQ1〜Q6に流れる電流の電流経路がプリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各FETQ4,Q5,Q6と直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、下アーム側の対応するFETQ4,Q5,Q6のソース端子Sに接続され、他端が、プリント配線基板上に設けられた負電極端子B(−)に接続され、該負電極端子B(−)は直流電源の負極側に接続されるとともに制御回路の回路グランドGに接続されて構成されるモータ制御装置において、下アーム側のFETQ4,Q5,Q6の導通時における電圧降下を基に、該FETに流れる電流を検出する電流検出回路14は、下アーム側の各FETQ4,Q5,Q6に対応して、FETQ4,Q5,Q6のドレイン端子Dと回路グランドGとの間に接続される第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)とからなるそれぞれの抵抗直列回路を備え、上記それぞれの抵抗直列回路においては、第1の抵抗(R1,R2,R3)の一端が対応するFETのドレイン端子に接続され、他端が第2の抵抗(Ro1,Ro2,Ro3)の一端に接続され、第2の抵抗(Ro1,Ro2,Ro3)の他端が回路グランドGに接続され、第2の抵抗(Ro1,Ro2,Ro3)と第1の抵抗(R1,R2,R3)との抵抗値の比(第2の抵抗/第1の抵抗)が、対応するFETの導通時のオン抵抗(Ron)と配線パターン抵抗(Rp1,Rp2,Rp3)との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)との接続点の電圧であって回路グランドGに対する電圧を各FET(Q4,Q5,Q6)に流れる電流の検出信号として出力する。

【0106】

このような構成のモータ制御装置11では、図2に示すように、下アーム側のFET(Q4,Q5,Q6)の導通時における電圧降下を基に、該下アーム側のFET(Q4,Q5,Q6)に流れる電流を検出する電流検出回路14を備える。そして、電流検出回路14は、下アーム側の各FET(Q4,Q5,Q6)に対応して、それぞれが第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)とからなる抵抗直列回路(抵抗分圧回路)を備える。この抵抗直列回路(抵抗分圧回路)においては、第1の抵抗(R1,R2,R3)の一端が対応するFET(Q4,Q5,Q6)のドレイン端子Dに接続され、他端が第2の抵抗(Ro1,Ro2,Ro3)の一端に接続され、第2の抵抗(Ro1,Ro2,Ro3)の他端が回路グランドGに接続される。そして、第2の抵抗(Ro1,Ro2,Ro3)と第1の抵抗(R1,R2,R3)との抵抗値の比(例えば、第2の抵抗Ro1/第1の抵抗R1)が、対応するFET(Q4,Q5,Q6)の導通時のオン抵抗Ronと配線パターン抵抗(Rp1,Rp2,Rp3)との抵抗値の比(例えば、オン抵抗Ron/配線パターン抵抗Rp3)に一致するように設定され、第1の抵抗(R1,R2,R3)と第2の抵抗(Ro1,Ro2,Ro3)との接続点(ノードN1,N2,N3)の電圧であって回路グランドGに対する電圧をFET(Q4,Q5,Q6)に流れる電流の検出信号として出力する。

【0107】

これにより、モータ制御装置11では、プリント配線基板上に搭載されるFET(Q4,Q5,Q6)に流れる電流を、FET(Q4,Q5,Q6)のオン時のドレイン端子Dと回路グランドGとの間の電圧降下VDGを基に検出する際に、FET(Q4,Q5,Q6)の電流経路を形成する配線パターンの配線パターン抵抗(Rp1,Rp2,Rp3)により発生するオフセット分を容易にキャンセルして、FET(Q4,Q5,Q6)のドレイン・ソース間電圧VDSを検出することができる。このため、配線パターン抵抗(Rp1,Rp2,Rp3)の影響をキャンセルして、FET(Q4,Q5,Q6)に流れる電流を検出することができる。

【0108】

(4)また、上記実施形態において、モータ制御装置11は、FET(Q4,Q5,Q6)のオン抵抗(Ron)および前記配線パターン抵抗(Rp1,Rp2,Rp3)の抵抗値に比べて、第1の抵抗(R1,R2,R3)および第2の抵抗(Ro1,Ro2,Ro3)の抵抗値が、FET(Q4,Q5,Q6)に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される。

これにより、オフセット抵抗(Ro1,Ro2,Ro3)と検出部抵抗(R1,R2,R3)を通して流れる電流を少なくし、FET(Q4,Q5,Q6)に流れる電流の検出誤差を少なくすることができる。

【0109】

(5)また、上記実施形態において、モータ制御装置11は、下アーム側の各FET(Q4,Q5,Q6に対応する抵抗直列回路内の第2の抵抗(Ro1,Ro2,Ro3)のそれぞれに並列に接続されるスイッチ(スイッチSW1,SW2,SW3)であって、下アーム側の対応するFET(Q4,Q5,Q6)の導通タイミングに合わせてオフし、対応するFET(Q4,Q5,Q6)の電流検出信号を当該FETの導通時にのみ出力するスイッチ(スイッチSW1,SW2,SW3)を備える。

【0110】

これにより、FET(Q4,Q5,Q6)の電流検出信号を当該FETの導通時にのみ出力することができる。このため、FETがオフしている場合には、電流検出信号の出力を停止するので、他の相の電流検出信号にノイズ等の影響を与えることがなくなる。また、図4に示す特許文献1に記載のモータ制御装置では、アナログスイッチAS1,AS2,AS3が、信号の検出経路(FETのドレイン端子とアンプAMの入力端子を繋ぐ信号線の経路)に挿入されているため、このアナログスイッチAS1,AS2,AS3の内部インピーダンスにより電流検出信号が影響を受ける可能性があるが、図2に示す本実施形態のモータ制御装置11では、スイッチ(SW1,SW2,SW3)が信号の検出経路(FETのドレイン端子とコンパレータの入力端子を繋ぐ信号線の経路)に挿入されないため、信号の検出の際に、スイッチ(SW1,SW2,SW3)の内部インピーダンスによる影響を受けることがない。

【0111】

(6)また、上記実施形態において、モータ制御装置11は、下アーム側のFET(Q4,Q5,Q6)のオン時の電流検出信号が所定の過電流設定基準電圧(VR1,VR2,VR3,VR4)を超えたときに過電流検出信号を出力する過電流検出回路15と、過電流検出回路15から過電流検出信号が出力された場合に、3相ブリッジ回路12の各FET(Q1〜Q6)のすべてをオフする過電流保護部24と、を備える。

これにより、下アーム側のFET(Q4,Q5,Q6)のいずれかにおいて過電流状態が検出された場合に、3相ブリッジ回路12の各FET(Q4,Q5,Q6)のすべてを直ちに一括オフすることができる。このため、過電流によりFET(Q4,Q5,Q6)が損傷することを回避することができる。

【0112】

以上、本発明の実施の形態について説明したが、本発明の電流検出回路。およびモータ制御装置は、上述の図示例にのみ限定されるものではなく、本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。また、本発明のスイッチ素子は、上述の図示例ではFETで示してあるが、スイッチ素子であればこれに限定されない。また、本発明のスイッチは、スイッチ素子であっても、アナログスイッチであっても良く、これに限定されない。

【符号の説明】

【0113】

1、14 電流検出回路、

10 3相交流モータ

11 モータ制御装置

12 3相ブリッジ回路

13 ゲート駆動回路

14 電流検出回路

15 過電流検出回路

20 制御部

21 FET信号生成部

22 通電制御部

23 同期信号生成部

24 過電流保護部

Q1,Q2,Q3 上アーム側のFET

Q4,Q5,Q6 下アーム側のFET

CP1,CP2,CP3,CP4 コンパレータ

Ron FETのオン抵抗

Rp1,Rp2,Rp3 配線パターン抵抗

Rd,R1,R2,R3 検出部抵抗(第1の抵抗)

Ro,Ro1,Ro2,Ro3 オフセット抵抗(第2の抵抗)

SW1,SW2,SW3 スイッチ

AM11,AM12,AM13 アンプ(増幅器)

【特許請求の範囲】

【請求項1】

プリント配線基板上に実装されるスイッチ素子の一方の入出力端子が、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記スイッチ素子に電流を供給する直流電源の負極側に接続されるとともに、前記スイッチ素子を制御する制御回路の回路グランドに接続される回路において、

前記スイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなる抵抗直列回路を備え、

前記抵抗直列回路においては、

前記第1の抵抗の一端が前記スイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、

前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記スイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、

前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力する

ことを特徴とする電流検出回路。

【請求項2】

前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される

ことを特徴とする請求項1に記載の電流検出回路。

【請求項3】

プリント配線基板上に実装されるスイッチ素子の3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置であって、前記直流電源から各スイッチ素子に流れる電流の電流経路が前記プリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各スイッチ素子と前記直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、前記下アーム側の対応するスイッチ素子の一方の入出力端子に接続され、他端が、前記プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記直流電源の負極側に接続されるとともに前記制御回路の回路グランドに接続されて構成されるモータ制御装置において、

前記下アーム側のスイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記下アーム側の各スイッチ素子に対応して、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなるそれぞれの抵抗直列回路を備え、

前記それぞれの抵抗直列回路においては、

前記第1の抵抗の一端が対応するスイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、

前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記対応するスイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、

前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力する

ことを特徴とするモータ制御装置。

【請求項4】

前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される

ことを特徴とする請求項3に記載のモータ制御装置。

【請求項5】

前記下アーム側の各スイッチ素子に対応する第2の抵抗のそれぞれに並列に接続されるスイッチであって、

前記下アーム側の対応するスイッチ素子の導通タイミングに合わせてオフし、前記対応するスイッチ素子の電流検出信号を当該スイッチ素子の導通時にのみ出力するスイッチを備える

ことを特徴とする請求項3または請求項4に記載のモータ制御装置。

【請求項6】

前記下アーム側のスイッチ素子のオン時の電流検出信号が所定の過電流設定基準電圧を超えたときに過電流検出信号を出力する過電流検出回路と、

前記過電流検出回路から過電流検出信号が出力された場合に、前記3相ブリッジ回路の各スイッチ素子のすべてをオフする過電流保護部と、

を備えることを特徴とする請求項3から5のいずれか1項に記載のモータ制御装置。

【請求項1】

プリント配線基板上に実装されるスイッチ素子の一方の入出力端子が、このプリント配線基板上の配線パターンを介して当該プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記スイッチ素子に電流を供給する直流電源の負極側に接続されるとともに、前記スイッチ素子を制御する制御回路の回路グランドに接続される回路において、

前記スイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなる抵抗直列回路を備え、

前記抵抗直列回路においては、

前記第1の抵抗の一端が前記スイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、

前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記スイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、

前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力する

ことを特徴とする電流検出回路。

【請求項2】

前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される

ことを特徴とする請求項1に記載の電流検出回路。

【請求項3】

プリント配線基板上に実装されるスイッチ素子の3相ブリッジ回路とその制御回路からなるインバータを用いて、直流電源から入力される直流電圧から3相交流電圧を生成して3相交流モータの回転を制御するモータ制御装置であって、前記直流電源から各スイッチ素子に流れる電流の電流経路が前記プリント配線基板上の配線パターンにより形成され、かつ、下アーム側の各スイッチ素子と前記直流電源の負極側との間の電流経路となるそれぞれの配線パターンは、一端が、前記下アーム側の対応するスイッチ素子の一方の入出力端子に接続され、他端が、前記プリント配線基板上に設けられた負電極端子に接続され、該負電極端子は前記直流電源の負極側に接続されるとともに前記制御回路の回路グランドに接続されて構成されるモータ制御装置において、

前記下アーム側のスイッチ素子の導通時における電圧降下を基に、該スイッチ素子に流れる電流を検出する電流検出回路は、前記下アーム側の各スイッチ素子に対応して、前記スイッチ素子の他方の入出力端子と前記回路グランドとの間に接続される第1の抵抗と第2の抵抗とからなるそれぞれの抵抗直列回路を備え、

前記それぞれの抵抗直列回路においては、

前記第1の抵抗の一端が対応するスイッチ素子の他方の入出力端子に接続され、他端が前記第2の抵抗の一端に接続され、前記第2の抵抗の他端が前記回路グランドに接続され、

前記第2の抵抗と第1の抵抗との抵抗値の比(第2の抵抗/第1の抵抗)が、前記対応するスイッチ素子の導通時のオン抵抗と配線パターン抵抗との抵抗値の比(オン抵抗/配線パターン抵抗)に一致するように設定され、

前記第1の抵抗と前記第2の抵抗との接続点の電圧であって前記回路グランドに対する電圧を前記スイッチ素子に流れる電流の検出信号として出力する

ことを特徴とするモータ制御装置。

【請求項4】

前記スイッチ素子のオン抵抗および前記配線パターン抵抗の抵抗値に比べて、前記第1の抵抗および第2の抵抗の抵抗値が、前記スイッチ素子に流れる電流を検出する際に必要される許容誤差を満たすように、十分大きな値に設定される

ことを特徴とする請求項3に記載のモータ制御装置。

【請求項5】

前記下アーム側の各スイッチ素子に対応する第2の抵抗のそれぞれに並列に接続されるスイッチであって、

前記下アーム側の対応するスイッチ素子の導通タイミングに合わせてオフし、前記対応するスイッチ素子の電流検出信号を当該スイッチ素子の導通時にのみ出力するスイッチを備える

ことを特徴とする請求項3または請求項4に記載のモータ制御装置。

【請求項6】

前記下アーム側のスイッチ素子のオン時の電流検出信号が所定の過電流設定基準電圧を超えたときに過電流検出信号を出力する過電流検出回路と、

前記過電流検出回路から過電流検出信号が出力された場合に、前記3相ブリッジ回路の各スイッチ素子のすべてをオフする過電流保護部と、

を備えることを特徴とする請求項3から5のいずれか1項に記載のモータ制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−70574(P2013−70574A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−208983(P2011−208983)

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月26日(2011.9.26)

【出願人】(000002037)新電元工業株式会社 (776)

【Fターム(参考)】

[ Back to top ]