電流狭窄型半導体発光素子

【課題】高発光効率を有する電流狭窄型半導体発光素子を提供する。

【解決手段】第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする。

【解決手段】第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体発光素子に関するものであって、特に、電流狭窄構造を有する半導体発光素子に関する。

【背景技術】

【0002】

一般に、スポットキュアリング、殺菌、分析分光器やセンサー等の用途に用いられる半導体発光素子に要求される性能として、高い発光効率を有することが挙げられる。このような要求を満足させるため、従来、半導体発光素子内部に電流阻止層または電流狭窄層を設け、発光層に効果的に電流を注入させることにより、発光効率を向上させる技術が知られている。

【0003】

半導体発光素子に電流狭窄層または電流狭窄層を設ける技術を開示した例としては、例えば、特許文献1〜3が挙げられる。

【0004】

特許文献1および2には、半導体層内に島状の電流阻止層または電流狭窄層を設けた、いわゆる埋め込み型の電流狭窄型半導体発光素子が開示されている。しかしながら、前記電流阻止層または電流狭窄層を半導体層内に埋設する場合、エッチング等の付加的な作業工程が必要となるため、エピタキシャル成長を複数回で行わなければならず、作業性の悪化やコスト増加といった問題があり、さらに、前記エッチング工程後に成長させる半導体層に、前記エッチングに起因する欠陥が生じ、結晶品質が低下することにより、発光効率が低下してしまうという問題もある。

【0005】

一方、特許文献3には、半導体層上に電流狭窄層を形成し、この電流狭窄層および電流狭窄層の開口部分上に電極を形成した電流狭窄型半導体発光素子が開示されている。この技術によれば、上述したような作業性の悪化およびコスト増加、並びに結晶品質の低下の問題は改善されているものの、前記電流狭窄層の開口部分上に電極を設けているため、発光層で発生した光が前記電極に吸収され、発光効率が低下してしまうという問題がある。

【0006】

上記問題に加え、特許文献1〜3に記載された半導体発光素子においては、発光層で発生した光は、素子表面だけではなく裏面にも等方的に向かうこととなり、裏面に向かった光は基板によって吸収され、または基板を透過してしまい、素子表面から十分な光を取り出すことができず、発光効率が低下してしまうという問題がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2003−243703号公報

【特許文献2】特開2003−86841号公報

【特許文献3】特開平11−150296号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、高発光効率を有する電流狭窄型半導体発光素子を提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明の要旨構成は以下の通りである。

(1) 第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、

前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする電流狭窄型半導体発光素子。

【0010】

(2)前記第1導電型積層体は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体であり、前記発光層は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体である上記(1)に記載の電流狭窄型半導体発光素子。

【0011】

(3)前記電流狭窄層は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなる上記(1)または(2)に記載の電流狭窄型半導体発光素子。

【0012】

(4)前記n型積層体が、n−コンタクト層および該n−コンタクト層上に設けられたn−クラッド層を有する上記(2)または(3)に記載の電流狭窄型半導体発光素子。

【0013】

(5)前記p型積層体が、p−電子ブロック層、該p−電子ブロック層上に設けられたp−クラッド層および該p−クラッド層上に設けられたp−コンタクト層を有する上記(2)、(3)または(4)に記載の電流狭窄型半導体発光素子。

【0014】

(6)前記発光層が、多重量子井戸層である上記(1)〜(5)のいずれか1に記載の電流狭窄型半導体発光素子。

【0015】

(7)前記第1導電型積層体は、Si材料からなる基板上に配設され、前記反射面は、前記基板の上面である上記(1)〜(6)のいずれか1に記載の電流狭窄型半導体発光素子。

【発明の効果】

【0016】

本発明の電流狭窄型半導体発光素子は、第2導電型積層体の上方でかつ第1電極の直下位置に所定形状の電流狭窄層を有し、かつ、第1導電型積層体の、発光波長が200〜350nmの発光層とは反対側に、200〜350nmの波長範囲に対し、高い反射率の反射面を具えることにより、発光効率を向上させることができる。

【図面の簡単な説明】

【0017】

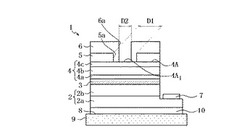

【図1】本発明に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図2】種々の材料における入射光波長と反射率との関係を示すグラフである。

【図3】本発明の第1実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図4】本発明の第2実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図5】本発明の第3実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図6】比較例1に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図7】比較例2に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図8】比較例3に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図9】比較例4に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【発明を実施するための形態】

【0018】

次に、本発明の半導導体発光素子の実施形態について図面を参照しながら説明する。図1は、この発明に従う半導体発光素子の断面構造を模式的に示したものである。

【0019】

図1に示す本発明に従う電流狭窄型半導体発光素子1は、第1導電型積層体2、発光層3、第2導電型積層体4、電流狭窄層5、第1開口6aを有する第1電極6、および、前記発光層3の、前記第2導電型積層体4とは反対側に配設される第2電極7を具え、前記電流狭窄層5は前記第2導電型積層体4を露出する第2開口5aを有し、前記第2開口5aは前記第1開口6aと中心を同じくしてなり、前記第2開口5aの面積(以下、「狭窄開口面積」という。)は前記第1開口6aの面積(以下、「発光開口面積」という。)よりも大きく、前記第1電極6の一部が前記第2導電型積層体4と接し、かつ前記第1開口6aから前記第2導電型積層体4の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具え、このような構成を採用することにより、発光効率を向上させることを可能にしたものである。ここで、前記第1開口6aおよび前記第2開口5aの形状は、いずれも円形、矩形等の対照形状であればよく、本発明の一実施形態において、前記狭窄開口面積および前記発光開口面積は、それぞれ半導体発光素子1の横断面における幅方向の長さである狭窄径D1、発光径D2に対応するものとして説明する。なお、図中のハッチングは、説明のため、便宜上施したものである。

【0020】

前記第1導電型積層体2は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体2であり、前記発光層3は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体4は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体4であるのが好ましい。また、前記電流狭窄層5は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなるのが好ましい。図1は、一例として、前記第1導電型積層体2がn型積層体2であり、前記第2導電型積層体4がp型積層体4である場合を示したものである。

【0021】

前記n型積層体2は、n−コンタクト層2aおよびこのn−コンタクト層上2aに設けられたn−クラッド層2bを有するのが好ましく、前記p型積層体4は、p−電子ブロック層4a、このp−電子ブロック層4a上に設けられたp−クラッド層4bおよびこのp−クラッド層4b上に設けられたp−コンタクト層4cを有するのが好ましい。また、前記発光層3は、多重量子井戸層3であるのが好ましい。

【0022】

前記n−コンタクト層2aおよび前記n−クラッド層2bは、好適にはそれぞれ1〜5μm、および200〜1000nmの厚さを有し、前記p−電子ブロック層4a、前記p−クラッド層4bおよび前記p−コンタクト層4cは、好適にはそれぞれ5〜50nm、200〜500μmおよび10〜50nmの厚さを有するのが好ましく、前記発光層3は、好適には20〜150nmの厚さを有するのが好ましい。また、前記電流狭窄層5は、好適には0.8〜1.5μmの厚さを有するのが好ましい。これらは、発光素子として良好に機能し、かつ、光の吸収、結晶歪みの増大、順方向電圧の上昇を十分に回避するのに好適な範囲である。

【0023】

本発明の電流狭窄型半導体発光素子1では、電流狭窄層5が前記第1電極6の直下位置に配設されているため、前記狭窄径D1と前記発光径D2とが一致する場合には、前記発光素子1には電流がほとんど流れない。このため、本発明では、前記狭窄径D1は、前記発光径D2よりも大きい必要がある。

【0024】

本発明の発光素子の場合、前記狭窄径D1が小さくなるほど、順方向電圧Vfが高くなる傾向にあり、また、前記発光径D2を前記狭窄径D1対比で小さくするほど、前記第1電極層6の電極面積は増加するので、順方向電圧Vfは低下するものの、前記発光径D2が小さくなるため、総発光出力P0は減少する傾向にある。

【0025】

このため、本発明では、高い総発光出力P0と低い順方向電圧Vfの双方をバランスよく満足させるには、前記狭窄径D1を、前記発光径D2との対比で適正に設定することが好ましい。

【0026】

前記反射面8の、ピーク波長が200〜350nmの範囲に対する反射率は、60%以上であるのが好ましい。製品として要求される発光効率を十分に実現させるためである。図2に、一例として、Si、GaAs、SiCおよびサファイアの、光の波長(nm)と反射率(%)との関係を示すグラフを示す。なお、図2に示す反射率は、所定波長の光を、入射角度5°でAl反射鏡に入射させたときの反射光を紫外可視分光光度計を用いて測定し、これらの値を100%として相対値を算出したものである。

【0027】

図2から、波長200〜350nmの光に対して、Siの反射率は60%以上、GaAsの反射率は45%以上であり、波長200〜265nmの光に対しては、Siの反射率は70%以上、GaAsの反射率は60%以上であることがわかる。したがって、前記反射面8を構成する好適な材料としては、SiまたはGaAsが好ましく、より好適には、Siとするのが好ましい。

【0028】

前記第1導電型積層体2は、Si材料からなる基板9上に配設され、前記反射面8は、前記基板9の上面であるのが好ましい。

【0029】

前記基板9と前記第1導電型積層体2との間にAlN材料からなるバッファ層10を具えてもよい。基板9との格子不整合に起因する転位を抑え、バッファ層10上に積層する結晶の転位密度を下げるためである。

また、図示しないが、バッファ層10に接してリフトオフのための分離層を設けても良い。また、後述するようにバッファ層10が絶縁のAlN材料の場合、狭窄層として使用することも出来る。

本実施例では、サファイアなどの仮の基板上にバッファ層10を介して素子を形成した後、貼り付けやリフトオフなどの手法によりSi材料からなる基板9上に移設したが、Si基板上に直接バッファ層10を成長させ、その上に素子形成する方が、工程が省略されてより好ましい。

【0030】

前記第2電極7は、前記Si材料からなる基板9の、前記発光層3とは反対側に配設されるのが好ましい。素子に流れる電流が均等になってジュール熱が減少し、また、発光部分が素子中心にくることにより、発光効率を向上させることができるためである。また、図1に示すように、前記第2電極7を、一部露出した前記第1導電型積層体2の上面に配設してもよい。

【0031】

次に、本発明の電流狭窄型半導体発光素子の製造方法の一例について、以下で説明する。

本発明の第1実施形態に従う電流狭窄型半導体発光素子21の製造方法は、図3(a)〜(e)に示すように、結晶成長基板31の上面の側に、MOCVD法により、電流狭窄層25、第2導電型積層体24、発光層23、第1導電型積層体22を順次エピタキシャル成長させて形成し、その後、前記第1導電型積層体22の、前記発光層23とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板29を接着した後、前記結晶成長基板31を除去する。また、前記電流狭窄層25に第2開口25aを形成し、この第2開口25aの面積よりも小さな面積の第1開口26aをもつ第1電極層26を、前記電流狭窄層25に隣接する第2導電型積層体24の表面24Aの一部24A1が露出するように形成する。その後、前記支持基板29の下面の側に、第2電極層27を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

【0032】

前記第1導電型積層体22は、p型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型積層体22であり、前記発光層3は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体24は、n型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型積層体24であるのが好ましい。また、前記電流狭窄層5は、絶縁体であるAlN材料からなるのが好ましい。

【0033】

前記p型積層体22は、p−クラッド層およびこのp−コンタクト層上に成長させたp−コンタクト層を有するのが好ましく、前記n型積層体24は、n−コンタクト層、このn−コンタクト層上に成長させたn−クラッド層を有するのが好ましい。また、前記発光層23は、多重量子井戸層23であるのが好ましい。また、図示しないが、p型積層体22と発光層23との間にp−電子ブロック層を有しても良い。

【0034】

前記p−コンタクト層および前記p−クラッド層は、好適にはそれぞれ1〜5μm、および200〜1000nmの厚さを有し、前記n−電子ブロック層、前記n−クラッド層および前記n−コンタクト層は、好適にはそれぞれ5〜50nm、200〜500μmおよび10〜50nmの厚さを有するのが好ましく、前記発光層23は、好適には20〜150nmの厚さを有するのが好ましい。また、前記電流狭窄層25は、好適には0.8〜1.5μmの厚さを有するのが好ましい。これらは、発光素子として良好に機能し、かつ、光の吸収、結晶歪みの増大、順方向電圧の上昇を十分に回避するのに好適な範囲である。

【0035】

本発明の第2実施形態に従う電流狭窄型半導体発光素子41の製造方法は、図4(a)〜(f)に示すように、結晶成長基板51の上面の側に、MOCVD法により、第1導電型積層体42、発光層43、第2導電型積層体44、電流狭窄層45を順次エピタキシャル成長させて形成し、その後、前記電流狭窄層45の、発光層43とは反対側に、中間基板52を接着して、前記結晶成長基板51を除去し、前記第1導電型積層体42の、前記発光層43とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板49を接着する。その後、前記中間基板52を除去し、前記電流狭窄層45に第2開口45aを形成し、この第2開口45aの面積よりも小さな面積の第1開口46aをもつ第1電極層46を、前記電流狭窄層45に隣接する第2導電型積層体44の表面44Aの一部44A1が露出するように形成する。その後、前記支持基板49の下面の側に、第2電極層47を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

また、前記基板51と前記第1導電型積層体42との間にAlN材料からなるバッファ層50を形成し、前記基板51の除去の際に同時に除去(分離)してもよい。

ここで、中間基板52は接着と除去が容易で、支持基板49の接着時に耐えられるものであり、除去の際に他の部位に影響が無いものであることが好ましい。例えばSiやGaAsなどの半導体基板や金属基板、樹脂などである。

【0036】

本発明の第3実施形態に従う電流狭窄型半導体発光素子61の製造方法は、図5(a)〜(g)に示すように、結晶成長基板71の上面の側に、MOCVD法により、第1導電型積層体62、発光層63、第2導電型積層体64、電流狭窄層65を順次エピタキシャル成長させて形成し、その後、前記電流狭窄層65の、前記発光層63とは反対側に、中間基板72を接着し、前記結晶成長基板71を除去して、前記第1導電型積層体62の前記発光層63とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板69を接着する。また、前記中間基板72を除去し、前記他の基板69を接着後、前記第1導電型積層体62の上面の一部を露出させる。また、前記電流狭窄層65に第2開口65aを形成し、この第2開口65aの面積よりも小さな面積の第1開口66aをもつ第1電極層66を、前記電流狭窄層65に隣接する第2導電型積層体64の表面64Aの一部64A1が露出するように形成し、また、前記露出させた前記第1導電型積層体66上に第2電極層67を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

また、前記基板71と前記第1導電型積層体62との間にAlN材料からなるバッファ層70を形成してもよい。

【0037】

上述したところは、この発明の実施形態の一例を示したにすぎず、請求の範囲において種々の変更を加えることができる。

【実施例】

【0038】

[実験例1]

(実施例1)

図3(a)に示すように、サファイア基板31の上面の側に、MOCVD法により、その後電流狭窄層となるAlNバッファ層25(厚さ:1000nm)、n型積層体である第1導電型積層体24(厚さ:2500nm)、発光層23(厚さ:90nm)、および、p型積層体である第2導電型積層体22(厚さ:240nm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体24は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層23は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体22は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0039】

次に図3(b)および図3(c)に示すように、前記第2導電型積層体22に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板29(厚さ:300μm)を接着した後、前記サファイア基板31をリフトオフにより除去した。

【0040】

次に、図3(d)に示すように、前記構造体の上下を反転させた後、ウェットエッチング法により、前記AlN電流狭窄層25に円形の第2開口25aを形成し、前記第2開口25aの径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口26aをもつ第1電極26(厚さ:200nm)を、前記電流狭窄層25に隣接する第2導電型積層体24の表面24Aの一部24A1が露出するように形成した。

また、前記Si基板29上に、第2電極27(厚さ:2μm)を形成することにより、本発明の第1実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0041】

(実施例2)

図4(a)に示すように、サファイア基板51の上面の側に、MOCVD法により、AlNバッファ層50(厚さ:1000nm)、n型積層体である第1導電型積層体42(厚さ:2500nm)、発光層43(厚さ:90nm)、および、p型積層体である第2導電型積層体44(厚さ:240nm)を順次形成した後、前記第2導電型積層体44とは逆導電型、この例ではn型の電流狭窄層45(厚さ:1μm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体42は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層43は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体44は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0042】

次に図4(b)および図4(c)に示すように、前記電流狭窄層45上に適当な中間基板52を接着した後、前記サファイア基板51および前記AlNバッファ層50をリフトオフにより除去した。その後、図4(d)および図4(e)に示すように、前記サファイア基板51および前記AlNバッファ層50の除去により露出した前記第1導電型積層体42上に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板49(厚さ:300μm)を接着した後、前記適当な中間基板52を除去した。

【0043】

次に、図4(f)に示すように、ウェットエッチング法により、前記電流狭窄層45に円形の第2開口45aを形成し、前記第2開口45aの径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口46aをもつ第1電極46(厚さ:2μm)を、前記電流狭窄層45に隣接する第2導電型積層体44の表面44Aの一部44A1が露出するように形成した。

また、前記Si基板49上に、第2電極47(厚さ:200m)を形成することにより、本発明の第2実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0044】

(実施例3)

図5(a)に示すように、サファイア基板71の上面の側に、MOCVD法により、AlNバッファ層70(厚さ:1μm)、n型積層体である第1導電型積層体62(厚さ:2500nm)、発光層63(厚さ:90nm)、および、p型積層体である第2導電型積層体64(厚さ:240nm)を順次形成した後、前記第2導電型積層体64とは逆導電型、この例ではn型のAl0.7Ga0.3Nからなる電流狭窄層65(厚さ:1μm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体62は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層2a(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層2b(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層63は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体64は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0045】

次に図5(b)および図5(c)に示すように、前記電流狭窄層65上に適当な中間基板72を接着した後、前記サファイア基板71をリフトオフにより除去した。その後、図5(d)および図5(e)に示すように、前記サファイア基板71の除去により露出した前記AlNバッファ層70上に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板69(厚さ:300μm)を接着した後、前記適当な中間基板72を除去した。

【0046】

次に、図5(f)に示すように、ドライエッチングにより前記第1導電型積層体62の一部を露出させた。また、図5(g)に示すように、ウェットエッチング法により、前記電流狭窄層65に円形の第2開口65aを形成し、前記第2開口の径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口66aをもつ第1電極66(厚さ:2μm)を、前記電流狭窄層65に隣接する第2導電型積層体64の表面64Aの一部64A1が露出するように形成した。

また、前記露出した第1導電型積層体62上に、第2電極67(厚さ:200m)を形成することにより、本発明の第3実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0047】

(比較例1)

図6に示すように、p−クラッド層上に電流狭窄層105を形成し、エッチング工程を行った後、再度p−コンタクト層を結晶成長させたこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0048】

(比較例2)

図7に示すように、ウェットエッチング法により、電流狭窄層205に第2開口を形成し、この第2開口にかぶさるように第1電極206を形成したこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0049】

(比較例3)

図8に示すように、Si基板を接着せずに、サファイア基板309のままであること以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0050】

(比較例4)

図9に示すように、電流狭窄層を形成しないこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0051】

(性能評価)

実施例1〜3および比較例1〜4について、20mAの電流を流したときの発光出力P0(μW)の測定結果を表1に示す。

【0052】

【表1】

【0053】

表1の結果より、実施例1〜3の電流狭窄型半導体発光素子は、電流狭窄層を設けない比較例4、および、反射面を有さない比較例3よりも総発光出力が大きいことがわかる。また、電流狭窄層および反射面を有する比較例1および比較例2と比較しても、電流狭窄層を適切に配置した実施例1〜3は、総発光出力が格段に向上していることがわかる。

【0054】

[実験例2]

上記実施例3の電流狭窄型半導体発光素子について、狭窄径D1および発光径D2を変化させたサンプルNo.1〜4を作製し、これらサンプルNo.1〜4に20mAの電流を流したときの、発光出力P0(μW)と順方向電圧Vf(V)を測定した結果を表2に示す。

【0055】

【表2】

【0056】

表2の結果から、高い総発光出力P0と低い順方向電圧Vfの双方をバランスよく満足するために好適な、狭窄径D1の発光径D2に対する比は、1.5〜2.0が好ましい。

【産業上の利用可能性】

【0057】

本発明の電流狭窄型半導体発光素子は、第2導電型積層体の上方でかつ第1電極の直下位置に所定形状の電流狭窄層を有し、かつ、第1導電型積層体の、発光層とは反対側に、所定の波長範囲に対し、高い反射率の反射面を具えることにより、発光効率を向上させることができる。

【符号の説明】

【0058】

1 電流狭窄型半導体発光素子

2 第1導電型積層体

2a n−コンタクト層

2b n−クラッド層

3 発光層

4 第2導電型積層体

4a p−電子ブロック層

4b p−クラッド層

4c p−コンタクト層

4A 第1表面

4A1 第1表面の一部

5 電流狭窄層

5a 第2開口

6 第1電極

6a 第1開口

7 第2電極

8 反射面

9 Si基板

10 バッファ層

D1 狭窄径

D2 発光径

105 電流狭窄層

106 第1電極

205 電流狭窄層

305 電流狭窄層

306 第1電極

309 サファイア基板

406 第1電極

【技術分野】

【0001】

本発明は、半導体発光素子に関するものであって、特に、電流狭窄構造を有する半導体発光素子に関する。

【背景技術】

【0002】

一般に、スポットキュアリング、殺菌、分析分光器やセンサー等の用途に用いられる半導体発光素子に要求される性能として、高い発光効率を有することが挙げられる。このような要求を満足させるため、従来、半導体発光素子内部に電流阻止層または電流狭窄層を設け、発光層に効果的に電流を注入させることにより、発光効率を向上させる技術が知られている。

【0003】

半導体発光素子に電流狭窄層または電流狭窄層を設ける技術を開示した例としては、例えば、特許文献1〜3が挙げられる。

【0004】

特許文献1および2には、半導体層内に島状の電流阻止層または電流狭窄層を設けた、いわゆる埋め込み型の電流狭窄型半導体発光素子が開示されている。しかしながら、前記電流阻止層または電流狭窄層を半導体層内に埋設する場合、エッチング等の付加的な作業工程が必要となるため、エピタキシャル成長を複数回で行わなければならず、作業性の悪化やコスト増加といった問題があり、さらに、前記エッチング工程後に成長させる半導体層に、前記エッチングに起因する欠陥が生じ、結晶品質が低下することにより、発光効率が低下してしまうという問題もある。

【0005】

一方、特許文献3には、半導体層上に電流狭窄層を形成し、この電流狭窄層および電流狭窄層の開口部分上に電極を形成した電流狭窄型半導体発光素子が開示されている。この技術によれば、上述したような作業性の悪化およびコスト増加、並びに結晶品質の低下の問題は改善されているものの、前記電流狭窄層の開口部分上に電極を設けているため、発光層で発生した光が前記電極に吸収され、発光効率が低下してしまうという問題がある。

【0006】

上記問題に加え、特許文献1〜3に記載された半導体発光素子においては、発光層で発生した光は、素子表面だけではなく裏面にも等方的に向かうこととなり、裏面に向かった光は基板によって吸収され、または基板を透過してしまい、素子表面から十分な光を取り出すことができず、発光効率が低下してしまうという問題がある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2003−243703号公報

【特許文献2】特開2003−86841号公報

【特許文献3】特開平11−150296号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、高発光効率を有する電流狭窄型半導体発光素子を提供することにある。

【課題を解決するための手段】

【0009】

上記目的を達成するため、本発明の要旨構成は以下の通りである。

(1) 第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、

前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする電流狭窄型半導体発光素子。

【0010】

(2)前記第1導電型積層体は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体であり、前記発光層は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体である上記(1)に記載の電流狭窄型半導体発光素子。

【0011】

(3)前記電流狭窄層は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなる上記(1)または(2)に記載の電流狭窄型半導体発光素子。

【0012】

(4)前記n型積層体が、n−コンタクト層および該n−コンタクト層上に設けられたn−クラッド層を有する上記(2)または(3)に記載の電流狭窄型半導体発光素子。

【0013】

(5)前記p型積層体が、p−電子ブロック層、該p−電子ブロック層上に設けられたp−クラッド層および該p−クラッド層上に設けられたp−コンタクト層を有する上記(2)、(3)または(4)に記載の電流狭窄型半導体発光素子。

【0014】

(6)前記発光層が、多重量子井戸層である上記(1)〜(5)のいずれか1に記載の電流狭窄型半導体発光素子。

【0015】

(7)前記第1導電型積層体は、Si材料からなる基板上に配設され、前記反射面は、前記基板の上面である上記(1)〜(6)のいずれか1に記載の電流狭窄型半導体発光素子。

【発明の効果】

【0016】

本発明の電流狭窄型半導体発光素子は、第2導電型積層体の上方でかつ第1電極の直下位置に所定形状の電流狭窄層を有し、かつ、第1導電型積層体の、発光波長が200〜350nmの発光層とは反対側に、200〜350nmの波長範囲に対し、高い反射率の反射面を具えることにより、発光効率を向上させることができる。

【図面の簡単な説明】

【0017】

【図1】本発明に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図2】種々の材料における入射光波長と反射率との関係を示すグラフである。

【図3】本発明の第1実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図4】本発明の第2実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図5】本発明の第3実施形態に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図6】比較例1に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図7】比較例2に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図8】比較例3に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【図9】比較例4に従う電流狭窄型半導体発光素子の断面構造を示す模式図である。

【発明を実施するための形態】

【0018】

次に、本発明の半導導体発光素子の実施形態について図面を参照しながら説明する。図1は、この発明に従う半導体発光素子の断面構造を模式的に示したものである。

【0019】

図1に示す本発明に従う電流狭窄型半導体発光素子1は、第1導電型積層体2、発光層3、第2導電型積層体4、電流狭窄層5、第1開口6aを有する第1電極6、および、前記発光層3の、前記第2導電型積層体4とは反対側に配設される第2電極7を具え、前記電流狭窄層5は前記第2導電型積層体4を露出する第2開口5aを有し、前記第2開口5aは前記第1開口6aと中心を同じくしてなり、前記第2開口5aの面積(以下、「狭窄開口面積」という。)は前記第1開口6aの面積(以下、「発光開口面積」という。)よりも大きく、前記第1電極6の一部が前記第2導電型積層体4と接し、かつ前記第1開口6aから前記第2導電型積層体4の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具え、このような構成を採用することにより、発光効率を向上させることを可能にしたものである。ここで、前記第1開口6aおよび前記第2開口5aの形状は、いずれも円形、矩形等の対照形状であればよく、本発明の一実施形態において、前記狭窄開口面積および前記発光開口面積は、それぞれ半導体発光素子1の横断面における幅方向の長さである狭窄径D1、発光径D2に対応するものとして説明する。なお、図中のハッチングは、説明のため、便宜上施したものである。

【0020】

前記第1導電型積層体2は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体2であり、前記発光層3は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体4は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体4であるのが好ましい。また、前記電流狭窄層5は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなるのが好ましい。図1は、一例として、前記第1導電型積層体2がn型積層体2であり、前記第2導電型積層体4がp型積層体4である場合を示したものである。

【0021】

前記n型積層体2は、n−コンタクト層2aおよびこのn−コンタクト層上2aに設けられたn−クラッド層2bを有するのが好ましく、前記p型積層体4は、p−電子ブロック層4a、このp−電子ブロック層4a上に設けられたp−クラッド層4bおよびこのp−クラッド層4b上に設けられたp−コンタクト層4cを有するのが好ましい。また、前記発光層3は、多重量子井戸層3であるのが好ましい。

【0022】

前記n−コンタクト層2aおよび前記n−クラッド層2bは、好適にはそれぞれ1〜5μm、および200〜1000nmの厚さを有し、前記p−電子ブロック層4a、前記p−クラッド層4bおよび前記p−コンタクト層4cは、好適にはそれぞれ5〜50nm、200〜500μmおよび10〜50nmの厚さを有するのが好ましく、前記発光層3は、好適には20〜150nmの厚さを有するのが好ましい。また、前記電流狭窄層5は、好適には0.8〜1.5μmの厚さを有するのが好ましい。これらは、発光素子として良好に機能し、かつ、光の吸収、結晶歪みの増大、順方向電圧の上昇を十分に回避するのに好適な範囲である。

【0023】

本発明の電流狭窄型半導体発光素子1では、電流狭窄層5が前記第1電極6の直下位置に配設されているため、前記狭窄径D1と前記発光径D2とが一致する場合には、前記発光素子1には電流がほとんど流れない。このため、本発明では、前記狭窄径D1は、前記発光径D2よりも大きい必要がある。

【0024】

本発明の発光素子の場合、前記狭窄径D1が小さくなるほど、順方向電圧Vfが高くなる傾向にあり、また、前記発光径D2を前記狭窄径D1対比で小さくするほど、前記第1電極層6の電極面積は増加するので、順方向電圧Vfは低下するものの、前記発光径D2が小さくなるため、総発光出力P0は減少する傾向にある。

【0025】

このため、本発明では、高い総発光出力P0と低い順方向電圧Vfの双方をバランスよく満足させるには、前記狭窄径D1を、前記発光径D2との対比で適正に設定することが好ましい。

【0026】

前記反射面8の、ピーク波長が200〜350nmの範囲に対する反射率は、60%以上であるのが好ましい。製品として要求される発光効率を十分に実現させるためである。図2に、一例として、Si、GaAs、SiCおよびサファイアの、光の波長(nm)と反射率(%)との関係を示すグラフを示す。なお、図2に示す反射率は、所定波長の光を、入射角度5°でAl反射鏡に入射させたときの反射光を紫外可視分光光度計を用いて測定し、これらの値を100%として相対値を算出したものである。

【0027】

図2から、波長200〜350nmの光に対して、Siの反射率は60%以上、GaAsの反射率は45%以上であり、波長200〜265nmの光に対しては、Siの反射率は70%以上、GaAsの反射率は60%以上であることがわかる。したがって、前記反射面8を構成する好適な材料としては、SiまたはGaAsが好ましく、より好適には、Siとするのが好ましい。

【0028】

前記第1導電型積層体2は、Si材料からなる基板9上に配設され、前記反射面8は、前記基板9の上面であるのが好ましい。

【0029】

前記基板9と前記第1導電型積層体2との間にAlN材料からなるバッファ層10を具えてもよい。基板9との格子不整合に起因する転位を抑え、バッファ層10上に積層する結晶の転位密度を下げるためである。

また、図示しないが、バッファ層10に接してリフトオフのための分離層を設けても良い。また、後述するようにバッファ層10が絶縁のAlN材料の場合、狭窄層として使用することも出来る。

本実施例では、サファイアなどの仮の基板上にバッファ層10を介して素子を形成した後、貼り付けやリフトオフなどの手法によりSi材料からなる基板9上に移設したが、Si基板上に直接バッファ層10を成長させ、その上に素子形成する方が、工程が省略されてより好ましい。

【0030】

前記第2電極7は、前記Si材料からなる基板9の、前記発光層3とは反対側に配設されるのが好ましい。素子に流れる電流が均等になってジュール熱が減少し、また、発光部分が素子中心にくることにより、発光効率を向上させることができるためである。また、図1に示すように、前記第2電極7を、一部露出した前記第1導電型積層体2の上面に配設してもよい。

【0031】

次に、本発明の電流狭窄型半導体発光素子の製造方法の一例について、以下で説明する。

本発明の第1実施形態に従う電流狭窄型半導体発光素子21の製造方法は、図3(a)〜(e)に示すように、結晶成長基板31の上面の側に、MOCVD法により、電流狭窄層25、第2導電型積層体24、発光層23、第1導電型積層体22を順次エピタキシャル成長させて形成し、その後、前記第1導電型積層体22の、前記発光層23とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板29を接着した後、前記結晶成長基板31を除去する。また、前記電流狭窄層25に第2開口25aを形成し、この第2開口25aの面積よりも小さな面積の第1開口26aをもつ第1電極層26を、前記電流狭窄層25に隣接する第2導電型積層体24の表面24Aの一部24A1が露出するように形成する。その後、前記支持基板29の下面の側に、第2電極層27を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

【0032】

前記第1導電型積層体22は、p型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型積層体22であり、前記発光層3は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体24は、n型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型積層体24であるのが好ましい。また、前記電流狭窄層5は、絶縁体であるAlN材料からなるのが好ましい。

【0033】

前記p型積層体22は、p−クラッド層およびこのp−コンタクト層上に成長させたp−コンタクト層を有するのが好ましく、前記n型積層体24は、n−コンタクト層、このn−コンタクト層上に成長させたn−クラッド層を有するのが好ましい。また、前記発光層23は、多重量子井戸層23であるのが好ましい。また、図示しないが、p型積層体22と発光層23との間にp−電子ブロック層を有しても良い。

【0034】

前記p−コンタクト層および前記p−クラッド層は、好適にはそれぞれ1〜5μm、および200〜1000nmの厚さを有し、前記n−電子ブロック層、前記n−クラッド層および前記n−コンタクト層は、好適にはそれぞれ5〜50nm、200〜500μmおよび10〜50nmの厚さを有するのが好ましく、前記発光層23は、好適には20〜150nmの厚さを有するのが好ましい。また、前記電流狭窄層25は、好適には0.8〜1.5μmの厚さを有するのが好ましい。これらは、発光素子として良好に機能し、かつ、光の吸収、結晶歪みの増大、順方向電圧の上昇を十分に回避するのに好適な範囲である。

【0035】

本発明の第2実施形態に従う電流狭窄型半導体発光素子41の製造方法は、図4(a)〜(f)に示すように、結晶成長基板51の上面の側に、MOCVD法により、第1導電型積層体42、発光層43、第2導電型積層体44、電流狭窄層45を順次エピタキシャル成長させて形成し、その後、前記電流狭窄層45の、発光層43とは反対側に、中間基板52を接着して、前記結晶成長基板51を除去し、前記第1導電型積層体42の、前記発光層43とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板49を接着する。その後、前記中間基板52を除去し、前記電流狭窄層45に第2開口45aを形成し、この第2開口45aの面積よりも小さな面積の第1開口46aをもつ第1電極層46を、前記電流狭窄層45に隣接する第2導電型積層体44の表面44Aの一部44A1が露出するように形成する。その後、前記支持基板49の下面の側に、第2電極層47を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

また、前記基板51と前記第1導電型積層体42との間にAlN材料からなるバッファ層50を形成し、前記基板51の除去の際に同時に除去(分離)してもよい。

ここで、中間基板52は接着と除去が容易で、支持基板49の接着時に耐えられるものであり、除去の際に他の部位に影響が無いものであることが好ましい。例えばSiやGaAsなどの半導体基板や金属基板、樹脂などである。

【0036】

本発明の第3実施形態に従う電流狭窄型半導体発光素子61の製造方法は、図5(a)〜(g)に示すように、結晶成長基板71の上面の側に、MOCVD法により、第1導電型積層体62、発光層63、第2導電型積層体64、電流狭窄層65を順次エピタキシャル成長させて形成し、その後、前記電流狭窄層65の、前記発光層63とは反対側に、中間基板72を接着し、前記結晶成長基板71を除去して、前記第1導電型積層体62の前記発光層63とは反対側に、ピーク波長が200〜350nmの範囲において高い反射率の反射面を有するSi材料からなる支持基板69を接着する。また、前記中間基板72を除去し、前記他の基板69を接着後、前記第1導電型積層体62の上面の一部を露出させる。また、前記電流狭窄層65に第2開口65aを形成し、この第2開口65aの面積よりも小さな面積の第1開口66aをもつ第1電極層66を、前記電流狭窄層65に隣接する第2導電型積層体64の表面64Aの一部64A1が露出するように形成し、また、前記露出させた前記第1導電型積層体66上に第2電極層67を形成することにより、本発明の電流狭窄型半導体発光素子を製造することができる。

また、前記基板71と前記第1導電型積層体62との間にAlN材料からなるバッファ層70を形成してもよい。

【0037】

上述したところは、この発明の実施形態の一例を示したにすぎず、請求の範囲において種々の変更を加えることができる。

【実施例】

【0038】

[実験例1]

(実施例1)

図3(a)に示すように、サファイア基板31の上面の側に、MOCVD法により、その後電流狭窄層となるAlNバッファ層25(厚さ:1000nm)、n型積層体である第1導電型積層体24(厚さ:2500nm)、発光層23(厚さ:90nm)、および、p型積層体である第2導電型積層体22(厚さ:240nm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体24は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層23は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体22は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0039】

次に図3(b)および図3(c)に示すように、前記第2導電型積層体22に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板29(厚さ:300μm)を接着した後、前記サファイア基板31をリフトオフにより除去した。

【0040】

次に、図3(d)に示すように、前記構造体の上下を反転させた後、ウェットエッチング法により、前記AlN電流狭窄層25に円形の第2開口25aを形成し、前記第2開口25aの径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口26aをもつ第1電極26(厚さ:200nm)を、前記電流狭窄層25に隣接する第2導電型積層体24の表面24Aの一部24A1が露出するように形成した。

また、前記Si基板29上に、第2電極27(厚さ:2μm)を形成することにより、本発明の第1実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0041】

(実施例2)

図4(a)に示すように、サファイア基板51の上面の側に、MOCVD法により、AlNバッファ層50(厚さ:1000nm)、n型積層体である第1導電型積層体42(厚さ:2500nm)、発光層43(厚さ:90nm)、および、p型積層体である第2導電型積層体44(厚さ:240nm)を順次形成した後、前記第2導電型積層体44とは逆導電型、この例ではn型の電流狭窄層45(厚さ:1μm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体42は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層43は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体44は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0042】

次に図4(b)および図4(c)に示すように、前記電流狭窄層45上に適当な中間基板52を接着した後、前記サファイア基板51および前記AlNバッファ層50をリフトオフにより除去した。その後、図4(d)および図4(e)に示すように、前記サファイア基板51および前記AlNバッファ層50の除去により露出した前記第1導電型積層体42上に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板49(厚さ:300μm)を接着した後、前記適当な中間基板52を除去した。

【0043】

次に、図4(f)に示すように、ウェットエッチング法により、前記電流狭窄層45に円形の第2開口45aを形成し、前記第2開口45aの径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口46aをもつ第1電極46(厚さ:2μm)を、前記電流狭窄層45に隣接する第2導電型積層体44の表面44Aの一部44A1が露出するように形成した。

また、前記Si基板49上に、第2電極47(厚さ:200m)を形成することにより、本発明の第2実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0044】

(実施例3)

図5(a)に示すように、サファイア基板71の上面の側に、MOCVD法により、AlNバッファ層70(厚さ:1μm)、n型積層体である第1導電型積層体62(厚さ:2500nm)、発光層63(厚さ:90nm)、および、p型積層体である第2導電型積層体64(厚さ:240nm)を順次形成した後、前記第2導電型積層体64とは逆導電型、この例ではn型のAl0.7Ga0.3Nからなる電流狭窄層65(厚さ:1μm)を、1回のエピタキシャル成長で順次形成した。

前記第1導電型積層体62は、SiドープAl0.5Ga0.5Nからなるn−コンタクト層2a(厚さ:2μm)、および、SiドープAl0.48Ga0.52Nからなるn−クラッド層2b(厚さ:500nm)を順次成長させたn型積層体とする。

前記発光層63は、In0.01Al0.42Ga0.57Nのバリア層およびIn0.01Al0.34Ga0.65Nの井戸層からなるInAlGaNの多重量子井戸層とする。

また、前記第2導電型積層体64は、MgドープAl0.70Ga0.30Nからなるp−電子ブロック層(厚さ:20nm)、MgドープAl0.50Ga0.50Nからなるp−クラッド層(厚さ:200nm)、MgドープGaNからなるp−コンタクト層(厚さ:20nm)を順次成長させたp型積層体とする。

【0045】

次に図5(b)および図5(c)に示すように、前記電流狭窄層65上に適当な中間基板72を接着した後、前記サファイア基板71をリフトオフにより除去した。その後、図5(d)および図5(e)に示すように、前記サファイア基板71の除去により露出した前記AlNバッファ層70上に、ピーク波長が200〜350nmの範囲に対し、高い反射率を有するSi基板69(厚さ:300μm)を接着した後、前記適当な中間基板72を除去した。

【0046】

次に、図5(f)に示すように、ドライエッチングにより前記第1導電型積層体62の一部を露出させた。また、図5(g)に示すように、ウェットエッチング法により、前記電流狭窄層65に円形の第2開口65aを形成し、前記第2開口の径D1(狭窄径D1:150μm)よりも小さな径D2(発光径D2:100μm)の円形の第1開口66aをもつ第1電極66(厚さ:2μm)を、前記電流狭窄層65に隣接する第2導電型積層体64の表面64Aの一部64A1が露出するように形成した。

また、前記露出した第1導電型積層体62上に、第2電極67(厚さ:200m)を形成することにより、本発明の第3実施形態に従う電流狭窄型半導体発光素子(サイズ:300μm×300μm)を得た。なお、発光波長は300nmになるように調整した。

【0047】

(比較例1)

図6に示すように、p−クラッド層上に電流狭窄層105を形成し、エッチング工程を行った後、再度p−コンタクト層を結晶成長させたこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0048】

(比較例2)

図7に示すように、ウェットエッチング法により、電流狭窄層205に第2開口を形成し、この第2開口にかぶさるように第1電極206を形成したこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0049】

(比較例3)

図8に示すように、Si基板を接着せずに、サファイア基板309のままであること以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0050】

(比較例4)

図9に示すように、電流狭窄層を形成しないこと以外は、実施例3と同様な方法で電流狭窄型半導体発光素子を得た。

【0051】

(性能評価)

実施例1〜3および比較例1〜4について、20mAの電流を流したときの発光出力P0(μW)の測定結果を表1に示す。

【0052】

【表1】

【0053】

表1の結果より、実施例1〜3の電流狭窄型半導体発光素子は、電流狭窄層を設けない比較例4、および、反射面を有さない比較例3よりも総発光出力が大きいことがわかる。また、電流狭窄層および反射面を有する比較例1および比較例2と比較しても、電流狭窄層を適切に配置した実施例1〜3は、総発光出力が格段に向上していることがわかる。

【0054】

[実験例2]

上記実施例3の電流狭窄型半導体発光素子について、狭窄径D1および発光径D2を変化させたサンプルNo.1〜4を作製し、これらサンプルNo.1〜4に20mAの電流を流したときの、発光出力P0(μW)と順方向電圧Vf(V)を測定した結果を表2に示す。

【0055】

【表2】

【0056】

表2の結果から、高い総発光出力P0と低い順方向電圧Vfの双方をバランスよく満足するために好適な、狭窄径D1の発光径D2に対する比は、1.5〜2.0が好ましい。

【産業上の利用可能性】

【0057】

本発明の電流狭窄型半導体発光素子は、第2導電型積層体の上方でかつ第1電極の直下位置に所定形状の電流狭窄層を有し、かつ、第1導電型積層体の、発光層とは反対側に、所定の波長範囲に対し、高い反射率の反射面を具えることにより、発光効率を向上させることができる。

【符号の説明】

【0058】

1 電流狭窄型半導体発光素子

2 第1導電型積層体

2a n−コンタクト層

2b n−クラッド層

3 発光層

4 第2導電型積層体

4a p−電子ブロック層

4b p−クラッド層

4c p−コンタクト層

4A 第1表面

4A1 第1表面の一部

5 電流狭窄層

5a 第2開口

6 第1電極

6a 第1開口

7 第2電極

8 反射面

9 Si基板

10 バッファ層

D1 狭窄径

D2 発光径

105 電流狭窄層

106 第1電極

205 電流狭窄層

305 電流狭窄層

306 第1電極

309 サファイア基板

406 第1電極

【特許請求の範囲】

【請求項1】

第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、

前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする電流狭窄型半導体発光素子。

【請求項2】

前記第1導電型積層体は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体であり、前記発光層は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体である請求項1記載の電流狭窄型半導体発光素子。

【請求項3】

前記電流狭窄層は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなる請求項1または2に記載の電流狭窄型半導体発光素子。

【請求項4】

前記n型積層体が、n−コンタクト層および該n−コンタクト層上に設けられたn−クラッド層を有する請求項2または3に記載の電流狭窄型半導体発光素子。

【請求項5】

前記p型積層体が、p−電子ブロック層、該p−電子ブロック層上に設けられたp−クラッド層および該p−クラッド層上に設けられたp−コンタクト層を有する請求項2、3または4に記載の電流狭窄型半導体発光素子。

【請求項6】

前記発光層が、多重量子井戸層である請求項1〜5のいずれか1項に記載の電流狭窄型半導体発光素子。

【請求項7】

前記第1導電型積層体は、Si材料からなる基板上に配設され、前記反射面は、前記基板の上面である請求項1〜6のいずれか1項に記載の電流狭窄型半導体発光素子。

【請求項1】

第1導電型積層体、発光波長が200〜350nmの発光層、第2導電型積層体、電流狭窄層、第1開口を有する第1電極を順に具え、さらに、前記発光層の、前記第2導電型積層体側とは反対側に配設される第2電極を具える電流狭窄型半導体発光素子において、

前記電流狭窄層は前記第2導電型積層体を露出する第2開口を有し、前記第2開口は前記第1開口と中心を同じくしてなり、前記第2開口の面積は前記第1開口の面積よりも大きく、前記第1電極の一部が前記第2導電型積層体と接し、かつ前記第1開口から前記第2導電型積層体の一部が露出するように配置され、

前記第1導電型積層体の、前記発光層側とは反対側に、ピーク波長が200〜350nmの範囲に対し、高い反射率の反射面を具えることを特徴とする電流狭窄型半導体発光素子。

【請求項2】

前記第1導電型積層体は、n型不純物またはp型不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるn型またはp型積層体であり、前記発光層は、GaN、AlGaN、InGaN、InAlGaN系材料からなり、前記第2導電型積層体は、前記第1導電型積層体とは逆導電型の不純物をドープしたGaN、AlGaN、InGaN、InAlGaN系材料からなるp型またはn型積層体である請求項1記載の電流狭窄型半導体発光素子。

【請求項3】

前記電流狭窄層は、n型またはi型のGaN、AlGaN、InGaN、InAlGaN系材料または絶縁体であるAlN材料若しくはSiO2材料からなる請求項1または2に記載の電流狭窄型半導体発光素子。

【請求項4】

前記n型積層体が、n−コンタクト層および該n−コンタクト層上に設けられたn−クラッド層を有する請求項2または3に記載の電流狭窄型半導体発光素子。

【請求項5】

前記p型積層体が、p−電子ブロック層、該p−電子ブロック層上に設けられたp−クラッド層および該p−クラッド層上に設けられたp−コンタクト層を有する請求項2、3または4に記載の電流狭窄型半導体発光素子。

【請求項6】

前記発光層が、多重量子井戸層である請求項1〜5のいずれか1項に記載の電流狭窄型半導体発光素子。

【請求項7】

前記第1導電型積層体は、Si材料からなる基板上に配設され、前記反射面は、前記基板の上面である請求項1〜6のいずれか1項に記載の電流狭窄型半導体発光素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−231193(P2012−231193A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2012−190402(P2012−190402)

【出願日】平成24年8月30日(2012.8.30)

【分割の表示】特願2008−96242(P2008−96242)の分割

【原出願日】平成20年4月2日(2008.4.2)

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成24年8月30日(2012.8.30)

【分割の表示】特願2008−96242(P2008−96242)の分割

【原出願日】平成20年4月2日(2008.4.2)

【出願人】(506334182)DOWAエレクトロニクス株式会社 (336)

【Fターム(参考)】

[ Back to top ]