電源制御回路モジュール

【課題】電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供する。

【解決手段】積層体20の表面には、スイッチングレギュレータ用素子31A,31B,31C,31Dおよびリニアレギュレータ用素子32が間隔をおいて実装されている。積層体20の誘電体層202,203の界面には、電極非形成部300によって分離された内部グランド電極2211,2212,2213,2214,2215が形成されている。内部グランド電極2211,2212,2214,2215は、それぞれスイッチングレギュレータ用素子31A,31B,31C,31Dに接続されている。内部グランド電極2213は、リニアレギュレータ用素子32に接続されている。内部グランド電極2211,2212,2213,2214,2215は、それぞれ異なる外部グランド端子に接続されている。

【解決手段】積層体20の表面には、スイッチングレギュレータ用素子31A,31B,31C,31Dおよびリニアレギュレータ用素子32が間隔をおいて実装されている。積層体20の誘電体層202,203の界面には、電極非形成部300によって分離された内部グランド電極2211,2212,2213,2214,2215が形成されている。内部グランド電極2211,2212,2214,2215は、それぞれスイッチングレギュレータ用素子31A,31B,31C,31Dに接続されている。内部グランド電極2213は、リニアレギュレータ用素子32に接続されている。内部グランド電極2211,2212,2213,2214,2215は、それぞれ異なる外部グランド端子に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のレギュレータを備えた電源制御回路モジュールに関する。

【背景技術】

【0002】

現在、携帯用電子機器に用いられる回路モジュールは、回路素子の高密度化が要求されている。このため、このような回路モジュールは、特許文献1に示すように、一般的には、電極パターンを有する誘電体層を複数層積層した積層体と、該積層体に実装される実装型電子部品と、によって構成される。

【0003】

ところで、このような回路モジュールの中には、電源制御回路モジュールもある。電源制御回路モジュールは、各種のレギュレータを備えており、交流電源や直流電池から供給される電力を、出力先(例えば通信制御モジュールや表示制御モジュール)の電力仕様に応じた電圧、電流に変換して出力する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−235808号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図10(A)は、従来の電源制御回路モジュールの各レギュレータ素子の配置を示す側面図であり、図10(B)は従来の電源制御回路モジュールにおける内部グランド電極のパターンの概略形状を示した図である。

【0006】

従来の電源制御回路モジュール10Pは、積層体20Pと、スイッチングレギュレータ用素子31と、リニアレギュレータ用素子32を備える。積層体20Pは、誘電体層201P,202P,203P,204P,205Pが順次積層されてなる。積層体20Pの誘電体層202P,203Pの界面には内部グランド電極221Pが形成されており、誘電体層204P,205Pの界面には内部グランド電極222Pが形成されている。複数のスイッチングレギュレータ用素子31およびリニアレギュレータ用素子32は、積層体20Pの表面(誘電体層201P)の表面に実装されている。複数のスイッチングレギュレータ用素子31のグランド端子は、導電性ビアホール231Pを介して内部グランド電極221Pに接続されている。内部グランド電極221Pは導電性ビアホール241Pを介して内部グランド電極222Pに接続されている。内部グランド電極222Pは、導電性ビアホール251Pを介して、積層体20Pの裏面に形成された外部グランド接続端子211Pに接続されている。

【0007】

このように、従来の電源制御回路モジュール10Pは、複数のスイッチングレギュレータ用素子31とリニアレギュレータ用素子32とが同じ内部グランド電極221Pに接続されており、スイッチングレギュレータ用素子31で発生するノイズがリニアレギュレータ用素子32に伝搬されないように、各素子が所定の間隔DPをおいて配置されている。もし、この間隔DPよりも短い間隔で各素子を配置すると、スイッチングレギュレータ用素子31間のノイズによる干渉、およびスイッチングレギュレータ用素子31からリニアレギュレータ用素子32へのノイズによる干渉によって、電源制御回路モジュールが出力電圧を安定して制御できなくなる可能性がある。

【0008】

このため、従来の電源制御回路モジュール10Pでは、この間隔DPを必ず保持しなければならない。これにより、積層体20Pの小型化は容易ではなく、この積層体20Pを含む電源制御回路モジュール10Pの小型化も容易ではない。

【0009】

したがって、本発明の目的は、電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供することにある。

【課題を解決するための手段】

【0010】

この発明の電源制御回路モジュールは、次の構成を備えることを特徴としている。電源制御回路モジュールは、複数の誘電体層を積層してなる積層体と、該積層体の表面に実装され、スイッチングレギュレータ用素子を含む複数のレギュレータ用素子とを備える。電源制御回路モジュールは、複数のレギュレータ用素子が接続し、積層体の内部の所定誘電体層の略全面に形成された第1内部グランド電極と、この第1内部グランド電極に接続し、積層体の裏面に形成された第1外部グランド接続端子とを備える。この電源制御回路モジュールの第1内部グランド電極は、レギュレータ素子毎に、電気的に分割されている。この分割された第1内部グランド電極を構成する各個別電極は、それぞれ異なる第1外部グランド接続端子へ接続されている。

【0011】

この構成では、各レギュレータ素子のグランドが積層体内で接続されないため、各レギュレータ素子間のアイソレーションが高くなる。これにより、互いにノイズを発生しやすい複数のスイッチングレギュレータ用素子間のノイズ干渉や、スイッチングレギュレータ用素子からリニアレギュレータ用素子へのノイズ干渉が抑圧される。そして、各個別電極間が電極非形成部によって離間されるため、従来の構成よりも素子間隔を狭くしても、素子間のアイソレーションを十分に確保できる。

【0012】

また、この発明の電源制御回路モジュールは次の構成を備えることが好ましい。電源制御回路モジュールは、積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子と、第1内部グランド電極とは異なる誘電体層の略全面に形成された第2内部グランド電極と、この第2内部グランド電極に接続し、積層体の裏面に形成された第2外部グランド接続端子と、を備える。そして、外部ノイズの影響を受けやすい回路素子は、第2内部グランド電極に接続されている。

【0013】

この構成では、ノイズを発生しやすいスイッチングレギュレータ用素子を含む複数のレギュレータ用素子は、積層体の表面に実装され、外部ノイズの影響を受けやすい回路素子は積層体の裏面に実装される。さらに、積層体の表面に実装されるレギュレータ用素子と、積層体の裏面に実装される素子とで、接続される内部グランド電極が異なる。これにより、積層体の表面に実装されるレギュレータ用素子と、積層体の裏面に実装される外部ノイズの影響を受けやすい回路素子との間で、高いアイソレーションを実現できる。したがって、積層体の表面に実装されるレギュレータ用素子で発生したノイズは、積層体の裏面に実装されている外部ノイズの影響を受けやすい回路素子に伝搬されることなく、外部ノイズの影響を受けやすい回路素子を保護できる。

【0014】

また、この発明の電源制御回路モジュールでは、次の構成を適用することもできる。積層体の表面に実装されたレギュレータ用素子は、スイッチングレギュレータ用素子である。積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子は、リニアレギュレータ用素子またはデジタルIC素子である。

【0015】

この構成では、ノイズを発生しやすいスイッチングレギュレータ用素子と、ノイズを殆ど発生することなく外部ノイズの影響を受けやすいリニアレギュレータ用素子またはデジタルIC素子とが、積層体の対向する面に実装され、積層体内ではグランド電極も接続しない。したがって、スイッチングレギュレータ用素子が発するノイズが、外部ノイズの影響を受けやすいリニアレギュレータ用素子またはデジタルIC素子に悪影響を及ぼすことを、さらに抑圧できる。

【0016】

また、この発明の電源制御回路モジュールは、次の構成であることが好ましい。電源制御回路モジュールは、複数の第1の導電性ビアホールと、裏面側絶縁性樹脂と、複数の第2の導電性ビアホールと、を備える。第1の導電性ビアホールは、積層体の積層方向に沿って延びる形状からなり、第1内部グランド電極と第1外部グランド接続端子とを接続する。裏面側絶縁性樹脂は、積層体の裏面に形成され、外部ノイズの影響を受けやすい回路素子を覆うように形成されている。第2の導電性ビアホールは、第1の導電性ビアホールに連続するように裏面側絶縁性樹脂に形成されている。複数の第1、第2の導電性ビアホールは、外部ノイズの影響を受けやすい回路素子の実装領域を囲むように、配設されている。

【0017】

この構成では、外部ノイズの影響を受けやすい回路素子が、第1、第2の内部グランド電極、第2の導電性ビアホールによって、周囲の五面が囲まれる。これにより、スイッチングレギュレータ用素子の発するノイズから、外部ノイズの影響を受けやすい回路素子を保護できる。さらに、当該電源制御回路モジュールが実装されるマザー基板は、一般的に、電源制御回路モジュールの実装領域の略全域にグランド電極が形成されている。したがって、これを利用することで、外部ノイズの影響を受けやすい回路素子を三次元的にノイズから保護することができる。

【0018】

また、この発明の電源制御回路モジュールでは、第1、第2の導電性ビアホールは、スイッチングレギュレータ用素子の発するノイズの裏面側絶縁性樹脂での実効波長λNの1/4未満の間隔で配設されていることが好ましい。

【0019】

この構成のように、導電性ビアホールの間隔を決定することで、スイッチングレギュレータ用素子の発するノイズは、確実に遮断され、外部ノイズの影響を受けやすい回路素子まで伝搬されることを防止できる。

【0020】

また、この発明の電源制御回路モジュールは、次の構成であることが好ましい。電源制御回路モジュールを構成する積層体の所定層には、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが形成されている。線状電極パターンは、第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された線状電極パターンを基準に第2のグランド電極と反対側に形成された平面状電極と、によって、囲まれている。

【0021】

この構成では、積層体内に、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンを形成する場合を示している。そして、この構成では、第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された線状電極パターンを基準に第2のグランド電極と反対側に形成された平面状電極によって、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが、ノイズから保護される。

【0022】

また、この発明の電源制御回路モジュールでは、次の構成であることが好ましい。電源制御回路モジュールの積層体の表面には、複数のレギュレータ用素子を内包する形状で且つ電磁波を遮蔽するシールド部材が配設されている。

【0023】

この構成では、積層体の表面に実装されたレギュレータ用素子から発するノイズがシール部材で遮蔽される。これにより、積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子への悪影響を、さらに抑圧できる。

【発明の効果】

【0024】

この発明によれば、電源制御の特性を低下させることなく、従来よりも小型の電源制御回路モジュールを実現することができる。

【図面の簡単な説明】

【0025】

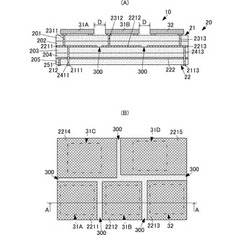

【図1】第1の実施形態に係る電源制御回路モジュール10の構成を示す側面図、および内部グランド電極のパターンの概略形状を示した図である。

【図2】第2の実施形態に係る電源制御回路モジュール10Aの構成を示す側面図である。

【図3】第3の実施形態に係る電源制御回路モジュール10Bの構成を示す側面図である。

【図4】第4の実施形態に係る電源制御回路モジュール10Cの構成を示す側面図である。

【図5】第5の実施形態に係る電源制御回路モジュール10Dの構成を示す側面図である。

【図6】第6の実施形態に係る電源制御回路モジュール10Eの構成を示す側面図である。

【図7】第6の実施形態に係る電源制御回路モジュール10Eをマザー基板61へ実装した状態を示す側面図である。

【図8】第7の実施形態に係る電源制御回路モジュール10Fをマザー基板61へ実装した状態を示す側面図である。

【図9】第8の実施形態に係る電源制御回路モジュール10Gをマザー基板61へ実装した状態を示す側面図である。

【図10】従来の電源制御回路モジュール10Pの構成を示す側面図、および内部グランド電極のパターンの概略形状を示した図である。

【発明を実施するための形態】

【0026】

本発明の第1の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図1(A)は、第1の実施形態に係る電源制御回路モジュール10の構成を示す側面図であり、図1(B)は内部グランド電極のパターンの概略形状を示した図である。なお、本実施形態の電源制御回路モジュール10は、図示する電極パターンの他に電源入力端子や電源出力端子やこれらに接続する配線パターンも備えられているが、以下の説明では、グランド接続する配線パターンのみを図示して説明する。

【0027】

電源制御回路モジュール10は、積層体20、四個のスイッチングレギュレータ用素子31A,31B,31C,31D、一個のリニアレギュレータ用素子32を備える。

【0028】

積層体20は、誘電体層201,202,203,204,205が順次積層されてなる。誘電体層201が最上層となり、誘電体層205が最下層となるように構成される。これにより、誘電体層201の表面が積層体20の表面21となり、誘電体層205の裏面が積層体20の裏面22となる。

【0029】

積層体20の表面21(誘電体層201の表面)には、図示しない実装用ランド電極等が形成されている。積層体20の表面21には、スイッチングレギュレータ用素子31A,31B,31C,31Dと、リニアレギュレータ用素子32が実装されている。これらスイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ用素子32とは、上述の実装用ランド電極に実装されている。また、図示しないが、積層体20の表面21には、各種の受動素子(インダクタ、キャパシタ等)が実装されており、スイッチングレギュレータ用素子31A,31B,31C,31DとともにそれぞれにDC−DCコンバータ回路を構成したり、リニアレギュレータ用素子32とともにLDO(Low Drop Out)レギュレータを構成している。

【0030】

積層体20の誘電体層202,203の界面には、内部グランド電極2211,2212,2213,2214,2215が形成されている。これら内部グランド電極2111,2212,2213,2214,2215は、所定幅のグランド電極非形成部300によって分離されている。電極非形成部300の幅は、例えば、当該積層体20に形成する導電性ビアホールの径よりも若干広く設定されている。言い換えれば、積層体20の製造ばらつきに基づいて、グランド電極非形成部に形成される導電性ビアホールの電極が各内部グランド電極2211,2212,2213,2214,2215に接触しない程度の幅に設定されている。

【0031】

内部グランド電極2211は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Aの実装領域を含むような形状で形成されている。内部グランド電極2211とスイッチングレギュレータ用素子31Aは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2311によって接続されている。内部グランド電極2211は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2411によって、積層体20の裏面22に形成された外部グランド接続端子2111に接続されている。

【0032】

内部グランド電極2212は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Bの実装領域を含むような形状で形成されている。内部グランド電極2212とスイッチングレギュレータ用素子31Bは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2312によって接続されている。内部グランド電極2212は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0033】

内部グランド電極2213は、誘電体層の積層方向に沿って見て、リニアレギュレータ用素子32の実装領域を含むような形状で形成されている。内部グランド電極2213とリニアレギュレータ用素子32は、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2313によって接続されている。内部グランド電極2213は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2413によって、積層体20の裏面22に形成された外部グランド接続端子2113に接続されている。

【0034】

内部グランド電極2214は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Cの実装領域を含むような形状で形成されている。内部グランド電極2214とスイッチングレギュレータ用素子31Cは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール(図示せず)によって接続されている。内部グランド電極2214は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0035】

内部グランド電極2215は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Dの実装領域を含むような形状で形成されている。内部グランド電極2215とスイッチングレギュレータ用素子31Dは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール(図示せず)によって接続されている。内部グランド電極2215は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0036】

積層体20の誘電体層204,205の界面には、内部グランド電極222が形成されている。内部グランド電極222は、誘電体層204,205の界面の略全面に形成されている。内部グランド電極222には、局所的にグランド電極非形成領域が設けられており、当該グランド電極非形成領域を、内部グランド電極2211,2212,2213,2214,2215と導通する導電性ビアホールが貫通している。内部グランド電極222は、誘電体層205を積層方向に沿って貫通する導電性ビアホール251によって、積層体20の裏面に形成された外部グランド接続端子212に接続されている。なお、内部グランド電極222は、上述のDC−DCコンバータ回路やLDOレギュレータ以外の回路のグランドとして機能するものであり、必要に応じて省略することもできる。

【0037】

このような構成とすることで、スイッチングレギュレータ用素子31A,31B,31C,31D用の内部グランド電極2211,2212,2214,2215と、リニアレギュレータ用素子32用の内部グランド電極2213とが、それぞれ電気的に分離されており、各レギュレータ用素子のグランドが、積層体20内で接続されない。従って、グランド電極を介して、スイッチングレギュレータ用素子31A,31B,31C,31D間およびスイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ32間のノイズの伝搬を抑制できる。

【0038】

このため、スイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ用素子32を、従来構成よりも近づけて配置しても(D<DP)、スイッチングレギュレータ用素子31A,31B,31C,31D間でのノイズの相互伝搬や、スイッチングレギュレータ用素子31A,31B,31C,31Dからリニアレギュレータ用素子32へのノイズの伝搬を抑制できる。これにより、電源制御特性を低下させることなく、レギュレータ用素子の配置間隔を狭くすることができ、従来構成よりも小型の電源制御回路モジュールを実現することができる。

【0039】

次に、第2の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図2は、第2の実施形態に係る電源制御回路モジュール10Aの構成を示す側面図である。本実施形態の電源制御回路モジュール10Aは、スイッチングレギュレータ用素子の配置と、リニアレギュレータ用素子の配置とが、第1の実施形態に示した電源制御回路モジュール10と異なるものであり、第1の実施形態と同じ構成箇所は説明を簡略化する。

【0040】

概略的には、本実施形態の電源制御回路モジュール10Aでは、スイッチングレギュレータ用素子31A,31B,31Cは積層体20Aの表面21に実装されている。また、リニアレギュレータ用素子32A,32Bは積層体20Aの裏面22に実装されている。

【0041】

電源制御回路モジュール10Aは、積層体20A、三個のスイッチングレギュレータ用素子31A,31B,31C、二個のリニアレギュレータ用素子32A,32Bを備える。

【0042】

積層体20Aは、誘電体層201,202,203,204,205が順次積層されてなる。誘電体層201が最上層となり、誘電体層205が最下層となるように構成される。これにより、誘電体層201の表面が積層体20の表面21となり、誘電体層205の裏面が積層体20の裏面22となる。

【0043】

積層体20Aの表面21には、スイッチングレギュレータ用素子31A,31B,31Cが実装されている。

【0044】

積層体20Aの誘電体層202,203の界面には、内部グランド電極2211,2212,2213が形成されている。これら内部グランド電極2111,2212,2213は、所定幅のグランド電極非形成部300によって分離されている。

【0045】

内部グランド電極2211は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Aの実装領域を含むような形状で形成されている。内部グランド電極2211とスイッチングレギュレータ用素子31Aは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2311によって接続されている。内部グランド電極2211は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2411によって、積層体20Aの裏面22に形成された外部グランド接続端子2111に接続されている。

【0046】

内部グランド電極2212は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Bの実装領域を含むような形状で形成されている。内部グランド電極2212とスイッチングレギュレータ用素子31Bは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2312によって接続されている。内部グランド電極2212は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20Aの裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0047】

内部グランド電極2213は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Cの実装領域を含むような形状で形成されている。内部グランド電極2213とスイッチングレギュレータ用素子31Cは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2313によって接続されている。内部グランド電極2213は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2413によって、積層体20Aの裏面22に形成された外部グランド接続端子2113に接続されている。

【0048】

積層体20Aの裏面22には、リニアレギュレータ用素子32A,32Bが実装されている。

【0049】

積層体20の誘電体層204,205の界面には、内部グランド電極222が形成されている。内部グランド電極222は、誘電体層204,205の界面の略全面に形成されている。

【0050】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261Aによって、リニアレギュレータ用素子32Aへ接続されている。内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261Bによって、リニアレギュレータ用素子32Bへ接続されている。

【0051】

内部グランド電極222には、局所的にグランド電極非形成領域が設けられており、当該グランド電極非形成領域を、内部グランド電極2211,2212,2213と導通する導電性ビアホールが貫通している。なお、図には内部グランド電極2212に接続する導電性ビアホールおよびグランド電極非形成領域は図示されていないが実際には設けられている。

【0052】

内部グランド電極222は、誘電体層205を積層方向に沿って貫通する導電性ビアホール251によって、積層体20の裏面に形成された外部グランド接続端子212に接続されている。

【0053】

積層体20Aの裏面22の全面には、リニアレギュレータ用素子32A,32Bが埋まり込む厚みで絶縁性樹脂42が配設されている。絶縁性樹脂42における積層体20Aと反対側の面(以下、絶縁性樹脂42の裏面と称する。)には、上述の積層体20Aの裏面に形成された各外部グランド接続端子を含む各端子に接続する外部接続用端子が形成されている。

【0054】

例えば、絶縁性樹脂42の裏面形成された外部接続端子2811は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材2611によって、外部グランド接続端子2111に接続されている。絶縁性樹脂42の裏面形成された外部接続端子2813は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材2613によって、外部グランド接続端子2113に接続されている。絶縁性樹脂42の裏面形成された外部接続端子282は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材271によって、外部グランド接続端子212に接続されている。なお、導電性部材としては、例えば、導電性ビアホールや金属のピンを使用することができる。

【0055】

このような構成とすることで、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32A,32Bとが、積層体20Aの異なる面に実装される。特に、本実施形態の構成では、積層体20Aを介した両面(表面21と裏面22)にそれぞれ実装される。これにより、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32A,32Bは、近接しない。また、スイッチングレギュレータ用素子31A,31B,31C用の内部グランド電極2211,2212,2213と、リニアレギュレータ用素子32A,32B用の内部グランド電極222とが、それぞれ電気的に分離されており、各レギュレータ用素子のグランドが、積層体20内で接続されない。

【0056】

このため、スイッチングレギュレータ用素子31A,31B,31Cとリニアレギュレータ用素子32A,32Bとの間のアイソレーションをより高くすることができ、より確実に、ノイズの干渉による電源制御特性の低下を防止できる。さらに、積層体20Aの両面に実装することで、同じ数のレギュレータ用素子を積層体の表面のみに実装するよりも、小面積化が可能になる。逆に言えば、同じ面積の積層体を用いて、より多数のレギュレータを備える電源制御回路モジュールを実現することができる。

【0057】

次に、第3の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図3は、第3の実施形態に係る電源制御回路モジュール10Bの構成を示す側面図である。本実施形態の電源制御回路モジュール10Bは、第2の実施形態に係る電源制御回路モジュール10Aに対して、さらに、積層体20Bの表面側に絶縁性樹脂41とシールド部材51とを備えたものであり、他の構成は第2の実施形態に係る電源制御回路モジュール10Aと同じである。したがって、以下では異なる箇所のみを説明する。

【0058】

積層体20Bの表面21の全面には、スイッチングレギュレータ用素子31A,31B,31Cが埋まり込む厚みで絶縁性樹脂41が配設されている。さらに絶縁性樹脂41を覆うように、蓋状のシールド部材51が配設されている。シールド部材51は、金属等の導電性材料からなる。

【0059】

なお、この際、積層体20Bの表面21側となる誘電体層201B,202Bは、電源制御回路モジュールの低背化のために、外周が削られていてもよい。そして、シールド部材51は、誘電体層201B,202Bも覆うように配設されている。

【0060】

シールド部材51は、内部グランド電極2211,2213等に接続されている。これにより、シールド部材51は、グランドに接続される。

【0061】

このような構成とすることで、上述の第2の実施形態に示した効果とともに、スイッチングレギュレータ用素子31A,31B,31Cが動作することによって放射されるノイズがシールド部材51で遮断されて、外部に放射されない。また、絶縁性樹脂42およびシールド部材51を介して、スイッチングレギュレータ用素子31A,31B,31Cで発生した熱が効果的に外部へ放射されるため、放熱性の高い電源制御回路モジュールを実現することができる。特に、熱伝導率が高い絶縁性樹脂を用いれば、より放熱性の高い電源制御回路モジュールを実現することができる。

【0062】

なお、スイッチングレギュレータ用素子から外部へ放射されるノイズは、スイッチングレギュレータ用素子に接続する内部グランド電極に漏洩するノイズと比較して、十分に小さい。このため、シールド部材51に伝搬するノイズは極小さい。さらに、シールド部材51は積層体の外部グランド接続端子に接続されている。したがって、複数のスイッチングレギュレータ用素子のそれぞれが発したノイズがシールド部材51に伝搬されても、相互に悪影響を与えることはない。

【0063】

以上のように、本実施形態の構成を用いれば、より信頼性の高い電源制御回路モジュールを実現することができる。

【0064】

次に、第4の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図4は、第4の実施形態に係る電源制御回路モジュール10Cの構成を示す側面図である。本実施形態の電源制御回路モジュール10Cは、第3の実施形態に係るモジュール10Bにおけるリニアレギュレータ用素子32A,32Bに替えて、積層体20Cの裏面22に、デジタルIC50を実装したものである。したがって、以下では、第3の実施形態の電源制御回路モジュール10Bと異なる箇所のみを具体的に説明する。

【0065】

積層体20Cの裏面22には、デジタルIC50が実装されている。デジタルICとは、例えば、シリアルインターフェース制御用IC、USB制御用IC、論理IC、マイクロプロセッサ、オーディオIC、およびビデオIC等のデジタル信号で制御等を行うICである。

【0066】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール262によって、デジタルIC50へ接続されている。

【0067】

内部グランド電極222は、誘電体層205を積層方向に沿って貫通する複数の導電性ビアホール251によって、積層体20の裏面に形成された複数の外部グランド接続端子212に接続されている。

【0068】

積層体20Cの裏面22の全面には、デジタルICが埋まり込む厚みで絶縁性樹脂42が配設されている。絶縁性樹脂42における積層体20Cと反対側の面(以下、絶縁性樹脂42の裏面と称する。)には、上述の積層体20Cの裏面に形成された各外部グランド接続端子を含む各端子に接続する外部接続用端子が形成されている。

【0069】

例えば、絶縁性樹脂42の裏面形成された外部接続端子2811は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性ビアホール2611によって、外部グランド接続端子2111に接続されている。絶縁性樹脂42の裏面形成された外部接続端子2813は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性ビアホール2613によって、外部グランド接続端子2113に接続されている。絶縁性樹脂42の裏面形成された複数の外部接続端子282は、絶縁性樹脂42の厚み方向を貫通するように形成された複数の導電性部材271によって、それぞれに対応する外部グランド接続端子212に接続されている。

【0070】

このような構成とすることで、ノイズを発生するスイッチングレギュレータ用素子31A,31B,31Cと、ノイズの影響を受けやすいデジタルIC50とが積層体20Cの異なる面に配設される。特に、本実施形態の構成では、積層体20Cを介した両面(表面21と裏面22)にそれぞれ実装される。このため、スイッチングレギュレータ用素子31A,31B,31CとデジタルIC50は、近接しない。また、スイッチングレギュレータ用素子31A,31B,31Cで発生するノイズは、シールド部材51によって遮断され、外部へ放射されない。したがって、スイッチングレギュレータ用素子31A,31B,31Cで発生したノイズは、デジタルIC50へ伝搬されない。これにより、デジタルIC50は、安定して動作する。

【0071】

なお、本実施形態に説明では、積層体20Cの表面21に、スイッチングレギュレータ用素子のみを配置する例を示したが、第1の実施形態に示したように、スイッチングレギュレータ用素子とリニアレギュレータ用素子とを積層体20Cの表面21に実装してもよい。

【0072】

次に、第5の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図5は、第5の実施形態に係る電源制御回路モジュール10Dの構成を示す側面図である。

【0073】

本実施形態の電源制御回路モジュール10Dは、第4の実施形態に係るモジュール10CがデジタルIC50のみを実装しているのに対して、積層体20Dの裏面22に、リニアレギュレータ用素子32とデジタルIC50を実装したものである。したがって、以下では、第4の実施形態の電源制御回路モジュール10Cと異なる箇所のみを具体的に説明する。

【0074】

積層体20Dの裏面22には、リニアレギュレータ用素子32とデジタルIC50が実装されている。

【0075】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261によって、リニアレギュレータ用素子32へ接続されている。内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール262によって、デジタルIC50へ接続されている。

【0076】

このような構成とすることで、ノイズを発生するスイッチングレギュレータ用素子31A,31B,31Cと、ノイズの影響を受けやすいリニアレギュレータ用素子32およびデジタルIC50とが積層体20Dの異なる面に配設される。特に、本実施形態の構成では、積層体20Dを介した両面(表面21と裏面22)にそれぞれ実装される。このため、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32およびデジタルIC50は、近接しない。また、スイッチングレギュレータ用素子31A,31B,31Cで発生するノイズは、シールド部材51によって遮断され、外部へ放射されない。したがって、スイッチングレギュレータ用素子31A,31B,31Cで発生したノイズは、リニアレギュレータ用素子32およびデジタルIC50へ伝搬されない。これにより、リニアレギュレータ用素子32とデジタルIC50は、安定して動作する。

【0077】

なお、本実施形態の構成では、リニアレギュレータ用素子32とデジタルIC50とが同じ内部グランド電極222に接続されているが、リニアレギュレータ用素子32はノイズを殆ど発生しないため、デジタルIC50に与える悪影響はない。ただし、リニアレギュレータ用素子32とデジタルIC50とを異なる内部グランド電極222に接続してもよい。

【0078】

次に、第6の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図6(A)は、第6の実施形態に係る電源制御回路モジュール10Eの構成を示す側面図であり、図6(B)は、積層体20Eの裏面22から見た導電性ビアホールの配置パターンを示す図である。

【0079】

本実施形態の電源制御回路モジュール10Eは、第2の実施形態に係る電源制御回路モジュール10Aに対して、導電性ビアホールの形成パターンが異なるものであり、他の構成は同じである。したがって、導電性ビアホールの形成パターンに関する箇所のみを説明する。

【0080】

積層体20Eの最下層である誘電体層205には、図6(B)に示すように、外周に沿って、複数の導電性ビアホールが所定間隔で配列形成されている。これらの導電性ビアホールは、外部グランド接続端子を含む各種の外部接続端子へ接続される。導電性ビアホールは、外周に沿って二列で配列形成されている。

【0081】

絶縁性樹脂42には、これらの積層体20Eに形成された導電性ビアホールに連続するように、これらの導電性ビアホールと同じ間隔で、絶縁性樹脂42を厚み方向に貫通する導電性ビアホールが形成されている。

【0082】

外周側(積層体20Eの側面に近い側)の導電性ビアホール群内には、内部グランド電極2211,2212,2213に接続する複数の導電性ビアホール241Gが含まれている。内周側(積層体20Eの側面に離れた側)の導電性ビアホール群内には、内部グランド電極222に接続する複数の導電性ビアホール251Gが含まれている。このような構成において、積層体20Eの側面に沿った隣り合う導電性ビアホール241Gは、間隔PG1で形成されている。積層体20Eの角部において隣り合う導電性ビアホール241Gは、間隔PG2で形成されている。

【0083】

間隔PG1,PG2は、絶縁性樹脂42の誘電率を加味した上で、スイッチングレギュレータ用素子31A,31B,31Cが発するノイズが絶縁性樹脂42を伝搬する実効波長をλNとして、λN/4未満の長さになるように設定されている。

【0084】

絶縁性樹脂42には、導電性ビアホール241Gに連続する導電性部材261Gが形成されている。これにより、導電性部材261Gは、間隔PG1もしくは間隔PG2で形成されることになる。したがって、導電性部材261Gもスイッチングレギュレータ用素子31A,31B,31Cが発するノイズの実効波長λNの1/4(λN/4)未満の間隔で形成されることになる。これにより、スイッチングレギュレータ用素子31A,31B,31Cから生じ、積層体20Eの側面から裏面21に回り込んだノイズは、絶縁性樹脂42に形成された導電性部材261Gでトラップされる。したがって、リニアレギュレータ用素子32A,32Bへノイズが伝搬されることを、より効果的に抑圧できる。さらに、この構成とすることで、外部からのノイズがリニアレギュレータ用素子32A,32Bに伝搬されることも抑制できる。

【0085】

さらに、内周側に設けた複数の導電性ビアホール251Gの間隔をλN/4未満にするとよりよい。これにより、複数の導電性ビアホール251Gに接続する絶縁性樹脂42に形成された導電性部材271Gの間隔がλN/4未満になる。これにより、ノイズに対する二重のトラップを構成することも可能である。

【0086】

なお、外周側に導電性ビアホール251Gを含み、内周側に導電性ビアホール241Gを含むようにしてもよい。また、外周側、内周側で、それぞれ導電性ビアホール241G,251Gを含むようにしてもよい。しかしながら、導電性ビアホール241Gは、リニアレギュレータ用素子32A,32Bに接続する内部グランド電極222に接続するため、上述のように、導電性ビアホール241Gは内周側のみにある方が望ましい。

【0087】

このような構成からなる電源制御回路モジュール10Eは、図7に示すように、グランド電極62を有するマザー基板61に実装される。図7は、第6の実施形態に係る電源制御回路モジュール10Eをマザー基板61へ実装した状態を示す側面図である。

【0088】

図7に示すように、電源制御回路モジュール10Eの導電性ビアホール241G(導電性部材261G)、導電性ビアホール251G(導電性部材271G)に接続する外部接続端子281G,282Gは、マザー基板61に形成された導電性ビアホール631G,632Gを介して、マザー基板61のグランド電極62に接続されている。マザー基板61における電源制御回路モジュールが実装される領域には、図7に示すように略全面に亘る形状のグランド電極62が形成される。

【0089】

このような構成により、マザー基板61に実装された状態で、電源制御回路モジュール10Eのリニアレギュレータ用素子32A,32Bの積層体20Eと反対側の面は、マザー基板61のグランド電極62で、全面に覆われる。したがって、このグランド電極62によっても、リニアレギュレータ用素子32A,32Bへのノイズの伝搬は抑圧される。

【0090】

以上のように、本実施形態の構成を用いることで、リニアレギュレータ用素子32A,32Bは、積層体20E内の内部グランド電極、これに接続する導電性ビアホール群、およびマザー基板61のグランド電極62によって、スイッチングレギュレータ用素子31A,31B,31Cの発生するノイズに対して、三次元的にシールドされる。これにより、電源制御特性の低下を、より確実に防ぐことができる。

【0091】

次に、第7の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図8は、第7の実施形態に係る電源制御回路モジュール10Fをマザー基板61へ実装した状態を示す側面図である。本実施形態の電源制御回路モジュール10Fは、第6の実施形態に示した電源制御回路モジュール10Eの導電性ビアホールの構成を有しながら、さらに、第3の実施形態に係る電源制御回路モジュール10Bと同様に、積層体20Fの表面21にシールド部材51を配置したものである。

【0092】

このような構成とすることで、より一層、ノイズに対するシールド性が高い電源制御回路モジュールを実現することができる。

【0093】

次に、第8の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図9は、第8の実施形態に係る電源制御回路モジュール10Gをマザー基板61へ実装した状態を示す側面図である。

【0094】

本実施形態の電源制御回路モジュール10Gは、第7の実施形態に係る電源制御回路モジュール10Fに対して、中間層の誘電体層206が増加し、デジタル信号が伝搬される内部パターン電極がさらに形成された場合を示している。したがって、異なる箇所のみを説明する。

【0095】

上述の各実施形態に示した誘電体層203、204間には、誘電体層206が備えられている。

【0096】

誘電体層203、206の界面には、内部グランド電極223が形成されている。誘電体層206、204の界面には、デジタル信号用の線状電極パターン290が形成されている。

【0097】

誘電体層206,204には、線状電極パターン290の形成領域を囲むように、所定間隔で、複数の導電性ビアホール291が形成されている。複数の導電性ビアホール291は、内部グランド電極222,223に接続されている。これら複数の導電性ビアホール291は、上述のλN/4未満の間隔で配列形成されている。

【0098】

このような構成とすることで、線状電極パターン290は、内部グランド電極222,223、複数の導電性ビアホール291によって、スイッチングレギュレータ用素子31A,31B,31Cの発生するノイズに対して、三次元的にシールドされる。これにより、デジタル信号にノイズが重畳することを防止でき、電源制御特性の低下を、より確実に防ぐことができる。

【0099】

なお、上述の各実施形態において、シールド部材51を用いる場合においては、当該シールド部材51に替えて、絶縁性樹脂41に、複数の導電性ビアホールを設け、絶縁性樹脂41の表面の略全面に平膜状の電極パターンを形成するようにしてもよい。この場合、複数の導電性ビアホールは、絶縁性樹脂41の外周に沿って形成すればよく、配置間隔はλN/4にする。複数の導電性ビアホールは、絶縁性樹脂41の表面に形成された平膜状の電極パターンに接続させるとともに、スイッチングレギュレータ用素子に接続する内部グランド電極に接続させる。

【0100】

また、上述の実施形態におけるデジタルICを用いる実施形態は、デジタルICに替えて、オーディオIC、RF回路を構成する素子群、センサ周辺回路を構成する素子群、水晶等の振動子、プロセッサ等の外部ノイズに弱い電子部品を用いる態様へ適用することもできる。

【0101】

また、さらに、上述の各実施形態では、積層体の一方面に実装されるレギュレータ用素子として、個別に実装する素子を例に説明したが、複数のレギュレータ素子が一つのチップ内に搭載された複合レギュレータICを用いた場合にも、上述の実施形態の構成を適用することができる。

【符号の説明】

【0102】

10,10A,10B,10C,10D,10E,10F,10G,10P:電源制御回路モジュール、

20,20A,20B,20C,20D,20E,20F,20G,20P:積層体、21:表面、22:裏面、

31,31A,31B,31C,31D:スイッチングレギュレータ用素子、32,32A,32B:リニアレギュレータ用素子、

41,42:絶縁性樹脂、

50:デジタルIC、

51:シールド部材、

61:マザー基板、

62:グランド電極、

201−205,201B,202B,201C,202C,201D,202D,201F,202F,201P−205P:誘電体層、

2111,2113,212,211P:外部グランド接続端子、

2311,2312,2313,2411,2413,251,261A,261B,2811,2813,231P,241P,251P,241G,251G,631G,632G:導電性ビアホール、

2611,2613,271,261G,271G:導電性部材、

2211−2215,222,223,221P,222P:内部グランド電極、

300:グランド電極非形成部、

2811,2813,282,281G,282G:外部接続端子、

290:線状電極パターン

【技術分野】

【0001】

本発明は、複数のレギュレータを備えた電源制御回路モジュールに関する。

【背景技術】

【0002】

現在、携帯用電子機器に用いられる回路モジュールは、回路素子の高密度化が要求されている。このため、このような回路モジュールは、特許文献1に示すように、一般的には、電極パターンを有する誘電体層を複数層積層した積層体と、該積層体に実装される実装型電子部品と、によって構成される。

【0003】

ところで、このような回路モジュールの中には、電源制御回路モジュールもある。電源制御回路モジュールは、各種のレギュレータを備えており、交流電源や直流電池から供給される電力を、出力先(例えば通信制御モジュールや表示制御モジュール)の電力仕様に応じた電圧、電流に変換して出力する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2005−235808号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

図10(A)は、従来の電源制御回路モジュールの各レギュレータ素子の配置を示す側面図であり、図10(B)は従来の電源制御回路モジュールにおける内部グランド電極のパターンの概略形状を示した図である。

【0006】

従来の電源制御回路モジュール10Pは、積層体20Pと、スイッチングレギュレータ用素子31と、リニアレギュレータ用素子32を備える。積層体20Pは、誘電体層201P,202P,203P,204P,205Pが順次積層されてなる。積層体20Pの誘電体層202P,203Pの界面には内部グランド電極221Pが形成されており、誘電体層204P,205Pの界面には内部グランド電極222Pが形成されている。複数のスイッチングレギュレータ用素子31およびリニアレギュレータ用素子32は、積層体20Pの表面(誘電体層201P)の表面に実装されている。複数のスイッチングレギュレータ用素子31のグランド端子は、導電性ビアホール231Pを介して内部グランド電極221Pに接続されている。内部グランド電極221Pは導電性ビアホール241Pを介して内部グランド電極222Pに接続されている。内部グランド電極222Pは、導電性ビアホール251Pを介して、積層体20Pの裏面に形成された外部グランド接続端子211Pに接続されている。

【0007】

このように、従来の電源制御回路モジュール10Pは、複数のスイッチングレギュレータ用素子31とリニアレギュレータ用素子32とが同じ内部グランド電極221Pに接続されており、スイッチングレギュレータ用素子31で発生するノイズがリニアレギュレータ用素子32に伝搬されないように、各素子が所定の間隔DPをおいて配置されている。もし、この間隔DPよりも短い間隔で各素子を配置すると、スイッチングレギュレータ用素子31間のノイズによる干渉、およびスイッチングレギュレータ用素子31からリニアレギュレータ用素子32へのノイズによる干渉によって、電源制御回路モジュールが出力電圧を安定して制御できなくなる可能性がある。

【0008】

このため、従来の電源制御回路モジュール10Pでは、この間隔DPを必ず保持しなければならない。これにより、積層体20Pの小型化は容易ではなく、この積層体20Pを含む電源制御回路モジュール10Pの小型化も容易ではない。

【0009】

したがって、本発明の目的は、電源制御の特性を低下させることなく、より小型な電源制御回路モジュールを提供することにある。

【課題を解決するための手段】

【0010】

この発明の電源制御回路モジュールは、次の構成を備えることを特徴としている。電源制御回路モジュールは、複数の誘電体層を積層してなる積層体と、該積層体の表面に実装され、スイッチングレギュレータ用素子を含む複数のレギュレータ用素子とを備える。電源制御回路モジュールは、複数のレギュレータ用素子が接続し、積層体の内部の所定誘電体層の略全面に形成された第1内部グランド電極と、この第1内部グランド電極に接続し、積層体の裏面に形成された第1外部グランド接続端子とを備える。この電源制御回路モジュールの第1内部グランド電極は、レギュレータ素子毎に、電気的に分割されている。この分割された第1内部グランド電極を構成する各個別電極は、それぞれ異なる第1外部グランド接続端子へ接続されている。

【0011】

この構成では、各レギュレータ素子のグランドが積層体内で接続されないため、各レギュレータ素子間のアイソレーションが高くなる。これにより、互いにノイズを発生しやすい複数のスイッチングレギュレータ用素子間のノイズ干渉や、スイッチングレギュレータ用素子からリニアレギュレータ用素子へのノイズ干渉が抑圧される。そして、各個別電極間が電極非形成部によって離間されるため、従来の構成よりも素子間隔を狭くしても、素子間のアイソレーションを十分に確保できる。

【0012】

また、この発明の電源制御回路モジュールは次の構成を備えることが好ましい。電源制御回路モジュールは、積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子と、第1内部グランド電極とは異なる誘電体層の略全面に形成された第2内部グランド電極と、この第2内部グランド電極に接続し、積層体の裏面に形成された第2外部グランド接続端子と、を備える。そして、外部ノイズの影響を受けやすい回路素子は、第2内部グランド電極に接続されている。

【0013】

この構成では、ノイズを発生しやすいスイッチングレギュレータ用素子を含む複数のレギュレータ用素子は、積層体の表面に実装され、外部ノイズの影響を受けやすい回路素子は積層体の裏面に実装される。さらに、積層体の表面に実装されるレギュレータ用素子と、積層体の裏面に実装される素子とで、接続される内部グランド電極が異なる。これにより、積層体の表面に実装されるレギュレータ用素子と、積層体の裏面に実装される外部ノイズの影響を受けやすい回路素子との間で、高いアイソレーションを実現できる。したがって、積層体の表面に実装されるレギュレータ用素子で発生したノイズは、積層体の裏面に実装されている外部ノイズの影響を受けやすい回路素子に伝搬されることなく、外部ノイズの影響を受けやすい回路素子を保護できる。

【0014】

また、この発明の電源制御回路モジュールでは、次の構成を適用することもできる。積層体の表面に実装されたレギュレータ用素子は、スイッチングレギュレータ用素子である。積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子は、リニアレギュレータ用素子またはデジタルIC素子である。

【0015】

この構成では、ノイズを発生しやすいスイッチングレギュレータ用素子と、ノイズを殆ど発生することなく外部ノイズの影響を受けやすいリニアレギュレータ用素子またはデジタルIC素子とが、積層体の対向する面に実装され、積層体内ではグランド電極も接続しない。したがって、スイッチングレギュレータ用素子が発するノイズが、外部ノイズの影響を受けやすいリニアレギュレータ用素子またはデジタルIC素子に悪影響を及ぼすことを、さらに抑圧できる。

【0016】

また、この発明の電源制御回路モジュールは、次の構成であることが好ましい。電源制御回路モジュールは、複数の第1の導電性ビアホールと、裏面側絶縁性樹脂と、複数の第2の導電性ビアホールと、を備える。第1の導電性ビアホールは、積層体の積層方向に沿って延びる形状からなり、第1内部グランド電極と第1外部グランド接続端子とを接続する。裏面側絶縁性樹脂は、積層体の裏面に形成され、外部ノイズの影響を受けやすい回路素子を覆うように形成されている。第2の導電性ビアホールは、第1の導電性ビアホールに連続するように裏面側絶縁性樹脂に形成されている。複数の第1、第2の導電性ビアホールは、外部ノイズの影響を受けやすい回路素子の実装領域を囲むように、配設されている。

【0017】

この構成では、外部ノイズの影響を受けやすい回路素子が、第1、第2の内部グランド電極、第2の導電性ビアホールによって、周囲の五面が囲まれる。これにより、スイッチングレギュレータ用素子の発するノイズから、外部ノイズの影響を受けやすい回路素子を保護できる。さらに、当該電源制御回路モジュールが実装されるマザー基板は、一般的に、電源制御回路モジュールの実装領域の略全域にグランド電極が形成されている。したがって、これを利用することで、外部ノイズの影響を受けやすい回路素子を三次元的にノイズから保護することができる。

【0018】

また、この発明の電源制御回路モジュールでは、第1、第2の導電性ビアホールは、スイッチングレギュレータ用素子の発するノイズの裏面側絶縁性樹脂での実効波長λNの1/4未満の間隔で配設されていることが好ましい。

【0019】

この構成のように、導電性ビアホールの間隔を決定することで、スイッチングレギュレータ用素子の発するノイズは、確実に遮断され、外部ノイズの影響を受けやすい回路素子まで伝搬されることを防止できる。

【0020】

また、この発明の電源制御回路モジュールは、次の構成であることが好ましい。電源制御回路モジュールを構成する積層体の所定層には、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが形成されている。線状電極パターンは、第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された線状電極パターンを基準に第2のグランド電極と反対側に形成された平面状電極と、によって、囲まれている。

【0021】

この構成では、積層体内に、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンを形成する場合を示している。そして、この構成では、第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された線状電極パターンを基準に第2のグランド電極と反対側に形成された平面状電極によって、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが、ノイズから保護される。

【0022】

また、この発明の電源制御回路モジュールでは、次の構成であることが好ましい。電源制御回路モジュールの積層体の表面には、複数のレギュレータ用素子を内包する形状で且つ電磁波を遮蔽するシールド部材が配設されている。

【0023】

この構成では、積層体の表面に実装されたレギュレータ用素子から発するノイズがシール部材で遮蔽される。これにより、積層体の裏面に実装された外部ノイズの影響を受けやすい回路素子への悪影響を、さらに抑圧できる。

【発明の効果】

【0024】

この発明によれば、電源制御の特性を低下させることなく、従来よりも小型の電源制御回路モジュールを実現することができる。

【図面の簡単な説明】

【0025】

【図1】第1の実施形態に係る電源制御回路モジュール10の構成を示す側面図、および内部グランド電極のパターンの概略形状を示した図である。

【図2】第2の実施形態に係る電源制御回路モジュール10Aの構成を示す側面図である。

【図3】第3の実施形態に係る電源制御回路モジュール10Bの構成を示す側面図である。

【図4】第4の実施形態に係る電源制御回路モジュール10Cの構成を示す側面図である。

【図5】第5の実施形態に係る電源制御回路モジュール10Dの構成を示す側面図である。

【図6】第6の実施形態に係る電源制御回路モジュール10Eの構成を示す側面図である。

【図7】第6の実施形態に係る電源制御回路モジュール10Eをマザー基板61へ実装した状態を示す側面図である。

【図8】第7の実施形態に係る電源制御回路モジュール10Fをマザー基板61へ実装した状態を示す側面図である。

【図9】第8の実施形態に係る電源制御回路モジュール10Gをマザー基板61へ実装した状態を示す側面図である。

【図10】従来の電源制御回路モジュール10Pの構成を示す側面図、および内部グランド電極のパターンの概略形状を示した図である。

【発明を実施するための形態】

【0026】

本発明の第1の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図1(A)は、第1の実施形態に係る電源制御回路モジュール10の構成を示す側面図であり、図1(B)は内部グランド電極のパターンの概略形状を示した図である。なお、本実施形態の電源制御回路モジュール10は、図示する電極パターンの他に電源入力端子や電源出力端子やこれらに接続する配線パターンも備えられているが、以下の説明では、グランド接続する配線パターンのみを図示して説明する。

【0027】

電源制御回路モジュール10は、積層体20、四個のスイッチングレギュレータ用素子31A,31B,31C,31D、一個のリニアレギュレータ用素子32を備える。

【0028】

積層体20は、誘電体層201,202,203,204,205が順次積層されてなる。誘電体層201が最上層となり、誘電体層205が最下層となるように構成される。これにより、誘電体層201の表面が積層体20の表面21となり、誘電体層205の裏面が積層体20の裏面22となる。

【0029】

積層体20の表面21(誘電体層201の表面)には、図示しない実装用ランド電極等が形成されている。積層体20の表面21には、スイッチングレギュレータ用素子31A,31B,31C,31Dと、リニアレギュレータ用素子32が実装されている。これらスイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ用素子32とは、上述の実装用ランド電極に実装されている。また、図示しないが、積層体20の表面21には、各種の受動素子(インダクタ、キャパシタ等)が実装されており、スイッチングレギュレータ用素子31A,31B,31C,31DとともにそれぞれにDC−DCコンバータ回路を構成したり、リニアレギュレータ用素子32とともにLDO(Low Drop Out)レギュレータを構成している。

【0030】

積層体20の誘電体層202,203の界面には、内部グランド電極2211,2212,2213,2214,2215が形成されている。これら内部グランド電極2111,2212,2213,2214,2215は、所定幅のグランド電極非形成部300によって分離されている。電極非形成部300の幅は、例えば、当該積層体20に形成する導電性ビアホールの径よりも若干広く設定されている。言い換えれば、積層体20の製造ばらつきに基づいて、グランド電極非形成部に形成される導電性ビアホールの電極が各内部グランド電極2211,2212,2213,2214,2215に接触しない程度の幅に設定されている。

【0031】

内部グランド電極2211は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Aの実装領域を含むような形状で形成されている。内部グランド電極2211とスイッチングレギュレータ用素子31Aは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2311によって接続されている。内部グランド電極2211は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2411によって、積層体20の裏面22に形成された外部グランド接続端子2111に接続されている。

【0032】

内部グランド電極2212は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Bの実装領域を含むような形状で形成されている。内部グランド電極2212とスイッチングレギュレータ用素子31Bは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2312によって接続されている。内部グランド電極2212は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0033】

内部グランド電極2213は、誘電体層の積層方向に沿って見て、リニアレギュレータ用素子32の実装領域を含むような形状で形成されている。内部グランド電極2213とリニアレギュレータ用素子32は、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2313によって接続されている。内部グランド電極2213は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2413によって、積層体20の裏面22に形成された外部グランド接続端子2113に接続されている。

【0034】

内部グランド電極2214は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Cの実装領域を含むような形状で形成されている。内部グランド電極2214とスイッチングレギュレータ用素子31Cは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール(図示せず)によって接続されている。内部グランド電極2214は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0035】

内部グランド電極2215は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Dの実装領域を含むような形状で形成されている。内部グランド電極2215とスイッチングレギュレータ用素子31Dは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール(図示せず)によって接続されている。内部グランド電極2215は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20の裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0036】

積層体20の誘電体層204,205の界面には、内部グランド電極222が形成されている。内部グランド電極222は、誘電体層204,205の界面の略全面に形成されている。内部グランド電極222には、局所的にグランド電極非形成領域が設けられており、当該グランド電極非形成領域を、内部グランド電極2211,2212,2213,2214,2215と導通する導電性ビアホールが貫通している。内部グランド電極222は、誘電体層205を積層方向に沿って貫通する導電性ビアホール251によって、積層体20の裏面に形成された外部グランド接続端子212に接続されている。なお、内部グランド電極222は、上述のDC−DCコンバータ回路やLDOレギュレータ以外の回路のグランドとして機能するものであり、必要に応じて省略することもできる。

【0037】

このような構成とすることで、スイッチングレギュレータ用素子31A,31B,31C,31D用の内部グランド電極2211,2212,2214,2215と、リニアレギュレータ用素子32用の内部グランド電極2213とが、それぞれ電気的に分離されており、各レギュレータ用素子のグランドが、積層体20内で接続されない。従って、グランド電極を介して、スイッチングレギュレータ用素子31A,31B,31C,31D間およびスイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ32間のノイズの伝搬を抑制できる。

【0038】

このため、スイッチングレギュレータ用素子31A,31B,31C,31Dとリニアレギュレータ用素子32を、従来構成よりも近づけて配置しても(D<DP)、スイッチングレギュレータ用素子31A,31B,31C,31D間でのノイズの相互伝搬や、スイッチングレギュレータ用素子31A,31B,31C,31Dからリニアレギュレータ用素子32へのノイズの伝搬を抑制できる。これにより、電源制御特性を低下させることなく、レギュレータ用素子の配置間隔を狭くすることができ、従来構成よりも小型の電源制御回路モジュールを実現することができる。

【0039】

次に、第2の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図2は、第2の実施形態に係る電源制御回路モジュール10Aの構成を示す側面図である。本実施形態の電源制御回路モジュール10Aは、スイッチングレギュレータ用素子の配置と、リニアレギュレータ用素子の配置とが、第1の実施形態に示した電源制御回路モジュール10と異なるものであり、第1の実施形態と同じ構成箇所は説明を簡略化する。

【0040】

概略的には、本実施形態の電源制御回路モジュール10Aでは、スイッチングレギュレータ用素子31A,31B,31Cは積層体20Aの表面21に実装されている。また、リニアレギュレータ用素子32A,32Bは積層体20Aの裏面22に実装されている。

【0041】

電源制御回路モジュール10Aは、積層体20A、三個のスイッチングレギュレータ用素子31A,31B,31C、二個のリニアレギュレータ用素子32A,32Bを備える。

【0042】

積層体20Aは、誘電体層201,202,203,204,205が順次積層されてなる。誘電体層201が最上層となり、誘電体層205が最下層となるように構成される。これにより、誘電体層201の表面が積層体20の表面21となり、誘電体層205の裏面が積層体20の裏面22となる。

【0043】

積層体20Aの表面21には、スイッチングレギュレータ用素子31A,31B,31Cが実装されている。

【0044】

積層体20Aの誘電体層202,203の界面には、内部グランド電極2211,2212,2213が形成されている。これら内部グランド電極2111,2212,2213は、所定幅のグランド電極非形成部300によって分離されている。

【0045】

内部グランド電極2211は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Aの実装領域を含むような形状で形成されている。内部グランド電極2211とスイッチングレギュレータ用素子31Aは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2311によって接続されている。内部グランド電極2211は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2411によって、積層体20Aの裏面22に形成された外部グランド接続端子2111に接続されている。

【0046】

内部グランド電極2212は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Bの実装領域を含むような形状で形成されている。内部グランド電極2212とスイッチングレギュレータ用素子31Bは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2312によって接続されている。内部グランド電極2212は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール(図示せず)によって、積層体20Aの裏面22に形成された外部グランド接続端子(図示せず)に接続されている。

【0047】

内部グランド電極2213は、誘電体層の積層方向に沿って見て、スイッチングレギュレータ用素子31Cの実装領域を含むような形状で形成されている。内部グランド電極2213とスイッチングレギュレータ用素子31Cは、誘電体層201,202を積層方向に沿って貫通する導電性ビアホール2313によって接続されている。内部グランド電極2213は、誘電体層203,204,205を積層方向に沿って貫通する導電性ビアホール2413によって、積層体20Aの裏面22に形成された外部グランド接続端子2113に接続されている。

【0048】

積層体20Aの裏面22には、リニアレギュレータ用素子32A,32Bが実装されている。

【0049】

積層体20の誘電体層204,205の界面には、内部グランド電極222が形成されている。内部グランド電極222は、誘電体層204,205の界面の略全面に形成されている。

【0050】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261Aによって、リニアレギュレータ用素子32Aへ接続されている。内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261Bによって、リニアレギュレータ用素子32Bへ接続されている。

【0051】

内部グランド電極222には、局所的にグランド電極非形成領域が設けられており、当該グランド電極非形成領域を、内部グランド電極2211,2212,2213と導通する導電性ビアホールが貫通している。なお、図には内部グランド電極2212に接続する導電性ビアホールおよびグランド電極非形成領域は図示されていないが実際には設けられている。

【0052】

内部グランド電極222は、誘電体層205を積層方向に沿って貫通する導電性ビアホール251によって、積層体20の裏面に形成された外部グランド接続端子212に接続されている。

【0053】

積層体20Aの裏面22の全面には、リニアレギュレータ用素子32A,32Bが埋まり込む厚みで絶縁性樹脂42が配設されている。絶縁性樹脂42における積層体20Aと反対側の面(以下、絶縁性樹脂42の裏面と称する。)には、上述の積層体20Aの裏面に形成された各外部グランド接続端子を含む各端子に接続する外部接続用端子が形成されている。

【0054】

例えば、絶縁性樹脂42の裏面形成された外部接続端子2811は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材2611によって、外部グランド接続端子2111に接続されている。絶縁性樹脂42の裏面形成された外部接続端子2813は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材2613によって、外部グランド接続端子2113に接続されている。絶縁性樹脂42の裏面形成された外部接続端子282は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性部材271によって、外部グランド接続端子212に接続されている。なお、導電性部材としては、例えば、導電性ビアホールや金属のピンを使用することができる。

【0055】

このような構成とすることで、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32A,32Bとが、積層体20Aの異なる面に実装される。特に、本実施形態の構成では、積層体20Aを介した両面(表面21と裏面22)にそれぞれ実装される。これにより、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32A,32Bは、近接しない。また、スイッチングレギュレータ用素子31A,31B,31C用の内部グランド電極2211,2212,2213と、リニアレギュレータ用素子32A,32B用の内部グランド電極222とが、それぞれ電気的に分離されており、各レギュレータ用素子のグランドが、積層体20内で接続されない。

【0056】

このため、スイッチングレギュレータ用素子31A,31B,31Cとリニアレギュレータ用素子32A,32Bとの間のアイソレーションをより高くすることができ、より確実に、ノイズの干渉による電源制御特性の低下を防止できる。さらに、積層体20Aの両面に実装することで、同じ数のレギュレータ用素子を積層体の表面のみに実装するよりも、小面積化が可能になる。逆に言えば、同じ面積の積層体を用いて、より多数のレギュレータを備える電源制御回路モジュールを実現することができる。

【0057】

次に、第3の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図3は、第3の実施形態に係る電源制御回路モジュール10Bの構成を示す側面図である。本実施形態の電源制御回路モジュール10Bは、第2の実施形態に係る電源制御回路モジュール10Aに対して、さらに、積層体20Bの表面側に絶縁性樹脂41とシールド部材51とを備えたものであり、他の構成は第2の実施形態に係る電源制御回路モジュール10Aと同じである。したがって、以下では異なる箇所のみを説明する。

【0058】

積層体20Bの表面21の全面には、スイッチングレギュレータ用素子31A,31B,31Cが埋まり込む厚みで絶縁性樹脂41が配設されている。さらに絶縁性樹脂41を覆うように、蓋状のシールド部材51が配設されている。シールド部材51は、金属等の導電性材料からなる。

【0059】

なお、この際、積層体20Bの表面21側となる誘電体層201B,202Bは、電源制御回路モジュールの低背化のために、外周が削られていてもよい。そして、シールド部材51は、誘電体層201B,202Bも覆うように配設されている。

【0060】

シールド部材51は、内部グランド電極2211,2213等に接続されている。これにより、シールド部材51は、グランドに接続される。

【0061】

このような構成とすることで、上述の第2の実施形態に示した効果とともに、スイッチングレギュレータ用素子31A,31B,31Cが動作することによって放射されるノイズがシールド部材51で遮断されて、外部に放射されない。また、絶縁性樹脂42およびシールド部材51を介して、スイッチングレギュレータ用素子31A,31B,31Cで発生した熱が効果的に外部へ放射されるため、放熱性の高い電源制御回路モジュールを実現することができる。特に、熱伝導率が高い絶縁性樹脂を用いれば、より放熱性の高い電源制御回路モジュールを実現することができる。

【0062】

なお、スイッチングレギュレータ用素子から外部へ放射されるノイズは、スイッチングレギュレータ用素子に接続する内部グランド電極に漏洩するノイズと比較して、十分に小さい。このため、シールド部材51に伝搬するノイズは極小さい。さらに、シールド部材51は積層体の外部グランド接続端子に接続されている。したがって、複数のスイッチングレギュレータ用素子のそれぞれが発したノイズがシールド部材51に伝搬されても、相互に悪影響を与えることはない。

【0063】

以上のように、本実施形態の構成を用いれば、より信頼性の高い電源制御回路モジュールを実現することができる。

【0064】

次に、第4の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図4は、第4の実施形態に係る電源制御回路モジュール10Cの構成を示す側面図である。本実施形態の電源制御回路モジュール10Cは、第3の実施形態に係るモジュール10Bにおけるリニアレギュレータ用素子32A,32Bに替えて、積層体20Cの裏面22に、デジタルIC50を実装したものである。したがって、以下では、第3の実施形態の電源制御回路モジュール10Bと異なる箇所のみを具体的に説明する。

【0065】

積層体20Cの裏面22には、デジタルIC50が実装されている。デジタルICとは、例えば、シリアルインターフェース制御用IC、USB制御用IC、論理IC、マイクロプロセッサ、オーディオIC、およびビデオIC等のデジタル信号で制御等を行うICである。

【0066】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール262によって、デジタルIC50へ接続されている。

【0067】

内部グランド電極222は、誘電体層205を積層方向に沿って貫通する複数の導電性ビアホール251によって、積層体20の裏面に形成された複数の外部グランド接続端子212に接続されている。

【0068】

積層体20Cの裏面22の全面には、デジタルICが埋まり込む厚みで絶縁性樹脂42が配設されている。絶縁性樹脂42における積層体20Cと反対側の面(以下、絶縁性樹脂42の裏面と称する。)には、上述の積層体20Cの裏面に形成された各外部グランド接続端子を含む各端子に接続する外部接続用端子が形成されている。

【0069】

例えば、絶縁性樹脂42の裏面形成された外部接続端子2811は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性ビアホール2611によって、外部グランド接続端子2111に接続されている。絶縁性樹脂42の裏面形成された外部接続端子2813は、絶縁性樹脂42の厚み方向を貫通するように形成された導電性ビアホール2613によって、外部グランド接続端子2113に接続されている。絶縁性樹脂42の裏面形成された複数の外部接続端子282は、絶縁性樹脂42の厚み方向を貫通するように形成された複数の導電性部材271によって、それぞれに対応する外部グランド接続端子212に接続されている。

【0070】

このような構成とすることで、ノイズを発生するスイッチングレギュレータ用素子31A,31B,31Cと、ノイズの影響を受けやすいデジタルIC50とが積層体20Cの異なる面に配設される。特に、本実施形態の構成では、積層体20Cを介した両面(表面21と裏面22)にそれぞれ実装される。このため、スイッチングレギュレータ用素子31A,31B,31CとデジタルIC50は、近接しない。また、スイッチングレギュレータ用素子31A,31B,31Cで発生するノイズは、シールド部材51によって遮断され、外部へ放射されない。したがって、スイッチングレギュレータ用素子31A,31B,31Cで発生したノイズは、デジタルIC50へ伝搬されない。これにより、デジタルIC50は、安定して動作する。

【0071】

なお、本実施形態に説明では、積層体20Cの表面21に、スイッチングレギュレータ用素子のみを配置する例を示したが、第1の実施形態に示したように、スイッチングレギュレータ用素子とリニアレギュレータ用素子とを積層体20Cの表面21に実装してもよい。

【0072】

次に、第5の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図5は、第5の実施形態に係る電源制御回路モジュール10Dの構成を示す側面図である。

【0073】

本実施形態の電源制御回路モジュール10Dは、第4の実施形態に係るモジュール10CがデジタルIC50のみを実装しているのに対して、積層体20Dの裏面22に、リニアレギュレータ用素子32とデジタルIC50を実装したものである。したがって、以下では、第4の実施形態の電源制御回路モジュール10Cと異なる箇所のみを具体的に説明する。

【0074】

積層体20Dの裏面22には、リニアレギュレータ用素子32とデジタルIC50が実装されている。

【0075】

内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール261によって、リニアレギュレータ用素子32へ接続されている。内部グランド電極222は、誘電体層205を積層方向に貫通する導電性ビアホール262によって、デジタルIC50へ接続されている。

【0076】

このような構成とすることで、ノイズを発生するスイッチングレギュレータ用素子31A,31B,31Cと、ノイズの影響を受けやすいリニアレギュレータ用素子32およびデジタルIC50とが積層体20Dの異なる面に配設される。特に、本実施形態の構成では、積層体20Dを介した両面(表面21と裏面22)にそれぞれ実装される。このため、スイッチングレギュレータ用素子31A,31B,31Cと、リニアレギュレータ用素子32およびデジタルIC50は、近接しない。また、スイッチングレギュレータ用素子31A,31B,31Cで発生するノイズは、シールド部材51によって遮断され、外部へ放射されない。したがって、スイッチングレギュレータ用素子31A,31B,31Cで発生したノイズは、リニアレギュレータ用素子32およびデジタルIC50へ伝搬されない。これにより、リニアレギュレータ用素子32とデジタルIC50は、安定して動作する。

【0077】

なお、本実施形態の構成では、リニアレギュレータ用素子32とデジタルIC50とが同じ内部グランド電極222に接続されているが、リニアレギュレータ用素子32はノイズを殆ど発生しないため、デジタルIC50に与える悪影響はない。ただし、リニアレギュレータ用素子32とデジタルIC50とを異なる内部グランド電極222に接続してもよい。

【0078】

次に、第6の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図6(A)は、第6の実施形態に係る電源制御回路モジュール10Eの構成を示す側面図であり、図6(B)は、積層体20Eの裏面22から見た導電性ビアホールの配置パターンを示す図である。

【0079】

本実施形態の電源制御回路モジュール10Eは、第2の実施形態に係る電源制御回路モジュール10Aに対して、導電性ビアホールの形成パターンが異なるものであり、他の構成は同じである。したがって、導電性ビアホールの形成パターンに関する箇所のみを説明する。

【0080】

積層体20Eの最下層である誘電体層205には、図6(B)に示すように、外周に沿って、複数の導電性ビアホールが所定間隔で配列形成されている。これらの導電性ビアホールは、外部グランド接続端子を含む各種の外部接続端子へ接続される。導電性ビアホールは、外周に沿って二列で配列形成されている。

【0081】

絶縁性樹脂42には、これらの積層体20Eに形成された導電性ビアホールに連続するように、これらの導電性ビアホールと同じ間隔で、絶縁性樹脂42を厚み方向に貫通する導電性ビアホールが形成されている。

【0082】

外周側(積層体20Eの側面に近い側)の導電性ビアホール群内には、内部グランド電極2211,2212,2213に接続する複数の導電性ビアホール241Gが含まれている。内周側(積層体20Eの側面に離れた側)の導電性ビアホール群内には、内部グランド電極222に接続する複数の導電性ビアホール251Gが含まれている。このような構成において、積層体20Eの側面に沿った隣り合う導電性ビアホール241Gは、間隔PG1で形成されている。積層体20Eの角部において隣り合う導電性ビアホール241Gは、間隔PG2で形成されている。

【0083】

間隔PG1,PG2は、絶縁性樹脂42の誘電率を加味した上で、スイッチングレギュレータ用素子31A,31B,31Cが発するノイズが絶縁性樹脂42を伝搬する実効波長をλNとして、λN/4未満の長さになるように設定されている。

【0084】

絶縁性樹脂42には、導電性ビアホール241Gに連続する導電性部材261Gが形成されている。これにより、導電性部材261Gは、間隔PG1もしくは間隔PG2で形成されることになる。したがって、導電性部材261Gもスイッチングレギュレータ用素子31A,31B,31Cが発するノイズの実効波長λNの1/4(λN/4)未満の間隔で形成されることになる。これにより、スイッチングレギュレータ用素子31A,31B,31Cから生じ、積層体20Eの側面から裏面21に回り込んだノイズは、絶縁性樹脂42に形成された導電性部材261Gでトラップされる。したがって、リニアレギュレータ用素子32A,32Bへノイズが伝搬されることを、より効果的に抑圧できる。さらに、この構成とすることで、外部からのノイズがリニアレギュレータ用素子32A,32Bに伝搬されることも抑制できる。

【0085】

さらに、内周側に設けた複数の導電性ビアホール251Gの間隔をλN/4未満にするとよりよい。これにより、複数の導電性ビアホール251Gに接続する絶縁性樹脂42に形成された導電性部材271Gの間隔がλN/4未満になる。これにより、ノイズに対する二重のトラップを構成することも可能である。

【0086】

なお、外周側に導電性ビアホール251Gを含み、内周側に導電性ビアホール241Gを含むようにしてもよい。また、外周側、内周側で、それぞれ導電性ビアホール241G,251Gを含むようにしてもよい。しかしながら、導電性ビアホール241Gは、リニアレギュレータ用素子32A,32Bに接続する内部グランド電極222に接続するため、上述のように、導電性ビアホール241Gは内周側のみにある方が望ましい。

【0087】

このような構成からなる電源制御回路モジュール10Eは、図7に示すように、グランド電極62を有するマザー基板61に実装される。図7は、第6の実施形態に係る電源制御回路モジュール10Eをマザー基板61へ実装した状態を示す側面図である。

【0088】

図7に示すように、電源制御回路モジュール10Eの導電性ビアホール241G(導電性部材261G)、導電性ビアホール251G(導電性部材271G)に接続する外部接続端子281G,282Gは、マザー基板61に形成された導電性ビアホール631G,632Gを介して、マザー基板61のグランド電極62に接続されている。マザー基板61における電源制御回路モジュールが実装される領域には、図7に示すように略全面に亘る形状のグランド電極62が形成される。

【0089】

このような構成により、マザー基板61に実装された状態で、電源制御回路モジュール10Eのリニアレギュレータ用素子32A,32Bの積層体20Eと反対側の面は、マザー基板61のグランド電極62で、全面に覆われる。したがって、このグランド電極62によっても、リニアレギュレータ用素子32A,32Bへのノイズの伝搬は抑圧される。

【0090】

以上のように、本実施形態の構成を用いることで、リニアレギュレータ用素子32A,32Bは、積層体20E内の内部グランド電極、これに接続する導電性ビアホール群、およびマザー基板61のグランド電極62によって、スイッチングレギュレータ用素子31A,31B,31Cの発生するノイズに対して、三次元的にシールドされる。これにより、電源制御特性の低下を、より確実に防ぐことができる。

【0091】

次に、第7の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図8は、第7の実施形態に係る電源制御回路モジュール10Fをマザー基板61へ実装した状態を示す側面図である。本実施形態の電源制御回路モジュール10Fは、第6の実施形態に示した電源制御回路モジュール10Eの導電性ビアホールの構成を有しながら、さらに、第3の実施形態に係る電源制御回路モジュール10Bと同様に、積層体20Fの表面21にシールド部材51を配置したものである。

【0092】

このような構成とすることで、より一層、ノイズに対するシールド性が高い電源制御回路モジュールを実現することができる。

【0093】

次に、第8の実施形態に係る電源制御回路モジュールについて、図を参照して説明する。図9は、第8の実施形態に係る電源制御回路モジュール10Gをマザー基板61へ実装した状態を示す側面図である。

【0094】

本実施形態の電源制御回路モジュール10Gは、第7の実施形態に係る電源制御回路モジュール10Fに対して、中間層の誘電体層206が増加し、デジタル信号が伝搬される内部パターン電極がさらに形成された場合を示している。したがって、異なる箇所のみを説明する。

【0095】

上述の各実施形態に示した誘電体層203、204間には、誘電体層206が備えられている。

【0096】

誘電体層203、206の界面には、内部グランド電極223が形成されている。誘電体層206、204の界面には、デジタル信号用の線状電極パターン290が形成されている。

【0097】

誘電体層206,204には、線状電極パターン290の形成領域を囲むように、所定間隔で、複数の導電性ビアホール291が形成されている。複数の導電性ビアホール291は、内部グランド電極222,223に接続されている。これら複数の導電性ビアホール291は、上述のλN/4未満の間隔で配列形成されている。

【0098】

このような構成とすることで、線状電極パターン290は、内部グランド電極222,223、複数の導電性ビアホール291によって、スイッチングレギュレータ用素子31A,31B,31Cの発生するノイズに対して、三次元的にシールドされる。これにより、デジタル信号にノイズが重畳することを防止でき、電源制御特性の低下を、より確実に防ぐことができる。

【0099】

なお、上述の各実施形態において、シールド部材51を用いる場合においては、当該シールド部材51に替えて、絶縁性樹脂41に、複数の導電性ビアホールを設け、絶縁性樹脂41の表面の略全面に平膜状の電極パターンを形成するようにしてもよい。この場合、複数の導電性ビアホールは、絶縁性樹脂41の外周に沿って形成すればよく、配置間隔はλN/4にする。複数の導電性ビアホールは、絶縁性樹脂41の表面に形成された平膜状の電極パターンに接続させるとともに、スイッチングレギュレータ用素子に接続する内部グランド電極に接続させる。

【0100】

また、上述の実施形態におけるデジタルICを用いる実施形態は、デジタルICに替えて、オーディオIC、RF回路を構成する素子群、センサ周辺回路を構成する素子群、水晶等の振動子、プロセッサ等の外部ノイズに弱い電子部品を用いる態様へ適用することもできる。

【0101】

また、さらに、上述の各実施形態では、積層体の一方面に実装されるレギュレータ用素子として、個別に実装する素子を例に説明したが、複数のレギュレータ素子が一つのチップ内に搭載された複合レギュレータICを用いた場合にも、上述の実施形態の構成を適用することができる。

【符号の説明】

【0102】

10,10A,10B,10C,10D,10E,10F,10G,10P:電源制御回路モジュール、

20,20A,20B,20C,20D,20E,20F,20G,20P:積層体、21:表面、22:裏面、

31,31A,31B,31C,31D:スイッチングレギュレータ用素子、32,32A,32B:リニアレギュレータ用素子、

41,42:絶縁性樹脂、

50:デジタルIC、

51:シールド部材、

61:マザー基板、

62:グランド電極、

201−205,201B,202B,201C,202C,201D,202D,201F,202F,201P−205P:誘電体層、

2111,2113,212,211P:外部グランド接続端子、

2311,2312,2313,2411,2413,251,261A,261B,2811,2813,231P,241P,251P,241G,251G,631G,632G:導電性ビアホール、

2611,2613,271,261G,271G:導電性部材、

2211−2215,222,223,221P,222P:内部グランド電極、

300:グランド電極非形成部、

2811,2813,282,281G,282G:外部接続端子、

290:線状電極パターン

【特許請求の範囲】

【請求項1】

複数の誘電体層を積層してなる積層体と、

該積層体の表面に実装され、スイッチングレギュレータ用素子を含む複数のレギュレータ用素子と、

前記複数のレギュレータ用素子が接続し、前記積層体の内部の所定誘電体層の略全面に形成された第1内部グランド電極と、

該第1内部グランド電極に接続し、前記積層体の裏面に形成された第1外部グランド接続端子と、

を備え、

前記第1内部グランド電極は、前記レギュレータ素子毎に、電気的に分割されており、

分割された第1内部グランド電極の個別電極は、それぞれ異なる第1外部グランド接続端子へ接続されている、電源制御回路モジュール。

【請求項2】

前記積層体の裏面に実装された、外部ノイズの影響を受けやすい回路素子と、

前記第1内部グランド電極とは異なる誘電体層の略全面に形成された第2内部グランド電極と、

該第2内部グランド電極に接続し、前記積層体の裏面に形成された第2外部グランド接続端子と、

を備え、

前記外部ノイズの影響を受けやすい回路素子は、前記第2内部グランド電極に接続されている、請求項1に記載の電源制御回路モジュール。

【請求項3】

前記積層体の表面に実装されたレギュレータ用素子は、スイッチングレギュレータ用素子である、請求項2に記載の電源制御回路モジュール。

【請求項4】

前記積層体の積層方向に沿って延びる形状からなり、前記第1内部グランド電極と前記第1外部グランド接続端子とを接続する複数の第1の導電性ビアホールと、

前記積層体の裏面に形成され、前記外部ノイズの影響を受けやすい回路素子を覆うように形成された裏面側絶縁性樹脂と、

前記複数の第1の導電性ビアホールに連続するように前記裏面側絶縁性樹脂に形成された複数の第2の導電性ビアホールと、を備え、

前記複数の第1、第2の導電性ビアホールは、前記外部ノイズの影響を受けやすい回路素子の実装領域を囲むように、配設されている、請求項2または請求項3に記載の電源制御回路モジュール。

【請求項5】

前記第1、第2の導電性ビアホールは、前記スイッチングレギュレータ用素子の発するノイズの前記裏面側絶縁性樹脂での実効波長λNの1/4未満の間隔で配設されている、請求項4に記載の電源制御回路モジュール。

【請求項6】

前記積層体の所定層には、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが形成されており、

該線状電極パターンは、前記第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された前記線状電極パターンを基準に前記第2のグランド電極と反対側に形成された平面状電極と、によって、囲まれている、請求項2乃至請求項5の何れか一項に記載の電源制御回路モジュール。

【請求項7】

前記積層体の表面には、前記複数のレギュレータ用素子を内包する形状で且つ電磁波を遮蔽するシールド部材が配設されている、請求項1乃至請求項6の何れか一項に記載の電源制御回路モジュール。

【請求項1】

複数の誘電体層を積層してなる積層体と、

該積層体の表面に実装され、スイッチングレギュレータ用素子を含む複数のレギュレータ用素子と、

前記複数のレギュレータ用素子が接続し、前記積層体の内部の所定誘電体層の略全面に形成された第1内部グランド電極と、

該第1内部グランド電極に接続し、前記積層体の裏面に形成された第1外部グランド接続端子と、

を備え、

前記第1内部グランド電極は、前記レギュレータ素子毎に、電気的に分割されており、

分割された第1内部グランド電極の個別電極は、それぞれ異なる第1外部グランド接続端子へ接続されている、電源制御回路モジュール。

【請求項2】

前記積層体の裏面に実装された、外部ノイズの影響を受けやすい回路素子と、

前記第1内部グランド電極とは異なる誘電体層の略全面に形成された第2内部グランド電極と、

該第2内部グランド電極に接続し、前記積層体の裏面に形成された第2外部グランド接続端子と、

を備え、

前記外部ノイズの影響を受けやすい回路素子は、前記第2内部グランド電極に接続されている、請求項1に記載の電源制御回路モジュール。

【請求項3】

前記積層体の表面に実装されたレギュレータ用素子は、スイッチングレギュレータ用素子である、請求項2に記載の電源制御回路モジュール。

【請求項4】

前記積層体の積層方向に沿って延びる形状からなり、前記第1内部グランド電極と前記第1外部グランド接続端子とを接続する複数の第1の導電性ビアホールと、

前記積層体の裏面に形成され、前記外部ノイズの影響を受けやすい回路素子を覆うように形成された裏面側絶縁性樹脂と、

前記複数の第1の導電性ビアホールに連続するように前記裏面側絶縁性樹脂に形成された複数の第2の導電性ビアホールと、を備え、

前記複数の第1、第2の導電性ビアホールは、前記外部ノイズの影響を受けやすい回路素子の実装領域を囲むように、配設されている、請求項2または請求項3に記載の電源制御回路モジュール。

【請求項5】

前記第1、第2の導電性ビアホールは、前記スイッチングレギュレータ用素子の発するノイズの前記裏面側絶縁性樹脂での実効波長λNの1/4未満の間隔で配設されている、請求項4に記載の電源制御回路モジュール。

【請求項6】

前記積層体の所定層には、外部ノイズの影響を受けやすい信号が伝送される線状電極パターンが形成されており、

該線状電極パターンは、前記第2のグランド電極と、当該第2のグランド電極に接続された複数の導電性ビアホールと、該導電性ビアホールによって接続された前記線状電極パターンを基準に前記第2のグランド電極と反対側に形成された平面状電極と、によって、囲まれている、請求項2乃至請求項5の何れか一項に記載の電源制御回路モジュール。

【請求項7】

前記積層体の表面には、前記複数のレギュレータ用素子を内包する形状で且つ電磁波を遮蔽するシールド部材が配設されている、請求項1乃至請求項6の何れか一項に記載の電源制御回路モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−59220(P2013−59220A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−196611(P2011−196611)

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月9日(2011.9.9)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]