電源制御回路

【課題】 複数の電源を切り換えて使用する機器において、いずれの電源を使用する場合でも電源電圧の降下を防止する。

【解決手段】 この電源制御回路は、複数の入力端子に接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタQP1〜QP3と、複数の入力端子における電位を比較して、比較結果を表す比較信号を出力する比較回路11〜13と、比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路100とを具備する。

【解決手段】 この電源制御回路は、複数の入力端子に接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタQP1〜QP3と、複数の入力端子における電位を比較して、比較結果を表す比較信号を出力する比較回路11〜13と、比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路100とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の電源を切り換えて使用する機器において、電源の切換えを制御する電源制御回路に関する。

【背景技術】

【0002】

持ち運びが可能な光ディスクプレーヤ等の携帯機器においては、バッテリで駆動する場合の他に、ACアダプタやUSB(ユニバーサル・シリアル・バス)等の電源ラインに接続して駆動することができるように設計されているものが多い。そのような機器に複数の電源が接続された場合には、例えば、最も高い電圧を有する電源を使用することが行われている。その際に、電流が逆流するのを防止するダイオードスイッチが使用されることが多いが、ダイオードスイッチを使用する場合には、ダイオードの順方向電圧(通常は、約0.6V)だけ、電源電圧が低下してしまうという問題がある。

【0003】

あるいは、予め定められた優先順位に従って、複数の電源の中から1つの電源を選択して使用することも考えられる。その場合には、電源の切換えの際に電源電圧が低下する期間がなるべく短くなるようにすることが望ましい。

【0004】

関連する技術として、下記の特許文献1には、外部電源用の遅延手段と、バッテリ用の逆流防止用ダイオードに並列接続したリレースイッチとを備え、逆流防止用ダイオードの順方向バイアス電圧による電圧降下と電力損失を無くしてバッテリ使用の長時間化を図ることのできる電源切替装置が開示されている。この電源切替装置は、外部電源に接続される遅延手段及び電圧検出手段と、遅延手段と出力端子との間に接続された第1のダイオードと、バッテリの正極と出力端子との間に並列接続されたリレースイッチ及び第2のダイオードとを備え、電圧検出手段が、遅延する前の外部電源の電圧値を検出して、該電圧値に応じてリレースイッチを開閉する。

【0005】

この電源切替装置においては、外部電源から所定の電圧が出力されていない場合に、リレースイッチを閉じることにより、電源として使用するバッテリに接続された第2のダイオードによる電圧降下を防止することができる。しかしながら、電源として外部電源を使用する場合においては、第1のダイオードによる電圧降下を防止することはできない。もし、外部電源と出力端子との間に第2のリレースイッチを設けるとしたら、バッテリと外部電源とがショートしないように対策を立てる必要がある。また、リレースイッチを用いることにより、機器が大型化してしまう。

【特許文献1】特開平10−336912号公報(第1〜2頁、図1)

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、上記の点に鑑み、本発明の第1の目的は、複数の電源を切り換えて使用する機器において、いずれの電源を使用する場合でも電源電圧の降下を防止することである。また、本発明の第2の目的は、予め定められた優先順位に従って複数の電源の中から1つの電源を選択して使用する機器において、電源の切換えの際に電源電圧が低下する期間がなるべく短くなるようにすることである。

【課題を解決するための手段】

【0007】

以上の課題を解決するため、本発明の第1の観点に係る電源制御回路は、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、複数の入力端子に接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタと、複数の入力端子における電位を比較して、比較結果を表す少なくとも1つの比較信号を出力する少なくとも1つの比較回路と、少なくとも1つの比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路とを具備する。

【0008】

ここで、複数のMOSトランジスタの各々は、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。

【0009】

さらに、判定回路は、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されてから、所定の遅延を伴って、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力するようにしても良い。

【0010】

また、本発明の第2の観点に係る電源制御回路は、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、複数の入力端子に接続されたそれぞれのソースを有し、バックゲートがソースに接続された複数の第1のMOSトランジスタと、複数の第1のMOSトランジスタのドレインに接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数の第2のMOSトランジスタと、出力端子に供給される電源電位に基づいて、複数の第1のMOSトランジスタのゲート電位をそれぞれ生成する複数のゲート電位生成回路と、複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する複数の検出回路と、複数の入力端子における電位を出力端子における電位と比較して、比較結果を表す複数の比較信号をそれぞれ出力する複数の比較回路と、複数の検出回路から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、複数の第2のMOSトランジスタをオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、出力端子の電位が優先順位の高い電源の電位よりも低下したことを確認した後に、優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせるゲート電位を出力する判定回路とを具備する。

【0011】

ここで、複数の第1のMOSトランジスタの各々は、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有し、複数の第2のMOSトランジスタの各々は、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。

【0012】

さらに、判定回路は、優先順位が最も高い電源に接続されている第1のMOSトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、複数のゲート電位生成回路に供給される複数の制御信号を生成するようにしても良い。

【発明の効果】

【0013】

本発明の第1の観点によれば、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタがオフしていることを確認して複数の電源間がショートされることを防止すると共に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせることにより、いずれの電源を使用する場合でも電源電圧の降下を防止することができる。

【0014】

また、本発明の第2の観点によれば、電源電位が印加されている入力端子を判定し、現在接続されている電源よりも優先順位の高い電源が接続された場合に、全ての第2のMOSトランジスタを一旦オフさせて、出力端子の電位が優先順位の高い電源の電位よりも低下したことを確認した後に、優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせることにより、電源の切換えの際に電源電圧が低下する期間をなるべく短くなるようにすることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら詳しく説明する。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

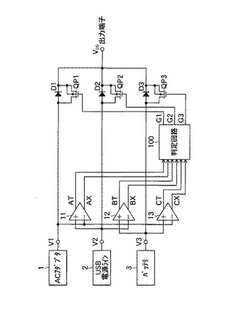

図1は、本発明の第1の実施形態に係る電源制御回路の構成を示す図である。この電源制御回路は、半導体集積回路内に形成され、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位VDDを供給する。本実施形態においては、複数の電源として、ACアダプタ1とUSB電源ライン2とバッテリ3とが複数の入力端子にそれぞれ接続されており、これらの電源の内で最も電位の高い電源が選択される。

【0016】

図1に示すように、電源制御回路は、複数の入力端子と出力端子との間にソース・ドレインが接続されたPチャネルMOSトランジスタQP1〜QP3と、複数の入力端子における電位V1〜V3を比較して比較信号を出力する比較回路11〜13と、比較信号に基づいてトランジスタQP1〜QP3のゲート電位G1〜G3を出力する判定回路100とを有している。

【0017】

図2は、本実施形態において用いられるPチャネルMOSトランジスタQP1〜QP3の構造を示す半導体集積回路の断面図である。図2に示すように、P型の半導体基板201内にNウエル202が形成されており、Nウエル202が形成された半導体基板201の所定の領域上に、ゲート絶縁膜203及びゲート電極204を含むゲートが形成されている。また、ゲートの両側の半導体基板201内には、ソースとなるP型の不純物拡散領域205と、ドレインとなるP型の不純物拡散領域206とが形成されている。なお、N型の半導体基板を用いる場合には、Nウエルを形成せずに、N型の半導体基板内にP型の不純物拡散領域を直接形成しても良い。また、PチャネルMOSトランジスタの替わりにNチャネルMOSトランジスタを用いる場合には、P型の半導体基板又はPウエル内にNチャネルMOSトランジスタを形成すれば良い。

【0018】

図2に示すように、PチャネルMOSトランジスタQP1〜QP3においては、P型の不純物拡散領域205及び206とNウエル202との間のPN接合によって、2つの寄生ダイオードが形成されている。ここで、バックゲートとなるNウエル202が、ドレインとなる不純物拡散領域206に接続されているので、ソース・ドレイン間に電気的に接続されたアノード・カソードを有するダイオードが、等価的に発生することになる。このダイオードは、図1において、ダイオードD1〜D3として示されている。

【0019】

再び図1を参照すると、ACアダプタ1の電位V1とUSB電源ライン2の電位V2とバッテリ3の電位V3との内で最も高い電位によって、ダイオードD1〜D3のいずれかがオンして、出力端子に電源電位VDDが供給される。ただし、この段階においては、ダイオードの順方向電圧(通常は、約0.6V)だけ、電源電位VDDが低下している。この電源電位VDDは、電源制御回路の各部に供給されて、各部が動作を開始する。

【0020】

比較回路11〜13は、例えばオペアンプによって構成され、複数の入力端子における電位を比較して、比較結果を表す比較信号AT〜CT及びAX〜CXを出力する。ここで、比較信号AX〜CXは、比較信号AT〜CTをそれぞれ反転した信号である。これらの比較信号に基づいて、判定回路100は、最も高い電源電位が印加されている入力端子を判定し、最も高い電源電位が印加されている入力端子に接続されたトランジスタをオンさせるゲート電位を出力すると共に、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位を出力する。

【0021】

図3は、図1に示す判定回路の具体例を示す回路図である。図3に示す判定回路100は、最も高い電源電位が電源電位V1であるときにハイレベルの信号を出力するNOR回路111と、最も高い電源電位が電源電位V2であるときにローレベルの信号を出力するNAND回路112と、最も高い電源電位が電源電位V3であるときにローレベルの信号を出力するNAND回路113と、比較回路11〜13の比較結果に矛盾がある場合にハイレベルの信号を出力するNOR回路114及び115と、NOR回路111、114及び115から出力される信号を入力するNOR回路120とを含んでいる。

【0022】

また、判定回路100は、NOR回路120、NAND回路112及び113から出力される信号をそれぞれ入力するNOR回路131〜133と、NOR回路131〜133から出力される信号を反転してゲート電位G1〜G3をそれぞれ出力するインバータ141〜143と、NAND回路151〜153と、遅延回路(DL)161〜163とを含んでいる。

【0023】

例えば、ACアダプタ1の電位V1が最も高い場合には、比較信号AT及びCTがローレベルとなるので、NOR回路111がハイレベルの信号を出力し、NOR回路120がローレベルの信号を出力する。これにより、NOR回路131において、一方の入力信号がローレベルとなる。

【0024】

また、比較信号AT及びCTがローレベルとなるので、NAND回路112及び113がハイレベルの信号を出力する。NOR回路132は、一方の入力信号がハイレベルとなるので、ローレベルの信号を出力し、インバータ142は、これを反転してハイレベルのゲート電位G2を出力するので、図1に示すトランジスタQP2がオフとなる。同様に、NOR回路133は、一方の入力信号がハイレベルとなるので、ローレベルの信号を出力し、インバータ143は、これを反転してハイレベルのゲート電位G3を出力するので、図1に示すトランジスタQP3がオフとなる。

【0025】

ゲート電位G2及びG3がハイレベルになると、NAND回路151からローレベルの信号が出力され、これが遅延回路161によって所定の期間遅延されて、NOR回路131に、他方の入力信号として印加される。NOR回路131の一方の入力信号は既にローレベルとなっているので、NOR回路131からハイレベルの信号が出力され、インバータ141は、これを反転してローレベルのゲート電位G1を出力するので、図1に示すトランジスタQP1がオンとなる。

【0026】

このように、判定回路100は、他の入力端子に接続されたトランジスタQP2及びQP3をオフさせるハイレベルのゲート電位G2及びG3が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたトランジスタQP1をオンさせるローレベルのゲート電位G1を出力する。これにより、ダイオードD1の順方向電圧分の低下を伴わずに、電源電位VDDを出力することができる。USB電源ライン2の電位V2が最も高い場合や、バッテリ3の電位V3が最も高い場合にも、同様の動作を行うことができる。

【0027】

次に、本発明の第2の実施形態について説明する。

図4は、本発明の第2の実施形態に係る電源制御回路の構成を示す図である。この電源制御回路は、半導体集積回路内に形成され、複数の入力端子にそれぞれ接続される複数の電源の内から、予め定められた優先順位に従って1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位VDDを供給する。本実施形態においては、ACアダプタ1の優先順位を1位、USB電源ライン2の優先順位を2位、バッテリ3の優先順位を3位とする。

【0028】

図4に示すように、この電源制御回路は、複数の入力端子と出力端子との間にそれぞれ接続された第1群のPチャネルMOSトランジスタQP11〜QP13及び第2群のPチャネルMOSトランジスタQP21〜QP23と、複数の入力端子に電源電位が印加されているか否かを検出する電位検出回路21〜23と、複数の入力端子における電位を出力端子における電位と比較する比較回路31〜33と、第1群のトランジスタQP11〜QP13のゲート電位を生成するゲート電位生成回路41〜43等と、第2群のMOSトランジスタの内で、優先順位の高い電源から電源電位が供給されるトランジスタをオンさせるゲート電位を出力する判定回路200とを有している。電源制御回路の出力端子には、供給される電源電位VDDによって電荷を蓄積するコンデンサC1が接続されている。

【0029】

ここで、第1群のトランジスタQP11〜QP13は、ソースがそれぞれの入力端子に接続され、バックゲートがソースに接続されており、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。このダイオードは、図1において、ダイオードD11〜D13として示されている。

【0030】

一方、第2群のトランジスタQP21〜QP23は、ソースがそれぞれの第1のトランジスタのドレインに接続され、ドレインが出力端子に接続され、バックゲートがドレインに接続されており、図2に示すのと同様に、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。このダイオードは、図1において、ダイオードD21〜D23として示されている。

【0031】

ゲート電位生成回路41〜43等は、オペアンプ41〜43と、基準電圧源51〜53と、抵抗R21〜R23及びR31〜R33とを含んでおり、出力端子に供給される電源電位VDDと接地電位との間の電圧を抵抗分割して、得られた電圧を基準電圧と比較することにより、第1のトランジスタQP11〜QP13のゲート電位をそれぞれ生成する。これらは、電源電位VDDを安定化させるレギュレータとして機能する。なお、イネーブル信号EN1〜EN3が非活性化されてゲート電位生成回路41〜43等が動作していない場合に、ACアダプタ1等の電源が接続されると、プルアップ抵抗R11〜R13によって、第1群のトランジスタQP11〜QP13のゲートがハイレベルにされる。

【0032】

電位検出回路21〜23は、複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する。一方、比較回路31〜33は、複数の入力端子における電位V1〜V3を出力端子における電源電位VDDと比較して、比較結果を表す複数の比較信号をそれぞれ出力する。

【0033】

判定回路200は、電位検出回路21〜23から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、第2群のトランジスタQP21〜QP23をオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、出力端子の電源電位VDDが優先順位の高い電源の電位よりも低下したことを確認した後に、第2群のトランジスタの内で優先順位の高い電源から電源電位が供給されるトランジスタをオンさせるゲート電位を出力する。

【0034】

また、判定回路200は、優先順位が最も高い電源に接続されているトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、複数のゲート電位生成回路41〜43等に供給されるイネーブル信号EN1〜EN3を生成する。

【0035】

例えば、図5の(a)に示すように、バッテリ3が接続されて機器が動作している。ここで、能動状態にあるトランジスタQP13及びQP23は、等価的に抵抗として表されている。コンデンサC1は、電源電位VDDを保持する。次に、図5の(b)に示すように、バッテリ3よりも優先順位が高いUSB電源ライン2が活性化すると、判定回路200は、第2群のトランジスタQP21〜QP23をオフさせるハイレベルのゲート電位を一旦出力し、コンデンサC1に保持されている電源電位VDDが低下する。

【0036】

判定回路200は、比較回路32から出力される比較信号に基づいて、出力端子の電源電位VDDがUSB電源ライン2の電位V2よりも低下したことを確認した後に、図5の(c)に示すように、USB電源ライン2から電源電位が供給されるトランジスタQP22をオンさせるローレベルのゲート電位を出力する。

【0037】

また、判定回路200は、トランジスタQP11及びQP13のゲート電位を生成するゲート電位生成回路41及び43等を非活性化し、USB電源ライン2に接続されているトランジスタQP12のゲート電位を生成するゲート電位生成回路42等を活性化するように、イネーブル信号EN1〜EN3を生成する。ここで、能動状態にあるトランジスタQP12及びQP22は、等価的に抵抗として表されている。

【0038】

一方、図6の(a)に示すように、USB電源ライン2が接続されて機器が動作している。ここで、能動状態にあるトランジスタQP12及びQP22は、等価的に抵抗として表されている。コンデンサC1は、電源電位VDDを保持する。次に、図6の(b)に示すように、USB電源ライン2が非活性化すると、判定回路200は、第2群のトランジスタQP21〜QP23をオフさせるハイレベルのゲート電位を一旦出力し、コンデンサC1に保持されている電源電位VDDが低下する。

【0039】

判定回路200は、比較回路33から出力される比較信号に基づいて、出力端子の電源電位VDDがバッテリ3の電位V3よりも低下したことを確認した後に、図6の(c)に示すように、バッテリ3から電源電位が供給されるトランジスタQP23をオンさせるローレベルのゲート電位を出力する。

【0040】

また、判定回路200は、トランジスタQP11及びQP12のゲート電位を生成するゲート電位生成回路41及び43等を非活性化し、バッテリ3に接続されているトランジスタQP13のゲート電位を生成するゲート電位生成回路43等を活性化するように、イネーブル信号EN1〜EN3を生成する。ここで、能動状態にあるトランジスタQP13及びQP23は、等価的に抵抗として表されている。

【0041】

このように、本実施形態によれば、電源電位が印加されている入力端子を判定し、優先順位の高い電源が接続又は切り離された場合に、第2群のトランジスタQP21〜QP23を一旦オフさせて、出力端子の電位が新たに接続される電源の電位よりも低下したことを確認した後に、第2群のトランジスタQP21〜QP23の内で新たに接続される電源から電源電位が供給されるトランジスタをオンさせることにより、電源の切換えの際に電源電圧が低下する期間をなるべく短くなるようにすることができる。

【図面の簡単な説明】

【0042】

【図1】本発明の第1の実施形態に係る電源制御回路の構成を示す図。

【図2】トランジスタQP1〜QP3の構造を示す半導体集積回路の断面図。

【図3】図1に示す判定回路の具体例を示す回路図。

【図4】本発明の第2の実施形態に係る電源制御回路の構成を示す図。

【図5】USB電源ラインが活性化される際の図4の電源制御回路の動作を示す図。

【図6】USB電源ラインが非活性化される際の図4の電源制御回路の動作を示す図。

【符号の説明】

【0043】

1 ACアダプタ、 2 USB電源ライン、 3 バッテリ、 11〜13、31〜33 比較回路、 21〜23 電位検出回路、 41〜43 オペアンプ、 51〜53 基準電圧源、 100、200 判定回路、 201 半導体基板、 202 Nウエル、 203 ゲート絶縁膜、 204 ゲート電極、 205、206 不純物拡散領域、 QP1〜QP3、QP11〜QP13、QP21〜QP23 PチャネルMOSトランジスタ、 D1〜D3、D11〜D13、D21〜D23 ダイオード、 111、114、115、120、131〜133 NOR回路、 112、113、151〜153 NAND回路、 141〜143 インバータ、 161〜163 遅延回路、 R11〜R13、R21〜R23、R31〜R33 抵抗

【技術分野】

【0001】

本発明は、複数の電源を切り換えて使用する機器において、電源の切換えを制御する電源制御回路に関する。

【背景技術】

【0002】

持ち運びが可能な光ディスクプレーヤ等の携帯機器においては、バッテリで駆動する場合の他に、ACアダプタやUSB(ユニバーサル・シリアル・バス)等の電源ラインに接続して駆動することができるように設計されているものが多い。そのような機器に複数の電源が接続された場合には、例えば、最も高い電圧を有する電源を使用することが行われている。その際に、電流が逆流するのを防止するダイオードスイッチが使用されることが多いが、ダイオードスイッチを使用する場合には、ダイオードの順方向電圧(通常は、約0.6V)だけ、電源電圧が低下してしまうという問題がある。

【0003】

あるいは、予め定められた優先順位に従って、複数の電源の中から1つの電源を選択して使用することも考えられる。その場合には、電源の切換えの際に電源電圧が低下する期間がなるべく短くなるようにすることが望ましい。

【0004】

関連する技術として、下記の特許文献1には、外部電源用の遅延手段と、バッテリ用の逆流防止用ダイオードに並列接続したリレースイッチとを備え、逆流防止用ダイオードの順方向バイアス電圧による電圧降下と電力損失を無くしてバッテリ使用の長時間化を図ることのできる電源切替装置が開示されている。この電源切替装置は、外部電源に接続される遅延手段及び電圧検出手段と、遅延手段と出力端子との間に接続された第1のダイオードと、バッテリの正極と出力端子との間に並列接続されたリレースイッチ及び第2のダイオードとを備え、電圧検出手段が、遅延する前の外部電源の電圧値を検出して、該電圧値に応じてリレースイッチを開閉する。

【0005】

この電源切替装置においては、外部電源から所定の電圧が出力されていない場合に、リレースイッチを閉じることにより、電源として使用するバッテリに接続された第2のダイオードによる電圧降下を防止することができる。しかしながら、電源として外部電源を使用する場合においては、第1のダイオードによる電圧降下を防止することはできない。もし、外部電源と出力端子との間に第2のリレースイッチを設けるとしたら、バッテリと外部電源とがショートしないように対策を立てる必要がある。また、リレースイッチを用いることにより、機器が大型化してしまう。

【特許文献1】特開平10−336912号公報(第1〜2頁、図1)

【発明の開示】

【発明が解決しようとする課題】

【0006】

そこで、上記の点に鑑み、本発明の第1の目的は、複数の電源を切り換えて使用する機器において、いずれの電源を使用する場合でも電源電圧の降下を防止することである。また、本発明の第2の目的は、予め定められた優先順位に従って複数の電源の中から1つの電源を選択して使用する機器において、電源の切換えの際に電源電圧が低下する期間がなるべく短くなるようにすることである。

【課題を解決するための手段】

【0007】

以上の課題を解決するため、本発明の第1の観点に係る電源制御回路は、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、複数の入力端子に接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタと、複数の入力端子における電位を比較して、比較結果を表す少なくとも1つの比較信号を出力する少なくとも1つの比較回路と、少なくとも1つの比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路とを具備する。

【0008】

ここで、複数のMOSトランジスタの各々は、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。

【0009】

さらに、判定回路は、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されてから、所定の遅延を伴って、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力するようにしても良い。

【0010】

また、本発明の第2の観点に係る電源制御回路は、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、複数の入力端子に接続されたそれぞれのソースを有し、バックゲートがソースに接続された複数の第1のMOSトランジスタと、複数の第1のMOSトランジスタのドレインに接続されたそれぞれのソースと出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数の第2のMOSトランジスタと、出力端子に供給される電源電位に基づいて、複数の第1のMOSトランジスタのゲート電位をそれぞれ生成する複数のゲート電位生成回路と、複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する複数の検出回路と、複数の入力端子における電位を出力端子における電位と比較して、比較結果を表す複数の比較信号をそれぞれ出力する複数の比較回路と、複数の検出回路から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、複数の第2のMOSトランジスタをオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、出力端子の電位が優先順位の高い電源の電位よりも低下したことを確認した後に、優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせるゲート電位を出力する判定回路とを具備する。

【0011】

ここで、複数の第1のMOSトランジスタの各々は、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有し、複数の第2のMOSトランジスタの各々は、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。

【0012】

さらに、判定回路は、優先順位が最も高い電源に接続されている第1のMOSトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、複数のゲート電位生成回路に供給される複数の制御信号を生成するようにしても良い。

【発明の効果】

【0013】

本発明の第1の観点によれば、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタがオフしていることを確認して複数の電源間がショートされることを防止すると共に、最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせることにより、いずれの電源を使用する場合でも電源電圧の降下を防止することができる。

【0014】

また、本発明の第2の観点によれば、電源電位が印加されている入力端子を判定し、現在接続されている電源よりも優先順位の高い電源が接続された場合に、全ての第2のMOSトランジスタを一旦オフさせて、出力端子の電位が優先順位の高い電源の電位よりも低下したことを確認した後に、優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせることにより、電源の切換えの際に電源電圧が低下する期間をなるべく短くなるようにすることができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら詳しく説明する。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

図1は、本発明の第1の実施形態に係る電源制御回路の構成を示す図である。この電源制御回路は、半導体集積回路内に形成され、複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位VDDを供給する。本実施形態においては、複数の電源として、ACアダプタ1とUSB電源ライン2とバッテリ3とが複数の入力端子にそれぞれ接続されており、これらの電源の内で最も電位の高い電源が選択される。

【0016】

図1に示すように、電源制御回路は、複数の入力端子と出力端子との間にソース・ドレインが接続されたPチャネルMOSトランジスタQP1〜QP3と、複数の入力端子における電位V1〜V3を比較して比較信号を出力する比較回路11〜13と、比較信号に基づいてトランジスタQP1〜QP3のゲート電位G1〜G3を出力する判定回路100とを有している。

【0017】

図2は、本実施形態において用いられるPチャネルMOSトランジスタQP1〜QP3の構造を示す半導体集積回路の断面図である。図2に示すように、P型の半導体基板201内にNウエル202が形成されており、Nウエル202が形成された半導体基板201の所定の領域上に、ゲート絶縁膜203及びゲート電極204を含むゲートが形成されている。また、ゲートの両側の半導体基板201内には、ソースとなるP型の不純物拡散領域205と、ドレインとなるP型の不純物拡散領域206とが形成されている。なお、N型の半導体基板を用いる場合には、Nウエルを形成せずに、N型の半導体基板内にP型の不純物拡散領域を直接形成しても良い。また、PチャネルMOSトランジスタの替わりにNチャネルMOSトランジスタを用いる場合には、P型の半導体基板又はPウエル内にNチャネルMOSトランジスタを形成すれば良い。

【0018】

図2に示すように、PチャネルMOSトランジスタQP1〜QP3においては、P型の不純物拡散領域205及び206とNウエル202との間のPN接合によって、2つの寄生ダイオードが形成されている。ここで、バックゲートとなるNウエル202が、ドレインとなる不純物拡散領域206に接続されているので、ソース・ドレイン間に電気的に接続されたアノード・カソードを有するダイオードが、等価的に発生することになる。このダイオードは、図1において、ダイオードD1〜D3として示されている。

【0019】

再び図1を参照すると、ACアダプタ1の電位V1とUSB電源ライン2の電位V2とバッテリ3の電位V3との内で最も高い電位によって、ダイオードD1〜D3のいずれかがオンして、出力端子に電源電位VDDが供給される。ただし、この段階においては、ダイオードの順方向電圧(通常は、約0.6V)だけ、電源電位VDDが低下している。この電源電位VDDは、電源制御回路の各部に供給されて、各部が動作を開始する。

【0020】

比較回路11〜13は、例えばオペアンプによって構成され、複数の入力端子における電位を比較して、比較結果を表す比較信号AT〜CT及びAX〜CXを出力する。ここで、比較信号AX〜CXは、比較信号AT〜CTをそれぞれ反転した信号である。これらの比較信号に基づいて、判定回路100は、最も高い電源電位が印加されている入力端子を判定し、最も高い電源電位が印加されている入力端子に接続されたトランジスタをオンさせるゲート電位を出力すると共に、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位を出力する。

【0021】

図3は、図1に示す判定回路の具体例を示す回路図である。図3に示す判定回路100は、最も高い電源電位が電源電位V1であるときにハイレベルの信号を出力するNOR回路111と、最も高い電源電位が電源電位V2であるときにローレベルの信号を出力するNAND回路112と、最も高い電源電位が電源電位V3であるときにローレベルの信号を出力するNAND回路113と、比較回路11〜13の比較結果に矛盾がある場合にハイレベルの信号を出力するNOR回路114及び115と、NOR回路111、114及び115から出力される信号を入力するNOR回路120とを含んでいる。

【0022】

また、判定回路100は、NOR回路120、NAND回路112及び113から出力される信号をそれぞれ入力するNOR回路131〜133と、NOR回路131〜133から出力される信号を反転してゲート電位G1〜G3をそれぞれ出力するインバータ141〜143と、NAND回路151〜153と、遅延回路(DL)161〜163とを含んでいる。

【0023】

例えば、ACアダプタ1の電位V1が最も高い場合には、比較信号AT及びCTがローレベルとなるので、NOR回路111がハイレベルの信号を出力し、NOR回路120がローレベルの信号を出力する。これにより、NOR回路131において、一方の入力信号がローレベルとなる。

【0024】

また、比較信号AT及びCTがローレベルとなるので、NAND回路112及び113がハイレベルの信号を出力する。NOR回路132は、一方の入力信号がハイレベルとなるので、ローレベルの信号を出力し、インバータ142は、これを反転してハイレベルのゲート電位G2を出力するので、図1に示すトランジスタQP2がオフとなる。同様に、NOR回路133は、一方の入力信号がハイレベルとなるので、ローレベルの信号を出力し、インバータ143は、これを反転してハイレベルのゲート電位G3を出力するので、図1に示すトランジスタQP3がオフとなる。

【0025】

ゲート電位G2及びG3がハイレベルになると、NAND回路151からローレベルの信号が出力され、これが遅延回路161によって所定の期間遅延されて、NOR回路131に、他方の入力信号として印加される。NOR回路131の一方の入力信号は既にローレベルとなっているので、NOR回路131からハイレベルの信号が出力され、インバータ141は、これを反転してローレベルのゲート電位G1を出力するので、図1に示すトランジスタQP1がオンとなる。

【0026】

このように、判定回路100は、他の入力端子に接続されたトランジスタQP2及びQP3をオフさせるハイレベルのゲート電位G2及びG3が出力されていることを確認した後に、最も高い電源電位が印加されている入力端子に接続されたトランジスタQP1をオンさせるローレベルのゲート電位G1を出力する。これにより、ダイオードD1の順方向電圧分の低下を伴わずに、電源電位VDDを出力することができる。USB電源ライン2の電位V2が最も高い場合や、バッテリ3の電位V3が最も高い場合にも、同様の動作を行うことができる。

【0027】

次に、本発明の第2の実施形態について説明する。

図4は、本発明の第2の実施形態に係る電源制御回路の構成を示す図である。この電源制御回路は、半導体集積回路内に形成され、複数の入力端子にそれぞれ接続される複数の電源の内から、予め定められた優先順位に従って1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位VDDを供給する。本実施形態においては、ACアダプタ1の優先順位を1位、USB電源ライン2の優先順位を2位、バッテリ3の優先順位を3位とする。

【0028】

図4に示すように、この電源制御回路は、複数の入力端子と出力端子との間にそれぞれ接続された第1群のPチャネルMOSトランジスタQP11〜QP13及び第2群のPチャネルMOSトランジスタQP21〜QP23と、複数の入力端子に電源電位が印加されているか否かを検出する電位検出回路21〜23と、複数の入力端子における電位を出力端子における電位と比較する比較回路31〜33と、第1群のトランジスタQP11〜QP13のゲート電位を生成するゲート電位生成回路41〜43等と、第2群のMOSトランジスタの内で、優先順位の高い電源から電源電位が供給されるトランジスタをオンさせるゲート電位を出力する判定回路200とを有している。電源制御回路の出力端子には、供給される電源電位VDDによって電荷を蓄積するコンデンサC1が接続されている。

【0029】

ここで、第1群のトランジスタQP11〜QP13は、ソースがそれぞれの入力端子に接続され、バックゲートがソースに接続されており、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。このダイオードは、図1において、ダイオードD11〜D13として示されている。

【0030】

一方、第2群のトランジスタQP21〜QP23は、ソースがそれぞれの第1のトランジスタのドレインに接続され、ドレインが出力端子に接続され、バックゲートがドレインに接続されており、図2に示すのと同様に、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有している。このダイオードは、図1において、ダイオードD21〜D23として示されている。

【0031】

ゲート電位生成回路41〜43等は、オペアンプ41〜43と、基準電圧源51〜53と、抵抗R21〜R23及びR31〜R33とを含んでおり、出力端子に供給される電源電位VDDと接地電位との間の電圧を抵抗分割して、得られた電圧を基準電圧と比較することにより、第1のトランジスタQP11〜QP13のゲート電位をそれぞれ生成する。これらは、電源電位VDDを安定化させるレギュレータとして機能する。なお、イネーブル信号EN1〜EN3が非活性化されてゲート電位生成回路41〜43等が動作していない場合に、ACアダプタ1等の電源が接続されると、プルアップ抵抗R11〜R13によって、第1群のトランジスタQP11〜QP13のゲートがハイレベルにされる。

【0032】

電位検出回路21〜23は、複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する。一方、比較回路31〜33は、複数の入力端子における電位V1〜V3を出力端子における電源電位VDDと比較して、比較結果を表す複数の比較信号をそれぞれ出力する。

【0033】

判定回路200は、電位検出回路21〜23から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、第2群のトランジスタQP21〜QP23をオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、出力端子の電源電位VDDが優先順位の高い電源の電位よりも低下したことを確認した後に、第2群のトランジスタの内で優先順位の高い電源から電源電位が供給されるトランジスタをオンさせるゲート電位を出力する。

【0034】

また、判定回路200は、優先順位が最も高い電源に接続されているトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、複数のゲート電位生成回路41〜43等に供給されるイネーブル信号EN1〜EN3を生成する。

【0035】

例えば、図5の(a)に示すように、バッテリ3が接続されて機器が動作している。ここで、能動状態にあるトランジスタQP13及びQP23は、等価的に抵抗として表されている。コンデンサC1は、電源電位VDDを保持する。次に、図5の(b)に示すように、バッテリ3よりも優先順位が高いUSB電源ライン2が活性化すると、判定回路200は、第2群のトランジスタQP21〜QP23をオフさせるハイレベルのゲート電位を一旦出力し、コンデンサC1に保持されている電源電位VDDが低下する。

【0036】

判定回路200は、比較回路32から出力される比較信号に基づいて、出力端子の電源電位VDDがUSB電源ライン2の電位V2よりも低下したことを確認した後に、図5の(c)に示すように、USB電源ライン2から電源電位が供給されるトランジスタQP22をオンさせるローレベルのゲート電位を出力する。

【0037】

また、判定回路200は、トランジスタQP11及びQP13のゲート電位を生成するゲート電位生成回路41及び43等を非活性化し、USB電源ライン2に接続されているトランジスタQP12のゲート電位を生成するゲート電位生成回路42等を活性化するように、イネーブル信号EN1〜EN3を生成する。ここで、能動状態にあるトランジスタQP12及びQP22は、等価的に抵抗として表されている。

【0038】

一方、図6の(a)に示すように、USB電源ライン2が接続されて機器が動作している。ここで、能動状態にあるトランジスタQP12及びQP22は、等価的に抵抗として表されている。コンデンサC1は、電源電位VDDを保持する。次に、図6の(b)に示すように、USB電源ライン2が非活性化すると、判定回路200は、第2群のトランジスタQP21〜QP23をオフさせるハイレベルのゲート電位を一旦出力し、コンデンサC1に保持されている電源電位VDDが低下する。

【0039】

判定回路200は、比較回路33から出力される比較信号に基づいて、出力端子の電源電位VDDがバッテリ3の電位V3よりも低下したことを確認した後に、図6の(c)に示すように、バッテリ3から電源電位が供給されるトランジスタQP23をオンさせるローレベルのゲート電位を出力する。

【0040】

また、判定回路200は、トランジスタQP11及びQP12のゲート電位を生成するゲート電位生成回路41及び43等を非活性化し、バッテリ3に接続されているトランジスタQP13のゲート電位を生成するゲート電位生成回路43等を活性化するように、イネーブル信号EN1〜EN3を生成する。ここで、能動状態にあるトランジスタQP13及びQP23は、等価的に抵抗として表されている。

【0041】

このように、本実施形態によれば、電源電位が印加されている入力端子を判定し、優先順位の高い電源が接続又は切り離された場合に、第2群のトランジスタQP21〜QP23を一旦オフさせて、出力端子の電位が新たに接続される電源の電位よりも低下したことを確認した後に、第2群のトランジスタQP21〜QP23の内で新たに接続される電源から電源電位が供給されるトランジスタをオンさせることにより、電源の切換えの際に電源電圧が低下する期間をなるべく短くなるようにすることができる。

【図面の簡単な説明】

【0042】

【図1】本発明の第1の実施形態に係る電源制御回路の構成を示す図。

【図2】トランジスタQP1〜QP3の構造を示す半導体集積回路の断面図。

【図3】図1に示す判定回路の具体例を示す回路図。

【図4】本発明の第2の実施形態に係る電源制御回路の構成を示す図。

【図5】USB電源ラインが活性化される際の図4の電源制御回路の動作を示す図。

【図6】USB電源ラインが非活性化される際の図4の電源制御回路の動作を示す図。

【符号の説明】

【0043】

1 ACアダプタ、 2 USB電源ライン、 3 バッテリ、 11〜13、31〜33 比較回路、 21〜23 電位検出回路、 41〜43 オペアンプ、 51〜53 基準電圧源、 100、200 判定回路、 201 半導体基板、 202 Nウエル、 203 ゲート絶縁膜、 204 ゲート電極、 205、206 不純物拡散領域、 QP1〜QP3、QP11〜QP13、QP21〜QP23 PチャネルMOSトランジスタ、 D1〜D3、D11〜D13、D21〜D23 ダイオード、 111、114、115、120、131〜133 NOR回路、 112、113、151〜153 NAND回路、 141〜143 インバータ、 161〜163 遅延回路、 R11〜R13、R21〜R23、R31〜R33 抵抗

【特許請求の範囲】

【請求項1】

複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、

前記複数の入力端子に接続されたそれぞれのソースと前記出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタと、

前記複数の入力端子における電位を比較して、比較結果を表す少なくとも1つの比較信号を出力する少なくとも1つの比較回路と、

前記少なくとも1つの比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、前記最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路と、

を具備する電源制御回路。

【請求項2】

前記複数のMOSトランジスタの各々が、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有する、請求項1記載の電源制御回路。

【請求項3】

前記判定回路が、前記他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されてから、所定の遅延を伴って、前記最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する、請求項1又は2記載の電源制御回路。

【請求項4】

複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、

前記複数の入力端子に接続されたそれぞれのソースを有し、バックゲートがソースに接続された複数の第1のMOSトランジスタと、

前記複数の第1のMOSトランジスタのドレインに接続されたそれぞれのソースと前記出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数の第2のMOSトランジスタと、

前記出力端子に供給される電源電位に基づいて、前記複数の第1のMOSトランジスタのゲート電位をそれぞれ生成する複数のゲート電位生成回路と、

前記複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する複数の検出回路と、

前記複数の入力端子における電位を前記出力端子における電位と比較して、比較結果を表す複数の比較信号をそれぞれ出力する複数の比較回路と、

前記複数の検出回路から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、前記複数の第2のMOSトランジスタをオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、前記出力端子の電位が前記優先順位の高い電源の電位よりも低下したことを確認した後に、前記優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせるゲート電位を出力する判定回路と、

を具備する電源制御回路。

【請求項5】

前記複数の第1のMOSトランジスタの各々が、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有し、前記複数の第2のMOSトランジスタの各々が、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有する、請求項4記載の電源制御回路。

【請求項6】

前記判定回路が、優先順位が最も高い電源に接続されている第1のMOSトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、前記複数のゲート電位生成回路に供給される複数の制御信号を生成する、請求項4又は5記載の電源制御回路。

【請求項1】

複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、

前記複数の入力端子に接続されたそれぞれのソースと前記出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数のMOSトランジスタと、

前記複数の入力端子における電位を比較して、比較結果を表す少なくとも1つの比較信号を出力する少なくとも1つの比較回路と、

前記少なくとも1つの比較回路から出力される少なくとも1つの比較信号に基づいて、最も高い電源電位が印加されている入力端子を判定し、他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されていることを確認した後に、前記最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する判定回路と、

を具備する電源制御回路。

【請求項2】

前記複数のMOSトランジスタの各々が、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有する、請求項1記載の電源制御回路。

【請求項3】

前記判定回路が、前記他の入力端子に接続されたMOSトランジスタをオフさせるゲート電位が出力されてから、所定の遅延を伴って、前記最も高い電源電位が印加されている入力端子に接続されたMOSトランジスタをオンさせるゲート電位を出力する、請求項1又は2記載の電源制御回路。

【請求項4】

複数の入力端子にそれぞれ接続される複数の電源の内から1つの電源を選択して、選択された電源から供給される電源電位に基づいて出力端子に電源電位を供給する電源制御回路であって、

前記複数の入力端子に接続されたそれぞれのソースを有し、バックゲートがソースに接続された複数の第1のMOSトランジスタと、

前記複数の第1のMOSトランジスタのドレインに接続されたそれぞれのソースと前記出力端子に接続されたドレインとを有し、バックゲートがドレインに接続された複数の第2のMOSトランジスタと、

前記出力端子に供給される電源電位に基づいて、前記複数の第1のMOSトランジスタのゲート電位をそれぞれ生成する複数のゲート電位生成回路と、

前記複数の入力端子に電源電位が印加されているか否かを検出して、検出結果を表す複数の検出信号をそれぞれ出力する複数の検出回路と、

前記複数の入力端子における電位を前記出力端子における電位と比較して、比較結果を表す複数の比較信号をそれぞれ出力する複数の比較回路と、

前記複数の検出回路から出力される複数の検出信号に基づいて、電源電位が印加されている入力端子を判定し、予め定められた優先順位に従って、現在接続されている電源よりも優先順位の高い電源が接続された場合に、前記複数の第2のMOSトランジスタをオフさせるゲート電位を一旦出力し、対応する比較回路から出力される比較信号に基づいて、前記出力端子の電位が前記優先順位の高い電源の電位よりも低下したことを確認した後に、前記優先順位の高い電源から電源電位が供給される第2のMOSトランジスタをオンさせるゲート電位を出力する判定回路と、

を具備する電源制御回路。

【請求項5】

前記複数の第1のMOSトランジスタの各々が、ドレインとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有し、前記複数の第2のMOSトランジスタの各々が、ソースとなる不純物拡散領域とバックゲートとなるウエル又は半導体基板との間のPN接合によって形成された寄生ダイオードを有する、請求項4記載の電源制御回路。

【請求項6】

前記判定回路が、優先順位が最も高い電源に接続されている第1のMOSトランジスタのゲート電位を生成するゲート電位生成回路を活性化するように、前記複数のゲート電位生成回路に供給される複数の制御信号を生成する、請求項4又は5記載の電源制御回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2006−42402(P2006−42402A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−213938(P2004−213938)

【出願日】平成16年7月22日(2004.7.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月22日(2004.7.22)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]