電源制御装置及び電源制御方法

【課題】電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供すること。

【解決手段】電源制御装置は、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶するレジスタ10と、レジスタ10に記憶されたオン情報を選択するMUX20と、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する電源制御部30とを備える。

【解決手段】電源制御装置は、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶するレジスタ10と、レジスタ10に記憶されたオン情報を選択するMUX20と、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する電源制御部30とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の電源を制御する電源制御装置及び電源制御方法に関する。

【背景技術】

【0002】

従来より、高効率動作のため、システム電源ICにおいて複数の電源を制御することが知られている(特許文献1参照)。すなわち、回路ブロック毎に異なる電源電圧を供給し、この電源供給も個別にオン・オフすることができるようになっている。

【0003】

例えば、3つの電源電圧V1,V2,V3を供給する装置において、入力信号SEQの値に応じて2種類の電源オンするタイミング・シーケンスを考える。具体的には、入力信号SEQが0である場合は、図15に示すように、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。また、入力信号SEQが1である場合は、図16に示すように、起動信号POWER_ONがオンになってから15ms,20ms,5ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。このような状況で入力信号SEQが1である場合に電源電圧V1を供給する動作を図17及び図18を用いて説明する。

【0004】

まず、起動信号POWER_ONが1になると、ダウン・カウンタ101に値がロードされる。ここでは、入力信号SEQが1である場合を想定しているので、MUX102により15msの値が選択され、クロック信号clkを用いて15ms分の値がロードされることになる。また、それと同時にダウン・カウンタ101のEnable信号cnt_enも1になり、ダウン・カウント動作が始まる。ダウン・カウンタ101の値cot_outが0になると、比較器103の出力信号eq0が1になり、ダウン・カウンタ101のEnable信号cnt_enを0に戻し、電圧V1供給回路104をオンにする。これにより、起動信号POWER_ONがオンになってから15ms後に所定の回路ブロックに対して電源電圧V1を供給することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−134576号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来技術によると、電源電圧V1をオンするタイミング・シーケンスを変更する場合、MUX102の入力値(10ms,15ms)を変更する必要がある。3つの電源電圧V1,V2,V3がある場合はMUXも3つあるので、それぞれの入力値を変更しなければならない。電源電圧の数が増えるほど、入力値の変更箇所も増えていく。そのため、入力値を変更する際にミスを誘発する恐れがあり、また、入力値の変更作業が正しいかどうかを確認するために多くの時間が必要であった。

【0007】

本発明の目的は、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明の一態様によれば、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶部と、前記記憶部に記憶されたオン情報を選択する選択部と、前記選択部により選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御部とを備える電源制御装置が提供される。

【0009】

また、本発明の他の態様によれば、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶工程と、前記記憶工程で記憶されたオン情報を選択する選択工程と、前記選択工程で選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御工程とを有する電源制御方法が提供される。

【発明の効果】

【0010】

本発明によれば、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態に係る電源制御装置の要部の模式的内部構成図。

【図2】第1の実施の形態に係るレジスタの模式的内部構成図。

【図3】第1の実施の形態に係るオン情報を説明するための図。

【図4】第1の実施の形態に係るオン情報の模式的内部構成図であって、(a)入力信号が0である場合の構成例、(b)入力信号が1である場合の構成例。

【図5】第1の実施の形態に係る電源制御部の模式的内部構成図。

【図6】第1の実施の形態に係るON信号生成回路の模式的内部構成図。

【図7】第1の実施の形態に係る電源制御装置の動作例を示すタイムチャート。

【図8】第1の実施の形態に係る他のオン情報の模式的内部構成図。

【図9】第2の実施の形態に係るオン情報を説明するための図。

【図10】第2の実施の形態に係るオン情報の模式的内部構成図。

【図11】第2の実施の形態に係る電源制御装置の要部の模式的内部構成図。

【図12】第2の実施の形態に係る電源制御部の模式的内部構成図。

【図13】第2の実施の形態に係るON信号生成回路の模式的内部構成図。

【図14】第2の実施の形態に係る電源制御装置の動作例を示すタイムチャート。

【図15】従来技術を説明するための図であって、入力信号が0である場合を示す図。

【図16】従来技術を説明するための図であって、入力信号が1である場合を示す図。

【図17】従来の電源制御装置の電源電圧V1を供給する部分の模式的内部構成図。

【図18】従来の電源制御装置の動作例を示すタイムチャート。

【発明を実施するための形態】

【0012】

次に、図面を参照して、本発明の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。ただし、図面は模式的なものであり、各構成部品の厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0013】

又、以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0014】

[第1の実施の形態]

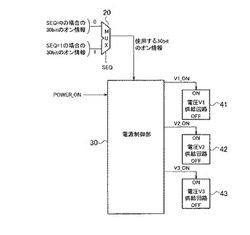

第1の実施の形態に係る電源制御装置は、図1に示すように、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶するレジスタ10等の記憶部(後述する。)と、レジスタ10に記憶されたオン情報を選択するMUX20等の選択部と、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する電源制御部30とを備える。

【0015】

また、レジスタ10は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶し、MUX20は、所定の環境条件又は動作条件が与えられると、その環境条件又は動作条件に対応するオン情報を選択してもよい。

【0016】

また、レジスタ10は、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶してもよい。

【0017】

また、レジスタ10は、オンする順番に対応する領域毎に、複数の電源に含まれる個々の電源を意味する値を記憶してもよい。

【0018】

また、レジスタ10は、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶してもよい。

【0019】

また、レジスタ10は、n番目の電源をオンしてからn−1番目の電源をオンするまでの時間を意味する値を記憶してもよい。

【0020】

また、電源制御部30は、オン情報に規定されたタイミングに基づいて複数のオン信号を生成し、生成した複数のオン信号をオン情報に規定された順番に基づいて選択的に電圧V1供給回路41,電圧V2供給回路42,電圧V3供給回路43に入力してもよい。

【0021】

以下、第1の実施の形態に係る電源制御装置の構成をより詳細に説明する。この電源制御装置は、図1に示すように、複数の電源電圧を供給するシステム電源IC等であって、MUX20と、電源制御部30とを備えている。MUX20は、レジスタ10に記憶されたオン情報を選択し、選択したオン情報を後段の電源制御部30に供給する。電源制御部30は、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する。具体的には、電圧V1供給回路41,電圧V2供給回路42,電圧V3供給回路43(以下、一括して「電圧供給回路」という場合がある。)を個別にオンにするオン信号V1_ON,V2_ON,V3_ONを生成して各電圧供給回路に入力する。電圧供給回路には、CPUやビデオプロセッサ、オーディオプロセッサ等、電圧供給対象となる回路ブロックが接続されている。回路ブロック毎に異なる電源電圧を供給し、この電源供給を個別にオン・オフすることができるようになっている。

【0022】

図2は、第1の実施の形態に係るレジスタ10の模式的内部構成図である。このレジスタ10は、30bitのオン情報を記憶している。

【0023】

オン情報の前6bitは、複数の電源をオンする順番を規定している。すなわち、先頭2bit分の領域11には、電圧V1供給回路41をオンする順番を意味する値が記憶されている。また、次の2bit分の領域12には、電圧V2供給回路42をオンする順番を意味する値が記憶されている。更に、次の2bit分の領域13には、電圧V3供給回路43をオンする順番を意味する値が記憶されている。言い換えると、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値が記憶されるようになっている。ここでは、2ビットの値“00”は、オンする順番が1番目であることを意味し、“01”は、オンする順番が2番目であることを意味し、“10”は、オンする順番が3番目であることを意味するものとする。3つの電源電圧V1,V2,V3がある場合を想定しているため、“11”は使用しない。もちろん、4つの電源電圧V1,V2,V3,V4がある場合は、オンする順番が4番目であることを意味する値として“11”を使用することができる。

【0024】

一方、オン情報の後ろ24bitは、複数の電源をオンするタイミングを規定している。すなわち、図3に示すように、8bit分の領域14には、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1が記憶されている。また、次の8bit分の領域15には、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2が記憶されている。更に、次の8bit分の領域16には、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3が記憶されている。

【0025】

レジスタ10は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶している。ここでいう環境条件又は動作条件は、電源供給のタイミング・シーケンスに関係する種々の条件を意味し、一例を挙げると“電圧供給対象となる回路ブロックの種類”が該当する。すなわち、回路ブロックの種類によって電源供給のタイミング・シーケンスを変更したい場合があり、その場合は予め各回路ブロックの種類と対応付けて複数のオン情報をレジスタ10に記憶しておく。回路ブロックの種類は、入力信号SEQの値により指定することが可能である。例えば、入力信号SEQが0の場合はビデオプロセッサAを意味し、入力信号SEQが1の場合はビデオプロセッサBを意味するようにしておく。MUX20は、回路ブロックの種類を指定する入力信号SEQが与えられると、その回路ブロックの種類(入力信号SEQ)と対応付けてレジスタ10に記憶されているオン情報を選択するようになっている。

【0026】

以下、オン情報の具体例を挙げて説明する。

【0027】

ここでも、図15の例を用いて説明する。すなわち、入力信号SEQが0である場合は、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。この場合の30bitのオン情報は、図4(a)に示す通りである。すなわち、電圧V1供給回路41をオンする順番は1番目であるため、領域11aには“00”が記憶される。また、電圧V2供給回路42をオンする順番は2番目であるため、領域12aには“01”が記憶される。更に、電圧V3供給回路43をオンする順番は3番目であるため、領域13aには“10”が記憶される。一方、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1は10msであるため、領域14aには“10ms”を意味する値が記憶される。また、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2は10msであるため、領域15aには“10ms”を意味する値が記憶される。更に、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3は10msであるため、領域16aには“10ms”を意味する値が記憶される。

【0028】

次いで、図16の例を用いて説明する。すなわち、入力信号SEQが1である場合は、起動信号POWER_ONがオンになってから15ms,20ms,5ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。この場合の30bitのオン情報は、図4(b)に示す通りである。すなわち、電圧V1供給回路41をオンする順番は2番目であるため、領域11bには“01”が記憶される。また、電圧V2供給回路42をオンする順番は3番目であるため、領域12bには“10”が記憶される。更に、電圧V3供給回路43をオンする順番は1番目であるため、領域13bには“00”が記憶される。一方、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1は5msであるため、領域14bには“5ms”を意味する値が記憶される。また、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2は10msであるため、領域15bには“10ms”を意味する値が記憶される。更に、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3は5msであるため、領域16bには“5ms”を意味する値が記憶される。

【0029】

図5は、第1の実施の形態に係る電源制御部30の模式的内部構成図である。この図に示すように、電源制御部30は、OR回路31と、MUX32と、第1のダウン・カウンタt_cntと、比較器33と、nth_cnt_en生成回路34と、第2のダウン・カウンタnth_cntと、ON信号生成回路35とを備えている。入力信号SEQが0である場合は、レジスタ10の領域14a,15a,16aからΔt1,Δt2,Δt3が読み出されてMUX32に入力されるとともに、レジスタ10の領域11a,12a,13aからV1_nth,V2_nth,V3_nthが読み出されてON信号生成回路35に入力される。一方、入力信号SEQが1である場合は、レジスタ10の領域14b,15b,16bからΔt1,Δt2,Δt3が読み出されてMUX32に入力されるとともに、レジスタ10の領域11b,12b,13bからV1_nth,V2_nth,V3_nthが読み出されてON信号生成回路35に入力される。詳細については後述するが、起動信号POWER_ONがオンになると、ダウン・カウント動作が始まってΔt1,Δt2,Δt3後に立ち上がるオン信号が発生し、このオン信号をV1_nth,V2_nth,V3_nthに基づいて選択的に電圧供給回路に入力するようになっている。

【0030】

図6は、第1の実施の形態に係るON信号生成回路35の模式的内部構成図である。この図に示すように、ON信号生成回路35は、第1のeq0出力回路35aと、第2のeq0出力回路35bと、第3のeq0出力回路35cと、MUX35d〜35fとを備えている。第1のeq0出力回路35aは、第2のダウン・カウンタの値nth_cnt_outが2である場合、比較器33の出力信号eq0をオン信号on_1stとして出力する。第2のeq0出力回路35bは、第2のダウン・カウンタの値nth_cnt_outが1である場合、比較器33の出力信号eq0をオン信号on_2ndとして出力する。第3のeq0出力回路35cは、第2のダウン・カウンタの値nth_cnt_outが0である場合、比較器33の出力信号eq0をオン信号on_3rdとして出力する。これらオン信号on_1st,on_2nd,on_3rdはMUX35d〜35fに入力されるようになっている。ここでは、MUX35dは、V1_nth“00”に基づいてon_1stを選択してV1_ONを出力する。また、MUX35eは、V2_nth“01”に基づいてon_2ndを選択してV2_ONを出力する。更に、MUX35fは、V3_nth“10”に基づいてon_3rdを選択してV3_ONを出力する。

【0031】

以下、図7に従って、第1の実施の形態に係る電源制御装置の動作を説明する。ここでも、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。

【0032】

まず、起動信号POWER_ONが1になると、第1のダウン・カウンタのロードEnable信号t_load_enが1になるとともに、第2のダウン・カウンタのロードEnable信号nth_load_enが1になる。このとき、第2のダウン・カウンタの値nth_cnt_outは0であるので、MUX32によりΔt1(10ms)が選択され、このΔt1が第1のダウン・カウンタt_cntにロードされる(t_load_val)。一方、ここでは3つの電源電圧V1,V2,V3がある場合を想定しているため、第2のダウン・カウンタnth_cntには固定値2がロードされる(nth_load_val)。

【0033】

また、起動信号POWER_ONが1になると、第1のダウン・カウンタのカウントEnable信号t_cnt_enが1になり、第1のダウン・カウンタt_cntがダウン・カウント動作を開始する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0034】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが2であるため、第1のダウン・カウンタt_cntにΔt2(10ms)がロードされる。また、第2のダウン・カウンタの値nth_cnt_outが2であるため、ロードEnable信号nth_load_enが1となり、第2のダウン・カウンタの値nth_cnt_outがダウン・カウントされて1になる。更に、第2のダウン・カウンタの値nth_cnt_outが2であるため、1番目のオン信号on_1stが比較器33の出力信号eq0と同じタイミングで発生する。

【0035】

その後も第1のダウン・カウンタt_cntはダウン・カウント動作を継続する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0036】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが1であるため、第1のダウン・カウンタt_cntにΔt3(10ms)がロードされる。また、第2のダウン・カウンタの値nth_cnt_outが1であるため、ロードEnable信号nth_load_enが1となり、第2のダウン・カウンタの値nth_cnt_outがダウン・カウントされて0になる。更に、第2のダウン・カウンタの値nth_cnt_outが1であるため、2番目のオン信号on_2stが比較器33の出力信号eq0と同じタイミングで発生する。

【0037】

その後も第1のダウン・カウンタt_cntはダウン・カウント動作を継続する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0038】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが0であるため、第1のダウン・カウンタt_cntにΔt1がロードされる。それと同時にロードEnable信号t_load_enが0になり、第1のダウン・カウンタt_cntが停止する。また、第2のダウン・カウンタの値nth_cnt_outが0である場合は、比較器33の出力信号eq0が発生してもロードEnable信号nth_load_enは0のままであるため、第2のダウン・カウンタの値nth_cnt_outは0を維持する。更に、第2のダウン・カウンタの値nth_cnt_outが0であるため、3番目のオン信号on_3stが比較器33の出力信号eq0と同じタイミングで発生する。

【0039】

このような動作でオン信号on_1st,on_2nd,on_3rdが発生したら、ON信号生成回路35は、V1_nth,V2_nth,V3_nthの指示通りにオン信号V1_ON、V2_ON、V3_ONを生成する。ここでは、電源電圧V1,V2,V3の順にオンする場合を想定しているため、オン信号on_1stがV1_ONとなり、on_2stがV2_ONとなり、on_3stがV3_ONとなる。

【0040】

オン信号V1_ONが電圧V1供給回路41に入力されると、電圧V1供給回路41がオンになって電源電圧V1を供給する。また、オン信号V2_ONが電圧V2供給回路42に入力されると、電圧V2供給回路42がオンになって電源電圧V2を供給する。更に、オン信号V3_ONが電圧V3供給回路43に入力されると、電圧V3供給回路43がオンになって電源電圧V3を供給する。その結果、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3がそれぞれ供給されることになる。

【0041】

以上説明したように、第1の実施の形態に係る電源制御装置よれば、電源供給のタイミング・シーケンスを容易に変更可能である。すなわち、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶しておき、そのオン情報に基づいて複数の電源をオンする順番及びタイミングを制御するようにしているので、このオン情報を変更するだけで電源供給のタイミング・シーケンスを変更することできる。そのため、従来と比べて変更作業のミスを誘発する可能性が低減し、また、変更作業の確認に要する時間を短縮することが可能である。このような効果は、供給する電源電圧の数が増えるほど顕著となるのはいうまでもない。

【0042】

なお、レジスタ10は、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶することとしているが、本発明はこれに限定されるものではない。すなわち、図8に示すように、オンする順番に対応する領域毎に、複数の電源に含まれる個々の電源を意味する値を記憶するようにしてもよい。すなわち、先頭2bit分の領域11には、1番目にオンする電圧供給回路を意味する値を記憶する。また、次の2bit分の領域12には、2番目にオンする電圧供給回路を意味する値を記憶する。更に、次の2bit分の領域13には、3番目にオンする電圧供給回路を意味する値を記憶する。このようにしても、複数の電源をオンする順番を規定することができるので、前記と同様の効果を得ることが可能である。

【0043】

また、ここでは、3つの電源電圧V1,V2,V3がある場合を想定しているため、オン情報の“11”は使用しないこととしているが、本発明はこれに限定されるものではない。すなわち、オン情報の“11”に特別な意味を持たせて使用することも可能である。例えば、3つの電源電圧V1,V2,V3の全部を使用するのではなく、V1とV3だけを使用するようにしてもよい。この場合は、使用しないV2に対応する領域12aに“11”を記憶しておき、Δt3を規定する領域16aにNULL等を記憶しておく。言い換えると、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶するようになっている。このようにすれば、オン情報を変更するという簡単な方法で複数の電源のうちの一部のみを選択的に使用することが可能である。

【0044】

[第2の実施の形態]

ところで、複数の電源をオフする場合は、オンした順番及びタイミングと同じ順番及びタイミングでオフするが通常である。しかしながら、オンした順番及びタイミングと異なる順番及びタイミングでオフしたい場合もある。そこで、第2の実施の形態では、以下の構成を採用している。

【0045】

すなわち、レジスタ10は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶する。また、MUX20は、レジスタ10に記憶されたオフ情報を選択する。更に、電源制御部30は、MUX20により選択されたオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御する。

【0046】

以下、第2の実施の形態に係る電源制御装置の構成を具体的に説明する。ここでは、図9に示すように、終了信号POWER_OFFがオンになってから10ms経過する毎に電源電圧V1,V3,V2の順にオフする場合を例示する。この場合の30bitのオフ情報は、図10に示す通りである。すなわち、電圧V1供給回路41をオフする順番は1番目であるため、領域11cには“00”が記憶される。また、電圧V2供給回路42をオフする順番は3番目であるため、領域12cには“10”が記憶される。更に、電圧V3供給回路43をオフする順番は2番目であるため、領域13cには“01”が記憶される。一方、終了信号POWER_OFFがオンになってから1番目の電源をオフするまでの時間Δt1,Δt2,Δt3はいずれも10msであるため、領域14c,15c,16cにはいずれも“10ms”を意味する値が記憶される。

【0047】

電源制御装置の構成は基本的に第1の実施の形態と同じである。すなわち、レジスタ10は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶し、MUX20は、レジスタ10に記憶されたオフ情報を選択し、電源制御部30は、MUX20により選択されたオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御する。

【0048】

ただし、本実施の形態では、図11及び図12に示すように、電源制御部30には起動信号POWER_ONに代えて終了信号POWER_OFFが入力される。また、電源制御部30からはオン信号V1_ON、V2_ON、V3_ONに代えてオフ信号V1_OFF、V2_OFF、V3_OFFが出力される。そのため、ON信号生成回路35ではなくOFF信号生成回路35と表記しているが、内部構成は同じである(図13参照)。そのため、図12(図13)に示すOFF信号生成回路の参照符号は、図5(図6)に示すON信号生成回路と同じものを用いている。

【0049】

ここでは、電源電圧V1,V3,V2の順にオフする場合を想定しているため、図14に示すように、オフ信号off_1stがV1_OFFとなり、off_2stがV3_OFFとなり、off_3stがV2_OFFとなる。その結果、終了信号POWER_OFFがオンになってから10ms経過する毎に電源電圧V1,V3,V2の順にオフされることになる。

【0050】

以上説明したように、第2の実施の形態に係る電源制御装置よれば、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶しておき、そのオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御するようにしているので、オンした順番及びタイミングと異なる順番及びタイミングでオフすることができる。しかも、オフ情報を変更するだけで電源供給のタイミング・シーケンスを容易に変更可能である。

【0051】

以上説明したように、本発明によれば、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することができる。

【0052】

[その他の実施の形態]

上記のように、本発明は第1〜第2の実施の形態によって記載したが、この開示の一部をなす論述および図面は例示的なものであり、この発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0053】

このように、本発明はここでは記載していない様々な実施の形態などを含む。例えば、ここでは電源制御装置の構成について説明したが、この電源制御装置が備える特徴的な処理部を工程とする電源制御方法として実現することも可能である。

【産業上の利用可能性】

【0054】

本発明に係る電源制御装置及び電源制御方法は、複数の電源電圧を供給するシステム電源IC等に適用することができるので、携帯電話やパーソナル・コンピュータ等の様々な電子機器に応用することが可能である。

【符号の説明】

【0055】

10…レジスタ(記憶部)

20…MUX(選択部)

30…電源制御部

41…電圧V1供給回路

42…電圧V2供給回路

43…電圧V3供給回路

【技術分野】

【0001】

本発明は、複数の電源を制御する電源制御装置及び電源制御方法に関する。

【背景技術】

【0002】

従来より、高効率動作のため、システム電源ICにおいて複数の電源を制御することが知られている(特許文献1参照)。すなわち、回路ブロック毎に異なる電源電圧を供給し、この電源供給も個別にオン・オフすることができるようになっている。

【0003】

例えば、3つの電源電圧V1,V2,V3を供給する装置において、入力信号SEQの値に応じて2種類の電源オンするタイミング・シーケンスを考える。具体的には、入力信号SEQが0である場合は、図15に示すように、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。また、入力信号SEQが1である場合は、図16に示すように、起動信号POWER_ONがオンになってから15ms,20ms,5ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。このような状況で入力信号SEQが1である場合に電源電圧V1を供給する動作を図17及び図18を用いて説明する。

【0004】

まず、起動信号POWER_ONが1になると、ダウン・カウンタ101に値がロードされる。ここでは、入力信号SEQが1である場合を想定しているので、MUX102により15msの値が選択され、クロック信号clkを用いて15ms分の値がロードされることになる。また、それと同時にダウン・カウンタ101のEnable信号cnt_enも1になり、ダウン・カウント動作が始まる。ダウン・カウンタ101の値cot_outが0になると、比較器103の出力信号eq0が1になり、ダウン・カウンタ101のEnable信号cnt_enを0に戻し、電圧V1供給回路104をオンにする。これにより、起動信号POWER_ONがオンになってから15ms後に所定の回路ブロックに対して電源電圧V1を供給することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2009−134576号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、従来技術によると、電源電圧V1をオンするタイミング・シーケンスを変更する場合、MUX102の入力値(10ms,15ms)を変更する必要がある。3つの電源電圧V1,V2,V3がある場合はMUXも3つあるので、それぞれの入力値を変更しなければならない。電源電圧の数が増えるほど、入力値の変更箇所も増えていく。そのため、入力値を変更する際にミスを誘発する恐れがあり、また、入力値の変更作業が正しいかどうかを確認するために多くの時間が必要であった。

【0007】

本発明の目的は、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することにある。

【課題を解決するための手段】

【0008】

本発明の一態様によれば、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶部と、前記記憶部に記憶されたオン情報を選択する選択部と、前記選択部により選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御部とを備える電源制御装置が提供される。

【0009】

また、本発明の他の態様によれば、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶工程と、前記記憶工程で記憶されたオン情報を選択する選択工程と、前記選択工程で選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御工程とを有する電源制御方法が提供される。

【発明の効果】

【0010】

本発明によれば、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施の形態に係る電源制御装置の要部の模式的内部構成図。

【図2】第1の実施の形態に係るレジスタの模式的内部構成図。

【図3】第1の実施の形態に係るオン情報を説明するための図。

【図4】第1の実施の形態に係るオン情報の模式的内部構成図であって、(a)入力信号が0である場合の構成例、(b)入力信号が1である場合の構成例。

【図5】第1の実施の形態に係る電源制御部の模式的内部構成図。

【図6】第1の実施の形態に係るON信号生成回路の模式的内部構成図。

【図7】第1の実施の形態に係る電源制御装置の動作例を示すタイムチャート。

【図8】第1の実施の形態に係る他のオン情報の模式的内部構成図。

【図9】第2の実施の形態に係るオン情報を説明するための図。

【図10】第2の実施の形態に係るオン情報の模式的内部構成図。

【図11】第2の実施の形態に係る電源制御装置の要部の模式的内部構成図。

【図12】第2の実施の形態に係る電源制御部の模式的内部構成図。

【図13】第2の実施の形態に係るON信号生成回路の模式的内部構成図。

【図14】第2の実施の形態に係る電源制御装置の動作例を示すタイムチャート。

【図15】従来技術を説明するための図であって、入力信号が0である場合を示す図。

【図16】従来技術を説明するための図であって、入力信号が1である場合を示す図。

【図17】従来の電源制御装置の電源電圧V1を供給する部分の模式的内部構成図。

【図18】従来の電源制御装置の動作例を示すタイムチャート。

【発明を実施するための形態】

【0012】

次に、図面を参照して、本発明の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。ただし、図面は模式的なものであり、各構成部品の厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。又、図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることはもちろんである。

【0013】

又、以下に示す実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の実施の形態は、各構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の実施の形態は、特許請求の範囲において、種々の変更を加えることができる。

【0014】

[第1の実施の形態]

第1の実施の形態に係る電源制御装置は、図1に示すように、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶するレジスタ10等の記憶部(後述する。)と、レジスタ10に記憶されたオン情報を選択するMUX20等の選択部と、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する電源制御部30とを備える。

【0015】

また、レジスタ10は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶し、MUX20は、所定の環境条件又は動作条件が与えられると、その環境条件又は動作条件に対応するオン情報を選択してもよい。

【0016】

また、レジスタ10は、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶してもよい。

【0017】

また、レジスタ10は、オンする順番に対応する領域毎に、複数の電源に含まれる個々の電源を意味する値を記憶してもよい。

【0018】

また、レジスタ10は、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶してもよい。

【0019】

また、レジスタ10は、n番目の電源をオンしてからn−1番目の電源をオンするまでの時間を意味する値を記憶してもよい。

【0020】

また、電源制御部30は、オン情報に規定されたタイミングに基づいて複数のオン信号を生成し、生成した複数のオン信号をオン情報に規定された順番に基づいて選択的に電圧V1供給回路41,電圧V2供給回路42,電圧V3供給回路43に入力してもよい。

【0021】

以下、第1の実施の形態に係る電源制御装置の構成をより詳細に説明する。この電源制御装置は、図1に示すように、複数の電源電圧を供給するシステム電源IC等であって、MUX20と、電源制御部30とを備えている。MUX20は、レジスタ10に記憶されたオン情報を選択し、選択したオン情報を後段の電源制御部30に供給する。電源制御部30は、MUX20により選択されたオン情報に基づいて複数の電源をオンする順番及びタイミングを制御する。具体的には、電圧V1供給回路41,電圧V2供給回路42,電圧V3供給回路43(以下、一括して「電圧供給回路」という場合がある。)を個別にオンにするオン信号V1_ON,V2_ON,V3_ONを生成して各電圧供給回路に入力する。電圧供給回路には、CPUやビデオプロセッサ、オーディオプロセッサ等、電圧供給対象となる回路ブロックが接続されている。回路ブロック毎に異なる電源電圧を供給し、この電源供給を個別にオン・オフすることができるようになっている。

【0022】

図2は、第1の実施の形態に係るレジスタ10の模式的内部構成図である。このレジスタ10は、30bitのオン情報を記憶している。

【0023】

オン情報の前6bitは、複数の電源をオンする順番を規定している。すなわち、先頭2bit分の領域11には、電圧V1供給回路41をオンする順番を意味する値が記憶されている。また、次の2bit分の領域12には、電圧V2供給回路42をオンする順番を意味する値が記憶されている。更に、次の2bit分の領域13には、電圧V3供給回路43をオンする順番を意味する値が記憶されている。言い換えると、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値が記憶されるようになっている。ここでは、2ビットの値“00”は、オンする順番が1番目であることを意味し、“01”は、オンする順番が2番目であることを意味し、“10”は、オンする順番が3番目であることを意味するものとする。3つの電源電圧V1,V2,V3がある場合を想定しているため、“11”は使用しない。もちろん、4つの電源電圧V1,V2,V3,V4がある場合は、オンする順番が4番目であることを意味する値として“11”を使用することができる。

【0024】

一方、オン情報の後ろ24bitは、複数の電源をオンするタイミングを規定している。すなわち、図3に示すように、8bit分の領域14には、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1が記憶されている。また、次の8bit分の領域15には、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2が記憶されている。更に、次の8bit分の領域16には、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3が記憶されている。

【0025】

レジスタ10は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶している。ここでいう環境条件又は動作条件は、電源供給のタイミング・シーケンスに関係する種々の条件を意味し、一例を挙げると“電圧供給対象となる回路ブロックの種類”が該当する。すなわち、回路ブロックの種類によって電源供給のタイミング・シーケンスを変更したい場合があり、その場合は予め各回路ブロックの種類と対応付けて複数のオン情報をレジスタ10に記憶しておく。回路ブロックの種類は、入力信号SEQの値により指定することが可能である。例えば、入力信号SEQが0の場合はビデオプロセッサAを意味し、入力信号SEQが1の場合はビデオプロセッサBを意味するようにしておく。MUX20は、回路ブロックの種類を指定する入力信号SEQが与えられると、その回路ブロックの種類(入力信号SEQ)と対応付けてレジスタ10に記憶されているオン情報を選択するようになっている。

【0026】

以下、オン情報の具体例を挙げて説明する。

【0027】

ここでも、図15の例を用いて説明する。すなわち、入力信号SEQが0である場合は、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。この場合の30bitのオン情報は、図4(a)に示す通りである。すなわち、電圧V1供給回路41をオンする順番は1番目であるため、領域11aには“00”が記憶される。また、電圧V2供給回路42をオンする順番は2番目であるため、領域12aには“01”が記憶される。更に、電圧V3供給回路43をオンする順番は3番目であるため、領域13aには“10”が記憶される。一方、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1は10msであるため、領域14aには“10ms”を意味する値が記憶される。また、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2は10msであるため、領域15aには“10ms”を意味する値が記憶される。更に、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3は10msであるため、領域16aには“10ms”を意味する値が記憶される。

【0028】

次いで、図16の例を用いて説明する。すなわち、入力信号SEQが1である場合は、起動信号POWER_ONがオンになってから15ms,20ms,5ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。この場合の30bitのオン情報は、図4(b)に示す通りである。すなわち、電圧V1供給回路41をオンする順番は2番目であるため、領域11bには“01”が記憶される。また、電圧V2供給回路42をオンする順番は3番目であるため、領域12bには“10”が記憶される。更に、電圧V3供給回路43をオンする順番は1番目であるため、領域13bには“00”が記憶される。一方、起動信号POWER_ONがオンになってから1番目の電源をオンするまでの時間Δt1は5msであるため、領域14bには“5ms”を意味する値が記憶される。また、1番目の電源をオンしてから2番目の電源をオンするまでの時間Δt2は10msであるため、領域15bには“10ms”を意味する値が記憶される。更に、2番目の電源をオンしてから3番目の電源をオンするまでの時間Δt3は5msであるため、領域16bには“5ms”を意味する値が記憶される。

【0029】

図5は、第1の実施の形態に係る電源制御部30の模式的内部構成図である。この図に示すように、電源制御部30は、OR回路31と、MUX32と、第1のダウン・カウンタt_cntと、比較器33と、nth_cnt_en生成回路34と、第2のダウン・カウンタnth_cntと、ON信号生成回路35とを備えている。入力信号SEQが0である場合は、レジスタ10の領域14a,15a,16aからΔt1,Δt2,Δt3が読み出されてMUX32に入力されるとともに、レジスタ10の領域11a,12a,13aからV1_nth,V2_nth,V3_nthが読み出されてON信号生成回路35に入力される。一方、入力信号SEQが1である場合は、レジスタ10の領域14b,15b,16bからΔt1,Δt2,Δt3が読み出されてMUX32に入力されるとともに、レジスタ10の領域11b,12b,13bからV1_nth,V2_nth,V3_nthが読み出されてON信号生成回路35に入力される。詳細については後述するが、起動信号POWER_ONがオンになると、ダウン・カウント動作が始まってΔt1,Δt2,Δt3後に立ち上がるオン信号が発生し、このオン信号をV1_nth,V2_nth,V3_nthに基づいて選択的に電圧供給回路に入力するようになっている。

【0030】

図6は、第1の実施の形態に係るON信号生成回路35の模式的内部構成図である。この図に示すように、ON信号生成回路35は、第1のeq0出力回路35aと、第2のeq0出力回路35bと、第3のeq0出力回路35cと、MUX35d〜35fとを備えている。第1のeq0出力回路35aは、第2のダウン・カウンタの値nth_cnt_outが2である場合、比較器33の出力信号eq0をオン信号on_1stとして出力する。第2のeq0出力回路35bは、第2のダウン・カウンタの値nth_cnt_outが1である場合、比較器33の出力信号eq0をオン信号on_2ndとして出力する。第3のeq0出力回路35cは、第2のダウン・カウンタの値nth_cnt_outが0である場合、比較器33の出力信号eq0をオン信号on_3rdとして出力する。これらオン信号on_1st,on_2nd,on_3rdはMUX35d〜35fに入力されるようになっている。ここでは、MUX35dは、V1_nth“00”に基づいてon_1stを選択してV1_ONを出力する。また、MUX35eは、V2_nth“01”に基づいてon_2ndを選択してV2_ONを出力する。更に、MUX35fは、V3_nth“10”に基づいてon_3rdを選択してV3_ONを出力する。

【0031】

以下、図7に従って、第1の実施の形態に係る電源制御装置の動作を説明する。ここでも、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3をそれぞれオンするものとする。

【0032】

まず、起動信号POWER_ONが1になると、第1のダウン・カウンタのロードEnable信号t_load_enが1になるとともに、第2のダウン・カウンタのロードEnable信号nth_load_enが1になる。このとき、第2のダウン・カウンタの値nth_cnt_outは0であるので、MUX32によりΔt1(10ms)が選択され、このΔt1が第1のダウン・カウンタt_cntにロードされる(t_load_val)。一方、ここでは3つの電源電圧V1,V2,V3がある場合を想定しているため、第2のダウン・カウンタnth_cntには固定値2がロードされる(nth_load_val)。

【0033】

また、起動信号POWER_ONが1になると、第1のダウン・カウンタのカウントEnable信号t_cnt_enが1になり、第1のダウン・カウンタt_cntがダウン・カウント動作を開始する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0034】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが2であるため、第1のダウン・カウンタt_cntにΔt2(10ms)がロードされる。また、第2のダウン・カウンタの値nth_cnt_outが2であるため、ロードEnable信号nth_load_enが1となり、第2のダウン・カウンタの値nth_cnt_outがダウン・カウントされて1になる。更に、第2のダウン・カウンタの値nth_cnt_outが2であるため、1番目のオン信号on_1stが比較器33の出力信号eq0と同じタイミングで発生する。

【0035】

その後も第1のダウン・カウンタt_cntはダウン・カウント動作を継続する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0036】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが1であるため、第1のダウン・カウンタt_cntにΔt3(10ms)がロードされる。また、第2のダウン・カウンタの値nth_cnt_outが1であるため、ロードEnable信号nth_load_enが1となり、第2のダウン・カウンタの値nth_cnt_outがダウン・カウントされて0になる。更に、第2のダウン・カウンタの値nth_cnt_outが1であるため、2番目のオン信号on_2stが比較器33の出力信号eq0と同じタイミングで発生する。

【0037】

その後も第1のダウン・カウンタt_cntはダウン・カウント動作を継続する。これにより、第1のダウン・カウンタの値t_cnt_outが0になると、比較器33の出力信号eq0が1になる。

【0038】

ここで、第1のダウン・カウンタのロードEnable信号t_load_enが1であり、かつ、第2のダウン・カウンタの値nth_cnt_outが0であるため、第1のダウン・カウンタt_cntにΔt1がロードされる。それと同時にロードEnable信号t_load_enが0になり、第1のダウン・カウンタt_cntが停止する。また、第2のダウン・カウンタの値nth_cnt_outが0である場合は、比較器33の出力信号eq0が発生してもロードEnable信号nth_load_enは0のままであるため、第2のダウン・カウンタの値nth_cnt_outは0を維持する。更に、第2のダウン・カウンタの値nth_cnt_outが0であるため、3番目のオン信号on_3stが比較器33の出力信号eq0と同じタイミングで発生する。

【0039】

このような動作でオン信号on_1st,on_2nd,on_3rdが発生したら、ON信号生成回路35は、V1_nth,V2_nth,V3_nthの指示通りにオン信号V1_ON、V2_ON、V3_ONを生成する。ここでは、電源電圧V1,V2,V3の順にオンする場合を想定しているため、オン信号on_1stがV1_ONとなり、on_2stがV2_ONとなり、on_3stがV3_ONとなる。

【0040】

オン信号V1_ONが電圧V1供給回路41に入力されると、電圧V1供給回路41がオンになって電源電圧V1を供給する。また、オン信号V2_ONが電圧V2供給回路42に入力されると、電圧V2供給回路42がオンになって電源電圧V2を供給する。更に、オン信号V3_ONが電圧V3供給回路43に入力されると、電圧V3供給回路43がオンになって電源電圧V3を供給する。その結果、起動信号POWER_ONがオンになってから10ms,20ms,30ms後に電源電圧V1,V2,V3がそれぞれ供給されることになる。

【0041】

以上説明したように、第1の実施の形態に係る電源制御装置よれば、電源供給のタイミング・シーケンスを容易に変更可能である。すなわち、複数の電源をオンする順番及びタイミングを規定したオン情報を記憶しておき、そのオン情報に基づいて複数の電源をオンする順番及びタイミングを制御するようにしているので、このオン情報を変更するだけで電源供給のタイミング・シーケンスを変更することできる。そのため、従来と比べて変更作業のミスを誘発する可能性が低減し、また、変更作業の確認に要する時間を短縮することが可能である。このような効果は、供給する電源電圧の数が増えるほど顕著となるのはいうまでもない。

【0042】

なお、レジスタ10は、複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶することとしているが、本発明はこれに限定されるものではない。すなわち、図8に示すように、オンする順番に対応する領域毎に、複数の電源に含まれる個々の電源を意味する値を記憶するようにしてもよい。すなわち、先頭2bit分の領域11には、1番目にオンする電圧供給回路を意味する値を記憶する。また、次の2bit分の領域12には、2番目にオンする電圧供給回路を意味する値を記憶する。更に、次の2bit分の領域13には、3番目にオンする電圧供給回路を意味する値を記憶する。このようにしても、複数の電源をオンする順番を規定することができるので、前記と同様の効果を得ることが可能である。

【0043】

また、ここでは、3つの電源電圧V1,V2,V3がある場合を想定しているため、オン情報の“11”は使用しないこととしているが、本発明はこれに限定されるものではない。すなわち、オン情報の“11”に特別な意味を持たせて使用することも可能である。例えば、3つの電源電圧V1,V2,V3の全部を使用するのではなく、V1とV3だけを使用するようにしてもよい。この場合は、使用しないV2に対応する領域12aに“11”を記憶しておき、Δt3を規定する領域16aにNULL等を記憶しておく。言い換えると、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶するようになっている。このようにすれば、オン情報を変更するという簡単な方法で複数の電源のうちの一部のみを選択的に使用することが可能である。

【0044】

[第2の実施の形態]

ところで、複数の電源をオフする場合は、オンした順番及びタイミングと同じ順番及びタイミングでオフするが通常である。しかしながら、オンした順番及びタイミングと異なる順番及びタイミングでオフしたい場合もある。そこで、第2の実施の形態では、以下の構成を採用している。

【0045】

すなわち、レジスタ10は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶する。また、MUX20は、レジスタ10に記憶されたオフ情報を選択する。更に、電源制御部30は、MUX20により選択されたオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御する。

【0046】

以下、第2の実施の形態に係る電源制御装置の構成を具体的に説明する。ここでは、図9に示すように、終了信号POWER_OFFがオンになってから10ms経過する毎に電源電圧V1,V3,V2の順にオフする場合を例示する。この場合の30bitのオフ情報は、図10に示す通りである。すなわち、電圧V1供給回路41をオフする順番は1番目であるため、領域11cには“00”が記憶される。また、電圧V2供給回路42をオフする順番は3番目であるため、領域12cには“10”が記憶される。更に、電圧V3供給回路43をオフする順番は2番目であるため、領域13cには“01”が記憶される。一方、終了信号POWER_OFFがオンになってから1番目の電源をオフするまでの時間Δt1,Δt2,Δt3はいずれも10msであるため、領域14c,15c,16cにはいずれも“10ms”を意味する値が記憶される。

【0047】

電源制御装置の構成は基本的に第1の実施の形態と同じである。すなわち、レジスタ10は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶し、MUX20は、レジスタ10に記憶されたオフ情報を選択し、電源制御部30は、MUX20により選択されたオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御する。

【0048】

ただし、本実施の形態では、図11及び図12に示すように、電源制御部30には起動信号POWER_ONに代えて終了信号POWER_OFFが入力される。また、電源制御部30からはオン信号V1_ON、V2_ON、V3_ONに代えてオフ信号V1_OFF、V2_OFF、V3_OFFが出力される。そのため、ON信号生成回路35ではなくOFF信号生成回路35と表記しているが、内部構成は同じである(図13参照)。そのため、図12(図13)に示すOFF信号生成回路の参照符号は、図5(図6)に示すON信号生成回路と同じものを用いている。

【0049】

ここでは、電源電圧V1,V3,V2の順にオフする場合を想定しているため、図14に示すように、オフ信号off_1stがV1_OFFとなり、off_2stがV3_OFFとなり、off_3stがV2_OFFとなる。その結果、終了信号POWER_OFFがオンになってから10ms経過する毎に電源電圧V1,V3,V2の順にオフされることになる。

【0050】

以上説明したように、第2の実施の形態に係る電源制御装置よれば、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶しておき、そのオフ情報に基づいて複数の電源をオフする順番及びタイミングを制御するようにしているので、オンした順番及びタイミングと異なる順番及びタイミングでオフすることができる。しかも、オフ情報を変更するだけで電源供給のタイミング・シーケンスを容易に変更可能である。

【0051】

以上説明したように、本発明によれば、電源供給のタイミング・シーケンスを容易に変更可能な電源制御装置及び電源制御方法を提供することができる。

【0052】

[その他の実施の形態]

上記のように、本発明は第1〜第2の実施の形態によって記載したが、この開示の一部をなす論述および図面は例示的なものであり、この発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

【0053】

このように、本発明はここでは記載していない様々な実施の形態などを含む。例えば、ここでは電源制御装置の構成について説明したが、この電源制御装置が備える特徴的な処理部を工程とする電源制御方法として実現することも可能である。

【産業上の利用可能性】

【0054】

本発明に係る電源制御装置及び電源制御方法は、複数の電源電圧を供給するシステム電源IC等に適用することができるので、携帯電話やパーソナル・コンピュータ等の様々な電子機器に応用することが可能である。

【符号の説明】

【0055】

10…レジスタ(記憶部)

20…MUX(選択部)

30…電源制御部

41…電圧V1供給回路

42…電圧V2供給回路

43…電圧V3供給回路

【特許請求の範囲】

【請求項1】

複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶部と、

前記記憶部に記憶されたオン情報を選択する選択部と、

前記選択部により選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御部と

を備えることを特徴とする電源制御装置。

【請求項2】

前記記憶部は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶し、

前記選択部は、前記所定の環境条件又は動作条件が与えられると、その環境条件又は動作条件に対応するオン情報を選択することを特徴とする請求項1に記載の電源制御装置。

【請求項3】

前記記憶部は、前記複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶することを特徴とする請求項1又は2に記載の電源制御装置。

【請求項4】

前記記憶部は、オンする順番に対応する領域毎に、前記複数の電源に含まれる個々の電源を意味する値を記憶することを特徴とする請求項1又は2に記載の電源制御装置。

【請求項5】

前記記憶部は、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶することを特徴とする請求項3又は4に記載の電源制御装置。

【請求項6】

前記記憶部は、n番目の電源をオンしてからn−1番目の電源をオンするまでの時間を意味する値を記憶することを特徴とする請求項1から5のいずれか一項に記載の電源制御装置。

【請求項7】

前記電源制御部は、前記オン情報に規定されたタイミングに基づいて複数のオン信号を生成し、生成した複数のオン信号を前記オン情報に規定された順番に基づいて選択的に電圧供給回路に入力することを特徴とする請求項1から6のいずれか一項に記載の電源制御装置。

【請求項8】

前記記憶部は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶し、

前記選択部は、前記記憶部に記憶されたオフ情報を選択し、

前期電源制御部は、前記選択部により選択されたオフ情報に基づいて前記複数の電源をオフする順番及びタイミングを制御することを特徴とする請求項1から7のいずれか一項に記載の電源制御装置。

【請求項9】

複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶工程と、

前記記憶工程で記憶されたオン情報を選択する選択工程と、

前記選択工程で選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御工程と

を有することを特徴とする電源制御方法。

【請求項1】

複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶部と、

前記記憶部に記憶されたオン情報を選択する選択部と、

前記選択部により選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御部と

を備えることを特徴とする電源制御装置。

【請求項2】

前記記憶部は、所定の環境条件又は動作条件と対応付けて複数のオン情報を記憶し、

前記選択部は、前記所定の環境条件又は動作条件が与えられると、その環境条件又は動作条件に対応するオン情報を選択することを特徴とする請求項1に記載の電源制御装置。

【請求項3】

前記記憶部は、前記複数の電源に含まれる個々の電源に対応する領域毎に、オンする順番を意味する値を記憶することを特徴とする請求項1又は2に記載の電源制御装置。

【請求項4】

前記記憶部は、オンする順番に対応する領域毎に、前記複数の電源に含まれる個々の電源を意味する値を記憶することを特徴とする請求項1又は2に記載の電源制御装置。

【請求項5】

前記記憶部は、複数の電源をオンする順番を規定する領域に、当該電源を使用しない旨の情報を記憶することを特徴とする請求項3又は4に記載の電源制御装置。

【請求項6】

前記記憶部は、n番目の電源をオンしてからn−1番目の電源をオンするまでの時間を意味する値を記憶することを特徴とする請求項1から5のいずれか一項に記載の電源制御装置。

【請求項7】

前記電源制御部は、前記オン情報に規定されたタイミングに基づいて複数のオン信号を生成し、生成した複数のオン信号を前記オン情報に規定された順番に基づいて選択的に電圧供給回路に入力することを特徴とする請求項1から6のいずれか一項に記載の電源制御装置。

【請求項8】

前記記憶部は、複数の電源をオフする順番及びタイミングを規定したオフ情報を記憶し、

前記選択部は、前記記憶部に記憶されたオフ情報を選択し、

前期電源制御部は、前記選択部により選択されたオフ情報に基づいて前記複数の電源をオフする順番及びタイミングを制御することを特徴とする請求項1から7のいずれか一項に記載の電源制御装置。

【請求項9】

複数の電源をオンする順番及びタイミングを規定したオン情報を記憶する記憶工程と、

前記記憶工程で記憶されたオン情報を選択する選択工程と、

前記選択工程で選択されたオン情報に基づいて前記複数の電源をオンする順番及びタイミングを制御する電源制御工程と

を有することを特徴とする電源制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−109551(P2013−109551A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253541(P2011−253541)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]