電源制御装置

【課題】回路規模が小さく、かつ十分に安定した応答特性を有する電源制御装置を構成する。

【解決手段】

目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、第1の伝達関数Wc(z)の特性を有する補償器(101)と、第2の伝達関数Wp(z)の特性を有し、補償器(101)からの出力に応じて出力信号を生成する制御対象(102)と、第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有する外乱キャンセル器(103)と、第4の伝達関数K(z)の特性を有するフィルタ回路(104)とを具備する電源制御装置(1)を構成する。ここにおいて、補償器は、差分信号と出力信号とを入力として受け取り、差分信号と出力信号との各々に基づいて、制御量yを目標値に一致させる補償動作を行う。

【解決手段】

目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、第1の伝達関数Wc(z)の特性を有する補償器(101)と、第2の伝達関数Wp(z)の特性を有し、補償器(101)からの出力に応じて出力信号を生成する制御対象(102)と、第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有する外乱キャンセル器(103)と、第4の伝達関数K(z)の特性を有するフィルタ回路(104)とを具備する電源制御装置(1)を構成する。ここにおいて、補償器は、差分信号と出力信号とを入力として受け取り、差分信号と出力信号との各々に基づいて、制御量yを目標値に一致させる補償動作を行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源制御装置に関し、特に、ディジタル制御方式のスイッチング電源制御装置を小型化する技術に関する。

【背景技術】

【0002】

近年、ディジタル家電や携帯機器等の民生機器において、通信状況に応じた動作シーケンスと連携した電源供給のために、スイッチング電源装置の応答速度の向上や雑音(ノイズ)の低減等の性能向上が要求されている。スイッチング電源装置の性能向上に関する技術が知られている(例えば、特許文献1参照)。

【0003】

図1は、特許文献1に記載の電源制御装置の構成を示すブロック図である。その電源制御装置は、等価外乱Qを考慮した伝達関数Wry(z)、WQy(z)を含むシステムの伝達要素161と、逆システムWm−1(z)の伝達要素162と、フィルタK(z)を含むロバスト補償器としての伝達要素163とを備えている。

【0004】

伝達要素161の出力である制御量yは、引き出し点164で引き出されて伝達要素162の入力に印加される。伝達要素163の出力と目標値rとを加算する加え合せ点165からの出力は、引き出し点166によって別な加え合せ点167に加算されると共に、伝達要素161に入力される。また加え合せ点167は、引き出し点166で分岐した加え合せ点165からの出力と、伝達要素162の出力との偏差(減算値)を、伝達要素163に供給する。

【0005】

図2は、図1に示した電源制御装置を等価変換したブロック図である。図2を参照すると、この電源制御装置は、入力h、制御量y、第1の等価外乱qy、遅れξがそれぞれ与えられた時に、下記の状態方程式

【数1】

を満足する制御対象要素154と、ディジタル制御器170と、加え合せ点143Eとを含んでいる。第1の等価外乱qyは、加え合せ点143Eによって制御対象要素154からの出力に加算され、その加算結果が制御量yとして出力される。

【0006】

ディジタル制御器170は、k1、k2、k3、k4、k5、k6、k1r、k2r、k3r、ki、kiz、kinの各パラメータを有する伝達要素(フィードバック要素171〜要素182)と、1サンプル遅れに相当する次数1/z(但し、z=exp(jωt))の要素144A、要素144Fと、積分器となる次数1/z−1の要素183と、加え合せ点143A、加え合せ点143B、加え合せ点184、加え合せ点185との組み合わせにより構成される。

【0007】

また、図2に示されているように、パラメータk1rのフィードフォワード要素177と、パラメータk2rのフィードフォワード要素178、パラメータk3rのフィードフォワード要素179には、目標値rが入力として供給されている。また、パラメータk1、パラメータk2、パラメータk6の各フィードバック要素171、フィードバック要素172、フィードバック要素176には、制御量yが入力として供給されている。

【0008】

パラメータk3のフィードバック要素173には、ディジタル制御器170内部における演算遅れ出力ξ1を入力として供給されると共に、目標値rと基準値yとの偏差が、加え合せ点184から次数1/z−1の要素183に入力されている。また、その次数1/z−1の要素183からの遅れ出力ξ4が、パラメータkinの要素182に入力されている。

【0009】

パラメータkinの要素182からの出力と、パラメータk5、k6の各フィードバック要素175、フィードバック要素176からの出力と、パラメータk3rのフィードフォワード要素179からの出力は、第2の加え合せ点185で夫々加算されている。

【0010】

この第2の加え合せ点185で加算した出力は、次数1/zの第1要素144Fに入力され、その次数1/zの第1要素144Fからの遅れ出力ξ3は、パラメータk5のフィードバック要素175と、パラメータki、kizの要素180、要素181に夫々入力されている。

【0011】

パラメータkiの要素180からの出力と、パラメータk1、k3、k4の各フィードバック要素171、173、174からの出力と、パラメータk2rのフィードフォワード要素178からの出力と、第2の等価外乱qvは、第3の加え合せ点143Aで夫々加算されている。

【0012】

この第3の加え合せ点143Aで加算した出力vは、次数1/zの第2要素144Aに入力され、その次数1/zの第2要素144Aからの遅れ出力ξ2と、パラメータk2のフィードバック要素172からの出力と、パラメータk1rのフィードフォワード要素177からの出力と、パラメータkizの要素181からの出力が、第4の加え合せ点143Bで夫々加算されている。上述の次数1/zの第2要素144Aからの遅れ出力ξ2は、パラメータk4のフィードバック要素174に入力され、そして第4の加え合せ点143Bで加算した出力が、入力hとして制御対象要素154に与えられる。

【0013】

換言すると、図2に示されるディジタル制御器で構成される電源制御装置の制御系は、制御量yとパラメータk1との積を出力する第1のフィードバック要素と、その制御量yとパラメータk2との積を出力する第2のフィードバック要素と、第1の遅れ出力ξ1とパラメータk3との積を出力する第3のフィードバック要素と、第2の遅れ出力ξ2とパラメータk4との積を出力する第4のフィードバック要素と、第3の遅れ出力ξ3とパラメータk5との積を出力する第5のフィードバック要素と、その制御量yとパラメータk6との積を出力する第6のフィードバック要素とを含む。

【0014】

また、その制御系は、その制御量yとその目標値rとの偏差を算出する第1の演算要素と、その第1の演算要素からの演算値を積分して第4の遅れ出力ξ4に変換する積分要素と、その積分要素からの第4の遅れ出力ξ4とパラメータkinとの積を出力する第1の積算要素と、その第1の積算要素からの出力、その第5のフィードバック要素からの出力、およびその第6のフィードバック要素からの出力を加算する第1の加算要素と、その第1の加算要素からの加算結果をサンプリング遅れさせたその第3の遅れ出力ξ3とする第1の遅延要素と、その第3の遅れ出力ξ3とパラメータkiとの積を出力する第2の積算要素と、その第3の遅れ出力ξ3とパラメータkizとの積を出力する第3の積算要素とを含む。

【0015】

そして、その制御系は、第2の等価外乱qv、その第2の積算要素からの出力、その第1のフィードバック要素からの出力、その第3のフィードバック要素からの出力、およびその第4のフィードバック要素からの出力を加算する第2の加算要素と、その第2の加算要素からの加算結果をサンプリング遅れさせたその第2の遅れ出力ξ2とする第2の遅延要素と、その第2の遅延要素からの出力、その第3の積算要素からの出力、およびその第2のフィードバック要素からの出力を加算し、その制御対象に対する入力hを生成する第3の加算要素とを含む。

【0016】

ここで、加え合せ点143Aは、第1の加算要素と第2の加算要素に対応し、加え合せ点143Bは、第2の加算要素と第3の加算要素に対応し、要素144Aはと第2の遅延要素に対応し、要素144Fは、第1の遅延要素と遅延要素に対応する。また、制御対象要素154と制御対象とが対応し、フィードバック要素171と第1のフィードバック要素とが対応し、フィードバック要素172と第2のフィードバック要素とが対応し、フィードバック要素173と第3のフィードバック要素とが対応し、フィードバック要素174と第4のフィードバック要素とが対応し、フィードバック要素175と第5のフィードバック要素とが対応し、フィードバック要素176と第6のフィードバック要素とが対応している。また、フィードフォワード要素177と第1のフィードフォワード要素とが対応し、フィードフォワード要素178と第2のフィードフォワード要素とが対応し、フィードフォワード要素179と第3のフィードフォワード要素とが対応している。また、要素80と第2の積算要素に対応し、要素82と第1の積算要素とが対応し、要素83と積分要素とが対応し、第1の加え合せ点84と第1の演算要素とが対応し、第2の加え合せ点85と第1の加算要素とが対応し、第1の加え合せ点87と第1の演算要素とが対応している。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2006−050723号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

スイッチング電源装置の性能向上要求を満たすためには、システムの動作状態に合わせた電源供給を実現することが必要であり、サーバ等の大型装置向けに使用されているディジタル制御方式のスイッチング電源装置を小型化して民生機器に搭載する必要性が高まってきた。

【0019】

上述の特許文献1に記載の技術は、広範な負荷変動に対しても、また直流電源の電圧変動に対しても、1個の制御器で対応できるいわゆるロバストなPWM電力増幅器を目的とした技術であり、制御対象を離散時間系で表現し、DSPを用いて状態フィードバック系を構成し、フィードバック系を近似して得られるロバスト補償器を制御対象に結合するものであり、出力ノイズに強いディジタル制御器を実現させている。

【0020】

しかしながら、上述の特許文献1に記載の技術は、回路面積が大きくなるという問題がある。その理由は、ディジタル制御器で構成する制御系が、定数との積を出力する第1〜第6のフィードバック要素と、第1〜第3の積算要素と、第1〜第3のフィードフォワード要素とを有することにより、制御系をハードウェアで実現する場合には12個の積算器が必要のため、回路の小型化ができないためである。

【課題を解決するための手段】

【0021】

以下に、[発明を実施するための形態]で使用される番号を用いて、[課題を解決するための手段]を説明する。これらの番号は、[特許請求の範囲]の記載と[発明を実施するための形態]との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0022】

上記の課題を解決するために、目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、第1の伝達関数Wc(z)の特性を有し、差分信号に基づいて制御信号を生成する補償器(101)と、第2の伝達関数Wp(z)の特性を有し、制御信号に応じて生成される出力信号を出力する制御対象(102)と、第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有し、制御量yに対応する出力信号に基づいて外乱キャンセル信号を生成する外乱キャンセル器(103)と、第1の加算器の出力と外乱キャンセル信号とに基づいて差分外乱信号を生成する第2の加算器と、第4の伝達関数K(z)の特性を有し、差分外乱信号に基づいてフィードバック信号を生成するフィルタ回路(104)とを具備する電源制御装置(1)を構成する。ここにおいて、補償器は、差分信号と出力信号とを入力として受け取り、差分信号と出力信号との各々に基づいて、制御量yを目標値に一致させる補償動作を行う。

【発明の効果】

【0023】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、ディジタル制御方式のスイッチング電源制御装置において、伝達関数Wc(z)

の特性を有する補償器と、伝達関数Wp(z)の特性を有する制御対象と、伝達関数

{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}

の特性を有する外乱キャンセル器を有することでコンデンサの容量や入力電圧の条件の影響が小さい電源制御装置を構成することができる。

その補償器と制御対象と外乱キャンセル器の伝達関数を近似および等価変換して得られる回路が、制御対象の比例補償を行う比例補償ゲインKpと、制御対象の積分補償を行う積分補償ゲインKiと、外乱の伝達をキャンセルするフィードバックゲインKfと、フィルタ回路ゲインKzの4つの積算器で構成できる。そのため、従来技術に比べて積算器の数を大幅に減らすことができ、電源制御装置の回路規模を小さくすることができる効果がある。

【図面の簡単な説明】

【0024】

【図1】図1は、特許文献1に記載の電源制御装置の構成を示すブロック図である。

【図2】図2は、特許文献1に記載の電源制御装置を等価変換したブロック図である。

【図3】図3は、本実施形態の電源制御装置の構成を例示する回路図である。

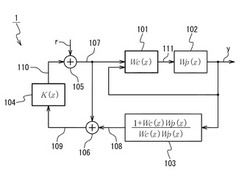

【図4】図4は、本実施形態の電源制御装置1を、伝達関数を用いて表した場合のブロック図である。

【図5】図5は、本実施形態の補償器101の構成を例示するブロック図である。

【図6】図6は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図7】図7は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図8】図8は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図9A】図9Aは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。

【図9B】図9Bは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。

【図10A】図10Aは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。

【図10B】図10Bは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。

【図11】図11は、本実施形態の電源制御装置1の入力電圧が変化した場合の起動時における出力電圧の応答特性を示すグラフである。

【発明を実施するための形態】

【0025】

以下、本発明の実施の形態を図面に基づいて説明する。なお、実施の形態を説明するための図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0026】

図3は、本実施形態の電源制御装置1の構成を例示する回路図である。本実施形態の電源制御装置1は、降圧DCDCコンバータ2と、A/D変換器ADCと、コントローラCNTとを備えている。降圧DCDCコンバータ2には、入力電圧Viを供給する電源と、ハイサイドスイッチング素子SW1と、ロウサイドスイッチング素子SW2と、インダクタLと、抵抗Rと、コンデンサCと、負荷抵抗Rと、パルス発生器PWMと、ドライバDRVとが備えられている。

【0027】

降圧DCDCコンバータ2の電源は、ハイサイドスイッチング素子SW1に接続されている。また、その電源の接地電圧側には、ロウサイドスイッチング素子SW2が接続されている。ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2は接続ノードを介して接続されている。その接続ノードには、インダクタLと、そのインダクタLの直流抵抗成分の抵抗Rと、コンデンサCとで構成されたLC平滑化フィルタが接続されている。抵抗RとコンデンサCとを接続するノードには、負荷抵抗Rが接続され、その負荷抵抗Rの両端の電圧が出力電圧Voとなる。

【0028】

A/D変換器ADCは、出力電圧Voを入力として受ける。A/D変換器ADCは、出力電圧VoをAD変換して、コントローラCNTにディジタルコードを出力する。コントローラCNTは、A/D変換器ADCが出力するディジタルコードを入力として受ける。コントローラCNTは、受け取ったディジタルコードに応答して生成した制御出力をパルス発生器PWMに供給する。ドライバDRVは、パルス発生器PWMからの出力を受け取り、ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2の開閉を制御するためのパルス信号を出力する。

【0029】

図4は、本実施形態の電源制御装置1を、伝達関数を用いて表した場合のブロック図である。本実施形態の電源制御装置1は、補償器101と、制御対象102と、外乱キャンセル器103と、第2加算器106と、フィルタ回路104と、第1加算器105とを備えている。

【0030】

補償器101は、差分信号107と制御量yとを入力として受け、制御信号111を出力する。補償器101は、下記(1)式で表される伝達関数Wc(z)の特性を有している。

【数2】

その補償器101は、制御対象102に対し、積算係数Kpの項で比例補償をし、積算係数Kiを有する項で積分補償を行うことで制御量yを目標値rに一致させるように補償動作を行う。

【0031】

制御対象102は、制御信号111を入力として受け、制御量yを出力する。その制御対象102は、下記(2)式で表される伝達関数Wp(z)の特性を有している。

【数3】

ここで、(2)式において、Kdはゲイン、e1とe2は零点、d1、d2およびd3は極を表すものとする。

【0032】

ここで、差分信号107を入力し補償器101と制御対象102を伝達して制御量yを出力する合成伝達関数Wcp(z)は、下記(3)式で表される。

【数4】

【0033】

外乱キャンセル器103は、制御量yに対して(3)式の逆伝達特性を有する。その伝達関数Wcp(z)−1は、下記(4)式で表される。

【数5】

そして、外乱キャンセル器103は、制御量yを入力として受け、外乱キャンセル信号108を出力する。

【0034】

第2加算器106は、差分信号107と外乱キャンセル信号108とを入力として受け、差分外乱信号109を出力する。外乱キャンセル器103が、第2加算器106が外乱キャンセル信号108と差分信号107の差分を算出することで、合成伝達関数Wcp(z)では伝達しないが制御量yに加えられたノイズを抽出した信号である差分外乱信号109を算出する。

【0035】

フィルタ回路104は、下記(5)式で表される伝達関数K(z)の特性を有し、差分外乱信号109を入力として受け、フィードバック信号110を出力する。

【数6】

フィルタ回路104は、伝達関数K(z)は、差分外乱信号109の入力に対してロウパス特性を有している。したがって、フィルタ回路104によって差分外乱信号109の低周波数成分が除去される。なお、積算係数Kzはロウパス特性の周波数特性を決定する。

【0036】

第1加算器105は、目標値rとフィードバック信号110とを入力として受け、差分信号107を出力する。第1加算器105は、フィードバック信号110と目標値rとの差分を算出し、差分信号107を出力することで、制御量yと目標値rとを一致させるように補償動作を行う。

【0037】

図5は、本実施形態の補償器101の構成を例示するブロック図である。補償器101は、比例補償ゲインブロック204と、積分補償ゲインブロック205と、第3加算器201と、第4加算器202と、第5加算器203と、遅延器206とを備えている。比例補償ゲインブロック204は、第3加算器201の出力を入力として受け取り、積算係数Kpとの積を第5加算器203に出力する。積分補償ゲインブロック205は、第3加算器201の出力を入力として受け取り、積算係数Kiとの積を第4加算器202に出力する。

【0038】

第3加算器201は、差分信号107と制御量yとを加算し、比例補償ゲインブロック204と積分補償ゲインブロック205に、その加算結果を出力する。第4加算器202は、積分補償ゲインブロック205の出力と遅延器206の出力とを加算し、遅延器206に、その加算結果を出力する。第5加算器203は、比例補償ゲインブロック204の出力と遅延器206の出力とを加算し、その加算結果を制御信号111として出力する。遅延器206は、第4加算器202の出力を入力として受け取り、単位時間だけ遅らせて第5加算器203に出力する。

【0039】

図6は、図4の電源制御装置1を等価変換した回路を例示するブロック図である。図6には、本実施形態の理解を容易にするために、図4および図5と同一の構成部分に、同一の参照符号を付与している。図6に示す電源制御装置1は、図5の補償器101と同様の補償器101と、制御対象102と、外乱キャンセル器103と、フィルタ回路104とを備えている。上述のように、外乱キャンセル器103は、(3)式で表される合成伝達関数Wcp(z)の逆伝達特性を有している。

【0040】

ここにおいて、上述の(3)式で表される合成伝達関数Wcp(z)は、その合成伝達関数Wcp(z)が有する極のうち、過渡応答の大勢を決定する極P1、すなわち0<|P1|<1で、最大の絶対値となる極を1つ有し、ゲインが1である下記(6)式に表す伝達関数に近似する。

【数7】

したがって、外乱キャンセル器103は、

【数8】

で表される特性を有する。

【0041】

また、フィルタ回路104は、フィルタ回路ゲインブロック303と、遅延器305と、加算器307とを備えている。フィルタ回路ゲインブロック303は、遅延器305からの出力を入力として受け取り、積算係数Kzとの積を第1加算器105に出力する。また、加算器307には、遅延器305の出力がフィードバックされる。

【0042】

図7は、図6の電源制御装置1を等価変換した回路を例示するブロック図である。図7に例示されているように、外乱キャンセル器103は、要素103A、要素103B、および要素103Cの特性を有する伝達関数に分割される。また、等価変換された電源制御装置1には、第2加算器106と加算器307とを合わせて、第7加算器306が構成されている。

【0043】

図8は、図7の電源制御装置1を、さらに等価変換した回路を例示するブロック図である。その電源制御装置1は、制御対象102と、コントローラ機能ブロック301とで構成されている。コントローラ機能ブロック301には、制御量yと、要素103Aの特性を有するフィードバックを合わせることによってフィードバックゲインブロック302が構成されている。また、要素103Bと要素103Cとを合算することで、ゲインが1となり、乗算係数の無いフィードバックが形成されている。さらに、第1加算器105と第3加算器201が合わさることで、第6加算器304が構成されている。

【0044】

また、コントローラ機能ブロック301は、第4加算器202と、第5加算器203と、比例補償ゲインブロック204と、積分補償ゲインブロック205と、遅延器206と、コントローラ機能ブロック301は、フィルタ回路ゲインブロック303と、第6加算器304と、遅延器305と、第7加算器306を備えている。

【0045】

フィルタ回路ゲインブロック303は、遅延器305からの出力を入力として受けとる。そして、受け取った出力と積算係数Kzとの積を演算して第6加算器304に出力する。第6加算器304は、目標値rとフィードバックゲインブロック302の出力とフィルタ回路ゲインブロック303の出力を加算し、比例補償ゲインブロック204および積分補償ゲインブロック205に加算結果を出力する。遅延器305は、第7加算器306からの出力を入力として受け取る。そして受け取った出力を単位時間だけ遅らせてフィルタ回路ゲインブロック303に出力する。第7加算器306は、目標値rと制御量yと遅延器305の出力を加算し、遅延器305に加算結果を出力する。

【0046】

上述したように、外乱キャンセル器103の伝達関数を(6)式の逆伝達関数としたとき、図4の電源制御装置1を等価変換することにより、図8のブロック図に示されるようなコントローラ機能ブロック301が構成される。図8のコントローラ機能ブロック301において、フィードバックゲインブロック302のフィードバックゲインKfは、下記(8)式で表される。

【数9】

【0047】

このコントローラ機能ブロック301は、図4の電源制御装置1のコントローラCNTに相当する。図8に示されているように、本実施形態の電源制御装置1は、4つの積算器(比例補償ゲインブロック204、積分補償ゲインブロック205、フィードバックゲインブロック302、フィルタ回路ゲインブロック303)と、4つの加算器(第4加算器202、第5加算器203、第6加算器304、第7加算器306)と、2つの遅延器(遅延器206、遅延器305)とでコントローラCNTを構成することができる。

【0048】

また、本実施形態の電源制御装置1は、電源制御装置の回路規模を小さくしつつ、十分安定した応答特性を実現することができる。以下に、本実施形態の電源制御装置1の動作について、具体的な回路を参照しながら説明する。上述の図3を参照すると、入力電圧Viは、ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2のオン/オフ制御によってLC平滑フィルタのL成分、C成分を介して直流電圧である出力電圧Voに変換される。

【0049】

その出力電圧Voは、A/D変換器ADCを介してディジタル出力電圧信号に変換される。コントローラCNTは、出力電圧Voが発振せずに安定した出力をするように制御演算をする。コントローラCNTの出力は、パルス発生器PWMでパルス信号に変換した後、ドライバDRVを介してハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2とを駆動するオン/オフ時間比に変換される。

【0050】

電源制御装置1のコントローラCNTは、図8のコントローラ機能ブロック301に相当している。また、降圧DCDCコンバータ2は、制御対象102に相当している。降圧DCDCコンバータ2を状態方程式は、下記(9)式で表される。

【数10】

【0051】

その(9)式をスイッチング周期Tで離散化した離散状態方程式は、(10)式で表される。

【数11】

【0052】

その(10)式の伝達関数は、下記(11)式で表され、制御対象102の伝達関数Wp(z)が求められる。その(11)式において、Iは単位行列を、adjは余因子行列を、detは行列式を表す。

【数12】

【0053】

以下に、本実施形態の電源制御装置1の作用効果について説明する。上述の図3の降圧DCDCコンバータ2を構成している各要素が、以下の条件であるとする。

Vi=3.3V

C=10uF

L=2.2uF

r=0.72Ω

R=5Ω

このとき、その条件を(11)式に代入すると、制御対象102に相当する降圧DCDCコンバータ2の伝達関数は、(12)式になる。

【数13】

【0054】

一方、補償器101の条件を、

Kp=1.9

Ki=0.05

としたとき、補償器101の伝達関数は(13)式である。

【数14】

【0055】

したがって、制御対象と補償器の合成伝達関数は、(14)式である。

【数15】

【0056】

(14)式の合成伝達関数の極のうち、絶対値が最大の極をP1=0.98433と定め(8)式に代入する。その結果、コントローラ機能ブロック301におけるフィードバックゲインKfは、下記(15)式で示される値になる。

【数16】

0<Kzで推移させて出力電圧Voの応答を確認し、出力電圧Voが発振せずに安定するKz=0.22を設定することで安定した応答特性を有する電源制御装置を実現することができる。

【0057】

図9A、図9Bは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。図9Aは時間経過に対する出力電圧の変化を示す波形図である。図9Bは、時間経過に対する負荷電流の変化を示す波形図である。図9A、図9Bに示されているように、負荷電流(コイル電流i)は、200mAから400mAに急に変化している。このとき、出力電圧Voの変動は、25mV以下に抑えられており、十分安定した応答特性を実現することができる。

【0058】

図10A、図10Bは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。図10Aは、コンデンサCoの容量を7μFにした場合と、13μFにした場合の時間経過に対する出力電圧の変化を示す波形図である。図10Bは、負荷電流(コイル電流i)を200mAから400mAに急に変化させた場合の時間経過に対する負荷電流の変化を示す波形図である。コンデンサCoの容量を7μFにした場合と、13μFにした場合に、負荷電流(コイル電流i)を200mAから400mAに急に変化させた場合の応答を比較してみると、出力電圧Voの変動に大きな差が発生せずに十分安定した応答特性を実現することができる。

【0059】

図11は、本実施形態の電源制御装置1の入力電圧が変化した場合の起動時における出力電圧の応答特性を示すグラフである。図11には、入力電圧Viを3.0Vにした場合と、3.6Vにした場合の起動時の応答特性を示す波形が例示されている。図11に示されているように、入力電圧Viを3.0Vにした場合と、3.6Vにした場合であっても、本実施形態の電源制御装置1は、比較してみると、起動時間や過渡応答に大きな差が発生せずに十分安定した応答特性を実現することができる。

【0060】

図10A、図10Bおよび図11に示されているように、本実施形態の電源制御装置1は、コンデンサCoの容量や入力電圧Viの条件に依存しない、いわゆるロバスト性を有する電源制御装置として構成されている。また、その電源制御装置1は、比例補償ゲインブロック204と、積分補償ゲインブロック205と、フィードバックゲインブロック302と、フィルタ回路ゲインブロック303の4つの積算器と第4加算器202と、第5加算器203と、第6加算器304と、第7加算器306の4つの加算器と遅延器206と遅延器305の2つの遅延器で電源制御装置1のコントローラCNTを構成することができる。そのため、従来の技術に比べて積算器が8個減らすことができる。これにより、回路規模が小さく、かつ十分に安定した応答特性を有する電源制御装置を構成することができる。

【0061】

以上、本願発明の実施の形態を具体的に説明した。本願発明は上述の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【符号の説明】

【0062】

1…電源制御装置

2…降圧DCDCコンバータ

101…補償器

102…制御対象

103…外乱キャンセル器

103A…要素

103B…要素

103C…要素

104…フィルタ回路

105…第1加算器

106…第2加算器

107…差分信号

108…外乱キャンセル信号

109…差分外乱信号

110…フィードバック信号

111…制御信号

201…第3加算器

202…第4加算器

203…第5加算器

204…比例補償ゲインブロック

205…積分補償ゲインブロック

206…遅延器

301…コントローラ機能ブロック

302…フィードバックゲインブロック

303…フィルタ回路ゲインブロック

304…第6加算器

305…遅延器

306…第7加算器

307…加算器

ADC…A/D変換器

CNT…コントローラ

Vi…入力電圧

Vo…出力電圧

SW1…ハイサイドスイッチング素子

SW2…ロウサイドスイッチング素子

L…インダクタ

R…抵抗

R1…負荷抵抗

r…目標値

y…制御量

143A…加え合せ点

143B…加え合せ点

143E…加え合せ点

144A…要素

144F…要素

154…制御対象要素

161…伝達要素

162…伝達要素

163…伝達要素

164…引き出し点

165…加え合せ点

166…引き出し点

167…加え合せ点

170…ディジタル制御器

171…フィードバック要素

172…フィードバック要素

173…フィードバック要素

174…フィードバック要素

175…フィードバック要素

176…フィードバック要素

177…フィードフォワード要素

178…フィードフォワード要素

179…フィードフォワード要素

180…要素

181…要素

182…要素

183…要素

184…加え合せ点

185…加え合せ点

【技術分野】

【0001】

本発明は、電源制御装置に関し、特に、ディジタル制御方式のスイッチング電源制御装置を小型化する技術に関する。

【背景技術】

【0002】

近年、ディジタル家電や携帯機器等の民生機器において、通信状況に応じた動作シーケンスと連携した電源供給のために、スイッチング電源装置の応答速度の向上や雑音(ノイズ)の低減等の性能向上が要求されている。スイッチング電源装置の性能向上に関する技術が知られている(例えば、特許文献1参照)。

【0003】

図1は、特許文献1に記載の電源制御装置の構成を示すブロック図である。その電源制御装置は、等価外乱Qを考慮した伝達関数Wry(z)、WQy(z)を含むシステムの伝達要素161と、逆システムWm−1(z)の伝達要素162と、フィルタK(z)を含むロバスト補償器としての伝達要素163とを備えている。

【0004】

伝達要素161の出力である制御量yは、引き出し点164で引き出されて伝達要素162の入力に印加される。伝達要素163の出力と目標値rとを加算する加え合せ点165からの出力は、引き出し点166によって別な加え合せ点167に加算されると共に、伝達要素161に入力される。また加え合せ点167は、引き出し点166で分岐した加え合せ点165からの出力と、伝達要素162の出力との偏差(減算値)を、伝達要素163に供給する。

【0005】

図2は、図1に示した電源制御装置を等価変換したブロック図である。図2を参照すると、この電源制御装置は、入力h、制御量y、第1の等価外乱qy、遅れξがそれぞれ与えられた時に、下記の状態方程式

【数1】

を満足する制御対象要素154と、ディジタル制御器170と、加え合せ点143Eとを含んでいる。第1の等価外乱qyは、加え合せ点143Eによって制御対象要素154からの出力に加算され、その加算結果が制御量yとして出力される。

【0006】

ディジタル制御器170は、k1、k2、k3、k4、k5、k6、k1r、k2r、k3r、ki、kiz、kinの各パラメータを有する伝達要素(フィードバック要素171〜要素182)と、1サンプル遅れに相当する次数1/z(但し、z=exp(jωt))の要素144A、要素144Fと、積分器となる次数1/z−1の要素183と、加え合せ点143A、加え合せ点143B、加え合せ点184、加え合せ点185との組み合わせにより構成される。

【0007】

また、図2に示されているように、パラメータk1rのフィードフォワード要素177と、パラメータk2rのフィードフォワード要素178、パラメータk3rのフィードフォワード要素179には、目標値rが入力として供給されている。また、パラメータk1、パラメータk2、パラメータk6の各フィードバック要素171、フィードバック要素172、フィードバック要素176には、制御量yが入力として供給されている。

【0008】

パラメータk3のフィードバック要素173には、ディジタル制御器170内部における演算遅れ出力ξ1を入力として供給されると共に、目標値rと基準値yとの偏差が、加え合せ点184から次数1/z−1の要素183に入力されている。また、その次数1/z−1の要素183からの遅れ出力ξ4が、パラメータkinの要素182に入力されている。

【0009】

パラメータkinの要素182からの出力と、パラメータk5、k6の各フィードバック要素175、フィードバック要素176からの出力と、パラメータk3rのフィードフォワード要素179からの出力は、第2の加え合せ点185で夫々加算されている。

【0010】

この第2の加え合せ点185で加算した出力は、次数1/zの第1要素144Fに入力され、その次数1/zの第1要素144Fからの遅れ出力ξ3は、パラメータk5のフィードバック要素175と、パラメータki、kizの要素180、要素181に夫々入力されている。

【0011】

パラメータkiの要素180からの出力と、パラメータk1、k3、k4の各フィードバック要素171、173、174からの出力と、パラメータk2rのフィードフォワード要素178からの出力と、第2の等価外乱qvは、第3の加え合せ点143Aで夫々加算されている。

【0012】

この第3の加え合せ点143Aで加算した出力vは、次数1/zの第2要素144Aに入力され、その次数1/zの第2要素144Aからの遅れ出力ξ2と、パラメータk2のフィードバック要素172からの出力と、パラメータk1rのフィードフォワード要素177からの出力と、パラメータkizの要素181からの出力が、第4の加え合せ点143Bで夫々加算されている。上述の次数1/zの第2要素144Aからの遅れ出力ξ2は、パラメータk4のフィードバック要素174に入力され、そして第4の加え合せ点143Bで加算した出力が、入力hとして制御対象要素154に与えられる。

【0013】

換言すると、図2に示されるディジタル制御器で構成される電源制御装置の制御系は、制御量yとパラメータk1との積を出力する第1のフィードバック要素と、その制御量yとパラメータk2との積を出力する第2のフィードバック要素と、第1の遅れ出力ξ1とパラメータk3との積を出力する第3のフィードバック要素と、第2の遅れ出力ξ2とパラメータk4との積を出力する第4のフィードバック要素と、第3の遅れ出力ξ3とパラメータk5との積を出力する第5のフィードバック要素と、その制御量yとパラメータk6との積を出力する第6のフィードバック要素とを含む。

【0014】

また、その制御系は、その制御量yとその目標値rとの偏差を算出する第1の演算要素と、その第1の演算要素からの演算値を積分して第4の遅れ出力ξ4に変換する積分要素と、その積分要素からの第4の遅れ出力ξ4とパラメータkinとの積を出力する第1の積算要素と、その第1の積算要素からの出力、その第5のフィードバック要素からの出力、およびその第6のフィードバック要素からの出力を加算する第1の加算要素と、その第1の加算要素からの加算結果をサンプリング遅れさせたその第3の遅れ出力ξ3とする第1の遅延要素と、その第3の遅れ出力ξ3とパラメータkiとの積を出力する第2の積算要素と、その第3の遅れ出力ξ3とパラメータkizとの積を出力する第3の積算要素とを含む。

【0015】

そして、その制御系は、第2の等価外乱qv、その第2の積算要素からの出力、その第1のフィードバック要素からの出力、その第3のフィードバック要素からの出力、およびその第4のフィードバック要素からの出力を加算する第2の加算要素と、その第2の加算要素からの加算結果をサンプリング遅れさせたその第2の遅れ出力ξ2とする第2の遅延要素と、その第2の遅延要素からの出力、その第3の積算要素からの出力、およびその第2のフィードバック要素からの出力を加算し、その制御対象に対する入力hを生成する第3の加算要素とを含む。

【0016】

ここで、加え合せ点143Aは、第1の加算要素と第2の加算要素に対応し、加え合せ点143Bは、第2の加算要素と第3の加算要素に対応し、要素144Aはと第2の遅延要素に対応し、要素144Fは、第1の遅延要素と遅延要素に対応する。また、制御対象要素154と制御対象とが対応し、フィードバック要素171と第1のフィードバック要素とが対応し、フィードバック要素172と第2のフィードバック要素とが対応し、フィードバック要素173と第3のフィードバック要素とが対応し、フィードバック要素174と第4のフィードバック要素とが対応し、フィードバック要素175と第5のフィードバック要素とが対応し、フィードバック要素176と第6のフィードバック要素とが対応している。また、フィードフォワード要素177と第1のフィードフォワード要素とが対応し、フィードフォワード要素178と第2のフィードフォワード要素とが対応し、フィードフォワード要素179と第3のフィードフォワード要素とが対応している。また、要素80と第2の積算要素に対応し、要素82と第1の積算要素とが対応し、要素83と積分要素とが対応し、第1の加え合せ点84と第1の演算要素とが対応し、第2の加え合せ点85と第1の加算要素とが対応し、第1の加え合せ点87と第1の演算要素とが対応している。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2006−050723号公報

【発明の概要】

【発明が解決しようとする課題】

【0018】

スイッチング電源装置の性能向上要求を満たすためには、システムの動作状態に合わせた電源供給を実現することが必要であり、サーバ等の大型装置向けに使用されているディジタル制御方式のスイッチング電源装置を小型化して民生機器に搭載する必要性が高まってきた。

【0019】

上述の特許文献1に記載の技術は、広範な負荷変動に対しても、また直流電源の電圧変動に対しても、1個の制御器で対応できるいわゆるロバストなPWM電力増幅器を目的とした技術であり、制御対象を離散時間系で表現し、DSPを用いて状態フィードバック系を構成し、フィードバック系を近似して得られるロバスト補償器を制御対象に結合するものであり、出力ノイズに強いディジタル制御器を実現させている。

【0020】

しかしながら、上述の特許文献1に記載の技術は、回路面積が大きくなるという問題がある。その理由は、ディジタル制御器で構成する制御系が、定数との積を出力する第1〜第6のフィードバック要素と、第1〜第3の積算要素と、第1〜第3のフィードフォワード要素とを有することにより、制御系をハードウェアで実現する場合には12個の積算器が必要のため、回路の小型化ができないためである。

【課題を解決するための手段】

【0021】

以下に、[発明を実施するための形態]で使用される番号を用いて、[課題を解決するための手段]を説明する。これらの番号は、[特許請求の範囲]の記載と[発明を実施するための形態]との対応関係を明らかにするために付加されたものである。ただし、それらの番号を、[特許請求の範囲]に記載されている発明の技術的範囲の解釈に用いてはならない。

【0022】

上記の課題を解決するために、目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、第1の伝達関数Wc(z)の特性を有し、差分信号に基づいて制御信号を生成する補償器(101)と、第2の伝達関数Wp(z)の特性を有し、制御信号に応じて生成される出力信号を出力する制御対象(102)と、第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有し、制御量yに対応する出力信号に基づいて外乱キャンセル信号を生成する外乱キャンセル器(103)と、第1の加算器の出力と外乱キャンセル信号とに基づいて差分外乱信号を生成する第2の加算器と、第4の伝達関数K(z)の特性を有し、差分外乱信号に基づいてフィードバック信号を生成するフィルタ回路(104)とを具備する電源制御装置(1)を構成する。ここにおいて、補償器は、差分信号と出力信号とを入力として受け取り、差分信号と出力信号との各々に基づいて、制御量yを目標値に一致させる補償動作を行う。

【発明の効果】

【0023】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、ディジタル制御方式のスイッチング電源制御装置において、伝達関数Wc(z)

の特性を有する補償器と、伝達関数Wp(z)の特性を有する制御対象と、伝達関数

{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}

の特性を有する外乱キャンセル器を有することでコンデンサの容量や入力電圧の条件の影響が小さい電源制御装置を構成することができる。

その補償器と制御対象と外乱キャンセル器の伝達関数を近似および等価変換して得られる回路が、制御対象の比例補償を行う比例補償ゲインKpと、制御対象の積分補償を行う積分補償ゲインKiと、外乱の伝達をキャンセルするフィードバックゲインKfと、フィルタ回路ゲインKzの4つの積算器で構成できる。そのため、従来技術に比べて積算器の数を大幅に減らすことができ、電源制御装置の回路規模を小さくすることができる効果がある。

【図面の簡単な説明】

【0024】

【図1】図1は、特許文献1に記載の電源制御装置の構成を示すブロック図である。

【図2】図2は、特許文献1に記載の電源制御装置を等価変換したブロック図である。

【図3】図3は、本実施形態の電源制御装置の構成を例示する回路図である。

【図4】図4は、本実施形態の電源制御装置1を、伝達関数を用いて表した場合のブロック図である。

【図5】図5は、本実施形態の補償器101の構成を例示するブロック図である。

【図6】図6は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図7】図7は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図8】図8は、電源制御装置1を等価変換した回路を例示するブロック図である。

【図9A】図9Aは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。

【図9B】図9Bは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。

【図10A】図10Aは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。

【図10B】図10Bは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。

【図11】図11は、本実施形態の電源制御装置1の入力電圧が変化した場合の起動時における出力電圧の応答特性を示すグラフである。

【発明を実施するための形態】

【0025】

以下、本発明の実施の形態を図面に基づいて説明する。なお、実施の形態を説明するための図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

【0026】

図3は、本実施形態の電源制御装置1の構成を例示する回路図である。本実施形態の電源制御装置1は、降圧DCDCコンバータ2と、A/D変換器ADCと、コントローラCNTとを備えている。降圧DCDCコンバータ2には、入力電圧Viを供給する電源と、ハイサイドスイッチング素子SW1と、ロウサイドスイッチング素子SW2と、インダクタLと、抵抗Rと、コンデンサCと、負荷抵抗Rと、パルス発生器PWMと、ドライバDRVとが備えられている。

【0027】

降圧DCDCコンバータ2の電源は、ハイサイドスイッチング素子SW1に接続されている。また、その電源の接地電圧側には、ロウサイドスイッチング素子SW2が接続されている。ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2は接続ノードを介して接続されている。その接続ノードには、インダクタLと、そのインダクタLの直流抵抗成分の抵抗Rと、コンデンサCとで構成されたLC平滑化フィルタが接続されている。抵抗RとコンデンサCとを接続するノードには、負荷抵抗Rが接続され、その負荷抵抗Rの両端の電圧が出力電圧Voとなる。

【0028】

A/D変換器ADCは、出力電圧Voを入力として受ける。A/D変換器ADCは、出力電圧VoをAD変換して、コントローラCNTにディジタルコードを出力する。コントローラCNTは、A/D変換器ADCが出力するディジタルコードを入力として受ける。コントローラCNTは、受け取ったディジタルコードに応答して生成した制御出力をパルス発生器PWMに供給する。ドライバDRVは、パルス発生器PWMからの出力を受け取り、ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2の開閉を制御するためのパルス信号を出力する。

【0029】

図4は、本実施形態の電源制御装置1を、伝達関数を用いて表した場合のブロック図である。本実施形態の電源制御装置1は、補償器101と、制御対象102と、外乱キャンセル器103と、第2加算器106と、フィルタ回路104と、第1加算器105とを備えている。

【0030】

補償器101は、差分信号107と制御量yとを入力として受け、制御信号111を出力する。補償器101は、下記(1)式で表される伝達関数Wc(z)の特性を有している。

【数2】

その補償器101は、制御対象102に対し、積算係数Kpの項で比例補償をし、積算係数Kiを有する項で積分補償を行うことで制御量yを目標値rに一致させるように補償動作を行う。

【0031】

制御対象102は、制御信号111を入力として受け、制御量yを出力する。その制御対象102は、下記(2)式で表される伝達関数Wp(z)の特性を有している。

【数3】

ここで、(2)式において、Kdはゲイン、e1とe2は零点、d1、d2およびd3は極を表すものとする。

【0032】

ここで、差分信号107を入力し補償器101と制御対象102を伝達して制御量yを出力する合成伝達関数Wcp(z)は、下記(3)式で表される。

【数4】

【0033】

外乱キャンセル器103は、制御量yに対して(3)式の逆伝達特性を有する。その伝達関数Wcp(z)−1は、下記(4)式で表される。

【数5】

そして、外乱キャンセル器103は、制御量yを入力として受け、外乱キャンセル信号108を出力する。

【0034】

第2加算器106は、差分信号107と外乱キャンセル信号108とを入力として受け、差分外乱信号109を出力する。外乱キャンセル器103が、第2加算器106が外乱キャンセル信号108と差分信号107の差分を算出することで、合成伝達関数Wcp(z)では伝達しないが制御量yに加えられたノイズを抽出した信号である差分外乱信号109を算出する。

【0035】

フィルタ回路104は、下記(5)式で表される伝達関数K(z)の特性を有し、差分外乱信号109を入力として受け、フィードバック信号110を出力する。

【数6】

フィルタ回路104は、伝達関数K(z)は、差分外乱信号109の入力に対してロウパス特性を有している。したがって、フィルタ回路104によって差分外乱信号109の低周波数成分が除去される。なお、積算係数Kzはロウパス特性の周波数特性を決定する。

【0036】

第1加算器105は、目標値rとフィードバック信号110とを入力として受け、差分信号107を出力する。第1加算器105は、フィードバック信号110と目標値rとの差分を算出し、差分信号107を出力することで、制御量yと目標値rとを一致させるように補償動作を行う。

【0037】

図5は、本実施形態の補償器101の構成を例示するブロック図である。補償器101は、比例補償ゲインブロック204と、積分補償ゲインブロック205と、第3加算器201と、第4加算器202と、第5加算器203と、遅延器206とを備えている。比例補償ゲインブロック204は、第3加算器201の出力を入力として受け取り、積算係数Kpとの積を第5加算器203に出力する。積分補償ゲインブロック205は、第3加算器201の出力を入力として受け取り、積算係数Kiとの積を第4加算器202に出力する。

【0038】

第3加算器201は、差分信号107と制御量yとを加算し、比例補償ゲインブロック204と積分補償ゲインブロック205に、その加算結果を出力する。第4加算器202は、積分補償ゲインブロック205の出力と遅延器206の出力とを加算し、遅延器206に、その加算結果を出力する。第5加算器203は、比例補償ゲインブロック204の出力と遅延器206の出力とを加算し、その加算結果を制御信号111として出力する。遅延器206は、第4加算器202の出力を入力として受け取り、単位時間だけ遅らせて第5加算器203に出力する。

【0039】

図6は、図4の電源制御装置1を等価変換した回路を例示するブロック図である。図6には、本実施形態の理解を容易にするために、図4および図5と同一の構成部分に、同一の参照符号を付与している。図6に示す電源制御装置1は、図5の補償器101と同様の補償器101と、制御対象102と、外乱キャンセル器103と、フィルタ回路104とを備えている。上述のように、外乱キャンセル器103は、(3)式で表される合成伝達関数Wcp(z)の逆伝達特性を有している。

【0040】

ここにおいて、上述の(3)式で表される合成伝達関数Wcp(z)は、その合成伝達関数Wcp(z)が有する極のうち、過渡応答の大勢を決定する極P1、すなわち0<|P1|<1で、最大の絶対値となる極を1つ有し、ゲインが1である下記(6)式に表す伝達関数に近似する。

【数7】

したがって、外乱キャンセル器103は、

【数8】

で表される特性を有する。

【0041】

また、フィルタ回路104は、フィルタ回路ゲインブロック303と、遅延器305と、加算器307とを備えている。フィルタ回路ゲインブロック303は、遅延器305からの出力を入力として受け取り、積算係数Kzとの積を第1加算器105に出力する。また、加算器307には、遅延器305の出力がフィードバックされる。

【0042】

図7は、図6の電源制御装置1を等価変換した回路を例示するブロック図である。図7に例示されているように、外乱キャンセル器103は、要素103A、要素103B、および要素103Cの特性を有する伝達関数に分割される。また、等価変換された電源制御装置1には、第2加算器106と加算器307とを合わせて、第7加算器306が構成されている。

【0043】

図8は、図7の電源制御装置1を、さらに等価変換した回路を例示するブロック図である。その電源制御装置1は、制御対象102と、コントローラ機能ブロック301とで構成されている。コントローラ機能ブロック301には、制御量yと、要素103Aの特性を有するフィードバックを合わせることによってフィードバックゲインブロック302が構成されている。また、要素103Bと要素103Cとを合算することで、ゲインが1となり、乗算係数の無いフィードバックが形成されている。さらに、第1加算器105と第3加算器201が合わさることで、第6加算器304が構成されている。

【0044】

また、コントローラ機能ブロック301は、第4加算器202と、第5加算器203と、比例補償ゲインブロック204と、積分補償ゲインブロック205と、遅延器206と、コントローラ機能ブロック301は、フィルタ回路ゲインブロック303と、第6加算器304と、遅延器305と、第7加算器306を備えている。

【0045】

フィルタ回路ゲインブロック303は、遅延器305からの出力を入力として受けとる。そして、受け取った出力と積算係数Kzとの積を演算して第6加算器304に出力する。第6加算器304は、目標値rとフィードバックゲインブロック302の出力とフィルタ回路ゲインブロック303の出力を加算し、比例補償ゲインブロック204および積分補償ゲインブロック205に加算結果を出力する。遅延器305は、第7加算器306からの出力を入力として受け取る。そして受け取った出力を単位時間だけ遅らせてフィルタ回路ゲインブロック303に出力する。第7加算器306は、目標値rと制御量yと遅延器305の出力を加算し、遅延器305に加算結果を出力する。

【0046】

上述したように、外乱キャンセル器103の伝達関数を(6)式の逆伝達関数としたとき、図4の電源制御装置1を等価変換することにより、図8のブロック図に示されるようなコントローラ機能ブロック301が構成される。図8のコントローラ機能ブロック301において、フィードバックゲインブロック302のフィードバックゲインKfは、下記(8)式で表される。

【数9】

【0047】

このコントローラ機能ブロック301は、図4の電源制御装置1のコントローラCNTに相当する。図8に示されているように、本実施形態の電源制御装置1は、4つの積算器(比例補償ゲインブロック204、積分補償ゲインブロック205、フィードバックゲインブロック302、フィルタ回路ゲインブロック303)と、4つの加算器(第4加算器202、第5加算器203、第6加算器304、第7加算器306)と、2つの遅延器(遅延器206、遅延器305)とでコントローラCNTを構成することができる。

【0048】

また、本実施形態の電源制御装置1は、電源制御装置の回路規模を小さくしつつ、十分安定した応答特性を実現することができる。以下に、本実施形態の電源制御装置1の動作について、具体的な回路を参照しながら説明する。上述の図3を参照すると、入力電圧Viは、ハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2のオン/オフ制御によってLC平滑フィルタのL成分、C成分を介して直流電圧である出力電圧Voに変換される。

【0049】

その出力電圧Voは、A/D変換器ADCを介してディジタル出力電圧信号に変換される。コントローラCNTは、出力電圧Voが発振せずに安定した出力をするように制御演算をする。コントローラCNTの出力は、パルス発生器PWMでパルス信号に変換した後、ドライバDRVを介してハイサイドスイッチング素子SW1とロウサイドスイッチング素子SW2とを駆動するオン/オフ時間比に変換される。

【0050】

電源制御装置1のコントローラCNTは、図8のコントローラ機能ブロック301に相当している。また、降圧DCDCコンバータ2は、制御対象102に相当している。降圧DCDCコンバータ2を状態方程式は、下記(9)式で表される。

【数10】

【0051】

その(9)式をスイッチング周期Tで離散化した離散状態方程式は、(10)式で表される。

【数11】

【0052】

その(10)式の伝達関数は、下記(11)式で表され、制御対象102の伝達関数Wp(z)が求められる。その(11)式において、Iは単位行列を、adjは余因子行列を、detは行列式を表す。

【数12】

【0053】

以下に、本実施形態の電源制御装置1の作用効果について説明する。上述の図3の降圧DCDCコンバータ2を構成している各要素が、以下の条件であるとする。

Vi=3.3V

C=10uF

L=2.2uF

r=0.72Ω

R=5Ω

このとき、その条件を(11)式に代入すると、制御対象102に相当する降圧DCDCコンバータ2の伝達関数は、(12)式になる。

【数13】

【0054】

一方、補償器101の条件を、

Kp=1.9

Ki=0.05

としたとき、補償器101の伝達関数は(13)式である。

【数14】

【0055】

したがって、制御対象と補償器の合成伝達関数は、(14)式である。

【数15】

【0056】

(14)式の合成伝達関数の極のうち、絶対値が最大の極をP1=0.98433と定め(8)式に代入する。その結果、コントローラ機能ブロック301におけるフィードバックゲインKfは、下記(15)式で示される値になる。

【数16】

0<Kzで推移させて出力電圧Voの応答を確認し、出力電圧Voが発振せずに安定するKz=0.22を設定することで安定した応答特性を有する電源制御装置を実現することができる。

【0057】

図9A、図9Bは、本実施形態の電源制御装置1の負荷急変時の動的な負荷応答を示すグラフである。図9Aは時間経過に対する出力電圧の変化を示す波形図である。図9Bは、時間経過に対する負荷電流の変化を示す波形図である。図9A、図9Bに示されているように、負荷電流(コイル電流i)は、200mAから400mAに急に変化している。このとき、出力電圧Voの変動は、25mV以下に抑えられており、十分安定した応答特性を実現することができる。

【0058】

図10A、図10Bは、本実施形態の電源制御装置1のコンデンサ容量が変化した場合の負荷急変時の動的な負荷応答を示すグラフである。図10Aは、コンデンサCoの容量を7μFにした場合と、13μFにした場合の時間経過に対する出力電圧の変化を示す波形図である。図10Bは、負荷電流(コイル電流i)を200mAから400mAに急に変化させた場合の時間経過に対する負荷電流の変化を示す波形図である。コンデンサCoの容量を7μFにした場合と、13μFにした場合に、負荷電流(コイル電流i)を200mAから400mAに急に変化させた場合の応答を比較してみると、出力電圧Voの変動に大きな差が発生せずに十分安定した応答特性を実現することができる。

【0059】

図11は、本実施形態の電源制御装置1の入力電圧が変化した場合の起動時における出力電圧の応答特性を示すグラフである。図11には、入力電圧Viを3.0Vにした場合と、3.6Vにした場合の起動時の応答特性を示す波形が例示されている。図11に示されているように、入力電圧Viを3.0Vにした場合と、3.6Vにした場合であっても、本実施形態の電源制御装置1は、比較してみると、起動時間や過渡応答に大きな差が発生せずに十分安定した応答特性を実現することができる。

【0060】

図10A、図10Bおよび図11に示されているように、本実施形態の電源制御装置1は、コンデンサCoの容量や入力電圧Viの条件に依存しない、いわゆるロバスト性を有する電源制御装置として構成されている。また、その電源制御装置1は、比例補償ゲインブロック204と、積分補償ゲインブロック205と、フィードバックゲインブロック302と、フィルタ回路ゲインブロック303の4つの積算器と第4加算器202と、第5加算器203と、第6加算器304と、第7加算器306の4つの加算器と遅延器206と遅延器305の2つの遅延器で電源制御装置1のコントローラCNTを構成することができる。そのため、従来の技術に比べて積算器が8個減らすことができる。これにより、回路規模が小さく、かつ十分に安定した応答特性を有する電源制御装置を構成することができる。

【0061】

以上、本願発明の実施の形態を具体的に説明した。本願発明は上述の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能である。

【符号の説明】

【0062】

1…電源制御装置

2…降圧DCDCコンバータ

101…補償器

102…制御対象

103…外乱キャンセル器

103A…要素

103B…要素

103C…要素

104…フィルタ回路

105…第1加算器

106…第2加算器

107…差分信号

108…外乱キャンセル信号

109…差分外乱信号

110…フィードバック信号

111…制御信号

201…第3加算器

202…第4加算器

203…第5加算器

204…比例補償ゲインブロック

205…積分補償ゲインブロック

206…遅延器

301…コントローラ機能ブロック

302…フィードバックゲインブロック

303…フィルタ回路ゲインブロック

304…第6加算器

305…遅延器

306…第7加算器

307…加算器

ADC…A/D変換器

CNT…コントローラ

Vi…入力電圧

Vo…出力電圧

SW1…ハイサイドスイッチング素子

SW2…ロウサイドスイッチング素子

L…インダクタ

R…抵抗

R1…負荷抵抗

r…目標値

y…制御量

143A…加え合せ点

143B…加え合せ点

143E…加え合せ点

144A…要素

144F…要素

154…制御対象要素

161…伝達要素

162…伝達要素

163…伝達要素

164…引き出し点

165…加え合せ点

166…引き出し点

167…加え合せ点

170…ディジタル制御器

171…フィードバック要素

172…フィードバック要素

173…フィードバック要素

174…フィードバック要素

175…フィードバック要素

176…フィードバック要素

177…フィードフォワード要素

178…フィードフォワード要素

179…フィードフォワード要素

180…要素

181…要素

182…要素

183…要素

184…加え合せ点

185…加え合せ点

【特許請求の範囲】

【請求項1】

目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、

第1の伝達関数Wc(z)の特性を有し、前記差分信号に基づいて制御信号を生成する補償器と、

第2の伝達関数Wp(z)の特性を有し、前記制御信号に応じて生成される出力信号を出力する制御対象と、

第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有し、制御量yに対応する前記出力信号に基づいて外乱キャンセル信号を生成する外乱キャンセル器と、

前記第1の加算器の出力と前記外乱キャンセル信号とに基づいて差分外乱信号を生成する第2の加算器と、

第4の伝達関数K(z)の特性を有し、前記差分外乱信号に基づいて前記フィードバック信号を生成するフィルタ回路と

を具備し、

前記補償器は、

前記差分信号と前記出力信号とを入力として受け取り、前記差分信号と前記出力信号との各々に基づいて、前記制御量yを前記目標値に一致させる補償動作を行う

電源制御装置。

【請求項2】

請求項1に記載の電源制御装置において、

前記第1の伝達関数は、下記式

【数1】

であらわされる特性を有し、積算係数Kpの項で比例補償を実行し、積算係数Kiを有する項で積分補償を実行し、

前記第2の伝達関数Wp(z)は、Kdをゲイン、e1とe2を零点、d1、d2およびd3を極とするとき、下記式

【数2】

であらわされる特性を有する

電源制御装置。

【請求項3】

請求項2に記載の電源制御装置において、

前記補償器と前記制御対象とは、合成伝達関数Wcp(z)で表され、前記合成伝達関数Wcp(z)は、下記式

【数3】

であらわされる特性を有し、

前記外乱キャンセル器は、

前記制御量yに対して前記合成伝達関数Wcp(z)の逆伝達特性を有する

電源制御装置。

【請求項4】

請求項3に記載の電源制御装置において、

前記外乱キャンセル器は、

前記合成伝達関数が有する極のうち、過渡特性の大勢を決定する極を有し、ゲインが1であることを特徴とする

電源制御装置。

【請求項5】

請求項4に記載の電源制御装置において、

前記フィルタ回路は、下記の積算係数Kzを有する項を含む式

【数4】

であらわされる特性を有し、

前記フィルタ回路と前記補償器と前記外乱キャンセル器とに対応する前記第1の伝達関数と前記第3の伝達関数と前記第4の伝達関数を等価変換した回路は、

前記制御対象の比例補償を前記積算係数Kpで行う比例補償ゲインブロックと、

前記制御対象の積分補償を前記積算係数Kiで行う積分補償ゲインブロックと、

外乱の伝達をキャンセルするフィードバックゲインブロックと、

前記積算係数Kzを有する項を含む式あらわされる特性を有するフィルタ回路ゲインブロックと

を有し、

前記合成伝達関数が有する極のうち、過渡特性の大勢を決定する極を極P1とするとき、前記フィードバックゲインブロックは、

【数5】

であらわされる特性を有する

電源制御装置。

【請求項1】

目標値とフィードバック信号とに基づいて差分信号を生成する第1の加算器と、

第1の伝達関数Wc(z)の特性を有し、前記差分信号に基づいて制御信号を生成する補償器と、

第2の伝達関数Wp(z)の特性を有し、前記制御信号に応じて生成される出力信号を出力する制御対象と、

第3の伝達関数{1+Wc(z)・Wp(z)}/{Wc(z)・Wp(z)}の特性を有し、制御量yに対応する前記出力信号に基づいて外乱キャンセル信号を生成する外乱キャンセル器と、

前記第1の加算器の出力と前記外乱キャンセル信号とに基づいて差分外乱信号を生成する第2の加算器と、

第4の伝達関数K(z)の特性を有し、前記差分外乱信号に基づいて前記フィードバック信号を生成するフィルタ回路と

を具備し、

前記補償器は、

前記差分信号と前記出力信号とを入力として受け取り、前記差分信号と前記出力信号との各々に基づいて、前記制御量yを前記目標値に一致させる補償動作を行う

電源制御装置。

【請求項2】

請求項1に記載の電源制御装置において、

前記第1の伝達関数は、下記式

【数1】

であらわされる特性を有し、積算係数Kpの項で比例補償を実行し、積算係数Kiを有する項で積分補償を実行し、

前記第2の伝達関数Wp(z)は、Kdをゲイン、e1とe2を零点、d1、d2およびd3を極とするとき、下記式

【数2】

であらわされる特性を有する

電源制御装置。

【請求項3】

請求項2に記載の電源制御装置において、

前記補償器と前記制御対象とは、合成伝達関数Wcp(z)で表され、前記合成伝達関数Wcp(z)は、下記式

【数3】

であらわされる特性を有し、

前記外乱キャンセル器は、

前記制御量yに対して前記合成伝達関数Wcp(z)の逆伝達特性を有する

電源制御装置。

【請求項4】

請求項3に記載の電源制御装置において、

前記外乱キャンセル器は、

前記合成伝達関数が有する極のうち、過渡特性の大勢を決定する極を有し、ゲインが1であることを特徴とする

電源制御装置。

【請求項5】

請求項4に記載の電源制御装置において、

前記フィルタ回路は、下記の積算係数Kzを有する項を含む式

【数4】

であらわされる特性を有し、

前記フィルタ回路と前記補償器と前記外乱キャンセル器とに対応する前記第1の伝達関数と前記第3の伝達関数と前記第4の伝達関数を等価変換した回路は、

前記制御対象の比例補償を前記積算係数Kpで行う比例補償ゲインブロックと、

前記制御対象の積分補償を前記積算係数Kiで行う積分補償ゲインブロックと、

外乱の伝達をキャンセルするフィードバックゲインブロックと、

前記積算係数Kzを有する項を含む式あらわされる特性を有するフィルタ回路ゲインブロックと

を有し、

前記合成伝達関数が有する極のうち、過渡特性の大勢を決定する極を極P1とするとき、前記フィードバックゲインブロックは、

【数5】

であらわされる特性を有する

電源制御装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9A】

【図9B】

【図10A】

【図10B】

【図11】

【公開番号】特開2013−110854(P2013−110854A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253983(P2011−253983)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]