電源及びグランド対線路を含む多層配線基板構造

【課題】電源及びグランドの平板構造で見られる低特性インピーダンスを維持しつつ平板に置ける共振モードを防止する構造を提供する。

【解決手段】絶縁物層とパターニングされた導体層とを含む積層体10を有する多層配線基板において、前記積層体10内に互いに平行となるように配置された電源用の第1導電路1及びグランド用の第2導電路2と、前記第1導電路1の上面及び前記第2導電路2の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜3と、第1導電膜4又は第1半導体膜4とを有する第1積層膜と、を備える。

【解決手段】絶縁物層とパターニングされた導体層とを含む積層体10を有する多層配線基板において、前記積層体10内に互いに平行となるように配置された電源用の第1導電路1及びグランド用の第2導電路2と、前記第1導電路1の上面及び前記第2導電路2の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜3と、第1導電膜4又は第1半導体膜4とを有する第1積層膜と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板の電源線に適用される共振防止低インピーダンス電源線に関する技術である。

【背景技術】

【0002】

従来の配線基板電源は多層構造のある層を占有し板状に広がった構造が大半である。

例えば、この種の基板構造としては、例えば、特許文献1に示されるように、電源パターンの多い信号層、アース層、電源層、アースパターンの多い信号層の各層が順に積層された多層構造を有し、前記アース層・電源層間の中央基板層の厚さに対してその両側層の厚さを薄く形成し、前記各信号層の電源パターンとアースパターンとが対向する面積の基板総面積に対する比率を特定割合にした、プリント配線基板が知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−307894号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、このような配線基板では、デジタルやRF回路の高周波動作をするデバイスに供給する電源は回路動作に応じて瞬時応答が求められ、この応答に対応するため、板状に電源とグランドを配置した多層配線基板がよく用いられている。この構造の特徴はどの場所にある回路から見ても電源及びグランド対配線が低インピーダンスとなっていることで、瞬時電流を取り出すことができる。しかし、瞬時応答の電源平板の電流が慣性を持ち、瞬時遮断時に回路部分で反射して、その反射波が平板に均質に広がり、基板の端面で反射しその距離に応じた多重反射共振モードで共振して、電磁放射の原因となるばかりでなく、この電源電圧の揺らぎが自身の回路や他の隣接回路にも影響し、高速動作の大きな障害となるという問題が生じている。

【0005】

本発明は上記のような事情を考慮してなされたものであり、その目的は、電源及びグランドの平板構造で見られる低特性インピーダンスを維持しつつ平板に置ける共振モードを防止する構造を提案するものである。

【課題を解決するための手段】

【0006】

本発明の電源及びグランド対線路を含む多層配線基板構造は、絶縁物層とパターニングされた導体層とを含む積層体からなる多層配線基板において、前記積層体に設けられて互いに平行となるように配置された電源用の第1導電路及びグランド用の第2導電路と、前記第1導電路の上面及び前記第2導電路の上面にまたぐように設けられ、前記第1及び第2導電路側から順に積層された第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜と、を備えることを特徴とする。

【0007】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1積層膜上には、必要に応じて絶縁物層と信号用導体層が形成されていることを特徴とする。

【0008】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路及び前記第2導電路において、幅wと高さtの関係が、w/t≧2であることを特徴とする。

【0009】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路の下面及び前記第2導電路の下面に、前記第1及び第2導電路側から第2絶縁膜と第2導電膜又は第2半導体膜を順次積層した第2積層膜を備えてサンドウィッチ型とすることを特徴とする。

【0010】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路は電流の流れる方向に複数に分岐され、前記第2導電路は元電源側が積層体内で前記第1導電路の下層に位置し、複数分岐された後、ビアホールを経由して前記第1導電路層の分岐電路と交互に配置され、前記第1積層膜は、分岐された交互に配置された複数の第1、第2導電路の分岐導電路上の全体にまたぐように積層されることを特徴とする。

【0011】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1絶縁膜の膜厚が3μm〜30μmであることを特徴とする。

【0012】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜の膜厚が20〜100000nmであることを特徴とする。

【0013】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜は、1Ω/□以上のシート抵抗を有するであることを特徴とする。

【0014】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜は、Fe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物を含むことを特徴とする。

【0015】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜はnmから数千nm単位の径の粒子が重なった表面構造であることを特徴とする。

【0016】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路及び前記第2導電路の分岐構造が複数直列につながっている構造であり、その分岐点では第1又は第2導電路のどちらかがビアホールで下層又は上層で迂回する構造を有することを特徴とする。

【発明の効果】

【0017】

本発明によれば、電源及びグランド対配線を構成する電源用の第1導電路及びグランド用の第2導電路の上面に、これら第1及び第2導電路側から順次、第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜をまたがって積層することにより、単位長さあたりの容量とインダクタンスが大きい伝送線路型の電源及びグランド対配線を提供することができ、特性インピーダンスが低く、電気長が長い特性を併せ持つことができる。

【図面の簡単な説明】

【0018】

【図1】本発明の一実施例に係る多層配線基板の電源及びグランド対線路とLSIパッケージなど実装が予想される部分までの配線と接続状態を示す全体平面図である。

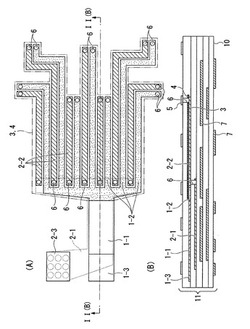

【図2】(A)は第1の実施例に対応する第1、第2導電路1,2の部分を示す部分平面図であり、(B)は図2(A)にII(B)−II(B)に沿う一点鎖線で切断した断面図である。

【図3】本発明の第2の実施例による図2(A)の断面図である

【図4】実施例の一例であるNi3Nスパッタによる半導体4と同様構造で比較した銅箔貼り付け構造のTDR測定結果を示すものであり、(A)及び(B)は比較例に係る実験結果、(C)は本実施例に係る実験結果である。

【図5】図4(C)に示した半導体膜4のTEM像である。

【発明を実施するための形態】

【0019】

[実施例]

以下、図面を参照して実施形態について説明する。

図1は第1の実施形態に係る、絶縁物層とパターニングされた導体層とを含む積層体10からなる多層基板11の電源及びグランド対配線を示すとともに、それにつながるLSIパッケージ13(点線で表示する)の実装を含む多層配線基板の全体像を表している。また、パターニングされた導体層はLSIパッケージ13に対して各種信号を送受信するための信号線7を含んでいる。

【0020】

前記電源及びグランド対配線は、具体的には、第1導電路1と、第2導電路2とからなる。具体的には、図2(A)で示される電源及びグランド対配線部の拡大平面図、及び図2(B)で示される図2(A)の一点鎖線に沿う断面図で表されるように、第1導電路1は、元電源につながる端子12に接続される元電源接続部1−3と、該元電源接続部1−3から延びる集合体の第1導電路1−1と、該1導電路1−1から分岐された分岐後の第1導電路1−2とから構成される。

また、第2導電路2は、グランドに接続される元グランド接続部2−3と、該元グランド接続部2−3から延びる集合体の第2導電路2−1と、該2導電路2−1から分岐された分岐後の第2導電路2−2とから構成される。

【0021】

前記第1導電路1の集合体となっている第1導電路1−1、及び前記第2導電路2の集合体となっている第2導電路2−1は、電源及びグランドの接続部14を介してLSIパッケージ13へつながっているが、図1、図2(A)では、平面視した場合に同一箇所となり、電源配線とグランド配線とは区別されていない。

【0022】

また、図2(A)及び図2(B)に示されるように、元電源接続部1−3からのそれぞれ導電路はそのまま平面的に第1導電路1−1につながり、一方、元グランド接続部2−3からのグランドは複数のビアホール6を介して下層に接続されて、下層にある第2導電路2−1につながっている。

また、電源配線の第1導電路1−1は、同じ層で分岐後の第1導電路1−2となる。グランド配線の第2導電路2−1は、ビアホール(図示略)を介して電源配線に隣接しかつ並行に配置されている分岐後の第2導電路2−2につながっている。これら電源配線の第1導電路1−1と、グランド配線の第2導電路2−1は、図2(A)で示されるように同一層内で交互に配置されている。

【0023】

分岐後の電源及びグランド対配線となる第1導電路1−2及び第2導電路2−2は、それぞれの延長線で各必要デバイス単位に分配され、図1のように電源及びグランドの接続部14を介してLSIパッケージ13などの電源及びグランドにつながっている。なお、この分岐電源及びグランド対配線部を構成している第1導電路1及び第2導電路2の長さはできるだけ長い方が望ましい。

【0024】

分岐電源及びグランド対配線部となる第1導電路1及び第2導電路2の二点鎖線(図2(A)参照)で示される領域の上部には、第1絶縁膜3(第1積層膜)、及び第1導電膜4又は第1半導体膜4(第1積層膜)が順次積層されている。

これら第1絶縁膜3、第1導電膜4又は第1半導体膜4は、同一層内で交互に配置された電源配線の第1導電路1−1及びグランド配線の第2導電路2−1の全体をまたぐように、これら第1導電路1−1及び第2導電路2−1の上層に配置されている。

【0025】

なお、第1積層膜である第1絶縁膜3及び第1導電膜4の上面には、必要に応じて絶縁物層と信号用導体層を形成しても良い。

また、これら第1導電路1−1及び第2導電路2−1の上層に、これら第1導電路1−1及び第2導電路2−1をまたぐように第1絶縁膜3(第1積層膜)、及び第1導電膜4又は第1半導体膜4(第1積層膜)を配置したが、これに加えて、これら第1導電路1−1及び第2導電路2−1の下層に、同様の第2絶縁膜(第2積層膜)、第2導電膜又は第2半導体膜(第2積層膜)を積層し、これら積層膜によりサンドウィッチ型電源及びグランド対線路としても良い。

【0026】

また、電源線である第1導電路1−1の下層には、グランド配線である第2導電路2−1が上下並行に配置されており、電源及びグランド対配線の特性インピーダンスが低く保たれている。下層の第2導電路2−1は、電源線である第1導電路1−1が分岐して第1導電路1−2になった部分で、ビアホール6を介して電源線に隣接した第2導電路2−2と同一平面となって、電源線と同じ層で引き回されている。

そして、その先ではビアホール6を介して最上層電極5に取り出され、LSIパッケージ13に接続される。また、第1絶縁膜3は、分岐した電源線である第1導電路1−2及びグランド配線である第2導電路2−2上を覆うように被覆され、その上層に第1導電膜4又は第1半導体膜4が被覆されることにより、多層配線基板の多層基板11の積層体10が形成されることになる。なお、ここで第1導電膜4又は第1半導体膜4が、絶縁物層となる基材シートを除き最上層に位置することも重要な事項となる。以下、詳細に説明する。

【0027】

第1導電膜4又は第1半導体膜4は、第1絶縁膜3(例えば、酸化膜など)上あるいは基材シート(図では符号省略)上に積層されている。基材シートは、例えばポリイミド、エポキシ樹脂などの耐熱性の有機絶縁物であるが、基材厚みは、第1導電膜4又は第1半導体膜4が支持可能な膜厚とするが、薄いほう(200μm以下)が好ましい。

【0028】

これら導電膜4又は半導体膜4は、例えばFe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物から構成される。導電膜4又は半導体膜4は、1Ω/□以上のシート抵抗を有するナノサイズの多結晶又はアモルファス薄膜、もしくは直径100nm以上1μm以下のクラスタが重なった膜である。導電膜4又は半導体膜4は、ボイドを有していてもよいし有していなくてもよい。ボイドが多い場合、シート抵抗が高くなるが、問題は生じない。導電膜又は半導体膜12は、例えばスパッタ、蒸着、めっき、イオンプレーティング、CVD、溶射などの手法で基材シート上に形成される。導電膜4又は半導体膜4の厚さは、20〜1000nmが好ましい。クラスタ形状を実現する好ましい方法はスパッタなどの条件で結晶成長させることで達成できる。

【0029】

絶縁膜3は、エポキシ、ビニリデン、ポリイミド、ポリスチレンなどの有機絶縁物であるが、ほう珪酸ガラス、ソーダライムガラスなどの無機絶縁物であってもよい。絶縁膜3は、例えばスパッタ、蒸着、めっき、イオンプレーティング、CVD、溶射などの手法で導電膜4又は半導体膜4上に形成されてもよいが、基板に接着できる手法、例えば上記材料のプライマー状態で接合加熱により一体化する方法が取れる。絶縁膜3の厚さは、3μm〜30μmが好ましい。第1導電路1と第2導電路2の電圧に対して十分な耐電圧を持つ厚みの範囲で薄いことが望ましい。

【0030】

本実施形態において、さらに、第1絶縁膜3は、比誘電率の高い材料か、比誘電率の高い材料が基材に混合されていることを含む。

【0031】

第1、第2導電路1,2は、例えば多層配線基板で用いられている銅から構成されている。導電路1,2の幅wは、例えば分岐配線を含めて1μm以上20mm以下であり、導電路1,2の間隔dは、例えば0.5μm以上10mm以下である。また導電路1,2の高さtは、例えば0.5〜10μmである。また、幅wと間隔dの関係は、w/d≧1.5が望ましい、また、幅wと高さtの関係は、w/t≧2が望ましい。

【0032】

第1、第2導電路1,2の間の高さtに相当する隙間には第1絶縁膜3又は基板絶縁材料で充填されている。このときの隙間に充填された絶縁物の実効的比誘電率は低いほうが望ましい。この隙間は空間であってもよい。第1導電膜4又は半導体膜4はその隙間に垂れ下がらないようにすることが望ましいが、必須事項ではない。

【0033】

上記した構造を有する電源及びグランド対配線である第1導電路1と第2導電路2において、電位変化を与えると、導電膜4と、導電路1,2間に広がった光速で伝達する変化電磁界により、導電膜4の表面の基底電子及びホールが励起される。電磁エネルギを量子化した状態、すなわちフォトンにより電子・ホール励起が起こり、これが粗密になった波、すなわち表面プラズモンという量子化したエネルギが電磁エネルギとはなれて伝達する。すなわち、フォトン‐表面プラズモンのエネルギ交換が行われる。表面プラズモンの電波速度は弾性波に近く、光速から比べ遅いこと、フォトン‐表面プラズモンーフォトンのエネルギ交換を繰り返すことから、導電路1,2内に流れる電磁エネルギ速度が遅くなり、電気長が長くなるのと等価の働き、すなわち、線路内の電荷蓄積量が大きくなると共に電源及びグランド対線路の見かけ上の長さが長くなる。その間の伝送時間をtpdすると、共振角周波数ωr=4/(2πtpd)となる。電源としての多重反射が長さだけ低周波にシフトする。フォトン‐表面プラズモンのエネルギ交換で反射エネルギは直流抵抗の減衰のように熱とならないで減衰する効果が大きく、この2つの現象で、共振エネルギが減衰し、常に安定な電源電圧が確保される。

【0034】

次に、図3は、図2(A)の配線における第2の実施例の構造による断面図である。第1の実施例における図2(B)の構造と異なる点は、第1導電路1−1と、この第1導電路の下層にある第2導電路2−1との間に第1導電膜4または第1半導体膜4を設けたものである。この図3の構造の場合、第1導電路1−1と第1導電膜4との間には、第1絶縁膜3が形成されている。この構成においても、すでに述べた図2(B)の構造と同様の効果を得ることができ、常に安定な電源電圧が確保される。

【0035】

次に、上述した図2の第1の実施例の構造において、ポリイミド基材上に窒素ガスを含む雰囲気で反応スパッタによりNi3Nを被着することで導電膜4を100nmの厚みで形成し、絶縁膜3を10μm付け、0.6mmの基板に第1導電路1及び第2導電路2(厚み60ミクロン、幅2.5mm、導電路間隔1.25mm、長さ200mm)上に貼り付けたときと、比較品として同様な絶縁膜10μmで貼り付けた銅箔を貼り付けたもののTDR測定の実験結果を図4に示す。なお、図4において、(A)及び(B)は比較例に係る実験結果、(C)は本実施例に係る実験結果である。

【0036】

Z0は電源及びグランド対配線の特性インピーダンスである。並行配線のみではZ0は120Ω程度であるが、銅箔は容量が増えるためZ0=√C0/L0という関係で、Z0が大きく低下する。ここでC0は単位長さあたりの容量、L0は単位長さあたりのインダクタンスである。これに対して電気長は2tpdを表し、その電磁波速度v=c0/√C0/L0の関係から伝送線路のみより64%長くなっている。ここでc0は真空中の光速である。導電膜4では100Ω/□のため、特性インピーダンスは銅箔より高くなるが、電気長は4.3倍となっている。C0の増大はもちろんL0の増大が大きく寄与していることが分かる。不対電子の励起の状態を量子化したものを表面マグノンと呼び、実験で採用されたNi3Nは磁性半導体のため、フォトン‐表面マグノンのエネルギ交換も含まれているものと思われる。銅箔も同様に表面プラズモンが存在し、同じように電気長が大きくなると予測できるが、それがあまり大きくないことから表面プラズモンの平均自由工程が短い(数μmオーダー)ことによると推定される結果である。表面プラズモン、表面マグノン共振エネルギの固定又は平均自由工程の数桁以上延長する状態を作ることが必要で、Ni3Nはその状態を保持しているものと思われる。

【0037】

前記Ni3N導電膜4は図5のTEM像にあるように、表面は10nmから20nmの粒子となっていて、下にある層は一体化していて、抵抗体の状態を維持している。粒子径が100nm以下では量子ドットとして特有の電子振動系を持つとされていることから、前記表面プラズモンあるいはマグノンは量子ドットの振動エネルギに固定された状態となり、フォトン‐表面プラズモンあるいは表面マグノンとのエネルギ交換を効率よく起こしていると推定される。このような導電膜4又は半導体膜4は表面作用と思われるため、厚みは10nmから200nmの範囲内で十分である。もう一つ、平均自由工程を数桁長く伸ばす材料としてグラフェン、カーボンナノチューブのπ結合電子があり(Cuの4桁長い平均自由工程)、これを分散した有機物が図4と同様な効果を示すことが実験結果で分かっている。これらも抵抗体膜であることが必要である。

これら有機物分散炭素結晶群は電磁波が内部まで浸透するため、この場合はフォトンと炭素結晶粒子内のプラズモンやマグノンのエネルギ交換であることから、導電膜4はある厚みを持つほうが効率的であり、200nmから100μmの範囲で、より厚い方が好ましいとされる。

【0038】

以上詳細に説明したように本実施例に示す電源及びグランド対線路を含む多層配線基板構造では、積層体10内に互いに平行となるように配置された電源用の第1導電路1及びグランド用の第2導電路2の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜3と、第1導電膜4又は第1半導体膜4とを有する第1積層膜を備えた構成であるので、単位長さあたりの容量とインダクタンスが大きい伝送線路型の電源及びグランド対配線を提供することができ、特性インピーダンスが低く、電気長が長い特性を併せ持つことができる。

【0039】

以上、本発明の実施形態について図面を参照して詳述したが、具体的な構成はこの実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【産業上の利用可能性】

【0040】

本発明は、配線基板の電源線に適用される共振防止低インピーダンス電源線に関する。

【符号の説明】

【0041】

1 第1導電路

1−1 集合部の電源用第1導電路

1−2 分岐後の第1導電路

1−3 第1導電路の元電源接続電極

2 第2導電路

2−1 集合部のグランド用第2導電路

2−2 分岐後の第2導電路

2−3 第2導電路の元電源接続電極

3 第1絶縁膜(第1積層膜)

4 第1導電膜又は半導体膜(第1積層膜)

5 表面電源またはグランド電極

6 層間接続のためのビアホール

7 多層基板内の信号配線

10 積層体

11 多層配線基板

12 元電源接続部

13 LSIなどのパッケージ

14 LSIなどのパッケージに電源を供給する接続部

【技術分野】

【0001】

本発明は、配線基板の電源線に適用される共振防止低インピーダンス電源線に関する技術である。

【背景技術】

【0002】

従来の配線基板電源は多層構造のある層を占有し板状に広がった構造が大半である。

例えば、この種の基板構造としては、例えば、特許文献1に示されるように、電源パターンの多い信号層、アース層、電源層、アースパターンの多い信号層の各層が順に積層された多層構造を有し、前記アース層・電源層間の中央基板層の厚さに対してその両側層の厚さを薄く形成し、前記各信号層の電源パターンとアースパターンとが対向する面積の基板総面積に対する比率を特定割合にした、プリント配線基板が知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平11−307894号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、このような配線基板では、デジタルやRF回路の高周波動作をするデバイスに供給する電源は回路動作に応じて瞬時応答が求められ、この応答に対応するため、板状に電源とグランドを配置した多層配線基板がよく用いられている。この構造の特徴はどの場所にある回路から見ても電源及びグランド対配線が低インピーダンスとなっていることで、瞬時電流を取り出すことができる。しかし、瞬時応答の電源平板の電流が慣性を持ち、瞬時遮断時に回路部分で反射して、その反射波が平板に均質に広がり、基板の端面で反射しその距離に応じた多重反射共振モードで共振して、電磁放射の原因となるばかりでなく、この電源電圧の揺らぎが自身の回路や他の隣接回路にも影響し、高速動作の大きな障害となるという問題が生じている。

【0005】

本発明は上記のような事情を考慮してなされたものであり、その目的は、電源及びグランドの平板構造で見られる低特性インピーダンスを維持しつつ平板に置ける共振モードを防止する構造を提案するものである。

【課題を解決するための手段】

【0006】

本発明の電源及びグランド対線路を含む多層配線基板構造は、絶縁物層とパターニングされた導体層とを含む積層体からなる多層配線基板において、前記積層体に設けられて互いに平行となるように配置された電源用の第1導電路及びグランド用の第2導電路と、前記第1導電路の上面及び前記第2導電路の上面にまたぐように設けられ、前記第1及び第2導電路側から順に積層された第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜と、を備えることを特徴とする。

【0007】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1積層膜上には、必要に応じて絶縁物層と信号用導体層が形成されていることを特徴とする。

【0008】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路及び前記第2導電路において、幅wと高さtの関係が、w/t≧2であることを特徴とする。

【0009】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路の下面及び前記第2導電路の下面に、前記第1及び第2導電路側から第2絶縁膜と第2導電膜又は第2半導体膜を順次積層した第2積層膜を備えてサンドウィッチ型とすることを特徴とする。

【0010】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路は電流の流れる方向に複数に分岐され、前記第2導電路は元電源側が積層体内で前記第1導電路の下層に位置し、複数分岐された後、ビアホールを経由して前記第1導電路層の分岐電路と交互に配置され、前記第1積層膜は、分岐された交互に配置された複数の第1、第2導電路の分岐導電路上の全体にまたぐように積層されることを特徴とする。

【0011】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1絶縁膜の膜厚が3μm〜30μmであることを特徴とする。

【0012】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜の膜厚が20〜100000nmであることを特徴とする。

【0013】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜は、1Ω/□以上のシート抵抗を有するであることを特徴とする。

【0014】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜は、Fe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物を含むことを特徴とする。

【0015】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電膜又は第1半導体膜はnmから数千nm単位の径の粒子が重なった表面構造であることを特徴とする。

【0016】

本発明の電源及びグランド対線路を含む多層配線基板構造は、前記第1導電路及び前記第2導電路の分岐構造が複数直列につながっている構造であり、その分岐点では第1又は第2導電路のどちらかがビアホールで下層又は上層で迂回する構造を有することを特徴とする。

【発明の効果】

【0017】

本発明によれば、電源及びグランド対配線を構成する電源用の第1導電路及びグランド用の第2導電路の上面に、これら第1及び第2導電路側から順次、第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜をまたがって積層することにより、単位長さあたりの容量とインダクタンスが大きい伝送線路型の電源及びグランド対配線を提供することができ、特性インピーダンスが低く、電気長が長い特性を併せ持つことができる。

【図面の簡単な説明】

【0018】

【図1】本発明の一実施例に係る多層配線基板の電源及びグランド対線路とLSIパッケージなど実装が予想される部分までの配線と接続状態を示す全体平面図である。

【図2】(A)は第1の実施例に対応する第1、第2導電路1,2の部分を示す部分平面図であり、(B)は図2(A)にII(B)−II(B)に沿う一点鎖線で切断した断面図である。

【図3】本発明の第2の実施例による図2(A)の断面図である

【図4】実施例の一例であるNi3Nスパッタによる半導体4と同様構造で比較した銅箔貼り付け構造のTDR測定結果を示すものであり、(A)及び(B)は比較例に係る実験結果、(C)は本実施例に係る実験結果である。

【図5】図4(C)に示した半導体膜4のTEM像である。

【発明を実施するための形態】

【0019】

[実施例]

以下、図面を参照して実施形態について説明する。

図1は第1の実施形態に係る、絶縁物層とパターニングされた導体層とを含む積層体10からなる多層基板11の電源及びグランド対配線を示すとともに、それにつながるLSIパッケージ13(点線で表示する)の実装を含む多層配線基板の全体像を表している。また、パターニングされた導体層はLSIパッケージ13に対して各種信号を送受信するための信号線7を含んでいる。

【0020】

前記電源及びグランド対配線は、具体的には、第1導電路1と、第2導電路2とからなる。具体的には、図2(A)で示される電源及びグランド対配線部の拡大平面図、及び図2(B)で示される図2(A)の一点鎖線に沿う断面図で表されるように、第1導電路1は、元電源につながる端子12に接続される元電源接続部1−3と、該元電源接続部1−3から延びる集合体の第1導電路1−1と、該1導電路1−1から分岐された分岐後の第1導電路1−2とから構成される。

また、第2導電路2は、グランドに接続される元グランド接続部2−3と、該元グランド接続部2−3から延びる集合体の第2導電路2−1と、該2導電路2−1から分岐された分岐後の第2導電路2−2とから構成される。

【0021】

前記第1導電路1の集合体となっている第1導電路1−1、及び前記第2導電路2の集合体となっている第2導電路2−1は、電源及びグランドの接続部14を介してLSIパッケージ13へつながっているが、図1、図2(A)では、平面視した場合に同一箇所となり、電源配線とグランド配線とは区別されていない。

【0022】

また、図2(A)及び図2(B)に示されるように、元電源接続部1−3からのそれぞれ導電路はそのまま平面的に第1導電路1−1につながり、一方、元グランド接続部2−3からのグランドは複数のビアホール6を介して下層に接続されて、下層にある第2導電路2−1につながっている。

また、電源配線の第1導電路1−1は、同じ層で分岐後の第1導電路1−2となる。グランド配線の第2導電路2−1は、ビアホール(図示略)を介して電源配線に隣接しかつ並行に配置されている分岐後の第2導電路2−2につながっている。これら電源配線の第1導電路1−1と、グランド配線の第2導電路2−1は、図2(A)で示されるように同一層内で交互に配置されている。

【0023】

分岐後の電源及びグランド対配線となる第1導電路1−2及び第2導電路2−2は、それぞれの延長線で各必要デバイス単位に分配され、図1のように電源及びグランドの接続部14を介してLSIパッケージ13などの電源及びグランドにつながっている。なお、この分岐電源及びグランド対配線部を構成している第1導電路1及び第2導電路2の長さはできるだけ長い方が望ましい。

【0024】

分岐電源及びグランド対配線部となる第1導電路1及び第2導電路2の二点鎖線(図2(A)参照)で示される領域の上部には、第1絶縁膜3(第1積層膜)、及び第1導電膜4又は第1半導体膜4(第1積層膜)が順次積層されている。

これら第1絶縁膜3、第1導電膜4又は第1半導体膜4は、同一層内で交互に配置された電源配線の第1導電路1−1及びグランド配線の第2導電路2−1の全体をまたぐように、これら第1導電路1−1及び第2導電路2−1の上層に配置されている。

【0025】

なお、第1積層膜である第1絶縁膜3及び第1導電膜4の上面には、必要に応じて絶縁物層と信号用導体層を形成しても良い。

また、これら第1導電路1−1及び第2導電路2−1の上層に、これら第1導電路1−1及び第2導電路2−1をまたぐように第1絶縁膜3(第1積層膜)、及び第1導電膜4又は第1半導体膜4(第1積層膜)を配置したが、これに加えて、これら第1導電路1−1及び第2導電路2−1の下層に、同様の第2絶縁膜(第2積層膜)、第2導電膜又は第2半導体膜(第2積層膜)を積層し、これら積層膜によりサンドウィッチ型電源及びグランド対線路としても良い。

【0026】

また、電源線である第1導電路1−1の下層には、グランド配線である第2導電路2−1が上下並行に配置されており、電源及びグランド対配線の特性インピーダンスが低く保たれている。下層の第2導電路2−1は、電源線である第1導電路1−1が分岐して第1導電路1−2になった部分で、ビアホール6を介して電源線に隣接した第2導電路2−2と同一平面となって、電源線と同じ層で引き回されている。

そして、その先ではビアホール6を介して最上層電極5に取り出され、LSIパッケージ13に接続される。また、第1絶縁膜3は、分岐した電源線である第1導電路1−2及びグランド配線である第2導電路2−2上を覆うように被覆され、その上層に第1導電膜4又は第1半導体膜4が被覆されることにより、多層配線基板の多層基板11の積層体10が形成されることになる。なお、ここで第1導電膜4又は第1半導体膜4が、絶縁物層となる基材シートを除き最上層に位置することも重要な事項となる。以下、詳細に説明する。

【0027】

第1導電膜4又は第1半導体膜4は、第1絶縁膜3(例えば、酸化膜など)上あるいは基材シート(図では符号省略)上に積層されている。基材シートは、例えばポリイミド、エポキシ樹脂などの耐熱性の有機絶縁物であるが、基材厚みは、第1導電膜4又は第1半導体膜4が支持可能な膜厚とするが、薄いほう(200μm以下)が好ましい。

【0028】

これら導電膜4又は半導体膜4は、例えばFe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物から構成される。導電膜4又は半導体膜4は、1Ω/□以上のシート抵抗を有するナノサイズの多結晶又はアモルファス薄膜、もしくは直径100nm以上1μm以下のクラスタが重なった膜である。導電膜4又は半導体膜4は、ボイドを有していてもよいし有していなくてもよい。ボイドが多い場合、シート抵抗が高くなるが、問題は生じない。導電膜又は半導体膜12は、例えばスパッタ、蒸着、めっき、イオンプレーティング、CVD、溶射などの手法で基材シート上に形成される。導電膜4又は半導体膜4の厚さは、20〜1000nmが好ましい。クラスタ形状を実現する好ましい方法はスパッタなどの条件で結晶成長させることで達成できる。

【0029】

絶縁膜3は、エポキシ、ビニリデン、ポリイミド、ポリスチレンなどの有機絶縁物であるが、ほう珪酸ガラス、ソーダライムガラスなどの無機絶縁物であってもよい。絶縁膜3は、例えばスパッタ、蒸着、めっき、イオンプレーティング、CVD、溶射などの手法で導電膜4又は半導体膜4上に形成されてもよいが、基板に接着できる手法、例えば上記材料のプライマー状態で接合加熱により一体化する方法が取れる。絶縁膜3の厚さは、3μm〜30μmが好ましい。第1導電路1と第2導電路2の電圧に対して十分な耐電圧を持つ厚みの範囲で薄いことが望ましい。

【0030】

本実施形態において、さらに、第1絶縁膜3は、比誘電率の高い材料か、比誘電率の高い材料が基材に混合されていることを含む。

【0031】

第1、第2導電路1,2は、例えば多層配線基板で用いられている銅から構成されている。導電路1,2の幅wは、例えば分岐配線を含めて1μm以上20mm以下であり、導電路1,2の間隔dは、例えば0.5μm以上10mm以下である。また導電路1,2の高さtは、例えば0.5〜10μmである。また、幅wと間隔dの関係は、w/d≧1.5が望ましい、また、幅wと高さtの関係は、w/t≧2が望ましい。

【0032】

第1、第2導電路1,2の間の高さtに相当する隙間には第1絶縁膜3又は基板絶縁材料で充填されている。このときの隙間に充填された絶縁物の実効的比誘電率は低いほうが望ましい。この隙間は空間であってもよい。第1導電膜4又は半導体膜4はその隙間に垂れ下がらないようにすることが望ましいが、必須事項ではない。

【0033】

上記した構造を有する電源及びグランド対配線である第1導電路1と第2導電路2において、電位変化を与えると、導電膜4と、導電路1,2間に広がった光速で伝達する変化電磁界により、導電膜4の表面の基底電子及びホールが励起される。電磁エネルギを量子化した状態、すなわちフォトンにより電子・ホール励起が起こり、これが粗密になった波、すなわち表面プラズモンという量子化したエネルギが電磁エネルギとはなれて伝達する。すなわち、フォトン‐表面プラズモンのエネルギ交換が行われる。表面プラズモンの電波速度は弾性波に近く、光速から比べ遅いこと、フォトン‐表面プラズモンーフォトンのエネルギ交換を繰り返すことから、導電路1,2内に流れる電磁エネルギ速度が遅くなり、電気長が長くなるのと等価の働き、すなわち、線路内の電荷蓄積量が大きくなると共に電源及びグランド対線路の見かけ上の長さが長くなる。その間の伝送時間をtpdすると、共振角周波数ωr=4/(2πtpd)となる。電源としての多重反射が長さだけ低周波にシフトする。フォトン‐表面プラズモンのエネルギ交換で反射エネルギは直流抵抗の減衰のように熱とならないで減衰する効果が大きく、この2つの現象で、共振エネルギが減衰し、常に安定な電源電圧が確保される。

【0034】

次に、図3は、図2(A)の配線における第2の実施例の構造による断面図である。第1の実施例における図2(B)の構造と異なる点は、第1導電路1−1と、この第1導電路の下層にある第2導電路2−1との間に第1導電膜4または第1半導体膜4を設けたものである。この図3の構造の場合、第1導電路1−1と第1導電膜4との間には、第1絶縁膜3が形成されている。この構成においても、すでに述べた図2(B)の構造と同様の効果を得ることができ、常に安定な電源電圧が確保される。

【0035】

次に、上述した図2の第1の実施例の構造において、ポリイミド基材上に窒素ガスを含む雰囲気で反応スパッタによりNi3Nを被着することで導電膜4を100nmの厚みで形成し、絶縁膜3を10μm付け、0.6mmの基板に第1導電路1及び第2導電路2(厚み60ミクロン、幅2.5mm、導電路間隔1.25mm、長さ200mm)上に貼り付けたときと、比較品として同様な絶縁膜10μmで貼り付けた銅箔を貼り付けたもののTDR測定の実験結果を図4に示す。なお、図4において、(A)及び(B)は比較例に係る実験結果、(C)は本実施例に係る実験結果である。

【0036】

Z0は電源及びグランド対配線の特性インピーダンスである。並行配線のみではZ0は120Ω程度であるが、銅箔は容量が増えるためZ0=√C0/L0という関係で、Z0が大きく低下する。ここでC0は単位長さあたりの容量、L0は単位長さあたりのインダクタンスである。これに対して電気長は2tpdを表し、その電磁波速度v=c0/√C0/L0の関係から伝送線路のみより64%長くなっている。ここでc0は真空中の光速である。導電膜4では100Ω/□のため、特性インピーダンスは銅箔より高くなるが、電気長は4.3倍となっている。C0の増大はもちろんL0の増大が大きく寄与していることが分かる。不対電子の励起の状態を量子化したものを表面マグノンと呼び、実験で採用されたNi3Nは磁性半導体のため、フォトン‐表面マグノンのエネルギ交換も含まれているものと思われる。銅箔も同様に表面プラズモンが存在し、同じように電気長が大きくなると予測できるが、それがあまり大きくないことから表面プラズモンの平均自由工程が短い(数μmオーダー)ことによると推定される結果である。表面プラズモン、表面マグノン共振エネルギの固定又は平均自由工程の数桁以上延長する状態を作ることが必要で、Ni3Nはその状態を保持しているものと思われる。

【0037】

前記Ni3N導電膜4は図5のTEM像にあるように、表面は10nmから20nmの粒子となっていて、下にある層は一体化していて、抵抗体の状態を維持している。粒子径が100nm以下では量子ドットとして特有の電子振動系を持つとされていることから、前記表面プラズモンあるいはマグノンは量子ドットの振動エネルギに固定された状態となり、フォトン‐表面プラズモンあるいは表面マグノンとのエネルギ交換を効率よく起こしていると推定される。このような導電膜4又は半導体膜4は表面作用と思われるため、厚みは10nmから200nmの範囲内で十分である。もう一つ、平均自由工程を数桁長く伸ばす材料としてグラフェン、カーボンナノチューブのπ結合電子があり(Cuの4桁長い平均自由工程)、これを分散した有機物が図4と同様な効果を示すことが実験結果で分かっている。これらも抵抗体膜であることが必要である。

これら有機物分散炭素結晶群は電磁波が内部まで浸透するため、この場合はフォトンと炭素結晶粒子内のプラズモンやマグノンのエネルギ交換であることから、導電膜4はある厚みを持つほうが効率的であり、200nmから100μmの範囲で、より厚い方が好ましいとされる。

【0038】

以上詳細に説明したように本実施例に示す電源及びグランド対線路を含む多層配線基板構造では、積層体10内に互いに平行となるように配置された電源用の第1導電路1及びグランド用の第2導電路2の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜3と、第1導電膜4又は第1半導体膜4とを有する第1積層膜を備えた構成であるので、単位長さあたりの容量とインダクタンスが大きい伝送線路型の電源及びグランド対配線を提供することができ、特性インピーダンスが低く、電気長が長い特性を併せ持つことができる。

【0039】

以上、本発明の実施形態について図面を参照して詳述したが、具体的な構成はこの実施形態に限られるものではなく、本発明の要旨を逸脱しない範囲の設計変更等も含まれる。

【産業上の利用可能性】

【0040】

本発明は、配線基板の電源線に適用される共振防止低インピーダンス電源線に関する。

【符号の説明】

【0041】

1 第1導電路

1−1 集合部の電源用第1導電路

1−2 分岐後の第1導電路

1−3 第1導電路の元電源接続電極

2 第2導電路

2−1 集合部のグランド用第2導電路

2−2 分岐後の第2導電路

2−3 第2導電路の元電源接続電極

3 第1絶縁膜(第1積層膜)

4 第1導電膜又は半導体膜(第1積層膜)

5 表面電源またはグランド電極

6 層間接続のためのビアホール

7 多層基板内の信号配線

10 積層体

11 多層配線基板

12 元電源接続部

13 LSIなどのパッケージ

14 LSIなどのパッケージに電源を供給する接続部

【特許請求の範囲】

【請求項1】

絶縁物層とパターニングされた導体層とを含む積層体を有する多層配線基板において、

前記積層体内に互いに平行となるように配置された電源用の第1導電路及びグランド用の第2導電路と、

前記第1導電路の上面及び前記第2導電路の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜と、を備えることを特徴とする電源及びグランド対線路を含む多層配線基板構造。

【請求項2】

前記第1積層膜上には、必要に応じて絶縁物層と信号用導体層が形成されていることを特徴とする請求項1に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項3】

前記第1導電路及び前記第2導電路は、幅wと高さtの関係が、w/t≧2であることを特徴とする請求項1又は2のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項4】

前記第1導電路の下面及び前記第2導電路の下面に、前記第1及び第2導電路側から第2絶縁膜と第2導電膜又は第2半導体膜を順次積層した第2積層膜を備えてサンドウィッチ型とすることを特徴とする請求項1〜3のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項5】

前記第1導電路は電流の流れる方向に複数に分岐され、

前記第2導電路は元電源側が積層体内で前記第1導電路の下層に位置し、複数分岐された後、ビアホールを経由して前記第1導電路層の分岐電路と交互に配置され、

前記第1積層膜は、分岐された交互に配置された複数の第1、第2導電路の分岐導電路上の全体にまたぐように積層されることを特徴とする請求項1〜4のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項6】

前記第1絶縁膜の膜厚が3μm〜30μmであることを特徴とする請求項1〜5のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項7】

前記第1導電膜又は第1半導体膜の膜厚が20〜100000nmであることを特徴とする請求項1〜6のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項8】

前記第1導電膜又は第1半導体膜は、1Ω/□以上のシート抵抗を有するであることを特徴とする請求項1〜7のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項9】

前記第1導電膜又は第1半導体膜は、Fe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物を含むことを特徴とする請求項1〜8のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項10】

前記第1導電膜又は第1半導体膜はnmから数千nm単位の径の粒子が重なった表面構造であることを特徴とする請求項1〜9のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項11】

前記第1導電路及び前記第2導電路の分岐構造が複数直列につながっている構造であり、その分岐点では第1又は第2導電路のどちらかがビアホールで下層又は上層で迂回する構造を有することを特徴とする請求項1〜10のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項1】

絶縁物層とパターニングされた導体層とを含む積層体を有する多層配線基板において、

前記積層体内に互いに平行となるように配置された電源用の第1導電路及びグランド用の第2導電路と、

前記第1導電路の上面及び前記第2導電路の上面にまたぐように設けられ、前記第1及び第2導電路側から順次積層された第1絶縁膜と、第1導電膜又は第1半導体膜とを有する第1積層膜と、を備えることを特徴とする電源及びグランド対線路を含む多層配線基板構造。

【請求項2】

前記第1積層膜上には、必要に応じて絶縁物層と信号用導体層が形成されていることを特徴とする請求項1に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項3】

前記第1導電路及び前記第2導電路は、幅wと高さtの関係が、w/t≧2であることを特徴とする請求項1又は2のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項4】

前記第1導電路の下面及び前記第2導電路の下面に、前記第1及び第2導電路側から第2絶縁膜と第2導電膜又は第2半導体膜を順次積層した第2積層膜を備えてサンドウィッチ型とすることを特徴とする請求項1〜3のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項5】

前記第1導電路は電流の流れる方向に複数に分岐され、

前記第2導電路は元電源側が積層体内で前記第1導電路の下層に位置し、複数分岐された後、ビアホールを経由して前記第1導電路層の分岐電路と交互に配置され、

前記第1積層膜は、分岐された交互に配置された複数の第1、第2導電路の分岐導電路上の全体にまたぐように積層されることを特徴とする請求項1〜4のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項6】

前記第1絶縁膜の膜厚が3μm〜30μmであることを特徴とする請求項1〜5のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項7】

前記第1導電膜又は第1半導体膜の膜厚が20〜100000nmであることを特徴とする請求項1〜6のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項8】

前記第1導電膜又は第1半導体膜は、1Ω/□以上のシート抵抗を有するであることを特徴とする請求項1〜7のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項9】

前記第1導電膜又は第1半導体膜は、Fe、Al、Ni、Ag、Mg、Cu、Si、C、N、O、Sからなる群から選ばれた少なくとも一つ、又は前記群から選ばれた少なくとも2つからなる合金又は共析物を含むことを特徴とする請求項1〜8のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項10】

前記第1導電膜又は第1半導体膜はnmから数千nm単位の径の粒子が重なった表面構造であることを特徴とする請求項1〜9のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【請求項11】

前記第1導電路及び前記第2導電路の分岐構造が複数直列につながっている構造であり、その分岐点では第1又は第2導電路のどちらかがビアホールで下層又は上層で迂回する構造を有することを特徴とする請求項1〜10のいずれか1項に記載の電源及びグランド対線路を含む多層配線基板構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−187839(P2011−187839A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−53668(P2010−53668)

【出願日】平成22年3月10日(2010.3.10)

【出願人】(500132214)学校法人明星学苑 (23)

【出願人】(000190116)信越ポリマー株式会社 (1,394)

【出願人】(000230216)日本ミクロン株式会社 (8)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月10日(2010.3.10)

【出願人】(500132214)学校法人明星学苑 (23)

【出願人】(000190116)信越ポリマー株式会社 (1,394)

【出願人】(000230216)日本ミクロン株式会社 (8)

【Fターム(参考)】

[ Back to top ]