電源回路、及び液晶表示装置

【課題】デジタル設定可能な電源回路であって、コマンド送信用の周辺部品によるデジタル設定を電源起動の度に行う必要がなく、またアナログ方式の電源回路の代替として用いることが可能な電源回路、及びこの電源回路を有する液晶表示装置を提供する。

【解決手段】デジタルデータにより動作設定を行う電源回路10であって、動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部14a,14bと、記録部に対して設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部20と、記録部より設定情報を読み出して電源回路に対する動作設定を行う制御部11とを備え、制御部は、記録部より読み出した設定情報に対して予め定められたチェック処理を行い、チェック処理においてエラーが検出された場合に、電源回路を停止状態へ移行させる。

【解決手段】デジタルデータにより動作設定を行う電源回路10であって、動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部14a,14bと、記録部に対して設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部20と、記録部より設定情報を読み出して電源回路に対する動作設定を行う制御部11とを備え、制御部は、記録部より読み出した設定情報に対して予め定められたチェック処理を行い、チェック処理においてエラーが検出された場合に、電源回路を停止状態へ移行させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、デジタル設定が可能な電源回路、及びこの電源回路を有する液晶表示装置に関するものである。

【背景技術】

【0002】

近年、外部のプロセッサからのコマンドを受けてデバイスに電圧を供給する電源回路において、コマンドを受信するためのデジタルインタフェースとしてI2C(Inter-Integrated Circuit)やSPI(System Packet Interface)等が利用されている。

【0003】

このような電源回路は、デジタルインタフェースを介して所定のコマンドが入力されることにより、その動作機能や動作範囲、動作形態をソフトウェア的に切り換えることが可能である。例えば、デジタルインタフェースに与えるコマンドによって、可変出力のレギュレータの出力電圧のオン/オフや、出力電圧の設定値を切り換える。

【0004】

上記の技術に関連して、入力されるコマンドの誤認識に起因して、電源回路、或いは電圧供給先のデバイスが誤動作するのを回避するための電源回路が開示・提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−20580号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、デジタルインタフェースを介してデジタル設定を行う電源回路は、コマンドを送信する周辺部品(例えばマイコン)を接続する必要があった。また、電源起動の度にコマンドを電源回路へ送信する必要であった。

【0007】

また、アナログ方式の電源回路を用いた電子装置において、デジタル方式の電源回路を用いた仕様に変更する場合、デジタルインタフェースやコマンドを送信する周辺部品が存在しないため、電子装置のシステム全体を見直す必要があった。

【0008】

本発明は、本願の発明者により見出された上記の問題点に鑑み、デジタル設定可能な電源回路であって、コマンド送信用の周辺部品によるデジタル設定を電源起動の度に行う必要がなく、またアナログ方式の電源回路の代替として用いることが可能な電源回路、及びこの電源回路を有する液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明に係る電源回路は、デジタルデータにより動作設定を行う電源回路であって、前記動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部と、前記記録部に対して前記設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部と、前記記録部より前記設定情報を読み出して前記電源回路に対する動作設定を行う制御部と、を備えたことを特徴とする構成(第1の構成)とされている。

【0010】

なお、上記第1の構成から成る電源回路は、前記制御部が、前記記録部より読み出した前記設定情報に対して予め定められたチェック処理を行うことを特徴とする構成(第2の構成)にするとよい。

【0011】

また、上記第2の構成から成る電源回路は、前記制御部が、前記チェック処理においてエラーが検出された場合に前記電源回路を停止状態へ移行させることを特徴とする構成(第3の構成)にするとよい。

【0012】

また、上記第3の構成から成る電源回路は、前記電源回路が、揮発性の記録媒体である第1レジスタを備え、前記制御部は、前記チェック処理として、前記記録部より読み出した前記設定情報を前記第1レジスタに記録した後に再び前記記録部より前記設定情報を読み出し、読み出した該設定情報と前記第1レジスタに記録されている前記設定情報とが一致するか否かを判定し、一致しない場合に前記エラーが検出されたとみなすことを特徴とする構成(第4の構成)にするとよい。

【0013】

また、上記第4の構成から成る電源回路は、揮発性の記録媒体である第2レジスタを備え、前記制御部は、前記チェック処理として、前記判定の結果一致した前記設定情報を前記第2レジスタに記録し、前記第1レジスタに記録されている前記設定情報と前記第2レジスタに記録されている前記設定情報とが一致するか否かを予め定められた時間間隔で判定し、一致しない場合に前記エラーが検出されたとみなすことを特徴とする構成(第5の構成)にするとよい。

【0014】

また、上記第5の構成から成る電源回路は、前記制御部が、前記チェック処理として、パリティビットまたはチェックサムを用いた誤り検出を行うことを特徴とする構成(第6の構成)にするとよい。

【0015】

また、上記第6の構成から成る電源回路は、前記制御部が、前記チェック処理として、前記設定情報に含まれる設定値が予め定められる範囲を超えるか否かを判定する範囲チェックを行うことを特徴とする構成(第7の構成)にするとよい。

【0016】

また、上記第7の構成から成る電源回路は、前記記録部が、前記電源回路に接続される外部装置に応じて設定値を変更する必要のない前記設定情報を記録する第1記録部と、該外部装置に応じて設定値を変更する必要のある前記設定情報を記録する第2記録部と、を含むことを特徴とする構成(第8の構成)にするとよい。

【0017】

また、上記第8の構成から成る電源回路は、液晶表示装置への電圧供給を行う出力部を備え、第1記録部は前記液晶表示装置に対するドライバ駆動電圧の供給動作に用いられる前記設定情報を記録し、第2記録部は前記液晶表示装置に対するコモン電圧の供給動作に用いられる前記設定情報を記録することを特徴とする構成(第9の構成)にするとよい。

【0018】

また、本発明に係る液体表示装置は、前記ドライバ駆動電圧を受けて動作するソースドライバ及びゲートドライバと前記コモン電圧を受けて動作する液晶表示パネルとを有する表示部と、前記表示部に電力供給を行う第9の構成の電源回路とを有することを特徴とする構成(第10の構成)にするとよい。

【発明の効果】

【0019】

本発明によれば、デジタル設定可能な電源回路であって、電源起動の度に周辺部品によるデジタル設定を行う必要のない電源回路を提供することができる。このため、アナログ方式の設定値固定型の電源回路が搭載されたセットを、デジタル方式の電源回路を用いた仕様に変更する場合に、セット全体のシステムを変更する必要がない。

【0020】

また本実施形態によれば、設定情報に対するチェック処理を起動時に行い、さらに起動後においても周期的に行う。このため、サージ等により設定情報が破損したとしても、装置が誤動作する事態を回避することができる。

【図面の簡単な説明】

【0021】

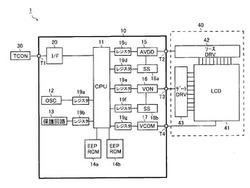

【図1】本発明に係る電源回路を含んだ液晶表示装置を示すブロック図

【図2】本発明に係る設定情報を示すテーブル図

【図3】本発明に係る電源起動処理を示すフロー図

【発明を実施するための形態】

【0022】

<液晶表示装置>

図1は、本発明の電源回路を含む液晶表示装置の一構成例を示す図である。本構成例の液晶表示装置1は、電源回路10と、TCON30と、表示部40と、を有する。

【0023】

電源回路10は、入力電圧VIN(例えば5V)を受けて表示部40への電力供給(ソース電圧AVDD、ゲート電圧VON、コモン電圧VCOM等)を行う。

【0024】

TCON30は、表示部40の表示タイミングをとるためのロジック回路であり、シフトクロック等に必要なパルスを供給するタイミングコントローラである。

【0025】

表示部40は、電源回路10から供給される電圧に応じて任意の文字や画像を表示する。表示部40は少なくとも、LCDパネル41、ソースドライバ42、及びゲートドライバ43を含む構成となっている。ソースドライバ42/ゲートドライバ43は、LCDパネル41(液晶表示パネル)の各画素に配置されたトランジスタのON/OFFを制御することにより、液晶分子に電圧を印加する。

【0026】

<電源回路>

電源回路10は、CPU11(制御部、第1記録部)と、OSC12と、保護回路13と、EEPROM14a及び14b(記録部)と、AVDD出力回路15(出力部)と、VON出力回路16(出力部)と、VCOM出力回路17(出力部)と、ソフトスタート制御回路18a及び18bと、レジスタ19a〜19g(第2記録部)と、インタフェース部20と、を集積化したモノリシック半導体集積回路装置である。

【0027】

また、電源回路10は、外部との電気的な接続を確立するために、外部端子T1〜T4を有する。外部端子T1(入力端子)は、デジタル信号の入力端子である。外部端子T2は、AVDDの出力端子である。外部端子T3は、VONの出力端子である。外部端子T4は、VCOMの出力端子である。

【0028】

CPU(Central Processing Unit)11は、データの演算処理を行うロジック回路である。CPU11は、電源回路10の各部動作を統括的に制御する。またCPU11はその内部に、後述するロジックデータ(設定情報)を一時的に記録するテンポラリレジスタ(第1レジスタ)を有する。

【0029】

OSC(Oscillator)12は、CR発振回路等により、電源回路10が有する電子回路を動作させるためのクロック信号を生成して出力する。

【0030】

保護回路13は、電源回路10に含まれる各電源の電圧を監視し、電圧が予め定められた閾値を下回る時間が所定時間を超えたこと(=タイムアウト)が検知された場合に、全ての電源を停止させる。また保護回路13は、タイムアウトが発生したか否かを判定するための判定時間を、電源毎に設定する設定機能を有する。

【0031】

EEPROM14a及び14bは、CPU11が実行するシステムプログラムや、電源回路10の各部の動作設定を行うための設定値を示すロジックデータ等を記録した、不揮発性半導体メモリである。本実施形態では、図1に示すように、2つのEEPROM14a及び14bが電源回路10に設けられている。

【0032】

EEPROM14a(第1記録部)は、電源回路10の内部構成に応じて設定値を調整したロジックデータである第1ロジックデータを記録する。第1ロジックデータには例えば、AVDD出力回路15またはVON出力回路16の出力電圧や、ソフトスタート制御回路18のソフトスタート時間等が含まれる。第1ロジックデータは、電源回路10が含まれる基板の組み立て工程等において、EEPROM14aに記録される。

【0033】

EEPROM14b(第2記録部)は、電源回路10に外部接続される装置(本実施形態では表示部40)に応じて設定値を調整したロジックデータである第2ロジックデータを記録する。第2ロジックデータには例えば、VCOM出力回路17の出力電圧等が含まれる。第2ロジックデータは、電源回路10が含まれる装置(本実施形態では液晶表示装置1)の調整工程等において、EEPROM14bに記録される。

【0034】

図2は、第1ロジックデータの一例を示したテーブル図である。本実施形態の第1ロジックデータには、設定項目として、パリティビット、AVDD出力電圧、VON出力電圧、OSC周波数、AVDDソフトスタート時間、VONソフトスタート時間等が含まれている。各設定項目に対しては、レジスタマップ、ビット数、及び設定値(左から16進数表記、2進数表記、10進数及び単位表記)が関連付けられている。

【0035】

AVDD出力回路15は、ソースドライバ42に対してソース電圧AVDDを印加する。なお印加するソース電圧AVDDの大きさは、レジスタ19cに記録されている設定値に基づいて決定される。

【0036】

VON出力回路16は、ゲートドライバ43に対してゲート電圧VONを印加する。なお印加するゲート電圧VONの大きさは、レジスタ19dに記録されている設定値に基づいて決定される。

【0037】

VCOM出力回路17は、LDCパネル41を形成する全ての画素に共通のコモン電極に対してコモン電圧VCOMを印加する。なお印加するコモン電圧VCOMの大きさは、レジスタ19eに記録されている設定値に基づいて決定される。

【0038】

ソフトスタート制御回路18a及び18bは、AVDD出力回路15及びVON出力回路16の出力電圧が急峻に変化してオーバーシュートが発生するのを回避するための回路である。ソフトスタート制御回路18a及び18bは、レジスタ19d及び19fから読み出されたソフトスタート時間に基づき段階的に出力電圧を変化させるよう、AVDD出力回路15及びVON出力回路16を制御する。

【0039】

レジスタ19a〜19gは、各装置の動作に用いられる設定値を記録する揮発性の記録媒体である。本実施形態では、図1に示すように、レジスタ19a〜レジスタ19gの7つのレジスタを有する構成を例示している。各レジスタ19a〜19gは、OSC12〜ソフトスタート制御回路18の動作に用いられる設定値を記録するのに用いられる。

【0040】

インタフェース部20は、I2Cバス等を介して外部の装置と通信を行うためのインタフェースである。インタフェース部20は例えば、TCON30よりデジタル信号を入力するのに用いられる。また例えば、EEPROM14a及び14bにロジックデータを記録するための制御信号を、不図示のマイコン等から入力するのに用いられる。

【0041】

次に、電源回路10の電源起動時の処理フローについて、図3のフローチャートを参照しながら説明する。本フローチャートで例示する処理は、ユーザ操作等により液晶表示装置1の電源が投入され、UVLO(Under Voltage Lock Out)が解除されることにより開始される。

【0042】

なお以下では、EEPROM14aに記録された第1ロジックデータの読み出し及び設定について説明するが、EEPROM14bに記録された第2ロジックデータの読み出し及び設定についても、同様の処理順序により、並行ないしは順次実施するものとする。

【0043】

本処理の開始後、まずCPU11は、EEPROM14aより第1ロジックデータを読み出す(ステップS11)。

【0044】

第1ロジックデータが読み出されると、次にCPU11は、第1ロジックデータのパリティチェックを行う(ステップS12)。なおパリティチェックは、図2に示すパリティビットを用いて行う。

【0045】

パリティチェックの結果、エラーが検知された場合、CPU11は電源回路10を待機状態へ移行させる。なおこの待機状態は、例えば液晶表示装置1の電源が再起動されるまで継続される。

【0046】

パリティチェックの結果、エラーが検知されなかった場合、次にCPU11は、CPU11の内部に有するテンポラリレジスタに、読み出した第1ロジックデータを記録する(ステップS13)。

【0047】

次にCPU11は、EEPROM14aより、再度第1ロジックデータを読み出す。なお、ここで読み出す第1ロジックデータは、ステップS11で読み出したデータと同一のデータである。

【0048】

第1ロジックデータが読み出されると、次にCPU11は、テンポラリレジスタに記録されている第1ロジックデータと、再度読み出した第1ロジックデータとを比較し、一致するか否かを判定する(ステップS15)。一致しない場合、CPU11は電源回路10を待機状態へ移行させる。

【0049】

一致する場合、次にCPU11は、一致した第1ロジックデータに含まれる各設定値を参照し、各設定値が予め定められた範囲内であるか否かを、設定値毎に判定する(ステップS16)。なおこの範囲を示す情報は、例えばCPU11が実行する制御プログラムの内部に予め組み込まれているものとする。

【0050】

予め定められた範囲を超える設定値が一つでも検出された場合、CPU11は、電源回路10を待機状態へ移行させる。予め定められた範囲を超える設定値が検出されなかった場合、CPU11は、第1ロジックデータに含まれる各設定値を、レジスタ19a〜19gに記録する(ステップS17)。例えば、AVDDの出力電圧を示す設定値であればレジスタ19cに記録し、VONの出力電圧を示す設定値であればレジスタ19eに記録する。

【0051】

次にCPU11は、AVDD出力回路15及びVON出力回路16を起動し、各電圧の出力を開始する(ステップS18)。なお起動後も、各レジスタ19に記録された設定値は保持される(ステップS19)。

【0052】

次にCPU11は、テンポラリレジスタに記録されている第1ロジックデータの値と、各レジスタ19a〜19gに記録されている設定値とを比較し、それぞれについて一致するか否かを判定する。

【0053】

一致しない設定値が検知された場合、CPU11は、各レジスタ19a〜19gを初期化した後、電圧の出力を停止するよう各部を制御して電源を遮断し、本処理を終了する。設定値が一致する場合、CPU11は、所定時間毎にステップS20の比較処理を繰り返し行う。

【0054】

なお、比較処理を行うタイミングとしては、例えばDC/DCのスイッチング周期と同期して比較処理を行う。またこの比較処理は、電源回路10がなんらかの要因により動作停止するまで継続する。

【0055】

以上に説明した本実施形態によれば、CPU11が、電源起動時にEEPROM14よりロジックデータを読み出してレジスタ19a〜19gに設定する。このため、起動の度に電源回路10へ設定コマンドを送信するマイコン等を、電源回路10に外部接続する必要がない。従って、アナログ方式の設定値固定型の電源回路が搭載されたセットにおいて、デジタル方式の電源回路を用いた仕様に変更する場合に、セット全体のシステムを変更する必要がない。

【0056】

また本実施形態によれば、ロジックデータの誤り検出を起動時に行い、さらに起動後において、周期的にロジックデータとレジスタ設定値との比較を行う。これにより、例えばサージ等によりレジスタ設定値が破損したとしても、装置が誤動作するのを回避することができる。

<その他の変形例>

【0057】

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【0058】

また上記実施形態では、パリティビットを用いてロジックデータの誤り検出を行っているが、誤り検出に用いる手法はこれに限定されるものではなく、本発明の主旨を逸脱しない範囲で変更可能である。例えば、8ビットのチェックサムをロジックデータに含めることにより、チェックサムを用いた誤り検出を行う形態でもよい。

【産業上の利用可能性】

【0059】

本発明は、マイクロプロセッサ、画像処理プロセッサ、マルチメディアプロセッサ、IPコア、パーソナルコンピュータ、ネットワークサーバ、モバイル機器、ゲーム機、PDAなどの装置において電源回路の汎用性向上を図る上で有用な技術である。

【符号の説明】

【0060】

1 液晶表示装置

10 電源回路

11 CPU(制御部、第1レジスタ)

12 OSC

13 保護回路

14a、14b EEPROM(記録部)

15 AVDD出力回路(出力部)

16 VON出力回路(出力部)

17 VCOM出力回路(出力部)

18a、18b ソフトスタート制御回路

19a〜19g レジスタ(第2レジスタ)

20 インタフェース部

30 TCON

40 表示部

41 LCDパネル(液晶表示パネル)

42 ソースドライバ

43 ゲートドライバ

T1 外部端子(入力端子)

T2〜T4 外部端子(出力端子)

【技術分野】

【0001】

本発明は、デジタル設定が可能な電源回路、及びこの電源回路を有する液晶表示装置に関するものである。

【背景技術】

【0002】

近年、外部のプロセッサからのコマンドを受けてデバイスに電圧を供給する電源回路において、コマンドを受信するためのデジタルインタフェースとしてI2C(Inter-Integrated Circuit)やSPI(System Packet Interface)等が利用されている。

【0003】

このような電源回路は、デジタルインタフェースを介して所定のコマンドが入力されることにより、その動作機能や動作範囲、動作形態をソフトウェア的に切り換えることが可能である。例えば、デジタルインタフェースに与えるコマンドによって、可変出力のレギュレータの出力電圧のオン/オフや、出力電圧の設定値を切り換える。

【0004】

上記の技術に関連して、入力されるコマンドの誤認識に起因して、電源回路、或いは電圧供給先のデバイスが誤動作するのを回避するための電源回路が開示・提案されている(例えば特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−20580号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、デジタルインタフェースを介してデジタル設定を行う電源回路は、コマンドを送信する周辺部品(例えばマイコン)を接続する必要があった。また、電源起動の度にコマンドを電源回路へ送信する必要であった。

【0007】

また、アナログ方式の電源回路を用いた電子装置において、デジタル方式の電源回路を用いた仕様に変更する場合、デジタルインタフェースやコマンドを送信する周辺部品が存在しないため、電子装置のシステム全体を見直す必要があった。

【0008】

本発明は、本願の発明者により見出された上記の問題点に鑑み、デジタル設定可能な電源回路であって、コマンド送信用の周辺部品によるデジタル設定を電源起動の度に行う必要がなく、またアナログ方式の電源回路の代替として用いることが可能な電源回路、及びこの電源回路を有する液晶表示装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明に係る電源回路は、デジタルデータにより動作設定を行う電源回路であって、前記動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部と、前記記録部に対して前記設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部と、前記記録部より前記設定情報を読み出して前記電源回路に対する動作設定を行う制御部と、を備えたことを特徴とする構成(第1の構成)とされている。

【0010】

なお、上記第1の構成から成る電源回路は、前記制御部が、前記記録部より読み出した前記設定情報に対して予め定められたチェック処理を行うことを特徴とする構成(第2の構成)にするとよい。

【0011】

また、上記第2の構成から成る電源回路は、前記制御部が、前記チェック処理においてエラーが検出された場合に前記電源回路を停止状態へ移行させることを特徴とする構成(第3の構成)にするとよい。

【0012】

また、上記第3の構成から成る電源回路は、前記電源回路が、揮発性の記録媒体である第1レジスタを備え、前記制御部は、前記チェック処理として、前記記録部より読み出した前記設定情報を前記第1レジスタに記録した後に再び前記記録部より前記設定情報を読み出し、読み出した該設定情報と前記第1レジスタに記録されている前記設定情報とが一致するか否かを判定し、一致しない場合に前記エラーが検出されたとみなすことを特徴とする構成(第4の構成)にするとよい。

【0013】

また、上記第4の構成から成る電源回路は、揮発性の記録媒体である第2レジスタを備え、前記制御部は、前記チェック処理として、前記判定の結果一致した前記設定情報を前記第2レジスタに記録し、前記第1レジスタに記録されている前記設定情報と前記第2レジスタに記録されている前記設定情報とが一致するか否かを予め定められた時間間隔で判定し、一致しない場合に前記エラーが検出されたとみなすことを特徴とする構成(第5の構成)にするとよい。

【0014】

また、上記第5の構成から成る電源回路は、前記制御部が、前記チェック処理として、パリティビットまたはチェックサムを用いた誤り検出を行うことを特徴とする構成(第6の構成)にするとよい。

【0015】

また、上記第6の構成から成る電源回路は、前記制御部が、前記チェック処理として、前記設定情報に含まれる設定値が予め定められる範囲を超えるか否かを判定する範囲チェックを行うことを特徴とする構成(第7の構成)にするとよい。

【0016】

また、上記第7の構成から成る電源回路は、前記記録部が、前記電源回路に接続される外部装置に応じて設定値を変更する必要のない前記設定情報を記録する第1記録部と、該外部装置に応じて設定値を変更する必要のある前記設定情報を記録する第2記録部と、を含むことを特徴とする構成(第8の構成)にするとよい。

【0017】

また、上記第8の構成から成る電源回路は、液晶表示装置への電圧供給を行う出力部を備え、第1記録部は前記液晶表示装置に対するドライバ駆動電圧の供給動作に用いられる前記設定情報を記録し、第2記録部は前記液晶表示装置に対するコモン電圧の供給動作に用いられる前記設定情報を記録することを特徴とする構成(第9の構成)にするとよい。

【0018】

また、本発明に係る液体表示装置は、前記ドライバ駆動電圧を受けて動作するソースドライバ及びゲートドライバと前記コモン電圧を受けて動作する液晶表示パネルとを有する表示部と、前記表示部に電力供給を行う第9の構成の電源回路とを有することを特徴とする構成(第10の構成)にするとよい。

【発明の効果】

【0019】

本発明によれば、デジタル設定可能な電源回路であって、電源起動の度に周辺部品によるデジタル設定を行う必要のない電源回路を提供することができる。このため、アナログ方式の設定値固定型の電源回路が搭載されたセットを、デジタル方式の電源回路を用いた仕様に変更する場合に、セット全体のシステムを変更する必要がない。

【0020】

また本実施形態によれば、設定情報に対するチェック処理を起動時に行い、さらに起動後においても周期的に行う。このため、サージ等により設定情報が破損したとしても、装置が誤動作する事態を回避することができる。

【図面の簡単な説明】

【0021】

【図1】本発明に係る電源回路を含んだ液晶表示装置を示すブロック図

【図2】本発明に係る設定情報を示すテーブル図

【図3】本発明に係る電源起動処理を示すフロー図

【発明を実施するための形態】

【0022】

<液晶表示装置>

図1は、本発明の電源回路を含む液晶表示装置の一構成例を示す図である。本構成例の液晶表示装置1は、電源回路10と、TCON30と、表示部40と、を有する。

【0023】

電源回路10は、入力電圧VIN(例えば5V)を受けて表示部40への電力供給(ソース電圧AVDD、ゲート電圧VON、コモン電圧VCOM等)を行う。

【0024】

TCON30は、表示部40の表示タイミングをとるためのロジック回路であり、シフトクロック等に必要なパルスを供給するタイミングコントローラである。

【0025】

表示部40は、電源回路10から供給される電圧に応じて任意の文字や画像を表示する。表示部40は少なくとも、LCDパネル41、ソースドライバ42、及びゲートドライバ43を含む構成となっている。ソースドライバ42/ゲートドライバ43は、LCDパネル41(液晶表示パネル)の各画素に配置されたトランジスタのON/OFFを制御することにより、液晶分子に電圧を印加する。

【0026】

<電源回路>

電源回路10は、CPU11(制御部、第1記録部)と、OSC12と、保護回路13と、EEPROM14a及び14b(記録部)と、AVDD出力回路15(出力部)と、VON出力回路16(出力部)と、VCOM出力回路17(出力部)と、ソフトスタート制御回路18a及び18bと、レジスタ19a〜19g(第2記録部)と、インタフェース部20と、を集積化したモノリシック半導体集積回路装置である。

【0027】

また、電源回路10は、外部との電気的な接続を確立するために、外部端子T1〜T4を有する。外部端子T1(入力端子)は、デジタル信号の入力端子である。外部端子T2は、AVDDの出力端子である。外部端子T3は、VONの出力端子である。外部端子T4は、VCOMの出力端子である。

【0028】

CPU(Central Processing Unit)11は、データの演算処理を行うロジック回路である。CPU11は、電源回路10の各部動作を統括的に制御する。またCPU11はその内部に、後述するロジックデータ(設定情報)を一時的に記録するテンポラリレジスタ(第1レジスタ)を有する。

【0029】

OSC(Oscillator)12は、CR発振回路等により、電源回路10が有する電子回路を動作させるためのクロック信号を生成して出力する。

【0030】

保護回路13は、電源回路10に含まれる各電源の電圧を監視し、電圧が予め定められた閾値を下回る時間が所定時間を超えたこと(=タイムアウト)が検知された場合に、全ての電源を停止させる。また保護回路13は、タイムアウトが発生したか否かを判定するための判定時間を、電源毎に設定する設定機能を有する。

【0031】

EEPROM14a及び14bは、CPU11が実行するシステムプログラムや、電源回路10の各部の動作設定を行うための設定値を示すロジックデータ等を記録した、不揮発性半導体メモリである。本実施形態では、図1に示すように、2つのEEPROM14a及び14bが電源回路10に設けられている。

【0032】

EEPROM14a(第1記録部)は、電源回路10の内部構成に応じて設定値を調整したロジックデータである第1ロジックデータを記録する。第1ロジックデータには例えば、AVDD出力回路15またはVON出力回路16の出力電圧や、ソフトスタート制御回路18のソフトスタート時間等が含まれる。第1ロジックデータは、電源回路10が含まれる基板の組み立て工程等において、EEPROM14aに記録される。

【0033】

EEPROM14b(第2記録部)は、電源回路10に外部接続される装置(本実施形態では表示部40)に応じて設定値を調整したロジックデータである第2ロジックデータを記録する。第2ロジックデータには例えば、VCOM出力回路17の出力電圧等が含まれる。第2ロジックデータは、電源回路10が含まれる装置(本実施形態では液晶表示装置1)の調整工程等において、EEPROM14bに記録される。

【0034】

図2は、第1ロジックデータの一例を示したテーブル図である。本実施形態の第1ロジックデータには、設定項目として、パリティビット、AVDD出力電圧、VON出力電圧、OSC周波数、AVDDソフトスタート時間、VONソフトスタート時間等が含まれている。各設定項目に対しては、レジスタマップ、ビット数、及び設定値(左から16進数表記、2進数表記、10進数及び単位表記)が関連付けられている。

【0035】

AVDD出力回路15は、ソースドライバ42に対してソース電圧AVDDを印加する。なお印加するソース電圧AVDDの大きさは、レジスタ19cに記録されている設定値に基づいて決定される。

【0036】

VON出力回路16は、ゲートドライバ43に対してゲート電圧VONを印加する。なお印加するゲート電圧VONの大きさは、レジスタ19dに記録されている設定値に基づいて決定される。

【0037】

VCOM出力回路17は、LDCパネル41を形成する全ての画素に共通のコモン電極に対してコモン電圧VCOMを印加する。なお印加するコモン電圧VCOMの大きさは、レジスタ19eに記録されている設定値に基づいて決定される。

【0038】

ソフトスタート制御回路18a及び18bは、AVDD出力回路15及びVON出力回路16の出力電圧が急峻に変化してオーバーシュートが発生するのを回避するための回路である。ソフトスタート制御回路18a及び18bは、レジスタ19d及び19fから読み出されたソフトスタート時間に基づき段階的に出力電圧を変化させるよう、AVDD出力回路15及びVON出力回路16を制御する。

【0039】

レジスタ19a〜19gは、各装置の動作に用いられる設定値を記録する揮発性の記録媒体である。本実施形態では、図1に示すように、レジスタ19a〜レジスタ19gの7つのレジスタを有する構成を例示している。各レジスタ19a〜19gは、OSC12〜ソフトスタート制御回路18の動作に用いられる設定値を記録するのに用いられる。

【0040】

インタフェース部20は、I2Cバス等を介して外部の装置と通信を行うためのインタフェースである。インタフェース部20は例えば、TCON30よりデジタル信号を入力するのに用いられる。また例えば、EEPROM14a及び14bにロジックデータを記録するための制御信号を、不図示のマイコン等から入力するのに用いられる。

【0041】

次に、電源回路10の電源起動時の処理フローについて、図3のフローチャートを参照しながら説明する。本フローチャートで例示する処理は、ユーザ操作等により液晶表示装置1の電源が投入され、UVLO(Under Voltage Lock Out)が解除されることにより開始される。

【0042】

なお以下では、EEPROM14aに記録された第1ロジックデータの読み出し及び設定について説明するが、EEPROM14bに記録された第2ロジックデータの読み出し及び設定についても、同様の処理順序により、並行ないしは順次実施するものとする。

【0043】

本処理の開始後、まずCPU11は、EEPROM14aより第1ロジックデータを読み出す(ステップS11)。

【0044】

第1ロジックデータが読み出されると、次にCPU11は、第1ロジックデータのパリティチェックを行う(ステップS12)。なおパリティチェックは、図2に示すパリティビットを用いて行う。

【0045】

パリティチェックの結果、エラーが検知された場合、CPU11は電源回路10を待機状態へ移行させる。なおこの待機状態は、例えば液晶表示装置1の電源が再起動されるまで継続される。

【0046】

パリティチェックの結果、エラーが検知されなかった場合、次にCPU11は、CPU11の内部に有するテンポラリレジスタに、読み出した第1ロジックデータを記録する(ステップS13)。

【0047】

次にCPU11は、EEPROM14aより、再度第1ロジックデータを読み出す。なお、ここで読み出す第1ロジックデータは、ステップS11で読み出したデータと同一のデータである。

【0048】

第1ロジックデータが読み出されると、次にCPU11は、テンポラリレジスタに記録されている第1ロジックデータと、再度読み出した第1ロジックデータとを比較し、一致するか否かを判定する(ステップS15)。一致しない場合、CPU11は電源回路10を待機状態へ移行させる。

【0049】

一致する場合、次にCPU11は、一致した第1ロジックデータに含まれる各設定値を参照し、各設定値が予め定められた範囲内であるか否かを、設定値毎に判定する(ステップS16)。なおこの範囲を示す情報は、例えばCPU11が実行する制御プログラムの内部に予め組み込まれているものとする。

【0050】

予め定められた範囲を超える設定値が一つでも検出された場合、CPU11は、電源回路10を待機状態へ移行させる。予め定められた範囲を超える設定値が検出されなかった場合、CPU11は、第1ロジックデータに含まれる各設定値を、レジスタ19a〜19gに記録する(ステップS17)。例えば、AVDDの出力電圧を示す設定値であればレジスタ19cに記録し、VONの出力電圧を示す設定値であればレジスタ19eに記録する。

【0051】

次にCPU11は、AVDD出力回路15及びVON出力回路16を起動し、各電圧の出力を開始する(ステップS18)。なお起動後も、各レジスタ19に記録された設定値は保持される(ステップS19)。

【0052】

次にCPU11は、テンポラリレジスタに記録されている第1ロジックデータの値と、各レジスタ19a〜19gに記録されている設定値とを比較し、それぞれについて一致するか否かを判定する。

【0053】

一致しない設定値が検知された場合、CPU11は、各レジスタ19a〜19gを初期化した後、電圧の出力を停止するよう各部を制御して電源を遮断し、本処理を終了する。設定値が一致する場合、CPU11は、所定時間毎にステップS20の比較処理を繰り返し行う。

【0054】

なお、比較処理を行うタイミングとしては、例えばDC/DCのスイッチング周期と同期して比較処理を行う。またこの比較処理は、電源回路10がなんらかの要因により動作停止するまで継続する。

【0055】

以上に説明した本実施形態によれば、CPU11が、電源起動時にEEPROM14よりロジックデータを読み出してレジスタ19a〜19gに設定する。このため、起動の度に電源回路10へ設定コマンドを送信するマイコン等を、電源回路10に外部接続する必要がない。従って、アナログ方式の設定値固定型の電源回路が搭載されたセットにおいて、デジタル方式の電源回路を用いた仕様に変更する場合に、セット全体のシステムを変更する必要がない。

【0056】

また本実施形態によれば、ロジックデータの誤り検出を起動時に行い、さらに起動後において、周期的にロジックデータとレジスタ設定値との比較を行う。これにより、例えばサージ等によりレジスタ設定値が破損したとしても、装置が誤動作するのを回避することができる。

<その他の変形例>

【0057】

なお、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【0058】

また上記実施形態では、パリティビットを用いてロジックデータの誤り検出を行っているが、誤り検出に用いる手法はこれに限定されるものではなく、本発明の主旨を逸脱しない範囲で変更可能である。例えば、8ビットのチェックサムをロジックデータに含めることにより、チェックサムを用いた誤り検出を行う形態でもよい。

【産業上の利用可能性】

【0059】

本発明は、マイクロプロセッサ、画像処理プロセッサ、マルチメディアプロセッサ、IPコア、パーソナルコンピュータ、ネットワークサーバ、モバイル機器、ゲーム機、PDAなどの装置において電源回路の汎用性向上を図る上で有用な技術である。

【符号の説明】

【0060】

1 液晶表示装置

10 電源回路

11 CPU(制御部、第1レジスタ)

12 OSC

13 保護回路

14a、14b EEPROM(記録部)

15 AVDD出力回路(出力部)

16 VON出力回路(出力部)

17 VCOM出力回路(出力部)

18a、18b ソフトスタート制御回路

19a〜19g レジスタ(第2レジスタ)

20 インタフェース部

30 TCON

40 表示部

41 LCDパネル(液晶表示パネル)

42 ソースドライバ

43 ゲートドライバ

T1 外部端子(入力端子)

T2〜T4 外部端子(出力端子)

【特許請求の範囲】

【請求項1】

デジタルデータにより動作設定を行う電源回路であって、

前記動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部と、

前記記録部に対して前記設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部と、

前記記録部より前記設定情報を読み出して前記電源回路に対する動作設定を行う制御部と、

を備えたことを特徴とする電源回路。

【請求項2】

前記制御部は、前記記録部より読み出した前記設定情報に対して予め定められたチェック処理を行うこと

を特徴とする請求項1に記載の電源回路。

【請求項3】

前記制御部は、前記チェック処理においてエラーが検出された場合に前記電源回路を停止状態へ移行させること

を特徴とする請求項2に記載の電源回路。

【請求項4】

前記電源回路は、揮発性の記録媒体である第1レジスタを備え、

前記制御部は、前記チェック処理として、前記記録部より読み出した前記設定情報を前記第1レジスタに記録した後に再び前記記録部より前記設定情報を読み出し、読み出した該設定情報と前記第1レジスタに記録されている前記設定情報とが一致するか否かを判定し、一致しない場合に前記エラーが検出されたとみなすこと

を特徴とする請求項3に記載の電源回路。

【請求項5】

前記電源回路は、揮発性の記録媒体である第2レジスタを備え、

前記制御部は、前記チェック処理として、前記判定の結果一致した前記設定情報を前記第2レジスタに記録し、前記第1レジスタに記録されている前記設定情報と前記第2レジスタに記録されている前記設定情報とが一致するか否かを予め定められた時間間隔で判定し、一致しない場合に前記エラーが検出されたとみなすこと

を特徴とする請求項4に記載の電源回路。

【請求項6】

前記制御部は、前記チェック処理として、パリティビットまたはチェックサムを用いた誤り検出を行うこと

を特徴とする請求項5に記載の電源回路。

【請求項7】

前記制御部は、前記チェック処理として、前記設定情報に含まれる設定値が予め定められる範囲を超えるか否かを判定する範囲チェックを行うこと

を特徴とする請求項6に記載の電源回路。

【請求項8】

前記記録部は、前記電源回路に接続される外部装置に応じて設定値を変更する必要のない前記設定情報を記録する第1記録部と、該外部装置に応じて設定値を変更する必要のある前記設定情報を記録する第2記録部と、を含むこと

を特徴とする請求項7に記載の電源回路。

【請求項9】

前記電源回路は、液晶表示装置への電圧供給を行う出力部を備え、

第1記録部は、前記液晶表示装置に対するドライバ駆動電圧の供給動作に用いられる前記設定情報を記録し、

第2記録部は、前記液晶表示装置に対するコモン電圧の供給動作に用いられる前記設定情報を記録すること

を特徴とする請求項8に記載の電源回路。

【請求項10】

前記ドライバ駆動電圧を受けて動作するソースドライバ及びゲートドライバと、前記コモン電圧を受けて動作する液晶表示パネルとを有する表示部と、

前記表示部に電力供給を行う請求項9に記載の電源回路と、

を有する液晶表示装置。

【請求項1】

デジタルデータにより動作設定を行う電源回路であって、

前記動作設定を行うための設定情報を記録する不揮発性の記録媒体を含む記録部と、

前記記録部に対して前記設定情報の記録/変更を行うためのデジタル信号を入力するインタフェース部と、

前記記録部より前記設定情報を読み出して前記電源回路に対する動作設定を行う制御部と、

を備えたことを特徴とする電源回路。

【請求項2】

前記制御部は、前記記録部より読み出した前記設定情報に対して予め定められたチェック処理を行うこと

を特徴とする請求項1に記載の電源回路。

【請求項3】

前記制御部は、前記チェック処理においてエラーが検出された場合に前記電源回路を停止状態へ移行させること

を特徴とする請求項2に記載の電源回路。

【請求項4】

前記電源回路は、揮発性の記録媒体である第1レジスタを備え、

前記制御部は、前記チェック処理として、前記記録部より読み出した前記設定情報を前記第1レジスタに記録した後に再び前記記録部より前記設定情報を読み出し、読み出した該設定情報と前記第1レジスタに記録されている前記設定情報とが一致するか否かを判定し、一致しない場合に前記エラーが検出されたとみなすこと

を特徴とする請求項3に記載の電源回路。

【請求項5】

前記電源回路は、揮発性の記録媒体である第2レジスタを備え、

前記制御部は、前記チェック処理として、前記判定の結果一致した前記設定情報を前記第2レジスタに記録し、前記第1レジスタに記録されている前記設定情報と前記第2レジスタに記録されている前記設定情報とが一致するか否かを予め定められた時間間隔で判定し、一致しない場合に前記エラーが検出されたとみなすこと

を特徴とする請求項4に記載の電源回路。

【請求項6】

前記制御部は、前記チェック処理として、パリティビットまたはチェックサムを用いた誤り検出を行うこと

を特徴とする請求項5に記載の電源回路。

【請求項7】

前記制御部は、前記チェック処理として、前記設定情報に含まれる設定値が予め定められる範囲を超えるか否かを判定する範囲チェックを行うこと

を特徴とする請求項6に記載の電源回路。

【請求項8】

前記記録部は、前記電源回路に接続される外部装置に応じて設定値を変更する必要のない前記設定情報を記録する第1記録部と、該外部装置に応じて設定値を変更する必要のある前記設定情報を記録する第2記録部と、を含むこと

を特徴とする請求項7に記載の電源回路。

【請求項9】

前記電源回路は、液晶表示装置への電圧供給を行う出力部を備え、

第1記録部は、前記液晶表示装置に対するドライバ駆動電圧の供給動作に用いられる前記設定情報を記録し、

第2記録部は、前記液晶表示装置に対するコモン電圧の供給動作に用いられる前記設定情報を記録すること

を特徴とする請求項8に記載の電源回路。

【請求項10】

前記ドライバ駆動電圧を受けて動作するソースドライバ及びゲートドライバと、前記コモン電圧を受けて動作する液晶表示パネルとを有する表示部と、

前記表示部に電力供給を行う請求項9に記載の電源回路と、

を有する液晶表示装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2013−89107(P2013−89107A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−230432(P2011−230432)

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月20日(2011.10.20)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]