電源回路、集積回路装置、固体撮像装置および電子機器

【課題】電源回路において、ソフトスタート回路による電源回路の回路規模を抑制する。

【解決手段】電源回路1の比較部11は、参照電圧と入力電圧とを比較して電圧差信号を出力し、出力電圧生成部12は、電圧差信号に基づいて出力電圧を生成し、入力電圧生成部14は、出力電圧から入力電圧を生成する。抵抗素子16は、電流出力部15の参照電流により参照電圧を生成する。キャパシタ17は、抵抗素子16と並列に接続され、参照電流により充電される。このような電源回路1において、電流出力部15は、起動する際の参照電流を、動作中の参照電流より小さくする。

【解決手段】電源回路1の比較部11は、参照電圧と入力電圧とを比較して電圧差信号を出力し、出力電圧生成部12は、電圧差信号に基づいて出力電圧を生成し、入力電圧生成部14は、出力電圧から入力電圧を生成する。抵抗素子16は、電流出力部15の参照電流により参照電圧を生成する。キャパシタ17は、抵抗素子16と並列に接続され、参照電流により充電される。このような電源回路1において、電流出力部15は、起動する際の参照電流を、動作中の参照電流より小さくする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、安定した電圧を出力する電源回路、集積回路装置、固体撮像装置および電子機器に関する。

【背景技術】

【0002】

電源回路は、所望の出力電圧を出力するために、出力電圧を参照電圧と比較し、出力電圧が参照電圧に対応した電圧となるように出力トランジスタなどの出力スイッチング素子をオンオフ制御する。

このような電源回路では、出力スイッチング素子をデジタル的にオンオフ制御するPWM(Pulse Width Modulation)制御方式、オンオフ制御するコンパレータ方式などが広く知られている。また、電源回路には、入力電圧より高い電圧を出力する昇圧型のものと、入力電圧より低い電圧を出力する降圧型のものとがある。

PWM制御方式では、たとえば出力電圧が参照電圧を下回る期間において、これらの電位差に応じたパルス幅の制御信号により出力スイッチング素子をオンオフ制御する。

コンパレータ方式では、たとえば出力電圧が参照電圧を下回った場合、出力電圧が参照電圧を上回るまで、出力スイッチング素子をオン状態に制御する。

また、コンパレータ方式には、たとえばヒステリシスコンパレータを用いて、出力電圧が下回る際に使用する参照電圧より、出力電圧が上回る際に使用する参照電圧が高くなるように、参照電圧を制御するヒステリシス制御方式のものがある(特許文献1)。

【0003】

ところで、これらの各方式の電源回路では、出力電圧と比較される参照電圧を起動時に徐々に立ち上げるソフトスタート回路を設けることがある。

ソフトスタート回路を設けることにより、起動直後の電源回路において、参照電圧と出力電圧との間に大きな電位差が生じないようにすることができる。

また、ソフトスタート回路には、キャパシタなどを用いた時定数回路が用いられる(特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−060978号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、このように電源回路にキャパシタを用いたソフトスタート回路を追加した場合、必要とするソフトスタート期間に応じて大容量のキャパシタが必要になる。

キャパシタの容量は面積に比例するため、電源回路の回路規模が大きくなり、たとえば集積回路における電源回路の占有面積が大きくなってしまう。

【0006】

このように電源回路では、ソフトスタート回路による電源回路の回路規模の大型化を抑制することが求められている。

【課題を解決するための手段】

【0007】

本発明の第1の観点の電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の前記参照電流より小さくする。

【0008】

本発明の第2の観点の集積回路装置は、出力電圧を出力する電源回路と、出力電圧が給電される被給電回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0009】

本発明の第3の観点の固体撮像装置は、複数の画素回路が二次元に配列され、各画素回路のアナログの画素信号を出力する画素アレイ部と、アナログの画素信号をデジタルに変換するカラム回路と、デジタルの画素信号をデジタル処理するデジタル処理部と、デジタル処理されたデジタルの画素信号を出力する出力制御部と、画素アレイ部、カラム回路、デジタル処理部および出力制御部のうちの少なくとも1個に出力電圧を出力する電源回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0010】

本発明の第4の観点の電子機器は、出力電圧を出力する電源回路と、出力電圧が給電される被給電回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0011】

本発明では、起動する際、キャパシタは、動作中の参照電流より小さい電流により充電される。

よって、本発明では、キャパシタの容量を小さくしつつ、長いソフトスタート期間が得られる。

【発明の効果】

【0012】

本発明では、ソフトスタート回路による電源回路の回路規模の大型化を抑制することができる。

【図面の簡単な説明】

【0013】

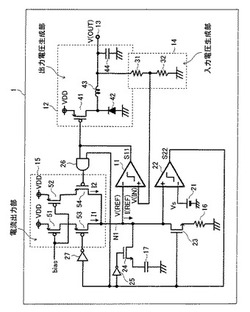

【図1】図1は、本発明の第1実施形態に係る電源回路の回路図である。

【図2】図2は、図1の電源回路のヒステリシス機能に関係する部分の回路図である。

【図3】図3は、図1の電源回路のヒステリシス動作のタイミングチャートである。

【図4】図4は、スロースタート動作の説明図である。

【図5】図5は、図1の電源回路での起動時の各種スイッチ動作トランジスタの動作説明図である。

【図6】図6は、図1の電源回路の起動動作のタイミングチャートである。

【図7】図7は、本発明の第2実施形態に係る固体撮像装置のブロック図である。

【図8】図8は、本発明の第3実施形態に係る固体撮像装置のブロック図である。

【図9】図9は、本発明の第4実施形態に係る固体撮像装置のブロック図である。

【図10】図10は、本発明の第5実施形態に係る電源回路の回路図である。

【図11】図11は、本発明の第6実施形態に係る撮像装置のブロック図である。

【図12】図12は、PWM制御方式の電源回路の説明図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を図面に関連付けて説明する。

説明は以下の順に行う。

1.第1実施形態(電源回路1の一例)

2.第2実施形態(固体撮像装置2の第1の例)

3.第3実施形態(固体撮像装置2の第2の例)

4.第4実施形態(固体撮像装置2の第3の例)

5.第5実施形態(電源回路1の他の例)

6.第6実施形態(撮像装置3の一例)

【0015】

<1.第1実施形態>

[電源回路1の構成]

図1は、本発明の第1実施形態に係る電源回路1の回路図である。

図1の電源回路1は、メインコンパレータ11、出力電圧生成部12、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、スロースタート用キャパシタ17を有する。

そして、図1の電源回路1は、メインコンパレータ11においてノードN1の参照電圧V(REF)と、出力電圧V(OUT)に基づく入力電圧V(IN)とを比較し、入力電圧V(IN)が参照電圧V(REF)となるように出力電圧V(OUT)を制御する。

電源回路1は、電源出力端子13から出力電圧V(OUT)を出力する。

【0016】

また、図1の電源回路1は、判定電圧生成部21、切替用コンパレータ22、抵抗接続トランジスタ23、容量接続トランジスタ24、容量用インバータ25、電源用論理回路26、電源用インバータ27を有する。

そして、図1の電源回路1は、これらの制御系の回路により、メインコンパレータ11にヒステリシス特性を持たせ、起動時に参照電圧V(REF)を徐々に上げるスロースタート機能を実現する。

ヒステリシス制御方式の電源回路1は、PWM制御方式のものと比べた場合、出力電圧のリップル成分が大きくなるが、応答速度が良い、発振しにくい、構成が簡素であるなどのメリットがある。

【0017】

なお、図1の電源回路1は、その全体が図示しない半導体基板上に集積化され、半導体基板上の集積回路の一部として実現されている。

【0018】

入力電圧生成部14は、第1分圧抵抗素子31と、第2分圧抵抗素子32とを有する。

第1分圧抵抗素子31および第2分圧抵抗素子32は、たとえば集積回路の配線層または拡散層により形成される。

第1分圧抵抗素子31は、一端が電源出力端子13に接続され、他端が第2分圧抵抗素子32の一端に接続される。第2分圧抵抗素子32の他端は、基板のグランドに接続される。

そして、入力電圧生成部14は、出力電圧V(OUT)を第1分圧抵抗素子31および第2分圧抵抗素子32で分圧し、入力電圧V(IN)を生成する。

【0019】

メインコンパレータ11は、反転入力ノード(−)、非反転入力ノード(+)、および出力ノードを有する。

メインコンパレータ11は、半導体基板に形成されたたとえば差動アンプにより形成することができる。

反転入力ノード(−)は、ノードN1に接続され、参照電圧V(REF)が入力される。

非反転入力ノード(+)は、参照電圧V(REF)生成部に接続され、入力電圧V(IN)が入力される。

そして、メインコンパレータ11は、入力電圧V(IN)を参照電圧V(REF)と比較し、参照電圧V(REF)と前記入力電圧V(IN)との電圧差に応じた電圧差信号S11を出力ノードから出力する。

たとえば入力電圧V(IN)が参照電圧V(REF)より低い場合、メインコンパレータ11は、ローレベルの電圧差信号S11を出力する。

また、入力電圧V(IN)が参照電圧V(REF)より高い場合、メインコンパレータ11は、ハイレベルの電圧差信号S11を出力する。

【0020】

出力電圧生成部12は、出力トランジスタ41、ダイオード42、インダクタ素子43、および平滑キャパシタ44を有する。

【0021】

出力トランジスタ41は、たとえば半導体基板に形成されたPMOSトランジスタである。

出力トランジスタ41は、ドレインが基板の電源VDDに接続され、ソースがダイオード42のカソードおよびインダクタ素子43の一端に接続され、ゲートがメインコンパレータ11の出力ノードに接続される。

【0022】

ダイオード42は、たとえば半導体基板のPN接合により形成され、アノードからカソードへ電流を流す特性を有する。

ダイオード42のアノードは、基板のグランドに接続される。

【0023】

インダクタ素子43は、たとえば集積回路の配線層や層間ビア、パッケージのワイヤボンディング、外付けインダクタ素子により形成される。

インダクタ素子43の他端は、電源出力端子13および平滑キャパシタ44の一端に接続される。

【0024】

平滑キャパシタ44は、たとえば集積回路の二層の配線層により形成される。

平滑キャパシタ44は、一端が電源出力端子13に接続され、他端が基板のグランドに接続される。

【0025】

そして、出力トランジスタ41は、メインコンパレータ11からローレベルの電圧差信号S11が入力されると、オン状態となる。

この場合、出力トランジスタ41およびインダクタ素子43を通じて、基板の電源VDDから平滑キャパシタ44へ電流が流れ、平滑キャパシタ44が充電される。

平滑キャパシタ44の充電電圧は、インダクタ素子43と平滑キャパシタ44とによる共振回路の特性に基づいてリップル成分を持ちながら上昇する。

この平滑キャパシタ44の充電電圧が、電源出力端子13から出力される。

【0026】

また、電圧差信号S11がハイレベルになると、出力トランジスタ41は、オフ状態となる。

仮にたとえば電源出力端子13に被給電回路が接続されているとした場合、被給電回路は、平滑キャパシタ44に蓄積された電荷を電流として使用する。

これにより、平滑キャパシタ44の充電電圧は、すなわち出力電圧V(OUT)は低下する。

【0027】

電流出力部15は、メイン電流源トランジスタ51、サブ電流源トランジスタ52、メインスイッチトランジスタ53、およびサブスイッチトランジスタ54を有する。

【0028】

メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、たとえば半導体基板に形成されたPMOSトランジスタである。

メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、ドレインが基板の電源VDDに接続され、ゲートが図示しないバイアス回路に接続される。

これにより、メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、バイアス電圧と電源電圧VDDとの電位差に応じた電流を供給する。

【0029】

ただし、メイン電流源トランジスタ51は、サブ電流源トランジスタ52より大きい電流をノードN1へ供給する。

たとえばメイン電流源トランジスタ51は、75マイクロアンペアを供給し、サブ電流源トランジスタ52は、1.6マイクロアンペアを供給する。

以下、メイン電流源トランジスタ51が供給する電流を第1電流I1とよび、サブ電流源トランジスタ52が供給する電流を第2電流I2とよぶ。

【0030】

メインスイッチトランジスタ53は、たとえば半導体基板に形成されたPMOSトランジスタである。

メインスイッチトランジスタ53は、ドレインがメイン電流源トランジスタ51のソースに接続され、ソースがノードN1に接続され、ゲートが電源用インバータ27の出力ノードに接続される。

そして、メインスイッチトランジスタ53は、ローレベルが入力されるとオン状態となり、ハイレベルが入力されるとオフ状態となる。

メインスイッチトランジスタ53は、オン状態である場合に、ノードN1に第1電流I1を供給する。

【0031】

サブスイッチトランジスタ54は、たとえば半導体基板に形成されたPMOSトランジスタである。

サブスイッチトランジスタ54は、ドレインがサブ電流源トランジスタ52のソースに接続され、ソースがノードN1に接続され、ゲートが電源用論理回路26の出力ノードに接続される。

そして、サブスイッチトランジスタ54は、ローレベルが入力されるとオン状態となり、ハイレベルが入力されるとオフ状態となる。

サブスイッチトランジスタ54は、オン状態である場合に、ノードN1に第2電流I2を供給する。

【0032】

以下、このメインスイッチトランジスタ53およびサブスイッチトランジスタ54を通じて電流出力部15がノードN1へ供給する電流を参照電流I(REF)とよぶ。

参照電流I(REF)の電流値は、メインスイッチトランジスタ53およびサブスイッチトランジスタ54のオンオフ状態に応じて変化する。

【0033】

抵抗素子16は、たとえば集積回路の配線層または拡散層に形成される。

抵抗接続トランジスタ23は、たとえば半導体基板に形成されたNMOSトランジスタである。

抵抗接続トランジスタ23は、ソースがノードN1に接続され、ドレインが抵抗素子16の一端に接続され、ゲートが切替用コンパレータ22の出力ノードに接続される。

抵抗素子16の他端は、基板のグランドに接続される。

これにより、抵抗素子16は、抵抗接続トランジスタ23がオン状態である場合、ノードN1に接続される。そして、抵抗素子16には、電流出力部15が出力した参照電流I(REF)が流れ、参照電圧V(REF)を発生する。

【0034】

スロースタート用キャパシタ17は、たとえば集積回路の二層の配線層により形成される。

容量接続トランジスタ24は、たとえば半導体基板に形成されたNMOSトランジスタである。

【0035】

容量接続トランジスタ24は、ソースがノードN1に接続され、ドレインがスロースタート用キャパシタ17の一端に接続され、ゲートが容量用インバータ25の出力ノードに接続される。

容量接続トランジスタ24は、基板のグランドに接続される。

これにより、容量接続トランジスタ24は、容量接続トランジスタ24がオン状態である場合、ノードN1に接続される。そして、容量接続トランジスタ24は、抵抗素子16と並列に接続される。

また、容量接続トランジスタ24は、電流出力部15が出力した参照電流I(REF)により充電される。

容量接続トランジスタ24は、参照電流I(REF)の電流値および容量接続トランジスタ24の容量に応じた充電速度で充電される。

【0036】

判定電圧生成部21は、たとえば一定の電圧を発生する電圧回路である。

判定電圧生成部21は、判定電圧Vsを生成する。

判定電圧Vsは、起動後の動作状態における参照電圧V(REF)より低い電圧であればよい。

【0037】

切替用コンパレータ22は、反転入力ノード(−)、非反転入力ノード(+)、および出力ノードを有する。

切替用コンパレータ22は、半導体基板に形成されたたとえば差動アンプにより形成することができる。

非反転入力ノード(+)は、ノードN1に接続され、参照電圧V(REF)が入力される。

反転入力ノード(−)は、判定電圧生成部21に接続され、判定電圧Vsが入力される。

そして、切替用コンパレータ22は、参照電圧V(REF)を判定電圧Vsと比較し、参照電圧V(REF)と判定電圧Vsとの電圧差に応じた判定信号S22を出力ノードから出力する。

たとえば参照電圧V(REF)が判定電圧Vsより低い場合、切替用コンパレータ22は、ローレベルの判定信号S22を出力する。

また、参照電圧V(REF)が判定電圧Vsより高い場合、切替用コンパレータ22は、ハイレベルの判定信号S22を出力する。

【0038】

容量用インバータ25および電源用インバータ27の入力ノードには、切替用コンパレータ22の出力ノードが接続される。

そして、容量用インバータ25は、判定信号S22を反転して、容量接続トランジスタ24へ出力する。

また、電源用インバータ27は、判定信号S22を反転して、メインスイッチトランジスタ53へ出力する。

【0039】

電源用論理回路26は、たとえば二入力の論理積回路である。

電源用論理回路26は、一方の入力ノードにメインコンパレータ11の出力ノードが接続され、他方の入力ノードに切替用コンパレータ22の出力ノードが接続される。

そして、電源用論理回路26は、電圧差信号S11および判定信号S22が共にハイレベルである場合、ハイレベルの論理積信号をサブスイッチトランジスタ54へ出力する。

それ以外の場合は、ローレベルの論理積信号を出力する。

【0040】

[ヒステリシス動作]

図2は、図1の電源回路1のヒステリシス機能に関する部分の回路図である。

電源回路1が起動され、出力電圧V(OUT)が略参照電圧V(REF)に対応した電圧となっている状態では、抵抗接続トランジスタ23および電源用インバータ27がオン状態に維持され、容量接続トランジスタ24がオフ状態に維持される。

また、容量用インバータ25がハイレベルの判定信号S22を出力するので、メインコンパレータ11の電圧差信号S11の信号レベルがそのままサブスイッチトランジスタ54に入力される状態になる。

【0041】

図3は、図1の電源回路1のヒステリシス動作のタイミングチャートである。

図3(A)は、メインコンパレータ11に入力される参照電圧V(REF)および入力電圧V(IN)の波形である。図3(B)は、メインコンパレータ11が出力する電圧信号の波形である。

【0042】

そして、図3のタイミングT1では、入力電圧V(IN)が参照電圧V(REF)より高い。

この場合、メインコンパレータ11は、ハイレベルの電圧差信号S11を出力する。

電圧差信号S11がハイレベルである場合、サブスイッチトランジスタ54は、オフ状態である。よって、抵抗素子16には、第1電流I1および第2電流I2のうちの第1電流I1のみが流れる。参照電圧V(REF)は、第1電流I1のみによる電圧となる。

また、電圧差信号S11がハイレベルである場合、出力トランジスタ41はオフ状態となる。よって、平滑キャパシタ44は、充電されず、既に充電された電圧を出力する。

【0043】

タイミングT2では、入力電圧V(IN)が参照電圧V(REF)より低くなる。

この場合、メインコンパレータ11は、電圧差信号S11をハイレベルからローレベルへ切り替える。

電圧差信号S11がローレベルになると、サブスイッチトランジスタ54は、オン状態となる。よって、抵抗素子16には、第1電流I1および第2電流I2が流れる。参照電圧V(REF)は、第1電流I1のみによる電圧より、高い電圧となる。

また、電圧差信号S11がローレベルになると、出力トランジスタ41はオン状態となる。よって、平滑キャパシタ44は、充電される。

その結果、タイミングT3に示すように、平滑キャパシタ44の充電に追従して、入力電圧V(IN)も上昇する。

【0044】

タイミングT4では、入力電圧V(IN)が、高い電圧状態にある参照電圧V(REF)より高くなる。

この場合、メインコンパレータ11は、電圧差信号S11をローレベルからハイレベルへ切り替える。

電圧差信号S11がハイレベルになると、サブスイッチトランジスタ54は、オフ状態となる。よって、抵抗素子16には、第1電流I1のみが流れる。参照電圧V(REF)は、再び第1電流I1のみによる低い電圧となる。

また、電圧差信号S11がハイレベルになると、出力トランジスタ41はオフ状態となる。よって、平滑キャパシタ44は、充電されない。

【0045】

以上の動作により、図1の電源回路1は、入力電圧V(IN)が高いレベルから低いレベルへ変化する場合と、入力電圧V(IN)が低いレベルから高いレベルへ変化する場合とで、異なる電圧レベルの参照電圧V(REF)と比較する。

また、電源回路1は、この比較結果に応じて、出力トランジスタ41のオンオフを制御する。

よって、メインコンパレータ11は、ヒステリシス特性を有する。

【0046】

[スロースタート動作]

図4は、スロースタート動作の説明図である。

図4の説明図では、メインコンパレータ11の非反転入力ノード(+)にスロースタート回路が接続されている。

このスロースタート回路は、電流源と、スロースタート用キャパシタ17とを有する。電流源は、図1の電流出力部15に対応する。

【0047】

そして、図4の電源回路1では、起動されると、電流源は、電流を出力し、スロースタート用キャパシタ17を充電する。

スロースタート用キャパシタ17の充電電圧は、電流源から供給される電流にしたがって徐々に上昇する。

メインコンパレータ11は、この起動後に徐々に上昇する参照電圧V(REF)と入力電圧V(IN)とを比較する。

入力電圧V(IN)が参照電圧V(REF)より低い場合、メインコンパレータ11は、ローレベルの電圧差信号S11を出力し、出力トランジスタ41をオン状態に制御する。出力トランジスタ41がオン状態になると、平滑キャパシタ44は充電される。

また、入力電圧V(IN)が参照電圧V(REF)より高くなると、メインコンパレータ11は、出力トランジスタ41をオフ状態に制御する。平滑キャパシタ44の充電は停止する。

このようにメインコンパレータ11は、起動後に徐々に上昇する参照電圧V(REF)に応じて平滑キャパシタ44の充電と停止とを繰り返す。

その結果、出力トランジスタ41を通じて平滑キャパシタ44に流れる電流も小さくなる。

【0048】

これに対して、仮にたとえば図4のスロースタート用キャパシタ17の換わりに抵抗素子16が接続されていた場合、参照電圧V(REF)は電源回路1の起動直後に所定の電圧となる。

この場合、メインコンパレータ11は、入力電圧V(IN)が参照電圧V(REF)より高くなるまで、出力トランジスタ41をオン状態に維持する。

また、平滑キャパシタ44は、大きな電流(突入電流)により一気に充電される。

【0049】

図5は、図1の電源回路1での起動時の各種スイッチ動作トランジスタの動作説明図である。

図5には、ノードN1に接続されたサブスイッチトランジスタ54、メインスイッチトランジスタ53、抵抗接続トランジスタ23、および容量接続トランジスタ24が示されている。

【0050】

そして、図5の表の上段に示すように、参照電圧V(REF)が判定電圧Vsより低い場合、サブスイッチトランジスタ54および容量接続トランジスタ24はオン状態となり、メインスイッチトランジスタ53および抵抗接続トランジスタ23はオフ状態となる。

よって、ノードN1には、サブ電流源トランジスタ52とスロースタート用キャパシタ17とが接続される。

電源回路1において図4の回路が実現され、スロースタート用キャパシタ17は、第2電流I2により充電される。

【0051】

また、図5の表の下段に示すように、参照電圧V(REF)が判定電圧Vsより高い場合、メインスイッチトランジスタ53および抵抗接続トランジスタ23はオン状態となり、サブスイッチトランジスタ54および容量接続トランジスタ24はオフ状態となる。

よって、ノードN1には、メインスイッチトランジスタ53および抵抗接続トランジスタ23とが接続される。

電源回路1において図2の回路が実現され、抵抗素子16は、第1電流I1により所望の参照電圧V(REF)を発生する。

【0052】

図6は、図1の電源回路1の起動動作のタイミングチャートである。

図6(A)は、ノードN1の参照電圧V(REF)の波形である。図6(B)は、切替用コンパレータ22が出力する判定信号S22の波形である。図6(C)は、サブスイッチトランジスタ54のゲート信号の波形である。図6(D)は、メインスイッチトランジスタ53のゲート信号の波形である。図6(E)は、抵抗接続トランジスタ23のゲート信号の波形である。図6(F)は、容量接続トランジスタ24のゲート信号の波形である。

【0053】

タイミングT11において電源回路1が起動されると、判定電圧生成部21は、判定電圧Vsを出力する。

停止状態および起動直後の電源回路1において、参照電圧V(REF)および出力電圧V(OUT)は共に0V(グランドレベル)である。よって、起動直後の参照電圧V(REF)は、判定電圧Vsより低い。

このため、図6(B)に示すように、切替用コンパレータ22は、ローレベルの判定信号S22を出力する。

また、サブスイッチトランジスタ54は、図6(C)に示すようにハイレベルの信号が入力され、オン状態となり、メインスイッチトランジスタ53は、図6(D)に示すようにハイレベルの信号が入力され、オフ状態となる。

よって、サブ電流源トランジスタ52のみがノードN1に接続され、電流出力部15は、第2電流I2のみをノードN1に供給する。

また、抵抗接続トランジスタ23は、図6(E)に示すようにオフ状態となり、容量接続トランジスタ24は、図6(F)に示すようにオン状態となる。

よって、起動直後は、容量接続トランジスタ24のみがノードN1に接続され、容量接続トランジスタ24は、第2電流I2で充電される。

その結果、容量接続トランジスタ24の充電電圧、すなわち参照電圧V(REF)は、図6(A)に示すように、第1電流I1より小さい第2電流I2で充電されることにより、時間をかけて徐々に上昇する。

【0054】

そして、タイミングT12において参照電圧V(REF)が判定電圧Vsを超えると、切替用コンパレータ22は、図6(B)に示すように判定信号S22をローレベルからハイレベルへ切り替える。

また、サブスイッチトランジスタ54は、図6(C)に示すようにローレベルの信号が入力され、オフ状態となり、メインスイッチトランジスタ53は、図6(D)に示すようにローレベルの信号が入力され、オン状態となる。

よって、メイン電流源トランジスタ51のみがノードN1に接続され、電流出力部15は、第1電流I1のみをノードN1に供給する。

また、抵抗接続トランジスタ23は、図6(E)に示すようにオン状態となり、容量接続トランジスタ24は、図6(F)に示すようにオフ状態となる。

よって、参照電圧V(REF)が判定電圧Vsを超えると、抵抗素子16のみがノードN1に接続され、抵抗素子16は、第1電流I1による参照電圧V(REF)を発生する。

【0055】

以上の動作により、電源回路1は起動され、メインコンパレータ11は、入力電圧V(IN)と参照電圧V(REF)とを比較し、これに応じて出力トランジスタ41をオンオフ制御する。

出力電圧V(OUT)は、入力電圧V(IN)が参照電圧V(REF)と略等しくなるように制御される。

【0056】

その後、出力電圧V(OUT)が下がり、たとえばタイミングT13において入力電圧V(IN)が参照電圧V(REF)を下回ると、メインコンパレータ11は、電圧差信号S11をハイレベルからローレベルに切り替える。

起動後の通常動作状態では、参照電圧V(REF)は判定電圧Vsより高いので、切替用コンパレータ22は、常にハイレベルの判定信号S22を出力している。

よって、電源用論理回路26は、電圧差信号S11のレベルをそのままサブスイッチトランジスタ54へ出力する。

また、サブスイッチトランジスタ54は、電圧差信号S11がハイレベルからローレベルに切り替わると、図6(C)に示すようにオン状態となる。

これにより、抵抗素子16には第1電流I1および第2電流I2が流れ、参照電圧V(REF)が少し上昇する。

【0057】

また、電圧差信号S11がハイレベルからローレベルに切り替わることにより、出力トランジスタ41がオン状態となり、平滑キャパシタ44が充電され、入力電圧生成部14が出力電圧V(OUT)に基づいて生成する入力電圧V(IN)が上昇する。

そして、入力電圧V(IN)が少し高くなった参照電圧V(REF)を超えると、メインコンパレータ11は、電圧差信号S11をローレベルからハイレベルに切り替える。

これにより、サブスイッチトランジスタ54は、オフ状態となり、参照電圧V(REF)は、第1電流I1のみによる元の電圧に戻る。

【0058】

通常動作状態では、電源回路1は以上の動作により、出力電圧V(OUT)を所望の電圧に維持する。

これにより、電源回路1は、所定の電圧レベルに安定した主力電圧を生成し、電源出力端子13から出力することができる。

【0059】

以上のように、第1実施形態の電源回路では、起動する際、スロースタート用キャパシタ17は、動作中の参照電流I(REF)より小さい電流(第2電流I2)により充電される。

よって、スロースタート用キャパシタ17の容量を小さくしても、長いソフトスタート期間が得られる。

【0060】

ここで、スロースタート機能を実現するために、本実施形態のように電流を絞った場合と、電流を絞らなかった場合における電源回路1の追加面積について説明する。

ここでは、たとえばスロースタート用キャパシタ17の電圧を、0ボルトから1.2ボルトまで上昇させるときのスロースタート時間として100マイクロ秒を実現する場合について説明する。

電流を絞らない場合、スロースタート用キャパシタ17の容量C1は、以下の式1の値となる。

これに対して、本実施形態のように電流を絞った場合、スロースタート用キャパシタ17の容量C2は、以下の式2の値となる。

下記の式1および式2から明らかなように、電流を絞ることにより、スロースタート用キャパシタ17の容量を約47分の1にすることができる。

【0061】

C1=I(REF)×T÷Vdif=75μA×100μs÷1.2V=6.25nF ・・・式1

C21=1.6μA×100μs÷1.2V=133pF ・・・式2

【0062】

また、電流を絞らない場合の6.25nFのスロースタート用キャパシタ17の面積は、あるプロセスにおいて約3.1329(=1.77mm×1.77mm)平方mmとなる。

これに対して、本実施形態のように電流を絞った場合の面積は、本実施形態での追加回路を考慮したとしても、約0.0708平方mmとなる。

ここでは、133pFのスロースタート用キャパシタ17の面積を約0.0676(=0.26mm×0.26mm)平方mmと計算し、追加回路の面積を約0.0032(=0.08mm×0.04mm)平方mmとして計算している。

このように本実施形態での追加面積は、追加回路を考慮したとしても、電流を絞らない場合の約1/44になる。

【0063】

また、第1実施形態では、入力電圧V(IN)が参照電圧V(REF)より低い場合、サブスイッチトランジスタ54はオン状態となり、第2電流I2が第1電流I1とともに抵抗素子16へ供給される。この場合、参照電圧V(REF)は高くなる。

逆に、入力電圧V(IN)が参照電圧V(REF)より高い場合、サブスイッチトランジスタ54はオフ状態となり、第1電流I1のみが抵抗素子16へ供給される。この場合、参照電圧V(REF)は低くなる。

このように第1実施形態では、入力電圧V(IN)に応じて参照電圧V(REF)が大小するので、メインコンパレータ11は、ヒステリシス特性を持つ。

そして、第1実施形態では、起動する際には、第2電流I2のみをスロースタート用キャパシタ17へ供給して参照電圧V(REF])を発生するので、起動する際の参照電流I(REF)は、動作中より小さくなる。

このように電流出力部15は、メインコンパレータ11にヒステリシス特性を持たせるための電流源としての機能と、スロースタート用の電流源としての機能とを兼用する。

よって、第1実施形態では、これら複数の回路を別々に設けた場合より電源回路1の回路構成を単純化し、回路規模を抑えることができる。

また、第1実施形態では、スロースタート時の電流を第2電流I2のみにしぼったので、スロースタート用キャパシタ17の容量を小さくしても、長いスロースタート期間を確保することができる。

【0064】

また、第1実施形態では、スロースタート用キャパシタ17は、起動した後の動作中にノードN1から切り離される。

よって、動作中の第1電流I1および第2電流I2は、すべて抵抗素子16に流れる。

その結果、動作中の参照電圧V(REF)は、電源回路1の出力電圧V(OUT)の増減に応じて早い応答速度により変化することができる。

すなわち、第1実施形態では、スロースタート用キャパシタ17がヒステリシス特性を有するメインコンパレータ11の応答特性を悪化させないようにすることができる。

【0065】

<2.第2実施形態>

[固体撮像装置2の構成および動作]

図7は、本発明の第2実施形態に係る固体撮像装置2のブロック図である。

図7の固体撮像装置2は、画素アレイ部61、複数のカラム回路62、デジタル演算処理回路63、出力制御回路64、電力供給回路65、および電源入力端子66を有する。

図7の固体撮像装置2の回路は、たとえば図7のレイアウトにより図示しない半導体基板に集積化される。

【0066】

画素アレイ部61には、複数の画素回路67が二次元に配列されている。

各画素回路67は、光電変換素子を有し、列毎に設けられた出力信号線68へアナログの画素信号を出力する。

【0067】

複数のカラム回路62は、複数の出力信号線68に接続される。

カラム回路62は、たとえば出力信号線68から入力されるアナログの画素信号をセンスアンプで増幅し、カウンタを用いたCDS(Correlated Double Sampling:相関二重サンプリング)処理によりデジタル値へ変換する。

【0068】

デジタル演算処理回路63は、複数のカラム回路62に接続され、複数のデジタルの画素信号が1列毎に入力される。

デジタル演算処理回路63は、たとえば画素回路67の個数よりも画像の画素数を減らすための演算処理などを必要に応じて実行する。

【0069】

出力制御回路64は、デジタル演算処理回路63に接続される。

出力制御回路64は、デジタル演算処理回路63により処理された複数のデジタルの画素信号を所定の順番でシリアルに含む画像信号を、集積回路の外部へ出力する。

【0070】

電源入力端子66は、半導体基板の配線により、画素アレイ部61の複数の画素回路67、複数のカラム回路62、および電力供給回路65に接続される。

電源入力端子66には、図示しない外部の電圧源が接続される。

電源入力端子66には、画素回路67およびカラム回路62が必要とする、たとえば2.7Vの電圧が供給される。

【0071】

電力供給回路65は、図1の電源回路1である。

電力供給回路65は、半導体基板の配線により、デジタル演算処理回路63および出力制御回路64に接続される。

デジタル演算処理回路63および出力制御回路64は、電力供給回路65の出力電圧が供給される被給電回路である。

図1の電源回路1は、その電源電圧より低い電圧を出力する。ここでは、電力供給回路65は、たとえば2.7Vより低い1.2Vの電圧を出力する。

【0072】

そして、図7の固体撮像装置2では、電源入力端子66から所望の電圧が入力されると、起動する。

電源入力端子66から入力された外部電圧により、複数の画素回路67および複数のカラム回路62は動作を開始する。

また、電力供給回路65は、電源入力端子66から入力された外部電圧に基づいて所望の出力電圧V(OUT)を生成し、デジタル演算処理回路63および出力制御回路64へ供給する。

これにより、デジタル演算処理回路63および出力制御回路64は、動作を開始する。

複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、それぞれに供給された電源電圧の下で動作する。

【0073】

<3.第3実施形態>

[固体撮像装置2の構成および動作]

図8は、本発明の第3実施形態に係る固体撮像装置2のブロック図である。

図8の固体撮像装置2では、電源入力端子66は、半導体基板の配線により、電力供給回路65に接続される。

【0074】

電力供給回路65は、半導体基板の配線により、画素アレイ部61の複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63および出力制御回路64に接続される。

複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63および出力制御回路64は、電力供給回路65の出力電圧が供給される被給電回路である。

第3実施形態の場合、電力供給回路65は、電源入力端子66に入力される電圧に基づいて、たとえば2.7Vの出力電圧V(OUT)を生成すればよい。

【0075】

第3実施形態に係る固体撮像装置2の上述した以外の構成は、第2実施形態に係る固体撮像装置2と同様であり、同一の符号を付して説明を省略する。

そして、第3実施形態に係る固体撮像装置2では、複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、共通の電源電圧V(OUT)の下で動作する。

【0076】

<4.第4実施形態>

[固体撮像装置2の構成および動作]

図9は、本発明の第4実施形態に係る固体撮像装置2のブロック図である。

図9の固体撮像装置2は、固体撮像素子71、スイッチング素子72、電圧変換用インダクタ73、ダイオード74を有する。これらの素子は、固体撮像素子モジュールとして一体化されている。

固体撮像素子71は、第2実施形態の図7の固体撮像装置2と同様に、画素アレイ部61、複数のカラム回路62、デジタル演算処理回路63、出力制御回路64、および電源入力端子66を有する。

【0077】

スイッチング素子72、電圧変換用インダクタ73、およびダイオード74は、固体撮像素子71に接続される。

固体撮像素子71は、部分電源回路75を有する。

部分電源回路75、スイッチング素子72、電圧変換用インダクタ73、およびダイオード74は、図1の電源回路1を構成し、デジタル演算処理回路63および出力制御回路64に電源電圧を供給するための電力供給回路として機能する。

すなわち、スイッチング素子72は、図1の出力トランジスタ41に対応する。

電圧変換用インダクタ73は、図1のインダクタ素子43に対応する。

ダイオード74は、図1のダイオード42に対応する。

また、部分電源回路75は、図1のメインコンパレータ11、平滑キャパシタ44、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、およびスロースタート用キャパシタ17を有する。

なお、図9に点線で示すように、固体撮像素子71に外部接続端子76を設け、平滑キャパシタ44を外部接続端子76に接続してもよい。

【0078】

そして、第4実施形態では、スイッチング素子72、電圧変換用インダクタ73、およびダイオード74を、固体撮像素子71と別体に形成することができる。

また、第4実施形態では、外部接続端子76に、外付けの平滑キャパシタ44を接続することにより、複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、それぞれに供給された電源電圧の下で動作する。

【0079】

<5.第5実施形態>

[電源回路1の構成および動作]

図10は、本発明の第5実施形態に係る電源回路の回路図である。

図10の電源回路1は、メインコンパレータ11、出力電圧生成部12、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、スロースタート用キャパシタ17を有する。

【0080】

出力電圧生成部12は、タイミング回路81、PMOSトランジスタ82、NMOSトランジスタ83、インダクタ素子43、および平滑キャパシタ44を有する。

【0081】

PMOSトランジスタ82は、ドレインが基板の電源VDDに接続され、ソースがNMOSトランジスタ83およびインダクタ素子43の一端に接続され、ゲートがタイミング回路81に接続される。

【0082】

NMOSトランジスタ83は、ドレインがPMOSトランジスタ82のソースおよびインダクタ素子43の一端に接続され、ソースがグランドに接続され、ゲートがタイミング回路81に接続される。

したがって、PMOSトランジスタ82とNMOSトランジスタ83とは、基板の電源VDDに対して直列に接続されている。

【0083】

タイミング回路81は、メインコンパレータ11に接続される。

そして、タイミング回路81は、メインコンパレータ11からの電圧差信号S11に基づいて、PMOSトランジスタ82およびNMOSトランジスタ83をスイッチング制御する。

たとえばメインコンパレータ11から入力される電圧差信号S11がローレベルになると、タイミング回路81は、PMOSトランジスタ82およびNMOSトランジスタ83を交互にオン状態とオフ状態の間で切り替える。

このスイッチング制御により、インダクタ素子43を通じて基板の電源VDDから平滑キャパシタ44へ電流が流れ、平滑キャパシタ44が充電される。

この他にもたとえば、電圧差信号S11がハイレベルになると、タイミング回路81は、PMOSトランジスタ82およびNMOSトランジスタ83を共にオフ状態に制御する。

以上の同期整流方式の制御により、出力電圧生成部12は、出力電圧を生成する。

【0084】

<6.第6実施形態>

[撮像装置3の構成および動作]

図11は、本発明の第6実施形態に係る撮像装置3のブロック図である。

図11の撮像装置3は、上記した第2実施形態から第4実施形態のいずれかに係る固体撮像装置2と、光学系102と、信号処理回路103とを有する。また、固体撮像装置2の電源回路1は、第1実施形態のものでも、第5実施形態のものでも、後述する図12ののものでもよい。

図11の撮像装置3は、例えば、ビデオカメラ、デジタルスチルカメラ、電子内視鏡用カメラなどである。

【0085】

光学系102は、被写体からの像光(入射光)を固体撮像装置2に結像させる。

これにより、固体撮像装置2の複数の画素回路67において、入射光は入射輝度に応じたアナログの画素信号に変換される。

【0086】

信号処理回路103は、固体撮像装置2の出力信号に対して種々の信号処理を施して映像信号として出力する。

【0087】

そして、図11の撮像装置3において、固体撮像装置2は、光学系102により結像された画像についての複数の画素信号を生成し、走査周期毎に、複数の画素信号をシリアル出力する。

信号処理回路103は、固体撮像装置2からシリアル出力された複数の画素信号に対して種々の信号処理を実行する。

【0088】

以上の各実施形態は、本発明の好適な実施形態の例であるが、本発明は、これに限定されるものではなく、発明の要旨を逸脱しない範囲において種々の変形または変更が可能である。

【0089】

上記各実施形態は、ヒステリシス制御方式の電源回路1に本発明が適用された例である。

この他にも例えば、本発明は、出力電圧V(OUT)と比較される参照電圧V(REF)を用いる電源回路であれば、PWM制御方式、コンパレータ方式などのものにも適用することができる。

【0090】

図12は、PWM制御方式の電源回路1の説明図である。

図12のPWM制御方式の電源回路1は、誤差アンプ71、三角波発生回路72、パルス生成用コンパレータ73、出力電圧生成部12、電源出力端子13、および入力電圧生成部14を有する。

誤差アンプ71は、参照電圧V(REF)と入力電圧V(IN)とを比較し、参照電圧V(REF)に対する入力電圧V(IN)の電圧差を示す誤差信号を出力する。

三角波発生回路72は、電圧レベルが所定範囲で繰り返し変化するランプ信号を出力する。

パルス生成用コンパレータ73は、誤差信号とランプ信号とを比較し、たとえばランプ信号が誤差信号のレベルを超える期間においてハイレベルとなるパルス信号を生成し、出力電圧生成部12へ出力する。

この図12のPWM制御方式の電源回路1では、参照電圧V(REF)を生成する回路として、図1の電流出力部15、抵抗素子16、スロースタート用キャパシタ17などを採用することができる。

【0091】

上記各実施形態の電源回路1は、電源回路1の電源電圧より低い出力電圧V(OUT)を生成する降圧型のものである。

この他にも例えば、本発明は、電源回路1の電源電圧より高い出力電圧V(OUT)を生成する昇圧型のものであってもよい。

【0092】

上記各実施形態では、スロースタート用キャパシタ17は、電源回路1または固体撮像装置2としての集積回路に設けられている。

この他にも例えば、集積回路に接続端子を設け、この接続端子にスロースタート用キャパシタ17を外付けとしてもよい。

【0093】

上記第6実施形態は、撮像装置3の固体撮像装置2に本発明が適用された例である。

この他にも例えば、本発明は、撮像装置3の信号処理回路103に適用されてもよい。

また、本発明は、撮像装置3以外にも、たとえば携帯電話機、コンピュータ装置、PDA(Personal Data Assistance)、電子ノートなどの電子機器に適用することができる。

【符号の説明】

【0094】

1…電源回路、2…固体撮像装置、3…撮像装置(電子機器)、11…メインコンパレータ(比較部)、12…出力電圧生成部、14…入力電圧生成部、15…電流出力部、16…抵抗素子、17…スロースタート用キャパシタ(キャパシタ)、22…切替用コンパレータ、23…抵抗接続トランジスタ(第4スイッチング素子)、24…容量接続トランジスタ(第3スイッチング素子)、26…電源用論理回路(第1論理回路)、27…電源用インバータ(第2論理回路)、41…出力トランジスタ(出力スイッチング素子)、42…ダイオード、43…インダクタ素子、44…平滑キャパシタ、51…メイン電流源トランジスタ(第1電流源)、52…サブ電流源トランジスタ(第2電流源)、53…メインスイッチトランジスタ(第2スイッチング素子)、54…サブスイッチトランジスタ(第1スイッチング素子)、62…カラム回路(被給電回路)、63…デジタル演算処理回路(デジタル処理部、被給電回路)、64…出力制御部(被給電回路)、65…電力供給回路(電源回路)、66…電源入力端子、67…画素回路(被給電回路)、76…外部接続端子、81…タイミング回路、82…PMOSトランジスタ、83…NMOSトランジスタ、N1…ノード、V(REF)…参照電圧、V(IN)…入力電圧、V(OUT)…出力電圧、Vs…判定電圧、S11…電圧差信号、S22…判定信号。

【技術分野】

【0001】

本発明は、安定した電圧を出力する電源回路、集積回路装置、固体撮像装置および電子機器に関する。

【背景技術】

【0002】

電源回路は、所望の出力電圧を出力するために、出力電圧を参照電圧と比較し、出力電圧が参照電圧に対応した電圧となるように出力トランジスタなどの出力スイッチング素子をオンオフ制御する。

このような電源回路では、出力スイッチング素子をデジタル的にオンオフ制御するPWM(Pulse Width Modulation)制御方式、オンオフ制御するコンパレータ方式などが広く知られている。また、電源回路には、入力電圧より高い電圧を出力する昇圧型のものと、入力電圧より低い電圧を出力する降圧型のものとがある。

PWM制御方式では、たとえば出力電圧が参照電圧を下回る期間において、これらの電位差に応じたパルス幅の制御信号により出力スイッチング素子をオンオフ制御する。

コンパレータ方式では、たとえば出力電圧が参照電圧を下回った場合、出力電圧が参照電圧を上回るまで、出力スイッチング素子をオン状態に制御する。

また、コンパレータ方式には、たとえばヒステリシスコンパレータを用いて、出力電圧が下回る際に使用する参照電圧より、出力電圧が上回る際に使用する参照電圧が高くなるように、参照電圧を制御するヒステリシス制御方式のものがある(特許文献1)。

【0003】

ところで、これらの各方式の電源回路では、出力電圧と比較される参照電圧を起動時に徐々に立ち上げるソフトスタート回路を設けることがある。

ソフトスタート回路を設けることにより、起動直後の電源回路において、参照電圧と出力電圧との間に大きな電位差が生じないようにすることができる。

また、ソフトスタート回路には、キャパシタなどを用いた時定数回路が用いられる(特許文献1)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−060978号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、このように電源回路にキャパシタを用いたソフトスタート回路を追加した場合、必要とするソフトスタート期間に応じて大容量のキャパシタが必要になる。

キャパシタの容量は面積に比例するため、電源回路の回路規模が大きくなり、たとえば集積回路における電源回路の占有面積が大きくなってしまう。

【0006】

このように電源回路では、ソフトスタート回路による電源回路の回路規模の大型化を抑制することが求められている。

【課題を解決するための手段】

【0007】

本発明の第1の観点の電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の前記参照電流より小さくする。

【0008】

本発明の第2の観点の集積回路装置は、出力電圧を出力する電源回路と、出力電圧が給電される被給電回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0009】

本発明の第3の観点の固体撮像装置は、複数の画素回路が二次元に配列され、各画素回路のアナログの画素信号を出力する画素アレイ部と、アナログの画素信号をデジタルに変換するカラム回路と、デジタルの画素信号をデジタル処理するデジタル処理部と、デジタル処理されたデジタルの画素信号を出力する出力制御部と、画素アレイ部、カラム回路、デジタル処理部および出力制御部のうちの少なくとも1個に出力電圧を出力する電源回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0010】

本発明の第4の観点の電子機器は、出力電圧を出力する電源回路と、出力電圧が給電される被給電回路とを有する。電源回路は、参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、出力電圧から入力電圧を生成する入力電圧生成部と、参照電流を出力する電流出力部と、参照電流により参照電圧を生成する抵抗素子と、抵抗素子と並列に接続され、参照電流により充電されるキャパシタとを有する。そして、電流出力部は、起動する際の参照電流を、動作中の参照電流より小さくする。

【0011】

本発明では、起動する際、キャパシタは、動作中の参照電流より小さい電流により充電される。

よって、本発明では、キャパシタの容量を小さくしつつ、長いソフトスタート期間が得られる。

【発明の効果】

【0012】

本発明では、ソフトスタート回路による電源回路の回路規模の大型化を抑制することができる。

【図面の簡単な説明】

【0013】

【図1】図1は、本発明の第1実施形態に係る電源回路の回路図である。

【図2】図2は、図1の電源回路のヒステリシス機能に関係する部分の回路図である。

【図3】図3は、図1の電源回路のヒステリシス動作のタイミングチャートである。

【図4】図4は、スロースタート動作の説明図である。

【図5】図5は、図1の電源回路での起動時の各種スイッチ動作トランジスタの動作説明図である。

【図6】図6は、図1の電源回路の起動動作のタイミングチャートである。

【図7】図7は、本発明の第2実施形態に係る固体撮像装置のブロック図である。

【図8】図8は、本発明の第3実施形態に係る固体撮像装置のブロック図である。

【図9】図9は、本発明の第4実施形態に係る固体撮像装置のブロック図である。

【図10】図10は、本発明の第5実施形態に係る電源回路の回路図である。

【図11】図11は、本発明の第6実施形態に係る撮像装置のブロック図である。

【図12】図12は、PWM制御方式の電源回路の説明図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を図面に関連付けて説明する。

説明は以下の順に行う。

1.第1実施形態(電源回路1の一例)

2.第2実施形態(固体撮像装置2の第1の例)

3.第3実施形態(固体撮像装置2の第2の例)

4.第4実施形態(固体撮像装置2の第3の例)

5.第5実施形態(電源回路1の他の例)

6.第6実施形態(撮像装置3の一例)

【0015】

<1.第1実施形態>

[電源回路1の構成]

図1は、本発明の第1実施形態に係る電源回路1の回路図である。

図1の電源回路1は、メインコンパレータ11、出力電圧生成部12、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、スロースタート用キャパシタ17を有する。

そして、図1の電源回路1は、メインコンパレータ11においてノードN1の参照電圧V(REF)と、出力電圧V(OUT)に基づく入力電圧V(IN)とを比較し、入力電圧V(IN)が参照電圧V(REF)となるように出力電圧V(OUT)を制御する。

電源回路1は、電源出力端子13から出力電圧V(OUT)を出力する。

【0016】

また、図1の電源回路1は、判定電圧生成部21、切替用コンパレータ22、抵抗接続トランジスタ23、容量接続トランジスタ24、容量用インバータ25、電源用論理回路26、電源用インバータ27を有する。

そして、図1の電源回路1は、これらの制御系の回路により、メインコンパレータ11にヒステリシス特性を持たせ、起動時に参照電圧V(REF)を徐々に上げるスロースタート機能を実現する。

ヒステリシス制御方式の電源回路1は、PWM制御方式のものと比べた場合、出力電圧のリップル成分が大きくなるが、応答速度が良い、発振しにくい、構成が簡素であるなどのメリットがある。

【0017】

なお、図1の電源回路1は、その全体が図示しない半導体基板上に集積化され、半導体基板上の集積回路の一部として実現されている。

【0018】

入力電圧生成部14は、第1分圧抵抗素子31と、第2分圧抵抗素子32とを有する。

第1分圧抵抗素子31および第2分圧抵抗素子32は、たとえば集積回路の配線層または拡散層により形成される。

第1分圧抵抗素子31は、一端が電源出力端子13に接続され、他端が第2分圧抵抗素子32の一端に接続される。第2分圧抵抗素子32の他端は、基板のグランドに接続される。

そして、入力電圧生成部14は、出力電圧V(OUT)を第1分圧抵抗素子31および第2分圧抵抗素子32で分圧し、入力電圧V(IN)を生成する。

【0019】

メインコンパレータ11は、反転入力ノード(−)、非反転入力ノード(+)、および出力ノードを有する。

メインコンパレータ11は、半導体基板に形成されたたとえば差動アンプにより形成することができる。

反転入力ノード(−)は、ノードN1に接続され、参照電圧V(REF)が入力される。

非反転入力ノード(+)は、参照電圧V(REF)生成部に接続され、入力電圧V(IN)が入力される。

そして、メインコンパレータ11は、入力電圧V(IN)を参照電圧V(REF)と比較し、参照電圧V(REF)と前記入力電圧V(IN)との電圧差に応じた電圧差信号S11を出力ノードから出力する。

たとえば入力電圧V(IN)が参照電圧V(REF)より低い場合、メインコンパレータ11は、ローレベルの電圧差信号S11を出力する。

また、入力電圧V(IN)が参照電圧V(REF)より高い場合、メインコンパレータ11は、ハイレベルの電圧差信号S11を出力する。

【0020】

出力電圧生成部12は、出力トランジスタ41、ダイオード42、インダクタ素子43、および平滑キャパシタ44を有する。

【0021】

出力トランジスタ41は、たとえば半導体基板に形成されたPMOSトランジスタである。

出力トランジスタ41は、ドレインが基板の電源VDDに接続され、ソースがダイオード42のカソードおよびインダクタ素子43の一端に接続され、ゲートがメインコンパレータ11の出力ノードに接続される。

【0022】

ダイオード42は、たとえば半導体基板のPN接合により形成され、アノードからカソードへ電流を流す特性を有する。

ダイオード42のアノードは、基板のグランドに接続される。

【0023】

インダクタ素子43は、たとえば集積回路の配線層や層間ビア、パッケージのワイヤボンディング、外付けインダクタ素子により形成される。

インダクタ素子43の他端は、電源出力端子13および平滑キャパシタ44の一端に接続される。

【0024】

平滑キャパシタ44は、たとえば集積回路の二層の配線層により形成される。

平滑キャパシタ44は、一端が電源出力端子13に接続され、他端が基板のグランドに接続される。

【0025】

そして、出力トランジスタ41は、メインコンパレータ11からローレベルの電圧差信号S11が入力されると、オン状態となる。

この場合、出力トランジスタ41およびインダクタ素子43を通じて、基板の電源VDDから平滑キャパシタ44へ電流が流れ、平滑キャパシタ44が充電される。

平滑キャパシタ44の充電電圧は、インダクタ素子43と平滑キャパシタ44とによる共振回路の特性に基づいてリップル成分を持ちながら上昇する。

この平滑キャパシタ44の充電電圧が、電源出力端子13から出力される。

【0026】

また、電圧差信号S11がハイレベルになると、出力トランジスタ41は、オフ状態となる。

仮にたとえば電源出力端子13に被給電回路が接続されているとした場合、被給電回路は、平滑キャパシタ44に蓄積された電荷を電流として使用する。

これにより、平滑キャパシタ44の充電電圧は、すなわち出力電圧V(OUT)は低下する。

【0027】

電流出力部15は、メイン電流源トランジスタ51、サブ電流源トランジスタ52、メインスイッチトランジスタ53、およびサブスイッチトランジスタ54を有する。

【0028】

メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、たとえば半導体基板に形成されたPMOSトランジスタである。

メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、ドレインが基板の電源VDDに接続され、ゲートが図示しないバイアス回路に接続される。

これにより、メイン電流源トランジスタ51およびサブ電流源トランジスタ52は、バイアス電圧と電源電圧VDDとの電位差に応じた電流を供給する。

【0029】

ただし、メイン電流源トランジスタ51は、サブ電流源トランジスタ52より大きい電流をノードN1へ供給する。

たとえばメイン電流源トランジスタ51は、75マイクロアンペアを供給し、サブ電流源トランジスタ52は、1.6マイクロアンペアを供給する。

以下、メイン電流源トランジスタ51が供給する電流を第1電流I1とよび、サブ電流源トランジスタ52が供給する電流を第2電流I2とよぶ。

【0030】

メインスイッチトランジスタ53は、たとえば半導体基板に形成されたPMOSトランジスタである。

メインスイッチトランジスタ53は、ドレインがメイン電流源トランジスタ51のソースに接続され、ソースがノードN1に接続され、ゲートが電源用インバータ27の出力ノードに接続される。

そして、メインスイッチトランジスタ53は、ローレベルが入力されるとオン状態となり、ハイレベルが入力されるとオフ状態となる。

メインスイッチトランジスタ53は、オン状態である場合に、ノードN1に第1電流I1を供給する。

【0031】

サブスイッチトランジスタ54は、たとえば半導体基板に形成されたPMOSトランジスタである。

サブスイッチトランジスタ54は、ドレインがサブ電流源トランジスタ52のソースに接続され、ソースがノードN1に接続され、ゲートが電源用論理回路26の出力ノードに接続される。

そして、サブスイッチトランジスタ54は、ローレベルが入力されるとオン状態となり、ハイレベルが入力されるとオフ状態となる。

サブスイッチトランジスタ54は、オン状態である場合に、ノードN1に第2電流I2を供給する。

【0032】

以下、このメインスイッチトランジスタ53およびサブスイッチトランジスタ54を通じて電流出力部15がノードN1へ供給する電流を参照電流I(REF)とよぶ。

参照電流I(REF)の電流値は、メインスイッチトランジスタ53およびサブスイッチトランジスタ54のオンオフ状態に応じて変化する。

【0033】

抵抗素子16は、たとえば集積回路の配線層または拡散層に形成される。

抵抗接続トランジスタ23は、たとえば半導体基板に形成されたNMOSトランジスタである。

抵抗接続トランジスタ23は、ソースがノードN1に接続され、ドレインが抵抗素子16の一端に接続され、ゲートが切替用コンパレータ22の出力ノードに接続される。

抵抗素子16の他端は、基板のグランドに接続される。

これにより、抵抗素子16は、抵抗接続トランジスタ23がオン状態である場合、ノードN1に接続される。そして、抵抗素子16には、電流出力部15が出力した参照電流I(REF)が流れ、参照電圧V(REF)を発生する。

【0034】

スロースタート用キャパシタ17は、たとえば集積回路の二層の配線層により形成される。

容量接続トランジスタ24は、たとえば半導体基板に形成されたNMOSトランジスタである。

【0035】

容量接続トランジスタ24は、ソースがノードN1に接続され、ドレインがスロースタート用キャパシタ17の一端に接続され、ゲートが容量用インバータ25の出力ノードに接続される。

容量接続トランジスタ24は、基板のグランドに接続される。

これにより、容量接続トランジスタ24は、容量接続トランジスタ24がオン状態である場合、ノードN1に接続される。そして、容量接続トランジスタ24は、抵抗素子16と並列に接続される。

また、容量接続トランジスタ24は、電流出力部15が出力した参照電流I(REF)により充電される。

容量接続トランジスタ24は、参照電流I(REF)の電流値および容量接続トランジスタ24の容量に応じた充電速度で充電される。

【0036】

判定電圧生成部21は、たとえば一定の電圧を発生する電圧回路である。

判定電圧生成部21は、判定電圧Vsを生成する。

判定電圧Vsは、起動後の動作状態における参照電圧V(REF)より低い電圧であればよい。

【0037】

切替用コンパレータ22は、反転入力ノード(−)、非反転入力ノード(+)、および出力ノードを有する。

切替用コンパレータ22は、半導体基板に形成されたたとえば差動アンプにより形成することができる。

非反転入力ノード(+)は、ノードN1に接続され、参照電圧V(REF)が入力される。

反転入力ノード(−)は、判定電圧生成部21に接続され、判定電圧Vsが入力される。

そして、切替用コンパレータ22は、参照電圧V(REF)を判定電圧Vsと比較し、参照電圧V(REF)と判定電圧Vsとの電圧差に応じた判定信号S22を出力ノードから出力する。

たとえば参照電圧V(REF)が判定電圧Vsより低い場合、切替用コンパレータ22は、ローレベルの判定信号S22を出力する。

また、参照電圧V(REF)が判定電圧Vsより高い場合、切替用コンパレータ22は、ハイレベルの判定信号S22を出力する。

【0038】

容量用インバータ25および電源用インバータ27の入力ノードには、切替用コンパレータ22の出力ノードが接続される。

そして、容量用インバータ25は、判定信号S22を反転して、容量接続トランジスタ24へ出力する。

また、電源用インバータ27は、判定信号S22を反転して、メインスイッチトランジスタ53へ出力する。

【0039】

電源用論理回路26は、たとえば二入力の論理積回路である。

電源用論理回路26は、一方の入力ノードにメインコンパレータ11の出力ノードが接続され、他方の入力ノードに切替用コンパレータ22の出力ノードが接続される。

そして、電源用論理回路26は、電圧差信号S11および判定信号S22が共にハイレベルである場合、ハイレベルの論理積信号をサブスイッチトランジスタ54へ出力する。

それ以外の場合は、ローレベルの論理積信号を出力する。

【0040】

[ヒステリシス動作]

図2は、図1の電源回路1のヒステリシス機能に関する部分の回路図である。

電源回路1が起動され、出力電圧V(OUT)が略参照電圧V(REF)に対応した電圧となっている状態では、抵抗接続トランジスタ23および電源用インバータ27がオン状態に維持され、容量接続トランジスタ24がオフ状態に維持される。

また、容量用インバータ25がハイレベルの判定信号S22を出力するので、メインコンパレータ11の電圧差信号S11の信号レベルがそのままサブスイッチトランジスタ54に入力される状態になる。

【0041】

図3は、図1の電源回路1のヒステリシス動作のタイミングチャートである。

図3(A)は、メインコンパレータ11に入力される参照電圧V(REF)および入力電圧V(IN)の波形である。図3(B)は、メインコンパレータ11が出力する電圧信号の波形である。

【0042】

そして、図3のタイミングT1では、入力電圧V(IN)が参照電圧V(REF)より高い。

この場合、メインコンパレータ11は、ハイレベルの電圧差信号S11を出力する。

電圧差信号S11がハイレベルである場合、サブスイッチトランジスタ54は、オフ状態である。よって、抵抗素子16には、第1電流I1および第2電流I2のうちの第1電流I1のみが流れる。参照電圧V(REF)は、第1電流I1のみによる電圧となる。

また、電圧差信号S11がハイレベルである場合、出力トランジスタ41はオフ状態となる。よって、平滑キャパシタ44は、充電されず、既に充電された電圧を出力する。

【0043】

タイミングT2では、入力電圧V(IN)が参照電圧V(REF)より低くなる。

この場合、メインコンパレータ11は、電圧差信号S11をハイレベルからローレベルへ切り替える。

電圧差信号S11がローレベルになると、サブスイッチトランジスタ54は、オン状態となる。よって、抵抗素子16には、第1電流I1および第2電流I2が流れる。参照電圧V(REF)は、第1電流I1のみによる電圧より、高い電圧となる。

また、電圧差信号S11がローレベルになると、出力トランジスタ41はオン状態となる。よって、平滑キャパシタ44は、充電される。

その結果、タイミングT3に示すように、平滑キャパシタ44の充電に追従して、入力電圧V(IN)も上昇する。

【0044】

タイミングT4では、入力電圧V(IN)が、高い電圧状態にある参照電圧V(REF)より高くなる。

この場合、メインコンパレータ11は、電圧差信号S11をローレベルからハイレベルへ切り替える。

電圧差信号S11がハイレベルになると、サブスイッチトランジスタ54は、オフ状態となる。よって、抵抗素子16には、第1電流I1のみが流れる。参照電圧V(REF)は、再び第1電流I1のみによる低い電圧となる。

また、電圧差信号S11がハイレベルになると、出力トランジスタ41はオフ状態となる。よって、平滑キャパシタ44は、充電されない。

【0045】

以上の動作により、図1の電源回路1は、入力電圧V(IN)が高いレベルから低いレベルへ変化する場合と、入力電圧V(IN)が低いレベルから高いレベルへ変化する場合とで、異なる電圧レベルの参照電圧V(REF)と比較する。

また、電源回路1は、この比較結果に応じて、出力トランジスタ41のオンオフを制御する。

よって、メインコンパレータ11は、ヒステリシス特性を有する。

【0046】

[スロースタート動作]

図4は、スロースタート動作の説明図である。

図4の説明図では、メインコンパレータ11の非反転入力ノード(+)にスロースタート回路が接続されている。

このスロースタート回路は、電流源と、スロースタート用キャパシタ17とを有する。電流源は、図1の電流出力部15に対応する。

【0047】

そして、図4の電源回路1では、起動されると、電流源は、電流を出力し、スロースタート用キャパシタ17を充電する。

スロースタート用キャパシタ17の充電電圧は、電流源から供給される電流にしたがって徐々に上昇する。

メインコンパレータ11は、この起動後に徐々に上昇する参照電圧V(REF)と入力電圧V(IN)とを比較する。

入力電圧V(IN)が参照電圧V(REF)より低い場合、メインコンパレータ11は、ローレベルの電圧差信号S11を出力し、出力トランジスタ41をオン状態に制御する。出力トランジスタ41がオン状態になると、平滑キャパシタ44は充電される。

また、入力電圧V(IN)が参照電圧V(REF)より高くなると、メインコンパレータ11は、出力トランジスタ41をオフ状態に制御する。平滑キャパシタ44の充電は停止する。

このようにメインコンパレータ11は、起動後に徐々に上昇する参照電圧V(REF)に応じて平滑キャパシタ44の充電と停止とを繰り返す。

その結果、出力トランジスタ41を通じて平滑キャパシタ44に流れる電流も小さくなる。

【0048】

これに対して、仮にたとえば図4のスロースタート用キャパシタ17の換わりに抵抗素子16が接続されていた場合、参照電圧V(REF)は電源回路1の起動直後に所定の電圧となる。

この場合、メインコンパレータ11は、入力電圧V(IN)が参照電圧V(REF)より高くなるまで、出力トランジスタ41をオン状態に維持する。

また、平滑キャパシタ44は、大きな電流(突入電流)により一気に充電される。

【0049】

図5は、図1の電源回路1での起動時の各種スイッチ動作トランジスタの動作説明図である。

図5には、ノードN1に接続されたサブスイッチトランジスタ54、メインスイッチトランジスタ53、抵抗接続トランジスタ23、および容量接続トランジスタ24が示されている。

【0050】

そして、図5の表の上段に示すように、参照電圧V(REF)が判定電圧Vsより低い場合、サブスイッチトランジスタ54および容量接続トランジスタ24はオン状態となり、メインスイッチトランジスタ53および抵抗接続トランジスタ23はオフ状態となる。

よって、ノードN1には、サブ電流源トランジスタ52とスロースタート用キャパシタ17とが接続される。

電源回路1において図4の回路が実現され、スロースタート用キャパシタ17は、第2電流I2により充電される。

【0051】

また、図5の表の下段に示すように、参照電圧V(REF)が判定電圧Vsより高い場合、メインスイッチトランジスタ53および抵抗接続トランジスタ23はオン状態となり、サブスイッチトランジスタ54および容量接続トランジスタ24はオフ状態となる。

よって、ノードN1には、メインスイッチトランジスタ53および抵抗接続トランジスタ23とが接続される。

電源回路1において図2の回路が実現され、抵抗素子16は、第1電流I1により所望の参照電圧V(REF)を発生する。

【0052】

図6は、図1の電源回路1の起動動作のタイミングチャートである。

図6(A)は、ノードN1の参照電圧V(REF)の波形である。図6(B)は、切替用コンパレータ22が出力する判定信号S22の波形である。図6(C)は、サブスイッチトランジスタ54のゲート信号の波形である。図6(D)は、メインスイッチトランジスタ53のゲート信号の波形である。図6(E)は、抵抗接続トランジスタ23のゲート信号の波形である。図6(F)は、容量接続トランジスタ24のゲート信号の波形である。

【0053】

タイミングT11において電源回路1が起動されると、判定電圧生成部21は、判定電圧Vsを出力する。

停止状態および起動直後の電源回路1において、参照電圧V(REF)および出力電圧V(OUT)は共に0V(グランドレベル)である。よって、起動直後の参照電圧V(REF)は、判定電圧Vsより低い。

このため、図6(B)に示すように、切替用コンパレータ22は、ローレベルの判定信号S22を出力する。

また、サブスイッチトランジスタ54は、図6(C)に示すようにハイレベルの信号が入力され、オン状態となり、メインスイッチトランジスタ53は、図6(D)に示すようにハイレベルの信号が入力され、オフ状態となる。

よって、サブ電流源トランジスタ52のみがノードN1に接続され、電流出力部15は、第2電流I2のみをノードN1に供給する。

また、抵抗接続トランジスタ23は、図6(E)に示すようにオフ状態となり、容量接続トランジスタ24は、図6(F)に示すようにオン状態となる。

よって、起動直後は、容量接続トランジスタ24のみがノードN1に接続され、容量接続トランジスタ24は、第2電流I2で充電される。

その結果、容量接続トランジスタ24の充電電圧、すなわち参照電圧V(REF)は、図6(A)に示すように、第1電流I1より小さい第2電流I2で充電されることにより、時間をかけて徐々に上昇する。

【0054】

そして、タイミングT12において参照電圧V(REF)が判定電圧Vsを超えると、切替用コンパレータ22は、図6(B)に示すように判定信号S22をローレベルからハイレベルへ切り替える。

また、サブスイッチトランジスタ54は、図6(C)に示すようにローレベルの信号が入力され、オフ状態となり、メインスイッチトランジスタ53は、図6(D)に示すようにローレベルの信号が入力され、オン状態となる。

よって、メイン電流源トランジスタ51のみがノードN1に接続され、電流出力部15は、第1電流I1のみをノードN1に供給する。

また、抵抗接続トランジスタ23は、図6(E)に示すようにオン状態となり、容量接続トランジスタ24は、図6(F)に示すようにオフ状態となる。

よって、参照電圧V(REF)が判定電圧Vsを超えると、抵抗素子16のみがノードN1に接続され、抵抗素子16は、第1電流I1による参照電圧V(REF)を発生する。

【0055】

以上の動作により、電源回路1は起動され、メインコンパレータ11は、入力電圧V(IN)と参照電圧V(REF)とを比較し、これに応じて出力トランジスタ41をオンオフ制御する。

出力電圧V(OUT)は、入力電圧V(IN)が参照電圧V(REF)と略等しくなるように制御される。

【0056】

その後、出力電圧V(OUT)が下がり、たとえばタイミングT13において入力電圧V(IN)が参照電圧V(REF)を下回ると、メインコンパレータ11は、電圧差信号S11をハイレベルからローレベルに切り替える。

起動後の通常動作状態では、参照電圧V(REF)は判定電圧Vsより高いので、切替用コンパレータ22は、常にハイレベルの判定信号S22を出力している。

よって、電源用論理回路26は、電圧差信号S11のレベルをそのままサブスイッチトランジスタ54へ出力する。

また、サブスイッチトランジスタ54は、電圧差信号S11がハイレベルからローレベルに切り替わると、図6(C)に示すようにオン状態となる。

これにより、抵抗素子16には第1電流I1および第2電流I2が流れ、参照電圧V(REF)が少し上昇する。

【0057】

また、電圧差信号S11がハイレベルからローレベルに切り替わることにより、出力トランジスタ41がオン状態となり、平滑キャパシタ44が充電され、入力電圧生成部14が出力電圧V(OUT)に基づいて生成する入力電圧V(IN)が上昇する。

そして、入力電圧V(IN)が少し高くなった参照電圧V(REF)を超えると、メインコンパレータ11は、電圧差信号S11をローレベルからハイレベルに切り替える。

これにより、サブスイッチトランジスタ54は、オフ状態となり、参照電圧V(REF)は、第1電流I1のみによる元の電圧に戻る。

【0058】

通常動作状態では、電源回路1は以上の動作により、出力電圧V(OUT)を所望の電圧に維持する。

これにより、電源回路1は、所定の電圧レベルに安定した主力電圧を生成し、電源出力端子13から出力することができる。

【0059】

以上のように、第1実施形態の電源回路では、起動する際、スロースタート用キャパシタ17は、動作中の参照電流I(REF)より小さい電流(第2電流I2)により充電される。

よって、スロースタート用キャパシタ17の容量を小さくしても、長いソフトスタート期間が得られる。

【0060】

ここで、スロースタート機能を実現するために、本実施形態のように電流を絞った場合と、電流を絞らなかった場合における電源回路1の追加面積について説明する。

ここでは、たとえばスロースタート用キャパシタ17の電圧を、0ボルトから1.2ボルトまで上昇させるときのスロースタート時間として100マイクロ秒を実現する場合について説明する。

電流を絞らない場合、スロースタート用キャパシタ17の容量C1は、以下の式1の値となる。

これに対して、本実施形態のように電流を絞った場合、スロースタート用キャパシタ17の容量C2は、以下の式2の値となる。

下記の式1および式2から明らかなように、電流を絞ることにより、スロースタート用キャパシタ17の容量を約47分の1にすることができる。

【0061】

C1=I(REF)×T÷Vdif=75μA×100μs÷1.2V=6.25nF ・・・式1

C21=1.6μA×100μs÷1.2V=133pF ・・・式2

【0062】

また、電流を絞らない場合の6.25nFのスロースタート用キャパシタ17の面積は、あるプロセスにおいて約3.1329(=1.77mm×1.77mm)平方mmとなる。

これに対して、本実施形態のように電流を絞った場合の面積は、本実施形態での追加回路を考慮したとしても、約0.0708平方mmとなる。

ここでは、133pFのスロースタート用キャパシタ17の面積を約0.0676(=0.26mm×0.26mm)平方mmと計算し、追加回路の面積を約0.0032(=0.08mm×0.04mm)平方mmとして計算している。

このように本実施形態での追加面積は、追加回路を考慮したとしても、電流を絞らない場合の約1/44になる。

【0063】

また、第1実施形態では、入力電圧V(IN)が参照電圧V(REF)より低い場合、サブスイッチトランジスタ54はオン状態となり、第2電流I2が第1電流I1とともに抵抗素子16へ供給される。この場合、参照電圧V(REF)は高くなる。

逆に、入力電圧V(IN)が参照電圧V(REF)より高い場合、サブスイッチトランジスタ54はオフ状態となり、第1電流I1のみが抵抗素子16へ供給される。この場合、参照電圧V(REF)は低くなる。

このように第1実施形態では、入力電圧V(IN)に応じて参照電圧V(REF)が大小するので、メインコンパレータ11は、ヒステリシス特性を持つ。

そして、第1実施形態では、起動する際には、第2電流I2のみをスロースタート用キャパシタ17へ供給して参照電圧V(REF])を発生するので、起動する際の参照電流I(REF)は、動作中より小さくなる。

このように電流出力部15は、メインコンパレータ11にヒステリシス特性を持たせるための電流源としての機能と、スロースタート用の電流源としての機能とを兼用する。

よって、第1実施形態では、これら複数の回路を別々に設けた場合より電源回路1の回路構成を単純化し、回路規模を抑えることができる。

また、第1実施形態では、スロースタート時の電流を第2電流I2のみにしぼったので、スロースタート用キャパシタ17の容量を小さくしても、長いスロースタート期間を確保することができる。

【0064】

また、第1実施形態では、スロースタート用キャパシタ17は、起動した後の動作中にノードN1から切り離される。

よって、動作中の第1電流I1および第2電流I2は、すべて抵抗素子16に流れる。

その結果、動作中の参照電圧V(REF)は、電源回路1の出力電圧V(OUT)の増減に応じて早い応答速度により変化することができる。

すなわち、第1実施形態では、スロースタート用キャパシタ17がヒステリシス特性を有するメインコンパレータ11の応答特性を悪化させないようにすることができる。

【0065】

<2.第2実施形態>

[固体撮像装置2の構成および動作]

図7は、本発明の第2実施形態に係る固体撮像装置2のブロック図である。

図7の固体撮像装置2は、画素アレイ部61、複数のカラム回路62、デジタル演算処理回路63、出力制御回路64、電力供給回路65、および電源入力端子66を有する。

図7の固体撮像装置2の回路は、たとえば図7のレイアウトにより図示しない半導体基板に集積化される。

【0066】

画素アレイ部61には、複数の画素回路67が二次元に配列されている。

各画素回路67は、光電変換素子を有し、列毎に設けられた出力信号線68へアナログの画素信号を出力する。

【0067】

複数のカラム回路62は、複数の出力信号線68に接続される。

カラム回路62は、たとえば出力信号線68から入力されるアナログの画素信号をセンスアンプで増幅し、カウンタを用いたCDS(Correlated Double Sampling:相関二重サンプリング)処理によりデジタル値へ変換する。

【0068】

デジタル演算処理回路63は、複数のカラム回路62に接続され、複数のデジタルの画素信号が1列毎に入力される。

デジタル演算処理回路63は、たとえば画素回路67の個数よりも画像の画素数を減らすための演算処理などを必要に応じて実行する。

【0069】

出力制御回路64は、デジタル演算処理回路63に接続される。

出力制御回路64は、デジタル演算処理回路63により処理された複数のデジタルの画素信号を所定の順番でシリアルに含む画像信号を、集積回路の外部へ出力する。

【0070】

電源入力端子66は、半導体基板の配線により、画素アレイ部61の複数の画素回路67、複数のカラム回路62、および電力供給回路65に接続される。

電源入力端子66には、図示しない外部の電圧源が接続される。

電源入力端子66には、画素回路67およびカラム回路62が必要とする、たとえば2.7Vの電圧が供給される。

【0071】

電力供給回路65は、図1の電源回路1である。

電力供給回路65は、半導体基板の配線により、デジタル演算処理回路63および出力制御回路64に接続される。

デジタル演算処理回路63および出力制御回路64は、電力供給回路65の出力電圧が供給される被給電回路である。

図1の電源回路1は、その電源電圧より低い電圧を出力する。ここでは、電力供給回路65は、たとえば2.7Vより低い1.2Vの電圧を出力する。

【0072】

そして、図7の固体撮像装置2では、電源入力端子66から所望の電圧が入力されると、起動する。

電源入力端子66から入力された外部電圧により、複数の画素回路67および複数のカラム回路62は動作を開始する。

また、電力供給回路65は、電源入力端子66から入力された外部電圧に基づいて所望の出力電圧V(OUT)を生成し、デジタル演算処理回路63および出力制御回路64へ供給する。

これにより、デジタル演算処理回路63および出力制御回路64は、動作を開始する。

複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、それぞれに供給された電源電圧の下で動作する。

【0073】

<3.第3実施形態>

[固体撮像装置2の構成および動作]

図8は、本発明の第3実施形態に係る固体撮像装置2のブロック図である。

図8の固体撮像装置2では、電源入力端子66は、半導体基板の配線により、電力供給回路65に接続される。

【0074】

電力供給回路65は、半導体基板の配線により、画素アレイ部61の複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63および出力制御回路64に接続される。

複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63および出力制御回路64は、電力供給回路65の出力電圧が供給される被給電回路である。

第3実施形態の場合、電力供給回路65は、電源入力端子66に入力される電圧に基づいて、たとえば2.7Vの出力電圧V(OUT)を生成すればよい。

【0075】

第3実施形態に係る固体撮像装置2の上述した以外の構成は、第2実施形態に係る固体撮像装置2と同様であり、同一の符号を付して説明を省略する。

そして、第3実施形態に係る固体撮像装置2では、複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、共通の電源電圧V(OUT)の下で動作する。

【0076】

<4.第4実施形態>

[固体撮像装置2の構成および動作]

図9は、本発明の第4実施形態に係る固体撮像装置2のブロック図である。

図9の固体撮像装置2は、固体撮像素子71、スイッチング素子72、電圧変換用インダクタ73、ダイオード74を有する。これらの素子は、固体撮像素子モジュールとして一体化されている。

固体撮像素子71は、第2実施形態の図7の固体撮像装置2と同様に、画素アレイ部61、複数のカラム回路62、デジタル演算処理回路63、出力制御回路64、および電源入力端子66を有する。

【0077】

スイッチング素子72、電圧変換用インダクタ73、およびダイオード74は、固体撮像素子71に接続される。

固体撮像素子71は、部分電源回路75を有する。

部分電源回路75、スイッチング素子72、電圧変換用インダクタ73、およびダイオード74は、図1の電源回路1を構成し、デジタル演算処理回路63および出力制御回路64に電源電圧を供給するための電力供給回路として機能する。

すなわち、スイッチング素子72は、図1の出力トランジスタ41に対応する。

電圧変換用インダクタ73は、図1のインダクタ素子43に対応する。

ダイオード74は、図1のダイオード42に対応する。

また、部分電源回路75は、図1のメインコンパレータ11、平滑キャパシタ44、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、およびスロースタート用キャパシタ17を有する。

なお、図9に点線で示すように、固体撮像素子71に外部接続端子76を設け、平滑キャパシタ44を外部接続端子76に接続してもよい。

【0078】

そして、第4実施形態では、スイッチング素子72、電圧変換用インダクタ73、およびダイオード74を、固体撮像素子71と別体に形成することができる。

また、第4実施形態では、外部接続端子76に、外付けの平滑キャパシタ44を接続することにより、複数の画素回路67、複数のカラム回路62、デジタル演算処理回路63、および出力制御回路64は、それぞれに供給された電源電圧の下で動作する。

【0079】

<5.第5実施形態>

[電源回路1の構成および動作]

図10は、本発明の第5実施形態に係る電源回路の回路図である。

図10の電源回路1は、メインコンパレータ11、出力電圧生成部12、電源出力端子13、入力電圧生成部14、電流出力部15、抵抗素子16、スロースタート用キャパシタ17を有する。

【0080】

出力電圧生成部12は、タイミング回路81、PMOSトランジスタ82、NMOSトランジスタ83、インダクタ素子43、および平滑キャパシタ44を有する。

【0081】

PMOSトランジスタ82は、ドレインが基板の電源VDDに接続され、ソースがNMOSトランジスタ83およびインダクタ素子43の一端に接続され、ゲートがタイミング回路81に接続される。

【0082】

NMOSトランジスタ83は、ドレインがPMOSトランジスタ82のソースおよびインダクタ素子43の一端に接続され、ソースがグランドに接続され、ゲートがタイミング回路81に接続される。

したがって、PMOSトランジスタ82とNMOSトランジスタ83とは、基板の電源VDDに対して直列に接続されている。

【0083】

タイミング回路81は、メインコンパレータ11に接続される。

そして、タイミング回路81は、メインコンパレータ11からの電圧差信号S11に基づいて、PMOSトランジスタ82およびNMOSトランジスタ83をスイッチング制御する。

たとえばメインコンパレータ11から入力される電圧差信号S11がローレベルになると、タイミング回路81は、PMOSトランジスタ82およびNMOSトランジスタ83を交互にオン状態とオフ状態の間で切り替える。

このスイッチング制御により、インダクタ素子43を通じて基板の電源VDDから平滑キャパシタ44へ電流が流れ、平滑キャパシタ44が充電される。

この他にもたとえば、電圧差信号S11がハイレベルになると、タイミング回路81は、PMOSトランジスタ82およびNMOSトランジスタ83を共にオフ状態に制御する。

以上の同期整流方式の制御により、出力電圧生成部12は、出力電圧を生成する。

【0084】

<6.第6実施形態>

[撮像装置3の構成および動作]

図11は、本発明の第6実施形態に係る撮像装置3のブロック図である。

図11の撮像装置3は、上記した第2実施形態から第4実施形態のいずれかに係る固体撮像装置2と、光学系102と、信号処理回路103とを有する。また、固体撮像装置2の電源回路1は、第1実施形態のものでも、第5実施形態のものでも、後述する図12ののものでもよい。

図11の撮像装置3は、例えば、ビデオカメラ、デジタルスチルカメラ、電子内視鏡用カメラなどである。

【0085】

光学系102は、被写体からの像光(入射光)を固体撮像装置2に結像させる。

これにより、固体撮像装置2の複数の画素回路67において、入射光は入射輝度に応じたアナログの画素信号に変換される。

【0086】

信号処理回路103は、固体撮像装置2の出力信号に対して種々の信号処理を施して映像信号として出力する。

【0087】

そして、図11の撮像装置3において、固体撮像装置2は、光学系102により結像された画像についての複数の画素信号を生成し、走査周期毎に、複数の画素信号をシリアル出力する。

信号処理回路103は、固体撮像装置2からシリアル出力された複数の画素信号に対して種々の信号処理を実行する。

【0088】

以上の各実施形態は、本発明の好適な実施形態の例であるが、本発明は、これに限定されるものではなく、発明の要旨を逸脱しない範囲において種々の変形または変更が可能である。

【0089】

上記各実施形態は、ヒステリシス制御方式の電源回路1に本発明が適用された例である。

この他にも例えば、本発明は、出力電圧V(OUT)と比較される参照電圧V(REF)を用いる電源回路であれば、PWM制御方式、コンパレータ方式などのものにも適用することができる。

【0090】

図12は、PWM制御方式の電源回路1の説明図である。

図12のPWM制御方式の電源回路1は、誤差アンプ71、三角波発生回路72、パルス生成用コンパレータ73、出力電圧生成部12、電源出力端子13、および入力電圧生成部14を有する。

誤差アンプ71は、参照電圧V(REF)と入力電圧V(IN)とを比較し、参照電圧V(REF)に対する入力電圧V(IN)の電圧差を示す誤差信号を出力する。

三角波発生回路72は、電圧レベルが所定範囲で繰り返し変化するランプ信号を出力する。

パルス生成用コンパレータ73は、誤差信号とランプ信号とを比較し、たとえばランプ信号が誤差信号のレベルを超える期間においてハイレベルとなるパルス信号を生成し、出力電圧生成部12へ出力する。

この図12のPWM制御方式の電源回路1では、参照電圧V(REF)を生成する回路として、図1の電流出力部15、抵抗素子16、スロースタート用キャパシタ17などを採用することができる。

【0091】

上記各実施形態の電源回路1は、電源回路1の電源電圧より低い出力電圧V(OUT)を生成する降圧型のものである。

この他にも例えば、本発明は、電源回路1の電源電圧より高い出力電圧V(OUT)を生成する昇圧型のものであってもよい。

【0092】

上記各実施形態では、スロースタート用キャパシタ17は、電源回路1または固体撮像装置2としての集積回路に設けられている。

この他にも例えば、集積回路に接続端子を設け、この接続端子にスロースタート用キャパシタ17を外付けとしてもよい。

【0093】

上記第6実施形態は、撮像装置3の固体撮像装置2に本発明が適用された例である。

この他にも例えば、本発明は、撮像装置3の信号処理回路103に適用されてもよい。

また、本発明は、撮像装置3以外にも、たとえば携帯電話機、コンピュータ装置、PDA(Personal Data Assistance)、電子ノートなどの電子機器に適用することができる。

【符号の説明】

【0094】

1…電源回路、2…固体撮像装置、3…撮像装置(電子機器)、11…メインコンパレータ(比較部)、12…出力電圧生成部、14…入力電圧生成部、15…電流出力部、16…抵抗素子、17…スロースタート用キャパシタ(キャパシタ)、22…切替用コンパレータ、23…抵抗接続トランジスタ(第4スイッチング素子)、24…容量接続トランジスタ(第3スイッチング素子)、26…電源用論理回路(第1論理回路)、27…電源用インバータ(第2論理回路)、41…出力トランジスタ(出力スイッチング素子)、42…ダイオード、43…インダクタ素子、44…平滑キャパシタ、51…メイン電流源トランジスタ(第1電流源)、52…サブ電流源トランジスタ(第2電流源)、53…メインスイッチトランジスタ(第2スイッチング素子)、54…サブスイッチトランジスタ(第1スイッチング素子)、62…カラム回路(被給電回路)、63…デジタル演算処理回路(デジタル処理部、被給電回路)、64…出力制御部(被給電回路)、65…電力供給回路(電源回路)、66…電源入力端子、67…画素回路(被給電回路)、76…外部接続端子、81…タイミング回路、82…PMOSトランジスタ、83…NMOSトランジスタ、N1…ノード、V(REF)…参照電圧、V(IN)…入力電圧、V(OUT)…出力電圧、Vs…判定電圧、S11…電圧差信号、S22…判定信号。

【特許請求の範囲】

【請求項1】

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

電源回路。

【請求項2】

前記比較部は、

一対の第1入力端子を有するメインコンパレータを有し、

前記メインコンパレータは、

前記一対の第1入力端子の一方の第1入力端子に、前記電流出力部、前記抵抗素子および前記キャパシタが接続されるノードが接続されて前記参照電圧が入力され、他方の第1入力端子に前記入力電圧が入力され、前記参照電圧に対する前記入力電圧の高低に応じて変化する電圧差信号を出力し、

前記電流出力部は、

前記ノードへ第1参照電流を出力する第1電流源と、

前記第1参照電流より小さい第2参照電流を前記ノードへ出力する第2電流源と、

前記ノードと前記第2電流源との間に接続された第1スイッチング素子と

を有し、

前記第1スイッチング素子は、

前記電圧差信号に応じて、前記参照電圧より前記入力電圧が低い場合にオン状態となり、前記参照電圧より前記入力電圧が高い場合にオフ状態となることにより、前記参照電圧を制御する

請求項1記載の電源回路。

【請求項3】

前記電流出力部は、

前記ノードと前記第1電流源との間に接続された第2スイッチング素子を有し、

前記第2スイッチング素子は、

起動する際にオフ状態とされることにより、起動する際の前記参照電流を動作中の前記参照電流より小さくする

請求項2記載の電源回路。

【請求項4】

前記電源回路は、

前記ノードと前記キャパシタとの間に接続された第3スイッチング素子を有し、

前記第3スイッチング素子は、

起動する場合にオンとなり、動作中にはオフとなることにより動作中に前記キャパシタを前記ノードから切り離す

請求項2または3記載の電源回路。

【請求項5】

前記電源回路は、

一対の第2入力端子を有する切替用コンパレータと、

前記ノードと前記抵抗素子との間に接続された第4スイッチング素子と

を有し、

前記切替用コンパレータは、

前記一対の第2入力端子の一方の第2入力端子に前記ノードが接続されて前記参照電圧が入力され、他方の第2入力端子に、前記抵抗素子に前記第1電流が流れた場合の参照電圧より低い判定電圧が入力され、前記判定電圧に対する前記参照電圧の高低に応じて切り替わる判定信号を出力する

前記第4スイッチング素子は、

前記判定信号に応じて、前記判定電圧より前記参照電圧が高い場合にオン状態となり、前記判定電圧より前記参照電圧が低い場合にオフ状態となることにより起動する際に前記抵抗素子を前記ノードから切り離す

請求項2から4のいずれか一項記載の電源回路。

【請求項6】

前記電源回路は、

前記メインコンパレータの電圧差信号および前記切替用コンパレータの判定信号が入力され、前記第1スイッチング素子へ制御信号を出力する第1論理回路と、

前記切替用コンパレータの判定信号が入力され、前記第2スイッチング素子へ制御信号を出力する第2論理回路と

を有する請求項5記載の電源回路。

【請求項7】

前記出力電圧生成部は、

前記電圧差信号によりスイッチング動作する出力スイッチング素子と、

前記出力スイッチング素子にカソードが接続されるダイオードと、

一端が前記出力スイッチング素子に接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと

を有する請求項1から6のいずれか一項記載の電源回路。

【請求項8】

前記出力電圧生成部は、

電源に対して直列に接続された第1スイッチング素子および第2スイッチング素子と、

前記第1スイッチング素子と前記第2スイッチング素子との接続ノードに一端が接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと、

前記電圧差信号が入力され、前記電圧差信号に応じて前記第1スイッチング素子および前記第2スイッチング素子をスイッチング制御するタイミング回路と

を有する請求項1から6のいずれか一項記載の電源回路。

【請求項9】

出力電圧を出力する電源回路と、

前記出力電圧が給電される被給電回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

集積回路装置。

【請求項10】

前記出力電圧生成部は、

前記電圧差信号によりスイッチング動作する出力スイッチング素子と、

前記出力スイッチング素子にカソードが接続されるダイオードと、

一端が前記出力スイッチング素子に接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、平滑キャパシタを接続可能な外部接続端子と

を有する請求項9記載の集積回路装置。

【請求項11】

前記出力電圧生成部は、

電源に対して直列に接続された第1スイッチング素子および第2スイッチング素子と、

前記第1スイッチング素子と前記第2スイッチング素子との接続ノードに一端が接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと、

前記電圧差信号が入力され、前記電圧差信号に応じて前記第1スイッチング素子および前記第2スイッチング素子をスイッチング制御するタイミング回路と

を有する請求項9記載の集積回路装置。

【請求項12】

複数の画素回路が二次元に配列され、各前記画素回路のアナログの画素信号を出力する画素アレイ部と、

前記アナログの画素信号をデジタルに変換するカラム回路と、

デジタルの前記画素信号をデジタル処理するデジタル処理部と、

デジタル処理されたデジタルの前記画素信号を出力する出力制御部と、

前記画素アレイ部、前記カラム回路、前記デジタル処理部および前記出力制御部のうちの少なくとも1個に出力電圧を出力する電源回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

固体撮像装置。

【請求項13】

前記画素アレイ部および前記カラム回路に給電するための電源入力端子を有し、

前記電源回路は、

前記電源入力端子の入力電圧を降圧した出力電圧を、前記デジタル処理部および前記出力制御部へ供給する

請求項12記載の固体撮像装置。

【請求項14】

出力電圧を出力する電源回路と、

前記出力電圧が給電される被給電回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

電子機器。

【請求項1】

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

電源回路。

【請求項2】

前記比較部は、

一対の第1入力端子を有するメインコンパレータを有し、

前記メインコンパレータは、

前記一対の第1入力端子の一方の第1入力端子に、前記電流出力部、前記抵抗素子および前記キャパシタが接続されるノードが接続されて前記参照電圧が入力され、他方の第1入力端子に前記入力電圧が入力され、前記参照電圧に対する前記入力電圧の高低に応じて変化する電圧差信号を出力し、

前記電流出力部は、

前記ノードへ第1参照電流を出力する第1電流源と、

前記第1参照電流より小さい第2参照電流を前記ノードへ出力する第2電流源と、

前記ノードと前記第2電流源との間に接続された第1スイッチング素子と

を有し、

前記第1スイッチング素子は、

前記電圧差信号に応じて、前記参照電圧より前記入力電圧が低い場合にオン状態となり、前記参照電圧より前記入力電圧が高い場合にオフ状態となることにより、前記参照電圧を制御する

請求項1記載の電源回路。

【請求項3】

前記電流出力部は、

前記ノードと前記第1電流源との間に接続された第2スイッチング素子を有し、

前記第2スイッチング素子は、

起動する際にオフ状態とされることにより、起動する際の前記参照電流を動作中の前記参照電流より小さくする

請求項2記載の電源回路。

【請求項4】

前記電源回路は、

前記ノードと前記キャパシタとの間に接続された第3スイッチング素子を有し、

前記第3スイッチング素子は、

起動する場合にオンとなり、動作中にはオフとなることにより動作中に前記キャパシタを前記ノードから切り離す

請求項2または3記載の電源回路。

【請求項5】

前記電源回路は、

一対の第2入力端子を有する切替用コンパレータと、

前記ノードと前記抵抗素子との間に接続された第4スイッチング素子と

を有し、

前記切替用コンパレータは、

前記一対の第2入力端子の一方の第2入力端子に前記ノードが接続されて前記参照電圧が入力され、他方の第2入力端子に、前記抵抗素子に前記第1電流が流れた場合の参照電圧より低い判定電圧が入力され、前記判定電圧に対する前記参照電圧の高低に応じて切り替わる判定信号を出力する

前記第4スイッチング素子は、

前記判定信号に応じて、前記判定電圧より前記参照電圧が高い場合にオン状態となり、前記判定電圧より前記参照電圧が低い場合にオフ状態となることにより起動する際に前記抵抗素子を前記ノードから切り離す

請求項2から4のいずれか一項記載の電源回路。

【請求項6】

前記電源回路は、

前記メインコンパレータの電圧差信号および前記切替用コンパレータの判定信号が入力され、前記第1スイッチング素子へ制御信号を出力する第1論理回路と、

前記切替用コンパレータの判定信号が入力され、前記第2スイッチング素子へ制御信号を出力する第2論理回路と

を有する請求項5記載の電源回路。

【請求項7】

前記出力電圧生成部は、

前記電圧差信号によりスイッチング動作する出力スイッチング素子と、

前記出力スイッチング素子にカソードが接続されるダイオードと、

一端が前記出力スイッチング素子に接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと

を有する請求項1から6のいずれか一項記載の電源回路。

【請求項8】

前記出力電圧生成部は、

電源に対して直列に接続された第1スイッチング素子および第2スイッチング素子と、

前記第1スイッチング素子と前記第2スイッチング素子との接続ノードに一端が接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと、

前記電圧差信号が入力され、前記電圧差信号に応じて前記第1スイッチング素子および前記第2スイッチング素子をスイッチング制御するタイミング回路と

を有する請求項1から6のいずれか一項記載の電源回路。

【請求項9】

出力電圧を出力する電源回路と、

前記出力電圧が給電される被給電回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

集積回路装置。

【請求項10】

前記出力電圧生成部は、

前記電圧差信号によりスイッチング動作する出力スイッチング素子と、

前記出力スイッチング素子にカソードが接続されるダイオードと、

一端が前記出力スイッチング素子に接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、平滑キャパシタを接続可能な外部接続端子と

を有する請求項9記載の集積回路装置。

【請求項11】

前記出力電圧生成部は、

電源に対して直列に接続された第1スイッチング素子および第2スイッチング素子と、

前記第1スイッチング素子と前記第2スイッチング素子との接続ノードに一端が接続されるインダクタ素子と、

前記インダクタ素子の他端に接続され、前記出力電圧を生成する平滑キャパシタと、

前記電圧差信号が入力され、前記電圧差信号に応じて前記第1スイッチング素子および前記第2スイッチング素子をスイッチング制御するタイミング回路と

を有する請求項9記載の集積回路装置。

【請求項12】

複数の画素回路が二次元に配列され、各前記画素回路のアナログの画素信号を出力する画素アレイ部と、

前記アナログの画素信号をデジタルに変換するカラム回路と、

デジタルの前記画素信号をデジタル処理するデジタル処理部と、

デジタル処理されたデジタルの前記画素信号を出力する出力制御部と、

前記画素アレイ部、前記カラム回路、前記デジタル処理部および前記出力制御部のうちの少なくとも1個に出力電圧を出力する電源回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

固体撮像装置。

【請求項13】

前記画素アレイ部および前記カラム回路に給電するための電源入力端子を有し、

前記電源回路は、

前記電源入力端子の入力電圧を降圧した出力電圧を、前記デジタル処理部および前記出力制御部へ供給する

請求項12記載の固体撮像装置。

【請求項14】

出力電圧を出力する電源回路と、

前記出力電圧が給電される被給電回路と

を有し、

前記電源回路は、

参照電圧と入力電圧とを比較して電圧差信号を出力する比較部と、

前記電圧差信号に基づいて出力電圧を生成する出力電圧生成部と、

前記出力電圧から前記入力電圧を生成する入力電圧生成部と、

参照電流を出力する電流出力部と、

前記参照電流により前記参照電圧を生成する抵抗素子と、

前記抵抗素子と並列に接続され、前記参照電流により充電されるキャパシタと

を有し、

前記電流出力部は、

起動する際の前記参照電流を、動作中の前記参照電流より小さくする

電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−250554(P2011−250554A)

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願番号】特願2010−120198(P2010−120198)

【出願日】平成22年5月26日(2010.5.26)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成23年12月8日(2011.12.8)

【国際特許分類】

【出願日】平成22年5月26日(2010.5.26)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]