電源回路および非接触ICカード

【課題】 回路の負荷変動によって生じる電流変動分を補償することにより、電源ノイズおよび電源電圧変動を抑制し、高性能な電源回路を実現する。

【解決手段】 リニアレギュレータ200を用いてデジタル回路300の負荷変動によって生じる電流変動分をモニターし、その電流変動分を電流補償回路400により電源電圧AVDDからグランドVSSに補償電流として流すことにより、電源AVDDの負荷インピーダンスを常に一定とする。その結果、電源電圧AVDDの変動およびノイズが低減され、高性能な電源回路1が得られる。

【解決手段】 リニアレギュレータ200を用いてデジタル回路300の負荷変動によって生じる電流変動分をモニターし、その電流変動分を電流補償回路400により電源電圧AVDDからグランドVSSに補償電流として流すことにより、電源AVDDの負荷インピーダンスを常に一定とする。その結果、電源電圧AVDDの変動およびノイズが低減され、高性能な電源回路1が得られる。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、回路の負荷変動により生じる電流変動分を補償することにより、電源ノイズや電源電圧変動を抑制することができる電源回路およびそれを用いた非接触ICカードに関する。

【0002】

【従来の技術】通常、アナログ回路やデジタル回路等の電子回路は、電源電圧を印加することにより作動する。このときに回路に流れる電流は、回路動作により異なる。特に、CPUやロジック回路、メモリ等のデジタル回路においては、電流変動が大きい。このような電流変動は、電源ノイズや電源電圧変動となって現れる。以下に、電源ノイズが発生するメカニズムについて説明する。

【0003】図11は、従来の半導体集積回路の構成を示す図である。この半導体集積回路3は、デジタル回路300とアナログ回路310とからなり、デジタル回路300はCPU301やメモリ302からなる。この半導体集積回路3には、外部からインダクタL1を通じて電源電圧VDDが与えられている。インダクタL1は、配線やボンディングワイヤ等により生じる寄生インダクタであり、その値は例えば数nF程度である。このとき、チップ(半導体集積回路)内の内部電源電圧はVDD1となる。

【0004】ここで、デジタル回路300とアナログ回路310とにより消費される電流I1が図12(b)に示すように変化した場合を考えると、チップ内の電源電圧VDD1は図12(a)に示すように、電流I1の変化点で変動を起こす。

【0005】このような電源ノイズは、アナログ回路310の回路動作には大きく影響する。例えば、ヒステリシス特性を有するコンパレータの場合には、電源電圧VDD1の変動によって比較値の極性が変わり、誤動作を引き起こすこともある。また、増幅器においても、電源電圧変動成分が付加されて信号の品質が劣化するという問題がある。以下に、アナログ回路の誤動作や特性劣化について、具体例を示す。

【0006】図13は、ヒステリシス特性を有するコンパレータの入出力特性を示す図である。一般に、コンパレータは、基準電圧に対して入力電圧が高いときにHIGH状態になり、基準電圧に対して入力電圧が低いときにLOW状態になる。これに対して、ヒステリシス特性を有するコンパレータにおいては、図13に示すように、入力電圧(入力信号Vin)が基準電圧Vref1に対してオフセット電圧を加えたレベルVH以上になると出力信号VoutがHIGH状態になり、入力電圧(入力信号Vin)が基準電圧Vref1に対してオフセット電圧を引いたレベルVL以下になると出力信号VoutがLOW状態になる。ここで、ヒステリシス特性を有するコンパレータの出力がHIGH状態であり、入力電圧が基準電圧Vref1と等しい場合を考える。この場合に、電源ノイズにより入力電圧がVL以下に下がったとすると、コンパレータの出力はHIGH状態からLOW状態になり、元の値(HIGH状態)に戻ることはない。

【0007】このような問題を解決するために、従来から、アナログ回路とデジタル回路の電源を分離したり、チップ内で電源電圧VDD1とグランドVSS間に容量Cpassを形成して電源電圧変動を抑制する方法が用いられてきた。

【0008】

【発明が解決しようとする課題】しかしながら、上述したような方法では、チップのピン(端子)数の増加や、チップ内に形成される容量の面積増大を招く。Cpassの値としては1μF以上が望まれるが、チップ内で形成可能な容量値は標準CMOSプロセスで1nF程度であり、回路の大きな負荷変動に対しては効果があまり得られない。

【0009】本発明は、このような従来技術の課題を解決するためになされたものであり、デジタル回路等の負荷変動によって生じる電流変動分を補償することにより、電源ノイズおよび電源電圧変動を抑制し、アナログ回路等、電源ノイズや電源電圧変動に影響を受け易い回路の誤動作や信号の品質劣化を抑制することができる高性能な電源回路および非接触ICカードを提供することを目的とする。

【0010】

【課題を解決するための手段】本発明の電源回路は、第1の電子回路に供給される第1の電源電圧と第2の電子回路に供給される第2の電源電圧との間に接続され、該第1の電源電圧部から該第2の電源電圧部に流れる電流をモニタするためのモニタ端子を有する電流検出回路と、該第1の電源電圧と該モニタ端子とに接続され、モニタした電流によって該第1の電源電圧部からグランドに流れる補償電流を制御して、該第2の電子回路の負荷変動によって生じる電流変動分を補償する電流補償回路とを備えており、そのことにより上記目的が達成される。

【0011】上記構成によれば、電流検出回路を用いて第2の電源電圧部に流れる電流をモニタすることにより、デジタル回路等の負荷変動によって生じる電流変動を検出し、その電流変動分を電源補償回路を用いて補償することにより、電源ノイズおよび電源電圧変動を抑制し、アナログ回路等、電源ノイズや電源電圧変動に影響を受け易い回路の誤動作や信号の品質劣化を抑制し、低ノイズで高性能な電源回路を実現することができる。

【0012】前記電流検出回路は、演算増幅器とトランジスタと2つの抵抗とを備えたリニアレギュレータを有し、該トランジスタは、ソースが前記第1の電源電圧に接続され、ゲートが該演算増幅器の出力端子に接続されると共に、ドレインが前記第2の電源電圧に接続され、該2つの抵抗は、該第2の電源電圧とグランドとの間に直列に接続されると共に、該2つの抵抗の接続点が該演算増幅器の非反転入力端子に接続され、該演算増幅器は、反転入力端子が基準電圧に接続されると共に、出力端子が前記モニタ端子として機能する構成としてもよい。

【0013】上記構成によれば、後述する実施の形態1に示すように、リニアレギュレータを用いてデジタル回路等の負荷変動によって生じる電流変動分をモニターすることが可能である。

【0014】前記電流検出回路は、前記第1の電源電圧と前記第2の電源電圧との間に接続された抵抗を有し、該第2の電源電圧側にモニタ端子を有する構成としてもよい。

【0015】上記構成によれば、後述する実施の形態2に示すように、電流検出回路を用いてデジタル回路等の負荷変動によって生じる電流変動分をモニターすることが可能である。

【0016】前記電流補償回路は、所定の電流と前記モニタ端子によって制御される電流との差電流を生成する引き算回路と、該差電流に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する構成としてもよい。

【0017】上記構成によれば、後述する実施の形態1に示すように、デジタル回路等の電流変動分を電源補償回路を用いて補償することが可能である。

【0018】前記電流補償回路は、参照電圧を生成する参照電圧発生回路と、該参照電圧と前記モニタ端子の電圧との差電圧に比例した差電流と所定の電流との和を生成する差動増幅回路と、該差電流と所定の電流との和に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する構成としてもよい。

【0019】上記構成によれば、後述する実施の形態2に示すように、デジタル回路等の電流変動分を電源補償回路を用いて補償することが可能である。

【0020】前記第1の電源電圧はアナログ回路に接続されるものであってもよい。

【0021】上記構成によれば、電源変動に影響され易いアナログ回路の誤動作や信号の品質劣化を抑制することが可能である。

【0022】前記第2の電源電圧はデジタル回路に接続されるものであってもよい。

【0023】上記構成によれば、電流変動が大きいデジタル回路等の負荷変動によって生じる電流変動を検出し、その電流変動分を電源補償回路を用いて補償することが可能である。

【0024】前記電流回路は、第4の抵抗を介してグランドに前記補償電流を流す構成としてもよい。

【0025】上記構成によれば、電流回路に設けられたトランジスタのばらつき等によって不必要に流れる電流を抑制することが可能である。

【0026】前記第1の電源電圧部から前記第2の電源電圧部に流れる電流と、該第1の電源電圧部からグランドに流れる前記補償電流の和が一定であるのが好ましい。

【0027】上記構成によれば、第2の電源電圧部に流れる電流変動分を補償して電源ノイズを抑制することができる。なお、補償電流と第2の電源電圧部に流れる電流の和は一定でなくてもよく、その場合には、電流変動分の一部を補償して電源ノイズの低減を図ることが可能である。

【0028】本発明の非接触ICカードは、コイルアンテナと、同調容量と充電容量と整流回路とアナログ回路とデジタル回路と本発明の電源回路とを備えた半導体集積回路とを有し、該コイルアンテナは、該同調容量と並列に接続されて該整流回路の入力に接続され、該整流回路は、出力が該充電容量に接続されて、該アナログ回路に供給される第1の電源電圧を生成し、該電源回路は、該第1の電源電圧から、該デジタル回路に供給される第2の電源電圧を生成し、そのことにより上記目的が達成される。

【0029】上記構成によれば、デジタル回路等の負荷変動によりアナログ回路等の誤動作や信号の品質劣化が生じるのを抑制し、高性能な非接触ICカードを実現することが可能である。

【0030】前記アナログ回路は復調回路を備えている構成としてもよい。

【0031】上記構成によれば、後述する実施の形態3に示すように、復調回路を有する高性能な非接触ICカードを実現することが可能である。

【0032】前記半導体集積回路は、前記同調容量と並列に接続されて該整流回路の入力に接続される変調回路をさらに備えている構成としてもよい。

【0033】上記構成によれば、後述する実施の形態4に示すように、変調回路を有する高性能な非接触ICカードを実現することが可能である。

【0034】前記変調回路は、変調信号により回路インピーダンスを変調させる構成としてもよい。

【0035】上記構成によれば、後述する実施の形態4に示すように、全波整流器を有する高性能な非接触ICカードを実現することが可能である。

【0036】前記整流回路は全波整流回路である構成としてもよい。

【0037】上記構成によれば、後述する実施の形態4に示すように、全波整流器を有する高性能な非接触ICカードを実現することが可能である。なお、整流回路としては、半波整流回路を用いてもよく、その場合には、半波整流器を有する高性能な非接触ICカードを実現することが可能である。

【0038】

【発明の実施の形態】以下に、本発明の実施の形態について、図面を参照しながら説明する。なお、以下の図において、同様の機能を有する構成要素については、従来技術と同じ符号を付してその説明を省略する。

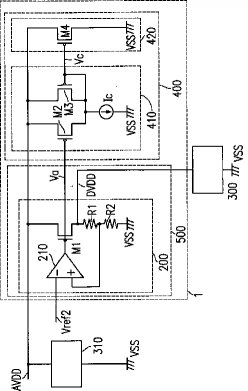

【0039】(実施の形態1)図1は実施の形態1に係る電源回路の構成を示す図である。この電源回路1は、電流検出回路500と電流補償回路400とを有している。デジタル回路300はデジタル電源電圧DVDDを電源とし、アナログ回路310はアナログ電源電圧AVDDを電源としている。

【0040】電流検出回路500はリニアレギュレータ200により実現され、リニアレギュレータ200は、抵抗R1、R2と、演算増幅器210と、pMOSトランジスタM1とにより構成されている。トランジスタM1のソースはアナログ電源電圧AVDDに接続され、ゲートは演算増幅器210の出力端子に接続され、ドレインはデジタル電源電圧DVDDに接続されている。演算増幅器210の出力端子は、デジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニタするモニタ端子(モニタ電圧Va)となっている。抵抗R1は、デジタル電源電圧DVDDと演算増幅器210の非反転入力端子に接続され、抵抗R2は、グランドVSSと演算増幅器210の非反転入力端子に接続されている。

【0041】電流補償回路は400は、引き算回路410と電流回路420とにより構成されている。引き算回路410は、所定の電流源IcとトランジスタM2、M3とにより構成されている。電流源Icは、グランドVSSとトランジスタM2、M3のドレインとに接続され、トランジスタM2、M3のソースはアナログ電源電圧AVDDに接続され、トランジスタM2のゲートはリニアレギュレータ200のモニタ端子(モニタ電圧Va)に接続され、トランジスタM3のゲートとドレインとは接続されて電流回路420の制御電圧Vcとなっている。電流回路420は、トランジスタM4により構成され、トランジスタM4のソースはアナログ電源電圧AVDDに接続され、ドレインはグランドVSSに接続され、ゲートは制御電圧Vcに接続されている。

【0042】ここで、上記演算増幅器210の反転入力端子に基準電圧Vref2(外部から供給される)を接続すると、デジタル電源電圧DVDDは、 DVDD=Vref×(R1+R2)/R2 ・・・(1)

のように表される。ここで、抵抗R1、R2に流れる電流をI1に比べて非常に小さくなるように選ぶと、トランジスタM2、M3、M4に流れる電流I2、I3、I4は、各々、I2=n×I1 ・・・(2)

I3=Ic−n×I1 ・・・(3)

I4=m×(Ic−n×I1) ・・・(4)

のように表される。従って、引き算回路410では所定の電流Icとモニタ端子(モニタ電圧Va)により制御される電流I2との差電流I3が生成され、電流回路420には差電流I3に比例した電流I4がアナログ電源電圧AVDD部からグランドVSSに補償電流として流れる。なお、上記式において、nはトランジスタM1とトランジスタM2のサイズ比であり、mはトランジスタM3とM4のサイズ比である。また、I1はトランジスタM1に流れる電流である。例えばトランジスタM1、M2、M3、M4のゲート幅をW1、W2、W3、W4とし、ゲート長をL1、L2、L3、L4とすると、nとmは、各々、n=(W2×L1)/(L2×W1) ・・・(5)

m=(W4×L3)/(L4×W3) ・・・(6)

のように表される。

【0043】そして、Ic=n×I0、m=1/nとすると、トランジスタM4に流れる電流I4は、I4=I0−I1となる。ここで、デジタル回路300に流れる電流がΔI1だけ増え、I1+ΔI1となったとすると、I4はI0−I1−ΔI1となり、デジタル回路300に流れる電流の変動分を補償する電流が電流回路420に流れることになる。アナログ電源電圧AVDD部からアナログ回路310に流れる電流は、図1の場合、デジタル回路300に流れる電流I1、引き算回路410に流れる電流Ic、電流補償回路420に流れる電流(I0−I1)の和(I0+Ic)となる。その結果、アナログ電源電圧AVDD部から流れる電流は、アナログ回路310に流れる電流を除けば、一定となる。これは、デジタル回路の負荷変動によって生じるアナログ電源電圧AVDDのノイズを低減することを意味する。

【0044】以上のことから、本実施形態では、電源電圧変動を抑制するためにデジタル回路とアナログ回路の電源を分離する必要が無いため、チップのピン数を削減することができる。また、電源電圧変動を抑制するためにチップ内でデジタル電源電圧とグランド間に大きな容量を形成する必要が無いため、チップ内に形成される容量の面積増大を防ぐことができる。その結果として、チップ実装が容易で電源ノイズの低い高性能な電源回路を実現することができる。

【0045】(実施の形態2)図2は実施の形態2に係る電源回路の構成を示す図である。この電源回路1は、電流検出回路500と電流補償回路400とを有している。デジタル回路300はデジタル電源電圧DVDDを電源とし、アナログ回路310はアナログ電源電圧AVDDを電源としている。

【0046】電流検出回路500は、抵抗R10をアナログ電源電圧AVDDとデジタル電源電圧DVDDとの間に接続して構成され、デジタル電源電圧DVDD側に、デジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニタするモニタ端子(モニタ電圧Va)を有している。

【0047】電流補償回路400は、参照電圧発生回路440、差動増幅回路430、電流回路420とにより構成されている。参照電圧発生回路440は、抵抗R11と抵抗R12とがアナログ電源電圧AVDDとグランドVSSとの間に直列に接続され、抵抗R11と抵抗R12の抵抗分割によって生成される電圧を参照電圧Vref3として出力する。差動増幅回路430は、nMOSトランジスタM10、M11とpMOSトランジスタM12、M13と電流源I10とにより構成されている。電流源I10は、グランドVSSとトランジスタM10、M11のソースとに接続され、トランジスタM10のドレインにはトランジスタM12のドレインが接続され、トランジスタM11のドレインにはトランジスタM13のドレインが接続されている。トランジスタM12とトランジスタM13はダイオード接続(ソースとゲートを接続してカソードとし、ドレインをアノードとした構造)され、トランジスタM11のドレインとトランジスタM13のゲートとドレインが電流回路420の制御電圧Vcに接続されている。トランジスタM12、M13のソースはアナログ電源電圧AVDDに接続され、トランジスタM11のゲートはモニタ端子(モニタ電圧Va)に接続され、トランジスタM10のゲートは参照電圧Vref3に接続されている。電流回路420は、トランジスタM4により構成され、トランジスタM4のソースはアナログ電源電圧AVDDに接続され、ドレインはグランドVSSに接続され、ゲートは制御電圧Vcに接続されている。この電流回路420は、差増増幅回路430からの制御電圧Vcによってアナログ電源電圧AVDD部からグランドVSSに流れる電流をコントロールする。

【0048】ここで、デジタル回路300において最大の電流を消費するときの負荷抵抗をRmaxとし、差動増幅器の電流ゲインをAとする。そして、抵抗R10〜R12とRmaxの関係を (R10/(Rmax+R10))/2=R11/(R11+R12)

・・・(7)

のように設定する。例えば、Rmax=90Ω、R10=10Ω、R11=10kΩ、R12=190kΩとする。このとき、参照電圧発生回路430における消費電流を小さくするために、R11/R10=10000とする。

【0049】そして、アナログ電源電圧AVDDを3Vとすると、参照電圧Vref3は2.85Vとなり、デジタル負荷最大時の電圧DVDDは2.7Vとなり、デジタル回路300の最大負荷電流は30mAとなる。ここで、トランジスタM13とトランジスタM4のミラー比(実施の形態1のサイズ比と同じ)をMとし、差増増幅回路430の電流ゲインをAとすると、トランジスタM4に流れる電流I4は、 I4=M×(A×(DVDD−Vref3)+I10/2) ・・・(8)

のように表される。これは、モニタ電圧DVDDと参照電圧Vref3の差電圧により流れる電流(A×(DVDD−Vref3)と所定の電流I10/2の和に比例した電流がI4に流れることを意味する。

【0050】ここで、A=0.001、I10=300μA、M=100とすると、デジタル回路の負荷電流が最大(デジタル回路300に流れる負荷電流が30mA)のときには電流回路420は0mAとなり、デジタル回路の負荷電流が最少(デジタル回路300に流れる負荷電流が0mA)のときには電流回路420は30mAとなる。その結果、AVDDからアナログ回路310に流れる電流を除けば、デジタル回路の負荷変動によらず、常に一定の電流30mAが流れることになる。なお、差動増幅回路430および参照電圧発生回路440に流れる電流は、電流回路420とデジタル回路300に流れる電流に比べて非常に小さいので、無視することができる。よって、電源電圧AVDD部にデジタル回路の負荷変動によるノイズが発生するのを抑制することができ、高性能な電源回路を実現することができる。

【0051】以上のことから、本実施形態では、電源電圧変動を抑制するためにデジタル回路とアナログ回路の電源を分離する必要が無いため、チップのピン数を削減することができる。また、電源電圧変動を抑制するためにチップ内でデジタル電源電圧とグランド間に大きな容量を形成する必要が無いため、チップ内に形成される容量の面積増大を防ぐことができる。その結果として、チップ実装が容易で電源ノイズの低い高性能な電源回路を実現することができる。

【0052】なお、本発明は、上記実施の形態1および実施の形態2で説明した電流検出回路500および電流補償回路400の具体例に限定されるものではない。図3R>3に示すように、電流検出回路500によりデジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニターし、電流補償回路400によってアナログ電源電圧AVDD部からグランドVSSに流れる補償電流を制御してデジタル回路300の電流変動分を補償することができる電源回路であれば、全て本発明の範囲に含まれる。

【0053】補償電流とデジタル電源電圧DVDD部に流れる電流の和を一定としたが、補償電流とデジタル電源電圧DVDD部に流れる電流の和は一定でなくてもよく、デジタル電源電圧DVDD部に流れる電流の変動分の一部を電流補償回路400によって補償することによっても、電源ノイズの低減を図ることができる。

【0054】上記実施の形態1および実施の形態2では、電流回路420においてトランジスタM4のドレインをグランドVSSに接続したが、図4に示すように、トランジスタM4のドレインを抵抗R3を介してグランドVSSに接続してもよい。この場合には、トランジスタM4の素子特性のばらつき等によって不必要に流れる電流を抑制することができる。

【0055】さらに、上記実施の形態1および実施の形態2では、デジタル回路300とアナログ回路310とに区別したが、デジタル回路の代わりに電源電圧変動に影響されにくい回路を用い、電源電圧変動に影響され易い回路をアナログ回路の代わりに用いた構成としてもよい。

【0056】以上のように、本発明は、高性能な電源回路を得ることに対して大いに寄与するものであり、極めて有用なものである。

【0057】(実施の形態3)図5は実施の形態3に係る非接触ICカードの構成を示す図である。この非接触ICカード4は、コイルアンテナL2と半導体集積回路3とを有している。半導体集積回路は、同調容量C3と充電容量C4と整流回路2とアナログ回路310とデジタル回路300と電源回路1とにより構成されている。同調容量C3とコイルアンテナL2とは並列に接続されて整流回路2の入力に接続されている。整流回路の出力は充電容量C4に充電され、アナログ回路310の電源電圧AVDDとなる。アナログ回路310は、電源電圧AVDDから受信信号を取り出す復調回路311を備えている。電源回路1は、電源電圧AVDDからデジタル回路300に供給される電源電圧DVDDを生成する。この電源回路1としては、上記実施の形態1および実施の形態2で説明したようなものを用いることができる。

【0058】半導体集積回路4で消費される電力と受信信号とはコイルアンテナL2により受電される。このとき、受信信号には振幅変調がかかっているものとする。そして、整流回路2としては図6に示すようなダイオードD1〜D4を用いた全波整流回路を用い、復調回路311としてはヒステリシスを有するコンパレータを用いる。コイルアンテナL2により受信された信号は、整流回路2により整流され、図7に示すような電源電圧AVDDが生成される。また、復調回路311により、電源電圧AVDDから信号成分が抽出される。このとき、復調回路311は、電源電圧AVDDが基準レベル以上に変化したときに、信号として取り出す。

【0059】ここで、デジタル回路300の電流変動が図8(a)に示すように起こったとすると、電源電圧AVDDの波形は図8(b)に点線で示すようになる。このようなデジタル回路300の電流変動(負荷変動)により、電源回路1が無い場合には、復調回路311が誤動作を引き起こし、復調信号が図8(c)の点線に示すようになる。これに対して、本実施の形態のように電源回路1を有する非接触ICカードでは、図8(b)に実線で示すようにデジタル回路300の負荷変動による電源電圧AVDDの変動を抑制することができ、その結果、図8(c)に示すように誤動作を生じずに復調することができることが分かった。

【0060】以上のことから、本実施形態では、デジタル回路の負荷変動によるアナログ回路の誤動作を低減することができ、その結果として、高性能な非接触ICカードを実現することができる。

【0061】(実施の形態4)図9は実施の形態4に係る非接触ICカードの構成を示す図である。本実施の形態と実施の形態3との相違点は、変調回路315が同調容量C3と並列に接続されて整流回路2の入力に接続されていることである。この変調回路315は、変調信号によって、半導体集積回路3のコイルアンテナL2間のインピーダンスを変調させる。

【0062】図10(a)は、図10(b)に示すような変調信号が入力された場合に、電源回路1を有する場合と電源回路1が無い場合とについて、コイルL2間のインピーダンスを示す図である。この図において、実線が電源回路1を有する場合を示し、点線が電源回路1が無い場合を示す。図10(c)に示すようにデジタル回路310で電流変動(負荷変動)が起こると、電源回路1が無い場合には、図10(a)に点線で示すように、コイルL2間のインピーダンスに影響を与える。これに対して、本実施形態のように電源回路1を有する非接触ICカードでは、図10(a)に実線で示すようにデジタル回路300の負荷変動による電源インピーダンスを一定にすることができる。

【0063】以上のことから、本実施形態では、デジタル回路の負荷変動によるアナログ回路の誤動作を低減することができ、その結果として、高性能な非接触ICカードを実現することができる。

【0064】なお、本発明は、上記実施の形態3および実施の形態4で説明した半導体集積回路3の具体例に限定されるものではない。電源回路として実施の形態1および実施の形態2で説明したような電源回路を有する非接触ICカードであれば、全て本発明の範囲に含まれる。

【0065】同調容量C3は、半導体集積回路3に形成したが、半導体チップの外部に実装しても良く、また、整流回路2またはコイルアンテナL2の寄生容量を用いてもよい。

【0066】さらに、上記実施の形態3および実施の形態4では、整流回路2として全波整流回路を用いたが、半波整流回路を用いてもよい。

【0067】以上のように、本発明は、高性能な非接触ICカードを得ることに対して大いに寄与するものであり、極めて有用なものである。

【0068】

【発明の効果】以上詳述したように、本発明によれば、電流検出回路を用いてデジタル電源電圧部等に流れる電流をモニタすることにより、デジタル回路等の負荷変動による電流変動分を検出し、その電流変動分を電源補償回路を用いて補償することにより、低ノイズで高性能な電源回路を実現することができる。

【0069】さらに、本発明によれば、本発明の電源回路を用いることにより、復調回路や変調回路を有する高性能な非接触ICカードを実現することができる。

【図面の簡単な説明】

【図1】実施の形態1に係る電源回路の構成を示す図である。

【図2】実施の形態2に係る電源回路の構成を示す図である。

【図3】本発明に係る電源回路の構成を示す図である。

【図4】実施の形態1および実施の形態2の電源回路における他の電流回路の構成を示す図である。

【図5】実施の形態3に係る非接触ICカードの構成を示す図である。

【図6】実施の形態3の非接触ICにおける整流回路の構成を示す図である。

【図7】実施の形態3において、振幅変調された信号を整流した後の波形AVDDを示す図である。

【図8】(a)は実施の形態3において、デジタル回路の消費電流を示す図であり、(b)は電源回路を有する場合と無い場合について電源電圧AVDDを示す図であり、(c)は電源回路を有する場合と無い場合について復調信号を示す図である。

【図9】実施の形態4に係る非接触ICカードの構成を示す図である。

【図10】(a)は実施の形態4において、電源回路を有する場合と無い場合についてコイルL2間のインピーダンスを示す図であり、(b)は変調信号を示す図であり、(c)はデジタル回路の消費電流を示す図である。

【図11】従来の半導体集積回路の構成を示す図である。

【図12】(a)および(b)は従来の半導体集積回路に流れる電流I1と電源電圧VDD1との関係を示す図である。

【図13】ヒステリシス特性を有するコンパレータの入出力特性を示す図である。

【符号の説明】

1 電源回路

2 整流回路

3 半導体集積回路

4 非接触ICカード

200 リニアレギュレータ

210 演算増幅器

300 デジタル回路

301 CPU

302 メモリ

310 アナログ回路

311 復調回路

315 変調回路

400 電流補償回路

410 引き算回路

420 電流回路

430 差動増幅回路

440 参照電圧発生回路

500 電流検出回路

M1、M2、M3、M4、M10、M11、M12、M13 トランジスタ

R1、R2、R3、R10、R11、R12 抵抗

Ic、I10 電流源

L1 インダクタ

L2 コイルアンテナ

C3 同調容量

C4 充電容量

D1、D2、D3、D4 ダイオード

VDD、VDD1、DVDD、AVDD 電源電圧

VSS グランド

Vref1、Vref2 基準電圧

Vref3 参照電圧

Va モニタ電圧

Vc 制御電圧

【0001】

【発明の属する技術分野】本発明は、回路の負荷変動により生じる電流変動分を補償することにより、電源ノイズや電源電圧変動を抑制することができる電源回路およびそれを用いた非接触ICカードに関する。

【0002】

【従来の技術】通常、アナログ回路やデジタル回路等の電子回路は、電源電圧を印加することにより作動する。このときに回路に流れる電流は、回路動作により異なる。特に、CPUやロジック回路、メモリ等のデジタル回路においては、電流変動が大きい。このような電流変動は、電源ノイズや電源電圧変動となって現れる。以下に、電源ノイズが発生するメカニズムについて説明する。

【0003】図11は、従来の半導体集積回路の構成を示す図である。この半導体集積回路3は、デジタル回路300とアナログ回路310とからなり、デジタル回路300はCPU301やメモリ302からなる。この半導体集積回路3には、外部からインダクタL1を通じて電源電圧VDDが与えられている。インダクタL1は、配線やボンディングワイヤ等により生じる寄生インダクタであり、その値は例えば数nF程度である。このとき、チップ(半導体集積回路)内の内部電源電圧はVDD1となる。

【0004】ここで、デジタル回路300とアナログ回路310とにより消費される電流I1が図12(b)に示すように変化した場合を考えると、チップ内の電源電圧VDD1は図12(a)に示すように、電流I1の変化点で変動を起こす。

【0005】このような電源ノイズは、アナログ回路310の回路動作には大きく影響する。例えば、ヒステリシス特性を有するコンパレータの場合には、電源電圧VDD1の変動によって比較値の極性が変わり、誤動作を引き起こすこともある。また、増幅器においても、電源電圧変動成分が付加されて信号の品質が劣化するという問題がある。以下に、アナログ回路の誤動作や特性劣化について、具体例を示す。

【0006】図13は、ヒステリシス特性を有するコンパレータの入出力特性を示す図である。一般に、コンパレータは、基準電圧に対して入力電圧が高いときにHIGH状態になり、基準電圧に対して入力電圧が低いときにLOW状態になる。これに対して、ヒステリシス特性を有するコンパレータにおいては、図13に示すように、入力電圧(入力信号Vin)が基準電圧Vref1に対してオフセット電圧を加えたレベルVH以上になると出力信号VoutがHIGH状態になり、入力電圧(入力信号Vin)が基準電圧Vref1に対してオフセット電圧を引いたレベルVL以下になると出力信号VoutがLOW状態になる。ここで、ヒステリシス特性を有するコンパレータの出力がHIGH状態であり、入力電圧が基準電圧Vref1と等しい場合を考える。この場合に、電源ノイズにより入力電圧がVL以下に下がったとすると、コンパレータの出力はHIGH状態からLOW状態になり、元の値(HIGH状態)に戻ることはない。

【0007】このような問題を解決するために、従来から、アナログ回路とデジタル回路の電源を分離したり、チップ内で電源電圧VDD1とグランドVSS間に容量Cpassを形成して電源電圧変動を抑制する方法が用いられてきた。

【0008】

【発明が解決しようとする課題】しかしながら、上述したような方法では、チップのピン(端子)数の増加や、チップ内に形成される容量の面積増大を招く。Cpassの値としては1μF以上が望まれるが、チップ内で形成可能な容量値は標準CMOSプロセスで1nF程度であり、回路の大きな負荷変動に対しては効果があまり得られない。

【0009】本発明は、このような従来技術の課題を解決するためになされたものであり、デジタル回路等の負荷変動によって生じる電流変動分を補償することにより、電源ノイズおよび電源電圧変動を抑制し、アナログ回路等、電源ノイズや電源電圧変動に影響を受け易い回路の誤動作や信号の品質劣化を抑制することができる高性能な電源回路および非接触ICカードを提供することを目的とする。

【0010】

【課題を解決するための手段】本発明の電源回路は、第1の電子回路に供給される第1の電源電圧と第2の電子回路に供給される第2の電源電圧との間に接続され、該第1の電源電圧部から該第2の電源電圧部に流れる電流をモニタするためのモニタ端子を有する電流検出回路と、該第1の電源電圧と該モニタ端子とに接続され、モニタした電流によって該第1の電源電圧部からグランドに流れる補償電流を制御して、該第2の電子回路の負荷変動によって生じる電流変動分を補償する電流補償回路とを備えており、そのことにより上記目的が達成される。

【0011】上記構成によれば、電流検出回路を用いて第2の電源電圧部に流れる電流をモニタすることにより、デジタル回路等の負荷変動によって生じる電流変動を検出し、その電流変動分を電源補償回路を用いて補償することにより、電源ノイズおよび電源電圧変動を抑制し、アナログ回路等、電源ノイズや電源電圧変動に影響を受け易い回路の誤動作や信号の品質劣化を抑制し、低ノイズで高性能な電源回路を実現することができる。

【0012】前記電流検出回路は、演算増幅器とトランジスタと2つの抵抗とを備えたリニアレギュレータを有し、該トランジスタは、ソースが前記第1の電源電圧に接続され、ゲートが該演算増幅器の出力端子に接続されると共に、ドレインが前記第2の電源電圧に接続され、該2つの抵抗は、該第2の電源電圧とグランドとの間に直列に接続されると共に、該2つの抵抗の接続点が該演算増幅器の非反転入力端子に接続され、該演算増幅器は、反転入力端子が基準電圧に接続されると共に、出力端子が前記モニタ端子として機能する構成としてもよい。

【0013】上記構成によれば、後述する実施の形態1に示すように、リニアレギュレータを用いてデジタル回路等の負荷変動によって生じる電流変動分をモニターすることが可能である。

【0014】前記電流検出回路は、前記第1の電源電圧と前記第2の電源電圧との間に接続された抵抗を有し、該第2の電源電圧側にモニタ端子を有する構成としてもよい。

【0015】上記構成によれば、後述する実施の形態2に示すように、電流検出回路を用いてデジタル回路等の負荷変動によって生じる電流変動分をモニターすることが可能である。

【0016】前記電流補償回路は、所定の電流と前記モニタ端子によって制御される電流との差電流を生成する引き算回路と、該差電流に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する構成としてもよい。

【0017】上記構成によれば、後述する実施の形態1に示すように、デジタル回路等の電流変動分を電源補償回路を用いて補償することが可能である。

【0018】前記電流補償回路は、参照電圧を生成する参照電圧発生回路と、該参照電圧と前記モニタ端子の電圧との差電圧に比例した差電流と所定の電流との和を生成する差動増幅回路と、該差電流と所定の電流との和に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する構成としてもよい。

【0019】上記構成によれば、後述する実施の形態2に示すように、デジタル回路等の電流変動分を電源補償回路を用いて補償することが可能である。

【0020】前記第1の電源電圧はアナログ回路に接続されるものであってもよい。

【0021】上記構成によれば、電源変動に影響され易いアナログ回路の誤動作や信号の品質劣化を抑制することが可能である。

【0022】前記第2の電源電圧はデジタル回路に接続されるものであってもよい。

【0023】上記構成によれば、電流変動が大きいデジタル回路等の負荷変動によって生じる電流変動を検出し、その電流変動分を電源補償回路を用いて補償することが可能である。

【0024】前記電流回路は、第4の抵抗を介してグランドに前記補償電流を流す構成としてもよい。

【0025】上記構成によれば、電流回路に設けられたトランジスタのばらつき等によって不必要に流れる電流を抑制することが可能である。

【0026】前記第1の電源電圧部から前記第2の電源電圧部に流れる電流と、該第1の電源電圧部からグランドに流れる前記補償電流の和が一定であるのが好ましい。

【0027】上記構成によれば、第2の電源電圧部に流れる電流変動分を補償して電源ノイズを抑制することができる。なお、補償電流と第2の電源電圧部に流れる電流の和は一定でなくてもよく、その場合には、電流変動分の一部を補償して電源ノイズの低減を図ることが可能である。

【0028】本発明の非接触ICカードは、コイルアンテナと、同調容量と充電容量と整流回路とアナログ回路とデジタル回路と本発明の電源回路とを備えた半導体集積回路とを有し、該コイルアンテナは、該同調容量と並列に接続されて該整流回路の入力に接続され、該整流回路は、出力が該充電容量に接続されて、該アナログ回路に供給される第1の電源電圧を生成し、該電源回路は、該第1の電源電圧から、該デジタル回路に供給される第2の電源電圧を生成し、そのことにより上記目的が達成される。

【0029】上記構成によれば、デジタル回路等の負荷変動によりアナログ回路等の誤動作や信号の品質劣化が生じるのを抑制し、高性能な非接触ICカードを実現することが可能である。

【0030】前記アナログ回路は復調回路を備えている構成としてもよい。

【0031】上記構成によれば、後述する実施の形態3に示すように、復調回路を有する高性能な非接触ICカードを実現することが可能である。

【0032】前記半導体集積回路は、前記同調容量と並列に接続されて該整流回路の入力に接続される変調回路をさらに備えている構成としてもよい。

【0033】上記構成によれば、後述する実施の形態4に示すように、変調回路を有する高性能な非接触ICカードを実現することが可能である。

【0034】前記変調回路は、変調信号により回路インピーダンスを変調させる構成としてもよい。

【0035】上記構成によれば、後述する実施の形態4に示すように、全波整流器を有する高性能な非接触ICカードを実現することが可能である。

【0036】前記整流回路は全波整流回路である構成としてもよい。

【0037】上記構成によれば、後述する実施の形態4に示すように、全波整流器を有する高性能な非接触ICカードを実現することが可能である。なお、整流回路としては、半波整流回路を用いてもよく、その場合には、半波整流器を有する高性能な非接触ICカードを実現することが可能である。

【0038】

【発明の実施の形態】以下に、本発明の実施の形態について、図面を参照しながら説明する。なお、以下の図において、同様の機能を有する構成要素については、従来技術と同じ符号を付してその説明を省略する。

【0039】(実施の形態1)図1は実施の形態1に係る電源回路の構成を示す図である。この電源回路1は、電流検出回路500と電流補償回路400とを有している。デジタル回路300はデジタル電源電圧DVDDを電源とし、アナログ回路310はアナログ電源電圧AVDDを電源としている。

【0040】電流検出回路500はリニアレギュレータ200により実現され、リニアレギュレータ200は、抵抗R1、R2と、演算増幅器210と、pMOSトランジスタM1とにより構成されている。トランジスタM1のソースはアナログ電源電圧AVDDに接続され、ゲートは演算増幅器210の出力端子に接続され、ドレインはデジタル電源電圧DVDDに接続されている。演算増幅器210の出力端子は、デジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニタするモニタ端子(モニタ電圧Va)となっている。抵抗R1は、デジタル電源電圧DVDDと演算増幅器210の非反転入力端子に接続され、抵抗R2は、グランドVSSと演算増幅器210の非反転入力端子に接続されている。

【0041】電流補償回路は400は、引き算回路410と電流回路420とにより構成されている。引き算回路410は、所定の電流源IcとトランジスタM2、M3とにより構成されている。電流源Icは、グランドVSSとトランジスタM2、M3のドレインとに接続され、トランジスタM2、M3のソースはアナログ電源電圧AVDDに接続され、トランジスタM2のゲートはリニアレギュレータ200のモニタ端子(モニタ電圧Va)に接続され、トランジスタM3のゲートとドレインとは接続されて電流回路420の制御電圧Vcとなっている。電流回路420は、トランジスタM4により構成され、トランジスタM4のソースはアナログ電源電圧AVDDに接続され、ドレインはグランドVSSに接続され、ゲートは制御電圧Vcに接続されている。

【0042】ここで、上記演算増幅器210の反転入力端子に基準電圧Vref2(外部から供給される)を接続すると、デジタル電源電圧DVDDは、 DVDD=Vref×(R1+R2)/R2 ・・・(1)

のように表される。ここで、抵抗R1、R2に流れる電流をI1に比べて非常に小さくなるように選ぶと、トランジスタM2、M3、M4に流れる電流I2、I3、I4は、各々、I2=n×I1 ・・・(2)

I3=Ic−n×I1 ・・・(3)

I4=m×(Ic−n×I1) ・・・(4)

のように表される。従って、引き算回路410では所定の電流Icとモニタ端子(モニタ電圧Va)により制御される電流I2との差電流I3が生成され、電流回路420には差電流I3に比例した電流I4がアナログ電源電圧AVDD部からグランドVSSに補償電流として流れる。なお、上記式において、nはトランジスタM1とトランジスタM2のサイズ比であり、mはトランジスタM3とM4のサイズ比である。また、I1はトランジスタM1に流れる電流である。例えばトランジスタM1、M2、M3、M4のゲート幅をW1、W2、W3、W4とし、ゲート長をL1、L2、L3、L4とすると、nとmは、各々、n=(W2×L1)/(L2×W1) ・・・(5)

m=(W4×L3)/(L4×W3) ・・・(6)

のように表される。

【0043】そして、Ic=n×I0、m=1/nとすると、トランジスタM4に流れる電流I4は、I4=I0−I1となる。ここで、デジタル回路300に流れる電流がΔI1だけ増え、I1+ΔI1となったとすると、I4はI0−I1−ΔI1となり、デジタル回路300に流れる電流の変動分を補償する電流が電流回路420に流れることになる。アナログ電源電圧AVDD部からアナログ回路310に流れる電流は、図1の場合、デジタル回路300に流れる電流I1、引き算回路410に流れる電流Ic、電流補償回路420に流れる電流(I0−I1)の和(I0+Ic)となる。その結果、アナログ電源電圧AVDD部から流れる電流は、アナログ回路310に流れる電流を除けば、一定となる。これは、デジタル回路の負荷変動によって生じるアナログ電源電圧AVDDのノイズを低減することを意味する。

【0044】以上のことから、本実施形態では、電源電圧変動を抑制するためにデジタル回路とアナログ回路の電源を分離する必要が無いため、チップのピン数を削減することができる。また、電源電圧変動を抑制するためにチップ内でデジタル電源電圧とグランド間に大きな容量を形成する必要が無いため、チップ内に形成される容量の面積増大を防ぐことができる。その結果として、チップ実装が容易で電源ノイズの低い高性能な電源回路を実現することができる。

【0045】(実施の形態2)図2は実施の形態2に係る電源回路の構成を示す図である。この電源回路1は、電流検出回路500と電流補償回路400とを有している。デジタル回路300はデジタル電源電圧DVDDを電源とし、アナログ回路310はアナログ電源電圧AVDDを電源としている。

【0046】電流検出回路500は、抵抗R10をアナログ電源電圧AVDDとデジタル電源電圧DVDDとの間に接続して構成され、デジタル電源電圧DVDD側に、デジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニタするモニタ端子(モニタ電圧Va)を有している。

【0047】電流補償回路400は、参照電圧発生回路440、差動増幅回路430、電流回路420とにより構成されている。参照電圧発生回路440は、抵抗R11と抵抗R12とがアナログ電源電圧AVDDとグランドVSSとの間に直列に接続され、抵抗R11と抵抗R12の抵抗分割によって生成される電圧を参照電圧Vref3として出力する。差動増幅回路430は、nMOSトランジスタM10、M11とpMOSトランジスタM12、M13と電流源I10とにより構成されている。電流源I10は、グランドVSSとトランジスタM10、M11のソースとに接続され、トランジスタM10のドレインにはトランジスタM12のドレインが接続され、トランジスタM11のドレインにはトランジスタM13のドレインが接続されている。トランジスタM12とトランジスタM13はダイオード接続(ソースとゲートを接続してカソードとし、ドレインをアノードとした構造)され、トランジスタM11のドレインとトランジスタM13のゲートとドレインが電流回路420の制御電圧Vcに接続されている。トランジスタM12、M13のソースはアナログ電源電圧AVDDに接続され、トランジスタM11のゲートはモニタ端子(モニタ電圧Va)に接続され、トランジスタM10のゲートは参照電圧Vref3に接続されている。電流回路420は、トランジスタM4により構成され、トランジスタM4のソースはアナログ電源電圧AVDDに接続され、ドレインはグランドVSSに接続され、ゲートは制御電圧Vcに接続されている。この電流回路420は、差増増幅回路430からの制御電圧Vcによってアナログ電源電圧AVDD部からグランドVSSに流れる電流をコントロールする。

【0048】ここで、デジタル回路300において最大の電流を消費するときの負荷抵抗をRmaxとし、差動増幅器の電流ゲインをAとする。そして、抵抗R10〜R12とRmaxの関係を (R10/(Rmax+R10))/2=R11/(R11+R12)

・・・(7)

のように設定する。例えば、Rmax=90Ω、R10=10Ω、R11=10kΩ、R12=190kΩとする。このとき、参照電圧発生回路430における消費電流を小さくするために、R11/R10=10000とする。

【0049】そして、アナログ電源電圧AVDDを3Vとすると、参照電圧Vref3は2.85Vとなり、デジタル負荷最大時の電圧DVDDは2.7Vとなり、デジタル回路300の最大負荷電流は30mAとなる。ここで、トランジスタM13とトランジスタM4のミラー比(実施の形態1のサイズ比と同じ)をMとし、差増増幅回路430の電流ゲインをAとすると、トランジスタM4に流れる電流I4は、 I4=M×(A×(DVDD−Vref3)+I10/2) ・・・(8)

のように表される。これは、モニタ電圧DVDDと参照電圧Vref3の差電圧により流れる電流(A×(DVDD−Vref3)と所定の電流I10/2の和に比例した電流がI4に流れることを意味する。

【0050】ここで、A=0.001、I10=300μA、M=100とすると、デジタル回路の負荷電流が最大(デジタル回路300に流れる負荷電流が30mA)のときには電流回路420は0mAとなり、デジタル回路の負荷電流が最少(デジタル回路300に流れる負荷電流が0mA)のときには電流回路420は30mAとなる。その結果、AVDDからアナログ回路310に流れる電流を除けば、デジタル回路の負荷変動によらず、常に一定の電流30mAが流れることになる。なお、差動増幅回路430および参照電圧発生回路440に流れる電流は、電流回路420とデジタル回路300に流れる電流に比べて非常に小さいので、無視することができる。よって、電源電圧AVDD部にデジタル回路の負荷変動によるノイズが発生するのを抑制することができ、高性能な電源回路を実現することができる。

【0051】以上のことから、本実施形態では、電源電圧変動を抑制するためにデジタル回路とアナログ回路の電源を分離する必要が無いため、チップのピン数を削減することができる。また、電源電圧変動を抑制するためにチップ内でデジタル電源電圧とグランド間に大きな容量を形成する必要が無いため、チップ内に形成される容量の面積増大を防ぐことができる。その結果として、チップ実装が容易で電源ノイズの低い高性能な電源回路を実現することができる。

【0052】なお、本発明は、上記実施の形態1および実施の形態2で説明した電流検出回路500および電流補償回路400の具体例に限定されるものではない。図3R>3に示すように、電流検出回路500によりデジタル電源電圧DVDD部に流れる電流(=デジタル回路300に流れる電流)をモニターし、電流補償回路400によってアナログ電源電圧AVDD部からグランドVSSに流れる補償電流を制御してデジタル回路300の電流変動分を補償することができる電源回路であれば、全て本発明の範囲に含まれる。

【0053】補償電流とデジタル電源電圧DVDD部に流れる電流の和を一定としたが、補償電流とデジタル電源電圧DVDD部に流れる電流の和は一定でなくてもよく、デジタル電源電圧DVDD部に流れる電流の変動分の一部を電流補償回路400によって補償することによっても、電源ノイズの低減を図ることができる。

【0054】上記実施の形態1および実施の形態2では、電流回路420においてトランジスタM4のドレインをグランドVSSに接続したが、図4に示すように、トランジスタM4のドレインを抵抗R3を介してグランドVSSに接続してもよい。この場合には、トランジスタM4の素子特性のばらつき等によって不必要に流れる電流を抑制することができる。

【0055】さらに、上記実施の形態1および実施の形態2では、デジタル回路300とアナログ回路310とに区別したが、デジタル回路の代わりに電源電圧変動に影響されにくい回路を用い、電源電圧変動に影響され易い回路をアナログ回路の代わりに用いた構成としてもよい。

【0056】以上のように、本発明は、高性能な電源回路を得ることに対して大いに寄与するものであり、極めて有用なものである。

【0057】(実施の形態3)図5は実施の形態3に係る非接触ICカードの構成を示す図である。この非接触ICカード4は、コイルアンテナL2と半導体集積回路3とを有している。半導体集積回路は、同調容量C3と充電容量C4と整流回路2とアナログ回路310とデジタル回路300と電源回路1とにより構成されている。同調容量C3とコイルアンテナL2とは並列に接続されて整流回路2の入力に接続されている。整流回路の出力は充電容量C4に充電され、アナログ回路310の電源電圧AVDDとなる。アナログ回路310は、電源電圧AVDDから受信信号を取り出す復調回路311を備えている。電源回路1は、電源電圧AVDDからデジタル回路300に供給される電源電圧DVDDを生成する。この電源回路1としては、上記実施の形態1および実施の形態2で説明したようなものを用いることができる。

【0058】半導体集積回路4で消費される電力と受信信号とはコイルアンテナL2により受電される。このとき、受信信号には振幅変調がかかっているものとする。そして、整流回路2としては図6に示すようなダイオードD1〜D4を用いた全波整流回路を用い、復調回路311としてはヒステリシスを有するコンパレータを用いる。コイルアンテナL2により受信された信号は、整流回路2により整流され、図7に示すような電源電圧AVDDが生成される。また、復調回路311により、電源電圧AVDDから信号成分が抽出される。このとき、復調回路311は、電源電圧AVDDが基準レベル以上に変化したときに、信号として取り出す。

【0059】ここで、デジタル回路300の電流変動が図8(a)に示すように起こったとすると、電源電圧AVDDの波形は図8(b)に点線で示すようになる。このようなデジタル回路300の電流変動(負荷変動)により、電源回路1が無い場合には、復調回路311が誤動作を引き起こし、復調信号が図8(c)の点線に示すようになる。これに対して、本実施の形態のように電源回路1を有する非接触ICカードでは、図8(b)に実線で示すようにデジタル回路300の負荷変動による電源電圧AVDDの変動を抑制することができ、その結果、図8(c)に示すように誤動作を生じずに復調することができることが分かった。

【0060】以上のことから、本実施形態では、デジタル回路の負荷変動によるアナログ回路の誤動作を低減することができ、その結果として、高性能な非接触ICカードを実現することができる。

【0061】(実施の形態4)図9は実施の形態4に係る非接触ICカードの構成を示す図である。本実施の形態と実施の形態3との相違点は、変調回路315が同調容量C3と並列に接続されて整流回路2の入力に接続されていることである。この変調回路315は、変調信号によって、半導体集積回路3のコイルアンテナL2間のインピーダンスを変調させる。

【0062】図10(a)は、図10(b)に示すような変調信号が入力された場合に、電源回路1を有する場合と電源回路1が無い場合とについて、コイルL2間のインピーダンスを示す図である。この図において、実線が電源回路1を有する場合を示し、点線が電源回路1が無い場合を示す。図10(c)に示すようにデジタル回路310で電流変動(負荷変動)が起こると、電源回路1が無い場合には、図10(a)に点線で示すように、コイルL2間のインピーダンスに影響を与える。これに対して、本実施形態のように電源回路1を有する非接触ICカードでは、図10(a)に実線で示すようにデジタル回路300の負荷変動による電源インピーダンスを一定にすることができる。

【0063】以上のことから、本実施形態では、デジタル回路の負荷変動によるアナログ回路の誤動作を低減することができ、その結果として、高性能な非接触ICカードを実現することができる。

【0064】なお、本発明は、上記実施の形態3および実施の形態4で説明した半導体集積回路3の具体例に限定されるものではない。電源回路として実施の形態1および実施の形態2で説明したような電源回路を有する非接触ICカードであれば、全て本発明の範囲に含まれる。

【0065】同調容量C3は、半導体集積回路3に形成したが、半導体チップの外部に実装しても良く、また、整流回路2またはコイルアンテナL2の寄生容量を用いてもよい。

【0066】さらに、上記実施の形態3および実施の形態4では、整流回路2として全波整流回路を用いたが、半波整流回路を用いてもよい。

【0067】以上のように、本発明は、高性能な非接触ICカードを得ることに対して大いに寄与するものであり、極めて有用なものである。

【0068】

【発明の効果】以上詳述したように、本発明によれば、電流検出回路を用いてデジタル電源電圧部等に流れる電流をモニタすることにより、デジタル回路等の負荷変動による電流変動分を検出し、その電流変動分を電源補償回路を用いて補償することにより、低ノイズで高性能な電源回路を実現することができる。

【0069】さらに、本発明によれば、本発明の電源回路を用いることにより、復調回路や変調回路を有する高性能な非接触ICカードを実現することができる。

【図面の簡単な説明】

【図1】実施の形態1に係る電源回路の構成を示す図である。

【図2】実施の形態2に係る電源回路の構成を示す図である。

【図3】本発明に係る電源回路の構成を示す図である。

【図4】実施の形態1および実施の形態2の電源回路における他の電流回路の構成を示す図である。

【図5】実施の形態3に係る非接触ICカードの構成を示す図である。

【図6】実施の形態3の非接触ICにおける整流回路の構成を示す図である。

【図7】実施の形態3において、振幅変調された信号を整流した後の波形AVDDを示す図である。

【図8】(a)は実施の形態3において、デジタル回路の消費電流を示す図であり、(b)は電源回路を有する場合と無い場合について電源電圧AVDDを示す図であり、(c)は電源回路を有する場合と無い場合について復調信号を示す図である。

【図9】実施の形態4に係る非接触ICカードの構成を示す図である。

【図10】(a)は実施の形態4において、電源回路を有する場合と無い場合についてコイルL2間のインピーダンスを示す図であり、(b)は変調信号を示す図であり、(c)はデジタル回路の消費電流を示す図である。

【図11】従来の半導体集積回路の構成を示す図である。

【図12】(a)および(b)は従来の半導体集積回路に流れる電流I1と電源電圧VDD1との関係を示す図である。

【図13】ヒステリシス特性を有するコンパレータの入出力特性を示す図である。

【符号の説明】

1 電源回路

2 整流回路

3 半導体集積回路

4 非接触ICカード

200 リニアレギュレータ

210 演算増幅器

300 デジタル回路

301 CPU

302 メモリ

310 アナログ回路

311 復調回路

315 変調回路

400 電流補償回路

410 引き算回路

420 電流回路

430 差動増幅回路

440 参照電圧発生回路

500 電流検出回路

M1、M2、M3、M4、M10、M11、M12、M13 トランジスタ

R1、R2、R3、R10、R11、R12 抵抗

Ic、I10 電流源

L1 インダクタ

L2 コイルアンテナ

C3 同調容量

C4 充電容量

D1、D2、D3、D4 ダイオード

VDD、VDD1、DVDD、AVDD 電源電圧

VSS グランド

Vref1、Vref2 基準電圧

Vref3 参照電圧

Va モニタ電圧

Vc 制御電圧

【特許請求の範囲】

【請求項1】 第1の電子回路に供給される第1の電源電圧と第2の電子回路に供給される第2の電源電圧との間に接続され、該第1の電源電圧部から該第2の電源電圧部に流れる電流をモニタするためのモニタ端子を有する電流検出回路と、該第1の電源電圧と該モニタ端子とに接続され、モニタした電流によって該第1の電源電圧部からグランドに流れる補償電流を制御して、該第2の電子回路の負荷変動によって生じる電流変動分を補償する電流補償回路とを備えている電源回路。

【請求項2】 前記電流検出回路は、演算増幅器とトランジスタと2つの抵抗とを備えたリニアレギュレータを有し、該トランジスタは、ソースが前記第1の電源電圧に接続され、ゲートが該演算増幅器の出力端子に接続されると共に、ドレインが前記第2の電源電圧に接続され、該2つの抵抗は、該第2の電源電圧とグランドとの間に直列に接続されると共に、該2つの抵抗の接続点が該演算増幅器の非反転入力端子に接続され、該演算増幅器は、反転入力端子が基準電圧に接続されると共に、出力端子が前記モニタ端子として機能する請求項1に記載の電源回路。

【請求項3】 前記電流検出回路は、前記第1の電源電圧と前記第2の電源電圧との間に接続された抵抗を有し、該第2の電源電圧側にモニタ端子を有する請求項1に記載の電源回路。

【請求項4】 前記電流補償回路は、所定の電流と前記モニタ端子によって制御される電流との差電流を生成する引き算回路と、該差電流に比例した電流を、前記第1の電源電圧部からグランドに補償電流として流す電流回路とを有する請求項1乃至請求項3のいずれかに記載の電源回路。

【請求項5】 前記電流補償回路は、参照電圧を生成する参照電圧発生回路と、該参照電圧と前記モニタ端子の電圧との差電圧に比例した差電流と所定の電流との和を生成する差動増幅回路と、該差電流と所定の電流との和に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する請求項1乃至請求項3のいずれかに記載の電源回路。

【請求項6】 前記第1の電源電圧はアナログ回路に接続される請求項1乃至請求項5のいずれかに記載の電源回路。

【請求項7】 前記第2の電源電圧はデジタル回路に接続される請求項1乃至請求項6のいずれかに記載の電源回路。

【請求項8】 前記電流回路は、第4の抵抗を介してグランドに前記補償電流を流す請求項4または請求項5に記載の電源回路。

【請求項9】 前記第1の電源電圧部から前記第2の電源電圧部に流れる電流と、該第1の電源電圧部からグランドに流れる前記補償電流の和が一定である請求項1乃至請求項8のいずれかに記載の電源回路。

【請求項10】 コイルアンテナと、同調容量と充電容量と整流回路とアナログ回路とデジタル回路と請求項1乃至請求項9のいずれかに記載の電源回路とを備えた半導体集積回路とを有し、該コイルアンテナは、該同調容量と並列に接続されて該整流回路の入力に接続され、該整流回路は、出力が該充電容量に接続されて、該アナログ回路に供給される第1の電源電圧を生成し、該電源回路は、該第1の電源電圧から、該デジタル回路に供給される第2の電源電圧を生成する非接触ICカード。

【請求項11】 前記アナログ回路は復調回路を備えている請求項10に記載の非接触ICカード。

【請求項12】 前記半導体集積回路は、前記同調容量と並列に接続されて該整流回路の入力に接続される変調回路をさらに備えている請求項10または請求項11に記載の非接触ICカード。

【請求項13】 前記変調回路は、変調信号により回路インピーダンスを変調させる請求項12に記載の非接触ICカード。

【請求項14】 前記整流回路は全波整流回路である請求項10乃至請求項13のいずれかに記載の非接触ICカード。

【請求項1】 第1の電子回路に供給される第1の電源電圧と第2の電子回路に供給される第2の電源電圧との間に接続され、該第1の電源電圧部から該第2の電源電圧部に流れる電流をモニタするためのモニタ端子を有する電流検出回路と、該第1の電源電圧と該モニタ端子とに接続され、モニタした電流によって該第1の電源電圧部からグランドに流れる補償電流を制御して、該第2の電子回路の負荷変動によって生じる電流変動分を補償する電流補償回路とを備えている電源回路。

【請求項2】 前記電流検出回路は、演算増幅器とトランジスタと2つの抵抗とを備えたリニアレギュレータを有し、該トランジスタは、ソースが前記第1の電源電圧に接続され、ゲートが該演算増幅器の出力端子に接続されると共に、ドレインが前記第2の電源電圧に接続され、該2つの抵抗は、該第2の電源電圧とグランドとの間に直列に接続されると共に、該2つの抵抗の接続点が該演算増幅器の非反転入力端子に接続され、該演算増幅器は、反転入力端子が基準電圧に接続されると共に、出力端子が前記モニタ端子として機能する請求項1に記載の電源回路。

【請求項3】 前記電流検出回路は、前記第1の電源電圧と前記第2の電源電圧との間に接続された抵抗を有し、該第2の電源電圧側にモニタ端子を有する請求項1に記載の電源回路。

【請求項4】 前記電流補償回路は、所定の電流と前記モニタ端子によって制御される電流との差電流を生成する引き算回路と、該差電流に比例した電流を、前記第1の電源電圧部からグランドに補償電流として流す電流回路とを有する請求項1乃至請求項3のいずれかに記載の電源回路。

【請求項5】 前記電流補償回路は、参照電圧を生成する参照電圧発生回路と、該参照電圧と前記モニタ端子の電圧との差電圧に比例した差電流と所定の電流との和を生成する差動増幅回路と、該差電流と所定の電流との和に比例した電流を、前記第1の電源電圧からグランドに補償電流として流す電流回路とを有する請求項1乃至請求項3のいずれかに記載の電源回路。

【請求項6】 前記第1の電源電圧はアナログ回路に接続される請求項1乃至請求項5のいずれかに記載の電源回路。

【請求項7】 前記第2の電源電圧はデジタル回路に接続される請求項1乃至請求項6のいずれかに記載の電源回路。

【請求項8】 前記電流回路は、第4の抵抗を介してグランドに前記補償電流を流す請求項4または請求項5に記載の電源回路。

【請求項9】 前記第1の電源電圧部から前記第2の電源電圧部に流れる電流と、該第1の電源電圧部からグランドに流れる前記補償電流の和が一定である請求項1乃至請求項8のいずれかに記載の電源回路。

【請求項10】 コイルアンテナと、同調容量と充電容量と整流回路とアナログ回路とデジタル回路と請求項1乃至請求項9のいずれかに記載の電源回路とを備えた半導体集積回路とを有し、該コイルアンテナは、該同調容量と並列に接続されて該整流回路の入力に接続され、該整流回路は、出力が該充電容量に接続されて、該アナログ回路に供給される第1の電源電圧を生成し、該電源回路は、該第1の電源電圧から、該デジタル回路に供給される第2の電源電圧を生成する非接触ICカード。

【請求項11】 前記アナログ回路は復調回路を備えている請求項10に記載の非接触ICカード。

【請求項12】 前記半導体集積回路は、前記同調容量と並列に接続されて該整流回路の入力に接続される変調回路をさらに備えている請求項10または請求項11に記載の非接触ICカード。

【請求項13】 前記変調回路は、変調信号により回路インピーダンスを変調させる請求項12に記載の非接触ICカード。

【請求項14】 前記整流回路は全波整流回路である請求項10乃至請求項13のいずれかに記載の非接触ICカード。

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図11】

【図13】

【図9】

【図10】

【図12】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図11】

【図13】

【図9】

【図10】

【図12】

【公開番号】特開2002−142356(P2002−142356A)

【公開日】平成14年5月17日(2002.5.17)

【国際特許分類】

【出願番号】特願2000−334025(P2000−334025)

【出願日】平成12年10月31日(2000.10.31)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

【公開日】平成14年5月17日(2002.5.17)

【国際特許分類】

【出願日】平成12年10月31日(2000.10.31)

【出願人】(000005821)松下電器産業株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]