電源回路及びその制御方法

【課題】 煩雑な制御を必要とせずに、ボルテージレギュレータの入出力電位差を最適化できる電源回路及びその制御方法を提供する。

【解決手段】 電源回路304は、バッテリ300の出力電圧を昇圧しまたは降圧するDCDCコンバータ301と、前記DCDCコンバータ301の出力電圧を降圧するボルテージレギュレータ302と、前記ボルテージレギュレータ302の出力電圧に相関する値に応じて前記DCDCコンバータ301の出力電圧の昇圧値または降圧値を設定する電圧設定手段303とを備える。

【解決手段】 電源回路304は、バッテリ300の出力電圧を昇圧しまたは降圧するDCDCコンバータ301と、前記DCDCコンバータ301の出力電圧を降圧するボルテージレギュレータ302と、前記ボルテージレギュレータ302の出力電圧に相関する値に応じて前記DCDCコンバータ301の出力電圧の昇圧値または降圧値を設定する電圧設定手段303とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、バッテリの電圧を定電圧化する電源回路及びその制御方法に関し、詳しくは、出力電圧の設定に際して煩雑な制御を必要としない電源回路及びその制御方法に関する。

【背景技術】

【0002】

一般的にバッテリ駆動の電子機器における電源回路は、バッテリと、そのバッテリの出力電圧(端子電圧ともいう)を安定化する安定化回路とにより構成されている。

【0003】

最も単純な安定化回路は、たとえば、下記の特許文献1に記載されているリニアレギュレータなどの「ボルテージレギュレータ」である。ボルテージレギュレータは、入力電圧を降下(降圧)させて安定化した電圧を出力するが、入力電圧の降下分をジュール熱として放出するため、電力損失が大きいという欠点がある。

【0004】

一方、スイッチング電源とも呼ばれるスイッチングレギュレータは、入力電力から希望の出力電力を得る電力変換装置において、電力を変換・調整するためにスイッチング素子(電気回路の一部をON/OFFできる素子)を用いた電源装置の総称であり、その中でも特に、直流電力を別の直流電力に変換するものを「DCDCコンバータ」といい、電圧降下をジュール熱として放出するボルテージレギュレータとは異なり、電力損失を少なくできるため、高精度・高効率を得ることができるという利点がある。DCDCコンバータの関連技術としては、たとえば、特許文献2や特許文献3に記載のものがある。

【0005】

特許文献2には、昇降圧DCDCコンバータにおいて、降圧および昇圧を往来するような出力電圧の変動を抑制することができ、出力電圧を安定させることができる技術が記載されている。また、特許文献3には、給電切り換えする電圧を低く抑えて、昇圧変換回路での無駄な変換損失を低減して省電力効果を向上させることができる技術が記載されている。

【0006】

このように、DCDCコンバータは電力損失を少なくできるという利点があることから、前記のボルテージレギュレータの代わりにDCDCコンバータを用いてバッテリの電圧を安定化することが考えられるが、すなわち、「バッテリ→DCDCコンバータ→負荷」という構成が考えられるが、この構成では、DCDCコンバータの出力に現れるリップルノイズ(スイッチングに伴う微小な振動成分)の影響で良質な出力電圧が得られないという課題がある。このため、一般的には、リップルノイズをドロッパ(ボルテージレギュレータ)で押さえ込むという構成、すなわち、「バッテリ→DCDCコンバータ→ボルテージレギュレータ→負荷」という組み合わせの構成がとられ、とりわけ、ノイズにシビアなデバイスの場合にはそのような構成がとられることが多い。

【0007】

DCDCコンバータとボルテージレギュレータとの組み合わせに関する技術としては、たとえば、下記の特許文献4や特許文献5に記載のものがある。

【0008】

特許文献4には、補助電源(リチウムイオン2次電池)の出力電圧を昇圧する昇圧部(DCDCコンバータ)と、昇圧部の出力を降圧して負荷に供給する降圧(ボルテージレギュレータ)とを備えた電源装置の技術が記載されている。また、特許文献5には、昇圧DCDCコンバータとボルテージレギュレータとを備えた定電圧電源装置の技術が記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−278311号公報

【特許文献2】特開2008−092779号公報

【特許文献3】特開2009−273249号公報

【特許文献4】特開平10−0333759号公報

【特許文献5】特開2007−336795号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

上記のとおり、ボルテージレギュレータは電力損失が大きいという欠点があり、また、DCDCコンバータはリップルノイズの影響で良質な出力電圧が得られないという欠点があることから、一般的にはそれらの組み合わせ、つまり、DCDCコンバータとボルテージレギュレータとの組み合わせからなる構成(以下、組み合わせ型という)とされることが多い。

【0011】

しかしながら、このような組み合わせ型は、ボルテージレギュレータの入出力電位差を最適化するために、ボルテージレギュレータの出力電圧に応じてDCDCコンバータの出力電圧を制御しなければならず、制御が煩雑になるという問題点がある。また、出力可変型(プログラマブル型)のボルテージレギュレータの場合は、DCDCコンバータの出力電圧の制御に加えて、ボルテージレギュレータの出力電圧の制御も行わなければならず、さらに制御が煩雑になるという問題点がある。

【0012】

そこで、本発明の目的は、煩雑な制御を必要とせずに、ボルテージレギュレータの入出力電位差を最適化できる電源回路及びその制御方法を提供することにある。

【課題を解決するための手段】

【0013】

本発明の電源回路は、バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータと、前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定手段とを備えたことを特徴とする。

本発明の電源回路の制御方法は、バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする。

【発明の効果】

【0014】

本発明によれば、煩雑な制御を必要とせずに、ボルテージレギュレータの入出力電位差を最適化できる電源回路及びその制御方法を提供することができる。

【図面の簡単な説明】

【0015】

【図1】基本形の電源回路の構成図である。

【図2】基本型の電源回路1における電圧制御のフローを示す図である。

【図3】基本型の電源回路1における電圧出力特性図である。

【図4】実施形態に係る電源回路の構成図である。

【図5】実施形態に係る電源回路100における電圧制御のフローを示す図である。

【図6】実施形態に係る電源回路100における電圧出力特性図である。

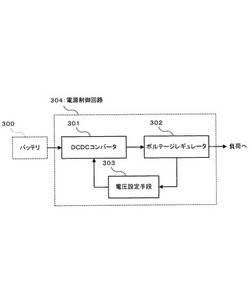

【図7】付記1の構成図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態を、図面を参照しながら説明する。

1.基本形の電源回路:

まず、実施形態を説明する前に、実施形態を適用しない基本形の電源回路について説明する。なお、基本形の電源回路とは、前記の問題点、すなわち、ボルテージレギュレータの入出力電位差を最適化する際に煩雑な制御を行う必要がある電源回路のことをいう。

図1は、基本形の電源回路の構成図である。この図において、電源回路1は、一端がグランド(GND)に接続され、他端がバッテリ電源線2に接続されたリチウムイオン2次電池などのバッテリ3と、このバッテリ3に並列に接続されたバイパスコンデンサ4と、バッテリ3の出力電圧(バッテリ電源線2とGNDの間の電圧;端子電圧ともいう)を任意の電圧に昇圧もしくは降圧する昇・降圧型のDCDCコンバータ5と、DCDCコンバータ5の出力とGNDとの間に接続された第1の位相補償用コンデンサ6と、DCDCコンバータ5の出力と負荷(任意の電子回路等)7との間に挿入されたボルテージレギュレータ8と、ボルテージレギュレータ8の出力とGNDとの間に接続された第2の位相補償用コンデンサ9と、DCDCコンバータ5やボルテージレギュレータ8の動作を制御する電源制御コントローラ10とを備えている。

【0017】

バッテリ3の出力電圧を「Vbat」、DCDCコンバータ5の出力電圧(ボルテージレギュレータ8の入力電圧でもある)を「Vddout」、ボルテージレギュレータ8の出力電圧を「Vregout」ということにする。

【0018】

<DCDCコンバータ5の構成>

DCDCコンバータ5は、4つのFET11〜14と、コイル15と、FET11〜14のオンオフを制御するDCDCコントローラ16と、スイッチング用の発振回路(OSC)17と、VddoutをモニタしてDCDCコントローラ16にフィードバックする分圧抵抗ラダー18及び分圧抵抗19と、補正用のエラーアンプ20と、所定の基準電圧Vr1を発生する基準電圧発生部21とから構成されている。

【0019】

このような構成を有するDCDCコンバータ5は、先にも述べたように、バッテリ3の端子電圧を昇圧もしくは降圧し、任意の電圧(Vddout)に変換して出力する。

【0020】

DCDCコンバータ5は、昇圧時と降圧時の二つの態様で動作し、昇圧時には、FET11をオンにしたまま、発振回路17の発振周期でFET13をオンオフし、コイル15に流れる電流をチョッピングしてコイル15に電流を蓄え、コイル15に蓄えた電流をFET14を介して第1の位相補償用コンデンサ6に吐き出すことによって所望の出力電圧(Vddout)を得るという動作を繰り返す。このとき、FET14は、FET13がオフの時にコイル15の電流を還流するためのスイッチとして働き、FET14とFET13は逆相で動作する。

【0021】

一方、降圧時には、発振回路17の発振周期でFET11をオンオフし、コイル15に流れる電流をチョッピングしてコイル15に電流を蓄え、コイル15に蓄えた電流をFET14を介して第1の位相補償用コンデンサ6に吐き出すことによって所望の出力電圧(Vddout)を得るという動作を繰り返す。このとき、FET12は、FET11がオフの時にコイル15の電流を還流するためのスイッチとして働き、FET12とFET11は逆相で動作する。

【0022】

DCDCコントローラ16は、昇圧時または降圧時におけるDCDCコンバータ5の出力電圧(Vddout)をエラーアンプ20の出力電圧に従って制御するものであり、このDCDCコントローラ16には、エラーアンプ20の出力電圧が加えられている。

【0023】

エラーアンプ20はオペアンプで構成されており、オペアンプ(エラーアンプ20)の反転入力(−入力)には、分圧抵抗ラダー18と分圧抵抗19とからなる抵抗分圧回路の分圧電圧Vaが加えられ、非反転入力(+入力)には基準電圧発生部21で作られた基準電圧Vr1が加えられている。

【0024】

一般にオペアンプは、反転入力と非反転入力の差分に相当する値を出力するので、かかるオペアンプ(エラーアンプ20)の出力電圧に従ってVddoutの値を制御するDCDCコントローラ16は、要するに、基準電圧Vr1に対応した一定の電圧となるようにVddoutの値を制御する。

【0025】

エラーアンプ20の反転入力(−入力)に加えられる分圧電圧Vaは、分圧抵抗ラダー18の値に応じて変化し、分圧抵抗ラダー18の値は、電源制御コントローラ10の制御に従って増減変化する仕組みになっている。

【0026】

したがって、DCDCコンバータ5は、その出力電圧(Vddout)を、電源制御コントローラ10の制御に従って任意に変化させることができるプログラム型の定電圧回路であり、且つ、バッテリ3の電圧を昇圧または降圧することができる昇・降圧型の定電圧回路である。

【0027】

<ボルテージレギュレータ8の構成>

ボルテージレギュレータ8は、ドライバ用のFET22と、ボルテージレギュレータ8の出力電圧(Vregout)をモニタするための分圧抵抗ラダー23及び分圧抵抗24と、エラーアンプ26と、基準電圧Vr2を発生する基準電圧発生部27とから構成されており、FET22のソース−ドレイン間を流れる電流(以下、iDS)を制御することにより、DCDCコンバータ5の出力電圧(Vddout)を降圧し、所定の直流電圧(Vregout)に安定化して出力する。

【0028】

FET22のiDSは、FET22のゲート電位に応じて変化し、FET22のゲート電位は、エラーアンプ25の出力電圧で与えられる。

【0029】

エラーアンプ25はオペアンプで構成されており、このオペアンプ(エラーアンプ25)の非反転入力(+入力)には、分圧抵抗ラダー23と分圧抵抗24とからなる抵抗分圧回路の分圧電圧Vbが加えられ、反転入力(−入力)には基準電圧発生部26で作られた基準電圧Vr2が加えられている。

【0030】

エラーアンプ25の非反転入力(+入力)に加えられる分圧電圧Vbは、分圧抵抗ラダー23の値に応じて変化し、分圧抵抗ラダー23の値は、電源制御コントローラ10の制御に従って増減変化する仕組みになっている。

【0031】

したがって、ボルテージレギュレータ8は、その出力電圧(Vregout)を、電源制御コントローラ10の制御に従って任意に変化させることができるプログラム型の定電圧回路であり、且つ、Vddoutを超えない電圧(vregout)に定電圧化できる降圧型の定電圧回路である。

【0032】

なお、以上の例では、DCDCコンバータ5を昇・降圧型としたが、常にバッテリ3の端子電圧以下で使用するのであれば、降圧型であってもよく、この場合、FET13は不要である。

【0033】

さて、図1に示す基本型の電源回路1における電圧制御は、もっぱら電源制御コントローラ10で行っている。

【0034】

図2は、基本型の電源回路1における電圧制御のフローを示す図である。この図において、電源制御コントローラ10は、まず、DCDCコンバータ5の出力電圧(Vddout)の設定(ステップS11)と、ボルテージレギュレータ8の初期の出力電圧(Vregout)の設定(ステップS12)とを行い、次いで、DCDCコンバータ5とボルテージレギュレータ8の動作をオンにする(ステップS13、ステップS14)。

【0035】

そして、ボルテージレギュレター8の出力電圧(Vregout)の変更ありか否かを判定し(ステップS15)、変更ありでなければ、そのままステップS15を繰り返し、変更ありであれば、次に、ボルテージレギュレータ8の出力電圧(Vregout)の変更方向(上げる/下げる)を判定し(ステップS16)、以降、その変更方向に対応した制御を実行した後、再び、ステップS15に復帰する。

【0036】

<上げる場合の制御>

ボルテージレギュレータ8の出力電圧(Vregout)の変更方向が「上げる」場合は、DCDCコンバータ5の出力電圧(Vddout)を上げるための設定(ステップS17;分圧抵抗ラダー18の値を変更する)と、ボルテージレギュレータ8の出力電圧(Vregout)を上げるための設定(ステップS18;分圧抵抗ラダー23の値を変更する)とを行う。

【0037】

<下げる場合の制御>

ボルテージレギュレータ8の出力電圧(Vregout)の変更方向が「下げる」場合は、DCDCコンバータ5の出力電圧(Vddout)を下げるための設定(ステップS19;分圧抵抗ラダー18の値を変更する)と、ボルテージレギュレータ8の出力電圧(Vregout)を下げるための設定(ステップS20;分圧抵抗ラダー23の値を変更する)とを行う。

【0038】

このような電圧制御において、DCDCコンバータ5の出力電圧(Vddout)は、ボルテージレギュレータ8の出力電圧(Vregout)に、そのボルテージレギュレータ8の最小入出力電圧差(以下、Vsat)を加えた以上の電圧があればよい。つまり、「Vddout≧Vregout+Vsat」であればよい。

【0039】

図3は、基本型の電源回路1における電圧出力特性図である。この図は、「Vddout≧Vregout+Vsat」の状態に制御しているときの様子を示している。すなわち、降圧時と昇圧時の双方で上記の条件(Vddout≧Vregout+Vsat)を満たすように制御しているときの様子を示している。図において、ΔVa〜ΔVeは、ボルテージレギュレータ8の入出力電位差、つまり、Vregout+Vsatを示している。このΔVa〜ΔVeは常に一定であることが望ましいものの、そのためには、より緻密な制御が必要であり、制御の煩雑を招くという欠点を生じる。一方、制御を簡素化すると、今度は入出力電位差(ΔVa〜ΔVd)が一定にならず、場所によっては必要以上に大きくなるところが生じてしまう。

【0040】

たとえば、この図では、時刻t0と時刻t2でそれぞれVregoutを下げる動作(降圧動作)を行っており、また、時刻t5でVregoutを上げる動作(昇圧動作)を行っている。昇圧動作と降圧動作にはそれぞれ所定の応答遅れがあるので、時刻t0で始まった降圧動作は時刻t1で完了し、また、時刻t2で始まった降圧動作は時刻t3で完了し、同様に、時刻t5で始まった昇圧動作は時刻t6で完了する。

【0041】

降圧動作におけるVregoutの目標電圧は、いずれもVddoutよりも小さい。したがって、降圧動作中、Vddoutの制御は行われず、Vddoutは一定値を保持しているので、この間のボルテージレギュレータ8の入出力電位差は、VddoutとVregoutの電位差で与えられる。具体的には時刻t0までの入出力電位差はΔVa、時刻t1〜時刻t2の入出力電位差はΔVb、時刻t3〜時刻t4の入出力電位差はΔVcで与えられる。

【0042】

ここで、降圧動作中のVddoutは前記のとおり一定値を保持しているので、これらの入出力電位差(ΔVa、ΔVb、ΔVc)は必然的に不等値(ΔVa<ΔVb<ΔVc)となる。冒頭で説明したとおり、ボルテージレギュレータ8は、入出力電位差に相当するジュール熱を発生し、その熱による損失を生じるから、結局のところ、基本型の電源回路1は上記の入出力電位差(ΔVa、ΔVb、ΔVc)の不等値(ΔVa<ΔVb<ΔVc)に対応した損失を生じてしまう。図中の一点鎖線で示す特性線はその損失を示している。すなわち、時刻t0までの損失に対して、時刻t0〜t2で損失が増え、さらに、時刻t2〜t4でより一層損失が増える様子を示している。時刻t0〜t2の損失はΔVa<ΔVbに対応し、また、時刻t2〜t4の損失はΔVb<ΔVcに対応している。

【0043】

さらに、損失は昇圧動作の開始段階でも増加する。すなわち、図示の例では時刻t5でVregoutの昇圧を開始しているが、Vddoutの応答遅れを加味して、それに先立つ時刻t4の時点でVddoutの昇圧を事前に開始しておく必要があり、この事前昇圧によって一時的にボルテージレギュレータ8の入出力電位差Vdが増えてしまうからである。昇圧動作時の損失は、時刻t6で昇圧動作が完了すると、その時点の入出力電位差ΔVeに対応した小さな値に収まる。

【0044】

このように、基本型の電源回路1は、Vregoutの降圧動作や昇圧動作に伴って損失が増加するという不都合がある。この不都合は、Vregoutの変更(特に降圧)に合わせてVddoutを変更することによって解決可能であるが、そのような解決は、制御の煩雑化を招くという不都合を生じる。Vddoutの変更、つまり、分圧抵抗ラダー18の値設定は電源制御コントローラ10からの指令によって行う必要があるからであり、電源制御コントローラ10における制御が煩雑化するからである。

【0045】

以下、かかる不都合(損失の増加と制御の煩雑化)の解決を意図した実施形態について説明する。

2.実施形態の電源回路:

実施形態は、損失低減と制御の煩雑化の回避を意図して、前記の基本形の電源回路を改良したものである。

図4は、実施形態に係る電源回路の構成図である。なお、この図(図4)において、先の基本形の電源回路1(図1参照)と共通する構成要素には同一の符号を付してある。

実施形態に係る電源回路100は、多くの点で先の基本形の電源回路1と共通しているが、以下の点で構成上の相違がある。

【0046】

〔第1の相違点〕

一定の基準電圧Vr1を発生する基準電圧発生部21の代わりに、ボルテージレギュレータ80の出力電圧(Vregout)に相関する値(ここではVb)に応じて動的にその値を変化させる基準電圧Vr1を発生する基準電圧発生部210を設けた点。

【0047】

〔第2の相違点〕

DCDCコンバータ50の出力電圧(Vddout)が、ボルテージレギュレータ80の出力電圧(Vregout)よりも、ボルテージレギュレータ80の入出力電位差(Vsat)以上高くなるよう最適設定されたオフセット電圧Vofstを発生するオフセット発生部101を新たに設けた点。

【0048】

〔第3の相違点〕

2入力型のオペアンプで構成されたエラーアンプ20の代わりに、3入力型のオペアンプで構成されたエラーアンプ200を設け、その反転入力(−入力)にVaを加えるとともに、第1の非反転入力(+入力)にVr1を加え、第2の非反転入力(+入力)にVofstを加えた点。

【0049】

以上の第1〜第3の相違点により、実施形態に係る電源回路100は、煩雑な電圧制御を必要とせずに損失の低減を図ることができるという特有の効果を奏することができる。

【0050】

以下、このことについて詳述する。

図5は、実施形態に係る電源回路100における電圧制御のフローを示す図である。この図において、ステップS11〜ステップS15は、先の基本型の電源回路1における電圧制御フロー(図2参照)の同じステップ番号と共通であり、相違は、先の電圧制御フロー(図2参照)におけステップS16〜ステップS20の代わりにステップS21を設けた点にある。

【0051】

すなわち、先の電圧制御フロー(図2参照)では、ボルテージレギュレータ8の出力電圧(Vregout)の変更方向(上げる/下げる)を判定し(ステップS16)、その判定結果に従い、上げる場合の制御(ステップS17、ステップS18)と、下げる場合の制御(ステップS19、ステップS20)とを行うという煩雑な制御を行っていたが、実施形態に係る電源回路100では、そのような煩雑な制御を行う必要がなく、単にボルテージレギュレータ80の出力電圧(Vregout)の変更に追従させてDCDCコンバータ50の出力電圧(Vddout)を自動設定するという単純な動作(ステップS21)を実行している点で相違する。

【0052】

これは、前記の構成上の相違点(第1の相違点〜第3の相違点)を有しているからであり、とりわけ、ボルテージレギュレータ80の出力電圧(Vregout)に相関する値(ここではVb)に応じて動的にその値を変化させる基準電圧Vr1を発生する基準電圧発生部210を設けるとともに、DCDCコンバータ50の出力電圧(Vddout)が、ボルテージレギュレータ80の出力電圧(Vregout)よりも、ボルテージレギュレータ80の入出力電位差(Vsat)以上高くなるよう最適設定されたオフセット電圧Vofstを発生するオフセット発生部101を新たに設け、且つ、3入力型のオペアンプで構成されたエラーアンプ200の反転入力(−入力)にVaを加えるとともに、第1の非反転入力(+入力)にVr1を加え、第2の非反転入力(+入力)にVofstを加えたからであって、これにより、ステップS21の動作、すなわち、ボルテージレギュレータ80の出力電圧(Vregout)の変更に追従させてDCDCコンバータ50の出力電圧(Vddout)を自動設定するという単純な動作が実行されるからである。

【0053】

このように、実施形態に係る電源回路100では、ボルテージレギュレータ80の出力電圧(Vregout)をDCDCコンバータ50の側でモニタできる構成とし、ボルテージレギュレータ80の出力電圧(Vregout)を基準としてDCDCコンバータ50の出力電圧(Vddout)、すなわち、ボルテージレギュレータ80の入力電圧にフィードバックがかかるようにしたので、ボルテージレギュレータ80の出力電圧に変更があった場合には、電圧の上昇・下降に関係なく、その変更がDCDCコンバータ50の側にフィードバックされ、DCDCコンバータ50の出力電圧(すなわち、ボルテージレギュレータ80の入力電圧)が追従して自動設定されるから、電源制御コントローラ10の制御を簡素化できるという第1の効果が得られる。

【0054】

また、ボルテージレギュレータ80の出力電圧の変更にかかわらず、常にボルテージレギュレータ80の入出力電位差を一定にすることができ、損失(発熱ロス)を最小に抑えることもできるという第2の効果も得られる。

【0055】

第2の効果について説明する。

図6は、実施形態に係る電源回路100における電圧出力特性図である。時刻t0及び時刻t2はVregoutの降圧動作開始点、時刻t4はVregoutの昇圧動作開始点であり、時刻t1、時刻t3、時刻t5は各々の動作完了点である。この図に示すように、実施形態の電源回路100では、Vregoutの降圧または昇圧動作に追従してVddoutの値が同方向且つ同量だけ変化する。すなわち、時刻t0〜t1にかけてVregoutが降圧動作しているが、このときVddoutも同方向且つ同量だけ追従変化している。同様に、時刻t2〜t3にかけてVregoutがさらに降圧動作しているが、このときにも、Vddoutが同方向且つ同量だけ追従変化している。同様に、時刻t4〜t5にかけてVregoutが昇圧動作しているが、このときにも、Vddoutが同方向且つ同量だけ追従変化している。

【0056】

したがって、いずれの場所においても、VregoutとVddoutの差分、つまり、ボルテージレギュレータ80の入出力電位差ΔVは「一定」であり、この入出力電位差ΔVは損失に相当するから、ボルテージレギュレータ80の出力電圧の変更にかかわらず、常にボルテージレギュレータ80の入出力電位差を一定に維持して、損失(発熱ロス)を最小に抑えることができる。しかも、このような入出力電位差ΔVの「一定」は、電源制御コントローラ10の制御によって行われるのではなく、Vregoutに相関する値(Vb)に追従して自動的に行われるから、制御の煩雑化を招くこともない。

【0057】

以上のとおりであるから、実施形態に係る電源回路100によれば、以下の効果を奏することができる。

(1)ボルテージレギュレータ80の出力電圧に対して自動的にDCDCコンバータ50の出力電圧、すなわちボルテージレギュレータ80の入力電圧を追従させることができ、ボルテージレギュレータ80の出力電圧やDCDCコンバータ50の出力電圧それぞれに対する煩雑な制御をなくして、電圧制御コントローラ10の処理負担を軽減することができる。

(2)ボルテージレギュレータ80の出力電圧に対して、ボルテージレギュレータ80の入力電圧(DCDCコンバータ50の出力電圧)を自動的に最適化することができ、損失を最小限にすることができる。

(3)DCDCコンバータ50の出力電圧をボルテージレギュレータ80の出力電圧に追従させて自動設定できるので、DCDCコンバータ50の出力電圧の制御を行う必要がなくなり、電源制御コントローラ10の制御負担を軽減できる。

【0058】

なお、実施形態に係る電源回路100の適用分野は特に限定されない。たとえば、携帯電話機等の携帯型電子機器などとしてもよいが、要は、バッテリで動作する電子機器であれば如何なるものであっても適用可能である。

【0059】

以下、本発明の特徴を付記する。

上記の実施形態の一部又は全部は、以下の付記のようにも記載されうるが、以下には限られない。

(付記1)

図7は、付記1の構成図である。

付記1は、

バッテリ300(実施形態のバッテリ3に相当)の出力電圧を昇圧しまたは降圧するDCDCコンバータ301(実施形態のDCDCコンバータ50に相当)と、

前記DCDCコンバータ301の出力電圧を降圧するボルテージレギュレータ302(実施形態のボルテージレギュレータ80に相当)と、

前記ボルテージレギュレータ302の出力電圧に相関する値に応じて前記DCDCコンバータ301の出力電圧の昇圧値または降圧値を設定する電圧設定手段303(実施形態の基準電圧発生部210、オフセット発生部101、エラーアンプ200に相当)と

を備えたことを特徴とする電源回路304(実施形態の電源回路100に相当)である。

【0060】

(付記2)

付記2は、

前記電圧設定手段は、前記ボルテージレギュレータの出力電圧に相関する値にに応じて動的にその値を変化させる基準電圧を発生するとともに、前記DCDCコンバータの出力電圧が前記ボルテージレギュレータの出力電圧よりも前記ボルテージレギュレータの入出力電位差以上高くなるよう設定されたオフセット電圧を発生し、これらの基準電圧とオフセット電圧とに基づいて前記DCDCコンバータの出力電圧を昇圧しまたは降圧することを特徴とする付記1に記載の電源回路である。

【0061】

(付記3)

付記3は、

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする、電源回路の制御方法である。

【符号の説明】

【0062】

300 バッテリ300

301 DCDCコンバータ

302 ボルテージレギュレータ

303 電圧設定手段

304 電源回路

【技術分野】

【0001】

本発明は、バッテリの電圧を定電圧化する電源回路及びその制御方法に関し、詳しくは、出力電圧の設定に際して煩雑な制御を必要としない電源回路及びその制御方法に関する。

【背景技術】

【0002】

一般的にバッテリ駆動の電子機器における電源回路は、バッテリと、そのバッテリの出力電圧(端子電圧ともいう)を安定化する安定化回路とにより構成されている。

【0003】

最も単純な安定化回路は、たとえば、下記の特許文献1に記載されているリニアレギュレータなどの「ボルテージレギュレータ」である。ボルテージレギュレータは、入力電圧を降下(降圧)させて安定化した電圧を出力するが、入力電圧の降下分をジュール熱として放出するため、電力損失が大きいという欠点がある。

【0004】

一方、スイッチング電源とも呼ばれるスイッチングレギュレータは、入力電力から希望の出力電力を得る電力変換装置において、電力を変換・調整するためにスイッチング素子(電気回路の一部をON/OFFできる素子)を用いた電源装置の総称であり、その中でも特に、直流電力を別の直流電力に変換するものを「DCDCコンバータ」といい、電圧降下をジュール熱として放出するボルテージレギュレータとは異なり、電力損失を少なくできるため、高精度・高効率を得ることができるという利点がある。DCDCコンバータの関連技術としては、たとえば、特許文献2や特許文献3に記載のものがある。

【0005】

特許文献2には、昇降圧DCDCコンバータにおいて、降圧および昇圧を往来するような出力電圧の変動を抑制することができ、出力電圧を安定させることができる技術が記載されている。また、特許文献3には、給電切り換えする電圧を低く抑えて、昇圧変換回路での無駄な変換損失を低減して省電力効果を向上させることができる技術が記載されている。

【0006】

このように、DCDCコンバータは電力損失を少なくできるという利点があることから、前記のボルテージレギュレータの代わりにDCDCコンバータを用いてバッテリの電圧を安定化することが考えられるが、すなわち、「バッテリ→DCDCコンバータ→負荷」という構成が考えられるが、この構成では、DCDCコンバータの出力に現れるリップルノイズ(スイッチングに伴う微小な振動成分)の影響で良質な出力電圧が得られないという課題がある。このため、一般的には、リップルノイズをドロッパ(ボルテージレギュレータ)で押さえ込むという構成、すなわち、「バッテリ→DCDCコンバータ→ボルテージレギュレータ→負荷」という組み合わせの構成がとられ、とりわけ、ノイズにシビアなデバイスの場合にはそのような構成がとられることが多い。

【0007】

DCDCコンバータとボルテージレギュレータとの組み合わせに関する技術としては、たとえば、下記の特許文献4や特許文献5に記載のものがある。

【0008】

特許文献4には、補助電源(リチウムイオン2次電池)の出力電圧を昇圧する昇圧部(DCDCコンバータ)と、昇圧部の出力を降圧して負荷に供給する降圧(ボルテージレギュレータ)とを備えた電源装置の技術が記載されている。また、特許文献5には、昇圧DCDCコンバータとボルテージレギュレータとを備えた定電圧電源装置の技術が記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−278311号公報

【特許文献2】特開2008−092779号公報

【特許文献3】特開2009−273249号公報

【特許文献4】特開平10−0333759号公報

【特許文献5】特開2007−336795号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

上記のとおり、ボルテージレギュレータは電力損失が大きいという欠点があり、また、DCDCコンバータはリップルノイズの影響で良質な出力電圧が得られないという欠点があることから、一般的にはそれらの組み合わせ、つまり、DCDCコンバータとボルテージレギュレータとの組み合わせからなる構成(以下、組み合わせ型という)とされることが多い。

【0011】

しかしながら、このような組み合わせ型は、ボルテージレギュレータの入出力電位差を最適化するために、ボルテージレギュレータの出力電圧に応じてDCDCコンバータの出力電圧を制御しなければならず、制御が煩雑になるという問題点がある。また、出力可変型(プログラマブル型)のボルテージレギュレータの場合は、DCDCコンバータの出力電圧の制御に加えて、ボルテージレギュレータの出力電圧の制御も行わなければならず、さらに制御が煩雑になるという問題点がある。

【0012】

そこで、本発明の目的は、煩雑な制御を必要とせずに、ボルテージレギュレータの入出力電位差を最適化できる電源回路及びその制御方法を提供することにある。

【課題を解決するための手段】

【0013】

本発明の電源回路は、バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータと、前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定手段とを備えたことを特徴とする。

本発明の電源回路の制御方法は、バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする。

【発明の効果】

【0014】

本発明によれば、煩雑な制御を必要とせずに、ボルテージレギュレータの入出力電位差を最適化できる電源回路及びその制御方法を提供することができる。

【図面の簡単な説明】

【0015】

【図1】基本形の電源回路の構成図である。

【図2】基本型の電源回路1における電圧制御のフローを示す図である。

【図3】基本型の電源回路1における電圧出力特性図である。

【図4】実施形態に係る電源回路の構成図である。

【図5】実施形態に係る電源回路100における電圧制御のフローを示す図である。

【図6】実施形態に係る電源回路100における電圧出力特性図である。

【図7】付記1の構成図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態を、図面を参照しながら説明する。

1.基本形の電源回路:

まず、実施形態を説明する前に、実施形態を適用しない基本形の電源回路について説明する。なお、基本形の電源回路とは、前記の問題点、すなわち、ボルテージレギュレータの入出力電位差を最適化する際に煩雑な制御を行う必要がある電源回路のことをいう。

図1は、基本形の電源回路の構成図である。この図において、電源回路1は、一端がグランド(GND)に接続され、他端がバッテリ電源線2に接続されたリチウムイオン2次電池などのバッテリ3と、このバッテリ3に並列に接続されたバイパスコンデンサ4と、バッテリ3の出力電圧(バッテリ電源線2とGNDの間の電圧;端子電圧ともいう)を任意の電圧に昇圧もしくは降圧する昇・降圧型のDCDCコンバータ5と、DCDCコンバータ5の出力とGNDとの間に接続された第1の位相補償用コンデンサ6と、DCDCコンバータ5の出力と負荷(任意の電子回路等)7との間に挿入されたボルテージレギュレータ8と、ボルテージレギュレータ8の出力とGNDとの間に接続された第2の位相補償用コンデンサ9と、DCDCコンバータ5やボルテージレギュレータ8の動作を制御する電源制御コントローラ10とを備えている。

【0017】

バッテリ3の出力電圧を「Vbat」、DCDCコンバータ5の出力電圧(ボルテージレギュレータ8の入力電圧でもある)を「Vddout」、ボルテージレギュレータ8の出力電圧を「Vregout」ということにする。

【0018】

<DCDCコンバータ5の構成>

DCDCコンバータ5は、4つのFET11〜14と、コイル15と、FET11〜14のオンオフを制御するDCDCコントローラ16と、スイッチング用の発振回路(OSC)17と、VddoutをモニタしてDCDCコントローラ16にフィードバックする分圧抵抗ラダー18及び分圧抵抗19と、補正用のエラーアンプ20と、所定の基準電圧Vr1を発生する基準電圧発生部21とから構成されている。

【0019】

このような構成を有するDCDCコンバータ5は、先にも述べたように、バッテリ3の端子電圧を昇圧もしくは降圧し、任意の電圧(Vddout)に変換して出力する。

【0020】

DCDCコンバータ5は、昇圧時と降圧時の二つの態様で動作し、昇圧時には、FET11をオンにしたまま、発振回路17の発振周期でFET13をオンオフし、コイル15に流れる電流をチョッピングしてコイル15に電流を蓄え、コイル15に蓄えた電流をFET14を介して第1の位相補償用コンデンサ6に吐き出すことによって所望の出力電圧(Vddout)を得るという動作を繰り返す。このとき、FET14は、FET13がオフの時にコイル15の電流を還流するためのスイッチとして働き、FET14とFET13は逆相で動作する。

【0021】

一方、降圧時には、発振回路17の発振周期でFET11をオンオフし、コイル15に流れる電流をチョッピングしてコイル15に電流を蓄え、コイル15に蓄えた電流をFET14を介して第1の位相補償用コンデンサ6に吐き出すことによって所望の出力電圧(Vddout)を得るという動作を繰り返す。このとき、FET12は、FET11がオフの時にコイル15の電流を還流するためのスイッチとして働き、FET12とFET11は逆相で動作する。

【0022】

DCDCコントローラ16は、昇圧時または降圧時におけるDCDCコンバータ5の出力電圧(Vddout)をエラーアンプ20の出力電圧に従って制御するものであり、このDCDCコントローラ16には、エラーアンプ20の出力電圧が加えられている。

【0023】

エラーアンプ20はオペアンプで構成されており、オペアンプ(エラーアンプ20)の反転入力(−入力)には、分圧抵抗ラダー18と分圧抵抗19とからなる抵抗分圧回路の分圧電圧Vaが加えられ、非反転入力(+入力)には基準電圧発生部21で作られた基準電圧Vr1が加えられている。

【0024】

一般にオペアンプは、反転入力と非反転入力の差分に相当する値を出力するので、かかるオペアンプ(エラーアンプ20)の出力電圧に従ってVddoutの値を制御するDCDCコントローラ16は、要するに、基準電圧Vr1に対応した一定の電圧となるようにVddoutの値を制御する。

【0025】

エラーアンプ20の反転入力(−入力)に加えられる分圧電圧Vaは、分圧抵抗ラダー18の値に応じて変化し、分圧抵抗ラダー18の値は、電源制御コントローラ10の制御に従って増減変化する仕組みになっている。

【0026】

したがって、DCDCコンバータ5は、その出力電圧(Vddout)を、電源制御コントローラ10の制御に従って任意に変化させることができるプログラム型の定電圧回路であり、且つ、バッテリ3の電圧を昇圧または降圧することができる昇・降圧型の定電圧回路である。

【0027】

<ボルテージレギュレータ8の構成>

ボルテージレギュレータ8は、ドライバ用のFET22と、ボルテージレギュレータ8の出力電圧(Vregout)をモニタするための分圧抵抗ラダー23及び分圧抵抗24と、エラーアンプ26と、基準電圧Vr2を発生する基準電圧発生部27とから構成されており、FET22のソース−ドレイン間を流れる電流(以下、iDS)を制御することにより、DCDCコンバータ5の出力電圧(Vddout)を降圧し、所定の直流電圧(Vregout)に安定化して出力する。

【0028】

FET22のiDSは、FET22のゲート電位に応じて変化し、FET22のゲート電位は、エラーアンプ25の出力電圧で与えられる。

【0029】

エラーアンプ25はオペアンプで構成されており、このオペアンプ(エラーアンプ25)の非反転入力(+入力)には、分圧抵抗ラダー23と分圧抵抗24とからなる抵抗分圧回路の分圧電圧Vbが加えられ、反転入力(−入力)には基準電圧発生部26で作られた基準電圧Vr2が加えられている。

【0030】

エラーアンプ25の非反転入力(+入力)に加えられる分圧電圧Vbは、分圧抵抗ラダー23の値に応じて変化し、分圧抵抗ラダー23の値は、電源制御コントローラ10の制御に従って増減変化する仕組みになっている。

【0031】

したがって、ボルテージレギュレータ8は、その出力電圧(Vregout)を、電源制御コントローラ10の制御に従って任意に変化させることができるプログラム型の定電圧回路であり、且つ、Vddoutを超えない電圧(vregout)に定電圧化できる降圧型の定電圧回路である。

【0032】

なお、以上の例では、DCDCコンバータ5を昇・降圧型としたが、常にバッテリ3の端子電圧以下で使用するのであれば、降圧型であってもよく、この場合、FET13は不要である。

【0033】

さて、図1に示す基本型の電源回路1における電圧制御は、もっぱら電源制御コントローラ10で行っている。

【0034】

図2は、基本型の電源回路1における電圧制御のフローを示す図である。この図において、電源制御コントローラ10は、まず、DCDCコンバータ5の出力電圧(Vddout)の設定(ステップS11)と、ボルテージレギュレータ8の初期の出力電圧(Vregout)の設定(ステップS12)とを行い、次いで、DCDCコンバータ5とボルテージレギュレータ8の動作をオンにする(ステップS13、ステップS14)。

【0035】

そして、ボルテージレギュレター8の出力電圧(Vregout)の変更ありか否かを判定し(ステップS15)、変更ありでなければ、そのままステップS15を繰り返し、変更ありであれば、次に、ボルテージレギュレータ8の出力電圧(Vregout)の変更方向(上げる/下げる)を判定し(ステップS16)、以降、その変更方向に対応した制御を実行した後、再び、ステップS15に復帰する。

【0036】

<上げる場合の制御>

ボルテージレギュレータ8の出力電圧(Vregout)の変更方向が「上げる」場合は、DCDCコンバータ5の出力電圧(Vddout)を上げるための設定(ステップS17;分圧抵抗ラダー18の値を変更する)と、ボルテージレギュレータ8の出力電圧(Vregout)を上げるための設定(ステップS18;分圧抵抗ラダー23の値を変更する)とを行う。

【0037】

<下げる場合の制御>

ボルテージレギュレータ8の出力電圧(Vregout)の変更方向が「下げる」場合は、DCDCコンバータ5の出力電圧(Vddout)を下げるための設定(ステップS19;分圧抵抗ラダー18の値を変更する)と、ボルテージレギュレータ8の出力電圧(Vregout)を下げるための設定(ステップS20;分圧抵抗ラダー23の値を変更する)とを行う。

【0038】

このような電圧制御において、DCDCコンバータ5の出力電圧(Vddout)は、ボルテージレギュレータ8の出力電圧(Vregout)に、そのボルテージレギュレータ8の最小入出力電圧差(以下、Vsat)を加えた以上の電圧があればよい。つまり、「Vddout≧Vregout+Vsat」であればよい。

【0039】

図3は、基本型の電源回路1における電圧出力特性図である。この図は、「Vddout≧Vregout+Vsat」の状態に制御しているときの様子を示している。すなわち、降圧時と昇圧時の双方で上記の条件(Vddout≧Vregout+Vsat)を満たすように制御しているときの様子を示している。図において、ΔVa〜ΔVeは、ボルテージレギュレータ8の入出力電位差、つまり、Vregout+Vsatを示している。このΔVa〜ΔVeは常に一定であることが望ましいものの、そのためには、より緻密な制御が必要であり、制御の煩雑を招くという欠点を生じる。一方、制御を簡素化すると、今度は入出力電位差(ΔVa〜ΔVd)が一定にならず、場所によっては必要以上に大きくなるところが生じてしまう。

【0040】

たとえば、この図では、時刻t0と時刻t2でそれぞれVregoutを下げる動作(降圧動作)を行っており、また、時刻t5でVregoutを上げる動作(昇圧動作)を行っている。昇圧動作と降圧動作にはそれぞれ所定の応答遅れがあるので、時刻t0で始まった降圧動作は時刻t1で完了し、また、時刻t2で始まった降圧動作は時刻t3で完了し、同様に、時刻t5で始まった昇圧動作は時刻t6で完了する。

【0041】

降圧動作におけるVregoutの目標電圧は、いずれもVddoutよりも小さい。したがって、降圧動作中、Vddoutの制御は行われず、Vddoutは一定値を保持しているので、この間のボルテージレギュレータ8の入出力電位差は、VddoutとVregoutの電位差で与えられる。具体的には時刻t0までの入出力電位差はΔVa、時刻t1〜時刻t2の入出力電位差はΔVb、時刻t3〜時刻t4の入出力電位差はΔVcで与えられる。

【0042】

ここで、降圧動作中のVddoutは前記のとおり一定値を保持しているので、これらの入出力電位差(ΔVa、ΔVb、ΔVc)は必然的に不等値(ΔVa<ΔVb<ΔVc)となる。冒頭で説明したとおり、ボルテージレギュレータ8は、入出力電位差に相当するジュール熱を発生し、その熱による損失を生じるから、結局のところ、基本型の電源回路1は上記の入出力電位差(ΔVa、ΔVb、ΔVc)の不等値(ΔVa<ΔVb<ΔVc)に対応した損失を生じてしまう。図中の一点鎖線で示す特性線はその損失を示している。すなわち、時刻t0までの損失に対して、時刻t0〜t2で損失が増え、さらに、時刻t2〜t4でより一層損失が増える様子を示している。時刻t0〜t2の損失はΔVa<ΔVbに対応し、また、時刻t2〜t4の損失はΔVb<ΔVcに対応している。

【0043】

さらに、損失は昇圧動作の開始段階でも増加する。すなわち、図示の例では時刻t5でVregoutの昇圧を開始しているが、Vddoutの応答遅れを加味して、それに先立つ時刻t4の時点でVddoutの昇圧を事前に開始しておく必要があり、この事前昇圧によって一時的にボルテージレギュレータ8の入出力電位差Vdが増えてしまうからである。昇圧動作時の損失は、時刻t6で昇圧動作が完了すると、その時点の入出力電位差ΔVeに対応した小さな値に収まる。

【0044】

このように、基本型の電源回路1は、Vregoutの降圧動作や昇圧動作に伴って損失が増加するという不都合がある。この不都合は、Vregoutの変更(特に降圧)に合わせてVddoutを変更することによって解決可能であるが、そのような解決は、制御の煩雑化を招くという不都合を生じる。Vddoutの変更、つまり、分圧抵抗ラダー18の値設定は電源制御コントローラ10からの指令によって行う必要があるからであり、電源制御コントローラ10における制御が煩雑化するからである。

【0045】

以下、かかる不都合(損失の増加と制御の煩雑化)の解決を意図した実施形態について説明する。

2.実施形態の電源回路:

実施形態は、損失低減と制御の煩雑化の回避を意図して、前記の基本形の電源回路を改良したものである。

図4は、実施形態に係る電源回路の構成図である。なお、この図(図4)において、先の基本形の電源回路1(図1参照)と共通する構成要素には同一の符号を付してある。

実施形態に係る電源回路100は、多くの点で先の基本形の電源回路1と共通しているが、以下の点で構成上の相違がある。

【0046】

〔第1の相違点〕

一定の基準電圧Vr1を発生する基準電圧発生部21の代わりに、ボルテージレギュレータ80の出力電圧(Vregout)に相関する値(ここではVb)に応じて動的にその値を変化させる基準電圧Vr1を発生する基準電圧発生部210を設けた点。

【0047】

〔第2の相違点〕

DCDCコンバータ50の出力電圧(Vddout)が、ボルテージレギュレータ80の出力電圧(Vregout)よりも、ボルテージレギュレータ80の入出力電位差(Vsat)以上高くなるよう最適設定されたオフセット電圧Vofstを発生するオフセット発生部101を新たに設けた点。

【0048】

〔第3の相違点〕

2入力型のオペアンプで構成されたエラーアンプ20の代わりに、3入力型のオペアンプで構成されたエラーアンプ200を設け、その反転入力(−入力)にVaを加えるとともに、第1の非反転入力(+入力)にVr1を加え、第2の非反転入力(+入力)にVofstを加えた点。

【0049】

以上の第1〜第3の相違点により、実施形態に係る電源回路100は、煩雑な電圧制御を必要とせずに損失の低減を図ることができるという特有の効果を奏することができる。

【0050】

以下、このことについて詳述する。

図5は、実施形態に係る電源回路100における電圧制御のフローを示す図である。この図において、ステップS11〜ステップS15は、先の基本型の電源回路1における電圧制御フロー(図2参照)の同じステップ番号と共通であり、相違は、先の電圧制御フロー(図2参照)におけステップS16〜ステップS20の代わりにステップS21を設けた点にある。

【0051】

すなわち、先の電圧制御フロー(図2参照)では、ボルテージレギュレータ8の出力電圧(Vregout)の変更方向(上げる/下げる)を判定し(ステップS16)、その判定結果に従い、上げる場合の制御(ステップS17、ステップS18)と、下げる場合の制御(ステップS19、ステップS20)とを行うという煩雑な制御を行っていたが、実施形態に係る電源回路100では、そのような煩雑な制御を行う必要がなく、単にボルテージレギュレータ80の出力電圧(Vregout)の変更に追従させてDCDCコンバータ50の出力電圧(Vddout)を自動設定するという単純な動作(ステップS21)を実行している点で相違する。

【0052】

これは、前記の構成上の相違点(第1の相違点〜第3の相違点)を有しているからであり、とりわけ、ボルテージレギュレータ80の出力電圧(Vregout)に相関する値(ここではVb)に応じて動的にその値を変化させる基準電圧Vr1を発生する基準電圧発生部210を設けるとともに、DCDCコンバータ50の出力電圧(Vddout)が、ボルテージレギュレータ80の出力電圧(Vregout)よりも、ボルテージレギュレータ80の入出力電位差(Vsat)以上高くなるよう最適設定されたオフセット電圧Vofstを発生するオフセット発生部101を新たに設け、且つ、3入力型のオペアンプで構成されたエラーアンプ200の反転入力(−入力)にVaを加えるとともに、第1の非反転入力(+入力)にVr1を加え、第2の非反転入力(+入力)にVofstを加えたからであって、これにより、ステップS21の動作、すなわち、ボルテージレギュレータ80の出力電圧(Vregout)の変更に追従させてDCDCコンバータ50の出力電圧(Vddout)を自動設定するという単純な動作が実行されるからである。

【0053】

このように、実施形態に係る電源回路100では、ボルテージレギュレータ80の出力電圧(Vregout)をDCDCコンバータ50の側でモニタできる構成とし、ボルテージレギュレータ80の出力電圧(Vregout)を基準としてDCDCコンバータ50の出力電圧(Vddout)、すなわち、ボルテージレギュレータ80の入力電圧にフィードバックがかかるようにしたので、ボルテージレギュレータ80の出力電圧に変更があった場合には、電圧の上昇・下降に関係なく、その変更がDCDCコンバータ50の側にフィードバックされ、DCDCコンバータ50の出力電圧(すなわち、ボルテージレギュレータ80の入力電圧)が追従して自動設定されるから、電源制御コントローラ10の制御を簡素化できるという第1の効果が得られる。

【0054】

また、ボルテージレギュレータ80の出力電圧の変更にかかわらず、常にボルテージレギュレータ80の入出力電位差を一定にすることができ、損失(発熱ロス)を最小に抑えることもできるという第2の効果も得られる。

【0055】

第2の効果について説明する。

図6は、実施形態に係る電源回路100における電圧出力特性図である。時刻t0及び時刻t2はVregoutの降圧動作開始点、時刻t4はVregoutの昇圧動作開始点であり、時刻t1、時刻t3、時刻t5は各々の動作完了点である。この図に示すように、実施形態の電源回路100では、Vregoutの降圧または昇圧動作に追従してVddoutの値が同方向且つ同量だけ変化する。すなわち、時刻t0〜t1にかけてVregoutが降圧動作しているが、このときVddoutも同方向且つ同量だけ追従変化している。同様に、時刻t2〜t3にかけてVregoutがさらに降圧動作しているが、このときにも、Vddoutが同方向且つ同量だけ追従変化している。同様に、時刻t4〜t5にかけてVregoutが昇圧動作しているが、このときにも、Vddoutが同方向且つ同量だけ追従変化している。

【0056】

したがって、いずれの場所においても、VregoutとVddoutの差分、つまり、ボルテージレギュレータ80の入出力電位差ΔVは「一定」であり、この入出力電位差ΔVは損失に相当するから、ボルテージレギュレータ80の出力電圧の変更にかかわらず、常にボルテージレギュレータ80の入出力電位差を一定に維持して、損失(発熱ロス)を最小に抑えることができる。しかも、このような入出力電位差ΔVの「一定」は、電源制御コントローラ10の制御によって行われるのではなく、Vregoutに相関する値(Vb)に追従して自動的に行われるから、制御の煩雑化を招くこともない。

【0057】

以上のとおりであるから、実施形態に係る電源回路100によれば、以下の効果を奏することができる。

(1)ボルテージレギュレータ80の出力電圧に対して自動的にDCDCコンバータ50の出力電圧、すなわちボルテージレギュレータ80の入力電圧を追従させることができ、ボルテージレギュレータ80の出力電圧やDCDCコンバータ50の出力電圧それぞれに対する煩雑な制御をなくして、電圧制御コントローラ10の処理負担を軽減することができる。

(2)ボルテージレギュレータ80の出力電圧に対して、ボルテージレギュレータ80の入力電圧(DCDCコンバータ50の出力電圧)を自動的に最適化することができ、損失を最小限にすることができる。

(3)DCDCコンバータ50の出力電圧をボルテージレギュレータ80の出力電圧に追従させて自動設定できるので、DCDCコンバータ50の出力電圧の制御を行う必要がなくなり、電源制御コントローラ10の制御負担を軽減できる。

【0058】

なお、実施形態に係る電源回路100の適用分野は特に限定されない。たとえば、携帯電話機等の携帯型電子機器などとしてもよいが、要は、バッテリで動作する電子機器であれば如何なるものであっても適用可能である。

【0059】

以下、本発明の特徴を付記する。

上記の実施形態の一部又は全部は、以下の付記のようにも記載されうるが、以下には限られない。

(付記1)

図7は、付記1の構成図である。

付記1は、

バッテリ300(実施形態のバッテリ3に相当)の出力電圧を昇圧しまたは降圧するDCDCコンバータ301(実施形態のDCDCコンバータ50に相当)と、

前記DCDCコンバータ301の出力電圧を降圧するボルテージレギュレータ302(実施形態のボルテージレギュレータ80に相当)と、

前記ボルテージレギュレータ302の出力電圧に相関する値に応じて前記DCDCコンバータ301の出力電圧の昇圧値または降圧値を設定する電圧設定手段303(実施形態の基準電圧発生部210、オフセット発生部101、エラーアンプ200に相当)と

を備えたことを特徴とする電源回路304(実施形態の電源回路100に相当)である。

【0060】

(付記2)

付記2は、

前記電圧設定手段は、前記ボルテージレギュレータの出力電圧に相関する値にに応じて動的にその値を変化させる基準電圧を発生するとともに、前記DCDCコンバータの出力電圧が前記ボルテージレギュレータの出力電圧よりも前記ボルテージレギュレータの入出力電位差以上高くなるよう設定されたオフセット電圧を発生し、これらの基準電圧とオフセット電圧とに基づいて前記DCDCコンバータの出力電圧を昇圧しまたは降圧することを特徴とする付記1に記載の電源回路である。

【0061】

(付記3)

付記3は、

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする、電源回路の制御方法である。

【符号の説明】

【0062】

300 バッテリ300

301 DCDCコンバータ

302 ボルテージレギュレータ

303 電圧設定手段

304 電源回路

【特許請求の範囲】

【請求項1】

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、

前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータと、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定手段と

を備えたことを特徴とする電源回路。

【請求項2】

前記電圧設定手段は、前記ボルテージレギュレータの出力電圧に相関する値にに応じて動的にその値を変化させる基準電圧を発生するとともに、前記DCDCコンバータの出力電圧が前記ボルテージレギュレータの出力電圧よりも前記ボルテージレギュレータの入出力電位差以上高くなるよう設定されたオフセット電圧を発生し、これらの基準電圧とオフセット電圧とに基づいて前記DCDCコンバータの出力電圧を昇圧しまたは降圧することを特徴とする請求項1に記載の電源回路。

【請求項3】

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする、電源回路の制御方法。

【請求項1】

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、

前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータと、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定手段と

を備えたことを特徴とする電源回路。

【請求項2】

前記電圧設定手段は、前記ボルテージレギュレータの出力電圧に相関する値にに応じて動的にその値を変化させる基準電圧を発生するとともに、前記DCDCコンバータの出力電圧が前記ボルテージレギュレータの出力電圧よりも前記ボルテージレギュレータの入出力電位差以上高くなるよう設定されたオフセット電圧を発生し、これらの基準電圧とオフセット電圧とに基づいて前記DCDCコンバータの出力電圧を昇圧しまたは降圧することを特徴とする請求項1に記載の電源回路。

【請求項3】

バッテリの出力電圧を昇圧しまたは降圧するDCDCコンバータと、前記DCDCコンバータの出力電圧を降圧するボルテージレギュレータとを備える電源回路の制御方法であって、

前記ボルテージレギュレータの出力電圧に相関する値に応じて前記DCDCコンバータの出力電圧の昇圧値または降圧値を設定する電圧設定工程を含むことを特徴とする、電源回路の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−59186(P2013−59186A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−195567(P2011−195567)

【出願日】平成23年9月8日(2011.9.8)

【出願人】(310006855)NECカシオモバイルコミュニケーションズ株式会社 (1,081)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月8日(2011.9.8)

【出願人】(310006855)NECカシオモバイルコミュニケーションズ株式会社 (1,081)

【Fターム(参考)】

[ Back to top ]