電源回路及びその動作制御方法

【課題】スイッチングレギュレータ方式のDC/DCコンバータに対してスパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させる。

【解決手段】スイッチング波形Lxのハイレベルからロウレベルへの変化時部分で、出力制御回路14は低電流容量でゲート電圧NGを出力する。波形検出回路15はスイッチング波形Lxが緩やかにハイレベルからロウレベルとなったことを検出し、その検出信号Pupを受けた出力制御回路14は高電流容量で出力ドライバM1にゲート電圧NGを印加し、ゲート電圧NGを直ちにハイレベルとする。スイッチング波形Lxのロウレベルからハイレベルへの変化時部分で、波形検出回路15はゲート電圧NGがハイレベルからモード切替え用基準値Vaになったことを検出し、その検出信号Pupを受けた出力制御回路14は出力ドライバM1へのゲート電圧NGの印加を低電流容量に切り替える。

【解決手段】スイッチング波形Lxのハイレベルからロウレベルへの変化時部分で、出力制御回路14は低電流容量でゲート電圧NGを出力する。波形検出回路15はスイッチング波形Lxが緩やかにハイレベルからロウレベルとなったことを検出し、その検出信号Pupを受けた出力制御回路14は高電流容量で出力ドライバM1にゲート電圧NGを印加し、ゲート電圧NGを直ちにハイレベルとする。スイッチング波形Lxのロウレベルからハイレベルへの変化時部分で、波形検出回路15はゲート電圧NGがハイレベルからモード切替え用基準値Vaになったことを検出し、その検出信号Pupを受けた出力制御回路14は出力ドライバM1へのゲート電圧NGの印加を低電流容量に切り替える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源回路及びその動作制御方法に関し、特に、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法に関するものである。本発明の電源回路及びその動作制御方法は例えばスイッチングレギュレータ方式のDC/DCコンバータに適用される。

【背景技術】

【0002】

入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路として、例えばスイッチングレギュレータ方式のDC/DCコンバータがある。

スイッチングレギュレータ方式のDC/DCコンバータにおいて、スパイクノイズを抑えるためスイッチング波形の高周波成分をなまらせる必要がある。

【0003】

例えば昇圧型DC/DCコンバータを例に挙げて説明すると、NMOSFET(N-channel Metal Oxide Semiconductor Field Effect Transistor)からなるNMOSドライバを駆動するためのCMOSインバータ(以下プリドライバと呼ぶ。)のドライブ能力(電流駆動能力)を低下させることで、スイッチング波形のハイレベルからロウレベルへの変化時及びロウレベルからハイレベルへの変化時における高周波成分をなまらせることが既に知られている。

【0004】

例えば、スパイクノイズを抑える目的で、駆動用スイッチング素子をオン状態からオフ状態へ移行させる際の駆動信号の遷移時間よりも、スイッチング素子をオフ状態からオン状態へ移行させる際の駆動信号の遷移時間の方が長くなるように駆動信号を生成することが提案されている(特許文献1を参照。)。具体的には、駆動用素子の駆動信号を作るCMOSインバータのPMOS(P-channel MOS)の電流駆動能力の方が、NMOSのそれより大きく、整流用素子の駆動信号を作るCMOSインバータのNMOSの電流駆動能力の方が、PMOSのそれより大きくすることで、スパイクノイズを低減する構成が特許文献1に開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、NMOSドライバを駆動するCMOSインバータのドライブ能力を低下させる手法では、NMOSドライバのゲート電圧が低く、オン抵抗が高い状態が長くなるので、電力変換効率が低下や最小オン時間が長くなるという問題があった。

【0006】

具体的には、スイッチング波形のハイレベルからロウレベルへの変化部分を説明すると、ゲート電圧が0VからNMOSドライバのしきい値電圧を越えたあたりでNMOSドライバが緩やかにオフからオンとなり、スイッチング波形は緩やかにハイレベルからロウレベルとなる。これによりスパイクノイズを抑えることができる。しかし、ゲート電圧がしきい値電圧からハイレベルになるまでの時間の方が一般的に長く、しきい値電圧からハイレベルまでNMOSドライバのゲート電圧が低い状態となるため、本来のオン抵抗よりも高い状態で動作させることになり、電力変換効率が低下してしまう。

【0007】

スイッチング波形のロウレベルからハイレベルへの変化時部分を説明すると、ゲート電圧がハイレベルからNMOSドライバのしきい値電圧を下回ったあたりでNMOSドライバが緩やかにオンからオフとなり、スイッチング波形は緩やかにロウレベルからハイレベルとなる。これにより、スパイクノイズを抑えることができる。しかし、ゲート電圧がハイレベルからしきい値電圧になるまでの時間の方が一般的に長く、ハイレベルからしきい値電圧になるまでNMOSドライバのゲート電圧が低い状態となるため、本来のオン抵抗よりも高い状態で動作させることになり効率が低下してしまう。

【0008】

さらに、ドライバを過電流保護、逆流防止監視用の抵抗として使用している場合に、抵抗値が高いと誤検出する恐れがあるため、十分低いオン抵抗になるオン時間までは過電流保護、逆流防止監視ができなくなり、最小オン時間が長くなってしまう。

昨今は外付け部品を小型化するために、DC/DCコンバータは高周波化してく流れであり、そのためには改善が必要である。

【0009】

本発明は、スイッチングレギュレータ方式のDC/DCコンバータに対してスパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる電源回路及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明にかかる電源回路は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路であって、制御信号に応じた動作を行なって上記出力電圧を制御するための出力トランジスタと、所定の基準電圧と上記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路と、上記誤差増幅回路の出力に基づいて上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタに上記制御信号としてのゲート電圧を出力する制御回路部と、を備え、上記制御回路部は、上記出力トランジスタの上記ゲート電圧を監視するための波形検出回路と、可変な電流容量で上記ゲート電圧を印加するための出力制御回路と、を備え、上記波形検出回路は、上記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて上記ゲート電圧を監視し、上記ゲート電圧が上記基準値以上のときは、上記出力制御回路を、上記ゲート電圧が上記基準値未満のときに比べて高い電流容量で動作させるものである。

【0011】

本発明にかかる電源回路の動作制御方法は、制御信号に応じた動作を行なって出力電圧を制御するための出力トランジスタを備え、入力端子から入力された入力電圧を所定の電圧に変換して上記出力端子から出力する電源回路の動作制御方法であって、所定の基準電圧と上記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路からの出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタの動作制御を行ない、上記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて上記出力トランジスタの上記ゲート電圧を監視し、上記ゲート電圧が上記基準値以上のときは、上記ゲート電圧が上記基準値未満のときに比べて高い電流容量で上記出力トランジスタに上記制御信号としてのゲート電圧を印加する。

【0012】

本発明の電源回路及び動作制御方法は、出力トランジスタのゲート電圧を監視し、ゲート電圧レベルに応じて、印加するゲート電圧について許容電流を変化させる。

【0013】

本発明の電源回路及び動作制御方法は、例えばスイッチングレギュレータ方式のDC/DCコンバータに適用される。ただし、本発明の電源回路及び動作制御方法の適用対象はこれに限定されない。

本発明の電源回路の一態様は、上記出力トランジスタは上記制御信号に応じてスイッチングを行ない、上記出力トランジスタのスイッチングによって上記入力電圧による充電が行なわれるインダクタと、上記出力トランジスタがオフして遮断状態になったときに上記インダクタの放電を行なう整流素子と、備え、上記制御回路部は、上記誤差増幅回路の出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタのスイッチング制御を行なう。

【0014】

本発明の電源回路の動作制御方法の一局面で、上記出力トランジスタは上記制御信号に応じてスイッチングを行ない、上記電源回路は上記出力トランジスタのスイッチングによって上記入力電圧による充電が行なわれるインダクタと、上記出力トランジスタがオフして遮断状態になったときに上記インダクタの放電を行なう整流素子と、を備え、上記制御回路部は、上記誤差増幅回路の出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタのスイッチング制御を行なうものである。

【0015】

この態様及び局面で、DC/DCコンバータのスイッチング波形のハイレベルからロウレベルへの変化時部分を説明すると、比較的低電流容量で出力ドライバにゲート電圧が印加され、ゲート電圧が0Vから出力ドライバのしきい値電圧を越え、出力ドライバが緩やかにオフからオンとなる。この態様及び局面は、スイッチング波形が緩やかにハイレベルからロウレベルとなったことをモード切替え用基準値を用いて検出した後、比較的高電流容量で出力ドライバにゲート電圧を印加し、ゲート電圧を直ちにハイレベルとする。

【0016】

スイッチング波形のロウレベルからハイレベルへの変化時部分を説明すると、この態様及び局面は、比較的高電流容量で出力ドライバにゲート電圧が印加された状態で、ゲート電圧がハイレベルから出力ドライバのしきい値電圧よりも少し上のモード切替え用基準値になったことを検出する。出力ドライバへのゲート電圧の印加を比較的低電流容量に切り替える。出力ドライバが緩やかにオンからオフとなり、スイッチング波形が緩やかにロウレベルからハイレベルとなる。

【0017】

本発明の電源回路において、上記出力制御回路の一例は、低電流駆動能力インバータと、上記低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備えている。上記ゲート電圧が上記基準値以上のときは上記低電流駆動能力インバータ及び上記高電流駆動能力インバータがオンされ、上記ゲート電圧が上記基準値未満のときは上記低電流駆動能力インバータのみがオンされる。ただし、本発明の電源回路において、出力制御回路の構成はこれに限定されず、出力制御回路は、可変な電流容量で上記ゲート電圧を印加できる構成であればどのような構成であってもよい。

【0018】

本発明の電源回路において、上記波形検出回路の一例は、上記ゲート電圧と上記基準値とを比較するコンパレータで形成されている。

本発明の電源回路において、上記波形検出回路の他の例は、上記出力電圧を電源とし、かつ上記基準値をしきい値とするCMOSインバータで形成されている。

ただし、本発明の電源回路において、波形検出回路の構成はこれらに限定されず、出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて出力トランジスタのゲート電圧を監視できる構成であればどのような構成であってもよい。

【発明の効果】

【0019】

本発明にかかる電源回路及びその動作制御方法は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法において、出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて出力トランジスタのゲート電圧を監視し、出力トランジスタのゲート電圧が上記基準値以上のときは、ゲート電圧が上記基準値未満のときに比べて高い電流容量で出力トランジスタにゲート電圧を印加するようにしたので、ゲート電圧レベルに応じて、印加するゲート電圧について許容電流を変化させることができる。これにより、本発明をスイッチングレギュレータ方式のDC/DCコンバータ及びその動作制御方法に適用した場合に、そのDC/DCコンバータを、スパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる。

【0020】

本発明の電源回路において、出力制御回路は、低電流駆動能力インバータと、低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備え、ゲート電圧がモード切替え用基準値以上のときは低電流駆動能力インバータ及び高電流駆動能力インバータがオンされ、ゲート電圧が上記基準値未満のときは低電流駆動能力インバータのみがオンされるようにすれば、簡単な構成で出力制御回路を形成できる。

【0021】

本発明の電源回路において、波形検出回路は、ゲート電圧と基準値とを比較するコンパレータで形成されているか、出力電圧を電源とし、かつ基準値をしきい値とするCMOSインバータで形成されているようにすれば、簡単な構成で波形検出回路を形成できる。

【図面の簡単な説明】

【0022】

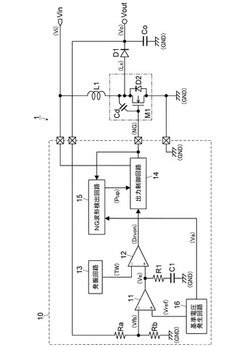

【図1】実施例を説明するための回路図である。

【図2】同実施例における出力制御回路の一例を説明するための回路図である。

【図3】同実施例におけるNG波形検出回路の一例を説明するための回路図である。

【図4】同実施例における出力制御回路及びNG波形検出回路の動作を説明するためのタイミングチャートである。

【図5】NG波形検出回路の他の例を説明するための回路図である。

【発明を実施するための形態】

【0023】

図1は、電源回路の一実施例を説明するための回路図である。

図1において、電源回路1は、入力端子Vinに入力された入力電圧Viを所定の定電圧に昇圧し、出力電圧Voとして出力端子Voutから出力する非同期整流型の昇圧型スイッチングレギュレータをなしている。

電源回路1は、NMOSFETからなるNMOSドライバM1と、整流用のダイオードD1とを備えている。

【0024】

さらに、電源回路1は、出力電圧検出用の抵抗R1,R2、インダクタL1、出力コンデンサCo、位相補償用の抵抗R1及びコンデンサC1、誤差増幅回路11、PWMコンパレータ12、発振回路13、出力制御回路14、NG波形検出回路15並びに基準電圧発生回路16を備えている。符号CdはNMOSドライバM1のドレイン−ゲート間容量である。符号D2はNMOSドライバM1のボディダイオードである。

【0025】

電源回路1において、NMOSドライバM1、ダイオードD1、インダクタL1及び出力コンデンサCoを除く各回路は半導体チップ10内に形成されている。ここで、NMOSドライバM1及びダイオードD1の一方又は両方は半導体チップ10内に形成されていてもよい。

【0026】

なお、図1では、NMOSドライバM1が出力トランジスタを、ダイオードD1が整流素子をそれぞれなし、誤差増幅回路11、PWMコンパレータ12、発振回路13、出力制御回路14、NG波形検出回路、基準電圧発生回路16、抵抗Ra,Rb,R1及びコンデンサC1は制御回路部をなす。

【0027】

基準電圧発生回路16は、所定の基準電圧Vrefとモード切替え用基準値Vaを生成して出力する。基準電圧Vrefとモード切替え用基準値Vaは互いに異なる値であってもよいし、同じ値であってもよい。出力電圧検出用の抵抗R1,R2は、出力電圧Voを分圧して帰還電圧Vfbを生成して出力する。誤差増幅回路11は、入力された帰還電圧Vfbと基準電圧Vrefとの電圧差を増幅して誤差電圧Veを生成して出力する。発振回路13は所定の三角波信号TWを生成して出力する。PWMコンパレータ12は誤差増幅回路11からの誤差電圧Veと発振回路13からの三角波信号TWからPWM制御を行なうためのパルス信号Drvonを生成して出力する。パルス信号Drvonは、出力制御回路14を介してNMOSドライバM1のゲートに入力される。

【0028】

NG波形検出回路15は、基準電圧発生回路11からのモード切替え用基準値Vaを用いてNMOSドライバM1のゲート電圧NGを監視し、ゲート電圧NGの高さに応じたLx波形Lレベル検出信号Pupを出力する。NG波形検出回路15は、ゲート電圧NGがモード切替え用基準値Va以上のときはハイレベルの信号を出力し、ゲート電圧NGがモード切替え用基準値Va未満のときはロウレベルの信号を出力する。モード切替え用基準値VaはNMOSドライバM1のしきい値電圧Vthよりも高い値に設定されている。

出力制御回路14は、PWMコンパレータ12からのパルス信号Drvon及びNG波形検出回路15からのLx波形Lレベル検出信号Pupに基づいて、可変な電流容量でNMOSドライバM1のゲートにゲート電圧NGを印加する。

【0029】

入力端子VinとNMOSドライバM1のドレインとの間にインダクタL1が接続されている。NMOSドライバM1のソースは接地電圧GNDに接続されている。

インダクタL1とNMOSドライバM1との接続部にダイオードD1のアノードが接続されている。ダイオードD1のカソードは出力端子Voutに接続されている。

出力端子Voutと接地電圧GNDとの間に、出力コンデンサCoが接続されるとともに、抵抗Ra,Rbが直列に接続されている。抵抗Raと抵抗Rbの間の電圧が帰還抵抗Vfbになる。

【0030】

誤差増幅回路11において、反転入力端には帰還電圧Vfbが、非反転入力端には基準電圧Vrefが入力される。誤差増幅回路11の出力端はPWMコンパレータ12の非反転入力端に接続されている。誤差増幅回路11の出力端と接地電圧GNDとの間には、抵抗R1及びコンデンサC1の直列回路が接続されている。

PWMコンパレータ12の反転入力端には三角波信号TWが入力される。PWMコンパレータ12から出力されたパルス信号Drvonは、出力制御回路14に入力される。

出力制御回路14は、PWMコンパレータ12からのパルス信号Drvon及びNG波形検出回路15からのLx波形Lレベル検出信号Pupに基づいて、可変な電流容量でNMOSドライバM1にゲート電圧を印加する。

【0031】

図2は、出力制御回路14の一例を説明するための回路図である。

出力制御回路14は、NOT回路21,22、OR回路23、AND回路24及びインバータ25,26を備えている。

NOT回路21にLx波形Lレベル検出信号Pupが入力される。NOT回路22にパルス信号Drvonが入力される。OR回路22にNOT回路21の出力とNOT回路22の出力が入力される。AND回路24にLx波形Lレベル検出信号PupとNOT回路22の出力が入力される。

【0032】

低電流容量インバータ25は、入力電圧Viと接地電位GNDの間に直列接続されたPMOSトランジスタM21とNMOSトランジスタM22を備えている。トランジスタM21,M22のゲートにNOT回路22の出力が入力される。低電流容量インバータ25の出力はNMOSドライバM1のゲートに印加されるゲート電圧NGとして出力される。

【0033】

高電流容量インバータ26は、入力電圧Viと接地電位GNDの間に直列接続されたPMOSトランジスタM23とNMOSトランジスタM24を備えている。トランジスタM23のゲートにOR回路23の出力が入力される。トランジスタM24のゲートにAND回路24の出力が入力される。高電流容量インバータ26の出力はNMOSドライバM1のゲートに印加されるゲート電圧NGとして出力される。

【0034】

高電流容量インバータ26の電流駆動能力は低電流容量インバータ25の電流駆動能力に比べて高い。例えば、高電流容量インバータ26のPMOSトランジスタM21は、低電流容量インバータ25のPMOSトランジスタM23の電流駆動能力に比べて10倍程度の電流駆動能力をもち、高電流容量インバータ26のNMOSトランジスタM22は、低電流容量インバータ25のNMOSトランジスタM24の電流駆動能力に比べて10倍程度の電流駆動能力をもつ。

【0035】

出力制御回路14は、NOT回路22によってパルス信号Drvonを反転した信号をインバータ25,26によってさらに反転した信号をゲート電圧NGとして出力する。

パルス信号Drvon及び検出信号Pupがともにロウレベルのとき、MOSトランジスタM22はオンし、MOSトランジスタM21,M23,M24はオフし、ゲート電圧NGは比較的高い電流容量をもって接地電位GNDに接続される。

パルス信号Drvonがハイレベルで検出信号Pupがロウレベルのとき、MOSトランジスタM21はオンし、MOSトランジスタM22,M23,M24はオフし、ゲート電圧NGは比較的低い電流容量をもって入力電圧Viに接続される。

パルス信号Drvon及び検出信号Pupがともにハイレベルのとき、MOSトランジスタM21,M23はオンし、MOSトランジスタM22,M24はオフし、ゲート電圧NGは比較的高い電流容量をもって入力電圧Viに接続される。

パルス信号Drvonがロウレベルで検出信号Pupがハイレベルのとき、MOSトランジスタM22,M24はオンし、MOSトランジスタM21,M23はオフし、ゲート電圧NGは比較的低い電流容量をもって接地電位GNDに接続される。

【0036】

図3は、NG波形検出回路15の一例を説明するための回路図である。

NG波形検出回路15は、ゲート電圧NGとモード切替え用基準値Vaとを比較するコンパレータ31で形成されている。コンパレータ31において、反転入力端にゲート電圧NGが入力され、非反転入力端にモード切替え用基準値Vaが入力される。コンパレータ31は、ゲート電圧NGがモード切替え用基準値Va以上のときはハイレベルの信号を出力し、ゲート電圧NGがモード切替え用基準値Va未満のときはロウレベルの信号を出力する。

【0037】

図1を参照して、電源回路1の動作を説明する。

電源回路1の誤差増幅回路11は、基準電圧Vrefと帰還電圧Vfbとの電圧差を増幅して誤差電圧Veを生成し、PWMコンパレータ12の非反転入力端に出力する。PWMコンパレータ12は、三角波信号TWの電圧が誤差電圧Ve未満の場合はハイレベルの信号を出力し、三角波信号TWの電圧が誤差電圧Ve以上である場合はロウレベルの信号を出力する。すなわち、PWMコンパレータ12は、誤差電圧Veに応じて出力するパルス信号Drvonのデューティサイクルを変化させる。

【0038】

NMOSドライバM1は、ゲートがハイレベルのときはオンして導通状態になり、ゲートがロウレベルのときはオフして遮断状態になる。NMOSドライバM1がオンしているとき、入力端子VinからインダクタL1とNMOSドライバM1を通って接地電圧GNDに電流が流れ、インダクタL1にエネルギーが蓄積される。NMOSドライバM1がオフすると、インダクタL1とNMOSドライバM1との接続部の電圧Lxは、インダクタL1の逆起電力の影響で入力電圧Viよりも高い電圧になる。インダクタL1に蓄積されたエネルギーが、ダイオードD1を介して出力コンデンサCoを充電するとともに出力端子Voutに接続された負荷に供給される。

【0039】

出力電圧Voが低下して帰還電圧Vfbが低下すると、誤差増幅回路11からの誤差電圧Veが上昇する。誤差電圧VeはPWMコンパレータ12の非反転入力端に入力されているため、誤差電圧Veが上昇するとPWMコンパレータ12から出力されたパルス信号Drvonのハイレベルの時間が長くなるとともにロウレベルの時間が短くなる。このため、NMOSドライバM1がオンする時間が長くなってインダクタL1に蓄えられるエネルギーが増加することから、出力電圧Voは上昇する。逆に、出力電圧Voが上昇して帰還電圧Vfbが上昇すると、誤差電圧Veが低下する。すると、PWMコンパレータ12から出力されるパルス信号Drvonのハイレベルの時間が短くなるとともにロウレベルの時間が長くなる。このため、NMOSドライバM1がオンする時間が短くなり、インダクタL1に蓄えられるエネルギーも減少することから、出力電圧Voは低下する。このような動作を繰り返すことにより、出力電圧Voは所定の電圧に維持される。

【0040】

図4は、出力制御回路14及びNG波形検出回路15の動作を説明するためのタイミングチャートである。

t0:

パルス信号Drvonがロウレベルからハイレベルへの変化時になる。ゲート電圧NGがモード切替え用基準値Va未満なので、Lx波形Lレベル検出信号Pupはロウレベルである。出力制御回路14のMOSトランジスタM21はオンし、MOSトランジスタM22,23,24はオフ状態で、ゲート電圧NGのノードをドライブする能力は低く抑えられている。

【0041】

t0〜t1:

ゲート電圧NGのノードをドライブする能力が低いため、ゲート電圧NGは緩やかに上昇し、NMOSドライバM1のしきい値電圧Vthを越えたあたりで、NMOSドライバM1がオンし、Lx波形がハイレベルから下がりだす。

【0042】

t1〜t2:

NMOSドライバM1のゲート電圧NGがしきい値電圧Vth付近のため、NMOSドライバは飽和領域で動作することになる。ゲート電圧NGはしきい値電圧Vth以上に上がろうとするが、ドレイン−ゲート間容量Cdがミラー効果により大きな容量として見えるため、Lx波形がロウレベルになるまで、しきい値電圧Vth付近で非常に緩やかな傾斜で上昇する。これにより、Lx波形の高周波成分が抑えられ、スパイクノイズを抑制することができる。一方、NMOSドライバM1の抵抗値は非常に高く、この間は電力変換効率が低下する。

【0043】

t2〜t3:

Lx波形がロウレベルになると、ドレイン−ゲート間容量Cdへのチャージが不要となり、ゲート電圧NGが緩やかに上昇し、モード切替え用基準値Vaに到達する。

【0044】

t3:ゲート電圧NGがモード切替え用基準値Va以上なので、NG波形検出回路15の検出信号Pupはロウレベルからハイレベルへの変化時になる。出力制御回路14において、MOSトランジスタM21がオン、MOSトランジスタM22,23,24がオフの状態から、MOSトランジスタM22〜24が動作可能状態となる。このとき、パルス信号Drvonがハイレベルなので、MOSトランジスタM22〜24のうちMOSトランジスタM23のみがオンし、ゲート電圧NGを急激にハイレベルに吊り上げる。これにより、NMOSドライバM1が線形領域となり抵抗値が本来の低いものになり、電力変換効率に影響がなくなる。

従来技術の回路であれば、ゲート電圧NGがハイレベルまで緩やかに上昇する間、NMOSドライバM1の抵抗値が高くなるため、電力変換効率が低下したり、NMOSドライバM1を電流検出用の抵抗として使用している場合には誤検出する原因となったりしていたが、本発明はこれらの不具合を解消できる。

【0045】

t4:

パルス信号Drvonがハイレベルからロウレベルへの変化時となる。このとき、検出信号Pupがハイレベルで、出力制御回路14はゲート電圧NGのノードをドライブする能力が高いため、NMOSドライバM1が線形領域であり、ゲート電圧NGは急峻に低下する。

従来技術の回路であれば、ゲート電圧NGがロウレベルまで緩やかに下降する間、NMOSドライバM1の抵抗値が高くなるため、電力変換効率が低下する。本発明はこの不具合を解消できる。

ゲート電圧NGがモード切替え用基準値Va未満となると検出信号Pupがロウレベルとなり、ゲート電圧NGのノードをドライブする能力は低く抑えられ、ゲート電圧NGがしきい値電圧Vth付近まで緩やかに下降する。

【0046】

t5〜t6:

NMOSドライバM1のしきい値電圧Vth付近に近づくと、NMOSドライバM1は飽和領域で動作する。ゲート電圧NGはしきい値電圧Vth以下に下がろうとするが、ドレイン−ゲート間容量Cdがミラー効果により大きな容量として見えるため、Lx波形がハイレベルになるまで、しきい値電圧Vth付近で非常に緩やかな傾斜で下降する。その結果、Lx波形の高周波成分が抑えられ、スパイクノイズを抑制することができる。一方、NMOSドライバM1の抵抗値が非常に高く、この間は効率が低下する。

【0047】

t7:

Lx波形がハイレベルになるとドレイン−ゲート間容量Cdへのチャージが不要となり、ゲート電圧NGは緩やかに下降し、ロウレベルに到達する。

このように、本発明は、スイッチング方式のDC/DCコンバータにおいて、スパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる。

【0048】

図5は、NG波形検出回路15の他の例を説明するための回路図である。

NG波形検出回路15は、出力電圧Voを電源とするCMOSインバータ51で形成されている。CMOSインバータ51のしきい値はモード切替え用基準値Vaに設定されている。例えば、PMOSトランジスタM51に対してNMOSトランジスタM52の電流駆動能力を数倍以上に設定することで、CMOSインバータ51のしきい値をNMOSドライバM1のしきい値電圧を上回る所望のモード切替え用基準値Vaに設定すればよい。

CMOSインバータ51は、ゲート電圧NGがモード切替え用基準値Va以上になると、ハイレベルのLx波形Lレベル検出信号Pupを出力する。

【0049】

上記実施例では、非同期整流型のスイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、同期整流型のスイッチングレギュレータにも適用することができる。この場合、例えば、図1のダイオードD1の代わりにPMOSトランジスタからなる同期整流用トランジスタを使用して、該同期整流用トランジスタがNMOSドライバM1と相反するスイッチング動作を行なうように、該同期整流用トランジスタのゲートをNMOSドライバM1のゲートにそれぞれ接続するようにしてもよい。

【0050】

また、上記実施例では、PWM制御を行なう場合のスイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、PFM制御等を行なう場合のスイッチングレギュレータにも適用することができる。

また、上記実施例では、昇圧型スイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、降圧型スイッチングレギュレータ、反転型スイッチングレギュレータ及びシリーズレギュレータ等のリニアレギュレータにも適用することができる。

【0051】

このように、本発明は、出力電圧Voutを分圧して帰還電圧Vfbを生成し、帰還電圧Vfbを基に誤差増幅回路を使用して出力電圧Voutが所定の電圧で一定になるように出力トランジスタの動作制御を行う構成の電源回路に対して適用することができる。

さらに、本発明は、インダクタL1に流れたインダクタ電流を検出し、該検出したインダクタ電流を基に誤差増幅回路を使用して出力電圧Voutが所定の電圧で一定になるように出力トランジスタの動作制御を行う構成の電流モード制御型スイッチングレギュレータにも適用することができる。

【0052】

以上、本発明の実施例を説明したが、回路構成や配置、サイズ、数値等は一例であり、本発明はこれらに限定されるものではなく、特許請求の範囲に記載された本発明の範囲内で種々の変更が可能である。

【産業上の利用可能性】

【0053】

本発明は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法、例えばDC/DCコンバータ及びその動作制御方法に応用できる。

【符号の説明】

【0054】

1 電源回路

11 差動増幅回路

14 出力制御回路

15 NG波形検出回路

25 低電流駆動能力インバータ

26 高電流駆動能力インバータ

31 コンパレータ

51 CMOSインバータ

D1 整流素子

L1 インダクタ

M1 出力トランジスタ

Vin 入力端子

Vout 出力端子

Drvon 制御信号

NG ゲート電圧

Va モード切替え用基準値

Vi 入力電圧

Vo 出力電圧

Vref 基準電圧

Vfb 帰還電圧

【先行技術文献】

【特許文献】

【0055】

【特許文献1】特開2010−178555号公報

【技術分野】

【0001】

本発明は、電源回路及びその動作制御方法に関し、特に、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法に関するものである。本発明の電源回路及びその動作制御方法は例えばスイッチングレギュレータ方式のDC/DCコンバータに適用される。

【背景技術】

【0002】

入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路として、例えばスイッチングレギュレータ方式のDC/DCコンバータがある。

スイッチングレギュレータ方式のDC/DCコンバータにおいて、スパイクノイズを抑えるためスイッチング波形の高周波成分をなまらせる必要がある。

【0003】

例えば昇圧型DC/DCコンバータを例に挙げて説明すると、NMOSFET(N-channel Metal Oxide Semiconductor Field Effect Transistor)からなるNMOSドライバを駆動するためのCMOSインバータ(以下プリドライバと呼ぶ。)のドライブ能力(電流駆動能力)を低下させることで、スイッチング波形のハイレベルからロウレベルへの変化時及びロウレベルからハイレベルへの変化時における高周波成分をなまらせることが既に知られている。

【0004】

例えば、スパイクノイズを抑える目的で、駆動用スイッチング素子をオン状態からオフ状態へ移行させる際の駆動信号の遷移時間よりも、スイッチング素子をオフ状態からオン状態へ移行させる際の駆動信号の遷移時間の方が長くなるように駆動信号を生成することが提案されている(特許文献1を参照。)。具体的には、駆動用素子の駆動信号を作るCMOSインバータのPMOS(P-channel MOS)の電流駆動能力の方が、NMOSのそれより大きく、整流用素子の駆動信号を作るCMOSインバータのNMOSの電流駆動能力の方が、PMOSのそれより大きくすることで、スパイクノイズを低減する構成が特許文献1に開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、NMOSドライバを駆動するCMOSインバータのドライブ能力を低下させる手法では、NMOSドライバのゲート電圧が低く、オン抵抗が高い状態が長くなるので、電力変換効率が低下や最小オン時間が長くなるという問題があった。

【0006】

具体的には、スイッチング波形のハイレベルからロウレベルへの変化部分を説明すると、ゲート電圧が0VからNMOSドライバのしきい値電圧を越えたあたりでNMOSドライバが緩やかにオフからオンとなり、スイッチング波形は緩やかにハイレベルからロウレベルとなる。これによりスパイクノイズを抑えることができる。しかし、ゲート電圧がしきい値電圧からハイレベルになるまでの時間の方が一般的に長く、しきい値電圧からハイレベルまでNMOSドライバのゲート電圧が低い状態となるため、本来のオン抵抗よりも高い状態で動作させることになり、電力変換効率が低下してしまう。

【0007】

スイッチング波形のロウレベルからハイレベルへの変化時部分を説明すると、ゲート電圧がハイレベルからNMOSドライバのしきい値電圧を下回ったあたりでNMOSドライバが緩やかにオンからオフとなり、スイッチング波形は緩やかにロウレベルからハイレベルとなる。これにより、スパイクノイズを抑えることができる。しかし、ゲート電圧がハイレベルからしきい値電圧になるまでの時間の方が一般的に長く、ハイレベルからしきい値電圧になるまでNMOSドライバのゲート電圧が低い状態となるため、本来のオン抵抗よりも高い状態で動作させることになり効率が低下してしまう。

【0008】

さらに、ドライバを過電流保護、逆流防止監視用の抵抗として使用している場合に、抵抗値が高いと誤検出する恐れがあるため、十分低いオン抵抗になるオン時間までは過電流保護、逆流防止監視ができなくなり、最小オン時間が長くなってしまう。

昨今は外付け部品を小型化するために、DC/DCコンバータは高周波化してく流れであり、そのためには改善が必要である。

【0009】

本発明は、スイッチングレギュレータ方式のDC/DCコンバータに対してスパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる電源回路及びその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明にかかる電源回路は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路であって、制御信号に応じた動作を行なって上記出力電圧を制御するための出力トランジスタと、所定の基準電圧と上記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路と、上記誤差増幅回路の出力に基づいて上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタに上記制御信号としてのゲート電圧を出力する制御回路部と、を備え、上記制御回路部は、上記出力トランジスタの上記ゲート電圧を監視するための波形検出回路と、可変な電流容量で上記ゲート電圧を印加するための出力制御回路と、を備え、上記波形検出回路は、上記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて上記ゲート電圧を監視し、上記ゲート電圧が上記基準値以上のときは、上記出力制御回路を、上記ゲート電圧が上記基準値未満のときに比べて高い電流容量で動作させるものである。

【0011】

本発明にかかる電源回路の動作制御方法は、制御信号に応じた動作を行なって出力電圧を制御するための出力トランジスタを備え、入力端子から入力された入力電圧を所定の電圧に変換して上記出力端子から出力する電源回路の動作制御方法であって、所定の基準電圧と上記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路からの出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタの動作制御を行ない、上記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて上記出力トランジスタの上記ゲート電圧を監視し、上記ゲート電圧が上記基準値以上のときは、上記ゲート電圧が上記基準値未満のときに比べて高い電流容量で上記出力トランジスタに上記制御信号としてのゲート電圧を印加する。

【0012】

本発明の電源回路及び動作制御方法は、出力トランジスタのゲート電圧を監視し、ゲート電圧レベルに応じて、印加するゲート電圧について許容電流を変化させる。

【0013】

本発明の電源回路及び動作制御方法は、例えばスイッチングレギュレータ方式のDC/DCコンバータに適用される。ただし、本発明の電源回路及び動作制御方法の適用対象はこれに限定されない。

本発明の電源回路の一態様は、上記出力トランジスタは上記制御信号に応じてスイッチングを行ない、上記出力トランジスタのスイッチングによって上記入力電圧による充電が行なわれるインダクタと、上記出力トランジスタがオフして遮断状態になったときに上記インダクタの放電を行なう整流素子と、備え、上記制御回路部は、上記誤差増幅回路の出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタのスイッチング制御を行なう。

【0014】

本発明の電源回路の動作制御方法の一局面で、上記出力トランジスタは上記制御信号に応じてスイッチングを行ない、上記電源回路は上記出力トランジスタのスイッチングによって上記入力電圧による充電が行なわれるインダクタと、上記出力トランジスタがオフして遮断状態になったときに上記インダクタの放電を行なう整流素子と、を備え、上記制御回路部は、上記誤差増幅回路の出力に基づいて、上記出力電圧が上記所定の電圧で一定になるように上記出力トランジスタのスイッチング制御を行なうものである。

【0015】

この態様及び局面で、DC/DCコンバータのスイッチング波形のハイレベルからロウレベルへの変化時部分を説明すると、比較的低電流容量で出力ドライバにゲート電圧が印加され、ゲート電圧が0Vから出力ドライバのしきい値電圧を越え、出力ドライバが緩やかにオフからオンとなる。この態様及び局面は、スイッチング波形が緩やかにハイレベルからロウレベルとなったことをモード切替え用基準値を用いて検出した後、比較的高電流容量で出力ドライバにゲート電圧を印加し、ゲート電圧を直ちにハイレベルとする。

【0016】

スイッチング波形のロウレベルからハイレベルへの変化時部分を説明すると、この態様及び局面は、比較的高電流容量で出力ドライバにゲート電圧が印加された状態で、ゲート電圧がハイレベルから出力ドライバのしきい値電圧よりも少し上のモード切替え用基準値になったことを検出する。出力ドライバへのゲート電圧の印加を比較的低電流容量に切り替える。出力ドライバが緩やかにオンからオフとなり、スイッチング波形が緩やかにロウレベルからハイレベルとなる。

【0017】

本発明の電源回路において、上記出力制御回路の一例は、低電流駆動能力インバータと、上記低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備えている。上記ゲート電圧が上記基準値以上のときは上記低電流駆動能力インバータ及び上記高電流駆動能力インバータがオンされ、上記ゲート電圧が上記基準値未満のときは上記低電流駆動能力インバータのみがオンされる。ただし、本発明の電源回路において、出力制御回路の構成はこれに限定されず、出力制御回路は、可変な電流容量で上記ゲート電圧を印加できる構成であればどのような構成であってもよい。

【0018】

本発明の電源回路において、上記波形検出回路の一例は、上記ゲート電圧と上記基準値とを比較するコンパレータで形成されている。

本発明の電源回路において、上記波形検出回路の他の例は、上記出力電圧を電源とし、かつ上記基準値をしきい値とするCMOSインバータで形成されている。

ただし、本発明の電源回路において、波形検出回路の構成はこれらに限定されず、出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて出力トランジスタのゲート電圧を監視できる構成であればどのような構成であってもよい。

【発明の効果】

【0019】

本発明にかかる電源回路及びその動作制御方法は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法において、出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて出力トランジスタのゲート電圧を監視し、出力トランジスタのゲート電圧が上記基準値以上のときは、ゲート電圧が上記基準値未満のときに比べて高い電流容量で出力トランジスタにゲート電圧を印加するようにしたので、ゲート電圧レベルに応じて、印加するゲート電圧について許容電流を変化させることができる。これにより、本発明をスイッチングレギュレータ方式のDC/DCコンバータ及びその動作制御方法に適用した場合に、そのDC/DCコンバータを、スパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる。

【0020】

本発明の電源回路において、出力制御回路は、低電流駆動能力インバータと、低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備え、ゲート電圧がモード切替え用基準値以上のときは低電流駆動能力インバータ及び高電流駆動能力インバータがオンされ、ゲート電圧が上記基準値未満のときは低電流駆動能力インバータのみがオンされるようにすれば、簡単な構成で出力制御回路を形成できる。

【0021】

本発明の電源回路において、波形検出回路は、ゲート電圧と基準値とを比較するコンパレータで形成されているか、出力電圧を電源とし、かつ基準値をしきい値とするCMOSインバータで形成されているようにすれば、簡単な構成で波形検出回路を形成できる。

【図面の簡単な説明】

【0022】

【図1】実施例を説明するための回路図である。

【図2】同実施例における出力制御回路の一例を説明するための回路図である。

【図3】同実施例におけるNG波形検出回路の一例を説明するための回路図である。

【図4】同実施例における出力制御回路及びNG波形検出回路の動作を説明するためのタイミングチャートである。

【図5】NG波形検出回路の他の例を説明するための回路図である。

【発明を実施するための形態】

【0023】

図1は、電源回路の一実施例を説明するための回路図である。

図1において、電源回路1は、入力端子Vinに入力された入力電圧Viを所定の定電圧に昇圧し、出力電圧Voとして出力端子Voutから出力する非同期整流型の昇圧型スイッチングレギュレータをなしている。

電源回路1は、NMOSFETからなるNMOSドライバM1と、整流用のダイオードD1とを備えている。

【0024】

さらに、電源回路1は、出力電圧検出用の抵抗R1,R2、インダクタL1、出力コンデンサCo、位相補償用の抵抗R1及びコンデンサC1、誤差増幅回路11、PWMコンパレータ12、発振回路13、出力制御回路14、NG波形検出回路15並びに基準電圧発生回路16を備えている。符号CdはNMOSドライバM1のドレイン−ゲート間容量である。符号D2はNMOSドライバM1のボディダイオードである。

【0025】

電源回路1において、NMOSドライバM1、ダイオードD1、インダクタL1及び出力コンデンサCoを除く各回路は半導体チップ10内に形成されている。ここで、NMOSドライバM1及びダイオードD1の一方又は両方は半導体チップ10内に形成されていてもよい。

【0026】

なお、図1では、NMOSドライバM1が出力トランジスタを、ダイオードD1が整流素子をそれぞれなし、誤差増幅回路11、PWMコンパレータ12、発振回路13、出力制御回路14、NG波形検出回路、基準電圧発生回路16、抵抗Ra,Rb,R1及びコンデンサC1は制御回路部をなす。

【0027】

基準電圧発生回路16は、所定の基準電圧Vrefとモード切替え用基準値Vaを生成して出力する。基準電圧Vrefとモード切替え用基準値Vaは互いに異なる値であってもよいし、同じ値であってもよい。出力電圧検出用の抵抗R1,R2は、出力電圧Voを分圧して帰還電圧Vfbを生成して出力する。誤差増幅回路11は、入力された帰還電圧Vfbと基準電圧Vrefとの電圧差を増幅して誤差電圧Veを生成して出力する。発振回路13は所定の三角波信号TWを生成して出力する。PWMコンパレータ12は誤差増幅回路11からの誤差電圧Veと発振回路13からの三角波信号TWからPWM制御を行なうためのパルス信号Drvonを生成して出力する。パルス信号Drvonは、出力制御回路14を介してNMOSドライバM1のゲートに入力される。

【0028】

NG波形検出回路15は、基準電圧発生回路11からのモード切替え用基準値Vaを用いてNMOSドライバM1のゲート電圧NGを監視し、ゲート電圧NGの高さに応じたLx波形Lレベル検出信号Pupを出力する。NG波形検出回路15は、ゲート電圧NGがモード切替え用基準値Va以上のときはハイレベルの信号を出力し、ゲート電圧NGがモード切替え用基準値Va未満のときはロウレベルの信号を出力する。モード切替え用基準値VaはNMOSドライバM1のしきい値電圧Vthよりも高い値に設定されている。

出力制御回路14は、PWMコンパレータ12からのパルス信号Drvon及びNG波形検出回路15からのLx波形Lレベル検出信号Pupに基づいて、可変な電流容量でNMOSドライバM1のゲートにゲート電圧NGを印加する。

【0029】

入力端子VinとNMOSドライバM1のドレインとの間にインダクタL1が接続されている。NMOSドライバM1のソースは接地電圧GNDに接続されている。

インダクタL1とNMOSドライバM1との接続部にダイオードD1のアノードが接続されている。ダイオードD1のカソードは出力端子Voutに接続されている。

出力端子Voutと接地電圧GNDとの間に、出力コンデンサCoが接続されるとともに、抵抗Ra,Rbが直列に接続されている。抵抗Raと抵抗Rbの間の電圧が帰還抵抗Vfbになる。

【0030】

誤差増幅回路11において、反転入力端には帰還電圧Vfbが、非反転入力端には基準電圧Vrefが入力される。誤差増幅回路11の出力端はPWMコンパレータ12の非反転入力端に接続されている。誤差増幅回路11の出力端と接地電圧GNDとの間には、抵抗R1及びコンデンサC1の直列回路が接続されている。

PWMコンパレータ12の反転入力端には三角波信号TWが入力される。PWMコンパレータ12から出力されたパルス信号Drvonは、出力制御回路14に入力される。

出力制御回路14は、PWMコンパレータ12からのパルス信号Drvon及びNG波形検出回路15からのLx波形Lレベル検出信号Pupに基づいて、可変な電流容量でNMOSドライバM1にゲート電圧を印加する。

【0031】

図2は、出力制御回路14の一例を説明するための回路図である。

出力制御回路14は、NOT回路21,22、OR回路23、AND回路24及びインバータ25,26を備えている。

NOT回路21にLx波形Lレベル検出信号Pupが入力される。NOT回路22にパルス信号Drvonが入力される。OR回路22にNOT回路21の出力とNOT回路22の出力が入力される。AND回路24にLx波形Lレベル検出信号PupとNOT回路22の出力が入力される。

【0032】

低電流容量インバータ25は、入力電圧Viと接地電位GNDの間に直列接続されたPMOSトランジスタM21とNMOSトランジスタM22を備えている。トランジスタM21,M22のゲートにNOT回路22の出力が入力される。低電流容量インバータ25の出力はNMOSドライバM1のゲートに印加されるゲート電圧NGとして出力される。

【0033】

高電流容量インバータ26は、入力電圧Viと接地電位GNDの間に直列接続されたPMOSトランジスタM23とNMOSトランジスタM24を備えている。トランジスタM23のゲートにOR回路23の出力が入力される。トランジスタM24のゲートにAND回路24の出力が入力される。高電流容量インバータ26の出力はNMOSドライバM1のゲートに印加されるゲート電圧NGとして出力される。

【0034】

高電流容量インバータ26の電流駆動能力は低電流容量インバータ25の電流駆動能力に比べて高い。例えば、高電流容量インバータ26のPMOSトランジスタM21は、低電流容量インバータ25のPMOSトランジスタM23の電流駆動能力に比べて10倍程度の電流駆動能力をもち、高電流容量インバータ26のNMOSトランジスタM22は、低電流容量インバータ25のNMOSトランジスタM24の電流駆動能力に比べて10倍程度の電流駆動能力をもつ。

【0035】

出力制御回路14は、NOT回路22によってパルス信号Drvonを反転した信号をインバータ25,26によってさらに反転した信号をゲート電圧NGとして出力する。

パルス信号Drvon及び検出信号Pupがともにロウレベルのとき、MOSトランジスタM22はオンし、MOSトランジスタM21,M23,M24はオフし、ゲート電圧NGは比較的高い電流容量をもって接地電位GNDに接続される。

パルス信号Drvonがハイレベルで検出信号Pupがロウレベルのとき、MOSトランジスタM21はオンし、MOSトランジスタM22,M23,M24はオフし、ゲート電圧NGは比較的低い電流容量をもって入力電圧Viに接続される。

パルス信号Drvon及び検出信号Pupがともにハイレベルのとき、MOSトランジスタM21,M23はオンし、MOSトランジスタM22,M24はオフし、ゲート電圧NGは比較的高い電流容量をもって入力電圧Viに接続される。

パルス信号Drvonがロウレベルで検出信号Pupがハイレベルのとき、MOSトランジスタM22,M24はオンし、MOSトランジスタM21,M23はオフし、ゲート電圧NGは比較的低い電流容量をもって接地電位GNDに接続される。

【0036】

図3は、NG波形検出回路15の一例を説明するための回路図である。

NG波形検出回路15は、ゲート電圧NGとモード切替え用基準値Vaとを比較するコンパレータ31で形成されている。コンパレータ31において、反転入力端にゲート電圧NGが入力され、非反転入力端にモード切替え用基準値Vaが入力される。コンパレータ31は、ゲート電圧NGがモード切替え用基準値Va以上のときはハイレベルの信号を出力し、ゲート電圧NGがモード切替え用基準値Va未満のときはロウレベルの信号を出力する。

【0037】

図1を参照して、電源回路1の動作を説明する。

電源回路1の誤差増幅回路11は、基準電圧Vrefと帰還電圧Vfbとの電圧差を増幅して誤差電圧Veを生成し、PWMコンパレータ12の非反転入力端に出力する。PWMコンパレータ12は、三角波信号TWの電圧が誤差電圧Ve未満の場合はハイレベルの信号を出力し、三角波信号TWの電圧が誤差電圧Ve以上である場合はロウレベルの信号を出力する。すなわち、PWMコンパレータ12は、誤差電圧Veに応じて出力するパルス信号Drvonのデューティサイクルを変化させる。

【0038】

NMOSドライバM1は、ゲートがハイレベルのときはオンして導通状態になり、ゲートがロウレベルのときはオフして遮断状態になる。NMOSドライバM1がオンしているとき、入力端子VinからインダクタL1とNMOSドライバM1を通って接地電圧GNDに電流が流れ、インダクタL1にエネルギーが蓄積される。NMOSドライバM1がオフすると、インダクタL1とNMOSドライバM1との接続部の電圧Lxは、インダクタL1の逆起電力の影響で入力電圧Viよりも高い電圧になる。インダクタL1に蓄積されたエネルギーが、ダイオードD1を介して出力コンデンサCoを充電するとともに出力端子Voutに接続された負荷に供給される。

【0039】

出力電圧Voが低下して帰還電圧Vfbが低下すると、誤差増幅回路11からの誤差電圧Veが上昇する。誤差電圧VeはPWMコンパレータ12の非反転入力端に入力されているため、誤差電圧Veが上昇するとPWMコンパレータ12から出力されたパルス信号Drvonのハイレベルの時間が長くなるとともにロウレベルの時間が短くなる。このため、NMOSドライバM1がオンする時間が長くなってインダクタL1に蓄えられるエネルギーが増加することから、出力電圧Voは上昇する。逆に、出力電圧Voが上昇して帰還電圧Vfbが上昇すると、誤差電圧Veが低下する。すると、PWMコンパレータ12から出力されるパルス信号Drvonのハイレベルの時間が短くなるとともにロウレベルの時間が長くなる。このため、NMOSドライバM1がオンする時間が短くなり、インダクタL1に蓄えられるエネルギーも減少することから、出力電圧Voは低下する。このような動作を繰り返すことにより、出力電圧Voは所定の電圧に維持される。

【0040】

図4は、出力制御回路14及びNG波形検出回路15の動作を説明するためのタイミングチャートである。

t0:

パルス信号Drvonがロウレベルからハイレベルへの変化時になる。ゲート電圧NGがモード切替え用基準値Va未満なので、Lx波形Lレベル検出信号Pupはロウレベルである。出力制御回路14のMOSトランジスタM21はオンし、MOSトランジスタM22,23,24はオフ状態で、ゲート電圧NGのノードをドライブする能力は低く抑えられている。

【0041】

t0〜t1:

ゲート電圧NGのノードをドライブする能力が低いため、ゲート電圧NGは緩やかに上昇し、NMOSドライバM1のしきい値電圧Vthを越えたあたりで、NMOSドライバM1がオンし、Lx波形がハイレベルから下がりだす。

【0042】

t1〜t2:

NMOSドライバM1のゲート電圧NGがしきい値電圧Vth付近のため、NMOSドライバは飽和領域で動作することになる。ゲート電圧NGはしきい値電圧Vth以上に上がろうとするが、ドレイン−ゲート間容量Cdがミラー効果により大きな容量として見えるため、Lx波形がロウレベルになるまで、しきい値電圧Vth付近で非常に緩やかな傾斜で上昇する。これにより、Lx波形の高周波成分が抑えられ、スパイクノイズを抑制することができる。一方、NMOSドライバM1の抵抗値は非常に高く、この間は電力変換効率が低下する。

【0043】

t2〜t3:

Lx波形がロウレベルになると、ドレイン−ゲート間容量Cdへのチャージが不要となり、ゲート電圧NGが緩やかに上昇し、モード切替え用基準値Vaに到達する。

【0044】

t3:ゲート電圧NGがモード切替え用基準値Va以上なので、NG波形検出回路15の検出信号Pupはロウレベルからハイレベルへの変化時になる。出力制御回路14において、MOSトランジスタM21がオン、MOSトランジスタM22,23,24がオフの状態から、MOSトランジスタM22〜24が動作可能状態となる。このとき、パルス信号Drvonがハイレベルなので、MOSトランジスタM22〜24のうちMOSトランジスタM23のみがオンし、ゲート電圧NGを急激にハイレベルに吊り上げる。これにより、NMOSドライバM1が線形領域となり抵抗値が本来の低いものになり、電力変換効率に影響がなくなる。

従来技術の回路であれば、ゲート電圧NGがハイレベルまで緩やかに上昇する間、NMOSドライバM1の抵抗値が高くなるため、電力変換効率が低下したり、NMOSドライバM1を電流検出用の抵抗として使用している場合には誤検出する原因となったりしていたが、本発明はこれらの不具合を解消できる。

【0045】

t4:

パルス信号Drvonがハイレベルからロウレベルへの変化時となる。このとき、検出信号Pupがハイレベルで、出力制御回路14はゲート電圧NGのノードをドライブする能力が高いため、NMOSドライバM1が線形領域であり、ゲート電圧NGは急峻に低下する。

従来技術の回路であれば、ゲート電圧NGがロウレベルまで緩やかに下降する間、NMOSドライバM1の抵抗値が高くなるため、電力変換効率が低下する。本発明はこの不具合を解消できる。

ゲート電圧NGがモード切替え用基準値Va未満となると検出信号Pupがロウレベルとなり、ゲート電圧NGのノードをドライブする能力は低く抑えられ、ゲート電圧NGがしきい値電圧Vth付近まで緩やかに下降する。

【0046】

t5〜t6:

NMOSドライバM1のしきい値電圧Vth付近に近づくと、NMOSドライバM1は飽和領域で動作する。ゲート電圧NGはしきい値電圧Vth以下に下がろうとするが、ドレイン−ゲート間容量Cdがミラー効果により大きな容量として見えるため、Lx波形がハイレベルになるまで、しきい値電圧Vth付近で非常に緩やかな傾斜で下降する。その結果、Lx波形の高周波成分が抑えられ、スパイクノイズを抑制することができる。一方、NMOSドライバM1の抵抗値が非常に高く、この間は効率が低下する。

【0047】

t7:

Lx波形がハイレベルになるとドレイン−ゲート間容量Cdへのチャージが不要となり、ゲート電圧NGは緩やかに下降し、ロウレベルに到達する。

このように、本発明は、スイッチング方式のDC/DCコンバータにおいて、スパイクノイズを抑制しつつ高電力変換効率及び短い最小オン時間で高周波動作させることができる。

【0048】

図5は、NG波形検出回路15の他の例を説明するための回路図である。

NG波形検出回路15は、出力電圧Voを電源とするCMOSインバータ51で形成されている。CMOSインバータ51のしきい値はモード切替え用基準値Vaに設定されている。例えば、PMOSトランジスタM51に対してNMOSトランジスタM52の電流駆動能力を数倍以上に設定することで、CMOSインバータ51のしきい値をNMOSドライバM1のしきい値電圧を上回る所望のモード切替え用基準値Vaに設定すればよい。

CMOSインバータ51は、ゲート電圧NGがモード切替え用基準値Va以上になると、ハイレベルのLx波形Lレベル検出信号Pupを出力する。

【0049】

上記実施例では、非同期整流型のスイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、同期整流型のスイッチングレギュレータにも適用することができる。この場合、例えば、図1のダイオードD1の代わりにPMOSトランジスタからなる同期整流用トランジスタを使用して、該同期整流用トランジスタがNMOSドライバM1と相反するスイッチング動作を行なうように、該同期整流用トランジスタのゲートをNMOSドライバM1のゲートにそれぞれ接続するようにしてもよい。

【0050】

また、上記実施例では、PWM制御を行なう場合のスイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、PFM制御等を行なう場合のスイッチングレギュレータにも適用することができる。

また、上記実施例では、昇圧型スイッチングレギュレータを例にして説明したが、これは一例であり、本発明はこれに限定されるものではなく、降圧型スイッチングレギュレータ、反転型スイッチングレギュレータ及びシリーズレギュレータ等のリニアレギュレータにも適用することができる。

【0051】

このように、本発明は、出力電圧Voutを分圧して帰還電圧Vfbを生成し、帰還電圧Vfbを基に誤差増幅回路を使用して出力電圧Voutが所定の電圧で一定になるように出力トランジスタの動作制御を行う構成の電源回路に対して適用することができる。

さらに、本発明は、インダクタL1に流れたインダクタ電流を検出し、該検出したインダクタ電流を基に誤差増幅回路を使用して出力電圧Voutが所定の電圧で一定になるように出力トランジスタの動作制御を行う構成の電流モード制御型スイッチングレギュレータにも適用することができる。

【0052】

以上、本発明の実施例を説明したが、回路構成や配置、サイズ、数値等は一例であり、本発明はこれらに限定されるものではなく、特許請求の範囲に記載された本発明の範囲内で種々の変更が可能である。

【産業上の利用可能性】

【0053】

本発明は、入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路及びその動作制御方法、例えばDC/DCコンバータ及びその動作制御方法に応用できる。

【符号の説明】

【0054】

1 電源回路

11 差動増幅回路

14 出力制御回路

15 NG波形検出回路

25 低電流駆動能力インバータ

26 高電流駆動能力インバータ

31 コンパレータ

51 CMOSインバータ

D1 整流素子

L1 インダクタ

M1 出力トランジスタ

Vin 入力端子

Vout 出力端子

Drvon 制御信号

NG ゲート電圧

Va モード切替え用基準値

Vi 入力電圧

Vo 出力電圧

Vref 基準電圧

Vfb 帰還電圧

【先行技術文献】

【特許文献】

【0055】

【特許文献1】特開2010−178555号公報

【特許請求の範囲】

【請求項1】

入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路において、

制御信号に応じた動作を行なって前記出力電圧を制御するための出力トランジスタと、

所定の基準電圧と前記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路と、

前記誤差増幅回路の出力に基づいて前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタに前記制御信号としてのゲート電圧を出力する制御回路部と、を備え、

前記制御回路部は、前記出力トランジスタの前記ゲート電圧を監視するための波形検出回路と、可変な電流容量で前記ゲート電圧を印加するための出力制御回路と、を備え、

前記波形検出回路は、前記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて前記ゲート電圧を監視し、前記ゲート電圧が前記基準値以上のときは、前記出力制御回路を、前記ゲート電圧が前記基準値未満のときに比べて高い電流容量で動作させることを特徴とする電源回路。

【請求項2】

前記出力トランジスタは前記制御信号に応じてスイッチングを行ない、

前記出力トランジスタのスイッチングによって前記入力電圧による充電が行なわれるインダクタと、

前記出力トランジスタがオフして遮断状態になったときに前記インダクタの放電を行なう整流素子と、

を備え、

前記制御回路部は、前記誤差増幅回路の出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタのスイッチング制御を行なう請求項1に記載の電源回路。

【請求項3】

前記出力制御回路は、低電流駆動能力インバータと、前記低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備え、前記ゲート電圧が前記基準値以上のときは前記低電流駆動能力インバータ及び前記高電流駆動能力インバータがオンされ、前記ゲート電圧が前記基準値未満のときは前記低電流駆動能力インバータのみがオンされる請求項1又は2に記載の電源回路。

【請求項4】

前記波形検出回路は、前記ゲート電圧と前記基準値とを比較するコンパレータで形成されている請求項1から3のいずれか一項に記載の電源回路。

【請求項5】

前記波形検出回路は、前記出力電圧を電源とし、かつ前記基準値をしきい値とするCMOSインバータで形成されている請求項1から3のいずれか一項に記載の電源回路。

【請求項6】

制御信号に応じた動作を行なって出力電圧を制御するための出力トランジスタを備え、入力端子から入力された入力電圧を所定の電圧に変換して前記出力端子から出力する電源回路の動作制御方法において、

所定の基準電圧と前記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路からの出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタの動作制御を行ない、

前記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて前記出力トランジスタの前記ゲート電圧を監視し、前記ゲート電圧が前記基準値以上のときは、前記ゲート電圧が前記基準値未満のときに比べて高い電流容量で前記出力トランジスタに前記制御信号としてのゲート電圧を印加することを特徴とする電源回路の動作制御方法。

【請求項7】

前記出力トランジスタは前記制御信号に応じてスイッチングを行ない、

前記電源回路は前記出力トランジスタのスイッチングによって前記入力電圧による充電が行なわれるインダクタと、前記出力トランジスタがオフして遮断状態になったときに前記インダクタの放電を行なう整流素子と、を備え、

前記制御回路部は、前記誤差増幅回路の出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタのスイッチング制御を行なうものである請求項6に記載の電源回路の動作制御方法。

【請求項1】

入力端子から入力された入力電圧を所定の電圧に変換して出力端子から出力電圧として出力する電源回路において、

制御信号に応じた動作を行なって前記出力電圧を制御するための出力トランジスタと、

所定の基準電圧と前記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路と、

前記誤差増幅回路の出力に基づいて前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタに前記制御信号としてのゲート電圧を出力する制御回路部と、を備え、

前記制御回路部は、前記出力トランジスタの前記ゲート電圧を監視するための波形検出回路と、可変な電流容量で前記ゲート電圧を印加するための出力制御回路と、を備え、

前記波形検出回路は、前記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて前記ゲート電圧を監視し、前記ゲート電圧が前記基準値以上のときは、前記出力制御回路を、前記ゲート電圧が前記基準値未満のときに比べて高い電流容量で動作させることを特徴とする電源回路。

【請求項2】

前記出力トランジスタは前記制御信号に応じてスイッチングを行ない、

前記出力トランジスタのスイッチングによって前記入力電圧による充電が行なわれるインダクタと、

前記出力トランジスタがオフして遮断状態になったときに前記インダクタの放電を行なう整流素子と、

を備え、

前記制御回路部は、前記誤差増幅回路の出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタのスイッチング制御を行なう請求項1に記載の電源回路。

【請求項3】

前記出力制御回路は、低電流駆動能力インバータと、前記低電流駆動能力インバータよりも電流駆動能力が高い高電流駆動能力インバータとを備え、前記ゲート電圧が前記基準値以上のときは前記低電流駆動能力インバータ及び前記高電流駆動能力インバータがオンされ、前記ゲート電圧が前記基準値未満のときは前記低電流駆動能力インバータのみがオンされる請求項1又は2に記載の電源回路。

【請求項4】

前記波形検出回路は、前記ゲート電圧と前記基準値とを比較するコンパレータで形成されている請求項1から3のいずれか一項に記載の電源回路。

【請求項5】

前記波形検出回路は、前記出力電圧を電源とし、かつ前記基準値をしきい値とするCMOSインバータで形成されている請求項1から3のいずれか一項に記載の電源回路。

【請求項6】

制御信号に応じた動作を行なって出力電圧を制御するための出力トランジスタを備え、入力端子から入力された入力電圧を所定の電圧に変換して前記出力端子から出力する電源回路の動作制御方法において、

所定の基準電圧と前記出力電圧に比例した帰還電圧との電圧差を増幅して出力する誤差増幅回路からの出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタの動作制御を行ない、

前記出力トランジスタのしきい値電圧よりも高く設定されたモード切替え用基準値を用いて前記出力トランジスタの前記ゲート電圧を監視し、前記ゲート電圧が前記基準値以上のときは、前記ゲート電圧が前記基準値未満のときに比べて高い電流容量で前記出力トランジスタに前記制御信号としてのゲート電圧を印加することを特徴とする電源回路の動作制御方法。

【請求項7】

前記出力トランジスタは前記制御信号に応じてスイッチングを行ない、

前記電源回路は前記出力トランジスタのスイッチングによって前記入力電圧による充電が行なわれるインダクタと、前記出力トランジスタがオフして遮断状態になったときに前記インダクタの放電を行なう整流素子と、を備え、

前記制御回路部は、前記誤差増幅回路の出力に基づいて、前記出力電圧が前記所定の電圧で一定になるように前記出力トランジスタのスイッチング制御を行なうものである請求項6に記載の電源回路の動作制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−196092(P2012−196092A)

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願番号】特願2011−59771(P2011−59771)

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成24年10月11日(2012.10.11)

【国際特許分類】

【出願日】平成23年3月17日(2011.3.17)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]