電源回路

【課題】 外部から供給される電源電圧に基づいて複数の電源電位を生成する電源回路を含む半導体集積回路において、実動作時における電圧関係を改善する。

【解決手段】 この半導体集積回路は、電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路10と、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路20と、第1の電位を分圧して第2の電位を含む複数の電位を生成する分圧回路30と、分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路42と、第2の電位以外の所定数の電位をバッファして電源電位として出力する増幅回路41及び43と、第1の電位と第2の電位とに基づいて昇圧動作を行うことにより、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路50とを具備する。

【解決手段】 この半導体集積回路は、電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路10と、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路20と、第1の電位を分圧して第2の電位を含む複数の電位を生成する分圧回路30と、分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路42と、第2の電位以外の所定数の電位をバッファして電源電位として出力する増幅回路41及び43と、第1の電位と第2の電位とに基づいて昇圧動作を行うことにより、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路50とを具備する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、外部から供給される電源電圧に基づいて複数の電源電位を生成する電源回路を含む半導体集積回路に関し、特に、液晶パネルを駆動するために用いられる複数の電源電位を生成する電源回路を含む半導体集積回路に関する。

【背景技術】

【0002】

液晶パネルを駆動するためには、複数の駆動電位が必要である。そのため、電源回路が複数の電源電位を発生し、液晶ドライバ回路が、それらの電源電位を利用して、液晶パネルの電極に印加する駆動電位を出力する。

【0003】

以前は、電源回路が、システムから供給される電源電位VDDと電源電位VSSとの間の電源電圧を分割することによって、液晶ドライバ回路に必要な電源電位を作り出していたが、近年においては、消費電力を低減するために、システムから供給される電源電圧が小さくなっており、電源電位VDDよりも高い電源電位や、電源電位VSSよりも低い電源電位を、電源回路において作り出す必要がある。

【0004】

図7に、そのような従来の電源回路の構成例を示す。この電源回路は、システムから電源電位VDD及び電源電位VSS(この例においては接地電位)が供給され、これらの間の電源電圧を2倍に昇圧して2倍昇圧電圧VDD×2を生成する2倍昇圧回路10と、2倍昇圧電圧が供給されて動作し、基準電位VREFを増幅して電源電位V1を生成するオペアンプ20と、電源電位V1と電源電位VSSとの間の電圧を分割する抵抗R1〜R3と、抵抗分割によって得られた1つの電位をバッファして電源電位VCを出力するオペアンプ44と、抵抗分割によって得られた他の電位をバッファして電源電位MV1を出力するオペアンプ45と、電源電位V1と電源電位MV1とに基づいて昇圧動作を行うことにより電源電位V2を出力する昇圧回路50とを有している。

【0005】

この例においては、システムから2.8Vの電源電位VDDを供給される電源回路が、無負荷時において、6.0Vの電源電位V2と、4.5Vの電源電位V1と、3.0Vの電源電位VCと、1.5Vの電源電位MV1を生成する。なお、電源電位VSS及び電源電位MV2は、0Vである。このように、電源電位V2は、2倍昇圧電圧VDD×2よりも高くなっている。

【0006】

ここで、2倍昇圧回路10の替わりに3倍昇圧回路を用いるようにすれば、電源電位V2についてもオペアンプを介して出力することが可能であるが、液晶ドライバ回路において消費電流が大きいのは電源電位V1及びMV1であるので、3倍昇圧回路を用いると、電力損失が増加して電力供給効率が低下してしまう。そこで、6.0Vの電源電位V2については、4.5Vの電源電位V1と1.5Vの電源電位MV1とに基づいて昇圧回路50が昇圧動作を行って生成することにより、電力損失を低減している。

【0007】

ところで、液晶パネルに直流成分が印加されると液晶の光学特性や信頼性が低下してしまうので、液晶パネルは交流駆動しなければならず、そのために、電源電位VCを中心として、電源電位V1と電源電位MV1とが対象関係にあり、電源電位V2と電源電位MV2とが対象関係にある必要がある。

【0008】

図8は、図7に示す従来の電源回路における負荷電流の増加に伴う電源電位の低下を示す図である。この電源回路において、オペアンプ20、44、45の出力インピーダンスは10Ω以下と小さいが、昇圧回路50の出力インピーダンスは1kΩ程度と比較的大きな値である。その結果、負荷電流が流れると、電源電位V2は、電源電位V1、VC、MV1よりも大きな割合で低下してしまう。その結果、負荷電流が流れる実動作時において、電源電位V2と電源電位V1との差ΔV(+)が電源電位MV1と電源電位MV2との差ΔV(−)とバランスせずに、液晶パネルに直流成分が印加されてしまうという現象が生じる。このような現象は、「バイアスずれ」と呼ばれている。

【0009】

関連する技術として、下記の特許文献1には、比較的簡単な回路構成で駆動用半導体素子の駆動電圧を安定化する液晶表示装置の駆動回路が開示されている。この駆動回路においては、駆動用半導体素子へのバイアス電圧の入力配線の電圧をバイアス電源部の演算増幅器の反転入力端子にフィードバックする帰還回路が設けられている。しかしながら、このような回路構成は、演算増幅器から出力される電圧よりも高い電源電圧が演算増幅器に供給される場合にのみ適用できるものであって、図7に示すように、供給される電源電圧よりも高い電圧を出力する昇圧回路50においては、適用することができない。

【0010】

また、下記の特許文献2には、コモン側駆動電圧とセグメント側電圧との関係を精度良く実現するために、セグメント側電圧を分割するための2つの抵抗の内のどちらかをトリミングした液晶用電源回路が開示されている。しかしながら、図7に示すような電源回路においては、トリミングによって無負荷時における電圧関係の精度を改善しても、負荷電流が流れる実動作時における電圧関係を改善することはできない。

【特許文献1】特開平6−230338号公報(第1頁、図1)

【特許文献2】特開2001−117068号公報(第1頁、図1)

【発明の開示】

【発明が解決しようとする課題】

【0011】

そこで、上記の点に鑑み、本発明は、外部から供給される電源電圧に基づいて複数の電源電位を生成する電源回路を含む半導体集積回路において、負荷電流が流れる実動作時における電圧関係を改善することを目的とする。

【課題を解決するための手段】

【0012】

以上の課題を解決するため、本発明に係る半導体集積回路は、外部から供給される電源電圧に基づいて複数の電源電位を生成する半導体集積回路であって、外部から供給される電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路と、第1の増幅回路によって生成される第1の電位を分圧して、第2の電位を含む複数の電位を生成する分圧回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、分圧回路によって生成される第2の電位以外の所定数の電位をバッファして電源電位として出力する複数の増幅回路と、第1の増幅回路によって生成される第1の電位と、第2の増幅回路から出力される第2の電位とに基づいて昇圧動作を行うことにより、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路とを具備する。

【0013】

ここで、分圧回路は、配線層のパターンを変更するのみで、複数の電位の内から選択された1つの電位を第2の電位として出力するように構成されても良い。あるいは、分圧回路は、複数の電位の内から選択された1つの電位を第2の電位として出力するための少なくとも1つのヒューズを含んでも良く、外部から供給される制御信号に従って複数の電位の内から1つの電位を選択して第2の電位として出力するための少なくとも1つのスイッチ回路を含んでも良い。

【発明の効果】

【0014】

本発明によれば、第1の増幅回路によって第1の電位を生成すると共に、分圧回路によって各種の電源電位の他に第2の電位を生成し、第2の電位をバッファして出力する第2の増幅回路を設けて、第1の増幅回路によって生成される第1の電位と第2の増幅回路から出力される第2の電位とに基づいて、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成することにより、負荷電流が流れる実動作時における電圧関係を改善することができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら詳しく説明する。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

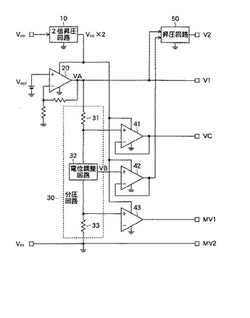

図1は、本発明の一実施形態に係る半導体集積回路に含まれている電源回路の構成を示す図である。図1に示すように、この電源回路は、システム等の外部回路から供給される電源電位VDDと電源電位VSS(本実施形態においては、接地電位とする)が供給され、これらの間の電源電圧を2倍に昇圧して2倍昇圧電圧VDD×2を生成する2倍昇圧回路10と、オペアンプ20と、分圧回路30と、オペアンプ41〜43と、昇圧回路50とを有しており、液晶ドライバ回路に印加する複数の電源電位V2、V1、VC、MV1、MV2を生成する。

【0016】

例えば、電源回路に供給される電源電位VDDは2.8Vであり、電源回路において生成される電源電位は、電源電位V2を6.0V、電源電位V1を4.5V、電源電位VCを3.0V、電源電位MV1を1.5Vとすることを目標とする。なお、電源電位VSS及び電源電位MV2は、0Vである。このように、電源電位V2は、2倍昇圧電圧VDD×2よりも高くなっている。これらの電源電位の中で、電流が大きくなるのは電源電位V1及びMV1であるので、昇圧回路10の昇圧比を3倍ではなく2倍とし、電源電位V2については、昇圧回路50を用いて生成した電位を直接出力するようにして、電力損失を低減している。

【0017】

オペアンプ20は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、基準電位VREFに基づいて第1の電位VAを生成して、電源電位V1として出力する。分圧回路30は、抵抗31及び33と電位調整回路32とを含み、オペアンプ20によって生成される第1の電位VAを分圧して、複数の電位を生成する。ここで、電位調整回路32は、第2の電位VBを生成する。

【0018】

オペアンプ42は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、電位調整回路32によって生成される第2の電位VBをバッファして出力する。また、オペアンプ41及び43は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、分圧回路30によって生成される2つの電位をバッファして、それぞれ電源電位VC及びMV1として出力する。

【0019】

昇圧回路50は、オペアンプ20によって生成される第1の電位VAと、オペアンプ42から出力される第2の電位VBとに基づいて昇圧動作を行うことにより、2倍昇圧回路10によって生成される2倍昇圧電圧よりも高い電源電位V2を生成する。

【0020】

ここで、オペアンプ41〜43の出力インピーダンスは10Ω以下と小さいが、昇圧回路50の出力インピーダンスは1kΩ程度と比較的大きな値である。その結果、負荷電流が流れると、電源電位V2は、電源電位V1、VC、MV1よりも大きな割合で低下してしまう。本実施形態においては、電源電位V2を生成するために、従来のように電源電位MV1を用いるのではなく、電位調整回路32によって調整された第2の電位VBをオペアンプ42によってバッファして用いることにより、負荷電流が流れる実動作時における電圧関係を改善している。以下に、そのような電位調整回路32の3つの具体例について説明する。

【0021】

図2は、図1に示す電位調整回路の第1の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されている。半導体集積回路において、これらの抵抗は、ポリシリコンに不純物をイオン化注入して形成されるが、ポリシリコンの上層に形成される層間絶縁膜において、隣接する2つの抵抗の接続点における部分(図2においては4つの白丸で示す)に4つのスルーホールをそれぞれ設けておく。これにより、層間絶縁膜の上層に形成されるメタル配線層における配線パターンを変更するのみで、図2の(a)〜(d)にそれぞれ示す配線32a〜32dの内のいずれかを選択的に形成し、複数の電位の内から選択された1つの電位を、第2の電位VBとしてオペアンプ42に供給することができる。

【0022】

図3は、図1に示す電位調整回路の第2の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されており、抵抗R321〜R324と並列に、ヒューズF1〜F4がそれぞれ接続されている。ここで、抵抗R320の抵抗値をRAとし、抵抗R321及び抵抗R324の抵抗値をRBとし、抵抗R322及び抵抗R323の抵抗値をRCとする(ただし、RA>>RB>RC)。また、電位調整回路32の両端電圧をΔVとおく。

【0023】

ヒューズF1〜F4を切断しない場合には、抵抗R321〜R324がヒューズF1〜F4によってそれぞれショートされているので、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、0Vとなる。

【0024】

ここで、過電流を流す等により、ヒューズF1及びF3を切断すると、抵抗R320〜R324の直列抵抗値は(RA+RB+RC)であり、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、ΔV・RC/(RA+RB+RC)に分圧される。

【0025】

一方、ヒューズF2及びF4を切断すると、抵抗R320〜R324の直列抵抗値は(RA+RB+RC)と変わらないが、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、ΔV・RB/(RA+RB+RC)に分圧される。

【0026】

このように、ヒューズの接続の仕方や切断の仕方によって、オペアンプ42に入力される第2の電位VBを様々に選択することができる。ここでは、複数のヒューズを設ける場合について説明したが、少なくとも1つのヒューズを設けることにより、オペアンプ42に入力される第2の電位VBを変化させることができる。

【0027】

図4は、図1に示す電位調整回路の第3の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されており、隣接する2つの抵抗の接続点とオペアンプ42の入力端子との間に、スイッチ回路SW1〜SW4が接続されている。スイッチ回路SW1〜SW4の各々は、例えば、並列に接続されたPチャネルMOSトランジスタ及びNチャネルMOSトランジスタを有するアナログスイッチによって構成される。

【0028】

システムのCPU等においてソフトウェアによって設定された制御信号に従って、スイッチ回路SW1〜SW4の内の1つがオンすることにより、4つの電位の内から1つの電位が選択されて、第2の電位VBとしてオペアンプ42に入力される。あるいは、電源回路を含む半導体集積回路において、一度設定された制御信号を格納するためのEEPROM等の格納手段を設けるようにしても良い。

【0029】

図5は、図1に示す昇圧回路の具体例を示す回路図である。図1に示すように、昇圧回路50は、第1の電位VAが供給されて動作するインバータを構成するPチャネルMOSトランジスタQP11及びNチャネルMOSトランジスタQN11と、第2の電位VBが供給されるPチャネルMOSトランジスタQP21と、トランジスタQP21に直列に接続され、ドレインから電源電位V2を出力するPチャネルMOSトランジスタQP22とを含んでいる。

【0030】

インバータを構成するトランジスタQP11及びQN11のゲ−トには、昇圧クロック信号CK1が供給され、トランジスタQP22のゲ−トには、昇圧クロック信号CK1と同相の昇圧クロック信号CK2が供給され、トランジスタQP21のゲ−トには、昇圧クロック信号CK2を反転した昇圧クロック信号CK2バーが供給される。

【0031】

次に、昇圧回路50の動作を説明する。第1の期間において、昇圧クロック信号CK1及びCK2がハイレベル、昇圧クロック信号CK2バーがローレベルをとり、これに続く第2の期間において、昇圧クロック信号CK1及びCK2がローレベル、昇圧クロック信号CK2バーがハイレベルをとり、これを繰り返す。

【0032】

第1の期間において、トランジスタQP11及びQN11によって構成されるインバータの出力がローレベルとなり、トランジスタQP21がオンして、トランジスタQP22がオフすることにより、コンデンサC1に電荷が蓄積される。第2の期間において、インバータの出力がハイレベルとなり、トランジスタQP21がオフして、トランジスタQP22がオンすることにより、コンデンサC1に蓄積されていた電荷が電源電位V2に放出される。これを繰り返すことにより、第1の電位VA及び第2の電位VBに基づいて昇圧動作が行われ、電位がほぼ(VA+VB)である電源電位V2が生成される。

【0033】

図6は、図1に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図である。図6に示すように、電源電位V2、V1、VC、MV1は、無負荷時において、それぞれV2(0)、V1(0)、VC(0)、MV1(0)となっているが、負荷電流が増加すると低下してしまう。しかしながら、液晶ドライバ回路に供給される電流はほぼ予測されるので、電位調整回路32を用いて電源電位MV1よりも高い第2の電位VBを発生させ、無負荷時における電源電位V2を高めに設定しておくことにより、実動作時において、電源電位V2と電源電位V1との差ΔV(+)が電源電位MV1と電源電位MV2との差ΔV(−)とバランスして、液晶パネルに直流成分が印加される「バイアスずれ」を防止することができる。

【図面の簡単な説明】

【0034】

【図1】本発明の一実施形態に含まれている電源回路の構成を示す図。

【図2】図1に示す電位調整回路の第1の具体例を示す回路図。

【図3】図1に示す電位調整回路の第2の具体例を示す回路図。

【図4】図1に示す電位調整回路の第3の具体例を示す回路図。

【図5】図1に示す昇圧回路の具体例を示す回路図。

【図6】図1に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図。

【図7】従来の電源回路の構成を示す図。

【図8】図7に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図。

【符号の説明】

【0035】

10 2倍昇圧回路、 20、41〜43 オペアンプ、 30 分圧回路、 31、33 抵抗、 32 電位調整回路、 32a〜32d 配線、 50 昇圧回路、 R320〜R324 抵抗、 F1〜F4 ヒューズ、 SW1〜SW4 スイッチ回路、 QP11〜QP22 PチャネルMOSトランジスタ、 QN11 NチャネルMOSトランジスタ、 C1 コンデンサ

【技術分野】

【0001】

本発明は、外部から供給される電源電圧に基づいて複数の電源電位を生成する電源回路を含む半導体集積回路に関し、特に、液晶パネルを駆動するために用いられる複数の電源電位を生成する電源回路を含む半導体集積回路に関する。

【背景技術】

【0002】

液晶パネルを駆動するためには、複数の駆動電位が必要である。そのため、電源回路が複数の電源電位を発生し、液晶ドライバ回路が、それらの電源電位を利用して、液晶パネルの電極に印加する駆動電位を出力する。

【0003】

以前は、電源回路が、システムから供給される電源電位VDDと電源電位VSSとの間の電源電圧を分割することによって、液晶ドライバ回路に必要な電源電位を作り出していたが、近年においては、消費電力を低減するために、システムから供給される電源電圧が小さくなっており、電源電位VDDよりも高い電源電位や、電源電位VSSよりも低い電源電位を、電源回路において作り出す必要がある。

【0004】

図7に、そのような従来の電源回路の構成例を示す。この電源回路は、システムから電源電位VDD及び電源電位VSS(この例においては接地電位)が供給され、これらの間の電源電圧を2倍に昇圧して2倍昇圧電圧VDD×2を生成する2倍昇圧回路10と、2倍昇圧電圧が供給されて動作し、基準電位VREFを増幅して電源電位V1を生成するオペアンプ20と、電源電位V1と電源電位VSSとの間の電圧を分割する抵抗R1〜R3と、抵抗分割によって得られた1つの電位をバッファして電源電位VCを出力するオペアンプ44と、抵抗分割によって得られた他の電位をバッファして電源電位MV1を出力するオペアンプ45と、電源電位V1と電源電位MV1とに基づいて昇圧動作を行うことにより電源電位V2を出力する昇圧回路50とを有している。

【0005】

この例においては、システムから2.8Vの電源電位VDDを供給される電源回路が、無負荷時において、6.0Vの電源電位V2と、4.5Vの電源電位V1と、3.0Vの電源電位VCと、1.5Vの電源電位MV1を生成する。なお、電源電位VSS及び電源電位MV2は、0Vである。このように、電源電位V2は、2倍昇圧電圧VDD×2よりも高くなっている。

【0006】

ここで、2倍昇圧回路10の替わりに3倍昇圧回路を用いるようにすれば、電源電位V2についてもオペアンプを介して出力することが可能であるが、液晶ドライバ回路において消費電流が大きいのは電源電位V1及びMV1であるので、3倍昇圧回路を用いると、電力損失が増加して電力供給効率が低下してしまう。そこで、6.0Vの電源電位V2については、4.5Vの電源電位V1と1.5Vの電源電位MV1とに基づいて昇圧回路50が昇圧動作を行って生成することにより、電力損失を低減している。

【0007】

ところで、液晶パネルに直流成分が印加されると液晶の光学特性や信頼性が低下してしまうので、液晶パネルは交流駆動しなければならず、そのために、電源電位VCを中心として、電源電位V1と電源電位MV1とが対象関係にあり、電源電位V2と電源電位MV2とが対象関係にある必要がある。

【0008】

図8は、図7に示す従来の電源回路における負荷電流の増加に伴う電源電位の低下を示す図である。この電源回路において、オペアンプ20、44、45の出力インピーダンスは10Ω以下と小さいが、昇圧回路50の出力インピーダンスは1kΩ程度と比較的大きな値である。その結果、負荷電流が流れると、電源電位V2は、電源電位V1、VC、MV1よりも大きな割合で低下してしまう。その結果、負荷電流が流れる実動作時において、電源電位V2と電源電位V1との差ΔV(+)が電源電位MV1と電源電位MV2との差ΔV(−)とバランスせずに、液晶パネルに直流成分が印加されてしまうという現象が生じる。このような現象は、「バイアスずれ」と呼ばれている。

【0009】

関連する技術として、下記の特許文献1には、比較的簡単な回路構成で駆動用半導体素子の駆動電圧を安定化する液晶表示装置の駆動回路が開示されている。この駆動回路においては、駆動用半導体素子へのバイアス電圧の入力配線の電圧をバイアス電源部の演算増幅器の反転入力端子にフィードバックする帰還回路が設けられている。しかしながら、このような回路構成は、演算増幅器から出力される電圧よりも高い電源電圧が演算増幅器に供給される場合にのみ適用できるものであって、図7に示すように、供給される電源電圧よりも高い電圧を出力する昇圧回路50においては、適用することができない。

【0010】

また、下記の特許文献2には、コモン側駆動電圧とセグメント側電圧との関係を精度良く実現するために、セグメント側電圧を分割するための2つの抵抗の内のどちらかをトリミングした液晶用電源回路が開示されている。しかしながら、図7に示すような電源回路においては、トリミングによって無負荷時における電圧関係の精度を改善しても、負荷電流が流れる実動作時における電圧関係を改善することはできない。

【特許文献1】特開平6−230338号公報(第1頁、図1)

【特許文献2】特開2001−117068号公報(第1頁、図1)

【発明の開示】

【発明が解決しようとする課題】

【0011】

そこで、上記の点に鑑み、本発明は、外部から供給される電源電圧に基づいて複数の電源電位を生成する電源回路を含む半導体集積回路において、負荷電流が流れる実動作時における電圧関係を改善することを目的とする。

【課題を解決するための手段】

【0012】

以上の課題を解決するため、本発明に係る半導体集積回路は、外部から供給される電源電圧に基づいて複数の電源電位を生成する半導体集積回路であって、外部から供給される電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路と、第1の増幅回路によって生成される第1の電位を分圧して、第2の電位を含む複数の電位を生成する分圧回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路と、第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、分圧回路によって生成される第2の電位以外の所定数の電位をバッファして電源電位として出力する複数の増幅回路と、第1の増幅回路によって生成される第1の電位と、第2の増幅回路から出力される第2の電位とに基づいて昇圧動作を行うことにより、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路とを具備する。

【0013】

ここで、分圧回路は、配線層のパターンを変更するのみで、複数の電位の内から選択された1つの電位を第2の電位として出力するように構成されても良い。あるいは、分圧回路は、複数の電位の内から選択された1つの電位を第2の電位として出力するための少なくとも1つのヒューズを含んでも良く、外部から供給される制御信号に従って複数の電位の内から1つの電位を選択して第2の電位として出力するための少なくとも1つのスイッチ回路を含んでも良い。

【発明の効果】

【0014】

本発明によれば、第1の増幅回路によって第1の電位を生成すると共に、分圧回路によって各種の電源電位の他に第2の電位を生成し、第2の電位をバッファして出力する第2の増幅回路を設けて、第1の増幅回路によって生成される第1の電位と第2の増幅回路から出力される第2の電位とに基づいて、第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成することにより、負荷電流が流れる実動作時における電圧関係を改善することができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明を実施するための最良の形態について、図面を参照しながら詳しく説明する。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

図1は、本発明の一実施形態に係る半導体集積回路に含まれている電源回路の構成を示す図である。図1に示すように、この電源回路は、システム等の外部回路から供給される電源電位VDDと電源電位VSS(本実施形態においては、接地電位とする)が供給され、これらの間の電源電圧を2倍に昇圧して2倍昇圧電圧VDD×2を生成する2倍昇圧回路10と、オペアンプ20と、分圧回路30と、オペアンプ41〜43と、昇圧回路50とを有しており、液晶ドライバ回路に印加する複数の電源電位V2、V1、VC、MV1、MV2を生成する。

【0016】

例えば、電源回路に供給される電源電位VDDは2.8Vであり、電源回路において生成される電源電位は、電源電位V2を6.0V、電源電位V1を4.5V、電源電位VCを3.0V、電源電位MV1を1.5Vとすることを目標とする。なお、電源電位VSS及び電源電位MV2は、0Vである。このように、電源電位V2は、2倍昇圧電圧VDD×2よりも高くなっている。これらの電源電位の中で、電流が大きくなるのは電源電位V1及びMV1であるので、昇圧回路10の昇圧比を3倍ではなく2倍とし、電源電位V2については、昇圧回路50を用いて生成した電位を直接出力するようにして、電力損失を低減している。

【0017】

オペアンプ20は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、基準電位VREFに基づいて第1の電位VAを生成して、電源電位V1として出力する。分圧回路30は、抵抗31及び33と電位調整回路32とを含み、オペアンプ20によって生成される第1の電位VAを分圧して、複数の電位を生成する。ここで、電位調整回路32は、第2の電位VBを生成する。

【0018】

オペアンプ42は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、電位調整回路32によって生成される第2の電位VBをバッファして出力する。また、オペアンプ41及び43は、2倍昇圧回路10によって生成される2倍昇圧電圧が供給されて動作し、分圧回路30によって生成される2つの電位をバッファして、それぞれ電源電位VC及びMV1として出力する。

【0019】

昇圧回路50は、オペアンプ20によって生成される第1の電位VAと、オペアンプ42から出力される第2の電位VBとに基づいて昇圧動作を行うことにより、2倍昇圧回路10によって生成される2倍昇圧電圧よりも高い電源電位V2を生成する。

【0020】

ここで、オペアンプ41〜43の出力インピーダンスは10Ω以下と小さいが、昇圧回路50の出力インピーダンスは1kΩ程度と比較的大きな値である。その結果、負荷電流が流れると、電源電位V2は、電源電位V1、VC、MV1よりも大きな割合で低下してしまう。本実施形態においては、電源電位V2を生成するために、従来のように電源電位MV1を用いるのではなく、電位調整回路32によって調整された第2の電位VBをオペアンプ42によってバッファして用いることにより、負荷電流が流れる実動作時における電圧関係を改善している。以下に、そのような電位調整回路32の3つの具体例について説明する。

【0021】

図2は、図1に示す電位調整回路の第1の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されている。半導体集積回路において、これらの抵抗は、ポリシリコンに不純物をイオン化注入して形成されるが、ポリシリコンの上層に形成される層間絶縁膜において、隣接する2つの抵抗の接続点における部分(図2においては4つの白丸で示す)に4つのスルーホールをそれぞれ設けておく。これにより、層間絶縁膜の上層に形成されるメタル配線層における配線パターンを変更するのみで、図2の(a)〜(d)にそれぞれ示す配線32a〜32dの内のいずれかを選択的に形成し、複数の電位の内から選択された1つの電位を、第2の電位VBとしてオペアンプ42に供給することができる。

【0022】

図3は、図1に示す電位調整回路の第2の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されており、抵抗R321〜R324と並列に、ヒューズF1〜F4がそれぞれ接続されている。ここで、抵抗R320の抵抗値をRAとし、抵抗R321及び抵抗R324の抵抗値をRBとし、抵抗R322及び抵抗R323の抵抗値をRCとする(ただし、RA>>RB>RC)。また、電位調整回路32の両端電圧をΔVとおく。

【0023】

ヒューズF1〜F4を切断しない場合には、抵抗R321〜R324がヒューズF1〜F4によってそれぞれショートされているので、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、0Vとなる。

【0024】

ここで、過電流を流す等により、ヒューズF1及びF3を切断すると、抵抗R320〜R324の直列抵抗値は(RA+RB+RC)であり、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、ΔV・RC/(RA+RB+RC)に分圧される。

【0025】

一方、ヒューズF2及びF4を切断すると、抵抗R320〜R324の直列抵抗値は(RA+RB+RC)と変わらないが、オペアンプ42に入力される電圧は、電位調整回路32と抵抗R33(図1)との接続点を基準として、ΔV・RB/(RA+RB+RC)に分圧される。

【0026】

このように、ヒューズの接続の仕方や切断の仕方によって、オペアンプ42に入力される第2の電位VBを様々に選択することができる。ここでは、複数のヒューズを設ける場合について説明したが、少なくとも1つのヒューズを設けることにより、オペアンプ42に入力される第2の電位VBを変化させることができる。

【0027】

図4は、図1に示す電位調整回路の第3の具体例を示す回路図である。この電位調整回路32においては、複数の抵抗R320〜R324が直列に接続されており、隣接する2つの抵抗の接続点とオペアンプ42の入力端子との間に、スイッチ回路SW1〜SW4が接続されている。スイッチ回路SW1〜SW4の各々は、例えば、並列に接続されたPチャネルMOSトランジスタ及びNチャネルMOSトランジスタを有するアナログスイッチによって構成される。

【0028】

システムのCPU等においてソフトウェアによって設定された制御信号に従って、スイッチ回路SW1〜SW4の内の1つがオンすることにより、4つの電位の内から1つの電位が選択されて、第2の電位VBとしてオペアンプ42に入力される。あるいは、電源回路を含む半導体集積回路において、一度設定された制御信号を格納するためのEEPROM等の格納手段を設けるようにしても良い。

【0029】

図5は、図1に示す昇圧回路の具体例を示す回路図である。図1に示すように、昇圧回路50は、第1の電位VAが供給されて動作するインバータを構成するPチャネルMOSトランジスタQP11及びNチャネルMOSトランジスタQN11と、第2の電位VBが供給されるPチャネルMOSトランジスタQP21と、トランジスタQP21に直列に接続され、ドレインから電源電位V2を出力するPチャネルMOSトランジスタQP22とを含んでいる。

【0030】

インバータを構成するトランジスタQP11及びQN11のゲ−トには、昇圧クロック信号CK1が供給され、トランジスタQP22のゲ−トには、昇圧クロック信号CK1と同相の昇圧クロック信号CK2が供給され、トランジスタQP21のゲ−トには、昇圧クロック信号CK2を反転した昇圧クロック信号CK2バーが供給される。

【0031】

次に、昇圧回路50の動作を説明する。第1の期間において、昇圧クロック信号CK1及びCK2がハイレベル、昇圧クロック信号CK2バーがローレベルをとり、これに続く第2の期間において、昇圧クロック信号CK1及びCK2がローレベル、昇圧クロック信号CK2バーがハイレベルをとり、これを繰り返す。

【0032】

第1の期間において、トランジスタQP11及びQN11によって構成されるインバータの出力がローレベルとなり、トランジスタQP21がオンして、トランジスタQP22がオフすることにより、コンデンサC1に電荷が蓄積される。第2の期間において、インバータの出力がハイレベルとなり、トランジスタQP21がオフして、トランジスタQP22がオンすることにより、コンデンサC1に蓄積されていた電荷が電源電位V2に放出される。これを繰り返すことにより、第1の電位VA及び第2の電位VBに基づいて昇圧動作が行われ、電位がほぼ(VA+VB)である電源電位V2が生成される。

【0033】

図6は、図1に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図である。図6に示すように、電源電位V2、V1、VC、MV1は、無負荷時において、それぞれV2(0)、V1(0)、VC(0)、MV1(0)となっているが、負荷電流が増加すると低下してしまう。しかしながら、液晶ドライバ回路に供給される電流はほぼ予測されるので、電位調整回路32を用いて電源電位MV1よりも高い第2の電位VBを発生させ、無負荷時における電源電位V2を高めに設定しておくことにより、実動作時において、電源電位V2と電源電位V1との差ΔV(+)が電源電位MV1と電源電位MV2との差ΔV(−)とバランスして、液晶パネルに直流成分が印加される「バイアスずれ」を防止することができる。

【図面の簡単な説明】

【0034】

【図1】本発明の一実施形態に含まれている電源回路の構成を示す図。

【図2】図1に示す電位調整回路の第1の具体例を示す回路図。

【図3】図1に示す電位調整回路の第2の具体例を示す回路図。

【図4】図1に示す電位調整回路の第3の具体例を示す回路図。

【図5】図1に示す昇圧回路の具体例を示す回路図。

【図6】図1に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図。

【図7】従来の電源回路の構成を示す図。

【図8】図7に示す電源回路における負荷電流の増加に伴う電源電位の低下を示す図。

【符号の説明】

【0035】

10 2倍昇圧回路、 20、41〜43 オペアンプ、 30 分圧回路、 31、33 抵抗、 32 電位調整回路、 32a〜32d 配線、 50 昇圧回路、 R320〜R324 抵抗、 F1〜F4 ヒューズ、 SW1〜SW4 スイッチ回路、 QP11〜QP22 PチャネルMOSトランジスタ、 QN11 NチャネルMOSトランジスタ、 C1 コンデンサ

【特許請求の範囲】

【請求項1】

外部から供給される電源電圧に基づいて複数の電源電位を生成する半導体集積回路であって、

外部から供給される電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路と、

前記第1の増幅回路によって生成される第1の電位を分圧して、第2の電位を含む複数の電位を生成する分圧回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、前記分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、前記分圧回路によって生成される第2の電位以外の所定数の電位をバッファして電源電位として出力する複数の増幅回路と、

前記第1の増幅回路によって生成される第1の電位と、前記第2の増幅回路から出力される第2の電位とに基づいて昇圧動作を行うことにより、前記第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路と、

を具備する半導体集積回路。

【請求項2】

前記分圧回路が、配線層のパターンを変更するのみで、複数の電位の内から選択された1つの電位を前記第2の電位として出力するように構成されている、請求項1記載の半導体集積回路。

【請求項3】

前記分圧回路が、複数の電位の内から選択された1つの電位を前記第2の電位として出力するための少なくとも1つのヒューズを含む、請求項1記載の半導体集積回路。

【請求項4】

前記分圧回路が、外部から供給される制御信号に従って複数の電位の内から1つの電位を選択して前記第2の電位として出力するための少なくとも1つのスイッチ回路を含む、請求項1記載の半導体集積回路。

【請求項1】

外部から供給される電源電圧に基づいて複数の電源電位を生成する半導体集積回路であって、

外部から供給される電源電圧を昇圧して昇圧電圧を生成する第1の昇圧回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、基準電位に基づいて第1の電位を生成して電源電位として出力する第1の増幅回路と、

前記第1の増幅回路によって生成される第1の電位を分圧して、第2の電位を含む複数の電位を生成する分圧回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、前記分圧回路によって生成される第2の電位をバッファして出力する第2の増幅回路と、

前記第1の昇圧回路によって生成される昇圧電圧が供給されて動作し、前記分圧回路によって生成される第2の電位以外の所定数の電位をバッファして電源電位として出力する複数の増幅回路と、

前記第1の増幅回路によって生成される第1の電位と、前記第2の増幅回路から出力される第2の電位とに基づいて昇圧動作を行うことにより、前記第1の昇圧回路によって生成される昇圧電圧よりも高い電源電圧を生成する第2の昇圧回路と、

を具備する半導体集積回路。

【請求項2】

前記分圧回路が、配線層のパターンを変更するのみで、複数の電位の内から選択された1つの電位を前記第2の電位として出力するように構成されている、請求項1記載の半導体集積回路。

【請求項3】

前記分圧回路が、複数の電位の内から選択された1つの電位を前記第2の電位として出力するための少なくとも1つのヒューズを含む、請求項1記載の半導体集積回路。

【請求項4】

前記分圧回路が、外部から供給される制御信号に従って複数の電位の内から1つの電位を選択して前記第2の電位として出力するための少なくとも1つのスイッチ回路を含む、請求項1記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−41216(P2006−41216A)

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願番号】特願2004−219641(P2004−219641)

【出願日】平成16年7月28日(2004.7.28)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成18年2月9日(2006.2.9)

【国際特許分類】

【出願日】平成16年7月28日(2004.7.28)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]