電源回路

【課題】起動時や低電圧動作時の出力挙動を改善することが可能な電源回路を提供する。

【解決手段】電源回路1は、入力電圧VINの印加端と出力電圧VREGの印加端との間に接続された出力トランジスタP1と、出力電圧VREGに応じた帰還電圧VFBと所定の基準電圧VBとの差分を増幅して誤差電圧Vaを生成する誤差増幅部X1と、入力電圧VINの印加端と出力トランジスタP1のゲートとの間に接続された抵抗部X2と、誤差電圧Vaに応じて抵抗部X2に流れる電流Iaの電流値を制御する電流制御部X3と、誤差電圧Vaに応じて抵抗部X2の抵抗値を制御する抵抗制御部X4と、を有する。

【解決手段】電源回路1は、入力電圧VINの印加端と出力電圧VREGの印加端との間に接続された出力トランジスタP1と、出力電圧VREGに応じた帰還電圧VFBと所定の基準電圧VBとの差分を増幅して誤差電圧Vaを生成する誤差増幅部X1と、入力電圧VINの印加端と出力トランジスタP1のゲートとの間に接続された抵抗部X2と、誤差電圧Vaに応じて抵抗部X2に流れる電流Iaの電流値を制御する電流制御部X3と、誤差電圧Vaに応じて抵抗部X2の抵抗値を制御する抵抗制御部X4と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源回路に関するものである。

【背景技術】

【0002】

従来より、入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタの導通度(オン抵抗値)を制御することで入力電圧から所望の出力電圧を生成するシリーズレギュレータが知られている。

【0003】

なお、上記に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−95838号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、従来のシリーズレギュレータでは、入力電圧が定常値よりも低い状態において、出力トランジスタのゲート・ソース間電圧を十分に高めることができなくなるおそれがあった。そのため、シリーズレギュレータの起動時においては、出力電圧の立ち上がり速度が遅いという問題があり、また、シリーズレギュレータの低電圧動作時においては、出力電流の増大に伴って出力電圧が大きく低下するという問題があった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、起動時や低電圧動作時の出力挙動を改善することが可能な電源回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係る電源回路は、入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタと、前記出力電圧に応じた帰還電圧と所定の基準電圧との差分を増幅して誤差電圧を生成する誤差増幅部と、前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された抵抗部と、前記誤差電圧に応じて前記抵抗部に流れる電流の電流値を制御する電流制御部と、前記誤差電圧に応じて前記抵抗部の抵抗値を制御する抵抗制御部と、を有する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成る電源回路において、前記出力トランジスタは、PMOSFET[P-channel type metal oxide semiconductor field effect transistor]である構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成る電源回路において、前記誤差増幅部は、前記帰還電圧と前記基準電圧との差分が大きいほど前記誤差電圧の電圧値を高くし、前記電流制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部に流れる電流の電流値を大きくし、前記抵抗制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部の抵抗値を高くする構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成る電源回路において、前記抵抗部は、ゲートとドレインがいずれも前記出力トランジスタのゲートに接続された第1PMOSFETと;ソースが前記入力電圧の印加端に接続されて、ドレインが前記第1PMOSFETのソースに接続された第2PMOSFETと;を含み、前記抵抗制御部は、前記第2PMOSFETのゲート電圧を制御する構成(第4の構成)にするとよい。

【0011】

また、上記第4の構成から成る電源回路において、前記誤差増幅部は、前記入力電圧よりも低い電源電圧の供給を受けて動作する構成(第5の構成)にするとよい。

【0012】

また、上記第5の構成から成る電源回路において、前記電流制御部は、ゲートが前記誤差電圧の印加端に接続されて、ソースが接地端に接続された第1NMOSFETと;ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1NMOSFETのドレインに接続されて、ドレインが前記出力トランジスタのゲートに接続された第2NMOSFETと;を含む構成(第6の構成)にするとよい。

【0013】

また、上記第6の構成から成る電源回路において、前記抵抗制御部は、ゲートが前記誤差電圧の印加端に接続されて、ドレインが接地端に接続された第3PMOSFETと;第1端が前記第3PMOSFETのソースに接続された第1抵抗と;ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1抵抗の第2端に接続されて、ドレインが前記第2PMOSFETのゲートに接続された第3NMOSFETと;前記入力電圧の印加端と前記第2PMOSFETのゲートとの間に接続された第2抵抗と;を含む構成(第7の構成)にするとよい。

【0014】

また、上記第7の構成から成る電源回路は、前記入力電圧が立ち上がるときに前記入力電圧の印加端と前記出力トランジスタのゲートとの間を導通するプルアップ部を有する構成(第8の構成)にするとよい。

【0015】

また、上記第8の構成から成る電源回路において、前記プルアップ部は、前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された第4PMOSFETと;前記入力電圧の印加端と前記第4PMOSFETのゲートとの間に接続された第3抵抗と;前記第4PMOSFETのゲートと接地端との間に接続されたキャパシタと;アノードが前記第4PMOSFETのゲートに接続されて、カソードが前記入力電圧の印加端に接続されたツェナダイオードと;を含む構成(第9の構成)にするとよい。

【発明の効果】

【0016】

本発明に係る電源回路であれば、起動時や低電圧動作時の出力挙動を改善することが可能となる。

【図面の簡単な説明】

【0017】

【図1】電源回路の第1実施形態を示す回路図

【図2】電源回路の入出力特性図

【図3】電源回路の第2実施形態を示す回路図

【図4】起動時における出力電圧VREGの出力挙動を示す図

【図5】低電圧動作時における出力電圧VREGの出力挙動を示す図

【図6】スタンバイ時における出力電圧VREGの異常出力を示す図

【図7】電源回路の第3実施形態を示す回路図

【図8】スタンバイ時における出力電圧VREGの正常出力を示す図

【発明を実施するための形態】

【0018】

<第1実施形態>

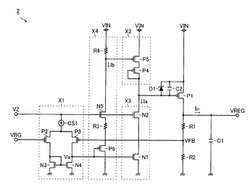

図1は、電源回路の第1実施形態を示す回路図である。第1実施形態の電源回路1は、入力電圧VIN(例えば12V)を降圧して出力電圧VREG(例えば5V)を生成するシリーズレギュレータであり、Pチャネル型MOS電界効果トランジスタP1〜P4と、Nチャネル型MOS電界効果トランジスタN1〜N4と、抵抗R1及びR2と、キャパシタC1及びC2と、ツェナダイオードD1と、電流源CS1と、を有する。なお、電源回路1の用途としては、例えば半導体装置の内部電源回路を挙げることができる。

【0019】

トランジスタP1のソースは、入力電圧VINの印加端に接続されている。トランジスタP1のドレインは、出力電圧VREGの印加端に接続されている。トランジスタP1のゲートとソースとの間には、ツェナダイオードD1とキャパシタC2が並列に接続されている。アノードがトランジスタP1のゲートに接続されて、カソードがトランジスタP1のソースに接続されている。出力電圧VREGの印加端と接地端との間には、抵抗R1及びR2が直列に接続されている。また、出力電圧VREGの印加端と接地端との間には、キャパシタC1が接続されている。

【0020】

トランジスタP2のゲートは、基準電圧VBG(例えば1.2V)の印加端に接続されている。トランジスタP3のゲートは、帰還電圧VFB(出力電圧VREGの分圧電圧)の印加端(抵抗R1と抵抗R2との接続ノード)に接続されている。トランジスタP2及びP3のソースは、いずれも電流源CS1を介して電源電圧VZ(例えば5V)の印加端に接続されている。トランジスタN3のドレインは、トランジスタP2のドレインに接続されている。トランジスタN4のドレインは、トランジスタP3のドレインに接続されている。トランジスタN3及びN4のゲートは、いずれもトランジスタN3のドレインに接続されている。トランジスタN3及びN4のソースはいずれも接地端に接続されている。なお、上記の基準電圧VBGや電源電圧VZは、別途の電源回路によって入力電圧VINから生成される。

【0021】

トランジスタP4のソースは、入力電圧VINの印加端に接続されている。トランジスタP4のゲート及びドレインは、いずれもトランジスタP1のゲートに接続されている。

【0022】

トランジスタN1のゲートは、誤差電圧Vaの印加端(トランジスタP3とトランジスタN4との接続ノード)に接続されている。トランジスタN1のソースは、接地端に接続されている。トランジスタN2のゲートは、電源電圧VZの印加端に接続されている。トランジスタN2のソースは、トランジスタN1のドレインに接続されている。トランジスタN2のドレインは、トランジスタP1のゲートに接続されている。

【0023】

上記構成から成る電源回路1において、トランジスタP1は、入力電圧VINの印加端と出力電圧VREGの印加端との間に接続された出力トランジスタに相当する。なお、ツェナダイオードD1は、トランジスタP1のゲート・ソース間電圧を所定の上限値にクランプする保護素子である。また、キャパシタC2は、トランジスタP1のゲート・ソース間電圧を安定させるために設けられている。

【0024】

トランジスタP2及びP3、トランジスタN3及びN4、並びに、電流源CS1は、出力電圧VREGに応じた帰還電圧VFBと所定の基準電圧VBGとの差分を増幅して誤差電圧Vaを生成する誤差増幅部X1を形成する。この誤差増幅部X1は、入力電圧VINよりも低い電源電圧VZの供給を受けて動作する構成であり、誤差増幅部X1を形成する回路要素(P2、P3、N3、N4、CS1)に入力電圧VINが直接印加されることはない。従って、誤差増幅部X1を形成する回路要素(P2、P3、N3、N4、CS1)として、入力電圧VINの印加に耐え得る高耐圧素子を用いる必要はない。

【0025】

トランジスタP4は、入力電圧VINの印加端とトランジスタP1のゲートとの間に接続された抵抗部X2を形成する。トランジスタP4のソース・ドレイン間には、トランジスタP4に流れる電流IaとトランジスタP4のオン抵抗値Ronとの乗算結果に相当する電圧降下(=Ia×Ron)が発生する。

【0026】

トランジスタN1及びN2は、誤差電圧Vaに応じて抵抗部X2に流れる電流Iaの電流値を制御する電流制御部X3に相当する。なお、トランジスタN1のドレインに印加される電圧は、トランジスタN2を介してほぼ電源電圧VZ(正確には電源電圧VZよりもトランジスタN2のゲート・ソース間電圧Vgs(N2)分だけ低い電圧)にバイアスされており、トランジスタN1のドレインに入力電圧VINが直接印加されることはない。従って、トランジスタN1として入力電圧VINの印加に耐え得る高耐圧素子を用いる必要はない。

【0027】

上記構成から成る電源回路1の動作について説明する。出力電圧VREGが目標値から大きく乖離しているときには、帰還電圧VFBと基準電圧VBGとの差分が大きくなり、誤差電圧Vaの電圧値が高くなる。誤差電圧Vaの電圧値が高くなると、トランジスタN1の導通度が高くなるので、抵抗部X2に流れる電流Iaの電流値が大きくなる。電流Iaが大きくなると、抵抗部X2で生じる電圧降下が大きくなるので、トランジスタP1のゲート・ソース間に生じる電位差が大きくなる。その結果、トランジスタP1の導通度が高くなり、出力電圧VREGの上昇が促進される。

【0028】

その後、出力電圧VREGが目標値に近付くにつれて、帰還電圧VFBと基準電圧VBGとの差分が小さくなり、誤差電圧Vaの電圧値が低くなる。誤差電圧Vaの電圧値が低くなると、トランジスタN1の導通度が低くなるので、抵抗部X2に流れる電流Iaの電流値が小さくなる。電流Iaが小さくなると、抵抗部X2で生じる電圧降下が小さくなるので、ランジスタP1のゲート・ソース間に生じる電位差が小さくなる。その結果、トランジスタP1の導通度が低くなり、出力電圧VREGの上昇が抑制される。

【0029】

このように、電源回路1では、出力電圧VREGの帰還制御に基づいて、トランジスタP1の導通度(オン抵抗値)を制御することにより、入力電圧VINから所望の出力電圧VREGを生成することができる(図2を参照)。

【0030】

<第2実施形態>

先に説明した第1実施形態の電源回路1では、従来のシリーズレギュレータと同様、入力電圧VINが定常値(例えば12V)よりも低い状態(電源回路1の起動時や低電圧動作時)において、トランジスタP1のゲート・ソース間電圧を十分に高めることができなくなるおそれがある。

【0031】

なお、トランジスタP4のオン抵抗値Ronを高めに設定しておけば、電源回路1の起動時や低電圧動作時においても、トランジスタP1のゲート・ソース間電圧を高めることは可能である。しかし、トランジスタP4のオン抵抗値Ronを高めに設定すると、帰還ループの位相余裕がなくなって出力発振を生じる危険性が増大してしまう。

【0032】

従って、出力発振を招くことなく、電源回路1の起動時や低電圧動作時における出力挙動を改善するためには、抵抗部X2の抵抗値を固定的に設定するのではなく、必要に応じて可変制御することが重要となる。

【0033】

図3は、電源回路の第2実施形態を示す回路図である。第2実施形態の電源回路1は、先述の第1実施形態に加えて、Pチャネル型MOS電界効果トランジスタP4〜P6と、Nチャネル型MOS電界効果トランジスタN5と、抵抗R3及びR4と、を有する点に特徴がある。そこで、第1実施形態と同様の構成部分については、図1と同一符号を付すことで重複した説明を割愛し、以下では、第2実施形態の特徴部分についてのみ、重点的な説明を行う。

【0034】

トランジスタP4のソースは、入力電圧VINの印加端に直接接続されるのではなく、トランジスタP5のドレインに接続されている。トランジスタP5のソースは、入力電圧VINの印加端に接続されている。このように、第2実施形態の電源回路1では、入力電圧VINの印加端とトランジスタP1のゲートとの間に直列接続されたトランジスタP4及びP5によって抵抗部X2が形成されている。従って、抵抗部X2の抵抗値は、トランジスタP4のオン抵抗値(固定値)とトランジスタP5のオン抵抗値(可変値)との直列合成値となる。

【0035】

トランジスタP6のゲートは、誤差電圧Vaの印加端に接続されている。トランジスタP6のドレインは、接地端に接続されている。トランジスタP6のソースは、抵抗R3の第1端に接続されている。抵抗R3の第2端は、トランジスタN5のソースに接続されている。トランジスタN5のゲートは、電源電圧VZの印加端に接続されている。トランジスタN5のドレインは、トランジスタP5のゲートに接続される一方、抵抗R4を介して入力電圧VINの印加端にも接続されている。なお、トランジスタP6、トランジスタN5、並びに、抵抗R3及びR4は、誤差電圧Vaに応じてトランジスタP5のゲート電圧を制御することによって抵抗部X2の抵抗値を可変制御する抵抗制御部X4を形成する。

【0036】

上記構成から成る抵抗制御部X4の動作について説明する。出力電圧VREGが目標値から大きく乖離しているときには、帰還電圧VFBと基準電圧VBGとの差分が大きくなり、誤差電圧Vaの電圧値が高くなる。誤差電圧Vaの電圧値が高くなると、トランジスタP6の導通度が低くなるので、抵抗R4に流れる電流Ibの電流値が小さくなる。電流Ibが小さくなると、抵抗R4で生じる電圧降下が小さくなるので、トランジスタP5のゲート・ソース間に生じる電位差が小さくなる。その結果、トランジスタP5の導通度が低くなり、抵抗部X2の抵抗値(トランジスタP4のオン抵抗値(固定値)とトランジスタP5のオン抵抗値(可変値)との直列合成値)が高くなる。

【0037】

その後、出力電圧VREGが目標値に近付くにつれて、帰還電圧VFBと基準電圧VBGの差分が小さくなり、誤差電圧Vaの電圧値が低くなる。誤差電圧Vaの電圧値が低くなると、トランジスタP6の導通度が高くなるので、抵抗R4に流れる電流Ibの電流値が大きくなる。電流Ibが大きくなると、抵抗R4で生じる電圧降下が大きくなるので、トランジスタP5のゲート・ソース間に生じる電位差が大きくなる。その結果、トランジスタP5の導通度が高くなり、抵抗部X2の抵抗値が低くなる。

【0038】

このように、抵抗部X2の抵抗値を固定的に設定するのではなく、必要に応じて可変制御する構成であれば、出力発振を招くことなくトランジスタP1のゲート・ソース間電圧を高めることが可能となり、延いては、電源回路1の起動時や低電圧動作時における出力挙動を改善することが可能となる。

【0039】

図4は、電源回路1の起動時における出力電圧VREGの出力挙動を示す図であり、入力電圧VINと出力電圧VREGの波形が縦に並べて描写されている。なお、出力電圧VREGについて、実線は第2実施形態の波形であり、破線は第1実施形態の波形である。図4で示したように、抵抗制御部X4を設けたことにより、電源回路1の起動時における出力電圧VREGの立ち上がり速度を改善することが可能となる。

【0040】

図5は、電源回路1の低電圧動作時における出力電圧VREGの出力挙動を示す図であり、横軸を出力電流Ioとし、縦軸を出力電圧VREGとしている。なお、図中の実線は第2実施形態の出力挙動を示しており、破線は第1実施形態の出力挙動を示している。図5で示したように、抵抗制御部X4を設けたことにより、電源回路1の低電圧動作時において出力電流Ioが増大したときであっても、出力電圧VREGの低下を抑制することが可能となる。

【0041】

<第3実施形態>

先述の第1実施形態や第2実施形態では、電源回路1がレディ状態(入力電圧VINの供給を受けて出力電圧VREGを出力する状態)であることを前提として、電源回路1の起動時や低電圧動作時における出力挙動の改善策を説明したが、第3実施形態では、電源回路1がスタンバイ状態(入力電圧VINの供給を受けている状態でありながら出力電圧VREGを出力させない状態)であるときに生じ得る問題点とその解決策について、詳細な説明を行う。

【0042】

図6は、スタンバイ時における出力電圧VREGの異常出力を示す図であり、上から順に、入力電圧VIN、トランジスタP1のゲート・ソース間電圧Vgs(P1)、及び、出力電圧VREGの波形が描写されている。

【0043】

入力電圧VINの投入に際して、トランジスタP1のゲート電圧が入力電圧VINの急峻な立ち上がりに追従できなかった場合、図6で示したように、トランジスタP1のゲート・ソース間電圧Vgs(P1)が意図せずに大きくなる。このような状態に陥ると、電源回路1がスタンバイ状態(誤差増幅部X1が誤差電圧Vaを出力しておらずトランジスタN1が完全にオフされている状態)であっても、トランジスタP1がオンとなって出力電圧VREGが上昇してしまう。

【0044】

従って、電源回路1を確実にスタンバイ状態とするためには、入力電圧VINの急峻な立ち上がりに追従してトランジスタP1のゲート電圧を速やかに引き上げてやることが重要である。

【0045】

図7は、電源回路の第3実施形態を示す回路図である。第3実施形態の電源回路1は、先述の第2実施形態に加えて、Pチャネル型MOS電界効果トランジスタP7と、抵抗R5と、キャパシタC3と、ツェナダイオードD2と、を有する点に特徴がある。そこで、第2実施形態と同様の構成部分については、図3と同一符号を付すことで重複した説明を割愛し、以下では、第3実施形態の特徴部分についてのみ、重点的な説明を行う。

【0046】

トランジスタP7のソースは、入力電圧VINの印加端に接続されている。トランジスタP7のドレインは、トランジスタP1のゲートに接続されている。抵抗R5の第1端は入力電圧VINの印加端に接続されている。抵抗R5の第2端とキャパシタC3の第1端は、いずれもトランジスタP7のゲートに接続されている。キャパシタC3の第2端は、接地端に接続されている。ツェナダイオードD2のアノードは、トランジスタP7のゲートに接続されている。ツェナダイオードD2のカソードは、入力電圧VINの印加端に接続されている。

【0047】

なお、第3実施形態で追加されたトランジスタP7、抵抗R5、キャパシタC3、及びツェナダイオードD2は、入力電圧VINが急峻に立ち上がるときに入力電圧VINの印加端とトランジスタP1のゲートとの間を導通するプルアップ部X5を形成する。

【0048】

上記構成から成るプルアップ部X5の動作について、図8を参照しながら詳細に説明する。図8は、スタンバイ時における出力電圧VREGの正常出力を示す図であり、上から順に、入力電圧VIN、トランジスタP1のゲート・ソース間電圧Vgs(P1)、トランジスタP7のゲート・ソース間電圧Vgs(P7)、及び、出力電圧VREGの波形が描写されている。なお、図中の実線は第3実施形態の波形を示しており、破線は第1実施形態または第2実施形態の波形を示している。

【0049】

入力電圧VINの投入に際して、入力電圧VINが急峻に立ち上がると、トランジスタP7のゲート電圧(キャパシタC3の充電電圧)がこれに追従せず、トランジスタP7のゲート・ソース間電圧Vgs(P7)が大きくなるので、トランジスタP7の導通度が高くなる。トランジスタP7の導通度が高くなると、トランジスタP1のゲートが入力電圧VINの印加端にプルアップされた状態(トランジスタP1のゲート・ソース間がショートされた状態)となる。その結果、トランジスタP1のゲート電圧が入力電圧VINの急峻な立ち上がりに追従して速やかに立ち上がるので、トランジスタP1のゲート・ソース間電圧Vgs(P1)がゼロ値(またはゼロ値近傍)に維持される。トランジスタP1のゲート・ソース間電圧Vgs(P1)が発生しなければ、出力電圧VREGの意図しない上昇も生じないので、電源回路1を確実にスタンバイ状態とすることができる。

【0050】

なお、プルアップ部X5は、入力電圧VINの急峻な立ち上がりに際して瞬間的に動作するものあり、レディ状態における出力電圧VREGの速やかな立ち上げ動作(図4を参照)に支障を及ぼすことはない。

【0051】

また、入力電圧VINの投入に際して、入力電圧VINが緩やかに上昇する場合には、トランジスタP7のゲート・ソース間電圧Vgs(P7)が生じないので、プルアップ部X5は動作しない。

【0052】

また、上記の第3実施形態では、第2実施形態にプルアップ部X5を追加した構成を例に挙げて説明を行ったが、本発明の構成はこれに限定されるものではなく、第1実施形態にプルアップ部X5を追加した構成としても構わない。

【0053】

<その他の変形例>

なお、上記の実施形態では、半導体装置の内部電源回路に本発明を適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、その他の用途に供されるシリーズレギュレータ型の電源回路全般に広く適用することが可能である。

【0054】

また、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0055】

本発明に係る電源回路は、例えば、半導体装置の内部電源回路として利用することが可能である。

【符号の説明】

【0056】

1 電源回路

P1〜P7 Pチャネル型MOS電界効果トランジスタ

N1〜N5 Nチャネル型MOS電界効果トランジスタ

R1〜R5 抵抗

C1〜C3 キャパシタ

D1、D2 ツェナダイオード

CS1 電流源

X1 誤差増幅部

X2 抵抗部

X3 電流制御部

X4 抵抗制御部

X5 プルアップ部

【技術分野】

【0001】

本発明は、電源回路に関するものである。

【背景技術】

【0002】

従来より、入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタの導通度(オン抵抗値)を制御することで入力電圧から所望の出力電圧を生成するシリーズレギュレータが知られている。

【0003】

なお、上記に関連する従来技術の一例としては、特許文献1を挙げることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−95838号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、従来のシリーズレギュレータでは、入力電圧が定常値よりも低い状態において、出力トランジスタのゲート・ソース間電圧を十分に高めることができなくなるおそれがあった。そのため、シリーズレギュレータの起動時においては、出力電圧の立ち上がり速度が遅いという問題があり、また、シリーズレギュレータの低電圧動作時においては、出力電流の増大に伴って出力電圧が大きく低下するという問題があった。

【0006】

本発明は、本願の発明者らにより見出された上記の問題点に鑑み、起動時や低電圧動作時の出力挙動を改善することが可能な電源回路を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明に係る電源回路は、入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタと、前記出力電圧に応じた帰還電圧と所定の基準電圧との差分を増幅して誤差電圧を生成する誤差増幅部と、前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された抵抗部と、前記誤差電圧に応じて前記抵抗部に流れる電流の電流値を制御する電流制御部と、前記誤差電圧に応じて前記抵抗部の抵抗値を制御する抵抗制御部と、を有する構成(第1の構成)とされている。

【0008】

なお、上記第1の構成から成る電源回路において、前記出力トランジスタは、PMOSFET[P-channel type metal oxide semiconductor field effect transistor]である構成(第2の構成)にするとよい。

【0009】

また、上記第2の構成から成る電源回路において、前記誤差増幅部は、前記帰還電圧と前記基準電圧との差分が大きいほど前記誤差電圧の電圧値を高くし、前記電流制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部に流れる電流の電流値を大きくし、前記抵抗制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部の抵抗値を高くする構成(第3の構成)にするとよい。

【0010】

また、上記第3の構成から成る電源回路において、前記抵抗部は、ゲートとドレインがいずれも前記出力トランジスタのゲートに接続された第1PMOSFETと;ソースが前記入力電圧の印加端に接続されて、ドレインが前記第1PMOSFETのソースに接続された第2PMOSFETと;を含み、前記抵抗制御部は、前記第2PMOSFETのゲート電圧を制御する構成(第4の構成)にするとよい。

【0011】

また、上記第4の構成から成る電源回路において、前記誤差増幅部は、前記入力電圧よりも低い電源電圧の供給を受けて動作する構成(第5の構成)にするとよい。

【0012】

また、上記第5の構成から成る電源回路において、前記電流制御部は、ゲートが前記誤差電圧の印加端に接続されて、ソースが接地端に接続された第1NMOSFETと;ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1NMOSFETのドレインに接続されて、ドレインが前記出力トランジスタのゲートに接続された第2NMOSFETと;を含む構成(第6の構成)にするとよい。

【0013】

また、上記第6の構成から成る電源回路において、前記抵抗制御部は、ゲートが前記誤差電圧の印加端に接続されて、ドレインが接地端に接続された第3PMOSFETと;第1端が前記第3PMOSFETのソースに接続された第1抵抗と;ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1抵抗の第2端に接続されて、ドレインが前記第2PMOSFETのゲートに接続された第3NMOSFETと;前記入力電圧の印加端と前記第2PMOSFETのゲートとの間に接続された第2抵抗と;を含む構成(第7の構成)にするとよい。

【0014】

また、上記第7の構成から成る電源回路は、前記入力電圧が立ち上がるときに前記入力電圧の印加端と前記出力トランジスタのゲートとの間を導通するプルアップ部を有する構成(第8の構成)にするとよい。

【0015】

また、上記第8の構成から成る電源回路において、前記プルアップ部は、前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された第4PMOSFETと;前記入力電圧の印加端と前記第4PMOSFETのゲートとの間に接続された第3抵抗と;前記第4PMOSFETのゲートと接地端との間に接続されたキャパシタと;アノードが前記第4PMOSFETのゲートに接続されて、カソードが前記入力電圧の印加端に接続されたツェナダイオードと;を含む構成(第9の構成)にするとよい。

【発明の効果】

【0016】

本発明に係る電源回路であれば、起動時や低電圧動作時の出力挙動を改善することが可能となる。

【図面の簡単な説明】

【0017】

【図1】電源回路の第1実施形態を示す回路図

【図2】電源回路の入出力特性図

【図3】電源回路の第2実施形態を示す回路図

【図4】起動時における出力電圧VREGの出力挙動を示す図

【図5】低電圧動作時における出力電圧VREGの出力挙動を示す図

【図6】スタンバイ時における出力電圧VREGの異常出力を示す図

【図7】電源回路の第3実施形態を示す回路図

【図8】スタンバイ時における出力電圧VREGの正常出力を示す図

【発明を実施するための形態】

【0018】

<第1実施形態>

図1は、電源回路の第1実施形態を示す回路図である。第1実施形態の電源回路1は、入力電圧VIN(例えば12V)を降圧して出力電圧VREG(例えば5V)を生成するシリーズレギュレータであり、Pチャネル型MOS電界効果トランジスタP1〜P4と、Nチャネル型MOS電界効果トランジスタN1〜N4と、抵抗R1及びR2と、キャパシタC1及びC2と、ツェナダイオードD1と、電流源CS1と、を有する。なお、電源回路1の用途としては、例えば半導体装置の内部電源回路を挙げることができる。

【0019】

トランジスタP1のソースは、入力電圧VINの印加端に接続されている。トランジスタP1のドレインは、出力電圧VREGの印加端に接続されている。トランジスタP1のゲートとソースとの間には、ツェナダイオードD1とキャパシタC2が並列に接続されている。アノードがトランジスタP1のゲートに接続されて、カソードがトランジスタP1のソースに接続されている。出力電圧VREGの印加端と接地端との間には、抵抗R1及びR2が直列に接続されている。また、出力電圧VREGの印加端と接地端との間には、キャパシタC1が接続されている。

【0020】

トランジスタP2のゲートは、基準電圧VBG(例えば1.2V)の印加端に接続されている。トランジスタP3のゲートは、帰還電圧VFB(出力電圧VREGの分圧電圧)の印加端(抵抗R1と抵抗R2との接続ノード)に接続されている。トランジスタP2及びP3のソースは、いずれも電流源CS1を介して電源電圧VZ(例えば5V)の印加端に接続されている。トランジスタN3のドレインは、トランジスタP2のドレインに接続されている。トランジスタN4のドレインは、トランジスタP3のドレインに接続されている。トランジスタN3及びN4のゲートは、いずれもトランジスタN3のドレインに接続されている。トランジスタN3及びN4のソースはいずれも接地端に接続されている。なお、上記の基準電圧VBGや電源電圧VZは、別途の電源回路によって入力電圧VINから生成される。

【0021】

トランジスタP4のソースは、入力電圧VINの印加端に接続されている。トランジスタP4のゲート及びドレインは、いずれもトランジスタP1のゲートに接続されている。

【0022】

トランジスタN1のゲートは、誤差電圧Vaの印加端(トランジスタP3とトランジスタN4との接続ノード)に接続されている。トランジスタN1のソースは、接地端に接続されている。トランジスタN2のゲートは、電源電圧VZの印加端に接続されている。トランジスタN2のソースは、トランジスタN1のドレインに接続されている。トランジスタN2のドレインは、トランジスタP1のゲートに接続されている。

【0023】

上記構成から成る電源回路1において、トランジスタP1は、入力電圧VINの印加端と出力電圧VREGの印加端との間に接続された出力トランジスタに相当する。なお、ツェナダイオードD1は、トランジスタP1のゲート・ソース間電圧を所定の上限値にクランプする保護素子である。また、キャパシタC2は、トランジスタP1のゲート・ソース間電圧を安定させるために設けられている。

【0024】

トランジスタP2及びP3、トランジスタN3及びN4、並びに、電流源CS1は、出力電圧VREGに応じた帰還電圧VFBと所定の基準電圧VBGとの差分を増幅して誤差電圧Vaを生成する誤差増幅部X1を形成する。この誤差増幅部X1は、入力電圧VINよりも低い電源電圧VZの供給を受けて動作する構成であり、誤差増幅部X1を形成する回路要素(P2、P3、N3、N4、CS1)に入力電圧VINが直接印加されることはない。従って、誤差増幅部X1を形成する回路要素(P2、P3、N3、N4、CS1)として、入力電圧VINの印加に耐え得る高耐圧素子を用いる必要はない。

【0025】

トランジスタP4は、入力電圧VINの印加端とトランジスタP1のゲートとの間に接続された抵抗部X2を形成する。トランジスタP4のソース・ドレイン間には、トランジスタP4に流れる電流IaとトランジスタP4のオン抵抗値Ronとの乗算結果に相当する電圧降下(=Ia×Ron)が発生する。

【0026】

トランジスタN1及びN2は、誤差電圧Vaに応じて抵抗部X2に流れる電流Iaの電流値を制御する電流制御部X3に相当する。なお、トランジスタN1のドレインに印加される電圧は、トランジスタN2を介してほぼ電源電圧VZ(正確には電源電圧VZよりもトランジスタN2のゲート・ソース間電圧Vgs(N2)分だけ低い電圧)にバイアスされており、トランジスタN1のドレインに入力電圧VINが直接印加されることはない。従って、トランジスタN1として入力電圧VINの印加に耐え得る高耐圧素子を用いる必要はない。

【0027】

上記構成から成る電源回路1の動作について説明する。出力電圧VREGが目標値から大きく乖離しているときには、帰還電圧VFBと基準電圧VBGとの差分が大きくなり、誤差電圧Vaの電圧値が高くなる。誤差電圧Vaの電圧値が高くなると、トランジスタN1の導通度が高くなるので、抵抗部X2に流れる電流Iaの電流値が大きくなる。電流Iaが大きくなると、抵抗部X2で生じる電圧降下が大きくなるので、トランジスタP1のゲート・ソース間に生じる電位差が大きくなる。その結果、トランジスタP1の導通度が高くなり、出力電圧VREGの上昇が促進される。

【0028】

その後、出力電圧VREGが目標値に近付くにつれて、帰還電圧VFBと基準電圧VBGとの差分が小さくなり、誤差電圧Vaの電圧値が低くなる。誤差電圧Vaの電圧値が低くなると、トランジスタN1の導通度が低くなるので、抵抗部X2に流れる電流Iaの電流値が小さくなる。電流Iaが小さくなると、抵抗部X2で生じる電圧降下が小さくなるので、ランジスタP1のゲート・ソース間に生じる電位差が小さくなる。その結果、トランジスタP1の導通度が低くなり、出力電圧VREGの上昇が抑制される。

【0029】

このように、電源回路1では、出力電圧VREGの帰還制御に基づいて、トランジスタP1の導通度(オン抵抗値)を制御することにより、入力電圧VINから所望の出力電圧VREGを生成することができる(図2を参照)。

【0030】

<第2実施形態>

先に説明した第1実施形態の電源回路1では、従来のシリーズレギュレータと同様、入力電圧VINが定常値(例えば12V)よりも低い状態(電源回路1の起動時や低電圧動作時)において、トランジスタP1のゲート・ソース間電圧を十分に高めることができなくなるおそれがある。

【0031】

なお、トランジスタP4のオン抵抗値Ronを高めに設定しておけば、電源回路1の起動時や低電圧動作時においても、トランジスタP1のゲート・ソース間電圧を高めることは可能である。しかし、トランジスタP4のオン抵抗値Ronを高めに設定すると、帰還ループの位相余裕がなくなって出力発振を生じる危険性が増大してしまう。

【0032】

従って、出力発振を招くことなく、電源回路1の起動時や低電圧動作時における出力挙動を改善するためには、抵抗部X2の抵抗値を固定的に設定するのではなく、必要に応じて可変制御することが重要となる。

【0033】

図3は、電源回路の第2実施形態を示す回路図である。第2実施形態の電源回路1は、先述の第1実施形態に加えて、Pチャネル型MOS電界効果トランジスタP4〜P6と、Nチャネル型MOS電界効果トランジスタN5と、抵抗R3及びR4と、を有する点に特徴がある。そこで、第1実施形態と同様の構成部分については、図1と同一符号を付すことで重複した説明を割愛し、以下では、第2実施形態の特徴部分についてのみ、重点的な説明を行う。

【0034】

トランジスタP4のソースは、入力電圧VINの印加端に直接接続されるのではなく、トランジスタP5のドレインに接続されている。トランジスタP5のソースは、入力電圧VINの印加端に接続されている。このように、第2実施形態の電源回路1では、入力電圧VINの印加端とトランジスタP1のゲートとの間に直列接続されたトランジスタP4及びP5によって抵抗部X2が形成されている。従って、抵抗部X2の抵抗値は、トランジスタP4のオン抵抗値(固定値)とトランジスタP5のオン抵抗値(可変値)との直列合成値となる。

【0035】

トランジスタP6のゲートは、誤差電圧Vaの印加端に接続されている。トランジスタP6のドレインは、接地端に接続されている。トランジスタP6のソースは、抵抗R3の第1端に接続されている。抵抗R3の第2端は、トランジスタN5のソースに接続されている。トランジスタN5のゲートは、電源電圧VZの印加端に接続されている。トランジスタN5のドレインは、トランジスタP5のゲートに接続される一方、抵抗R4を介して入力電圧VINの印加端にも接続されている。なお、トランジスタP6、トランジスタN5、並びに、抵抗R3及びR4は、誤差電圧Vaに応じてトランジスタP5のゲート電圧を制御することによって抵抗部X2の抵抗値を可変制御する抵抗制御部X4を形成する。

【0036】

上記構成から成る抵抗制御部X4の動作について説明する。出力電圧VREGが目標値から大きく乖離しているときには、帰還電圧VFBと基準電圧VBGとの差分が大きくなり、誤差電圧Vaの電圧値が高くなる。誤差電圧Vaの電圧値が高くなると、トランジスタP6の導通度が低くなるので、抵抗R4に流れる電流Ibの電流値が小さくなる。電流Ibが小さくなると、抵抗R4で生じる電圧降下が小さくなるので、トランジスタP5のゲート・ソース間に生じる電位差が小さくなる。その結果、トランジスタP5の導通度が低くなり、抵抗部X2の抵抗値(トランジスタP4のオン抵抗値(固定値)とトランジスタP5のオン抵抗値(可変値)との直列合成値)が高くなる。

【0037】

その後、出力電圧VREGが目標値に近付くにつれて、帰還電圧VFBと基準電圧VBGの差分が小さくなり、誤差電圧Vaの電圧値が低くなる。誤差電圧Vaの電圧値が低くなると、トランジスタP6の導通度が高くなるので、抵抗R4に流れる電流Ibの電流値が大きくなる。電流Ibが大きくなると、抵抗R4で生じる電圧降下が大きくなるので、トランジスタP5のゲート・ソース間に生じる電位差が大きくなる。その結果、トランジスタP5の導通度が高くなり、抵抗部X2の抵抗値が低くなる。

【0038】

このように、抵抗部X2の抵抗値を固定的に設定するのではなく、必要に応じて可変制御する構成であれば、出力発振を招くことなくトランジスタP1のゲート・ソース間電圧を高めることが可能となり、延いては、電源回路1の起動時や低電圧動作時における出力挙動を改善することが可能となる。

【0039】

図4は、電源回路1の起動時における出力電圧VREGの出力挙動を示す図であり、入力電圧VINと出力電圧VREGの波形が縦に並べて描写されている。なお、出力電圧VREGについて、実線は第2実施形態の波形であり、破線は第1実施形態の波形である。図4で示したように、抵抗制御部X4を設けたことにより、電源回路1の起動時における出力電圧VREGの立ち上がり速度を改善することが可能となる。

【0040】

図5は、電源回路1の低電圧動作時における出力電圧VREGの出力挙動を示す図であり、横軸を出力電流Ioとし、縦軸を出力電圧VREGとしている。なお、図中の実線は第2実施形態の出力挙動を示しており、破線は第1実施形態の出力挙動を示している。図5で示したように、抵抗制御部X4を設けたことにより、電源回路1の低電圧動作時において出力電流Ioが増大したときであっても、出力電圧VREGの低下を抑制することが可能となる。

【0041】

<第3実施形態>

先述の第1実施形態や第2実施形態では、電源回路1がレディ状態(入力電圧VINの供給を受けて出力電圧VREGを出力する状態)であることを前提として、電源回路1の起動時や低電圧動作時における出力挙動の改善策を説明したが、第3実施形態では、電源回路1がスタンバイ状態(入力電圧VINの供給を受けている状態でありながら出力電圧VREGを出力させない状態)であるときに生じ得る問題点とその解決策について、詳細な説明を行う。

【0042】

図6は、スタンバイ時における出力電圧VREGの異常出力を示す図であり、上から順に、入力電圧VIN、トランジスタP1のゲート・ソース間電圧Vgs(P1)、及び、出力電圧VREGの波形が描写されている。

【0043】

入力電圧VINの投入に際して、トランジスタP1のゲート電圧が入力電圧VINの急峻な立ち上がりに追従できなかった場合、図6で示したように、トランジスタP1のゲート・ソース間電圧Vgs(P1)が意図せずに大きくなる。このような状態に陥ると、電源回路1がスタンバイ状態(誤差増幅部X1が誤差電圧Vaを出力しておらずトランジスタN1が完全にオフされている状態)であっても、トランジスタP1がオンとなって出力電圧VREGが上昇してしまう。

【0044】

従って、電源回路1を確実にスタンバイ状態とするためには、入力電圧VINの急峻な立ち上がりに追従してトランジスタP1のゲート電圧を速やかに引き上げてやることが重要である。

【0045】

図7は、電源回路の第3実施形態を示す回路図である。第3実施形態の電源回路1は、先述の第2実施形態に加えて、Pチャネル型MOS電界効果トランジスタP7と、抵抗R5と、キャパシタC3と、ツェナダイオードD2と、を有する点に特徴がある。そこで、第2実施形態と同様の構成部分については、図3と同一符号を付すことで重複した説明を割愛し、以下では、第3実施形態の特徴部分についてのみ、重点的な説明を行う。

【0046】

トランジスタP7のソースは、入力電圧VINの印加端に接続されている。トランジスタP7のドレインは、トランジスタP1のゲートに接続されている。抵抗R5の第1端は入力電圧VINの印加端に接続されている。抵抗R5の第2端とキャパシタC3の第1端は、いずれもトランジスタP7のゲートに接続されている。キャパシタC3の第2端は、接地端に接続されている。ツェナダイオードD2のアノードは、トランジスタP7のゲートに接続されている。ツェナダイオードD2のカソードは、入力電圧VINの印加端に接続されている。

【0047】

なお、第3実施形態で追加されたトランジスタP7、抵抗R5、キャパシタC3、及びツェナダイオードD2は、入力電圧VINが急峻に立ち上がるときに入力電圧VINの印加端とトランジスタP1のゲートとの間を導通するプルアップ部X5を形成する。

【0048】

上記構成から成るプルアップ部X5の動作について、図8を参照しながら詳細に説明する。図8は、スタンバイ時における出力電圧VREGの正常出力を示す図であり、上から順に、入力電圧VIN、トランジスタP1のゲート・ソース間電圧Vgs(P1)、トランジスタP7のゲート・ソース間電圧Vgs(P7)、及び、出力電圧VREGの波形が描写されている。なお、図中の実線は第3実施形態の波形を示しており、破線は第1実施形態または第2実施形態の波形を示している。

【0049】

入力電圧VINの投入に際して、入力電圧VINが急峻に立ち上がると、トランジスタP7のゲート電圧(キャパシタC3の充電電圧)がこれに追従せず、トランジスタP7のゲート・ソース間電圧Vgs(P7)が大きくなるので、トランジスタP7の導通度が高くなる。トランジスタP7の導通度が高くなると、トランジスタP1のゲートが入力電圧VINの印加端にプルアップされた状態(トランジスタP1のゲート・ソース間がショートされた状態)となる。その結果、トランジスタP1のゲート電圧が入力電圧VINの急峻な立ち上がりに追従して速やかに立ち上がるので、トランジスタP1のゲート・ソース間電圧Vgs(P1)がゼロ値(またはゼロ値近傍)に維持される。トランジスタP1のゲート・ソース間電圧Vgs(P1)が発生しなければ、出力電圧VREGの意図しない上昇も生じないので、電源回路1を確実にスタンバイ状態とすることができる。

【0050】

なお、プルアップ部X5は、入力電圧VINの急峻な立ち上がりに際して瞬間的に動作するものあり、レディ状態における出力電圧VREGの速やかな立ち上げ動作(図4を参照)に支障を及ぼすことはない。

【0051】

また、入力電圧VINの投入に際して、入力電圧VINが緩やかに上昇する場合には、トランジスタP7のゲート・ソース間電圧Vgs(P7)が生じないので、プルアップ部X5は動作しない。

【0052】

また、上記の第3実施形態では、第2実施形態にプルアップ部X5を追加した構成を例に挙げて説明を行ったが、本発明の構成はこれに限定されるものではなく、第1実施形態にプルアップ部X5を追加した構成としても構わない。

【0053】

<その他の変形例>

なお、上記の実施形態では、半導体装置の内部電源回路に本発明を適用した構成を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、その他の用途に供されるシリーズレギュレータ型の電源回路全般に広く適用することが可能である。

【0054】

また、本明細書中に開示されている種々の技術的特徴は、上記実施形態のほか、その技術的創作の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0055】

本発明に係る電源回路は、例えば、半導体装置の内部電源回路として利用することが可能である。

【符号の説明】

【0056】

1 電源回路

P1〜P7 Pチャネル型MOS電界効果トランジスタ

N1〜N5 Nチャネル型MOS電界効果トランジスタ

R1〜R5 抵抗

C1〜C3 キャパシタ

D1、D2 ツェナダイオード

CS1 電流源

X1 誤差増幅部

X2 抵抗部

X3 電流制御部

X4 抵抗制御部

X5 プルアップ部

【特許請求の範囲】

【請求項1】

入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタと、

前記出力電圧に応じた帰還電圧と所定の基準電圧との差分を増幅して誤差電圧を生成する誤差増幅部と、

前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された抵抗部と、

前記誤差電圧に応じて前記抵抗部に流れる電流の電流値を制御する電流制御部と、

前記誤差電圧に応じて前記抵抗部の抵抗値を制御する抵抗制御部と、

を有することを特徴とする電源回路。

【請求項2】

前記出力トランジスタは、PMOSFETであることを特徴とする請求項1に記載の電源回路。

【請求項3】

前記誤差増幅部は、前記帰還電圧と前記基準電圧との差分が大きいほど前記誤差電圧の電圧値を高くし、

前記電流制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部に流れる電流の電流値を大きくし、

前記抵抗制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部の抵抗値を高くすることを特徴とする請求項2に記載の電源回路。

【請求項4】

前記抵抗部は、

ゲートとドレインがいずれも前記出力トランジスタのゲートに接続された第1PMOSFETと;

ソースが前記入力電圧の印加端に接続されて、ドレインが前記第1PMOSFETのソースに接続された第2PMOSFETと;

を含み、

前記抵抗制御部は、前記第2PMOSFETのゲート電圧を制御することを特徴とする請求項3に記載の電源回路。

【請求項5】

前記誤差増幅部は、前記入力電圧よりも低い電源電圧の供給を受けて動作することを特徴とする請求項4に記載の電源回路。

【請求項6】

前記電流制御部は、

ゲートが前記誤差電圧の印加端に接続されて、ソースが接地端に接続された第1NMOSFETと;

ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1NMOSFETのドレインに接続されて、ドレインが前記出力トランジスタのゲートに接続された第2NMOSFETと;

を含むことを特徴とする請求項5に記載の電源回路。

【請求項7】

前記抵抗制御部は、

ゲートが前記誤差電圧の印加端に接続されて、ドレインが接地端に接続された第3PMOSFETと;

第1端が前記第3PMOSFETのソースに接続された第1抵抗と;

ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1抵抗の第2端に接続されて、ドレインが前記第2PMOSFETのゲートに接続された第3NMOSFETと;

前記入力電圧の印加端と前記第2PMOSFETのゲートとの間に接続された第2抵抗と;

を含むことを特徴とする請求項6に記載の電源回路。

【請求項8】

前記入力電圧が立ち上がるときに前記入力電圧の印加端と前記出力トランジスタのゲートとの間を導通するプルアップ部を有することを特徴とする請求項7に記載の電源回路。

【請求項9】

前記プルアップ部は、

前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された第4PMOSFETと;

前記入力電圧の印加端と前記第4PMOSFETのゲートとの間に接続された第3抵抗と;

前記第4PMOSFETのゲートと接地端との間に接続されたキャパシタと;

アノードが前記第4PMOSFETのゲートに接続されて、カソードが前記入力電圧の印加端に接続されたツェナダイオードと;

を含むことを特徴とする請求項8に記載の電源回路。

【請求項1】

入力電圧の印加端と出力電圧の印加端との間に接続された出力トランジスタと、

前記出力電圧に応じた帰還電圧と所定の基準電圧との差分を増幅して誤差電圧を生成する誤差増幅部と、

前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された抵抗部と、

前記誤差電圧に応じて前記抵抗部に流れる電流の電流値を制御する電流制御部と、

前記誤差電圧に応じて前記抵抗部の抵抗値を制御する抵抗制御部と、

を有することを特徴とする電源回路。

【請求項2】

前記出力トランジスタは、PMOSFETであることを特徴とする請求項1に記載の電源回路。

【請求項3】

前記誤差増幅部は、前記帰還電圧と前記基準電圧との差分が大きいほど前記誤差電圧の電圧値を高くし、

前記電流制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部に流れる電流の電流値を大きくし、

前記抵抗制御部は、前記誤差電圧の電圧値が高いほど前記抵抗部の抵抗値を高くすることを特徴とする請求項2に記載の電源回路。

【請求項4】

前記抵抗部は、

ゲートとドレインがいずれも前記出力トランジスタのゲートに接続された第1PMOSFETと;

ソースが前記入力電圧の印加端に接続されて、ドレインが前記第1PMOSFETのソースに接続された第2PMOSFETと;

を含み、

前記抵抗制御部は、前記第2PMOSFETのゲート電圧を制御することを特徴とする請求項3に記載の電源回路。

【請求項5】

前記誤差増幅部は、前記入力電圧よりも低い電源電圧の供給を受けて動作することを特徴とする請求項4に記載の電源回路。

【請求項6】

前記電流制御部は、

ゲートが前記誤差電圧の印加端に接続されて、ソースが接地端に接続された第1NMOSFETと;

ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1NMOSFETのドレインに接続されて、ドレインが前記出力トランジスタのゲートに接続された第2NMOSFETと;

を含むことを特徴とする請求項5に記載の電源回路。

【請求項7】

前記抵抗制御部は、

ゲートが前記誤差電圧の印加端に接続されて、ドレインが接地端に接続された第3PMOSFETと;

第1端が前記第3PMOSFETのソースに接続された第1抵抗と;

ゲートが前記電源電圧の印加端に接続されて、ソースが前記第1抵抗の第2端に接続されて、ドレインが前記第2PMOSFETのゲートに接続された第3NMOSFETと;

前記入力電圧の印加端と前記第2PMOSFETのゲートとの間に接続された第2抵抗と;

を含むことを特徴とする請求項6に記載の電源回路。

【請求項8】

前記入力電圧が立ち上がるときに前記入力電圧の印加端と前記出力トランジスタのゲートとの間を導通するプルアップ部を有することを特徴とする請求項7に記載の電源回路。

【請求項9】

前記プルアップ部は、

前記入力電圧の印加端と前記出力トランジスタのゲートとの間に接続された第4PMOSFETと;

前記入力電圧の印加端と前記第4PMOSFETのゲートとの間に接続された第3抵抗と;

前記第4PMOSFETのゲートと接地端との間に接続されたキャパシタと;

アノードが前記第4PMOSFETのゲートに接続されて、カソードが前記入力電圧の印加端に接続されたツェナダイオードと;

を含むことを特徴とする請求項8に記載の電源回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−89188(P2013−89188A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−232099(P2011−232099)

【出願日】平成23年10月21日(2011.10.21)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月21日(2011.10.21)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]