電源装置、および電源装置の電圧切替方法

【課題】フレア現像用高圧出力として、NchFET駆動によるフルブリッジ回路を構成する場合、NchFET駆動用の電源は、DC(直流)バイアス電源から生成し、単独のFET駆動用電源を不要とするとともに、NchFETのスイッチング駆動に必要な最低限のゲート−ソース端子間への電圧の供給を可能とする。

【解決手段】スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、DCバイアス電源111の出力電圧を分圧して、前記スイッチング素子のゲート端子−ソース端子に所定の電圧を出力する分圧部111aを備える。

【解決手段】スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、DCバイアス電源111の出力電圧を分圧して、前記スイッチング素子のゲート端子−ソース端子に所定の電圧を出力する分圧部111aを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源装置、および電源装置の電圧切替方法に関する。

【背景技術】

【0002】

従来、複写機などの電子写真方式の画像形成装置に用いられる現像方式の一つとして、トナーをクラウド化(ホッピングさせた状態、以下、フレア現像という)させる方式が知られている。このフレア現像方式においては、フレア現像ローラに逆相のパルス電圧を交互に印加して、充放電を繰り返すことで、印刷中はトナーがフレア現像ローラ上でホッピングした状態となり、トナーのクラウド化を実現している。上記パルスを発生させる方式としては、直流バイアスに重畳させて、回路としてはNchFET駆動によるフルブリッジ回路による構成が挙げられる。なお、NchFETは、N型チャネル接合型FET(Field Effect Transistor)の略称であり、以下、適宜、NchFETと記述する。

【0003】

なお、ブートストラップ回路の出力安定化を図るブートストラップ回路として、出力端子に一方の電極が結合されたブートストラップ容量と、所定の定電圧端子との間に双方向に向くように接続された一対の一方向性素子を介してゲートが結合されたクランプ用MOSFETと、クランプ用MOSFETを介してチャージアップされたブートストラップ容量の他端に駆動電圧を供給する駆動回路と、定電圧端子からみて上記クランプ用MOSFETと一対の一方向性素子からなる回路と実質的に等価となる一対の一方向性素子と容量素子からなり、クランプ用MOSFETを通して伝えられる信号と逆相の信号が容量素子に供給されてなるダミー回路とを備えたものが開示されている(たとえば、特許文献1参照)。なお、MOSFETは、Metal Oxide Semiconductor FETの略称である。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記に示されるような、NchFET駆動によるフルブリッジ回路による構成にあっては、フレア現像用高圧電源として、直流バイアス用、フルブリッジのハイ(H)サイド電源用、NchFET駆動用の3種類が必要となるという問題があった。

【0005】

本発明は、上記に鑑みてなされたものであって、フレア現像用高圧出力として、NchFET駆動によるフルブリッジ回路を構成する場合、NchFET駆動用の電源は、直流バイアス電源から生成し、単独のNchFET駆動用電源を不要とするとともに、NchFETのスイッチング駆動に必要な最低限のゲート−ソース端子間への電圧の供給を可能とすることを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するために、本発明は、スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備えることを特徴とする。

【発明の効果】

【0007】

本発明は、直流バイアス電源からNchFET駆動用の電源を、分圧構成にて取り出す構成としたため、NchFET駆動用の電源を単独でもつ必要がなくなり、さらにNchFETのゲート−ソース端子間にスイッチング駆動に必要な最低限の電圧の供給を行うことができるという効果を奏する。

【図面の簡単な説明】

【0008】

【図1】図1は、実施の形態にかかる電子写真方式のカラー画像形成装置の画像形成部の一例の説明図である。

【図2】図2は、図1における画像形成部に電力を供給する電源装置の概要構成を示すブロック図である。

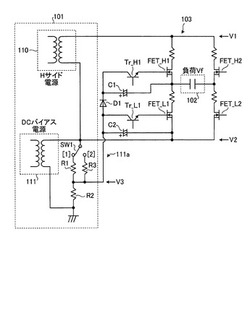

【図3】図3は、実施の形態にかかる電源装置の構成例1を示す回路図である。

【図4】図4は、図3の電源装置のシーケンス動作を示すタイミングチャートである。

【図5】図5は、実施の形態にかかる電源装置の構成例2を示す回路図である。

【図6】図6は、図5の電源装置のシーケンス動作を示すタイミングチャートである。

【図7】図7は、実施の形態にかかる電源装置の構成例3を示す回路図である。

【図8】図8は、実施の形態にかかる電源装置の構成例4を示す回路図である。

【発明を実施するための形態】

【0009】

以下に添付図面を参照して、この発明にかかる電源装置、および電源装置の電圧切替方法の一実施の形態を詳細に説明する。

【0010】

<実施の形態>

この実施の形態にかかる画像形成装置は、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する一般に複合機と称されるものであって、原稿を読み取り画像データに変換する画像読取部と、画像読取部で原稿を読み取って得られた画像データに対して画像処理を施す画像処理部と、画像処理された画像データに基づき紙面に画像を形成する画像形成部とを有する。

【0011】

まず、この実施の形態にかかるフレア現像用高圧電源が搭載される画像形成装置について説明する。図1は、電子写真方式のカラー画像形成装置における画像形成部の構成を示す説明図である。

【0012】

画像形成部は、4つの感光体ドラム10Y,10M,10C,10Kと、各感光体ドラム10Y,10M,10C,10K上に形成した潜像を互いに異なる色のトナー像にそれぞれ現像する複数の現像装置11Y,11M,11C,11Kと、異なる色のトナー像がそれぞれ重ね合わせ状態に一次転写される矢印A方向に回転する像担持体としての中間転写ベルト16とを備えている。

【0013】

中間転写ベルト16は、無端状のベルトである。本実施の形態では、中間転写ベルト16の上方に、中間転写ベルト16の回動方向Aに沿って、ブラック,シアン,マゼンタ,イエローの各色用の4個の上述した感光体ドラム10Y,10M,10C,10K(以下、それぞれを区別する必要が無い場合には、単に感光体ドラム10と記載する)を並列にそれぞれ配置している。感光体ドラム10の周囲には、帯電装置12と、前述した現像装置11と、一次転写装置を構成する一次転写ローラ14と、クリーニング装置13がそれぞれ配設されている。

【0014】

感光体ドラム10は、回転方向Bに回転駆動され、このとき帯電装置12によって感光体ドラム10の表面が所定の極性に帯電される。次いで、その帯電面に、露光装置15から画像データに応じて出射されるレーザ光が照射され、これによって感光体ドラム10に静電潜像が形成され、その静電潜像が現像装置11によって各色のトナー像として可視像化される。

【0015】

各感光体ドラム10には、一次転写ローラ14がそれぞれ対向配置されていて、その各一次転写ローラ14と感光体ドラム10との間には中間転写ベルト16が挟まれた状態で回動するようになっている。

【0016】

このとき、中間転写ベルト16は、駆動ローラ17とテンションローラ19の2個のローラによって支持されている。中間転写ベルト16を3個以上のローラによって張架しても良いが、できる限り小型化し、高さを抑制するため、本実施の形態では中間転写ベルト16を2個のローラによって張架することで、高さを抑制している。

【0017】

つぎに、その中間転写ベルト16の表面に、各感光体ドラム10に可視像化されたトナー像が、一次転写ローラ14の作用によって転写される。このようにして、ブラック(K),シアン(C),マゼンタ(M),イエロー(Y)のトナー像が、中間転写ベルト16に正確に順次重ね合わせた状態で転写されていき、フルカラーの合成カラー画像のトナー像が形成される。

【0018】

一方、中間転写ベルト16を挟んで、駆動ローラ17(二次転写対向ローラ)に対向して二次転写ローラ18が配設され、給紙ユニット21から記録媒体である転写紙Pが給紙される。これによりレジストローラ対22の回転によって、転写紙Pが所定のタイミングで、駆動ローラ17と二次転写ローラ18の間に送り込まれる。すると、中間転写ベルト16に担持されている合成カラー画像が二次転写ローラ18の作用により転写紙Pに一括して転写される。

【0019】

そして、その転写紙P上のトナー像が、定着装置23により熱と圧力によって定着され、図示しない排紙トレイ上に排出される。トナー像が二次転写された後の中間転写ベルト16の表面に付着している転写残トナーは、クリーニング装置20によって除去および回収される。

【0020】

なお、図1では、二次転写ローラ18を介して転写紙に転写する方式の例を示したが転写紙に直接転写する方式の画像形成装置を用いてもよい。

【0021】

上述した図1の画像形成部における現像装置11Y,11M,11C,11Kは、高容量のフレア現像ローラ102を有している。フレア現像方式は、先に述べたように、フレア現像ローラ102に逆相のパルス電圧を交互に印加して、充放電を繰り返すことで、印刷中はトナーがフレア現像ローラ102上でホッピングした状態となり、トナーのクラウド化を実現している。このパルスを発生させる方式としては、高圧電源の回路としてはNchFET駆動によるフルブリッジ回路による構成によってDCバイアスに重畳させることで実現される。本実施の形態では、この高容量のフレア現像ローラ102に後述するフレア現像用高圧電源回路により交流電圧を印加することで、トナーをホッピングさせた状態で現像するフレア現像を行っている。なお、上記DCは直流を示し、以下、DCと記載する。

【0022】

図2は、この実施の形態にかかる画像形成部に電力を供給する電源装置の概要構成を示すブロック図である。電源装置100は、フレア現像用の高圧電源を生成するフレア現像用高圧電源回路101と、フレア現像用高圧電源回路101からの電力供給を受けて容量性負荷Vfとして機能するフレア現像ローラ102に交流電圧を印加するフルブリッジ回路103と、フレア現像用高圧電源回路101およびフルブリッジ回路103を制御するコントローラ104と、を備えている。

【0023】

つぎに、上記の電源装置100の回路構成例1,2,3,4の詳細な構成について説明する。なお、以下に示すFETは、Field Effect Transistor:電界効果トランジスタの略称であり、以下、適宜、FETと記述し、また、NchはN型チャネルの略称である。

【0024】

(回路構成例1)

図3は、実施の形態にかかる電源装置100の回路構成例1を示す回路図である。この図3において、符号100はハイ(H)サイド電源、符号111はDCバイアス電源、符号111aは分圧部、符号R1,R2,R3は抵抗、符号SW1は図の接点[1],[2]側に切り替える切替スイッチ、符号D1はダイオード、符号C1,C2はコンデンサ、符号Tr_H1は高電位側トランジスタ、符号Tr_L1は低電位側トランジスタ、符号FET_H1は高電位側トランジスタスイッチ、符号FET_L1は低電位側トランジスタスイッチ、符号FET_H2は高電位側トランジスタスイッチ、符号FET_L2は低電位側トランジスタスイッチである。

【0025】

フルブリッジ回路103は、NchFET駆動による、高電位側トランジスタスイッチFET_H1、FET_H2および低電位側トランジスタスイッチFET_L1、FET_L2を備えている。ここで、高電位側トランジスタスイッチFET_H1と、低電位側トランジスタスイッチFET_L2と、は対となって動作しており、それぞれのゲート端子に制御信号が入力されることによりコントローラ104により同時にオン(閉状態)/オフ(開状態)される。

【0026】

また、同様に高電位側トランジスタスイッチFET_H2と、低電位側トランジスタスイッチFET_L1と、は対となって動作しており、それぞれのゲート端子に制御信号が入力されることでコントローラ104により同時にオン(閉状態)/オフ(開状態)される。

【0027】

したがって、容量性負荷としてのフレア現像ローラ102には、パルス電圧が印加されることとなる。また、切替スイッチSW1についても、コントローラ104からそれぞれ切替制御信号が入力され、コントローラ104の制御下で、オン/オフ(閉/開)制御がなされる。

【0028】

図3において、DCバイアス電源111の出力側に抵抗R1と抵抗R3が並列に接続され、分圧部111aを構成する切替スイッチSW1により、抵抗R1と抵抗R3が切り替えられる。コントローラ104により、起動前には抵抗R1が接続された接点[1]側、起動時には抵抗R3が接続された接点[2]側に接続の切り替えを行う。一般的に、これらの抵抗値は、R3>R2に設定される。

【0029】

図4は、図3の電源装置100のシーケンス動作を示すタイミングチャートである。このタイミングチャートは、切替スイッチSW1により切り替わる接点[1]の起動直前と接点[2]の起動後(横軸)に対して、DCバイアス電源111の分圧部111aで出力される電圧(縦軸)の関係について示している。

【0030】

図4に示すタイミングチャートでは、図3に示す電源装置100において、コントローラ104により、起動直前で分圧部111aの切替スイッチSW1は接点[1]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。このとき、フルブリッジ回路103のNchFETのゲート−ソース間に必要な電圧Vgs(本例では約20V)が抵抗R1と抵抗R2の分圧比によって出力される(V3−V2)。これらの抵抗値は、R1>R2とし、DCバイアス電源111の出力電圧(V2)は、Vmin(本来必要なバイアス電位)よりも小さい電位(作像に影響しない程度)になるように設定する。

【0031】

その後、コントローラ104は、起動時には、DCバイアス電源111の出力電圧(V2)はVminを出力し、同時に分圧部111aの切替スイッチSW1を接点[2]の位置に切り替える。起動時、コントローラ104により、DCバイアス電源111の出力は、分圧部111aの切替スイッチSW2は接点[2]の位置に制御され、DCバイアス電源111はVgsx(R3+R2)/R3に出力制御される。フルブリッジ回路103のNchFETのゲート−ソース間には、同様に分圧部111aの抵抗R2と抵抗R3の分圧比によって出力される。

【0032】

図3において、コントローラ104は切替スイッチSW1の切替制御によって、分圧部111aは、DCバイアス電源111の一部電圧を取り出す分圧構成で、その電圧でフルブリッジ回路103を駆動するNchFETのゲート−ソース端子間に供給する。コントローラ104は、高圧出力時にその分圧比を制御する。

【0033】

このように上述した図3の構成では、抵抗分圧方式の分圧部111aの抵抗比を切り替える構成とし、起動時に、コントローラ104が分圧部111aの切替を行う。また、DCバイアス電源111が負荷(フレア現像ローラ102)を考慮する場合、起動時に、コントローラ104が分圧部111aの抵抗分圧比の切替を行うことにより、DCバイアス電源111が負荷にかかるレベルを調整する。これにより、コントローラ104は、起動時に分圧部111aの切替制御を行うことで、パルス電圧出力とDCバイアス出力を同時に出力することが可能になる。

【0034】

(回路構成例2)

つぎに、上述した図3の構成とは異なる電源装置100の構成例について説明する。図5は、実施の形態にかかる電源装置100の構成例2を示す回路図である。この図5の電源装置100は、図3に示した電源装置100の構成に対して分圧部111bが異なり、他の構成のフルブリッジ回路103については図3と同様であるので、ここでの重複説明は省略する。図5に示す分圧部111bは、抵抗R1と抵抗R2の接続を切り替える切替スイッチSW2を有する。DCバイアス電源111の出力側に抵抗R1と抵抗R2が直列に接続され、分圧部111bを構成する切替スイッチSW2により、抵抗R1と抵抗R2が切り替えられる。

【0035】

図6は、図5の電源装置100のシーケンス動作を示すタイミングチャートである。このタイミングチャートは、切替スイッチSW2により切り替わる接点[1]の起動直前と接点[2]の起動後(横軸)に対して、DCバイアス電源111の分圧部111bで出力される電圧(縦軸)の関係について示している。

【0036】

図6に示すタイミングチャートでは、図5に示す電源装置100において、コントローラ104により、起動直前で分圧部111bの切替スイッチSW2は接点[1]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。DCバイアス電源111は、フルブリッジ回路103のNchFETのゲート−ソース間に必要な電圧Vgs(本例では約20V)に出力が制御される。このとき、この電圧がそのままNchFETのゲート−ソース間に出力される(V3−V2)。

【0037】

その後、コントローラ104は、起動時には、DCバイアス電源(V2)はVmin出力と、同時に分圧部111bの切替スイッチSW2を接点[2]の位置に切り替える。起動時、コントローラ104により、DCバイアス電源111の出力は、分圧部111bの切替スイッチSW2は接点[2]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。フルブリッジ回路103のNchFETのゲート−ソース間には、抵抗R1と抵抗R2の分圧比によって出力される。一般的に、これらの抵抗値は、R1>R2に設定される。

【0038】

また、コントローラ104は、DCバイアス電源111についてフローティング状態とするとするかしないかを、起動時に切替制御を行う。この切替制御は、高電位側のゲートーソース間をグランド基準に対してフローティング状態とするかを行うものである。

【0039】

このように、コントローラ104は、分圧部111bの抵抗分圧比を切り替える機能を有する。コントローラ104は、起動時に分圧部111bの切替制御を行い、パルス電圧出力およびDCバイアスを同時に出力することが可能となる。

【0040】

(回路構成例3)

つぎに、上述した図3の構成とは異なる他の電源装置100の構成例について説明する。ここでは、DCバイアス電源111からの分圧構成において、ツェナーダイオードを用いて、DCバイアス電源111の出力電圧に依存しない一定電圧に固定する例について示している。

【0041】

図7は、実施の形態にかかる電源装置100の構成例3を示す回路図である。この図7の電源装置100は、図3に示した電源装置100の構成に対して分圧部111cが異なり、他の構成のフルブリッジ回路103については図3と同様であるので、ここでの重複説明は省略する。図7に示す分圧部111cは、DCバイアス電源111の出力に依存しない一定の電圧を得るためのツェナーダイオードZD1、抵抗R2を有する。

【0042】

図7において、DCバイアス電源111からの出力電圧をツェナーダイオードZD1と抵抗R2で分圧し、ツェナーダイオードZD1間の電圧をNchFETのゲート−ソース間に必要な電圧Vgsを供給する(ツェナー電圧=Vgs電圧)。

【0043】

コントローラ104により、起動直前でDCバイアス電源111は、Vgs以上の電圧を出力しNchFETがスイッチングできる状態にして、起動時のスイッチング動作と同時にDCバイアス電源111は、所定のVmin電圧の出力を行う。これにより、DCバイアス電源111の出力電圧に依存しない一定電圧に固定した出力制御が可能になる。

【0044】

(回路構成例4)

つぎに、上述した図7の構成とは異なる電源装置100について説明する。ここでは、ツェナーダイオードと直列にNTCサーミスタを挿入し、NchFETのVgs電圧をNTCサーミスタが検知する周囲温度によって調整する構成とし、NchFETのゲート−ソース間の電圧Vgsには周囲温度に応じた必要最小限の電圧供給だけを行う例について示している。

【0045】

図8は、実施の形態にかかる電源装置100の構成例4を示す回路図である。この図8の電源装置100は、図7に示した電源装置100の構成に対して分圧部111dが異なり、他の構成のフルブリッジ回路103については図7と同様であるので、ここでの重複説明は省略する。図8に示す分圧部111dは、DCバイアス電源111の出力に依存しない一定の電圧を得るためのツェナーダイオードZD1、周囲温度を検知する温度検知手段としてのNTCサーミスタTH1、抵抗R2を有する。なお、NTCサーミスタは、温度の上昇に対して抵抗が減少するサーミスタであり、NTCはNegative Temperature coefficientの略称である。

【0046】

図8に示すように、本例の電源装置100は、図7の構成に対して、さらにツェナーダイオードZD1と、温度検知素子としてのNTCサーミスタTH1とを直列に挿入した構成とする。DCバイアス電源111からの出力電圧をツェナーダイオードZD1、NTCサーミスタTH1、抵抗R2で分圧し、ツェナーダイオードZD1とNTCサーミスタTH1間の電圧をNchFETのゲート−ソース間に必要な電圧Vgsを供給する(ツェナー電圧+TH1電圧=Vgs電圧)。

【0047】

NTCサーミスタTH1の電圧は、周囲温度によって変動するが(温度高いと、抵抗が低い)、この特性とNchFETのVgs温度特性は対比されたものとして、周囲温度が高い状態ではVgsに供給する電圧を低く、周囲温度が低い状態ではVgsに供給する電圧を高くする。そして前述した制御と同様に、コントローラ104により、起動直前でDCバイアス電源111は、Vgs以上の電圧を出力しNchFETがスイッチングできる状態にして、起動時のスイッチング動作と同時にDCバイアス電源111は、所定のVmin電圧の出力を行う。これにより、電源回路の周囲温度による特性を考慮するとともに、DCバイアス電源111の出力電圧に依存しない一定電圧に固定した出力制御が可能になる。

【0048】

したがって、上述した回路構成例1,2,3,4によれば、DCバイアス電源111からNchFET駆動用の電源を、分圧部111a,111b,111c,111dにより分圧構成にて取り出す構成としたため、従来のようにNchFET駆動用の電源を単独でもつ必要がなくなり、さらにNchFETのスイッチング駆動に必要な最低限のゲート−ソース間電圧の供給を行うことができる。

【0049】

また、上述した回路構成例1,2,3,4の電源装置100は、図1に示すような画像形成部の現像装置11のフレア現像方式の電源に用いることができる。

【0050】

なお、上記実施の形態では、画像形成装置を、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する複合機に適用した例を挙げて説明したが、複写機、プリンタ、ファクシミリ装置等のフレア現像方式を用いる画像形成装置であればいずれにも適用することができる。また、画像形成装置として、フレア現像方式を用いる画像形成装置であれば、モノクロ画像形成装置、フルカラー画像形成装置のいずれにも適用することができる。

【符号の説明】

【0051】

100 電源装置

101 フレア現像用高圧電源回路

102 フレア現像ローラ

103 フルブリッジ回路

104 コントローラ

110 Hサイド電源

111 DCバイアス電源

111a〜111d 分圧部

SW1,SW2 切替スイッチ

R1,R2,R3 抵抗

ZD1 ツェナーダイオード

TH1 NTCサーミスタ

Tr_H1 高電位側トランジスタ

Tr_L1 低電位側トランジスタ

FET_H1,FET_H2 高電位側トランジスタスイッチ

FET_L1,FET_L2 低電位側トランジスタスイッチ

【先行技術文献】

【特許文献】

【0052】

【特許文献1】特開平2−116215号公報

【技術分野】

【0001】

本発明は、電源装置、および電源装置の電圧切替方法に関する。

【背景技術】

【0002】

従来、複写機などの電子写真方式の画像形成装置に用いられる現像方式の一つとして、トナーをクラウド化(ホッピングさせた状態、以下、フレア現像という)させる方式が知られている。このフレア現像方式においては、フレア現像ローラに逆相のパルス電圧を交互に印加して、充放電を繰り返すことで、印刷中はトナーがフレア現像ローラ上でホッピングした状態となり、トナーのクラウド化を実現している。上記パルスを発生させる方式としては、直流バイアスに重畳させて、回路としてはNchFET駆動によるフルブリッジ回路による構成が挙げられる。なお、NchFETは、N型チャネル接合型FET(Field Effect Transistor)の略称であり、以下、適宜、NchFETと記述する。

【0003】

なお、ブートストラップ回路の出力安定化を図るブートストラップ回路として、出力端子に一方の電極が結合されたブートストラップ容量と、所定の定電圧端子との間に双方向に向くように接続された一対の一方向性素子を介してゲートが結合されたクランプ用MOSFETと、クランプ用MOSFETを介してチャージアップされたブートストラップ容量の他端に駆動電圧を供給する駆動回路と、定電圧端子からみて上記クランプ用MOSFETと一対の一方向性素子からなる回路と実質的に等価となる一対の一方向性素子と容量素子からなり、クランプ用MOSFETを通して伝えられる信号と逆相の信号が容量素子に供給されてなるダミー回路とを備えたものが開示されている(たとえば、特許文献1参照)。なお、MOSFETは、Metal Oxide Semiconductor FETの略称である。

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記に示されるような、NchFET駆動によるフルブリッジ回路による構成にあっては、フレア現像用高圧電源として、直流バイアス用、フルブリッジのハイ(H)サイド電源用、NchFET駆動用の3種類が必要となるという問題があった。

【0005】

本発明は、上記に鑑みてなされたものであって、フレア現像用高圧出力として、NchFET駆動によるフルブリッジ回路を構成する場合、NchFET駆動用の電源は、直流バイアス電源から生成し、単独のNchFET駆動用電源を不要とするとともに、NchFETのスイッチング駆動に必要な最低限のゲート−ソース端子間への電圧の供給を可能とすることを目的とする。

【課題を解決するための手段】

【0006】

上述した課題を解決し、目的を達成するために、本発明は、スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備えることを特徴とする。

【発明の効果】

【0007】

本発明は、直流バイアス電源からNchFET駆動用の電源を、分圧構成にて取り出す構成としたため、NchFET駆動用の電源を単独でもつ必要がなくなり、さらにNchFETのゲート−ソース端子間にスイッチング駆動に必要な最低限の電圧の供給を行うことができるという効果を奏する。

【図面の簡単な説明】

【0008】

【図1】図1は、実施の形態にかかる電子写真方式のカラー画像形成装置の画像形成部の一例の説明図である。

【図2】図2は、図1における画像形成部に電力を供給する電源装置の概要構成を示すブロック図である。

【図3】図3は、実施の形態にかかる電源装置の構成例1を示す回路図である。

【図4】図4は、図3の電源装置のシーケンス動作を示すタイミングチャートである。

【図5】図5は、実施の形態にかかる電源装置の構成例2を示す回路図である。

【図6】図6は、図5の電源装置のシーケンス動作を示すタイミングチャートである。

【図7】図7は、実施の形態にかかる電源装置の構成例3を示す回路図である。

【図8】図8は、実施の形態にかかる電源装置の構成例4を示す回路図である。

【発明を実施するための形態】

【0009】

以下に添付図面を参照して、この発明にかかる電源装置、および電源装置の電圧切替方法の一実施の形態を詳細に説明する。

【0010】

<実施の形態>

この実施の形態にかかる画像形成装置は、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する一般に複合機と称されるものであって、原稿を読み取り画像データに変換する画像読取部と、画像読取部で原稿を読み取って得られた画像データに対して画像処理を施す画像処理部と、画像処理された画像データに基づき紙面に画像を形成する画像形成部とを有する。

【0011】

まず、この実施の形態にかかるフレア現像用高圧電源が搭載される画像形成装置について説明する。図1は、電子写真方式のカラー画像形成装置における画像形成部の構成を示す説明図である。

【0012】

画像形成部は、4つの感光体ドラム10Y,10M,10C,10Kと、各感光体ドラム10Y,10M,10C,10K上に形成した潜像を互いに異なる色のトナー像にそれぞれ現像する複数の現像装置11Y,11M,11C,11Kと、異なる色のトナー像がそれぞれ重ね合わせ状態に一次転写される矢印A方向に回転する像担持体としての中間転写ベルト16とを備えている。

【0013】

中間転写ベルト16は、無端状のベルトである。本実施の形態では、中間転写ベルト16の上方に、中間転写ベルト16の回動方向Aに沿って、ブラック,シアン,マゼンタ,イエローの各色用の4個の上述した感光体ドラム10Y,10M,10C,10K(以下、それぞれを区別する必要が無い場合には、単に感光体ドラム10と記載する)を並列にそれぞれ配置している。感光体ドラム10の周囲には、帯電装置12と、前述した現像装置11と、一次転写装置を構成する一次転写ローラ14と、クリーニング装置13がそれぞれ配設されている。

【0014】

感光体ドラム10は、回転方向Bに回転駆動され、このとき帯電装置12によって感光体ドラム10の表面が所定の極性に帯電される。次いで、その帯電面に、露光装置15から画像データに応じて出射されるレーザ光が照射され、これによって感光体ドラム10に静電潜像が形成され、その静電潜像が現像装置11によって各色のトナー像として可視像化される。

【0015】

各感光体ドラム10には、一次転写ローラ14がそれぞれ対向配置されていて、その各一次転写ローラ14と感光体ドラム10との間には中間転写ベルト16が挟まれた状態で回動するようになっている。

【0016】

このとき、中間転写ベルト16は、駆動ローラ17とテンションローラ19の2個のローラによって支持されている。中間転写ベルト16を3個以上のローラによって張架しても良いが、できる限り小型化し、高さを抑制するため、本実施の形態では中間転写ベルト16を2個のローラによって張架することで、高さを抑制している。

【0017】

つぎに、その中間転写ベルト16の表面に、各感光体ドラム10に可視像化されたトナー像が、一次転写ローラ14の作用によって転写される。このようにして、ブラック(K),シアン(C),マゼンタ(M),イエロー(Y)のトナー像が、中間転写ベルト16に正確に順次重ね合わせた状態で転写されていき、フルカラーの合成カラー画像のトナー像が形成される。

【0018】

一方、中間転写ベルト16を挟んで、駆動ローラ17(二次転写対向ローラ)に対向して二次転写ローラ18が配設され、給紙ユニット21から記録媒体である転写紙Pが給紙される。これによりレジストローラ対22の回転によって、転写紙Pが所定のタイミングで、駆動ローラ17と二次転写ローラ18の間に送り込まれる。すると、中間転写ベルト16に担持されている合成カラー画像が二次転写ローラ18の作用により転写紙Pに一括して転写される。

【0019】

そして、その転写紙P上のトナー像が、定着装置23により熱と圧力によって定着され、図示しない排紙トレイ上に排出される。トナー像が二次転写された後の中間転写ベルト16の表面に付着している転写残トナーは、クリーニング装置20によって除去および回収される。

【0020】

なお、図1では、二次転写ローラ18を介して転写紙に転写する方式の例を示したが転写紙に直接転写する方式の画像形成装置を用いてもよい。

【0021】

上述した図1の画像形成部における現像装置11Y,11M,11C,11Kは、高容量のフレア現像ローラ102を有している。フレア現像方式は、先に述べたように、フレア現像ローラ102に逆相のパルス電圧を交互に印加して、充放電を繰り返すことで、印刷中はトナーがフレア現像ローラ102上でホッピングした状態となり、トナーのクラウド化を実現している。このパルスを発生させる方式としては、高圧電源の回路としてはNchFET駆動によるフルブリッジ回路による構成によってDCバイアスに重畳させることで実現される。本実施の形態では、この高容量のフレア現像ローラ102に後述するフレア現像用高圧電源回路により交流電圧を印加することで、トナーをホッピングさせた状態で現像するフレア現像を行っている。なお、上記DCは直流を示し、以下、DCと記載する。

【0022】

図2は、この実施の形態にかかる画像形成部に電力を供給する電源装置の概要構成を示すブロック図である。電源装置100は、フレア現像用の高圧電源を生成するフレア現像用高圧電源回路101と、フレア現像用高圧電源回路101からの電力供給を受けて容量性負荷Vfとして機能するフレア現像ローラ102に交流電圧を印加するフルブリッジ回路103と、フレア現像用高圧電源回路101およびフルブリッジ回路103を制御するコントローラ104と、を備えている。

【0023】

つぎに、上記の電源装置100の回路構成例1,2,3,4の詳細な構成について説明する。なお、以下に示すFETは、Field Effect Transistor:電界効果トランジスタの略称であり、以下、適宜、FETと記述し、また、NchはN型チャネルの略称である。

【0024】

(回路構成例1)

図3は、実施の形態にかかる電源装置100の回路構成例1を示す回路図である。この図3において、符号100はハイ(H)サイド電源、符号111はDCバイアス電源、符号111aは分圧部、符号R1,R2,R3は抵抗、符号SW1は図の接点[1],[2]側に切り替える切替スイッチ、符号D1はダイオード、符号C1,C2はコンデンサ、符号Tr_H1は高電位側トランジスタ、符号Tr_L1は低電位側トランジスタ、符号FET_H1は高電位側トランジスタスイッチ、符号FET_L1は低電位側トランジスタスイッチ、符号FET_H2は高電位側トランジスタスイッチ、符号FET_L2は低電位側トランジスタスイッチである。

【0025】

フルブリッジ回路103は、NchFET駆動による、高電位側トランジスタスイッチFET_H1、FET_H2および低電位側トランジスタスイッチFET_L1、FET_L2を備えている。ここで、高電位側トランジスタスイッチFET_H1と、低電位側トランジスタスイッチFET_L2と、は対となって動作しており、それぞれのゲート端子に制御信号が入力されることによりコントローラ104により同時にオン(閉状態)/オフ(開状態)される。

【0026】

また、同様に高電位側トランジスタスイッチFET_H2と、低電位側トランジスタスイッチFET_L1と、は対となって動作しており、それぞれのゲート端子に制御信号が入力されることでコントローラ104により同時にオン(閉状態)/オフ(開状態)される。

【0027】

したがって、容量性負荷としてのフレア現像ローラ102には、パルス電圧が印加されることとなる。また、切替スイッチSW1についても、コントローラ104からそれぞれ切替制御信号が入力され、コントローラ104の制御下で、オン/オフ(閉/開)制御がなされる。

【0028】

図3において、DCバイアス電源111の出力側に抵抗R1と抵抗R3が並列に接続され、分圧部111aを構成する切替スイッチSW1により、抵抗R1と抵抗R3が切り替えられる。コントローラ104により、起動前には抵抗R1が接続された接点[1]側、起動時には抵抗R3が接続された接点[2]側に接続の切り替えを行う。一般的に、これらの抵抗値は、R3>R2に設定される。

【0029】

図4は、図3の電源装置100のシーケンス動作を示すタイミングチャートである。このタイミングチャートは、切替スイッチSW1により切り替わる接点[1]の起動直前と接点[2]の起動後(横軸)に対して、DCバイアス電源111の分圧部111aで出力される電圧(縦軸)の関係について示している。

【0030】

図4に示すタイミングチャートでは、図3に示す電源装置100において、コントローラ104により、起動直前で分圧部111aの切替スイッチSW1は接点[1]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。このとき、フルブリッジ回路103のNchFETのゲート−ソース間に必要な電圧Vgs(本例では約20V)が抵抗R1と抵抗R2の分圧比によって出力される(V3−V2)。これらの抵抗値は、R1>R2とし、DCバイアス電源111の出力電圧(V2)は、Vmin(本来必要なバイアス電位)よりも小さい電位(作像に影響しない程度)になるように設定する。

【0031】

その後、コントローラ104は、起動時には、DCバイアス電源111の出力電圧(V2)はVminを出力し、同時に分圧部111aの切替スイッチSW1を接点[2]の位置に切り替える。起動時、コントローラ104により、DCバイアス電源111の出力は、分圧部111aの切替スイッチSW2は接点[2]の位置に制御され、DCバイアス電源111はVgsx(R3+R2)/R3に出力制御される。フルブリッジ回路103のNchFETのゲート−ソース間には、同様に分圧部111aの抵抗R2と抵抗R3の分圧比によって出力される。

【0032】

図3において、コントローラ104は切替スイッチSW1の切替制御によって、分圧部111aは、DCバイアス電源111の一部電圧を取り出す分圧構成で、その電圧でフルブリッジ回路103を駆動するNchFETのゲート−ソース端子間に供給する。コントローラ104は、高圧出力時にその分圧比を制御する。

【0033】

このように上述した図3の構成では、抵抗分圧方式の分圧部111aの抵抗比を切り替える構成とし、起動時に、コントローラ104が分圧部111aの切替を行う。また、DCバイアス電源111が負荷(フレア現像ローラ102)を考慮する場合、起動時に、コントローラ104が分圧部111aの抵抗分圧比の切替を行うことにより、DCバイアス電源111が負荷にかかるレベルを調整する。これにより、コントローラ104は、起動時に分圧部111aの切替制御を行うことで、パルス電圧出力とDCバイアス出力を同時に出力することが可能になる。

【0034】

(回路構成例2)

つぎに、上述した図3の構成とは異なる電源装置100の構成例について説明する。図5は、実施の形態にかかる電源装置100の構成例2を示す回路図である。この図5の電源装置100は、図3に示した電源装置100の構成に対して分圧部111bが異なり、他の構成のフルブリッジ回路103については図3と同様であるので、ここでの重複説明は省略する。図5に示す分圧部111bは、抵抗R1と抵抗R2の接続を切り替える切替スイッチSW2を有する。DCバイアス電源111の出力側に抵抗R1と抵抗R2が直列に接続され、分圧部111bを構成する切替スイッチSW2により、抵抗R1と抵抗R2が切り替えられる。

【0035】

図6は、図5の電源装置100のシーケンス動作を示すタイミングチャートである。このタイミングチャートは、切替スイッチSW2により切り替わる接点[1]の起動直前と接点[2]の起動後(横軸)に対して、DCバイアス電源111の分圧部111bで出力される電圧(縦軸)の関係について示している。

【0036】

図6に示すタイミングチャートでは、図5に示す電源装置100において、コントローラ104により、起動直前で分圧部111bの切替スイッチSW2は接点[1]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。DCバイアス電源111は、フルブリッジ回路103のNchFETのゲート−ソース間に必要な電圧Vgs(本例では約20V)に出力が制御される。このとき、この電圧がそのままNchFETのゲート−ソース間に出力される(V3−V2)。

【0037】

その後、コントローラ104は、起動時には、DCバイアス電源(V2)はVmin出力と、同時に分圧部111bの切替スイッチSW2を接点[2]の位置に切り替える。起動時、コントローラ104により、DCバイアス電源111の出力は、分圧部111bの切替スイッチSW2は接点[2]の位置に制御され、DCバイアス電源111はVgsx(R1+R2)/R1に出力制御される。フルブリッジ回路103のNchFETのゲート−ソース間には、抵抗R1と抵抗R2の分圧比によって出力される。一般的に、これらの抵抗値は、R1>R2に設定される。

【0038】

また、コントローラ104は、DCバイアス電源111についてフローティング状態とするとするかしないかを、起動時に切替制御を行う。この切替制御は、高電位側のゲートーソース間をグランド基準に対してフローティング状態とするかを行うものである。

【0039】

このように、コントローラ104は、分圧部111bの抵抗分圧比を切り替える機能を有する。コントローラ104は、起動時に分圧部111bの切替制御を行い、パルス電圧出力およびDCバイアスを同時に出力することが可能となる。

【0040】

(回路構成例3)

つぎに、上述した図3の構成とは異なる他の電源装置100の構成例について説明する。ここでは、DCバイアス電源111からの分圧構成において、ツェナーダイオードを用いて、DCバイアス電源111の出力電圧に依存しない一定電圧に固定する例について示している。

【0041】

図7は、実施の形態にかかる電源装置100の構成例3を示す回路図である。この図7の電源装置100は、図3に示した電源装置100の構成に対して分圧部111cが異なり、他の構成のフルブリッジ回路103については図3と同様であるので、ここでの重複説明は省略する。図7に示す分圧部111cは、DCバイアス電源111の出力に依存しない一定の電圧を得るためのツェナーダイオードZD1、抵抗R2を有する。

【0042】

図7において、DCバイアス電源111からの出力電圧をツェナーダイオードZD1と抵抗R2で分圧し、ツェナーダイオードZD1間の電圧をNchFETのゲート−ソース間に必要な電圧Vgsを供給する(ツェナー電圧=Vgs電圧)。

【0043】

コントローラ104により、起動直前でDCバイアス電源111は、Vgs以上の電圧を出力しNchFETがスイッチングできる状態にして、起動時のスイッチング動作と同時にDCバイアス電源111は、所定のVmin電圧の出力を行う。これにより、DCバイアス電源111の出力電圧に依存しない一定電圧に固定した出力制御が可能になる。

【0044】

(回路構成例4)

つぎに、上述した図7の構成とは異なる電源装置100について説明する。ここでは、ツェナーダイオードと直列にNTCサーミスタを挿入し、NchFETのVgs電圧をNTCサーミスタが検知する周囲温度によって調整する構成とし、NchFETのゲート−ソース間の電圧Vgsには周囲温度に応じた必要最小限の電圧供給だけを行う例について示している。

【0045】

図8は、実施の形態にかかる電源装置100の構成例4を示す回路図である。この図8の電源装置100は、図7に示した電源装置100の構成に対して分圧部111dが異なり、他の構成のフルブリッジ回路103については図7と同様であるので、ここでの重複説明は省略する。図8に示す分圧部111dは、DCバイアス電源111の出力に依存しない一定の電圧を得るためのツェナーダイオードZD1、周囲温度を検知する温度検知手段としてのNTCサーミスタTH1、抵抗R2を有する。なお、NTCサーミスタは、温度の上昇に対して抵抗が減少するサーミスタであり、NTCはNegative Temperature coefficientの略称である。

【0046】

図8に示すように、本例の電源装置100は、図7の構成に対して、さらにツェナーダイオードZD1と、温度検知素子としてのNTCサーミスタTH1とを直列に挿入した構成とする。DCバイアス電源111からの出力電圧をツェナーダイオードZD1、NTCサーミスタTH1、抵抗R2で分圧し、ツェナーダイオードZD1とNTCサーミスタTH1間の電圧をNchFETのゲート−ソース間に必要な電圧Vgsを供給する(ツェナー電圧+TH1電圧=Vgs電圧)。

【0047】

NTCサーミスタTH1の電圧は、周囲温度によって変動するが(温度高いと、抵抗が低い)、この特性とNchFETのVgs温度特性は対比されたものとして、周囲温度が高い状態ではVgsに供給する電圧を低く、周囲温度が低い状態ではVgsに供給する電圧を高くする。そして前述した制御と同様に、コントローラ104により、起動直前でDCバイアス電源111は、Vgs以上の電圧を出力しNchFETがスイッチングできる状態にして、起動時のスイッチング動作と同時にDCバイアス電源111は、所定のVmin電圧の出力を行う。これにより、電源回路の周囲温度による特性を考慮するとともに、DCバイアス電源111の出力電圧に依存しない一定電圧に固定した出力制御が可能になる。

【0048】

したがって、上述した回路構成例1,2,3,4によれば、DCバイアス電源111からNchFET駆動用の電源を、分圧部111a,111b,111c,111dにより分圧構成にて取り出す構成としたため、従来のようにNchFET駆動用の電源を単独でもつ必要がなくなり、さらにNchFETのスイッチング駆動に必要な最低限のゲート−ソース間電圧の供給を行うことができる。

【0049】

また、上述した回路構成例1,2,3,4の電源装置100は、図1に示すような画像形成部の現像装置11のフレア現像方式の電源に用いることができる。

【0050】

なお、上記実施の形態では、画像形成装置を、コピー機能、プリンタ機能、スキャナ機能およびファクシミリ機能のうち少なくとも2つの機能を有する複合機に適用した例を挙げて説明したが、複写機、プリンタ、ファクシミリ装置等のフレア現像方式を用いる画像形成装置であればいずれにも適用することができる。また、画像形成装置として、フレア現像方式を用いる画像形成装置であれば、モノクロ画像形成装置、フルカラー画像形成装置のいずれにも適用することができる。

【符号の説明】

【0051】

100 電源装置

101 フレア現像用高圧電源回路

102 フレア現像ローラ

103 フルブリッジ回路

104 コントローラ

110 Hサイド電源

111 DCバイアス電源

111a〜111d 分圧部

SW1,SW2 切替スイッチ

R1,R2,R3 抵抗

ZD1 ツェナーダイオード

TH1 NTCサーミスタ

Tr_H1 高電位側トランジスタ

Tr_L1 低電位側トランジスタ

FET_H1,FET_H2 高電位側トランジスタスイッチ

FET_L1,FET_L2 低電位側トランジスタスイッチ

【先行技術文献】

【特許文献】

【0052】

【特許文献1】特開平2−116215号公報

【特許請求の範囲】

【請求項1】

スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、

直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備えることを特徴とする電源装置。

【請求項2】

さらに電圧切替制御手段を有し、

前記電圧出力手段は、抵抗分圧回路を有し、前記抵抗分圧回路の抵抗を切り替えるものであって、

前記電圧切替制御手段は、起動時に前記電圧出力手段の前記抵抗分圧回路の抵抗を切り替えて前記スイッチング素子に出力することを特徴とする請求項1に記載の電源装置。

【請求項3】

さらに電圧切替制御手段を有し、

前記電圧出力手段は、抵抗分圧回路を有し、前記抵抗分圧回路の抵抗分圧比を切り替えるものであって、

前記電圧切替制御手段は、起動時に前記電圧出力手段の抵抗分圧比を切り替えて前記スイッチング素子に出力することを特徴とする請求項1に記載の電源装置。

【請求項4】

前記電圧切替制御手段は、前記直流バイアス電源の前記電圧出力手段に対してフローティング状態とするかの可否を切り替えることを特徴とする請求項1に記載の電源装置。

【請求項5】

前記電圧出力手段は、前記直流バイアス電源の出力電圧を定電圧に固定する定電圧手段を有することを特徴とする請求項1に記載の電源装置。

【請求項6】

前記電圧出力手段は、さらに回路の周囲温度を検知する温度検知手段を有することを特徴とする請求項4に記載の電源装置。

【請求項7】

スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置の電圧切替方法であって、

前記電源装置は、直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備え、

起動時に前記電圧出力手段の電圧出力を切り替えて前記スイッチング素子に出力する電圧切替制御工程を含むことを特徴とする電源装置の電圧切替方法。

【請求項1】

スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置であって、

直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備えることを特徴とする電源装置。

【請求項2】

さらに電圧切替制御手段を有し、

前記電圧出力手段は、抵抗分圧回路を有し、前記抵抗分圧回路の抵抗を切り替えるものであって、

前記電圧切替制御手段は、起動時に前記電圧出力手段の前記抵抗分圧回路の抵抗を切り替えて前記スイッチング素子に出力することを特徴とする請求項1に記載の電源装置。

【請求項3】

さらに電圧切替制御手段を有し、

前記電圧出力手段は、抵抗分圧回路を有し、前記抵抗分圧回路の抵抗分圧比を切り替えるものであって、

前記電圧切替制御手段は、起動時に前記電圧出力手段の抵抗分圧比を切り替えて前記スイッチング素子に出力することを特徴とする請求項1に記載の電源装置。

【請求項4】

前記電圧切替制御手段は、前記直流バイアス電源の前記電圧出力手段に対してフローティング状態とするかの可否を切り替えることを特徴とする請求項1に記載の電源装置。

【請求項5】

前記電圧出力手段は、前記直流バイアス電源の出力電圧を定電圧に固定する定電圧手段を有することを特徴とする請求項1に記載の電源装置。

【請求項6】

前記電圧出力手段は、さらに回路の周囲温度を検知する温度検知手段を有することを特徴とする請求項4に記載の電源装置。

【請求項7】

スイッチング素子によりパルス電圧をトナーに印加し、前記トナーを浮遊させて現像を行うフレア現像方式の画像形成装置に用いられる電源装置の電圧切替方法であって、

前記電源装置は、直流バイアス電源の出力電圧を分圧して、前記スイッチング素子のゲート端子―ソース端子に所定の電圧を出力する電圧出力手段を備え、

起動時に前記電圧出力手段の電圧出力を切り替えて前記スイッチング素子に出力する電圧切替制御工程を含むことを特徴とする電源装置の電圧切替方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−66277(P2013−66277A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−202676(P2011−202676)

【出願日】平成23年9月16日(2011.9.16)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月16日(2011.9.16)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]