電源装置、及びこれを用いた画像形成装置

【課題】短時間で目標電圧に近い高い電圧を出力する。

【解決手段】高圧電源装置301は、駆動周波数に対応して出力電圧が変化する圧電トランス304と、出力電圧と目標電圧とが一致するように、駆動周波数を帰還制御する出力電圧変換手段307および第一電圧比較手段308と、出力電圧と目標電圧との差分値が小さいとき、駆動周波数の変化量を小さくし、一方、差分値が大きいとき、駆動周波数の変化量を大きく設定する高圧制御部206とを備える。

【解決手段】高圧電源装置301は、駆動周波数に対応して出力電圧が変化する圧電トランス304と、出力電圧と目標電圧とが一致するように、駆動周波数を帰還制御する出力電圧変換手段307および第一電圧比較手段308と、出力電圧と目標電圧との差分値が小さいとき、駆動周波数の変化量を小さくし、一方、差分値が大きいとき、駆動周波数の変化量を大きく設定する高圧制御部206とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、圧電トランスを用いて昇圧する電源装置、及びこれを用いた画像形成装置に関する。

【背景技術】

【0002】

電子写真方式の画像形成装置は、高圧電源装置を内蔵しており、この高圧電源装置が、帯電ローラを介して感光体ドラムを帯電し、現像ローラ、供給ローラや転写ローラに所定のバイアス電圧を印加してトナーを感光体ドラムに移動させたり、媒体にトナー画像を転写させたりしている。

【0003】

また、高圧電源装置として、圧電トランスを用いて、出力電圧が目標電圧になるように定電圧制御する技術が開示されている(特許文献1参照)。圧電トランスは、駆動周波数を可変することで容易に出力電圧を可変することができるものである。圧電トランスは、駆動周波数に応じて出力電圧が変化するものであり、この駆動電圧を電圧制御発振器(VCO)で発生させていた。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−91757号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、一般に圧電トランスは、共振周波数において出力電圧が最大となるような“裾広がり”な特性をしており、圧電トランスの出力電圧を増加させる場合は、この圧電トランスの駆動周波数を高い方から低い方へ変化させることで可能となる。

しかしながら、一般的な電圧制御発振器などを用いた回路では、目標電圧に近い高い出力電圧を利用しようとした場合に、圧電トランスによる共振周波数のバラツキの影響で、共振周波数を超えて低い周波数で制御してしまう場合があった。

また、目標電圧に近い、高い出力電圧に設定した後で、改めて、圧電トランスの出力電圧を制御して、目標電圧に近づけるという2段階の電圧制御を行っていたため、短時間で目標電圧に定電圧制御することが困難であるという問題があった。

【0006】

そこで、本発明は、短時間で目標電圧に近い高い電圧を出力することができる電源装置、及びこれを用いた画像形成装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

前記目的を達成するため、本発明の電源装置は、駆動周波数に対応して出力電圧が変化する圧電トランス(304)を用いた電源装置(高圧電源装置301)であって、前記出力電圧と目標電圧とが一致するように、前記駆動周波数を帰還制御する帰還制御回路(307,308)と、前記出力電圧と前記目標電圧との差分値が小さいとき、前記駆動周波数の変化量を小さくし、前記差分値が大きいとき、前記駆動周波数の変化量を大きく設定する駆動周波数設定手段(206)と、を備えることを特徴とする。なお、( )内の符号や記号は例示である。

【0008】

これによれば、出力電圧と目標電圧との差分値が大きいとき、駆動周波数が大きく変化するので、早く、出力電圧が目標電圧に近づく。そして、出力電圧と目標電圧との差分値が小さくなったとき、駆動周波数が小さく変化するので、出力電圧が目標電圧を飛び超える可能性が少なくなる。

また、目標電圧に近い高い電圧を出力した際の駆動周波数を記憶し、次回、その駆動周波数を用いることで、いち早く目標電圧に近づける電圧制御を行うことができる。

【0009】

また、振幅が前記目標電圧の2倍の三角波信号を生成する三角波生成回路と、前記三角波信号の中間値と前記出力電圧の分圧値とを比較してパルス幅を計測することにより、前記差分値と方向とを推測することができる。推測した推測差分値と変化量との関係が規定されている変化量設定テーブル(テーブルレジスタ510)とを用いて、推測差分値から駆動周波数の変化量を演算することができる。また、圧電トランスの駆動周波数−電圧特性(非線形特性)を規定する特性テーブル(テーブルレジスタ511)を用いて、駆動周波数または出力電圧の分圧値から駆動周波数の変化量を補正することができる。

【発明の効果】

【0010】

本発明によれば、短時間で目標電圧に近い高い電圧を出力することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施形態の画像形成装置の全体構成図である。

【図2】本発明の第1の実施形態の画像形成装置を制御する制御回路及びその周辺部品の構成図である。

【図3】本発明の第1の実施形態の高圧電源装置のブロック図である。

【図4】本発明の第1の実施形態の高圧電源装置を中心として詳細に説明する回路図である。

【図5】圧電トランス304の二次側の出力特性を示す模式図である。

【図6】第1チャネル〜第4チャネルの出力端子から出力される信号の波形と、抵抗器に入力される電圧値の変化と、三角波発生手段から出力される波形とを示す図である。

【図7】本発明の第1の実施形態の高圧制御部のブロック図である。

【図8】テーブルレジスタ510が備えるテーブルの一例である。

【図9】テーブルレジスタ511が備えるテーブルの一例である。

【図10】テーブルレジスタ552が備えるテーブルの一例である。

【図11】出力端子(OUT1)の出力波形と、圧電トランス駆動回路の出力波形と、出力電圧変換手段の出力波形と、三角波発生回路の出力波形と、DACの出力波形と、第一電圧比較手段の出力波形と、第二電圧比較手段の出力波形とを示す図である。

【図12】出力電圧の駆動周波数依存性を示す図である。

【図13】無負荷時の出力電圧と駆動周波数との関係を示す図である。

【図14】150MΩ負荷時の出力電圧と駆動周波数との関係を示す図である。

【図15】駆動周波数108.46Hzの立ち上がり特性を示す図である。

【図16】駆動周波数111.61Hzの立ち上がり特性を示す図である。

【図17】演算指示部が出力する演算指示信号と、プリンタエンジン制御部が出力するON信号と、3ビットカウンタ部の3ビット値とを示す図である。

【図18】本発明の第2の実施形態の高圧電源装置のブロック図である。

【図19】本発明の第2の実施形態の高圧電源装置を中心として詳細に説明する回路図である。

【図20】本発明の第2の実施形態の高圧制御部のブロック図である。

【図21】本発明の第2の実施形態の高圧電源装置の出力電圧と分周比値との特性を示すテーブルである。(A)無負荷時特性、(B)ショート時(100MΩ負荷)特性を示す。

【図22】本発明の第2の実施形態における、DACの設定と、ON信号と、Hold信号と、Pre信号と、高圧出力とのタイミングチャートを示す。

【図23】本発明の第3の実施形態である画像形成装置の全体構成図である。

【図24】本発明の第3の実施形態の高圧電源装置のブロック図である。

【図25】本発明の第3の実施形態の高圧制御部のブロック図である。

【図26】本発明の第3の実施形態における、DACの設定と、ON信号と、Hold信号と、Pre信号と、高圧出力とのタイミングチャートを示す。

【発明を実施するための形態】

【0012】

以下、図面を参照して、本発明の実施の形態(以下、「本実施形態」と称する)につき詳細に説明する。なお、各図は、本発明について概略的に示してあるに過ぎない。よって、本発明は、図示例のみに限定されるものではない。また、各図において、共通する構成要素や同様な構成要素については、同一の符号を付し、それらの重複する説明を省略する。

【0013】

《第1の実施形態》

(構成の説明)

図1は、本発明の第1の実施形態である画像形成装置の全体構成図である。図1において、画像形成装置101(101A)は、電子写真方式を用いたタンデムカラー印刷装置であり、4色の現像器102(102K、102Y、102M、102C)と、4つの露光手段としてのLEDヘッド103(103K、103Y、103M、103C)と、転写ローラ111(111K、111Y、111M、111C)と、定着器123と、給紙部としての用紙カセット117と、転写ベルト114を含む搬送部と、スタッカ(排紙トレー)129と、転写ベルトクリーニングブレード115と、転写ベルトクリーナ容器116とを備える。

なお、トナーカートリッジ104(104K、104Y、104M、104C)は、現像器102(102K、102Y、102M、102C)にそれぞれ着脱可能で、内部のトナーを現像器内部に供給可能な構造となっている。

【0014】

現像器102(102K、102Y、102M、102C)は、内部に、像担持体としての感光体ドラム109(109K、109Y、109M、109C)と、帯電手段としての帯電ローラ105(105K、105Y、105M、105C)と、現像剤担持体としての現像ローラ107(107K、107Y、107M、107C)と、現像剤供給手段としての供給ローラ106(106K、106Y、106M、106C)と、薄層形成手段としての現像ブレード108(108K、108Y、108M、108C)と、クリーニングブレード110(110K、110Y、110M、110C)とを備える。なお、図面上は、感光体ドラム109K、帯電ローラ105K、現像ローラ107K、現像ブレード108K、クリーニングブレード110Kのみ示している。また、各ローラは、軸が用紙の搬送方向に垂直であって、搬送面に平行となる方向に配設されている。

【0015】

感光体ドラム109は、帯電ローラ105によって、一様に負極に帯電される。帯電された感光体ドラム109は、LEDヘッド103の発光・照射によって、照射部が放電され、静電潜像が形成される。例えば、感光体ドラム109は、−600Vの帯電電位から−40Vに放電される。

【0016】

一方、供給ローラ106は、負のバイアス電圧(例えば、−300V)が印加されており、トナーカートリッジ104内部の現像剤としてのトナーを帯電させ、帯電したトナーを現像ローラ107に供給する。現像ブレード108は、現像ローラ107に供給されたトナーを薄層化し、現像ローラ107の表面に一様なトナー層を形成する。現像ローラ107は、負のバイアス電圧(例えば、−200V)が印加されており、電界の作用により、負に帯電されたトナーを静電潜像に移動させる。感光体ドラム109は、現像ローラ107からトナーが移動することにより、静電潜像がトナー像(現像剤像)として現像される。クリーニングブレード110は、転写後の残トナーをクリーニングする機構である。

【0017】

転写ローラ111(111K、111Y、111M、111C)は、転写ベルト114裏面から転写位置にバイアス電圧が印加可能に配置される。転写ベルト駆動ローラ112、転写ベルト従動ローラ113は、転写ベルト114を張架し、ローラの駆動によって用紙を搬送可能となっている。また、転写ローラ111は、正のバイアス電圧(例えば、+2500V)が印加されており、感光体ドラム109の表面に形成され、負に帯電されたトナー画像を媒体に転写する。

【0018】

転写ベルトクリーニングブレード115は、転写ベルト114上のトナーを掻き落とせるようになっていて、転写ベルトクリーナ容器116には、転写ベルトクリーニングブレード115により掻き落とされたトナーが収容される。

【0019】

用紙カセット117は、画像形成装置101に着脱可能に取り付けられ用紙が積載される。給紙ローラ118は、転写媒体である用紙を用紙カセット117から給紙し、用紙ガイド119に沿って搬送する。レジストローラ120、121は、停止状態のところに用紙を突き当て、スキュー補正後に所定タイミングでレジストローラ120、121を駆動し、転写ベルト114に用紙を搬送する。用紙検出センサ122は、接触又は非接触で用紙の通過を検知する。

【0020】

定着器123は、加熱部材124、及び圧着部材125を備え、加熱部材124は、サーミスタ216及び定着器ヒータ217(図2)を備え、用紙上に転写されたトナー像を熱と加圧によって用紙に定着する。なお、加熱部材124、及び圧着部材125は、互いに圧接させられ、ニップ部が形成されている。画像形成装置101は、排出ローラ126、127によって用紙ガイド128に沿って用紙を搬送し、排紙トレー129にフェースダウンで排出する。

【0021】

図2は、本発明の第1の実施形態である画像形成装置を制御する制御回路、及びその周辺部品の構成図である。図2において、画像形成装置101は、前記したLEDヘッド103(103K、103Y、103M、103C)と、現像器102(102K、102Y、102M、102C)と、転写ローラ111(111K、111Y、111M、111C)と、定着器123とを備え、さらにホストインタフェース部201と、給紙モータ210と、搬送モータ211と、転写ベルト駆動モータ212と、定着器駆動モータ213と、感光体ドラム駆動モータ214と、記憶部215と、用紙検出センサ122と、これらを全体制御する制御回路200とを備える。

【0022】

制御回路200は、ホストインタフェース部201から入力される印刷データをコマンド/画像データに変換処理するコマンド/画像処理部202と、各モータ(210,211,212,213,214)を駆動するモータ制御部205と、LEDヘッド103(103K、103Y、103M、103C)を駆動するLEDヘッドインタフェース部203と、帯電ローラ105(105K,105Y,105M,105C)にバイアス電圧を印加する帯電バイアス発生部207と、供給ローラ106(106K,106Y,106M、106C)、及び現像ローラ107(107K,107Y,107M、107C)にバイアス電圧を印加する現像/供給バイアス発生部208と、転写ローラ111(111K、111Y、111M、111C)にバイアス電圧を印加する転写バイアス発生部209と、帯電バイアス発生部207、現像/供給バイアス発生部208、及び転写バイアス発生部209を制御する駆動周波数設定手段としての高圧制御部206と、コマンド/画像処理部202、モータ制御部205、LEDヘッドインタフェース部203、及び高圧制御部206を制御するプリンタエンジン制御部204とを備える。

【0023】

ホストインタフェース部201は、外部機器(ホスト)から送信される印刷データ(例えば、コマンドデータ、文書データ、画像データ)を受信し、印刷データをコマンド/画像処理部202に送信する。コマンド/画像処理部202は、ホストインタフェース部201から印刷データを受信し、ページ記述言語で記述された印刷データを画像データ(ビットマップデータ)に変換し、LEDヘッドインタフェース部203に画像データを送る。

【0024】

LEDヘッドインタフェース部203は、プリンタエンジン制御部204によってヘッド駆動パルス等が同期制御され、コマンド/画像処理部202が出力する画像データを用いてLEDヘッド103K、103Y、103M、103Cを発光させる。

【0025】

プリンタエンジン制御部204は、コマンド/画像処理部202から入力された印刷データや画像データを記憶部215に一時的に格納する。また、プリンタエンジン制御部204は、各モータ(210,211,212,213,214)を制御するモータ制御値を演算すると共に、帯電ローラ105K、105Y、105M、105C、供給ローラ106K、106Y、106M、106C、現像ローラ107K、107Y、107M、107C、転写ローラ111K、111Y、111M、111Cに印加する、それぞれのバイアス電圧を演算する。

【0026】

プリンタエンジン制御部204は、高圧制御部206に帯電バイアス、現像バイアス、転写バイアス等のバイアス電圧値データを送り、高圧制御部206は帯電バイアス発生部207、現像/供給バイアス発生部208、転写バイアス発生部209に制御信号を送る。

そして、帯電バイアス発生部207、現像/供給バイアス発生部208は、それぞれブラック現像器102K、イエロー現像器102Y、マゼンタ現像器102M、シアン現像器102Cの帯電ローラ105K、105Y、105M、105C、供給ローラ106K、106Y、106M、106C、現像ローラ107K、107Y、107M、107Cにバイアス電圧を印加する。また、転写バイアス発生部209は、転写ローラ111K、111Y、111M、111Cにバイアス電圧を印加する。

【0027】

用紙検出センサ122は、転写バイアスの発生タイミング、及びLEDヘッド103K、103Y、103M、103Cの点灯タイミングを調整するために用いられる。プリンタエンジン制御部204は、給紙モータ210、搬送モータ211、転写ベルト駆動モータ212、定着器駆動モータ213、感光体ドラム駆動モータ(K、Y、M、C各1個ずつ配置)214を所定のタイミングで駆動する。定着器123は、プリンタエンジン制御部204によって、定着器ヒータ217の温度制御がサーミスタ216の検出値に応じて行われる。

【0028】

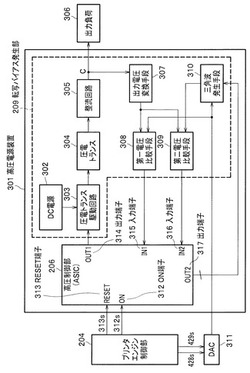

図3は、第1の実施形態の高圧電源装置のブロック図である。

図3において、高圧電源装置301は、高圧制御部206と転写バイアス発生部209とを有し、プリンタエンジン制御部204、デジタルアナログコンバータ(DAC(Digital Analog Converter))311、及び出力負荷306が接続されている。

高圧制御部206は、圧電トランス駆動信号を出力するためのASIC(Application Specific Integrated Circuit)として構成されている。なお、高圧制御部206は、高圧電源装置内にあるが、プリンタエンジン制御部204のLSI内にあっても構わない。また、本実施形態においては、ASICという呼称を用いているが、マイクロプロセッサ等のCPUを内蔵したものでも実現可能であるし、FPGA(Field Programmable Gate Array)でも実現可能である。

【0029】

転写バイアス発生部209は、DC電源302と、圧電トランス駆動回路303と、圧電トランス304と、整流回路305と、帰還制御手段としての出力電圧変換手段307および第一電圧比較手段308と、差分推測手段としての第二電圧比較手段309と、三角波生成手段としての三角波発生手段310とを備える。整流回路305の出力側と出力電圧変換手段307の入力側とは互いにC点で接続されている。

【0030】

圧電トランス駆動回路303は、スイッチング素子(NチャネルパワーMOSFET402)を用いた駆動回路であり、高圧制御部206から入力されるパルス信号(OUT1パルス)によって、DC電源302が印加する24Vの直流電圧をスイッチングすることにより、後記する圧電トランス304を駆動する。

この圧電トランス駆動回路303は、パルス信号(OUT1パルス)が「High」であれば、インダクタ401に励磁電流を流し、「Low」であれば、その励磁電流をコンデンサ404を介して放電させ、共振電流を流す。

【0031】

圧電トランス304は、セラミック等の圧電振動子の電気−機械変換作用を利用して機械共振させて、さらに機械−電気変換作用により昇圧を行う。これにより、一次側の入力電圧が昇圧されて、二次側から出力される。

整流回路305は、圧電トランス304の二次側交流電圧を直流電圧に整流する整流回路である。

DC電源302は各チャネル共通のDC電源である。

【0032】

出力負荷306は、転写ローラ111K,111Y,111M,111Cを意味し、例えば、転写ローラ印加バイアス電圧を生成(調整)する回路を含む。出力負荷306は、これらの調整されたバイアス電圧によって、高圧電源装置301としての負荷の重さが変動する。以下の本実施例では1回路のみを説明しているが、転写ローラそれぞれに回路を設けて4つ並置して4出力としてもよい。

【0033】

プリンタエンジン制御部204は、入力端子及び出力端子を備え、ON信号312s及びRESET信号313sを高圧制御部206に出力し、SDO信号428s及びSCLK信号429sをDAC311に出力する。

ON信号312sは、高圧電源装置301が負荷306に高電圧を印加するタイミングを提供する。

RESET信号313sは、高圧制御部206をリセットする。

SDO信号428sは、DAC311のシリアルデータ信号であり、SCLK信号429sは、DAC311の同期クロック信号である。

【0034】

高圧制御部206は、出力端子314(OUT1)と、入力端子315(IN1)と、入力端子316(IN2)と、出力端子317(OUT2)と、RESET端子313と、ON端子312とを有する。

出力端子314(OUT1)からは、圧電トランス304の駆動周波数を制御するパルス信号(出力信号)が出力される。パルス信号の周波数は、負荷306に印加される出力電圧に基づいて変えられる。

入力端子315(IN1)には、第一電圧比較手段308から信号(High/Low)が入力される。

入力端子316(IN2)には、第二電圧比較手段309から信号(High/Low)が入力される。

出力端子317(OUT2)からは、セレクタ部503(図7)からパルス(High/Low)が出力される。

RESET端子313には、プリンタエンジン制御部204からRESET信号313sが入力される。

ON端子312には、プリンタエンジン制御部204からON信号312sが入力される。

【0035】

図4は、図3の構成図について、高圧電源装置301を中心として詳細に説明する回路図である。図中で、図3と同じ構成要素には同じ符号を付している。

高圧電源装置301は、高圧回路350(転写バイアス発生部209に該当。なお、帯電バイアス発生部207と現像/供給バイアス発生部208も同じ高圧回路を持つ。)と高圧制御部206とを備え、高圧回路350は、DC電源302と、圧電トランス駆動回路303と、圧電トランス304と、整流回路305と、出力電圧変換手段307と、第一電圧比較手段308と、第二電圧比較手段309と、三角波発生手段310とを有している。

【0036】

圧電トランス駆動回路303は、スイッチング素子(NチャネルパワーMOSFET402)を用いた駆動回路であり、圧電トランス304を駆動する。詳細を後記する。

圧電トランス304は、図中Aで示した部分が一次側の入力端子であり、ここに圧電トランス駆動電圧を印加することにより、昇圧された交流電圧が図中Bで示した二次側から出力される。

整流回路305は、圧電トランス304の二次側交流電圧を負極性の直流電圧に整流する。DC電源302は、24Vの電源であり、図示しない低圧電源装置によって商用電源AC100Vから変圧・整流することによって実現される。

【0037】

発振器(OSC)414は、基準クロック50MHzを生成し、このクロック信号(CLK信号420s)を高圧制御部206に出力する。出力電圧変換手段307は、整流回路305の正負の2次側電圧を抵抗器409,410で分圧して、コンパレータである第一電圧比較手段308及び第二電圧比較手段309を介して、分圧電圧を高圧制御部206の入力端子315(IN1)及び入力端子316(IN2)に入力する。

【0038】

出力負荷306は、高圧電源装置301の正の出力電圧から転写バイアスを印加され、転写ローラの抵抗値および用紙の抵抗値、帯電したトナー量により、負荷が決定される。ここで、出力負荷306は抵抗器408と直列に接続されている。

【0039】

発振器414は、3.3V直流電源413から直流電力が供給され、電源電圧がVDD415、及び出力イネーブル端子OE416に印加される。

発振器414は、GND端子418が接地され、CLK_OUT端子417が抵抗器419を介して高圧制御部206のCLK端子420(CLK_IN)に接続される。

【0040】

高圧制御部206は、CLK端子420(CLK_IN)から入力される、50MHzのクロック信号(CLK信号420s)に同期して動作する。出力端子314(OUT1)は、圧電トランス駆動パルスとして、矩形波信号が出力される。プリンタエンジン制御部204と高圧制御部206とは、2種の信号(RESET信号313s、ON信号312s)を入出力する端子やポートで接続される。

【0041】

圧電トランス駆動回路303は、抵抗器403,480と、NチャネルパワーMOSFET402と、インダクタ401と、コンデンサ404とによって構成される。

【0042】

高圧制御部206が出力する出力端子314(OUT1)は、NチャネルパワーMOSFET402のゲートに入力される。

インダクタ401とコンデンサ404とはLC共振回路を構成し、インダクタ401は、圧電トランス304の一次側(入力側)Aに数十Vpeak程度の正弦半波が印加される。

【0043】

圧電トランス304は、昇圧比が周波数特性を有しているので、NチャネルパワーMOSFET402のスイッチング周波数、即ち、出力端子314(OUT1)のクロック周波数に応じた昇圧比の出力電圧を二次側Bに出力する。

圧電トランス304の二次側Bの出力特性は、図5の模式図で示すように駆動周波数によって変動するので、NチャネルパワーMOSFET402のスイッチング周波数と負荷の組み合わせにより昇圧比が決定される。圧電トランス304の出力制御は、高い周波数で駆動開始し、そこから駆動周波数を下げていくことにより出力電圧を上昇させ、目標の出力電圧を得るように制御を行う。

【0044】

再び、図4に戻って、整流回路305は、ダイオード405、406、及びコンデンサ407により構成され、圧電トランス304の二次側Bから出力される交流高電圧を正極性の直流高電圧に整流する。

【0045】

出力電圧変換手段307は、抵抗器409と抵抗器410とによって、二次側高電圧とアースとの電位差を分圧し、分圧された分圧電圧を抵抗器411とコンデンサ412とからなる低域通過フィルタにより平滑し、コンパレータである第一電圧比較手段308及び第二電圧比較手段309に分圧電圧が印加される。ここで、抵抗器409は100MΩであり、抵抗器410は47kΩである。

【0046】

アース電位が二次側高電圧の正負における分圧値の閾値となる。これにより、分圧された分圧電圧は、正極性側の最大電圧(7000V)時に約3.29Vとなる。

【0047】

第一電圧比較手段308は、デジタルアナログコンバータ(DAC)311から印加される電圧(DAC電圧)と、出力電圧変換手段307から印加される電圧(分圧電圧)とを比較する。比較した結果、DAC電圧値が分圧電圧値より大きいときに「High」を、DAC電圧値が分圧電圧値より小さいときに「Low」を、第一電圧比較手段308は高圧制御部206の入力端子315(IN1)に出力する。

【0048】

第二電圧比較手段309は、後記する三角波発生手段310から印加される電圧(三角波電圧)と、出力電圧変換手段307から印加される電圧(分圧電圧)とを比較する。比較した結果、三角波電圧値が分圧電圧値より大きいときに「High」を、三角波電圧値が分圧電圧値より小さいときに「Low」を、第二電圧比較手段309は高圧制御部206の入力端子316(IN2)に出力する。

【0049】

三角波発生手段310は、オペアンプ430、及び抵抗器431,432を備える非反転増幅回路と、抵抗器433〜436,470〜473、及びNPNトランジスタ437〜440を備えるドライブ回路と、抵抗器441〜444及び抵抗器445〜449を備えるR2R回路と、抵抗器450及びコンデンサ451によるCRフィルタとによって構成される。ここで、R2R回路を構成する抵抗器441〜444と、抵抗器445〜449との抵抗値比は2:1であり、抵抗器432と抵抗器431との抵抗値比は1:3である。

【0050】

図6は、第1チャネル〜第4チャネルの出力端子から出力される信号の波形と、抵抗器に入力される電圧値の変化と、三角波発生手段から出力される波形とを示す図である。

高圧制御部206の4チャネル(第1チャネル〜第4チャネル)の出力端子317(OUT2)から出力されるデジタル信号が、抵抗器470〜473を介してNPNトランジスタ437〜440のベースに入力される。ここでは、第1チャネルがNPNトランジスタ437のベースに入力され、第2チャネルがNPNトランジスタ438のベースに入力され、第3チャネルがNPNトランジスタ439のベースに入力され、第4チャネルがNPNトランジスタ440のベースに入力される。

【0051】

また、非反転増幅回路は、DAC311からオペアンプ430の+端子に印加された目標電圧を、抵抗器431及び抵抗器432による負帰還増幅により(4倍に)増幅する。この増幅電圧は、抵抗器433〜436を用いて、NPNトランジスタ437〜440それぞれのコレクタをプルアップする。例えば、抵抗器433でNPNトランジスタ437のコレクタをプルアップした増幅電圧は、抵抗器441に印加され、抵抗器434でNPNトランジスタ438のコレクタをプルアップした増幅電圧は、抵抗器442に印加され、抵抗器435でNPNトランジスタ439のコレクタをプルアップした電圧は、抵抗器443に印加され、抵抗器436でNPNトランジスタ440のコレクタをプルアップした電圧は、抵抗器444に印加される。

【0052】

NPNトランジスタ437〜440のベースに入力される信号により、NPNトランジスタ437〜440は、コレクタ電流のオンオフの切り替えを行う。このR2R回路は、出力電圧は、0VからDAC311が出力する2倍の電圧範囲を4ビットの分解能、すなわち0〜15段階で出力する。

【0053】

図7は、図3における高圧制御部(ASIC)のブロック図である。図中で、図3と同じ構成要素には同じ符号を付している。

図7において、高圧制御部206は、下位16ビット演算部801と、演算トリガ部802と、初期値記憶部803と、演算命令部804と、演算処理部805と、19ビット保持部806と、分周処理部807とを備える。

【0054】

下位16ビット演算部801は、分周部500と、5ビットカウンタ部501と、反転部502と、セレクタ部503と、5ビットカウンタ部504と、Dラッチ部505と、変化量設定テーブルとしてのテーブルレジスタ510と、特性テーブルとしてのテーブルレジスタ511と、補正手段としての乗算部513とを備える。

【0055】

分周部500は、256分周器であり、50MHzのCLK信号420sを256に分周し、195.3kHz(5.12μsec周期)のパルスを、5ビットカウンタ部501及び5ビットカウンタ部504に出力する。

【0056】

5ビットカウンタ部501は、分周部500から入力された5.12μsec周期のパルスをカウントする5bitのカウンタである。そして、最上位1bitをセレクタ部503に出力する。さらに、下位4bitをセレクタ部503及び反転部502に出力する。また、オーバーフロー時には、Dラッチ部505に「High」を出力し、それ以外では「Low」を出力する。

【0057】

反転部502は、入力されたビット値を反転して出力する。ここでは、5ビットカウンタ部501から入力される4ビット値(下位4bit)を反転してセレクタ部503に出力する。

セレクタ部503は、5ビットカウンタ部501の最上位bitが選択信号として入力され、5ビットカウンタ部501の下位4bitと反転部502の出力4bitとの何れかを出力する。これにより、三角波発生手段310は、DAC311が出力する目標電圧の2倍のピーク電圧の三角波を発生する(図6参照)。

【0058】

5ビットカウンタ部504は、分周部500から入力されるパルス(カウント用パルス)のタイミングで、第二電圧比較手段309から入力されるパルスのレベルをチェックし、レベルが「High」である回数をカウントする。その後、5ビットカウンタ部504は、5ビットカウンタ部501からオーバーフロー信号が入力されたとき、カウンタをクリア(0)する。

【0059】

Dラッチ部505は、5ビットカウンタ部501からオーバーフロー信号が入力されたとき、5ビットカウンタ部504の値を取得し、テーブルレジスタ510に記憶させる(ラッチする)。

【0060】

ここで、出力電圧変換手段307から第二電圧比較手段309に入力される電圧がほぼ0Vである初期状態の場合、第二電圧比較手段309の出力レベルは、ほぼ「High」である。ここで分周部500からパルスがON(カウントタイミング)で入力されたときに、5ビットカウンタ部504はカウント(カウンタを1加算)する。このカウントタイミングのとき、5ビットカウンタ部501もカウント(カウンタを1加算)する。その後、5ビットカウンタ部501のカウンタが「1Fh」(hは16進数を示す)となったときに、5ビットカウンタ部501はオーバーフロー信号を5ビットカウンタ部504及びDラッチ部505に出力する。これにより、Dラッチ部505は、5ビットカウンタ部504の値をラッチし、5ビットカウンタ部504は、Dラッチ部505がラッチした後でカウンタをクリアする(「00h」にする)。そして、5ビットカウンタ部501はオーバーフロー信号を出力後、自身のカウンタをクリアする(「00h」にする)。

【0061】

テーブルレジスタ510は、5ビットの入力値と、8ビットの出力値とを対応して記憶するテーブルを備え、Dラッチ部505からの入力があったときに、その入力値に対応する出力値をテーブルから抽出して、乗算部513に出力する。

テーブルレジスタ510が備えるテーブルの一例を図8に示す。このテーブルは、Dラッチ部505から入力される5ビットの入力値と、乗算部513に出力する8ビットの出力値とを対応付けて記憶する。すなわち、テーブルレジスタ510は、出力電圧と目標電圧との差分値に対応させて周波数変化量が記憶されている。

【0062】

ここで、テーブルレジスタ510が備えるテーブルは、入力値と出力値が中心(基準値)に対して周波数変化量が直線的に上下対称に設定されており、入力値が基準値(図8では中間値の10h)よりも大きくても小さくても、出力値が大きくなるように設定される。その一方、入力値が基準値であれば、出力値は小さくなるように設定される。これは、テーブルレジスタ510に入力される5ビットの入力値が5ビットカウンタ部504の値であるため、第二電圧比較手段309からの出力レベルが「High」である回数と「Low」である回数とでほぼ等しくなるときに、テーブルレジスタ510からの出力値が小さくなる。すなわち、三角波発生手段310の出力電圧の平均値(ピーク値の1/2)が出力電圧変換手段307の出力電圧値とほぼ等しくなるときに、出力値が小さくなるようにテーブルレジスタ510の入力値と出力値とは設定されている。

【0063】

テーブルレジスタ511は、7ビットの入力値と、8ビットの出力値とを対応して記憶するテーブルを備え、後記する19ビット保持部806からの入力があったときに、その入力値に対応する出力値をテーブルから抽出して、乗算部513に出力する。

テーブルレジスタ511が備えるテーブルの一例を図9に示す。このテーブルは、19ビット保持部806から入力される7ビットの入力値と、乗算部513に出力する8ビットの出力値とを対応付けて記憶する。

【0064】

このテーブルレジスタ511が備えるテーブルの入力値及び出力値は、次のように予め決められた値である。

本実施形態において、高圧制御部206が行う周波数制御範囲は上限値が「1CFh」であり、下限値が「180h」である。これが、19ビット保持部806の上位9bitの上限値と下限値として決められ、後記するカウンタ上限値記憶部519には、上限値「1CFh」(1 1100 1111b)が記憶されている。後記するカウンタ下限値記憶部520には、下限値「180h」(1 1000 0000b)が記憶されている。

【0065】

パルスの出力は、19ビット保持部806の19ビット値のうち、上位9bitを分周に、下位10bitを端数として演算する。CLK信号420sのクロック周期は、1/50MHz=20nsecである。

下限値「180h」のときの周波数は、

180h×20nsec=7.68μsec

1/7.68μsec=130.2kHz

となる。

同様に、上限値「1CFh」のときの周波数は、

1CFh×20nsec=9.26μsec

そのときの端数である下位10bitの「3FFh」も考慮して、

3FFh(=1023)×20nsec/1024=0.02μsec

1/(9.26μsec+0.02μsec)=107.76kHz

となる。

よって、制御周波数範囲は、107.76〜130.2kHzである。

【0066】

テーブルレジスタ511には、19ビット保持部806の19ビット値の上位9bitのうちの、最上位2bit(常に11bである)を除く、7bit(7ビット値)が入力される。つまり、7ビット値が00h(000 0000b)であれば、元の上位9bitは180h(1 1000 0000b)である。そして、7ビット値が47h(100 0111b)であれば、元の上位9bitは1C7h(1 1100 0111b)である。

【0067】

このテーブルレジスタ511には、いち早く目標電圧に近づけるための設定値が記憶されている。出力電圧が低く、周波数が高い領域では(つまり、圧電トランスの固有共振周波数から離れるほど)周波数の制御量、すなわち周波数の変化量に対する出力電圧の変換量が大きくなるように、入力値と出力値とが設定されている。このテーブルレジスタ511の値は、実験により得られた値である。

【0068】

乗算部513は、テーブルレジスタ510からの8ビット値と、テーブルレジスタ511からの8ビット値とを乗算して、算出した16ビット値を演算処理部805に出力する。本実施例において、乗算部513は常に乗算を行い、その乗算結果を演算処理部805に出力する。

【0069】

(演算トリガ部802)

演算トリガ部802は、周期値記憶部516と、シフト演算部550と、3ビットカウンタ部551と、テーブルレジスタ552と、演算指示部517とを備える。

周期値記憶部516は、制御周期を決定する13bitのメモリであり、140μsecに相当する値である「7000(1B58h)」が予め記憶されている。

【0070】

シフト演算部550は、3ビットカウンタ部551から取得した3ビット値に応じて、周期値記憶部516の13ビット値をシフト演算して、演算値を演算指示部517に出力する。

例えば、シフト演算部550は、3ビットカウンタ部551から取得した3ビット値が「000b」の場合は、13ビット値をシフトしない。3ビット値が「001b」の場合は1ビットシフトし、「010b」の場合は2ビットシフトし、「011b」の場合は3ビットシフトする。以降、3ビットカウンタ部551から取得した3ビット値が1ビット増えるごとに、シフト演算部550は、そのビット分のシフトを13ビット値に行う。

これにより、周期値記憶部516の13ビット値が「7000(01B58h)」である場合、シフト演算部550は、3ビット値が「000b」のときそのまま(シフトせずに)「7000(01B58h)」を演算指示部517に出力する。そして、「001b」のとき1ビットシフトして「14000(036B0h)」を出力し、「010b」のとき2ビットシフトして「28000(06D60h)」を出力する。

【0071】

演算指示部517は、シフト演算部550から演算値(20ビット値)を取得して保持する記憶手段と、カウンタとして値(20ビット値)を保持する記憶手段とを備え、さらに、カウンタの値をカウントアップする機能を備える。そして、演算指示部517は、カウンタの値と、演算値の値とが等しくなったときに、20ビット値を「00000h」として、CLK端子420(CLK_IN)から入力されるCLK信号420sのタイミングで1ビットずつカウントアップする。そして、20ビット値が「00800h」を超えるまで、演算指示部517は演算処理部805にパルスを「High」で出力する。そして、20ビット値が「00800h」を超えたときから(「00801h」となったときから)、シフト演算部550から取得した演算値(20ビット値)になるまで、演算指示部517は演算処理部805にパルスを「Low」で出力する。

つまり、シフト演算部550から取得した演算値(20ビット値)が「01B58h」であれば、カウンタの値が「01B58h」となるまで、演算指示部517は演算処理部805にパルスを「Low」で出力する。そして、演算指示部517は、カウンタの値と、演算値の値とが等しくなったことで、20ビット値を「00000h」に設定して、再び1ビットずつカウントアップをし、演算処理部805にパルスを再び「High」で出力する。

【0072】

3ビットカウンタ部551は、3ビット値を、演算指示部517からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)でカウントダウンする。そして、ON端子312からのON信号312sの立ち上がりエッジで、そのときの3ビット値をシフト演算部550に出力するとともに、テーブルレジスタ552から3ビット値を取得して、カウントダウン対象の3ビット値とする。

ここで、カウントダウン中に3ビット値が「000b」となった場合、3ビットカウンタ部551はその値を保持する。

【0073】

例えば、3ビットカウンタ部551にON信号312sの立ち上がりエッジが入力されたときに、3ビットカウンタ部551はテーブルレジスタ552から3ビット値を取得する。そして、3ビットカウンタ部551は、演算指示部517からの出力パルスの立ち上がりエッジがあるごとに3ビット値から1bitずつカウントダウンする。例えば、取得した3ビット値が「110b」である場合、「101b」、「100b」、「011b」、「010b」、「001b」、「000b」とカウントダウンする。一旦、「000b」となった後は、カウントダウンをせず、次のON信号312sの立ち上がりエッジが入力されるまで値を「000b」のまま保持する。

【0074】

テーブルレジスタ552は、7ビットの入力値と、3ビットの出力値とを対応して記憶するテーブルを備え、後記する19ビット保持部806からの入力があったときに、その入力値(7ビット値)に対応する出力値(3ビット値)をテーブルから抽出して、3ビットカウンタ部551に出力する。

テーブルレジスタ552が備えるテーブルの一例を図10に示す。このテーブルは、19ビット保持部806から入力される7ビットの入力値と、3ビットカウンタ部551に出力する3ビットの出力値とを対応付けて記憶する。ここで、19ビット保持部806からは、19ビット値(bit18〜bit0)のうち、bit16〜bit10の7ビットが入力値として入力される。

【0075】

初期状態について説明する。まず、出力電圧変換手段307の出力がほぼ0Vである初期状態において、テーブルレジスタ552には、7ビットの入力値が「00h」で入力される。テーブルレジスタ552は、図10のテーブルを参照して、3ビットの出力値として「000b」を3ビットカウンタ部551に出力する。ここで、3ビットカウンタ部551は、RESET信号313sにより初期化された値「000b」を保持している。結果、3ビットカウンタ部551がシフト演算部550に出力する3ビット値は「000b」となる。

【0076】

(初期値記憶部803)

初期値記憶部803は、カウンタ上限値記憶部519と、カウンタ下限値記憶部520とを備える。カウンタ上限値記憶部519には、上限値「1CFh」(1 1100 1111b)が記憶されている。カウンタ下限値記憶部520には、下限値「180h」(1 1000 0000b)が記憶されている。

【0077】

(演算命令部804)

演算命令部804は、演算処理部805に命令(3ビット値)を出力して、19ビット保持部806への出力値を制御する。この演算命令部804は、9ビットカウンタ部506と、Dラッチ部507と、比較部514とを備える。

【0078】

9ビットカウンタ部506は、第一電圧比較手段308から入力端子315(IN1)に入力される信号が「High」である時間を計測する。

本実施形態において、9ビットカウンタ部506は、50MHzのCLK信号420sのパルスがCLK端子420(CLK_IN)に入力されるタイミングで、入力端子315(IN1)に入力される信号の判定を行い、「High」であるときに1ビットずつ9ビットカウンタ値をカウントアップする。そして、出力セレクタ部528からの入力信号が立ち上がったタイミングで、9ビットカウンタ値はクリア(000h)される。このクリアは、後記するDラッチ部507が9ビットカウンタ値を取得した後で行われる。

【0079】

Dラッチ部507は、出力セレクタ部528からの入力信号が立ち上がったタイミングで、9ビットカウンタ部506の9ビットカウンタ値を取得する。そして、Dラッチ部507は、RESET信号313sがRESET端子313に入力されるタイミングで、記憶している値をクリア(000h)する。

【0080】

比較部514は、ON端子312に入力されるON信号312sに応じて、演算処理部805に対する演算命令(3ビット値)を決定して出力する。

本実施形態において、比較部514は、ON信号312sが「High」であるときに、Dラッチ部507の9ビットカウンタ値と、19ビット保持部806の上位9ビット値(bit18〜bit10)とを比較判定して、比較判定結果に応じて演算命令「000b」〜「100b」のいずれか一つを演算処理部805に出力する。一方、ON信号312sが「Low」であるとき、比較部514は、演算命令「010b」を演算処理部805に出力する。

【0081】

ここで、比較部514は比較判定の結果(判定結果A〜E)に応じて、以下に示す演算命令を出力する。

(判定結果A)「9ビットカウンタ値≧上位9ビット値−5」の場合、演算命令「000b」を出力する。

(判定結果B)「上位9ビット値−5>9ビットカウンタ値≧上位9ビット値×0.6」の場合、演算命令「001b」を出力する。

(判定結果C)「上位9ビット値×0.6>9ビットカウンタ値≧上位9ビット値×0.4」の場合、演算命令「010b」を出力する。

(判定結果D)「上位9ビット値×0.4>9ビットカウンタ値>5」の場合、演算命令「011b」を出力する。

(判定結果E)「5≧9ビットカウンタ値」の場合、演算命令「100b」を出力する。

【0082】

(演算処理部805)

演算処理部805は、演算命令部804(比較部514)からの演算命令に従って、19ビット保持部806が記憶する19ビット値に演算を行う。この演算は、演算指示部517からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)で行われる。

【0083】

ここで、演算処理部805は、比較部514からの演算命令に従って、以下に示す演算を行う。

演算命令「000b」の場合、乗算部513から16ビット値を取得し、19ビット保持部806にその16ビット値を加算する。

演算命令「001b」の場合、19ビット保持部806の値に1を加算する。

演算命令「010b」の場合、19ビット保持部806の値を更新しない(値をそのままにする)。

演算命令「011b」の場合、19ビット保持部806の値から1を減算する。

演算命令「100b」の場合、乗算部513から16ビット値を取得し、19ビット保持部806の値からその16ビット値を減算する。

【0084】

ここで、次の事象(事象A〜事象C)が発生した場合には、その事象に応じた割込処理を演算処理部805は行う。

(事象A)RESET信号313sがRESET端子313に入力されたとき、演算処理部805は、カウンタ下限値記憶部520から下限値「180h」(1 1000 0000b)を取得し、19ビット保持部806の上位9ビット値を下限値「1 1000 0000b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

(事象B)演算処理部805は、演算命令「001b」により加算を行った結果、上位9ビット値がカウンタ上限値記憶部519の上限値「1CFh」(1 1100 1111b)を超えた場合、19ビット保持部806の上位9ビット値を上限値「1 1100 1111b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

(事象C)演算処理部805は、演算命令「011b」により減算を行った結果、上位9ビット値がカウンタ下限値記憶部520の下限値「180h」(1 1000 0000b)を下回った(未満となった)場合、19ビット保持部806の上位9ビット値を下限値「1 1000 0000b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

【0085】

(19ビット保持部806)

19ビット保持部806は、19ビットの値を記憶するレジスタである。19ビットの値のうち、上位9ビット値は、比較部514、加算部525、及び分周セレクタ部526に出力され、下位10ビット値は、誤差保持部529に出力される。

【0086】

(分周処理部807)

分周処理部807は、19ビット保持部806の上位9ビット値に基づき、パルスの周波数を決め、パルスを生成して出力する。この分周処理部807は、加算部525と、分周セレクタ部526と、パルス生成部527と、出力セレクタ部528と、誤差保持部529とを備える。

【0087】

加算部525は、19ビット保持部806から取得した上位9ビット値に1を加算して、分周セレクタ部526に出力する。

【0088】

分周セレクタ部526は、後記する誤差保持部529からの入力値に応じて、19ビット保持部806または加算部525から取得した9ビット値をパルス生成部527に出力する。

本実施形態において、分周セレクタ部526は、誤差保持部529からの入力値が「High」である場合、加算部525から取得した9ビット値(上位9ビット値に1を加算した値)をパルス生成部527に出力する。一方、入力値が「Low」である場合、分周セレクタ部526は、19ビット保持部806から取得した上位9ビット値をパルス生成部527に出力する。

【0089】

パルス生成部527は、分周セレクタ部526から出力される9ビット値の周波数のパルスをデューティ比30%で生成し、パルスを出力セレクタ部528に出力する。

【0090】

出力セレクタ部528は、ON端子312からのON信号312sが「High」の場合、パルス生成部527から入力されるパルスをそのまま出力端子314(OUT1)に出力する。一方、ON信号312sが「Low」の場合、出力セレクタ部528は「Low」の信号を出力する。

【0091】

誤差保持部529は、10ビットのレジスタと1ビットのフラグレジスタとで構成され、RESET信号313sがRESET端子313に入力されるタイミングで、10ビットのレジスタ値及び1ビットのフラグレジスタ値をクリアする。

また、誤差保持部529は、パルス生成部527からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)で、19ビット保持部806の下位10ビット値を取得し、10ビットのレジスタに加算する。この加算時にオーバーフローが発生した場合、フラグレジスタを「1」とし、発生しなかった場合は「0」とする。

【0092】

(実施例1の動作説明)

まず、第1の実施形態における画像形成装置全体の概略動作を説明する。

図1の画像形成装置101は、外部機器からホストインタフェース部201(図2)を介してPDL(Page Description Language)などで記述された印刷データを入力する。入力された印刷データは、コマンド/画像処理部202によってビットマップデータに変換される。

【0093】

画像形成装置101は、定着器123の加熱部材124、及び圧着部材125を、サーミスタ216(図2)の検出値に応じて定着器ヒータ217(図2)を制御することにより所定温度にした後、印字動作を開始する。画像形成装置101は、用紙カセット117にセットされた用紙を給紙モータ210で駆動する給紙ローラ118で給紙する。用紙ガイド119に沿って用紙を搬送し、停止状態のレジストローラ120、121の対に用紙を突き当て、スキューを補正した後、以下で説明する画像形成動作に同期したタイミングで搬送モータ211を駆動開始し、レジストローラ120、121によって用紙は転写ベルト114上に搬送される。

【0094】

このとき、前記ビットマップデータに応じてLEDヘッド103K、103Y、103M、103Cが点灯される。これにより、感光体ドラム109K、109Y、109M、109Cには、静電潜像が形成される。

現像器102K、102Y、102M、102Cは、電子写真プロセスにより現像器内の感光体ドラム109K、109Y、109M、109Cにトナー像を形成する。現像器102K、102Y、102M、102Cによって現像されたトナー像は、転写ベルト114上を搬送される用紙に転写される。このとき、転写ベルト114を狭持して感光体ドラム109K、109Y、109M、109Cに対向して配設されている転写ローラ111K、111Y、111M、111Cは、転写バイアスが印加されている。

用紙上に4色のトナー像を転写した後、定着器123は、加熱・加圧により用紙上のトナー像を定着させ、排出ローラ126、127は、用紙ガイド128に沿って用紙を搬送し、排紙する。

【0095】

本実施形態での主要な制御対象は転写ローラ111K,111Y,111M,111Cに印加するバイアス電圧であるが、これらは同様の構成を4色分並置するものであるので、以下の説明は1色分とする。

プリンタエンジン制御部204は、感光体ドラム駆動モータ214(図2)により感光体ドラム109を回転駆動させると同時に、現像バイアスの印加を開始する。

【0096】

続いて図4の回路図を用いて詳細に説明する。

プリンタエンジン制御部204は、「Low」のRESET信号313sを出力して高圧制御部206の諸処の設定をリセットする。このリセット動作によって出力端子314(OUT1)から出力するパルスの分周比などの値が初期値となる。高圧制御部(ASIC)206は初期値にてCLK端子420(CLK_IN)から入力されるCLK信号420sを初期値の分周比、ONデューティ30%で分周する。但し、プリンタエンジン制御部204から高圧オンのコマンドを受信するまでは出力端子314(OUT1)から分周されたパルスは出力されず、出力端子314(OUT1)出力は「Low」レベルに保持される。

【0097】

プリンタエンジン制御部204は、SCLK信号429s(同期クロック)を出力し、前記クロックに同期してSDO信号428s(シリアルデータ)を出力し、高圧出力目標電圧をDAC311出力値である10bitデータをDAC311に送信する。例えば、7kVの場合には3.29Vの比較電圧となり、この場合3.3V 10bitであるので送信データは3Fbhとなる。ここで、高圧制御部206及びDAC311には、不図示の3.3V電源が接続されている。また、第一電圧比較手段308、第二電圧比較手段309、オペアンプ430の電源端子には不図示の24V電源及びGNDが接続されている。

【0098】

高圧制御部206のCLK端子420(CLK_IN)には、抵抗器419を介して発振器414が接続されている。発振器414は、電源端子VDD415と出力イネーブル端子OE416に3.3VのDC電源413が接続され、発振器414のCLK_OUT端子417から電源投入直後から50MHz、周期20nsecのクロックパルスが出力される。GND端子418は接地される。

出力端子314(OUT1)が出力するパルスが「Low」である間、NチャネルパワーMOSFET402はオフである。そのため、圧電トランス304の一次側端子(図4のAで示す部分)には、DC電源302から直流電圧24Vがそのまま印加される。

【0099】

このとき、DC電源302からインダクタ401を介して流れる電流値はほぼ0であり、圧電トランス304は圧電振動しない。そのため、圧電トランス304の二次側(図4のBで示す部分)の出力電圧は0Vであり、出力電圧変換手段307の出力電圧は0Vである。第一電圧比較手段308の「+」入力端子にはDAC311から目標電圧(3.29V)が印加され、「−」入力端子には出力電圧変換手段307から電圧(0V)が印加される。「+」入力端子の電圧の方が高いので、第一電圧比較手段308はオープンコレクタ出力となり、3.3V電源413に接続されているプルアップ抵抗器460のため、第一電圧比較手段308から「High」の信号が、入力端子315(IN1)に入力される。

【0100】

同様に、第二電圧比較手段309の「−」入力端子には出力電圧変換手段307から電圧(0V)が印加され、「+」入力端子には三角波発生手段310から三角波電圧が印加される。この三角波発生手段310には、高圧制御部206の出力端子317(OUT2)から4つの信号が入力される。

出力端子317(OUT2)の出力信号が「High」の場合、NPNトランジスタ437(〜440)にベース電流が流れ、NPNトランジスタ437(〜440)がONになり、抵抗器441(〜444)の一端は接地する(0V)。一方、出力端子317(OUT2)の出力信号が「Low」の場合、オペアンプ430の出力電圧が抵抗器433(〜436)でプルアップして出力される。

【0101】

オペアンプ430、及び抵抗器431及び抵抗器432を含む非反転増幅回路は、DAC311からの入力電圧を4倍に増幅する。そして、抵抗器441(〜444)と抵抗器445(〜449)との抵抗値比は2:1である。また、抵抗器441〜444及び抵抗器445〜449でR2Rを構成している。

4チャネルの出力端子317(OUT2)の出力信号(4bit)は、0000b〜1111bの16段階で出力され、抵抗器450及びコンデンサ451のCRフィルタにより波形が整形されて、第二電圧比較手段309の「+」入力端子に印加される。これにより、三角波発生手段310は、DAC311の出力電圧の2倍の値の三角波を出力する。

【0102】

図6に、4チャネルの出力端子317(OUT2)が出力する信号(第1チャネル出力〜第4チャネル出力)と、抵抗器450に印加される電圧値と、CRフィルタにより波形が整形されて印加される電圧値(つまり、三角波発生手段310の出力電圧値)とを示す。

【0103】

第二電圧比較手段309の「−」入力端子の電位が0Vであれば、3.3V電源413に接続されるプルアップ抵抗器461の電位で、ほぼ「High」レベルに近いデューティ100%弱の163.8μsec周期の波形(PWM波形)が、高圧制御部206の入力端子316(IN2)に入力される。

そして、高圧制御部206は、PWM波形を163.8μsec周期でサンプリングして、デューティを32段階で検出する。この検出値は、第二電圧比較手段309の「−」入力端子の電位が0Vの場合の初期状態において、1Fhとなる。

【0104】

ここで、感光体ドラム109(図1)と転写ベルト114(図1)が駆動され、用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204はON信号312sを「Low」から「High」に遷移して高圧制御部206に出力する。ON端子312からON信号312sを「High」で取得した高圧制御部206は、初期値にて分周したパルスを出力端子314(OUT1)から出力する。

【0105】

本実施例では初期値は384分周であり、1周期7.68μsec、ONデューティ29%である。出力端子314(OUT1)から出力されたパルスによってNチャネルパワーMOSFET402がスイッチングされ、インダクタ401とコンデンサ404と圧電トランス304とによって、圧電トランス304の一次側(Aで示す端子)には、図11に示す数十Vpeakの半波正弦波形が印加される(圧電トランス駆動回路303出力)。

【0106】

入力端子315(IN1)に印加される電圧が「High」レベルの場合、所定周期である140μsec毎に、384分周の分周比に1加算する。加算した結果、周波数が低くなり、図12で示すように出力電圧が上昇して行く。

【0107】

ここで、図12は、無負荷の場合のデータ(太線)と、負荷がある場合(100MΩの抵抗器408と50MΩの負荷306)のデータ(破線)であり、負荷により同じ電圧出力でも駆動周波数が異なることを示している。なお、図12では、駆動周波数約108kHzのときに最大出力電圧は7000Vであるが、圧電トランスの共振周波数は、108kHzよりも低い所に存在する(図5参照)。また、図13及び図14に、図12の特性に対する19bitレジスタ値を示す。

【0108】

出力電圧上昇に伴い、入力端子316(IN2)に入力される163.8μsec周期のPWM波形のデューティが小さくなる。その後、デューティが100%から目標電圧であるデューティ50%となるまで、所定の設定値によって分周比可変幅が大〜小へと変化する。ついには目標電圧付近にて入力端子315(IN1)の出力電圧が矩形波となったときに、分周比可変幅を最小分解能に落として、デューティが40〜60%となるように分周比設定値を加減算する。これにより目標電圧にて定電圧制御される。

以上の動作により、7000Vの目標電圧が転写ローラ111(111K,111Y,111M,111C)(図2)に印加される。

【0109】

さらに、用紙検出センサ122(図2)が用紙後端を検出した所定時間後、すなわち用紙が感光体ドラム109(図1)と転写ローラ111(図1)とのニップ部を通過する直前で、プリンタエンジン制御部204は、ON信号312sを「High」から「Low」に遷移して高圧制御部206に出力する。ON端子312からON信号312sを「Low」で取得した高圧制御部206は、出力端子314(OUT1)から出力する信号(圧電トランス駆動信号)をオフする。これにより、高圧電源装置301が出力する電圧が落とされる(0になる)。

【0110】

このとき、DAC311は3.29Vの電圧を印加し続ける。また高圧制御部206の内部では、オフする直前の、出力端子314(OUT1)の出力信号(圧電トランス駆動信号)が保持される。

そして、次の用紙がある場合には、その用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204はON信号312sを「Low」から「High」に遷移して高圧制御部206に出力する。2回目のON信号312sが出力される、すなわち2枚目以降の印刷では、前回の印刷後におけるオフする直前の、出力端子314(OUT1)の出力信号(圧電トランス駆動信号)の分周比値(駆動周波数)にて、駆動が開始される。このとき、圧電トランス駆動信号の分周比値を制御する周期を初回印刷時と異なるものとして制御を行う。

【0111】

以降、再度7000Vに制御され、連続印刷の間同じ動作を繰り返す。

指定枚数の用紙の印刷が終了後、プリンタエンジン制御部204はON信号312sを「High」から「Low」に遷移して高圧制御部206に出力し、さらにRESET信号313sを「High」から「Low」に遷移して高圧制御部206に出力する。これにより、高圧制御部206の内部設定値をリセットする。

【0112】

本実施例の高圧電源装置301の2枚目以降の印刷における出力特性を図15及び図16に示す。図15は、駆動周波数が108.46Hzの場合の立ち上がり特性を示し、図16は、駆動周波数が111.61Hzの場合の立ち上がり特性を示す。負荷値により出力電圧が変化するが、駆動周波数が等しければ負荷値によらず立ち上がり時間は等しかった。また、図の特性は100MΩの抵抗器408と負荷306との間のポイントを測定しており、実施例にて説明している制御電圧が7000Vとなる部分はダイオード406、抵抗器409、抵抗器408の接続部(図4のCで示す部分)である。

【0113】

本発明では駆動周波数と立ち上がり時間の関係が負荷によらずに等しいことから直前の印刷での駆動周波数で駆動を開始した場合の高圧立ち上がり時間に応じた時間だけ、駆動周波数を変化させる周期を長くすることによって早くて正確な立ち上げを実現している。また、連続印字時には印刷間での環境温度変化などはほとんどないので、負荷による駆動特性が一意に決定しない圧電トランスの駆動においても同一駆動周波数にて目標電圧に制御可能である。さらには、立ち上がり時間経過後において、出力電圧のフィードバック制御を短い周期で行うので、たとえ負荷変動があったとしても直ちに収束することができる。

【0114】

次に、第1の実施形態における高圧制御部206の概略動作を、図7を用いて説明する。

まず、プリンタエンジン制御部204からRESET信号313sが入力されたとき、高圧制御部206が備えるカウンタ部(5ビットカウンタ部501,5ビットカウンタ部504,9ビットカウンタ部506)の値が初期化される。

そして、演算処理部805は、上位9bitをカウンタ下限値記憶部520の9ビット値とし、下位10bitを0にする19ビット値を生成する。この19ビット値を19ビット保持部806に記憶させる。このとき、初期値として、19ビット保持部806には60000hが記憶される。

【0115】

そして、分周セレクタ部526には、19ビット保持部806の上位9bitと、加算部525により19ビット保持部806の上位9bitに1加算された値とが入力される。例えばそれぞれの値が180h、181hとなる。

初期状態、すなわちRESET信号313sが入力後では、19ビット保持部806の上位9bit(180h)がパルス生成部527に入力される。

パルス生成部527は0から180hまで、CLK端子420(CLK_IN)から入力されるCLK信号420sのクロックをカウントする毎に、パルスを出力する。パルス生成部527はCLK信号420sの立ち上がりでカウントアップする9ビットカウンタを備え、9ビットカウンタの値と分周セレクタ部526が出力する9ビット値との比較及び、9ビットカウンタの値と分周セレクタ部526が出力する9ビット値を約30%にした値(この値は実際には9ビット値の1/4値,1/32値,1/64値の和)との比較を行う。ここで、9ビットカウンタの値と、分周セレクタ部526が出力する9ビット値を約30%にした値と等しくなった場合、パルス生成部527は「Low」で出力する。一方、9ビットカウンタの値と、分周セレクタ部526が出力する9ビット値とが等しくなった場合、パルス生成部527は「High」を出力し、9ビットカウンタを0にする(クリアする)。

【0116】

以上の動作によって、パルス生成部527は、CLK信号420sを分周セレクタ部526が出力する9ビット値で分周した周波数で、約30%のONデューティのパルスを出力する。

そして、出力セレクタ部528は、ON信号312sがON(High)である場合にパルスを出力し、OFF(Low)の場合は「Low」を出力する。

【0117】

ここで、19ビット保持部806の下位10bitは、小数点以下の分周比を示すカウンタである。分周比は180h(384)分周であり、60000h(初期値、上位9bitが180h、下位10bitが0)から開始し、60400h(上位9bitが181h、下位10bitが0)になるまでの間、小数点以下を示す値の誤差を加算し、加算結果が1以上となった時にパルスの分周比を1加算された方を選択する。

【0118】

例えば、19ビット保持部806の値が60200hの場合、整数部(上位9bit)は180h、小数部(下位10bit)は200hとなる。このとき誤差保持部529の値が000h(10ビット値)でオーバーフローフラグが0の場合、19ビット保持部806の9ビット値が分周セレクタ部526で選択されて、パルス生成部527に入力され、パルス生成部527からは、180h(384)分周、130.208kHzのパルスが出力される。

【0119】

このパルス生成部527が出力するパルスは、出力セレクタ部528に出力されると共に、誤差保持部529にも出力される。これにより、誤差保持部529は、自身が保持する10ビット値(000h)に、19ビット保持部806の下位10bit(200h)を加算し、算出結果の200hを10ビット値として保持する。そして、オーバーフローフラグを「Low」にする。

【0120】

次に、パルス生成部527からパルスが入力されたタイミングで、誤差保持部529は、同様の処理を行う。誤差保持部529は、自身が保持する10ビット値(200h)に、19ビット保持部806の下位10bit(200h)を加算するため、算出結果は400hとなる。ここで、10bitレジスタ値の保持レンジは000〜3FFであるため、オーバーフローフラグを「High」に設定して、誤差保持部529の値を000hにする。

【0121】

そして、19ビット保持部806(?)から出力されるパルスの周波数指示値は、整数部が180h(384)で小数部が200h(512)であり、実数値としては384.5となる。この場合、384分周のパルスと385分周のパルスとが交互に出力される。そのため、分周比平均は384.5となる。

【0122】

また、小数部が180hである場合は、誤差保持部529の値は000h、180h、300h、080hとなり、300hから080hとなる時にオーバーフローフラグが「High」となる。整数部をN(Nは整数)とした場合に、N分周、N分周、N分周、N+1分周と分周比が変化し、分周比平均は最終的にN+(384/1024)となる。

【0123】

19ビット保持部806の分周比指示値は乗算部513により更新される。以下に説明する。プリンタエンジン制御部204からのON信号312sが「Low」である間は、出力セレクタ部528は「Low」を出力する。そのため、圧電トランス駆動回路303はオフ状態となる。

【0124】

その後、画像形成装置101(図1)は印字動作を開始し、転写バイアスを出力するために転写電圧に相当する10bit値をDAC311に設定する。例えば、DAC311の出力レンジ0〜3.3V、出力電圧範囲0〜7025Vとなるように各回路定数が設定されたとする。

【0125】

ここで、図4に示す抵抗器409は100MΩ、抵抗器410は47kΩである。

目標電圧を7000Vとした場合、プリンタエンジン制御部204はDAC311に、3FDhの10ビット値のSDO信号428sを出力する。DAC311は、10ビット値「3FDh」に該当する3.29VのDC電圧を、高圧電源装置301に出力する。

この時点で、高圧電源装置301はまだ高圧出力しておらず、出力電圧変換手段307の出力はほぼ0Vであり、第一電圧比較手段308の出力は「High」である。

【0126】

再び図7を用いて説明する。

分周部500は、50MHzのCLK信号420sを256分周して、195.3kHz、5.12μsec周期のパルスを出力する。出力されたパルスは5ビットカウンタ部501にてカウントアップされ、5ビット値の最上位ビットを反転指示信号としてセレクタ部503に出力することにより、下位4bitが増減を繰り返すように切り換えられる。結果カウント値は、0000,0001,0010,・・・,1110,1111,1111,1110,・・・,0010,0001,0000と変化し、この4ビット値が三角波発生手段310に出力される。結果、図6で示されるタイミングの波形が出力端子317(OUT2)から出力され、図6及び図11に示すように三角波発生手段310からピークが6.58Vの三角波が出力される。

出力電圧変換手段307の出力がほぼ0Vであるので、第二電圧比較手段309からは「High」が出力される。

【0127】

9ビットカウンタ部506は、第一電圧比較手段308の出力をカウントする。ON信号312sがオフ(Low)である場合、比較部514は3ビット値「010b」を出力するので、19ビット保持部806は初期値を保持される。

5ビットカウンタ部504は、第二電圧比較手段309の出力が「High」である時間を、分周部500のパルスの立ち上がりエッジのタイミングでカウントする。第二電圧比較手段309の出力が「High」レベルであればカウントアップを行い、一方、「Low」レベルであればカウント値を保持する(カウントしない)。そして、5ビットカウンタ部501のオーバーフロー時に、5ビットカウンタ部504は、このカウント値を0にする(クリアする)。

ここで、出力電圧変換手段307の出力がほぼ0Vである初期状態の場合、第二電圧比較手段309の出力はほぼ「High」レベルであるので、カウント値は0から順次カウントアップされる、1Fhまでカウントしたときに、5ビットカウンタ部501のオーバーフローによってクリアされると同時に、カウント値「1Fh」がDラッチ部505にラッチされる。

【0128】

演算指示部517は、CLK信号420sのパルスをカウントし、カウント値が00000〜00800hのときに「High」を出力し、カウント値が00801h以上となったときに「Low」を出力する。そして、シフト演算部550が出力する20ビット値と等しくなったら、再度、カウント値を00000hで初期化する。それによりシフト演算部550の設定周期のパルスを出力する。初期状態では140μsecに相当する値、7000(1B58h)である。

【0129】

図10にテーブルレジスタ552の入出力の対応関係を示す。

テーブルレジスタ552は、19ビット保持部806のbit16〜bit10の7ビット値に対応する3ビット値を3ビットカウンタ部551に出力する。初期状態では7ビット値は00hであるので、出力する3ビット値は000bである。また、3ビットカウンタ部551は、RESET信号313sが入力されて初期化されているため、000bを保持している。その結果、シフト演算部550に出力される3ビット値は000bとなり、前記説明したようにシフト演算部550の入出力値はビット幅が異なるのみで等しくなる。

【0130】

図9にテーブルレジスタ511の入出力の対応関係を示す。

テーブルレジスタ511は、テーブルレジスタ552同様、19ビット保持部806のbit16〜bit10の7ビット値に対応する8ビット値を乗算部513に出力する。初期状態では7ビット値は00hであるので、出力する8ビット値は80hである。

図8にテーブルレジスタ510の入出力の対応関係を示す。

テーブルレジスタ510は、Dラッチ部505の5ビット値に対応する8ビット値を乗算部513に出力する。初期状態では5ビット値は00hであるので、出力する8ビット値は80hである。

【0131】

乗算部513は、テーブルレジスタ510からの8ビット値(80h)と、テーブルレジスタ511からの8ビット値(80h)とを乗算して、乗算結果である16ビット値(4000h)を演算処理部805に出力する。

比較部514からの出力値(演算命令)が010bであるため、19bitレジスタ値60000hを保持する。

【0132】

次に転写バイアスを印加するために、プリンタエンジン制御部204は、高圧制御部206に出力するON信号312sを「High」に設定する。これにより、高圧制御部206の出力セレクタ部528と、比較部514と、3ビットカウンタ部551とにON信号312sが「High」で入力される。

【0133】

ON信号312sが「High」で入力された比較部514は、Dラッチ部507の9ビットカウンタ値と、19ビット保持部806の上位9bit(bit18〜bit10)とを比較判定して、比較判定結果に応じて演算命令「000b」〜「100b」のいずれか一つを演算処理部805に出力する。そして、演算処理部805は、演算指示部517からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)で、比較部514からの演算命令に従って、19ビット保持部806が記憶する19ビット値に演算を行う。

【0134】

また、ON信号312sが「High」で入力された3ビットカウンタ部551は、3ビット値をシフト演算部550に出力する。初期状態では3ビットカウンタ部551の3ビット値は000bであり、シフト演算部550にも000bが出力される。

【0135】

また、ON信号312sが「High」で入力された出力セレクタ部528はパルス(駆動周波数)を出力する。これにより、圧電トランス駆動回路303が駆動して、高圧出力が徐々に立ち上がる。

そして、出力セレクタ部528が出力したパルスがDラッチ部507にも入力され、Dラッチ部507は、パルスの立ち上がりエッジのタイミングで、9ビットカウンタ部506の9ビット値をラッチして、比較部514に出力される。

【0136】

ここで、出力セレクタ部528がパルスを出力した直後の高圧出力は0V付近である。そのため、Dラッチ部507は、第一電圧比較手段308(図3)が出力する「High」レベルを9ビットカウンタ部506がカウントした値、すなわち19ビット保持部806の上位9bitに近い値を保持することとなる。そのため、比較部514は、比較判定した結果の演算命令「000b」を演算処理部805に出力する。

そして、演算処理部805は、演算命令「000b」に従って、乗算部513が出力する16ビット値を19ビット保持部806の値に加算する。

【0137】

これにより、パルス出力の周波数が下がり、高圧の出力電圧が上昇する。出力電圧上昇に伴い、第二電圧比較手段309(図3)が出力する163.8μsec周期のPWM波形のデューティが減少し、Dラッチ部505が保持する5ビット値が初期値の1Fhから1Eh,1Dh,1Ch,・・・と減少する。また、19ビット保持部806の19ビット値が加算されることで、テーブルレジスタ511に出力される7ビット値も00h,01h,02h,・・・と増加する。

【0138】

本実施例の圧電トランスの出力電圧の駆動周波数依存特性を図12に示す。駆動開始直後の周波数である130kHzから120kHzまでは周波数変化に対する電圧変化は少なく、110kHzに近づくと急峻に増加する特性を示す。このような特性から駆動開始直後の周波数付近では、図9のテーブルレジスタ511の出力値に示すように、駆動周波数を決定する19ビット保持部806更新時の加算量を大きくしている。

【0139】

テーブルレジスタ552(図10)の入力値(7ビット値)が00hであるところは、19ビット保持部806の上位9bitが180hであり、駆動周波数が130.2kHzであり、出力値(8ビット値)が80hである。

また、テーブルレジスタ552(図10)の入力値(7ビット値)が47hであるところは、19ビット保持部806の上位9bitが1C7hであり、駆動周波数が109.7kHzであり、出力値(8ビット値)が00hである。

周波数によって単位周波数変化辺りの出力電圧変化量が異なるために、周波数変化に対して出力電圧変化が小さい領域で19bitレジスタ加算値が大きくなるようにテーブルを設定している。テーブル値は実験により得た値である。

【0140】

また、Dラッチ部505の5ビット値は、初期値の1Fhから目標電圧に近づくに従って減少し、目標電圧において10hとなる。図8のテーブルレジスタ510入出力値に示す通りである。これにより目標電圧から離れている状態では周波数制御値の変化量を大きくし、目標電圧付近では変化量を小さくする。さらに前記テーブルレジスタB値と乗算するので目標電圧到達までの時間を短縮し、かつ目標電圧到達時のオーバーシュートを防ぐことが可能となる。本実施例ではDラッチBの分解能を5bitとしてあるが、この値に限らず、もっと分解能を高めて多くのテーブル値を保持してもよい。

【0141】

駆動周波数を順次下げる方向に制御していくとDラッチB出力値が10hとなり、第一電圧比較手段308の出力が矩形波となり、結果、Dラッチ部507保持値が下記2条件いずれかとなる。

【0142】

この状態で19ビット保持部806を1ずつ加算または減算して制御することにより目標電圧である7000Vの定電圧制御が行われる。また演算処理部805での演算結果の上位9bitがカウンタ上限値記憶部519に設定され、その9ビット値が1CFhを超えた場合、19ビット保持部806の上位9bitを「1CEh」に更新する。それによって共振周波数を超えて低い周波数に制御されることがなくなる。

【0143】

そして、用紙の後端が感光体ドラム109(図1)と転写ローラ111(図1)とのニップ部を通過する直前に、プリンタエンジン制御部204はON信号312sを「High」から「Low」に遷移して高圧制御部206に出力する。これにより、バイアスをオフする。このとき、DAC311の出力値は、先に設定された目標電圧に対応した出力値を保持する。比較部514へのON信号312s入力が「Low」となるので、比較部514は010bの出力値(3ビット値)を演算処理部805に出力する。それによって、演算処理部805は、19ビット保持部806の値を更新せずに保持する。その結果、パルス生成部527は、出力オフ直前の駆動周波数のパルス出力を保持し続ける。図13及び図14で示すように無負荷では7000V出力での19ビット保持部806の値は73535hであり、150MΩの負荷がある場合、19ビット保持部806の値は73A26hである。電流値はそれぞれ0A、55μAであり、転写時は数μA〜十数μAの転写電流が流れるので19ビット保持部806値は73535〜73A26hの間となる。また、上位9bitについて言えば、1CDもしくは1CEhとなる。

【0144】

次の用紙、すなわち2枚目の用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204はON信号312sを「Low」から「High」に遷移して高圧制御部206に出力する。高圧制御部206は、前記説明した1枚目の印刷時とほぼ同様の処理を行うが、19ビット保持部806の値が異なることにより若干処理が異なるため、以下に説明する。

【0145】

19ビット保持部806は、1枚目を印刷した7000V出力時の駆動周波数相当の分周比値19ビット値を保持している。そして、19ビット保持部806の7ビット値(bit16〜bit10)がテーブルレジスタ552に入力される。テーブルレジスタ552は、上位9bitが前記説明したように1CDhもしくは1CEhであるので、7ビット値は4Dhもしくは4Fhである。図10で示すように、これら7ビット値の入力に対して、いずれの場合においても、110bの3ビット値を3ビットカウンタ部551に出力する。

【0146】

3ビットカウンタ部551はそれまで000bを保持しており、プリンタエンジン制御部204がON信号312sを「Low」から「High」に遷移して高圧制御部206に出力したときに、テーブルレジスタ552の値をラッチする(保持する)。3ビットカウンタ部551は、演算指示部517の出力パルスの立ち上がりエッジのタイミングで、3ビット値を減算してシフト演算部550に出力する。シフト演算部550は、周期値記憶部516の13ビット値(1B58h(=7000))を、3ビットカウンタ部551の値分の左シフトを行い、演算指示部517に出力する。例えば、3ビットカウンタ部551の値が110bの場合、6bit分の左シフトを行う。

【0147】

図17に、演算指示部517が演算指示信号を出力するタイミングチャートを示す。演算指示部517は、140μsecの64倍(8.96msec)を第1周期としてパルスの出力を開始し、パルスを出力する毎に半分の周期でパルスが出力される。第1周期目は8.96msec、第2周期目は4.48msec、第3周期目は2.24msec、第4周期目は1.12msec、第5周期目は0.56msec、第6周期目は0.28msecと、演算指示部517がパルスを出力する周期が変わる。

【0148】

図15に駆動周波数108.46kHz、すなわち19ビット保持部806の値が73400hの場合の同一周波数駆動での立ち上がり特性を示す。この特性は概ね7000Vでの立ち上がりと等しい。この特性から立ち上がりから出力立ち上がりは概ね20msec程度であることが読み取れる。8.96msec、4.48msec、2.24msec、1.12msec、0.56msec、0.28msecと制御周期が長くなる間の合計時間は約18msecであり、この時間でほぼ目標電圧付近となっている。また、目標電圧に対する割合としては8.96msecで75%程度、次の4.48msec後にはほぼ目標電圧に近く90%を超えている。よって前回の駆動周波数にて立ち上げた場合に、75%程度でDラッチ部505からの入力値(5ビット値)は0Chであり、テーブルレジスタ510の出力値は06hである(図8)。また、テーブルレジスタ511の値は01hとなるので、圧電トランス304(図3)の出力電圧が駆動周波数に対して安定するまでに、駆動周波数に加算される数は10〜20hである。図13)及び図14から明らかなように、40V単位の出力変化に対する値の半分程度である。

そして、出力オンから17.64msec以降は0Vから立ち上げる場合同様、140μsec周期にて制御が行われるので、直ちに目標電圧値に収束する。

【0149】

図15及び図16から明らかなように、駆動周波数によって立ち上がり時間が変化する。この駆動周波数に対する立ち上がり時間の変化分を調整するため、テーブルレジスタ552を用いて、前記制御周期を8.96、4.48、2.24、1.12、0.56、0.28、0.14msec周期それぞれからスタートできるようにしてある。ここで、3ビット値が110bであれば、8.96msec周期からスタートし、また、3ビット値が100bであれば、2.24msecからスタートする。

【0150】

指定枚数の用紙の印刷が終了後、プリンタエンジン制御部204は、RESET信号313sを高圧制御部206に出力し、最終印字時のバイアス保持値をクリアする。

【0151】

以上説明したように、2枚目以降の印字にて前回の転写バイアス印加時の駆動周波数を用いることにより、同じ出力を得たい場合に、用紙先端の負荷が短時間に極度に変動する部分の影響を受けず、スムーズに早い立ち上げ制御が可能となる。

【0152】

《第2の実施形態》

図18は、第2の実施形態の高圧電源装置のブロック図であり、図19は、図18の構成図について、高圧電源装置301Aを中心として詳細に説明する回路図である。

図18及び図19に示すように、第2の実施形態における高圧電源装置301Aは、プリンタエンジン制御部204AがPre信号1500s及びHold信号1501sを、高圧制御部206Aに出力する点で、第1の実施形態における高圧電源装置301と異なる。これ以外は、第1の実施形態における高圧電源装置301が備える構成と同じであるため、処理の説明を省略する。

【0153】

プリンタエンジン制御部204Aは、連続印字時の用紙間(転写ローラを用紙の後端が通過してから、転写ローラに次の用紙の先端が到達するまでの時間)に、Pre信号1500sを「High」で高圧制御部206Aに出力する。そして、それ以外の時には、Pre信号1500sを「Low」で高圧制御部206Aに出力する。

また、プリンタエンジン制御部204Aは、1枚目を印字する前にプレバイアスの設定を行ってからプレバイアスを印加させる制御を高圧制御部206Aに行う。これにより、転写バイアス発生部209は、転写ローラ111K、111Y、111M、111Cにプレバイアスを印加する。転写バイアス発生部209がそのプレバイアスで立ち上がった後(駆動後)、プリンタエンジン制御部204Aは、次に印字バイアスを設定する前に、プレバイアス印加時の駆動周波数を記憶させるべくHold信号(「Low」から「High」への立ち上がりエッジを持つパルス信号)を高圧制御部206Aに出力する。高圧制御部206Aは、このHold信号の「Low」から「High」への立ち上がりエッジトリガで処理を実行する。

【0154】

図20は、図18における高圧制御部のブロック図である。図中で、図18及び図19と同じ構成要素には同じ符号を付している。第2の実施形態における高圧制御部206Aは、Dラッチ部1502と、分周部1503と、第二出力セレクタ部1504とを備える。図21は、第2の実施形態の高圧電源装置301Aが電圧を印加する負荷306に対する特性を示し、(A)は無負荷時(負荷306)の特性を示し、(B)は100MΩの負荷をショートしたときの特性を示す。

【0155】

Dラッチ部1502は、Hold信号1501sの値に応じて、出力値を選択して分周部1503に出力する。Dラッチ部1502は、Hold信号1501sが「Low」の場合、カウンタ下限値記憶部520から9ビット値を取得して分周部1503に出力する。一方、Hold信号1501sが「High」の場合、19ビット保持部806から上位9ビット値を取得して分周部1503に出力する。

【0156】

分周部1503は、Dラッチ部1502から出力される9ビット値の周波数のパルスをデューティ比30%で生成し、パルスを第二出力セレクタ部1504に出力する。

【0157】

第二出力セレクタ部1504は、Pre信号1500sの値に応じて、出力信号を選択して出力端子314(OUT1)に出力する。Pre信号1500sが「Low」の場合、出力セレクタ部528から入力されるパルスをそのまま出力端子314(OUT1)に出力する。一方、Pre信号1500sが「High」の場合、分周部1503から入力されるパルスをそのまま出力端子314(OUT1)に出力する。

【0158】

(実施例2の動作説明)

動作については、実施例1と異なる部分のみ説明する。

図22は本実施例2を説明するタイミングチャートである。転写媒体に対する転写バイアス印加についてはON信号312sの出力(「High」または「Low」)に同期するが、DAC311に、プレバイアス設定と印字バイアス設定との2段階の設定を行ってから、プレバイアスを印加する点で異なる。実施例1では印字バイアスのDAC311を設定した直後に、プリンタエンジン制御部204Aは、ON信号312sを「High」としていたが、それより前のタイミングにてプレバイアスのDAC311設定に続いてON信号312sをオンしている。この部分を除けば転写媒体に印加する転写バイアスの印加、特に2枚目以降のバイアス印加については実施例1と同じ制御となっている。

【0159】

本実施例では実施例1に対して、プレバイアスを印加し、かつそのプレバイアス時の駆動周波数を保持して、以降の紙間バイアスを保持した分周比値から駆動を開始する。実施例1では1枚目の印字バイアスの駆動周波数を保持したが、実施例2では前記印字バイアスに追加してプレバイアスの駆動周波数を保持し、その周波数で紙間バイアスを印加する。まず、印刷用紙が転写ニップに到達するより以前、かつ転写ベルト114が転写ベルト駆動ローラ112で駆動された後の所定のタイミングにてプリンタエンジン制御部204AはDAC311にプレバイアスに相当するDAC311設定値を送信する。

例えば、プレバイアスを1000Vとした場合に、0.47V、10bit値で092hを設定する。続いてON信号312sが「High」となり、実施例1で説明したと同様な制御で1000Vが印加される。

【0160】

感光体ドラム109(図1)と転写ベルト114(図1)が駆動され、用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204Aは、印刷バイアス相当のDAC値をDAC311に出力して設定する。DAC311設定のシリアル通信速度はμsecオーダであるので、十分タイミングの同期を取ることは可能である。このDAC311設定に先立って図22で示すようにHold信号1501sを「Low」から「High」に設定する。Pre信号1500sは初期状態で「Low」であり、1枚目の印字時は「Low」を出力し続ける。

【0161】

図20に高圧制御部206Aの内部回路ブロックを示す。Dラッチ部1502は、初期値としてカウンタ下限値記憶部520から取得した9ビット値(初期値180h)を保持する。ここで、Hold信号1501sが「Low」から「High」となると、Dラッチ部1502は、19ビット保持部806の上位9bitを取得して、9ビット値とする(更新する)。このとき、1000V出力にて圧電トランスは駆動されているので、図21に示す特性から駆動周波数の分周比値は1C0〜1C2hの値の範囲となる。

【0162】

Dラッチ部1502が保持する値は、分周部1503で分周され、30%デューティの約1000Vのパルスとなり、第二出力セレクタ部1504に出力される。ただし、このときPre信号1500sは「Low」であるので、駆動パルスはパルス生成部527により出力が選択され、出力される。

【0163】

そして、図22のタイミングチャートで示されるように、プリンタエンジン制御部204Aは、ON信号312sを「Low」で出力すると共に、Pre信号1500sを「High」で出力する。これにより、第二出力セレクタ部1504から出力される駆動周波数が、分周部1503から出力される値に切り替わり、約1000Vが出力される。

ここで、図21で示される特性から分かるように、9bitの分解能では出力精度が±100V程度生じるが、画像形成のバイアスでないので十分許容値である。また固定周波数で駆動するので制御によるリップル、すなわち出力電圧が制御によって±100V近いリップルを発生することもない。

【0164】

以降、転写媒体へのバイアス印加時のON信号312sを「High」で出力する立ち上げるタイミングで、Pre信号1500sを「Low」で出力する。これにより、前回の出力時(転写バイアス時)に保持された駆動周波数と、プレバイアス印加時に保持された駆動周波数とで、駆動制御が行われる。

指定枚数の用紙の印刷が終了後、プリンタエンジン制御部204Aは、ON信号312s、Hold信号1501s及びPre信号1500sを共に「Low」で高圧制御部206Aに出力し、最終印字時のバイアス保持値をクリアする。

【0165】

《第3の実施形態》

(構成の説明)

図23は、本発明の第3の実施形態である画像形成装置の全体構成図である。図23において、画像形成装置101Bは、第1の実施形態における画像形成装置101(図1参照)に、用紙ガイド2121と、搬送ローラ対2122,2123,2124,2125とをさらに備えるものである。搬送ローラ対2122は、第1の実施形態における画像形成装置101が備える排出ローラ126,127に、逆回転する機能を備えたものである。これにより、排出ローラ126、127(搬送ローラ対2122)が逆回転することによって、用紙ガイド128に沿って搬送する用紙は、用紙ガイド2121に搬送され、さらに搬送ローラ対2123,2124,2125により、用紙ガイド119に搬送される。これにより、媒体(用紙)の表面にトナー画像が転写された後、媒体の裏面にトナー画像を転写することができる。つまり、第3の実施形態における画像形成装置101Bは両面印刷機能を有する装置である。

【0166】

図24は、第3の実施形態の高圧電源装置のブロック図である。

図24に示すように、第3の実施形態における高圧電源装置301Bは、プリンタエンジン制御部204BがOdd信号2502sを、高圧制御部206Bに出力する点で、第2の実施形態における高圧電源装置301Aと異なる。これ以外は、第2の実施形態における高圧電源装置301Aが備える構成と同じであるため、処理の説明を省略する。

【0167】

プリンタエンジン制御部204Bは、1面目(表面)の印刷を行う場合、Odd信号2502sを「High」で高圧制御部206Bに出力する。そして、2面目(裏面)の印刷を行う場合、Odd信号2502sを「Low」で高圧制御部206Bに出力する。

【0168】

図25は、図24における高圧制御部のブロック図である。図中で、図24と同じ構成要素には同じ符号を付している。第2の実施形態における高圧制御部206Aは、表裏セレクタ部2522と、下位10ビットセレクタ部2524と、表面用の19ビット保持部8061と、裏面用の19ビット保持部8062と、9ビットセレクタ部2523と、遅延部2517とを備える。

また、第3の実施形態におけるDラッチ部1502は、分周部1503に出力するだけでなく、さらに19ビット保持部8062(裏面)に出力する。

【0169】

表裏セレクタ部2522は、演算処理部805から入力された19ビット値を、Odd信号2502sの入力に応じて、19ビット保持部8061(表面)または19ビット保持部8062(裏面)に出力する。このとき、表裏セレクタ部2522は、Odd信号2502sからの入力値が「High」であれば、19ビット保持部8061(表面)に出力し、「Low」であれば、19ビット保持部8062(裏面)に出力する。

【0170】

下位10ビットセレクタ部2524は、Odd信号2502sの入力に応じて、19ビット保持部8061(表面)から入力される値と、19ビット保持部8062(裏面)から入力される値とのどちらか一方を誤差保持部529に出力する。このとき、表裏セレクタ部2522は、Odd信号2502sからの入力値が「High」であれば、19ビット保持部8061(表面)から入力される値を出力し、「Low」であれば、19ビット保持部8062(裏面)から入力される値を出力する。

【0171】

9ビットセレクタ部2523は、Odd信号2502sの入力に応じて、19ビット保持部8061(表面)から入力される値(上位9ビット値)と、19ビット保持部8062(裏面)から入力される値(上位9ビット値)とのどちらか一方を、比較部514、加算部525、分周セレクタ部526に出力する。このとき、表裏セレクタ部2522は、Odd信号2502sからの入力値が「High」であれば、19ビット保持部8061(表面)から入力される値を出力し、「Low」であれば、19ビット保持部8062(裏面)から入力される値を出力する。

【0172】

19ビット保持部8061(表面)及び19ビット保持部8062(裏面)は、第2の実施形態における19ビット保持部806と同様に、19ビットの値を記憶するレジスタである。

19ビット保持部8061(表面)及び19ビット保持部8062(裏面)は、保持する19ビットの値のうち、上位9ビット値が、9ビットセレクタ部2523を介して、比較部514、加算部525、分周セレクタ部526に出力され、下位10ビット値が、下位10ビットセレクタ部2524を介して、誤差保持部529に出力される。

さらに、19ビット保持部8062(裏面)は、遅延部2517からの入力に応じて、保持する19ビットの値を出力するタイミングを変える。また、19ビット保持部8062(裏面)は、Dラッチ部1502から入力される9ビット値で上位9bit値を更新する。

【0173】

遅延部2517は、Hold信号1501sからの入力を遅らせて、19ビット保持部8062(裏面)に出力する。

ここで、Dラッチ部1502は、Hold信号1501sの値に応じて、出力値を選択して分周部1503及び19ビット保持部8062(裏面)に出力する。

遅延した出力は、Dラッチ部1502がHold信号1501sにより9ビットセレクタ部2523出力をラッチするまでの間を遅延させ、Dラッチ部1502出力を19ビット保持部8062の上位9bit値としてセットする。初期値としてリセット時にオール0となるので下位10bitは000hである。

【0174】

(実施例3の動作説明)

動作については、実施例1及び実施例2と異なる部分のみ説明する。

図26は本実施例のタイミングチャートを説明する図である。本実施例は両面印刷でのタイミングを説明する。

両面印刷の場合、表面(1面目)の印刷バイアスより裏面(2面目)の印刷バイアスが高くなるため、DAC311には、表面と裏面とで異なる設定値が予め設定されている。

【0175】

図26に示すように、DAC311の設定を紙間で表面用の設定値と裏面用の設定値とで交互に切り替えることでそれに対応可能となる。

実施例2と同様に、(表面の)印刷終了後の紙間バイアス印加時にOdd信号2502sを「Low」とすることにより、19ビット保持部8062(裏面)には紙間バイアス印加時の分周比値が設定される。

【0176】

さらに裏面の印刷バイアスに相当するDAC311の設定値を紙間バイアス印加中に設定し、Odd信号2502sを「Low」とすることで次にON信号312sを「High」とすると19ビット保持部8062(裏面)の値が制御され、演算指示部517出力パルスは140μsec周期のまま裏面の印刷バイアス立ち上げが行われる。

【0177】

次の紙間で2枚目の印字に対する表面の印刷バイアスに相当するDAC311設定値が設定され、Odd信号2502sが「High」とされる。ON信号312sが2枚目にて「High」となる時は、1枚目の表面バイアス印加時に19ビット保持部8061(表面)に保持された値にて駆動が開始される。さらに次の紙間で裏面の印刷バイアスに相当するDAC311設定値が設定され、Odd信号2502sが「Low」に切り替えられ、1枚目の裏面バイアス印加時に19ビット保持部8062(裏面)に保持された値にて駆動が開始される。

【0178】

以降、Odd信号2502sとDAC311出力を紙間バイアス印加中に交互に切り替えることによりそれぞれ前の表面及び裏面の印刷バイアス駆動周波数で圧電トランスが駆動される。

最終印字終了後にHold信号1501s、Pre信号1500s、ON信号312sが「Low」にされ、Odd信号2502sが「High」とされ、リセット信号を一旦「Low」とすることで高圧制御部206Bの内部設定を初期化して次回の印刷に備える。

【0179】

ここで、プリンタエンジン制御部204Bは、Odd信号2502sの出力を「High」で固定することで、実施例2と同様に、片面印刷も実現可能である。

【0180】

本実施例では連続印刷中のみ保持するようにしたが、環境温度センサを設けて同一環境中は前回の印刷時に保持された値を利用することも容易であるし、時間計測手段によって所定時間内は連続印刷と同じ条件で制御することも可能である。

【0181】

本実施形態において、共振周波数約108kHz、駆動周波数範囲108〜130kHzの圧電トランスを用いたが、それよりサイズの小さい駆動周波数が高い圧電トランスを使用してもよいし、サイズの大きな駆動周波数の低い圧電トランスを用いてもよい。

【0182】

また、本実施形態において、CLK端子420(CLK_IN)に入力されるCLK信号420s(クロック信号)の周波数50MHzとしたが、25MHzなどの低い周波数でも実現可能である。例えば、その場合には19bitレジスタの上位8bitを整数部とし、下位11bitを小数部にすればほぼ同じ値にて制御も実現可能となる。

【0183】

また、本実施形態において、整数部9bit、小数部10bitで処理を行っているが、bit数についてはこの限りではない。

【0184】

また、本実施形態において、転写バイアス1chの場合について説明したが、他の高圧出力への応用も容易に実現可能である。

【0185】

また、本実施形態において、出力最大電圧は7kVとしているが、この電圧はダイオードの耐圧などにより決定した値であって、部品選定次第では10kVなどの高い出力電圧の高圧電源も容易に実現可能である。

【0186】

また、本実施形態において、転写バイアス7000Vで説明したが、説明のために最大出力電圧となる値としただけであり、転写バイアスは120〜7000Vの間の任意の値でよい。

【0187】

また、第1の実施形態において、三角波を負荷電圧と比較して、パルス幅に対応する周波数変化量をテーブルレジスタ511で非線形特性に修正したが、三角波を非線形に補正し、補正した非線形三角波と負荷電圧とを比較してもよい。

【符号の説明】

【0188】

101 画像形成装置

204 プリンタエンジン制御部

206 高圧制御部(ASIC)

209 転写バイアス発生部

301 高圧電源装置

302 DC電源

303 圧電トランス駆動回路

304 圧電トランス

305 整流回路

306 出力負荷

307 出力電圧変換手段

308 第一電圧比較手段(コンパレータ)

309 第二電圧比較手段(コンパレータ)

310 三角波発生手段

311 DAC

312 ON端子

312s ON信号

313 RESET端子

313s RESET信号

314 出力端子(OUT1)

315 入力端子(IN1)

316 入力端子(IN2)

317 出力端子(OUT2)

【技術分野】

【0001】

本発明は、圧電トランスを用いて昇圧する電源装置、及びこれを用いた画像形成装置に関する。

【背景技術】

【0002】

電子写真方式の画像形成装置は、高圧電源装置を内蔵しており、この高圧電源装置が、帯電ローラを介して感光体ドラムを帯電し、現像ローラ、供給ローラや転写ローラに所定のバイアス電圧を印加してトナーを感光体ドラムに移動させたり、媒体にトナー画像を転写させたりしている。

【0003】

また、高圧電源装置として、圧電トランスを用いて、出力電圧が目標電圧になるように定電圧制御する技術が開示されている(特許文献1参照)。圧電トランスは、駆動周波数を可変することで容易に出力電圧を可変することができるものである。圧電トランスは、駆動周波数に応じて出力電圧が変化するものであり、この駆動電圧を電圧制御発振器(VCO)で発生させていた。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006−91757号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、一般に圧電トランスは、共振周波数において出力電圧が最大となるような“裾広がり”な特性をしており、圧電トランスの出力電圧を増加させる場合は、この圧電トランスの駆動周波数を高い方から低い方へ変化させることで可能となる。

しかしながら、一般的な電圧制御発振器などを用いた回路では、目標電圧に近い高い出力電圧を利用しようとした場合に、圧電トランスによる共振周波数のバラツキの影響で、共振周波数を超えて低い周波数で制御してしまう場合があった。

また、目標電圧に近い、高い出力電圧に設定した後で、改めて、圧電トランスの出力電圧を制御して、目標電圧に近づけるという2段階の電圧制御を行っていたため、短時間で目標電圧に定電圧制御することが困難であるという問題があった。

【0006】

そこで、本発明は、短時間で目標電圧に近い高い電圧を出力することができる電源装置、及びこれを用いた画像形成装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

前記目的を達成するため、本発明の電源装置は、駆動周波数に対応して出力電圧が変化する圧電トランス(304)を用いた電源装置(高圧電源装置301)であって、前記出力電圧と目標電圧とが一致するように、前記駆動周波数を帰還制御する帰還制御回路(307,308)と、前記出力電圧と前記目標電圧との差分値が小さいとき、前記駆動周波数の変化量を小さくし、前記差分値が大きいとき、前記駆動周波数の変化量を大きく設定する駆動周波数設定手段(206)と、を備えることを特徴とする。なお、( )内の符号や記号は例示である。

【0008】

これによれば、出力電圧と目標電圧との差分値が大きいとき、駆動周波数が大きく変化するので、早く、出力電圧が目標電圧に近づく。そして、出力電圧と目標電圧との差分値が小さくなったとき、駆動周波数が小さく変化するので、出力電圧が目標電圧を飛び超える可能性が少なくなる。

また、目標電圧に近い高い電圧を出力した際の駆動周波数を記憶し、次回、その駆動周波数を用いることで、いち早く目標電圧に近づける電圧制御を行うことができる。

【0009】

また、振幅が前記目標電圧の2倍の三角波信号を生成する三角波生成回路と、前記三角波信号の中間値と前記出力電圧の分圧値とを比較してパルス幅を計測することにより、前記差分値と方向とを推測することができる。推測した推測差分値と変化量との関係が規定されている変化量設定テーブル(テーブルレジスタ510)とを用いて、推測差分値から駆動周波数の変化量を演算することができる。また、圧電トランスの駆動周波数−電圧特性(非線形特性)を規定する特性テーブル(テーブルレジスタ511)を用いて、駆動周波数または出力電圧の分圧値から駆動周波数の変化量を補正することができる。

【発明の効果】

【0010】

本発明によれば、短時間で目標電圧に近い高い電圧を出力することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の第1の実施形態の画像形成装置の全体構成図である。

【図2】本発明の第1の実施形態の画像形成装置を制御する制御回路及びその周辺部品の構成図である。

【図3】本発明の第1の実施形態の高圧電源装置のブロック図である。

【図4】本発明の第1の実施形態の高圧電源装置を中心として詳細に説明する回路図である。

【図5】圧電トランス304の二次側の出力特性を示す模式図である。

【図6】第1チャネル〜第4チャネルの出力端子から出力される信号の波形と、抵抗器に入力される電圧値の変化と、三角波発生手段から出力される波形とを示す図である。

【図7】本発明の第1の実施形態の高圧制御部のブロック図である。

【図8】テーブルレジスタ510が備えるテーブルの一例である。

【図9】テーブルレジスタ511が備えるテーブルの一例である。

【図10】テーブルレジスタ552が備えるテーブルの一例である。

【図11】出力端子(OUT1)の出力波形と、圧電トランス駆動回路の出力波形と、出力電圧変換手段の出力波形と、三角波発生回路の出力波形と、DACの出力波形と、第一電圧比較手段の出力波形と、第二電圧比較手段の出力波形とを示す図である。

【図12】出力電圧の駆動周波数依存性を示す図である。

【図13】無負荷時の出力電圧と駆動周波数との関係を示す図である。

【図14】150MΩ負荷時の出力電圧と駆動周波数との関係を示す図である。

【図15】駆動周波数108.46Hzの立ち上がり特性を示す図である。

【図16】駆動周波数111.61Hzの立ち上がり特性を示す図である。

【図17】演算指示部が出力する演算指示信号と、プリンタエンジン制御部が出力するON信号と、3ビットカウンタ部の3ビット値とを示す図である。

【図18】本発明の第2の実施形態の高圧電源装置のブロック図である。

【図19】本発明の第2の実施形態の高圧電源装置を中心として詳細に説明する回路図である。

【図20】本発明の第2の実施形態の高圧制御部のブロック図である。

【図21】本発明の第2の実施形態の高圧電源装置の出力電圧と分周比値との特性を示すテーブルである。(A)無負荷時特性、(B)ショート時(100MΩ負荷)特性を示す。

【図22】本発明の第2の実施形態における、DACの設定と、ON信号と、Hold信号と、Pre信号と、高圧出力とのタイミングチャートを示す。

【図23】本発明の第3の実施形態である画像形成装置の全体構成図である。

【図24】本発明の第3の実施形態の高圧電源装置のブロック図である。

【図25】本発明の第3の実施形態の高圧制御部のブロック図である。

【図26】本発明の第3の実施形態における、DACの設定と、ON信号と、Hold信号と、Pre信号と、高圧出力とのタイミングチャートを示す。

【発明を実施するための形態】

【0012】

以下、図面を参照して、本発明の実施の形態(以下、「本実施形態」と称する)につき詳細に説明する。なお、各図は、本発明について概略的に示してあるに過ぎない。よって、本発明は、図示例のみに限定されるものではない。また、各図において、共通する構成要素や同様な構成要素については、同一の符号を付し、それらの重複する説明を省略する。

【0013】

《第1の実施形態》

(構成の説明)

図1は、本発明の第1の実施形態である画像形成装置の全体構成図である。図1において、画像形成装置101(101A)は、電子写真方式を用いたタンデムカラー印刷装置であり、4色の現像器102(102K、102Y、102M、102C)と、4つの露光手段としてのLEDヘッド103(103K、103Y、103M、103C)と、転写ローラ111(111K、111Y、111M、111C)と、定着器123と、給紙部としての用紙カセット117と、転写ベルト114を含む搬送部と、スタッカ(排紙トレー)129と、転写ベルトクリーニングブレード115と、転写ベルトクリーナ容器116とを備える。

なお、トナーカートリッジ104(104K、104Y、104M、104C)は、現像器102(102K、102Y、102M、102C)にそれぞれ着脱可能で、内部のトナーを現像器内部に供給可能な構造となっている。

【0014】

現像器102(102K、102Y、102M、102C)は、内部に、像担持体としての感光体ドラム109(109K、109Y、109M、109C)と、帯電手段としての帯電ローラ105(105K、105Y、105M、105C)と、現像剤担持体としての現像ローラ107(107K、107Y、107M、107C)と、現像剤供給手段としての供給ローラ106(106K、106Y、106M、106C)と、薄層形成手段としての現像ブレード108(108K、108Y、108M、108C)と、クリーニングブレード110(110K、110Y、110M、110C)とを備える。なお、図面上は、感光体ドラム109K、帯電ローラ105K、現像ローラ107K、現像ブレード108K、クリーニングブレード110Kのみ示している。また、各ローラは、軸が用紙の搬送方向に垂直であって、搬送面に平行となる方向に配設されている。

【0015】

感光体ドラム109は、帯電ローラ105によって、一様に負極に帯電される。帯電された感光体ドラム109は、LEDヘッド103の発光・照射によって、照射部が放電され、静電潜像が形成される。例えば、感光体ドラム109は、−600Vの帯電電位から−40Vに放電される。

【0016】

一方、供給ローラ106は、負のバイアス電圧(例えば、−300V)が印加されており、トナーカートリッジ104内部の現像剤としてのトナーを帯電させ、帯電したトナーを現像ローラ107に供給する。現像ブレード108は、現像ローラ107に供給されたトナーを薄層化し、現像ローラ107の表面に一様なトナー層を形成する。現像ローラ107は、負のバイアス電圧(例えば、−200V)が印加されており、電界の作用により、負に帯電されたトナーを静電潜像に移動させる。感光体ドラム109は、現像ローラ107からトナーが移動することにより、静電潜像がトナー像(現像剤像)として現像される。クリーニングブレード110は、転写後の残トナーをクリーニングする機構である。

【0017】

転写ローラ111(111K、111Y、111M、111C)は、転写ベルト114裏面から転写位置にバイアス電圧が印加可能に配置される。転写ベルト駆動ローラ112、転写ベルト従動ローラ113は、転写ベルト114を張架し、ローラの駆動によって用紙を搬送可能となっている。また、転写ローラ111は、正のバイアス電圧(例えば、+2500V)が印加されており、感光体ドラム109の表面に形成され、負に帯電されたトナー画像を媒体に転写する。

【0018】

転写ベルトクリーニングブレード115は、転写ベルト114上のトナーを掻き落とせるようになっていて、転写ベルトクリーナ容器116には、転写ベルトクリーニングブレード115により掻き落とされたトナーが収容される。

【0019】

用紙カセット117は、画像形成装置101に着脱可能に取り付けられ用紙が積載される。給紙ローラ118は、転写媒体である用紙を用紙カセット117から給紙し、用紙ガイド119に沿って搬送する。レジストローラ120、121は、停止状態のところに用紙を突き当て、スキュー補正後に所定タイミングでレジストローラ120、121を駆動し、転写ベルト114に用紙を搬送する。用紙検出センサ122は、接触又は非接触で用紙の通過を検知する。

【0020】

定着器123は、加熱部材124、及び圧着部材125を備え、加熱部材124は、サーミスタ216及び定着器ヒータ217(図2)を備え、用紙上に転写されたトナー像を熱と加圧によって用紙に定着する。なお、加熱部材124、及び圧着部材125は、互いに圧接させられ、ニップ部が形成されている。画像形成装置101は、排出ローラ126、127によって用紙ガイド128に沿って用紙を搬送し、排紙トレー129にフェースダウンで排出する。

【0021】

図2は、本発明の第1の実施形態である画像形成装置を制御する制御回路、及びその周辺部品の構成図である。図2において、画像形成装置101は、前記したLEDヘッド103(103K、103Y、103M、103C)と、現像器102(102K、102Y、102M、102C)と、転写ローラ111(111K、111Y、111M、111C)と、定着器123とを備え、さらにホストインタフェース部201と、給紙モータ210と、搬送モータ211と、転写ベルト駆動モータ212と、定着器駆動モータ213と、感光体ドラム駆動モータ214と、記憶部215と、用紙検出センサ122と、これらを全体制御する制御回路200とを備える。

【0022】

制御回路200は、ホストインタフェース部201から入力される印刷データをコマンド/画像データに変換処理するコマンド/画像処理部202と、各モータ(210,211,212,213,214)を駆動するモータ制御部205と、LEDヘッド103(103K、103Y、103M、103C)を駆動するLEDヘッドインタフェース部203と、帯電ローラ105(105K,105Y,105M,105C)にバイアス電圧を印加する帯電バイアス発生部207と、供給ローラ106(106K,106Y,106M、106C)、及び現像ローラ107(107K,107Y,107M、107C)にバイアス電圧を印加する現像/供給バイアス発生部208と、転写ローラ111(111K、111Y、111M、111C)にバイアス電圧を印加する転写バイアス発生部209と、帯電バイアス発生部207、現像/供給バイアス発生部208、及び転写バイアス発生部209を制御する駆動周波数設定手段としての高圧制御部206と、コマンド/画像処理部202、モータ制御部205、LEDヘッドインタフェース部203、及び高圧制御部206を制御するプリンタエンジン制御部204とを備える。

【0023】

ホストインタフェース部201は、外部機器(ホスト)から送信される印刷データ(例えば、コマンドデータ、文書データ、画像データ)を受信し、印刷データをコマンド/画像処理部202に送信する。コマンド/画像処理部202は、ホストインタフェース部201から印刷データを受信し、ページ記述言語で記述された印刷データを画像データ(ビットマップデータ)に変換し、LEDヘッドインタフェース部203に画像データを送る。

【0024】

LEDヘッドインタフェース部203は、プリンタエンジン制御部204によってヘッド駆動パルス等が同期制御され、コマンド/画像処理部202が出力する画像データを用いてLEDヘッド103K、103Y、103M、103Cを発光させる。

【0025】

プリンタエンジン制御部204は、コマンド/画像処理部202から入力された印刷データや画像データを記憶部215に一時的に格納する。また、プリンタエンジン制御部204は、各モータ(210,211,212,213,214)を制御するモータ制御値を演算すると共に、帯電ローラ105K、105Y、105M、105C、供給ローラ106K、106Y、106M、106C、現像ローラ107K、107Y、107M、107C、転写ローラ111K、111Y、111M、111Cに印加する、それぞれのバイアス電圧を演算する。

【0026】

プリンタエンジン制御部204は、高圧制御部206に帯電バイアス、現像バイアス、転写バイアス等のバイアス電圧値データを送り、高圧制御部206は帯電バイアス発生部207、現像/供給バイアス発生部208、転写バイアス発生部209に制御信号を送る。

そして、帯電バイアス発生部207、現像/供給バイアス発生部208は、それぞれブラック現像器102K、イエロー現像器102Y、マゼンタ現像器102M、シアン現像器102Cの帯電ローラ105K、105Y、105M、105C、供給ローラ106K、106Y、106M、106C、現像ローラ107K、107Y、107M、107Cにバイアス電圧を印加する。また、転写バイアス発生部209は、転写ローラ111K、111Y、111M、111Cにバイアス電圧を印加する。

【0027】

用紙検出センサ122は、転写バイアスの発生タイミング、及びLEDヘッド103K、103Y、103M、103Cの点灯タイミングを調整するために用いられる。プリンタエンジン制御部204は、給紙モータ210、搬送モータ211、転写ベルト駆動モータ212、定着器駆動モータ213、感光体ドラム駆動モータ(K、Y、M、C各1個ずつ配置)214を所定のタイミングで駆動する。定着器123は、プリンタエンジン制御部204によって、定着器ヒータ217の温度制御がサーミスタ216の検出値に応じて行われる。

【0028】

図3は、第1の実施形態の高圧電源装置のブロック図である。

図3において、高圧電源装置301は、高圧制御部206と転写バイアス発生部209とを有し、プリンタエンジン制御部204、デジタルアナログコンバータ(DAC(Digital Analog Converter))311、及び出力負荷306が接続されている。

高圧制御部206は、圧電トランス駆動信号を出力するためのASIC(Application Specific Integrated Circuit)として構成されている。なお、高圧制御部206は、高圧電源装置内にあるが、プリンタエンジン制御部204のLSI内にあっても構わない。また、本実施形態においては、ASICという呼称を用いているが、マイクロプロセッサ等のCPUを内蔵したものでも実現可能であるし、FPGA(Field Programmable Gate Array)でも実現可能である。

【0029】

転写バイアス発生部209は、DC電源302と、圧電トランス駆動回路303と、圧電トランス304と、整流回路305と、帰還制御手段としての出力電圧変換手段307および第一電圧比較手段308と、差分推測手段としての第二電圧比較手段309と、三角波生成手段としての三角波発生手段310とを備える。整流回路305の出力側と出力電圧変換手段307の入力側とは互いにC点で接続されている。

【0030】

圧電トランス駆動回路303は、スイッチング素子(NチャネルパワーMOSFET402)を用いた駆動回路であり、高圧制御部206から入力されるパルス信号(OUT1パルス)によって、DC電源302が印加する24Vの直流電圧をスイッチングすることにより、後記する圧電トランス304を駆動する。

この圧電トランス駆動回路303は、パルス信号(OUT1パルス)が「High」であれば、インダクタ401に励磁電流を流し、「Low」であれば、その励磁電流をコンデンサ404を介して放電させ、共振電流を流す。

【0031】

圧電トランス304は、セラミック等の圧電振動子の電気−機械変換作用を利用して機械共振させて、さらに機械−電気変換作用により昇圧を行う。これにより、一次側の入力電圧が昇圧されて、二次側から出力される。

整流回路305は、圧電トランス304の二次側交流電圧を直流電圧に整流する整流回路である。

DC電源302は各チャネル共通のDC電源である。

【0032】

出力負荷306は、転写ローラ111K,111Y,111M,111Cを意味し、例えば、転写ローラ印加バイアス電圧を生成(調整)する回路を含む。出力負荷306は、これらの調整されたバイアス電圧によって、高圧電源装置301としての負荷の重さが変動する。以下の本実施例では1回路のみを説明しているが、転写ローラそれぞれに回路を設けて4つ並置して4出力としてもよい。

【0033】

プリンタエンジン制御部204は、入力端子及び出力端子を備え、ON信号312s及びRESET信号313sを高圧制御部206に出力し、SDO信号428s及びSCLK信号429sをDAC311に出力する。

ON信号312sは、高圧電源装置301が負荷306に高電圧を印加するタイミングを提供する。

RESET信号313sは、高圧制御部206をリセットする。

SDO信号428sは、DAC311のシリアルデータ信号であり、SCLK信号429sは、DAC311の同期クロック信号である。

【0034】

高圧制御部206は、出力端子314(OUT1)と、入力端子315(IN1)と、入力端子316(IN2)と、出力端子317(OUT2)と、RESET端子313と、ON端子312とを有する。

出力端子314(OUT1)からは、圧電トランス304の駆動周波数を制御するパルス信号(出力信号)が出力される。パルス信号の周波数は、負荷306に印加される出力電圧に基づいて変えられる。

入力端子315(IN1)には、第一電圧比較手段308から信号(High/Low)が入力される。

入力端子316(IN2)には、第二電圧比較手段309から信号(High/Low)が入力される。

出力端子317(OUT2)からは、セレクタ部503(図7)からパルス(High/Low)が出力される。

RESET端子313には、プリンタエンジン制御部204からRESET信号313sが入力される。

ON端子312には、プリンタエンジン制御部204からON信号312sが入力される。

【0035】

図4は、図3の構成図について、高圧電源装置301を中心として詳細に説明する回路図である。図中で、図3と同じ構成要素には同じ符号を付している。

高圧電源装置301は、高圧回路350(転写バイアス発生部209に該当。なお、帯電バイアス発生部207と現像/供給バイアス発生部208も同じ高圧回路を持つ。)と高圧制御部206とを備え、高圧回路350は、DC電源302と、圧電トランス駆動回路303と、圧電トランス304と、整流回路305と、出力電圧変換手段307と、第一電圧比較手段308と、第二電圧比較手段309と、三角波発生手段310とを有している。

【0036】

圧電トランス駆動回路303は、スイッチング素子(NチャネルパワーMOSFET402)を用いた駆動回路であり、圧電トランス304を駆動する。詳細を後記する。

圧電トランス304は、図中Aで示した部分が一次側の入力端子であり、ここに圧電トランス駆動電圧を印加することにより、昇圧された交流電圧が図中Bで示した二次側から出力される。

整流回路305は、圧電トランス304の二次側交流電圧を負極性の直流電圧に整流する。DC電源302は、24Vの電源であり、図示しない低圧電源装置によって商用電源AC100Vから変圧・整流することによって実現される。

【0037】

発振器(OSC)414は、基準クロック50MHzを生成し、このクロック信号(CLK信号420s)を高圧制御部206に出力する。出力電圧変換手段307は、整流回路305の正負の2次側電圧を抵抗器409,410で分圧して、コンパレータである第一電圧比較手段308及び第二電圧比較手段309を介して、分圧電圧を高圧制御部206の入力端子315(IN1)及び入力端子316(IN2)に入力する。

【0038】

出力負荷306は、高圧電源装置301の正の出力電圧から転写バイアスを印加され、転写ローラの抵抗値および用紙の抵抗値、帯電したトナー量により、負荷が決定される。ここで、出力負荷306は抵抗器408と直列に接続されている。

【0039】

発振器414は、3.3V直流電源413から直流電力が供給され、電源電圧がVDD415、及び出力イネーブル端子OE416に印加される。

発振器414は、GND端子418が接地され、CLK_OUT端子417が抵抗器419を介して高圧制御部206のCLK端子420(CLK_IN)に接続される。

【0040】

高圧制御部206は、CLK端子420(CLK_IN)から入力される、50MHzのクロック信号(CLK信号420s)に同期して動作する。出力端子314(OUT1)は、圧電トランス駆動パルスとして、矩形波信号が出力される。プリンタエンジン制御部204と高圧制御部206とは、2種の信号(RESET信号313s、ON信号312s)を入出力する端子やポートで接続される。

【0041】

圧電トランス駆動回路303は、抵抗器403,480と、NチャネルパワーMOSFET402と、インダクタ401と、コンデンサ404とによって構成される。

【0042】

高圧制御部206が出力する出力端子314(OUT1)は、NチャネルパワーMOSFET402のゲートに入力される。

インダクタ401とコンデンサ404とはLC共振回路を構成し、インダクタ401は、圧電トランス304の一次側(入力側)Aに数十Vpeak程度の正弦半波が印加される。

【0043】

圧電トランス304は、昇圧比が周波数特性を有しているので、NチャネルパワーMOSFET402のスイッチング周波数、即ち、出力端子314(OUT1)のクロック周波数に応じた昇圧比の出力電圧を二次側Bに出力する。

圧電トランス304の二次側Bの出力特性は、図5の模式図で示すように駆動周波数によって変動するので、NチャネルパワーMOSFET402のスイッチング周波数と負荷の組み合わせにより昇圧比が決定される。圧電トランス304の出力制御は、高い周波数で駆動開始し、そこから駆動周波数を下げていくことにより出力電圧を上昇させ、目標の出力電圧を得るように制御を行う。

【0044】

再び、図4に戻って、整流回路305は、ダイオード405、406、及びコンデンサ407により構成され、圧電トランス304の二次側Bから出力される交流高電圧を正極性の直流高電圧に整流する。

【0045】

出力電圧変換手段307は、抵抗器409と抵抗器410とによって、二次側高電圧とアースとの電位差を分圧し、分圧された分圧電圧を抵抗器411とコンデンサ412とからなる低域通過フィルタにより平滑し、コンパレータである第一電圧比較手段308及び第二電圧比較手段309に分圧電圧が印加される。ここで、抵抗器409は100MΩであり、抵抗器410は47kΩである。

【0046】

アース電位が二次側高電圧の正負における分圧値の閾値となる。これにより、分圧された分圧電圧は、正極性側の最大電圧(7000V)時に約3.29Vとなる。

【0047】

第一電圧比較手段308は、デジタルアナログコンバータ(DAC)311から印加される電圧(DAC電圧)と、出力電圧変換手段307から印加される電圧(分圧電圧)とを比較する。比較した結果、DAC電圧値が分圧電圧値より大きいときに「High」を、DAC電圧値が分圧電圧値より小さいときに「Low」を、第一電圧比較手段308は高圧制御部206の入力端子315(IN1)に出力する。

【0048】

第二電圧比較手段309は、後記する三角波発生手段310から印加される電圧(三角波電圧)と、出力電圧変換手段307から印加される電圧(分圧電圧)とを比較する。比較した結果、三角波電圧値が分圧電圧値より大きいときに「High」を、三角波電圧値が分圧電圧値より小さいときに「Low」を、第二電圧比較手段309は高圧制御部206の入力端子316(IN2)に出力する。

【0049】

三角波発生手段310は、オペアンプ430、及び抵抗器431,432を備える非反転増幅回路と、抵抗器433〜436,470〜473、及びNPNトランジスタ437〜440を備えるドライブ回路と、抵抗器441〜444及び抵抗器445〜449を備えるR2R回路と、抵抗器450及びコンデンサ451によるCRフィルタとによって構成される。ここで、R2R回路を構成する抵抗器441〜444と、抵抗器445〜449との抵抗値比は2:1であり、抵抗器432と抵抗器431との抵抗値比は1:3である。

【0050】

図6は、第1チャネル〜第4チャネルの出力端子から出力される信号の波形と、抵抗器に入力される電圧値の変化と、三角波発生手段から出力される波形とを示す図である。

高圧制御部206の4チャネル(第1チャネル〜第4チャネル)の出力端子317(OUT2)から出力されるデジタル信号が、抵抗器470〜473を介してNPNトランジスタ437〜440のベースに入力される。ここでは、第1チャネルがNPNトランジスタ437のベースに入力され、第2チャネルがNPNトランジスタ438のベースに入力され、第3チャネルがNPNトランジスタ439のベースに入力され、第4チャネルがNPNトランジスタ440のベースに入力される。

【0051】

また、非反転増幅回路は、DAC311からオペアンプ430の+端子に印加された目標電圧を、抵抗器431及び抵抗器432による負帰還増幅により(4倍に)増幅する。この増幅電圧は、抵抗器433〜436を用いて、NPNトランジスタ437〜440それぞれのコレクタをプルアップする。例えば、抵抗器433でNPNトランジスタ437のコレクタをプルアップした増幅電圧は、抵抗器441に印加され、抵抗器434でNPNトランジスタ438のコレクタをプルアップした増幅電圧は、抵抗器442に印加され、抵抗器435でNPNトランジスタ439のコレクタをプルアップした電圧は、抵抗器443に印加され、抵抗器436でNPNトランジスタ440のコレクタをプルアップした電圧は、抵抗器444に印加される。

【0052】

NPNトランジスタ437〜440のベースに入力される信号により、NPNトランジスタ437〜440は、コレクタ電流のオンオフの切り替えを行う。このR2R回路は、出力電圧は、0VからDAC311が出力する2倍の電圧範囲を4ビットの分解能、すなわち0〜15段階で出力する。

【0053】

図7は、図3における高圧制御部(ASIC)のブロック図である。図中で、図3と同じ構成要素には同じ符号を付している。

図7において、高圧制御部206は、下位16ビット演算部801と、演算トリガ部802と、初期値記憶部803と、演算命令部804と、演算処理部805と、19ビット保持部806と、分周処理部807とを備える。

【0054】

下位16ビット演算部801は、分周部500と、5ビットカウンタ部501と、反転部502と、セレクタ部503と、5ビットカウンタ部504と、Dラッチ部505と、変化量設定テーブルとしてのテーブルレジスタ510と、特性テーブルとしてのテーブルレジスタ511と、補正手段としての乗算部513とを備える。

【0055】

分周部500は、256分周器であり、50MHzのCLK信号420sを256に分周し、195.3kHz(5.12μsec周期)のパルスを、5ビットカウンタ部501及び5ビットカウンタ部504に出力する。

【0056】

5ビットカウンタ部501は、分周部500から入力された5.12μsec周期のパルスをカウントする5bitのカウンタである。そして、最上位1bitをセレクタ部503に出力する。さらに、下位4bitをセレクタ部503及び反転部502に出力する。また、オーバーフロー時には、Dラッチ部505に「High」を出力し、それ以外では「Low」を出力する。

【0057】

反転部502は、入力されたビット値を反転して出力する。ここでは、5ビットカウンタ部501から入力される4ビット値(下位4bit)を反転してセレクタ部503に出力する。

セレクタ部503は、5ビットカウンタ部501の最上位bitが選択信号として入力され、5ビットカウンタ部501の下位4bitと反転部502の出力4bitとの何れかを出力する。これにより、三角波発生手段310は、DAC311が出力する目標電圧の2倍のピーク電圧の三角波を発生する(図6参照)。

【0058】

5ビットカウンタ部504は、分周部500から入力されるパルス(カウント用パルス)のタイミングで、第二電圧比較手段309から入力されるパルスのレベルをチェックし、レベルが「High」である回数をカウントする。その後、5ビットカウンタ部504は、5ビットカウンタ部501からオーバーフロー信号が入力されたとき、カウンタをクリア(0)する。

【0059】

Dラッチ部505は、5ビットカウンタ部501からオーバーフロー信号が入力されたとき、5ビットカウンタ部504の値を取得し、テーブルレジスタ510に記憶させる(ラッチする)。

【0060】

ここで、出力電圧変換手段307から第二電圧比較手段309に入力される電圧がほぼ0Vである初期状態の場合、第二電圧比較手段309の出力レベルは、ほぼ「High」である。ここで分周部500からパルスがON(カウントタイミング)で入力されたときに、5ビットカウンタ部504はカウント(カウンタを1加算)する。このカウントタイミングのとき、5ビットカウンタ部501もカウント(カウンタを1加算)する。その後、5ビットカウンタ部501のカウンタが「1Fh」(hは16進数を示す)となったときに、5ビットカウンタ部501はオーバーフロー信号を5ビットカウンタ部504及びDラッチ部505に出力する。これにより、Dラッチ部505は、5ビットカウンタ部504の値をラッチし、5ビットカウンタ部504は、Dラッチ部505がラッチした後でカウンタをクリアする(「00h」にする)。そして、5ビットカウンタ部501はオーバーフロー信号を出力後、自身のカウンタをクリアする(「00h」にする)。

【0061】

テーブルレジスタ510は、5ビットの入力値と、8ビットの出力値とを対応して記憶するテーブルを備え、Dラッチ部505からの入力があったときに、その入力値に対応する出力値をテーブルから抽出して、乗算部513に出力する。

テーブルレジスタ510が備えるテーブルの一例を図8に示す。このテーブルは、Dラッチ部505から入力される5ビットの入力値と、乗算部513に出力する8ビットの出力値とを対応付けて記憶する。すなわち、テーブルレジスタ510は、出力電圧と目標電圧との差分値に対応させて周波数変化量が記憶されている。

【0062】

ここで、テーブルレジスタ510が備えるテーブルは、入力値と出力値が中心(基準値)に対して周波数変化量が直線的に上下対称に設定されており、入力値が基準値(図8では中間値の10h)よりも大きくても小さくても、出力値が大きくなるように設定される。その一方、入力値が基準値であれば、出力値は小さくなるように設定される。これは、テーブルレジスタ510に入力される5ビットの入力値が5ビットカウンタ部504の値であるため、第二電圧比較手段309からの出力レベルが「High」である回数と「Low」である回数とでほぼ等しくなるときに、テーブルレジスタ510からの出力値が小さくなる。すなわち、三角波発生手段310の出力電圧の平均値(ピーク値の1/2)が出力電圧変換手段307の出力電圧値とほぼ等しくなるときに、出力値が小さくなるようにテーブルレジスタ510の入力値と出力値とは設定されている。

【0063】

テーブルレジスタ511は、7ビットの入力値と、8ビットの出力値とを対応して記憶するテーブルを備え、後記する19ビット保持部806からの入力があったときに、その入力値に対応する出力値をテーブルから抽出して、乗算部513に出力する。

テーブルレジスタ511が備えるテーブルの一例を図9に示す。このテーブルは、19ビット保持部806から入力される7ビットの入力値と、乗算部513に出力する8ビットの出力値とを対応付けて記憶する。

【0064】

このテーブルレジスタ511が備えるテーブルの入力値及び出力値は、次のように予め決められた値である。

本実施形態において、高圧制御部206が行う周波数制御範囲は上限値が「1CFh」であり、下限値が「180h」である。これが、19ビット保持部806の上位9bitの上限値と下限値として決められ、後記するカウンタ上限値記憶部519には、上限値「1CFh」(1 1100 1111b)が記憶されている。後記するカウンタ下限値記憶部520には、下限値「180h」(1 1000 0000b)が記憶されている。

【0065】

パルスの出力は、19ビット保持部806の19ビット値のうち、上位9bitを分周に、下位10bitを端数として演算する。CLK信号420sのクロック周期は、1/50MHz=20nsecである。

下限値「180h」のときの周波数は、

180h×20nsec=7.68μsec

1/7.68μsec=130.2kHz

となる。

同様に、上限値「1CFh」のときの周波数は、

1CFh×20nsec=9.26μsec

そのときの端数である下位10bitの「3FFh」も考慮して、

3FFh(=1023)×20nsec/1024=0.02μsec

1/(9.26μsec+0.02μsec)=107.76kHz

となる。

よって、制御周波数範囲は、107.76〜130.2kHzである。

【0066】

テーブルレジスタ511には、19ビット保持部806の19ビット値の上位9bitのうちの、最上位2bit(常に11bである)を除く、7bit(7ビット値)が入力される。つまり、7ビット値が00h(000 0000b)であれば、元の上位9bitは180h(1 1000 0000b)である。そして、7ビット値が47h(100 0111b)であれば、元の上位9bitは1C7h(1 1100 0111b)である。

【0067】

このテーブルレジスタ511には、いち早く目標電圧に近づけるための設定値が記憶されている。出力電圧が低く、周波数が高い領域では(つまり、圧電トランスの固有共振周波数から離れるほど)周波数の制御量、すなわち周波数の変化量に対する出力電圧の変換量が大きくなるように、入力値と出力値とが設定されている。このテーブルレジスタ511の値は、実験により得られた値である。

【0068】

乗算部513は、テーブルレジスタ510からの8ビット値と、テーブルレジスタ511からの8ビット値とを乗算して、算出した16ビット値を演算処理部805に出力する。本実施例において、乗算部513は常に乗算を行い、その乗算結果を演算処理部805に出力する。

【0069】

(演算トリガ部802)

演算トリガ部802は、周期値記憶部516と、シフト演算部550と、3ビットカウンタ部551と、テーブルレジスタ552と、演算指示部517とを備える。

周期値記憶部516は、制御周期を決定する13bitのメモリであり、140μsecに相当する値である「7000(1B58h)」が予め記憶されている。

【0070】

シフト演算部550は、3ビットカウンタ部551から取得した3ビット値に応じて、周期値記憶部516の13ビット値をシフト演算して、演算値を演算指示部517に出力する。

例えば、シフト演算部550は、3ビットカウンタ部551から取得した3ビット値が「000b」の場合は、13ビット値をシフトしない。3ビット値が「001b」の場合は1ビットシフトし、「010b」の場合は2ビットシフトし、「011b」の場合は3ビットシフトする。以降、3ビットカウンタ部551から取得した3ビット値が1ビット増えるごとに、シフト演算部550は、そのビット分のシフトを13ビット値に行う。

これにより、周期値記憶部516の13ビット値が「7000(01B58h)」である場合、シフト演算部550は、3ビット値が「000b」のときそのまま(シフトせずに)「7000(01B58h)」を演算指示部517に出力する。そして、「001b」のとき1ビットシフトして「14000(036B0h)」を出力し、「010b」のとき2ビットシフトして「28000(06D60h)」を出力する。

【0071】

演算指示部517は、シフト演算部550から演算値(20ビット値)を取得して保持する記憶手段と、カウンタとして値(20ビット値)を保持する記憶手段とを備え、さらに、カウンタの値をカウントアップする機能を備える。そして、演算指示部517は、カウンタの値と、演算値の値とが等しくなったときに、20ビット値を「00000h」として、CLK端子420(CLK_IN)から入力されるCLK信号420sのタイミングで1ビットずつカウントアップする。そして、20ビット値が「00800h」を超えるまで、演算指示部517は演算処理部805にパルスを「High」で出力する。そして、20ビット値が「00800h」を超えたときから(「00801h」となったときから)、シフト演算部550から取得した演算値(20ビット値)になるまで、演算指示部517は演算処理部805にパルスを「Low」で出力する。

つまり、シフト演算部550から取得した演算値(20ビット値)が「01B58h」であれば、カウンタの値が「01B58h」となるまで、演算指示部517は演算処理部805にパルスを「Low」で出力する。そして、演算指示部517は、カウンタの値と、演算値の値とが等しくなったことで、20ビット値を「00000h」に設定して、再び1ビットずつカウントアップをし、演算処理部805にパルスを再び「High」で出力する。

【0072】

3ビットカウンタ部551は、3ビット値を、演算指示部517からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)でカウントダウンする。そして、ON端子312からのON信号312sの立ち上がりエッジで、そのときの3ビット値をシフト演算部550に出力するとともに、テーブルレジスタ552から3ビット値を取得して、カウントダウン対象の3ビット値とする。

ここで、カウントダウン中に3ビット値が「000b」となった場合、3ビットカウンタ部551はその値を保持する。

【0073】

例えば、3ビットカウンタ部551にON信号312sの立ち上がりエッジが入力されたときに、3ビットカウンタ部551はテーブルレジスタ552から3ビット値を取得する。そして、3ビットカウンタ部551は、演算指示部517からの出力パルスの立ち上がりエッジがあるごとに3ビット値から1bitずつカウントダウンする。例えば、取得した3ビット値が「110b」である場合、「101b」、「100b」、「011b」、「010b」、「001b」、「000b」とカウントダウンする。一旦、「000b」となった後は、カウントダウンをせず、次のON信号312sの立ち上がりエッジが入力されるまで値を「000b」のまま保持する。

【0074】

テーブルレジスタ552は、7ビットの入力値と、3ビットの出力値とを対応して記憶するテーブルを備え、後記する19ビット保持部806からの入力があったときに、その入力値(7ビット値)に対応する出力値(3ビット値)をテーブルから抽出して、3ビットカウンタ部551に出力する。

テーブルレジスタ552が備えるテーブルの一例を図10に示す。このテーブルは、19ビット保持部806から入力される7ビットの入力値と、3ビットカウンタ部551に出力する3ビットの出力値とを対応付けて記憶する。ここで、19ビット保持部806からは、19ビット値(bit18〜bit0)のうち、bit16〜bit10の7ビットが入力値として入力される。

【0075】

初期状態について説明する。まず、出力電圧変換手段307の出力がほぼ0Vである初期状態において、テーブルレジスタ552には、7ビットの入力値が「00h」で入力される。テーブルレジスタ552は、図10のテーブルを参照して、3ビットの出力値として「000b」を3ビットカウンタ部551に出力する。ここで、3ビットカウンタ部551は、RESET信号313sにより初期化された値「000b」を保持している。結果、3ビットカウンタ部551がシフト演算部550に出力する3ビット値は「000b」となる。

【0076】

(初期値記憶部803)

初期値記憶部803は、カウンタ上限値記憶部519と、カウンタ下限値記憶部520とを備える。カウンタ上限値記憶部519には、上限値「1CFh」(1 1100 1111b)が記憶されている。カウンタ下限値記憶部520には、下限値「180h」(1 1000 0000b)が記憶されている。

【0077】

(演算命令部804)

演算命令部804は、演算処理部805に命令(3ビット値)を出力して、19ビット保持部806への出力値を制御する。この演算命令部804は、9ビットカウンタ部506と、Dラッチ部507と、比較部514とを備える。

【0078】

9ビットカウンタ部506は、第一電圧比較手段308から入力端子315(IN1)に入力される信号が「High」である時間を計測する。

本実施形態において、9ビットカウンタ部506は、50MHzのCLK信号420sのパルスがCLK端子420(CLK_IN)に入力されるタイミングで、入力端子315(IN1)に入力される信号の判定を行い、「High」であるときに1ビットずつ9ビットカウンタ値をカウントアップする。そして、出力セレクタ部528からの入力信号が立ち上がったタイミングで、9ビットカウンタ値はクリア(000h)される。このクリアは、後記するDラッチ部507が9ビットカウンタ値を取得した後で行われる。

【0079】

Dラッチ部507は、出力セレクタ部528からの入力信号が立ち上がったタイミングで、9ビットカウンタ部506の9ビットカウンタ値を取得する。そして、Dラッチ部507は、RESET信号313sがRESET端子313に入力されるタイミングで、記憶している値をクリア(000h)する。

【0080】

比較部514は、ON端子312に入力されるON信号312sに応じて、演算処理部805に対する演算命令(3ビット値)を決定して出力する。

本実施形態において、比較部514は、ON信号312sが「High」であるときに、Dラッチ部507の9ビットカウンタ値と、19ビット保持部806の上位9ビット値(bit18〜bit10)とを比較判定して、比較判定結果に応じて演算命令「000b」〜「100b」のいずれか一つを演算処理部805に出力する。一方、ON信号312sが「Low」であるとき、比較部514は、演算命令「010b」を演算処理部805に出力する。

【0081】

ここで、比較部514は比較判定の結果(判定結果A〜E)に応じて、以下に示す演算命令を出力する。

(判定結果A)「9ビットカウンタ値≧上位9ビット値−5」の場合、演算命令「000b」を出力する。

(判定結果B)「上位9ビット値−5>9ビットカウンタ値≧上位9ビット値×0.6」の場合、演算命令「001b」を出力する。

(判定結果C)「上位9ビット値×0.6>9ビットカウンタ値≧上位9ビット値×0.4」の場合、演算命令「010b」を出力する。

(判定結果D)「上位9ビット値×0.4>9ビットカウンタ値>5」の場合、演算命令「011b」を出力する。

(判定結果E)「5≧9ビットカウンタ値」の場合、演算命令「100b」を出力する。

【0082】

(演算処理部805)

演算処理部805は、演算命令部804(比較部514)からの演算命令に従って、19ビット保持部806が記憶する19ビット値に演算を行う。この演算は、演算指示部517からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)で行われる。

【0083】

ここで、演算処理部805は、比較部514からの演算命令に従って、以下に示す演算を行う。

演算命令「000b」の場合、乗算部513から16ビット値を取得し、19ビット保持部806にその16ビット値を加算する。

演算命令「001b」の場合、19ビット保持部806の値に1を加算する。

演算命令「010b」の場合、19ビット保持部806の値を更新しない(値をそのままにする)。

演算命令「011b」の場合、19ビット保持部806の値から1を減算する。

演算命令「100b」の場合、乗算部513から16ビット値を取得し、19ビット保持部806の値からその16ビット値を減算する。

【0084】

ここで、次の事象(事象A〜事象C)が発生した場合には、その事象に応じた割込処理を演算処理部805は行う。

(事象A)RESET信号313sがRESET端子313に入力されたとき、演算処理部805は、カウンタ下限値記憶部520から下限値「180h」(1 1000 0000b)を取得し、19ビット保持部806の上位9ビット値を下限値「1 1000 0000b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

(事象B)演算処理部805は、演算命令「001b」により加算を行った結果、上位9ビット値がカウンタ上限値記憶部519の上限値「1CFh」(1 1100 1111b)を超えた場合、19ビット保持部806の上位9ビット値を上限値「1 1100 1111b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

(事象C)演算処理部805は、演算命令「011b」により減算を行った結果、上位9ビット値がカウンタ下限値記憶部520の下限値「180h」(1 1000 0000b)を下回った(未満となった)場合、19ビット保持部806の上位9ビット値を下限値「1 1000 0000b」にし、残りの下位10ビット値を「0」(00 0000 0000b)で更新する。

【0085】

(19ビット保持部806)

19ビット保持部806は、19ビットの値を記憶するレジスタである。19ビットの値のうち、上位9ビット値は、比較部514、加算部525、及び分周セレクタ部526に出力され、下位10ビット値は、誤差保持部529に出力される。

【0086】

(分周処理部807)

分周処理部807は、19ビット保持部806の上位9ビット値に基づき、パルスの周波数を決め、パルスを生成して出力する。この分周処理部807は、加算部525と、分周セレクタ部526と、パルス生成部527と、出力セレクタ部528と、誤差保持部529とを備える。

【0087】

加算部525は、19ビット保持部806から取得した上位9ビット値に1を加算して、分周セレクタ部526に出力する。

【0088】

分周セレクタ部526は、後記する誤差保持部529からの入力値に応じて、19ビット保持部806または加算部525から取得した9ビット値をパルス生成部527に出力する。

本実施形態において、分周セレクタ部526は、誤差保持部529からの入力値が「High」である場合、加算部525から取得した9ビット値(上位9ビット値に1を加算した値)をパルス生成部527に出力する。一方、入力値が「Low」である場合、分周セレクタ部526は、19ビット保持部806から取得した上位9ビット値をパルス生成部527に出力する。

【0089】

パルス生成部527は、分周セレクタ部526から出力される9ビット値の周波数のパルスをデューティ比30%で生成し、パルスを出力セレクタ部528に出力する。

【0090】

出力セレクタ部528は、ON端子312からのON信号312sが「High」の場合、パルス生成部527から入力されるパルスをそのまま出力端子314(OUT1)に出力する。一方、ON信号312sが「Low」の場合、出力セレクタ部528は「Low」の信号を出力する。

【0091】

誤差保持部529は、10ビットのレジスタと1ビットのフラグレジスタとで構成され、RESET信号313sがRESET端子313に入力されるタイミングで、10ビットのレジスタ値及び1ビットのフラグレジスタ値をクリアする。

また、誤差保持部529は、パルス生成部527からの出力パルスの立ち上がりエッジ(「Low」から「High」になったタイミング)で、19ビット保持部806の下位10ビット値を取得し、10ビットのレジスタに加算する。この加算時にオーバーフローが発生した場合、フラグレジスタを「1」とし、発生しなかった場合は「0」とする。

【0092】

(実施例1の動作説明)

まず、第1の実施形態における画像形成装置全体の概略動作を説明する。

図1の画像形成装置101は、外部機器からホストインタフェース部201(図2)を介してPDL(Page Description Language)などで記述された印刷データを入力する。入力された印刷データは、コマンド/画像処理部202によってビットマップデータに変換される。

【0093】

画像形成装置101は、定着器123の加熱部材124、及び圧着部材125を、サーミスタ216(図2)の検出値に応じて定着器ヒータ217(図2)を制御することにより所定温度にした後、印字動作を開始する。画像形成装置101は、用紙カセット117にセットされた用紙を給紙モータ210で駆動する給紙ローラ118で給紙する。用紙ガイド119に沿って用紙を搬送し、停止状態のレジストローラ120、121の対に用紙を突き当て、スキューを補正した後、以下で説明する画像形成動作に同期したタイミングで搬送モータ211を駆動開始し、レジストローラ120、121によって用紙は転写ベルト114上に搬送される。

【0094】

このとき、前記ビットマップデータに応じてLEDヘッド103K、103Y、103M、103Cが点灯される。これにより、感光体ドラム109K、109Y、109M、109Cには、静電潜像が形成される。

現像器102K、102Y、102M、102Cは、電子写真プロセスにより現像器内の感光体ドラム109K、109Y、109M、109Cにトナー像を形成する。現像器102K、102Y、102M、102Cによって現像されたトナー像は、転写ベルト114上を搬送される用紙に転写される。このとき、転写ベルト114を狭持して感光体ドラム109K、109Y、109M、109Cに対向して配設されている転写ローラ111K、111Y、111M、111Cは、転写バイアスが印加されている。

用紙上に4色のトナー像を転写した後、定着器123は、加熱・加圧により用紙上のトナー像を定着させ、排出ローラ126、127は、用紙ガイド128に沿って用紙を搬送し、排紙する。

【0095】

本実施形態での主要な制御対象は転写ローラ111K,111Y,111M,111Cに印加するバイアス電圧であるが、これらは同様の構成を4色分並置するものであるので、以下の説明は1色分とする。

プリンタエンジン制御部204は、感光体ドラム駆動モータ214(図2)により感光体ドラム109を回転駆動させると同時に、現像バイアスの印加を開始する。

【0096】

続いて図4の回路図を用いて詳細に説明する。

プリンタエンジン制御部204は、「Low」のRESET信号313sを出力して高圧制御部206の諸処の設定をリセットする。このリセット動作によって出力端子314(OUT1)から出力するパルスの分周比などの値が初期値となる。高圧制御部(ASIC)206は初期値にてCLK端子420(CLK_IN)から入力されるCLK信号420sを初期値の分周比、ONデューティ30%で分周する。但し、プリンタエンジン制御部204から高圧オンのコマンドを受信するまでは出力端子314(OUT1)から分周されたパルスは出力されず、出力端子314(OUT1)出力は「Low」レベルに保持される。

【0097】

プリンタエンジン制御部204は、SCLK信号429s(同期クロック)を出力し、前記クロックに同期してSDO信号428s(シリアルデータ)を出力し、高圧出力目標電圧をDAC311出力値である10bitデータをDAC311に送信する。例えば、7kVの場合には3.29Vの比較電圧となり、この場合3.3V 10bitであるので送信データは3Fbhとなる。ここで、高圧制御部206及びDAC311には、不図示の3.3V電源が接続されている。また、第一電圧比較手段308、第二電圧比較手段309、オペアンプ430の電源端子には不図示の24V電源及びGNDが接続されている。

【0098】

高圧制御部206のCLK端子420(CLK_IN)には、抵抗器419を介して発振器414が接続されている。発振器414は、電源端子VDD415と出力イネーブル端子OE416に3.3VのDC電源413が接続され、発振器414のCLK_OUT端子417から電源投入直後から50MHz、周期20nsecのクロックパルスが出力される。GND端子418は接地される。

出力端子314(OUT1)が出力するパルスが「Low」である間、NチャネルパワーMOSFET402はオフである。そのため、圧電トランス304の一次側端子(図4のAで示す部分)には、DC電源302から直流電圧24Vがそのまま印加される。

【0099】

このとき、DC電源302からインダクタ401を介して流れる電流値はほぼ0であり、圧電トランス304は圧電振動しない。そのため、圧電トランス304の二次側(図4のBで示す部分)の出力電圧は0Vであり、出力電圧変換手段307の出力電圧は0Vである。第一電圧比較手段308の「+」入力端子にはDAC311から目標電圧(3.29V)が印加され、「−」入力端子には出力電圧変換手段307から電圧(0V)が印加される。「+」入力端子の電圧の方が高いので、第一電圧比較手段308はオープンコレクタ出力となり、3.3V電源413に接続されているプルアップ抵抗器460のため、第一電圧比較手段308から「High」の信号が、入力端子315(IN1)に入力される。

【0100】

同様に、第二電圧比較手段309の「−」入力端子には出力電圧変換手段307から電圧(0V)が印加され、「+」入力端子には三角波発生手段310から三角波電圧が印加される。この三角波発生手段310には、高圧制御部206の出力端子317(OUT2)から4つの信号が入力される。

出力端子317(OUT2)の出力信号が「High」の場合、NPNトランジスタ437(〜440)にベース電流が流れ、NPNトランジスタ437(〜440)がONになり、抵抗器441(〜444)の一端は接地する(0V)。一方、出力端子317(OUT2)の出力信号が「Low」の場合、オペアンプ430の出力電圧が抵抗器433(〜436)でプルアップして出力される。

【0101】

オペアンプ430、及び抵抗器431及び抵抗器432を含む非反転増幅回路は、DAC311からの入力電圧を4倍に増幅する。そして、抵抗器441(〜444)と抵抗器445(〜449)との抵抗値比は2:1である。また、抵抗器441〜444及び抵抗器445〜449でR2Rを構成している。

4チャネルの出力端子317(OUT2)の出力信号(4bit)は、0000b〜1111bの16段階で出力され、抵抗器450及びコンデンサ451のCRフィルタにより波形が整形されて、第二電圧比較手段309の「+」入力端子に印加される。これにより、三角波発生手段310は、DAC311の出力電圧の2倍の値の三角波を出力する。

【0102】

図6に、4チャネルの出力端子317(OUT2)が出力する信号(第1チャネル出力〜第4チャネル出力)と、抵抗器450に印加される電圧値と、CRフィルタにより波形が整形されて印加される電圧値(つまり、三角波発生手段310の出力電圧値)とを示す。

【0103】

第二電圧比較手段309の「−」入力端子の電位が0Vであれば、3.3V電源413に接続されるプルアップ抵抗器461の電位で、ほぼ「High」レベルに近いデューティ100%弱の163.8μsec周期の波形(PWM波形)が、高圧制御部206の入力端子316(IN2)に入力される。

そして、高圧制御部206は、PWM波形を163.8μsec周期でサンプリングして、デューティを32段階で検出する。この検出値は、第二電圧比較手段309の「−」入力端子の電位が0Vの場合の初期状態において、1Fhとなる。

【0104】

ここで、感光体ドラム109(図1)と転写ベルト114(図1)が駆動され、用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204はON信号312sを「Low」から「High」に遷移して高圧制御部206に出力する。ON端子312からON信号312sを「High」で取得した高圧制御部206は、初期値にて分周したパルスを出力端子314(OUT1)から出力する。

【0105】

本実施例では初期値は384分周であり、1周期7.68μsec、ONデューティ29%である。出力端子314(OUT1)から出力されたパルスによってNチャネルパワーMOSFET402がスイッチングされ、インダクタ401とコンデンサ404と圧電トランス304とによって、圧電トランス304の一次側(Aで示す端子)には、図11に示す数十Vpeakの半波正弦波形が印加される(圧電トランス駆動回路303出力)。

【0106】

入力端子315(IN1)に印加される電圧が「High」レベルの場合、所定周期である140μsec毎に、384分周の分周比に1加算する。加算した結果、周波数が低くなり、図12で示すように出力電圧が上昇して行く。

【0107】

ここで、図12は、無負荷の場合のデータ(太線)と、負荷がある場合(100MΩの抵抗器408と50MΩの負荷306)のデータ(破線)であり、負荷により同じ電圧出力でも駆動周波数が異なることを示している。なお、図12では、駆動周波数約108kHzのときに最大出力電圧は7000Vであるが、圧電トランスの共振周波数は、108kHzよりも低い所に存在する(図5参照)。また、図13及び図14に、図12の特性に対する19bitレジスタ値を示す。

【0108】

出力電圧上昇に伴い、入力端子316(IN2)に入力される163.8μsec周期のPWM波形のデューティが小さくなる。その後、デューティが100%から目標電圧であるデューティ50%となるまで、所定の設定値によって分周比可変幅が大〜小へと変化する。ついには目標電圧付近にて入力端子315(IN1)の出力電圧が矩形波となったときに、分周比可変幅を最小分解能に落として、デューティが40〜60%となるように分周比設定値を加減算する。これにより目標電圧にて定電圧制御される。

以上の動作により、7000Vの目標電圧が転写ローラ111(111K,111Y,111M,111C)(図2)に印加される。

【0109】

さらに、用紙検出センサ122(図2)が用紙後端を検出した所定時間後、すなわち用紙が感光体ドラム109(図1)と転写ローラ111(図1)とのニップ部を通過する直前で、プリンタエンジン制御部204は、ON信号312sを「High」から「Low」に遷移して高圧制御部206に出力する。ON端子312からON信号312sを「Low」で取得した高圧制御部206は、出力端子314(OUT1)から出力する信号(圧電トランス駆動信号)をオフする。これにより、高圧電源装置301が出力する電圧が落とされる(0になる)。

【0110】

このとき、DAC311は3.29Vの電圧を印加し続ける。また高圧制御部206の内部では、オフする直前の、出力端子314(OUT1)の出力信号(圧電トランス駆動信号)が保持される。

そして、次の用紙がある場合には、その用紙が感光体ドラム109と転写ローラ111(図1)とのニップ部に到達するタイミングで、プリンタエンジン制御部204はON信号312sを「Low」から「High」に遷移して高圧制御部206に出力する。2回目のON信号312sが出力される、すなわち2枚目以降の印刷では、前回の印刷後におけるオフする直前の、出力端子314(OUT1)の出力信号(圧電トランス駆動信号)の分周比値(駆動周波数)にて、駆動が開始される。このとき、圧電トランス駆動信号の分周比値を制御する周期を初回印刷時と異なるものとして制御を行う。

【0111】

以降、再度7000Vに制御され、連続印刷の間同じ動作を繰り返す。

指定枚数の用紙の印刷が終了後、プリンタエンジン制御部204はON信号312sを「High」から「Low」に遷移して高圧制御部206に出力し、さらにRESET信号313sを「High」から「Low」に遷移して高圧制御部206に出力する。これにより、高圧制御部206の内部設定値をリセットする。

【0112】

本実施例の高圧電源装置301の2枚目以降の印刷における出力特性を図15及び図16に示す。図15は、駆動周波数が108.46Hzの場合の立ち上がり特性を示し、図16は、駆動周波数が111.61Hzの場合の立ち上がり特性を示す。負荷値により出力電圧が変化するが、駆動周波数が等しければ負荷値によらず立ち上がり時間は等しかった。また、図の特性は100MΩの抵抗器408と負荷306との間のポイントを測定しており、実施例にて説明している制御電圧が7000Vとなる部分はダイオード406、抵抗器409、抵抗器408の接続部(図4のCで示す部分)である。

【0113】

本発明では駆動周波数と立ち上がり時間の関係が負荷によらずに等しいことから直前の印刷での駆動周波数で駆動を開始した場合の高圧立ち上がり時間に応じた時間だけ、駆動周波数を変化させる周期を長くすることによって早くて正確な立ち上げを実現している。また、連続印字時には印刷間での環境温度変化などはほとんどないので、負荷による駆動特性が一意に決定しない圧電トランスの駆動においても同一駆動周波数にて目標電圧に制御可能である。さらには、立ち上がり時間経過後において、出力電圧のフィードバック制御を短い周期で行うので、たとえ負荷変動があったとしても直ちに収束することができる。

【0114】

次に、第1の実施形態における高圧制御部206の概略動作を、図7を用いて説明する。

まず、プリンタエンジン制御部204からRESET信号313sが入力されたとき、高圧制御部206が備えるカウンタ部(5ビットカウンタ部501,5ビットカウンタ部504,9ビットカウンタ部506)の値が初期化される。

そして、演算処理部805は、上位9bitをカウンタ下限値記憶部520の9ビット値とし、下位10bitを0にする19ビット値を生成する。この19ビット値を19ビット保持部806に記憶させる。このとき、初期値として、19ビット保持部806には60000hが記憶される。

【0115】

そして、分周セレクタ部526には、19ビット保持部806の上位9bitと、加算部525により19ビット保持部806の上位9bitに1加算された値とが入力される。例えばそれぞれの値が180h、181hとなる。

初期状態、すなわちRESET信号313sが入力後では、19ビット保持部806の上位9bit(180h)がパルス生成部527に入力される。

パルス生成部527は0から180hまで、CLK端子420(CLK_IN)から入力されるCLK信号420sのクロックをカウントする毎に、パルスを出力する。パルス生成部527はCLK信号420sの立ち上がりでカウントアップする9ビットカウンタを備え、9ビットカウンタの値と分周セレクタ部526が出力する9ビット値との比較及び、9ビットカウンタの値と分周セレクタ部526が出力する9ビット値を約30%にした値(この値は実際には9ビット値の1/4値,1/32値,1/64値の和)との比較を行う。ここで、9ビットカウンタの値と、分周セレクタ部526が出力する9ビット値を約30%にした値と等しくなった場合、パルス生成部527は「Low」で出力する。一方、9ビットカウンタの値と、分周セレクタ部526が出力する9ビット値とが等しくなった場合、パルス生成部527は「High」を出力し、9ビットカウンタを0にする(クリアする)。

【0116】

以上の動作によって、パルス生成部527は、CLK信号420sを分周セレクタ部526が出力する9ビット値で分周した周波数で、約30%のONデューティのパルスを出力する。

そして、出力セレクタ部528は、ON信号312sがON(High)である場合にパルスを出力し、OFF(Low)の場合は「Low」を出力する。

【0117】

ここで、19ビット保持部806の下位10bitは、小数点以下の分周比を示すカウンタである。分周比は180h(384)分周であり、60000h(初期値、上位9bitが180h、下位10bitが0)から開始し、60400h(上位9bitが181h、下位10bitが0)になるまでの間、小数点以下を示す値の誤差を加算し、加算結果が1以上となった時にパルスの分周比を1加算された方を選択する。

【0118】