電源装置及び画像形成装置

【課題】同期整流方式のスイッチング電源において、簡単な回路構成で、負荷の状態によらず正しく同期整流動作を実行する。

【解決手段】簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減するために、トランスの二次側の同期整流用のFETのオン時間を一定値で制御する。

【解決手段】簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減するために、トランスの二次側の同期整流用のFETのオン時間を一定値で制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、同期整流方式のスイッチング電源装置、その電源装置を搭載した画像形成装置に関する。

【背景技術】

【0002】

近年、電子機器装置の省電力化に伴い、電源装置の動作の効率化が要求されている。動作の効率化を実現した電源装置の一例として、特許文献1に記載の電源装置が提案されている。このような従来の電源装置の構成例を図8に示す。図8において、1は直流電源、2は主スイッチング素子としての電界効果トランジスタMOS−FET(以下、FETともいう)を制御する制御回路、4は主スイッチング素子としてのFET、5はトランスである。6は第2のスイッチング素子であるFET、7は平滑コンデンサ、8は電圧が供給される負荷、9は出力電圧検出回路、10はFET6に寄生するボディダイオード、11はFET6の駆動回路、12はFET6の電流検出回路である。

【0003】

直流電源1からの入力電圧は、制御回路2および駆動回路3で制御されるFET4を導通する(オンする)ことでトランス5の1次巻線n1に励磁エネルギとして蓄積される。一方、FET4を非導通する(オフする)タイミングでトランス5の1次巻線n1に励磁されたエネルギは2次巻線n2に変換され、ボディダイオード10と電流検知回路12を通して負荷に供給される。電流検知回路12は電流が流れたことを検出すると駆動回路11にオン信号を送出し、FET6をオンする。また、電流検知回路12は自身に流れている電流が所定値以下になると電流が流れ終ったと判断し、今度は駆動回路12にオフ信号を送出してFET6をオフする。ボディダイオード10の順方向電圧による損失に対してFET6による損失は非常に低い。このため、ボディダイオード10に流れる電流をFET6側に切り替えるように制御することで、効率の向上を図っていた。このような方式は同期整流方式と呼ばれており、FET6は同期整流用のFETとも呼ばれる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−115766号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来例では次のような課題があった。上記の同期整流方式の場合、動作の効率を向上するために同期整流用のFETのオンオフを検知する回路を設ける構成であり、この検知回路は複雑になる。従って、回路規模が大きくなり、コストアップを招いていた。また、二次巻線に流れる電流をカレントトランスで検知し、検知した電流によってFETのオンオフ制御を行う場合、軽負荷時では二次巻線に流れる電流量が僅かであり、カレントトランスから出力される電流も非常に小さくなってしまいFETのオンオフを正しく制御できない状態になる。FETのオンオフが正しく制御(駆動)されないと、効率の低下、また、消費電力が増大する可能性がある。このような軽負荷時(軽負荷状態)は、動作を待機しているスタンバイ状態や消費電力を低減する省エネモード(スリープモードともいう)を指し、所謂、電子機器におけるデフォルトの状態である。このデフォルトの状態は、電子装置において一日の中でかなりの時間を占める状態であり、FETのオンオフ動作による消費電力の増加や損失が電子機器のトータルの消費電力に大きく影響する。

【0006】

従って、本発明は、上記の点に鑑み、同期整流方式のスイッチング電源において、簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための本発明の電源装置は、トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部とを有することを特徴とする。

【0008】

また、本発明の画像形成装置は、記録材に画像を形成するための画像形成部と、前記画像形成部の動作を制御する制御部と、前記制御部に電圧を供給する電源と、を備え、前記電源は、トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部を有することを特徴とする。

【発明の効果】

【0009】

以上説明したように、本発明によれば、簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減することが可能になる。

【図面の簡単な説明】

【0010】

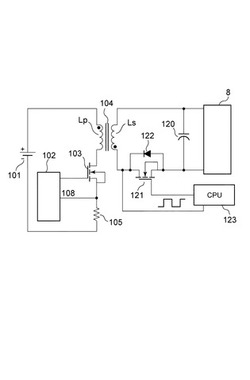

【図1】実施例1の電源装置の回路図

【図2】実施例1の回路の動作波形

【図3】実施例2の回路の動作波形

【図4】実施例2の電源装置の回路図

【図5】実施例2の動作を示すフロチャート

【図6】実施例3の電源装置の回路図

【図7】実施例3の回路の動作波形

【図8】従来の回路図

【図9】本発明の電源装置の適用例を示す図

【発明を実施するための形態】

【0011】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【実施例1】

【0012】

実施例1について以下に説明する。

図1は本発明の実施例1に係る電源装置の回路図であり、図2はその動作波形の一部を示した図である。以下、図1と図2を基にして、本実施例1の詳細説明を行う。

【0013】

101は直流電圧電源であり、コンセント(商用電源)から供給されてダイオードブリッジ(不図示)で全波整流されたAC電圧をコンデンサ(不図示)で平滑することで直流電圧が得られる。102は制御部としての制御ICであり、第一のスイッチング素子としてのMOS−FET103(以下、FETという)のオンオフ動作を制御する。104は一次側と二次側の絶縁を取りつつ一次側のエネルギを二次側に変換するトランスであり、一次巻線のインダクタンスをLp、二次巻線のインダクタンスはLsである。105はFET103の電流を検知する電流検知用の抵抗、120は二次側の平滑コンデンサ、121は第二のスイッチング素子としてのMOS−FET(以下、FETという)であり、二次側の電圧を整流する同期整流用のFETである。122は同じく二次側電圧を整流するためのダイオード(ボディダイオードともいう)、123は電子機器の動作を制御する制御IC(CPU)である。なお、8は電圧が出力される負荷である。

【0014】

電源装置が起動する際は、不図示の起動回路により制御IC102がFET103の駆動を開始する(オンする)。FET103がオンされるとトランス104の一次側、および、電流検知抵抗105に電流が流れるとともに、トランス104の一次巻き線に流れるピーク電流をIpとした場合、以下の式1で示されるエネルギE1が蓄積される。

E1=1/2Lp×Ip2 ・・・(式1)

このピーク電流Ipは電流検知抵抗によって電圧に変換され、制御IC102により一定値に制御される。このため入力電圧が変化してもトランス104に蓄積されるエネルギは略同じ値になる。例えば、100V系の電圧が入力される場合、入力電圧がAC85Vの時はピーク電流の傾きが立つ(単位時間あたりの変化量が大きい)ためFET103の駆動時間(オン時間ともいう)が短くなる。一方、入力電圧がAC140V時では電流の傾きが緩やかになる(単位時間あたりの変化量が小さい)ためFET103のオン時間は長くなる。このように入力電圧が異なっていても電流の流れている時間が異なるだけでピーク電流値は同じである。

【0015】

一方、二次巻線に蓄積されるエネルギE2は、二次巻線に発生するピーク電流をIsとすると、以下の式2で示される。

E2=1/2Ls×Is2 ・・・(式2)

フライバック方式の電源の場合は、トランスの一次側で発生したエネルギと二次側に変換するエネルギが等しいため、トランス104の二次巻線に流れる電流は、入力電圧によらずに一定時間流れることになる。本実施例1においては、トランスの一次側の電流のピーク値に基づいて出力を制御する方式が前提となる。

【0016】

入力電圧が一定の場合、FET103のオン時間も一定であり、また、トランスの二次側の電流のオン時間も一定になる。そして、負荷8の状態の変化(負荷が大きい/小さい)に対応するため、オフ時間を変化させて周波数を可変する。つまり負荷の状態が変化したとしても、トランスの二次側に電流が流れている時間は一定となる。

【0017】

図1の電源装置において、負荷8に対する出力電圧が大きい場合、例えば、24Vを出力している場合(重負荷時ともいう)は、二次側の電解コンデンサ120の出力側の電圧を検知してトランス104の一次側にフィードバックして、FET103の駆動を制御することに負荷に対して一定の電圧(24V)が出力するように制御される。なお、出力電圧が大きい場合とは、電子装置が動作を実行している状態であり、通常出力モードとも呼ばれる。

【0018】

一方、図2は、出力電圧が小さい場合、例えば、3.3Vを出力している場合(軽負荷時ともいう)の動作波形を示している。図2において、201はFET103に流れる電流波形、202はFET103のドレイン−ソース間の電圧波形、203はトランスの二次側の電流波形、204は同期整流用のFET121のドレイン−ソース間の電圧波形を示したものである。このように、FET121のドレイン−ソース間の電圧の立ち下がりとトランスの二次側の電流の流れ始めは同じタイミングになる。この立ち下りのタイミングを制御IC123で検出して、IC123がFET121ゲート端子をハイレベルにしてFET121を駆動する(オンする)。

【0019】

具体的には、ダイオード122のカソード端子に入力される電圧をIC123で検知して、その電圧の立下りタイミングを検知して、検知したタイミングでFET121を駆動するように制御する。

【0020】

また、FET121をオフするタイミングについては、本実施例1の方式がピーク電流を固定する方式を前提としているため、前述したようにオフ時間も固定となり、この時間を制御IC123に予め記憶させておく。IC123に予め記憶した一定時間経過後(オフ時間経過後)、FET121のゲート端子をローレベルにしてFET121をオフする。このオフ時間は予め設定された一定時間であり、本実施例では4μsに設定している。なお、このオフ時間は使用する回路や素子の特性に応じて適宜設定すればよい。

【0021】

なお、上記のIC123への電力は、トランス104の二次側からの電圧を降圧するDC/DCコンバータ(不図示)から供給されているものとする。

【0022】

また、出力電圧が小さい場合(軽負荷時)とは、電子装置が動作を実行せず、待機している状態であり、低電圧出力モードとも呼ばれる。

【0023】

以上、説明したように、同期整流方式の電源でトランスの一次側のピーク電流を固定する方式において、トランスの二次巻線の出力電圧の立ち下りを検出して、二次側の同期整流用FETの駆動を開始し、予め記憶した時間経過後に同期整流用のFETの駆動を停止するように制御する。これにより負荷の状態(大きさ)に関わらず安定して二次側の同期整流用のFETを正しく動作することができる。

【0024】

なお、本実施例1では二次側の整流用ダイオード122をFET121と個別に設ける構成したが、同期整流用のFETが備えるボディダイオードを利用することも可能である。

【実施例2】

【0025】

次に、実施例2について説明する。前述の実施例1では、トランスの一次側のピーク電流を固定する方式で、トランスの二次巻線の出力の立ち下りを検出して、二次側の同期整流用のFETの駆動を制御した。本実施例では、この実施例1の構成におけるトランスのインダクタンスのばらつきによる効率の低下を軽減する方式を提案する。

【0026】

実施例1で説明した構成では、例えば、トランスの一次側および二次側インダクタンスのばらつきや一次側の電流の検出回路である抵抗のばらつき等により、制御ICに記憶した時間と実際に二次側のFET121に電流が流れる時間に差が生じる可能性がある。特に、負荷がより大きい(重負荷ともいう)場合は、トランスの一次側に電流が流れ始めても、トランスの二次側のFET121を駆動し続けてしまう可能性がある。このような場合、一次側のFET6を再びオンする時、つまり、二次側巻線の巻き始め側に電圧が発生した時に、二次側のFET121が駆動し続けている状態になる。この状態では、二次側の電解コンデンサ120のマイナス側が逆方向にバイアスされて、二次側の電解コンデンサ120を劣化させる可能性がある。更には、電源の効率を低下させてしまう可能性もある。

【0027】

上記の記憶した時間と実際の時間に差が生じた時における、一次側の電流と二次側の電流の関係を図3に示す。301aは軽負荷時におけるトランスの一次側の電流,302bはトランスの二次側の電流を示しており、破線の区間がオフ時間となる。一方、302aが重負荷時におけるトランスの一次側の電流、302bが二次側の電流を示しており、二次側の電流がマイナス側に流れる期間(塗りつぶした三角形の領域)がトランスの一次側のFETと二次側のFETの駆動タイミングの重複期間である。この重複期間が生じると効率が低下する。なお同期整流方式ではなく、ダイオード整流方式であれば整流動作を終えた時点で自動的にオフするためこのような重複期間は略存在しない(ダイオードの逆回復時間は除く)。

【0028】

本実施例では、上記のようにトランスの一次側のFETと二次側のFETの駆動タイミングが重複しないようにするために、負荷が大きい重負荷状態では同期整流動作を行わずにダイオード整流とし、オフ時間が十分に確保できる軽負荷状態で同期整流動作を行うように制御する。これにより、重負荷時における効率の低下を回避することができる。なお、オフ時間が十分に確保できている軽負荷の場合には、制御ICに記憶した時間と実際にトランスの二次側のFETを駆動する時間に多少の差が生じても、トランスの一次側のFETが再びオンするまでの時間に余裕があり、上記のような効率の低下に陥ることはない。

【0029】

なお、オフ時間が確保できる軽負荷状態とは、電子機器では動作を待機している待機状態(例えば、スタンバイ状態やスリープ状態(省電力状態)、実施例1で説明した出力電圧が3.3Vの状態)である。一方、電子機器が動作状態であれば軽負荷状態に比べて負荷が大きい重負荷状態(実施例1で説明した出力電圧が24Vの状態)になる。電子機器では待機状態の時間の方が、動作状態(稼動している状態)に比べて長いため、電子機器のトータル消費電力を低下するには、この待機状態における消費電力を低下することが重要である。

【0030】

以下に、本実施例の動作について説明する。回路構成については実施例1(図1)の回路構成と略同様であるが、図4に示すように、二次側に整流用のダイオード124を追加している点が異なる。本実施例において実施例1と異なる動作は、トランスの二次側のFET121の駆動動作である。電子機器は、当然のことながら稼動状態のときに重負荷状態となり、機器が停止しているスタンバイ状態や機器の消費電力を下げたスリープ状態の時に軽負荷状態になる。本実施例では、電子機器の状態(モード)に応じてトランスの二次側のFETの動作を制御することを特徴とする。具体的には、重負荷状態においてはFET121を駆動させずに、ダイオード124によってダイオード整流動作に切り換える点が特徴である。

【0031】

図5のフロチャートに基づき具体的な動作について説明する。まず、ステップ401において、電子機器が稼動状態であるか否かを検知する。例えば、電子機器が動作を開始したときを稼動状態、それ以外を非稼動状態と定義することができる。例えば、動作を開始したタイミングで、装置が稼動状態に入ったと判断すればよい。電子機器が稼動状態の場合(S401がYesの場合)、重負荷状態であると判断し、制御IC123は同期整流用のFET121の動作(制御)は行わず、整流動作はダイオード122で行うようにする。つまり、制御IC123はFET121を駆動しないようにする。FET121の駆動制御を行わない場合、トランスの二次側の電圧は自動的にダイオード124で整流されるように動作する。この場合は、トランスの一次側に電流が流れている期間、二次巻線の巻き始め側を正極とする電圧が発生するが、ダイオード124でブロックされるため、負荷8側に電流は流れない。そして、一次側の電流が流れ終わった時点で今度は二次巻線の巻き終わり側を正極とする電圧が発生し、負荷8(および電解コンデンサ120)からダイオード124→トランス104の二次巻線というルートで電流が流れる。この時はダイオード124の順方向と電流の方向が同一であるためダイオード124で電流がブロックされることはない。一方、ステップ401がNoの場合、つまり電子機器がスタンバイ状態、または、スリープ状態に遷移した場合は、ステップ402において二次巻線の出力の立ち下がりエッジが来るまで待機する。立ち下がりエッジを検出すると(S402がYesの場合)、ステップ403において、FET121のゲート端子をハイレベルにして、FET121をオンさせる。次にステップ404においてタイマをセットする。このとき設定するタイマ値は実施例1で説明したトランスに二次側に電流が流れている時間と同じ値かもしくは若干小さめの値とする。若干小さめに設定する理由は、仮に二次側に電流が流れる時間よりも実際流れる時間がばらつき等で大きくなった場合に、二次側の平滑コンデンサ120から電流を逆流させてしまう可能性があり、エネルギを無駄に浪費してしまう可能性があるからである。ステップ405では、タイマがゼロになるまで待機し、タイマがゼロになった時点で、ステップ406にてFET121のゲート端子をローレベルに設定し、FET121をオフさせる。

【0032】

以上説明したように、電子機器が稼動状態である重負荷時は、同期整流方式ではなくダイオード整流方式とし、電子機器がスタンバイ状態、あるいは、スリープ状態の時に二次巻線の出力電圧の立ち下りを検出して同期整流用のFETの駆動を制御する。これにより、一次側のFETと二次側のFETの駆動タイミングが重複せずに駆動制御することができ、消費電力を抑えた同期整流動作が可能になる。

【0033】

なお、スリープ状態における更なる低消費電力化を図るため、スリープ状態で出力電圧を下げる電源装置に適用する場合は。電源の切り替え信号を基にしてダイオード整流と同期整流の切り替えを行うことができる。

【実施例3】

【0034】

次に実施例3について説明する。前述の実施例1、実施例2では、トランスの二次側のFETの駆動を電子機器の制御部(CPU)で制御していた。本実施例は、制御部ではなく駆動回路を用いて二次側のFETの駆動を制御する構成を特徴とする。

【0035】

以下、図6の回路図と図7の動作波形に基づき本実施例の構成について説明する。なお、図6において、実施例1(図1)と同じ構成要素については同一符号を付け、その説明は省略する。

【0036】

図6において、130は補助巻線であってトランスの二次側のFET121のゲート端子に電圧を供給するためのものである。C131はコンデンサであり、一端が補助巻線130の巻き終わり側に接続され、他端が二次側のFET121のゲート端子に接続されている。132は抵抗であり、一端が二次側のFET121のゲート端子に接続してあり、他端が補助巻線130の巻き始め側と二次側の出力のグランド側に接続してある。また、抵抗132と並列にダイオード133が、そのカソード側を二次側のFET121のゲート端子に接続されている。このような回路構成で、一次側のFET103がオフすると、補助巻線130の巻き終わり側を正極とする電圧が一定期間発生し、コンデンサ131を通して二次側のFET121のゲート端子に電圧が供給され始める。コンデンサ131と抵抗132は微分回路を形成しており、二次側のFET121に供給される電圧は徐々に減衰する。ダイオード133は二次側のFET121のゲート−ソース間の電圧が耐圧を超えないようにするために接続している。

【0037】

図7はFET121のゲート端子に印加される電圧波形を示したものである。なお、縦軸は電圧値(V)示し、横軸は時間(t)を示している。電圧の減衰曲線が二次側のFET121のオン電圧であるVthを下回るタイミングが二次側のFET121のオン期間になる。このオン期間が所定値になるようにコンデンサ131と抵抗132の値を調整する。このようにオン期間を所定値にして同期整流動作が可能になる。

【0038】

以上、説明したように、トランスに補助巻線を追加し、補助巻線の出力をコンデンサと抵抗による微分回路を通して二次側のFETのゲート端子に供給する。これにより、二次側のFETを一定時間オンすることができ、実施例1と同様に安定して正確な同期整流動作を実現することができる。

【0039】

なお、本実施例のようにハード的な回路を構成して同期整流用のFETを駆動制御した場合でも、実施例1や2と同様な動作を実現することが可能である。例えば、二次側のFETがオフするタイミングを二次側の電流がゼロになるタイミングよりも前(短く)設定し、二次側のFETのオフ直前でダイオード整流に切り替えるように制御すれば、各素子がばらついたとしても一次側のFETと二次側のFETの駆動タイミングを重複しないよう制御できる。

【0040】

また、実施例2の構成と同様に、整流用のダイオードを追加して、重負荷時においてダイオード整流に切り換える構成にすることも可能である。

【0041】

<電源装置の適用例の説明>

次に、上記で説明した実施例1〜実施例3の電源装置を適用した装置の一例を図9に基づき説明する。上記の実施例1乃至実施例3で説明した電流共振電源を例えばレーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源として適用することができる。画像形成装置における制御部としてのコントローラへの電力供給、また、用紙を搬送する搬送ローラの駆動部としてのモータへの電力供給のための電源として適用可能である。

【0042】

図9Aに画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。また、図9Bに画像形成装置の制御部としてのコントローラと駆動部としてのモータへの電源からの電力供給ラインを示す。前述の電流共振電源は、このような画像形成動作を制御するCPU310有するコントローラへ300の電力供給、また、画像形成のための駆動部としてのモータ312、313に電力を供給する低圧電源として適用できる。供給する電力としては、コントローラ300へは3.3V、モータへは24Vを供給する。例えばモータ312はシートを搬送する搬送ローラを駆動するモータ、モータ313は定着器214を駆動するモータである。

【0043】

このように画像形成装置の低電圧電源として適用した場合、画像形成動作を実行している状態の画像形成動作時は、モータに対して24Vを出力する状態であり、画像形成動作を実行せずに、動作を待機している省電力時は、コントローラに3.3Vを出力している状態である。

【0044】

なお、上記実施例1乃至3で説明した電源装置は、ここで説明した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【技術分野】

【0001】

本発明は、同期整流方式のスイッチング電源装置、その電源装置を搭載した画像形成装置に関する。

【背景技術】

【0002】

近年、電子機器装置の省電力化に伴い、電源装置の動作の効率化が要求されている。動作の効率化を実現した電源装置の一例として、特許文献1に記載の電源装置が提案されている。このような従来の電源装置の構成例を図8に示す。図8において、1は直流電源、2は主スイッチング素子としての電界効果トランジスタMOS−FET(以下、FETともいう)を制御する制御回路、4は主スイッチング素子としてのFET、5はトランスである。6は第2のスイッチング素子であるFET、7は平滑コンデンサ、8は電圧が供給される負荷、9は出力電圧検出回路、10はFET6に寄生するボディダイオード、11はFET6の駆動回路、12はFET6の電流検出回路である。

【0003】

直流電源1からの入力電圧は、制御回路2および駆動回路3で制御されるFET4を導通する(オンする)ことでトランス5の1次巻線n1に励磁エネルギとして蓄積される。一方、FET4を非導通する(オフする)タイミングでトランス5の1次巻線n1に励磁されたエネルギは2次巻線n2に変換され、ボディダイオード10と電流検知回路12を通して負荷に供給される。電流検知回路12は電流が流れたことを検出すると駆動回路11にオン信号を送出し、FET6をオンする。また、電流検知回路12は自身に流れている電流が所定値以下になると電流が流れ終ったと判断し、今度は駆動回路12にオフ信号を送出してFET6をオフする。ボディダイオード10の順方向電圧による損失に対してFET6による損失は非常に低い。このため、ボディダイオード10に流れる電流をFET6側に切り替えるように制御することで、効率の向上を図っていた。このような方式は同期整流方式と呼ばれており、FET6は同期整流用のFETとも呼ばれる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−115766号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記従来例では次のような課題があった。上記の同期整流方式の場合、動作の効率を向上するために同期整流用のFETのオンオフを検知する回路を設ける構成であり、この検知回路は複雑になる。従って、回路規模が大きくなり、コストアップを招いていた。また、二次巻線に流れる電流をカレントトランスで検知し、検知した電流によってFETのオンオフ制御を行う場合、軽負荷時では二次巻線に流れる電流量が僅かであり、カレントトランスから出力される電流も非常に小さくなってしまいFETのオンオフを正しく制御できない状態になる。FETのオンオフが正しく制御(駆動)されないと、効率の低下、また、消費電力が増大する可能性がある。このような軽負荷時(軽負荷状態)は、動作を待機しているスタンバイ状態や消費電力を低減する省エネモード(スリープモードともいう)を指し、所謂、電子機器におけるデフォルトの状態である。このデフォルトの状態は、電子装置において一日の中でかなりの時間を占める状態であり、FETのオンオフ動作による消費電力の増加や損失が電子機器のトータルの消費電力に大きく影響する。

【0006】

従って、本発明は、上記の点に鑑み、同期整流方式のスイッチング電源において、簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するための本発明の電源装置は、トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部とを有することを特徴とする。

【0008】

また、本発明の画像形成装置は、記録材に画像を形成するための画像形成部と、前記画像形成部の動作を制御する制御部と、前記制御部に電圧を供給する電源と、を備え、前記電源は、トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部を有することを特徴とする。

【発明の効果】

【0009】

以上説明したように、本発明によれば、簡単な回路構成で回路規模を小さくし、かつ、負荷の状態によらず同期整流動作を正しく実行して消費電力を低減することが可能になる。

【図面の簡単な説明】

【0010】

【図1】実施例1の電源装置の回路図

【図2】実施例1の回路の動作波形

【図3】実施例2の回路の動作波形

【図4】実施例2の電源装置の回路図

【図5】実施例2の動作を示すフロチャート

【図6】実施例3の電源装置の回路図

【図7】実施例3の回路の動作波形

【図8】従来の回路図

【図9】本発明の電源装置の適用例を示す図

【発明を実施するための形態】

【0011】

次に、上述した課題を解決するための本発明の具体的な構成について、以下に実施例に基づき説明する。なお、以下に示す実施例は一例であって、この発明の技術的範囲をそれらのみに限定する趣旨のものではない。

【実施例1】

【0012】

実施例1について以下に説明する。

図1は本発明の実施例1に係る電源装置の回路図であり、図2はその動作波形の一部を示した図である。以下、図1と図2を基にして、本実施例1の詳細説明を行う。

【0013】

101は直流電圧電源であり、コンセント(商用電源)から供給されてダイオードブリッジ(不図示)で全波整流されたAC電圧をコンデンサ(不図示)で平滑することで直流電圧が得られる。102は制御部としての制御ICであり、第一のスイッチング素子としてのMOS−FET103(以下、FETという)のオンオフ動作を制御する。104は一次側と二次側の絶縁を取りつつ一次側のエネルギを二次側に変換するトランスであり、一次巻線のインダクタンスをLp、二次巻線のインダクタンスはLsである。105はFET103の電流を検知する電流検知用の抵抗、120は二次側の平滑コンデンサ、121は第二のスイッチング素子としてのMOS−FET(以下、FETという)であり、二次側の電圧を整流する同期整流用のFETである。122は同じく二次側電圧を整流するためのダイオード(ボディダイオードともいう)、123は電子機器の動作を制御する制御IC(CPU)である。なお、8は電圧が出力される負荷である。

【0014】

電源装置が起動する際は、不図示の起動回路により制御IC102がFET103の駆動を開始する(オンする)。FET103がオンされるとトランス104の一次側、および、電流検知抵抗105に電流が流れるとともに、トランス104の一次巻き線に流れるピーク電流をIpとした場合、以下の式1で示されるエネルギE1が蓄積される。

E1=1/2Lp×Ip2 ・・・(式1)

このピーク電流Ipは電流検知抵抗によって電圧に変換され、制御IC102により一定値に制御される。このため入力電圧が変化してもトランス104に蓄積されるエネルギは略同じ値になる。例えば、100V系の電圧が入力される場合、入力電圧がAC85Vの時はピーク電流の傾きが立つ(単位時間あたりの変化量が大きい)ためFET103の駆動時間(オン時間ともいう)が短くなる。一方、入力電圧がAC140V時では電流の傾きが緩やかになる(単位時間あたりの変化量が小さい)ためFET103のオン時間は長くなる。このように入力電圧が異なっていても電流の流れている時間が異なるだけでピーク電流値は同じである。

【0015】

一方、二次巻線に蓄積されるエネルギE2は、二次巻線に発生するピーク電流をIsとすると、以下の式2で示される。

E2=1/2Ls×Is2 ・・・(式2)

フライバック方式の電源の場合は、トランスの一次側で発生したエネルギと二次側に変換するエネルギが等しいため、トランス104の二次巻線に流れる電流は、入力電圧によらずに一定時間流れることになる。本実施例1においては、トランスの一次側の電流のピーク値に基づいて出力を制御する方式が前提となる。

【0016】

入力電圧が一定の場合、FET103のオン時間も一定であり、また、トランスの二次側の電流のオン時間も一定になる。そして、負荷8の状態の変化(負荷が大きい/小さい)に対応するため、オフ時間を変化させて周波数を可変する。つまり負荷の状態が変化したとしても、トランスの二次側に電流が流れている時間は一定となる。

【0017】

図1の電源装置において、負荷8に対する出力電圧が大きい場合、例えば、24Vを出力している場合(重負荷時ともいう)は、二次側の電解コンデンサ120の出力側の電圧を検知してトランス104の一次側にフィードバックして、FET103の駆動を制御することに負荷に対して一定の電圧(24V)が出力するように制御される。なお、出力電圧が大きい場合とは、電子装置が動作を実行している状態であり、通常出力モードとも呼ばれる。

【0018】

一方、図2は、出力電圧が小さい場合、例えば、3.3Vを出力している場合(軽負荷時ともいう)の動作波形を示している。図2において、201はFET103に流れる電流波形、202はFET103のドレイン−ソース間の電圧波形、203はトランスの二次側の電流波形、204は同期整流用のFET121のドレイン−ソース間の電圧波形を示したものである。このように、FET121のドレイン−ソース間の電圧の立ち下がりとトランスの二次側の電流の流れ始めは同じタイミングになる。この立ち下りのタイミングを制御IC123で検出して、IC123がFET121ゲート端子をハイレベルにしてFET121を駆動する(オンする)。

【0019】

具体的には、ダイオード122のカソード端子に入力される電圧をIC123で検知して、その電圧の立下りタイミングを検知して、検知したタイミングでFET121を駆動するように制御する。

【0020】

また、FET121をオフするタイミングについては、本実施例1の方式がピーク電流を固定する方式を前提としているため、前述したようにオフ時間も固定となり、この時間を制御IC123に予め記憶させておく。IC123に予め記憶した一定時間経過後(オフ時間経過後)、FET121のゲート端子をローレベルにしてFET121をオフする。このオフ時間は予め設定された一定時間であり、本実施例では4μsに設定している。なお、このオフ時間は使用する回路や素子の特性に応じて適宜設定すればよい。

【0021】

なお、上記のIC123への電力は、トランス104の二次側からの電圧を降圧するDC/DCコンバータ(不図示)から供給されているものとする。

【0022】

また、出力電圧が小さい場合(軽負荷時)とは、電子装置が動作を実行せず、待機している状態であり、低電圧出力モードとも呼ばれる。

【0023】

以上、説明したように、同期整流方式の電源でトランスの一次側のピーク電流を固定する方式において、トランスの二次巻線の出力電圧の立ち下りを検出して、二次側の同期整流用FETの駆動を開始し、予め記憶した時間経過後に同期整流用のFETの駆動を停止するように制御する。これにより負荷の状態(大きさ)に関わらず安定して二次側の同期整流用のFETを正しく動作することができる。

【0024】

なお、本実施例1では二次側の整流用ダイオード122をFET121と個別に設ける構成したが、同期整流用のFETが備えるボディダイオードを利用することも可能である。

【実施例2】

【0025】

次に、実施例2について説明する。前述の実施例1では、トランスの一次側のピーク電流を固定する方式で、トランスの二次巻線の出力の立ち下りを検出して、二次側の同期整流用のFETの駆動を制御した。本実施例では、この実施例1の構成におけるトランスのインダクタンスのばらつきによる効率の低下を軽減する方式を提案する。

【0026】

実施例1で説明した構成では、例えば、トランスの一次側および二次側インダクタンスのばらつきや一次側の電流の検出回路である抵抗のばらつき等により、制御ICに記憶した時間と実際に二次側のFET121に電流が流れる時間に差が生じる可能性がある。特に、負荷がより大きい(重負荷ともいう)場合は、トランスの一次側に電流が流れ始めても、トランスの二次側のFET121を駆動し続けてしまう可能性がある。このような場合、一次側のFET6を再びオンする時、つまり、二次側巻線の巻き始め側に電圧が発生した時に、二次側のFET121が駆動し続けている状態になる。この状態では、二次側の電解コンデンサ120のマイナス側が逆方向にバイアスされて、二次側の電解コンデンサ120を劣化させる可能性がある。更には、電源の効率を低下させてしまう可能性もある。

【0027】

上記の記憶した時間と実際の時間に差が生じた時における、一次側の電流と二次側の電流の関係を図3に示す。301aは軽負荷時におけるトランスの一次側の電流,302bはトランスの二次側の電流を示しており、破線の区間がオフ時間となる。一方、302aが重負荷時におけるトランスの一次側の電流、302bが二次側の電流を示しており、二次側の電流がマイナス側に流れる期間(塗りつぶした三角形の領域)がトランスの一次側のFETと二次側のFETの駆動タイミングの重複期間である。この重複期間が生じると効率が低下する。なお同期整流方式ではなく、ダイオード整流方式であれば整流動作を終えた時点で自動的にオフするためこのような重複期間は略存在しない(ダイオードの逆回復時間は除く)。

【0028】

本実施例では、上記のようにトランスの一次側のFETと二次側のFETの駆動タイミングが重複しないようにするために、負荷が大きい重負荷状態では同期整流動作を行わずにダイオード整流とし、オフ時間が十分に確保できる軽負荷状態で同期整流動作を行うように制御する。これにより、重負荷時における効率の低下を回避することができる。なお、オフ時間が十分に確保できている軽負荷の場合には、制御ICに記憶した時間と実際にトランスの二次側のFETを駆動する時間に多少の差が生じても、トランスの一次側のFETが再びオンするまでの時間に余裕があり、上記のような効率の低下に陥ることはない。

【0029】

なお、オフ時間が確保できる軽負荷状態とは、電子機器では動作を待機している待機状態(例えば、スタンバイ状態やスリープ状態(省電力状態)、実施例1で説明した出力電圧が3.3Vの状態)である。一方、電子機器が動作状態であれば軽負荷状態に比べて負荷が大きい重負荷状態(実施例1で説明した出力電圧が24Vの状態)になる。電子機器では待機状態の時間の方が、動作状態(稼動している状態)に比べて長いため、電子機器のトータル消費電力を低下するには、この待機状態における消費電力を低下することが重要である。

【0030】

以下に、本実施例の動作について説明する。回路構成については実施例1(図1)の回路構成と略同様であるが、図4に示すように、二次側に整流用のダイオード124を追加している点が異なる。本実施例において実施例1と異なる動作は、トランスの二次側のFET121の駆動動作である。電子機器は、当然のことながら稼動状態のときに重負荷状態となり、機器が停止しているスタンバイ状態や機器の消費電力を下げたスリープ状態の時に軽負荷状態になる。本実施例では、電子機器の状態(モード)に応じてトランスの二次側のFETの動作を制御することを特徴とする。具体的には、重負荷状態においてはFET121を駆動させずに、ダイオード124によってダイオード整流動作に切り換える点が特徴である。

【0031】

図5のフロチャートに基づき具体的な動作について説明する。まず、ステップ401において、電子機器が稼動状態であるか否かを検知する。例えば、電子機器が動作を開始したときを稼動状態、それ以外を非稼動状態と定義することができる。例えば、動作を開始したタイミングで、装置が稼動状態に入ったと判断すればよい。電子機器が稼動状態の場合(S401がYesの場合)、重負荷状態であると判断し、制御IC123は同期整流用のFET121の動作(制御)は行わず、整流動作はダイオード122で行うようにする。つまり、制御IC123はFET121を駆動しないようにする。FET121の駆動制御を行わない場合、トランスの二次側の電圧は自動的にダイオード124で整流されるように動作する。この場合は、トランスの一次側に電流が流れている期間、二次巻線の巻き始め側を正極とする電圧が発生するが、ダイオード124でブロックされるため、負荷8側に電流は流れない。そして、一次側の電流が流れ終わった時点で今度は二次巻線の巻き終わり側を正極とする電圧が発生し、負荷8(および電解コンデンサ120)からダイオード124→トランス104の二次巻線というルートで電流が流れる。この時はダイオード124の順方向と電流の方向が同一であるためダイオード124で電流がブロックされることはない。一方、ステップ401がNoの場合、つまり電子機器がスタンバイ状態、または、スリープ状態に遷移した場合は、ステップ402において二次巻線の出力の立ち下がりエッジが来るまで待機する。立ち下がりエッジを検出すると(S402がYesの場合)、ステップ403において、FET121のゲート端子をハイレベルにして、FET121をオンさせる。次にステップ404においてタイマをセットする。このとき設定するタイマ値は実施例1で説明したトランスに二次側に電流が流れている時間と同じ値かもしくは若干小さめの値とする。若干小さめに設定する理由は、仮に二次側に電流が流れる時間よりも実際流れる時間がばらつき等で大きくなった場合に、二次側の平滑コンデンサ120から電流を逆流させてしまう可能性があり、エネルギを無駄に浪費してしまう可能性があるからである。ステップ405では、タイマがゼロになるまで待機し、タイマがゼロになった時点で、ステップ406にてFET121のゲート端子をローレベルに設定し、FET121をオフさせる。

【0032】

以上説明したように、電子機器が稼動状態である重負荷時は、同期整流方式ではなくダイオード整流方式とし、電子機器がスタンバイ状態、あるいは、スリープ状態の時に二次巻線の出力電圧の立ち下りを検出して同期整流用のFETの駆動を制御する。これにより、一次側のFETと二次側のFETの駆動タイミングが重複せずに駆動制御することができ、消費電力を抑えた同期整流動作が可能になる。

【0033】

なお、スリープ状態における更なる低消費電力化を図るため、スリープ状態で出力電圧を下げる電源装置に適用する場合は。電源の切り替え信号を基にしてダイオード整流と同期整流の切り替えを行うことができる。

【実施例3】

【0034】

次に実施例3について説明する。前述の実施例1、実施例2では、トランスの二次側のFETの駆動を電子機器の制御部(CPU)で制御していた。本実施例は、制御部ではなく駆動回路を用いて二次側のFETの駆動を制御する構成を特徴とする。

【0035】

以下、図6の回路図と図7の動作波形に基づき本実施例の構成について説明する。なお、図6において、実施例1(図1)と同じ構成要素については同一符号を付け、その説明は省略する。

【0036】

図6において、130は補助巻線であってトランスの二次側のFET121のゲート端子に電圧を供給するためのものである。C131はコンデンサであり、一端が補助巻線130の巻き終わり側に接続され、他端が二次側のFET121のゲート端子に接続されている。132は抵抗であり、一端が二次側のFET121のゲート端子に接続してあり、他端が補助巻線130の巻き始め側と二次側の出力のグランド側に接続してある。また、抵抗132と並列にダイオード133が、そのカソード側を二次側のFET121のゲート端子に接続されている。このような回路構成で、一次側のFET103がオフすると、補助巻線130の巻き終わり側を正極とする電圧が一定期間発生し、コンデンサ131を通して二次側のFET121のゲート端子に電圧が供給され始める。コンデンサ131と抵抗132は微分回路を形成しており、二次側のFET121に供給される電圧は徐々に減衰する。ダイオード133は二次側のFET121のゲート−ソース間の電圧が耐圧を超えないようにするために接続している。

【0037】

図7はFET121のゲート端子に印加される電圧波形を示したものである。なお、縦軸は電圧値(V)示し、横軸は時間(t)を示している。電圧の減衰曲線が二次側のFET121のオン電圧であるVthを下回るタイミングが二次側のFET121のオン期間になる。このオン期間が所定値になるようにコンデンサ131と抵抗132の値を調整する。このようにオン期間を所定値にして同期整流動作が可能になる。

【0038】

以上、説明したように、トランスに補助巻線を追加し、補助巻線の出力をコンデンサと抵抗による微分回路を通して二次側のFETのゲート端子に供給する。これにより、二次側のFETを一定時間オンすることができ、実施例1と同様に安定して正確な同期整流動作を実現することができる。

【0039】

なお、本実施例のようにハード的な回路を構成して同期整流用のFETを駆動制御した場合でも、実施例1や2と同様な動作を実現することが可能である。例えば、二次側のFETがオフするタイミングを二次側の電流がゼロになるタイミングよりも前(短く)設定し、二次側のFETのオフ直前でダイオード整流に切り替えるように制御すれば、各素子がばらついたとしても一次側のFETと二次側のFETの駆動タイミングを重複しないよう制御できる。

【0040】

また、実施例2の構成と同様に、整流用のダイオードを追加して、重負荷時においてダイオード整流に切り換える構成にすることも可能である。

【0041】

<電源装置の適用例の説明>

次に、上記で説明した実施例1〜実施例3の電源装置を適用した装置の一例を図9に基づき説明する。上記の実施例1乃至実施例3で説明した電流共振電源を例えばレーザビームプリンタ、複写機、ファクシミリ等の画像形成装置における低電圧電源として適用することができる。画像形成装置における制御部としてのコントローラへの電力供給、また、用紙を搬送する搬送ローラの駆動部としてのモータへの電力供給のための電源として適用可能である。

【0042】

図9Aに画像形成装置の一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ200は、画像形成部210として潜像が形成される像担持体としての感光ドラム211、感光ドラムに形成された潜像をトナーで現像する現像部212を備えている。そして感光ドラム211に現像されたトナー像をカセット216から供給された記録媒体としてのシート(不図示)に転写して、シートに転写したトナー像を定着器214で定着してトレイ215に排出する。また、図9Bに画像形成装置の制御部としてのコントローラと駆動部としてのモータへの電源からの電力供給ラインを示す。前述の電流共振電源は、このような画像形成動作を制御するCPU310有するコントローラへ300の電力供給、また、画像形成のための駆動部としてのモータ312、313に電力を供給する低圧電源として適用できる。供給する電力としては、コントローラ300へは3.3V、モータへは24Vを供給する。例えばモータ312はシートを搬送する搬送ローラを駆動するモータ、モータ313は定着器214を駆動するモータである。

【0043】

このように画像形成装置の低電圧電源として適用した場合、画像形成動作を実行している状態の画像形成動作時は、モータに対して24Vを出力する状態であり、画像形成動作を実行せずに、動作を待機している省電力時は、コントローラに3.3Vを出力している状態である。

【0044】

なお、上記実施例1乃至3で説明した電源装置は、ここで説明した画像形成装置に限らず他の電子機器の低電圧電源としても適用可能である。

【特許請求の範囲】

【請求項1】

トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、

前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、

前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、

前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部と

を有することを特徴とする電源装置。

【請求項2】

前記低電圧出力モード時よりも高い電圧を出力する通常出力モード時において、前記トランスの二次側の出力電圧に応じたオン期間になるように、前記第一スイッチング部が駆動することを特徴とする請求項1に記載の電源装置。

【請求項3】

前記トランスの二次側にダイオードを備え、

前記第二制御部は、前記通常出力モードにおいて、前記第二スイッチング部を停止することにより、前記ダイオードによって前記トランスの二次側の電圧が整流されることを特徴とする請求項1または2に記載の電源装置。

【請求項4】

更に、前記トランスの二次側に補助巻線を備え、

前記補助巻線からの電圧が前記二次側制御部に供給されることを特徴とする請求項1乃至3のいずれかの項に記載の電源装置。

【請求項5】

前記第二制御部は、コンデンサと抵抗からなる微分回路を含むことを特徴とする請求項1乃至4のいずれかの項に記載の電源装置。

【請求項6】

前記第二スイッチング部の駆動をオフするタイミングを、前記トランスの二次側の電流が流れ終る前に設定することを特徴とする請求項1乃至5のいずれかの項に記載の電源装置。

【請求項7】

前記第二スイッチング部はMOS−FETであることを特徴とする請求項1乃至6のいずれかの項に記載の電源装置。

【請求項8】

記録材に画像を形成するための画像形成部と、

前記画像形成部の動作を制御する制御部と、

前記制御部に電圧を供給する電源と、を備え、

前記電源は、

トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、

前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、

前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、

前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部を有することを特徴

とする画像形成装置。

【請求項9】

前記低電圧出力モード時よりも高い電圧を出力する通常出力モード時において、前記トランスの二次側の出力電圧に応じたオン期間になるように、前記第一スイッチング部が駆動することを特徴とする画像形成装置。

【請求項10】

前記トランスの二次側にダイオードを備え、

前記第二制御部は、前記通常出力モードにおいて、前記第二スイッチング部を停止することにより、前記ダイオードによって前記トランスの二次側の電圧が整流されることを特徴とする請求項8または9に記載の画像形成装置。

【請求項11】

前記通常出力モードとは、前記画像形成部によって画像形成を実行している動作状態であり、前記低電圧出力モードとは、前記画像形成部による画像形成を実行せずに待機している省電力状態であることを特徴とする請求項8乃至9のいずれかの項に記載の画像形成装置。

【請求項1】

トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、

前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、

前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、

前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部と

を有することを特徴とする電源装置。

【請求項2】

前記低電圧出力モード時よりも高い電圧を出力する通常出力モード時において、前記トランスの二次側の出力電圧に応じたオン期間になるように、前記第一スイッチング部が駆動することを特徴とする請求項1に記載の電源装置。

【請求項3】

前記トランスの二次側にダイオードを備え、

前記第二制御部は、前記通常出力モードにおいて、前記第二スイッチング部を停止することにより、前記ダイオードによって前記トランスの二次側の電圧が整流されることを特徴とする請求項1または2に記載の電源装置。

【請求項4】

更に、前記トランスの二次側に補助巻線を備え、

前記補助巻線からの電圧が前記二次側制御部に供給されることを特徴とする請求項1乃至3のいずれかの項に記載の電源装置。

【請求項5】

前記第二制御部は、コンデンサと抵抗からなる微分回路を含むことを特徴とする請求項1乃至4のいずれかの項に記載の電源装置。

【請求項6】

前記第二スイッチング部の駆動をオフするタイミングを、前記トランスの二次側の電流が流れ終る前に設定することを特徴とする請求項1乃至5のいずれかの項に記載の電源装置。

【請求項7】

前記第二スイッチング部はMOS−FETであることを特徴とする請求項1乃至6のいずれかの項に記載の電源装置。

【請求項8】

記録材に画像を形成するための画像形成部と、

前記画像形成部の動作を制御する制御部と、

前記制御部に電圧を供給する電源と、を備え、

前記電源は、

トランスの一次側に入力される電圧をスイッチングする第一スイッチング部と、

前記第一スイッチング部の駆動を制御することにより、前記トランスの二次側の出力電圧を制御する第一制御部と、

前記トランスの二次側に接続され、前記トランスの二次側に発生する電圧に応じて駆動する第二スイッチング部と、

前記トランスの二次側の出力電圧を低下させる低電圧出力モード時において、前記トランスの二次側の出力電圧の立ち上がりに応じて駆動を開始し、予め設定した時間経過後に駆動を停止するように第二スイッチング部の駆動を制御する第二制御部を有することを特徴

とする画像形成装置。

【請求項9】

前記低電圧出力モード時よりも高い電圧を出力する通常出力モード時において、前記トランスの二次側の出力電圧に応じたオン期間になるように、前記第一スイッチング部が駆動することを特徴とする画像形成装置。

【請求項10】

前記トランスの二次側にダイオードを備え、

前記第二制御部は、前記通常出力モードにおいて、前記第二スイッチング部を停止することにより、前記ダイオードによって前記トランスの二次側の電圧が整流されることを特徴とする請求項8または9に記載の画像形成装置。

【請求項11】

前記通常出力モードとは、前記画像形成部によって画像形成を実行している動作状態であり、前記低電圧出力モードとは、前記画像形成部による画像形成を実行せずに待機している省電力状態であることを特徴とする請求項8乃至9のいずれかの項に記載の画像形成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−114978(P2012−114978A)

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願番号】特願2010−259292(P2010−259292)

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]