電源装置及び発光素子駆動装置

【課題】デジタル回路からの出力信号のライン数を増やすことなく、簡単な回路構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックを生成する。

【解決手段】ADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、出力電圧Voutの安定化を図る。マイクロプロセッサ4からは、単独のパルス信号S3の出力ラインだけがあればよい。また、駆動信号S5の周波数はランプ信号S2と同一で、クロック信号S1に同期する。したがって、クロック信号S1ひいては駆動信号S5の周波数は、コンバータ2の仕様を考慮して決定できる。一方、パルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよい。

【解決手段】ADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、出力電圧Voutの安定化を図る。マイクロプロセッサ4からは、単独のパルス信号S3の出力ラインだけがあればよい。また、駆動信号S5の周波数はランプ信号S2と同一で、クロック信号S1に同期する。したがって、クロック信号S1ひいては駆動信号S5の周波数は、コンバータ2の仕様を考慮して決定できる。一方、パルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよい。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源装置及び発光素子駆動装置に関し、特に、マイクロプロセッサを用いてPWM制御を行なう電源装置及び発光素子駆動装置に関する。

【背景技術】

【0002】

特許文献1では、デジタル回路としてのマイクロプロセッサが制御指令値を算出し、その算出値を示すデジタル信号に基づいて、パルス発振器が所定のデューティ比の駆動信号を生成する発光素子駆動装置が開示されている。デジタル信号が10ビットの信号であれば、そのデジタル値0〜1023に基づいて駆動信号のデューティ比が変化する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平9−331017号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

デューティ比を調整できる段階は、デジタル信号のビット数に依存する。デューティ比を細かく調整したい場合には、デジタル信号のビット数を増やさなければならない。デジタル信号のビット数を増やすと、マイクロプロセッサからの出力信号のライン数が増加する。マイクロコンピュータ内で駆動信号を生成すれば、マイクロコンピュータの出力信号のライン数を減らすことができるが、駆動信号の周波数を高くしたい場合には、マイクロコンピュータの動作クロックの周波数を高くしなければならない。

【0005】

そこで本発明は、デジタル回路からの出力信号のライン数を増やすことなく、簡単な回路構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成できる電源装置及び発光素子駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、スイッチング素子のオン・オフ動作により電力を供給するコンバータと、制御指令値をデジタル演算により算出して、前記コンバータを制御するデジタル回路と、を備えた電源装置であって、前記コンバータの出力電圧を検出する電圧検出手段と、前記電圧検出手段により検出された電圧値をデジタル値に変換する変換回路と、前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、前記パルス信号が入力される積分回路と、前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えて構成される。

【0007】

本発明は、スイッチング素子のオン・オフ動作により電力を供給するコンバータと、制御指令値をデジタル演算により算出し、前記コンバータを制御するデジタル回路とを備え、前記コンバータから供給される電力により発光素子を駆動する発光素子駆動装置であって、前記発光素子に流れる電流を検出する電流検出手段と、前記電流検出手段により検出された電圧値をデジタル値に変換する変換回路と、前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、前記パルス信号が入力される積分回路と、前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えて構成される。

【発明の効果】

【0008】

本発明の電源装置によれば、コンバータの出力電圧を反映した変換回路からのデジタル値に基づいて、演算回路が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、パルス信号発生回路がパルス信号のデューティ比を決定し、積分回路からの出力電圧を連続的に上昇又は減少させることで、コンバータの出力電圧の安定化を図る。したがって、デジタル回路からは単独のパルス信号の出力ラインだけがあればよい。

【0009】

また、駆動信号生成回路で生成される駆動信号の周波数はランプ信号と同一となり、このランプ信号の周波数はクロック信号に同期したものとなる。したがって、クロック信号ひいては駆動信号の周波数は、演算回路により制御指令値を算出するための処理時間ではなく、コンバータの仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号の周波数は、ランプ信号の周波数よりも低くてもよく、駆動信号の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0010】

このように、デジタル回路からの出力ライン数を増やすことなく、積分回路を付加しただけの簡単な構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成することができる。

【0011】

本発明の発光素子駆動装置によれば、発光素子への出力電流を反映した変換回路からのデジタル値に基づいて、演算回路が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、パルス信号発生回路がパルス信号のデューティ比を決定し、積分回路からの出力電圧を連続的に上昇又は減少させることで、発光素子への出力電流の安定化を図る。したがって、デジタル回路からは単独のパルス信号の出力ラインだけがあればよい。

【0012】

また、駆動信号生成回路で生成される駆動信号の周波数はランプ信号と同一となり、このランプ信号の周波数はクロック信号に同期したものとなる。したがって、クロック信号ひいては駆動信号の周波数は、演算回路により制御指令値を算出するための処理時間ではなく、コンバータの仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号の周波数は、ランプ信号の周波数よりも低くてもよく、駆動信号の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0013】

このように、デジタル回路からの出力ライン数を増やすことなく、積分回路を付加しただけの簡単な構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成することができる。

【図面の簡単な説明】

【0014】

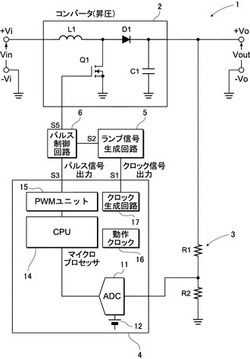

【図1】本発明の第一の実施形態に係る電源装置の回路図である。

【図2】同上、ランプ信号生成回路の回路図である。

【図3】同上、パルス制御回路の回路図である。

【図4】同上、各部のタイミングチャートである。

【図5】本発明の第二の実施形態に係る電源装置の回路図である。

【発明を実施するための形態】

【0015】

本発明に係る電源装置及び発光素子駆動装置について、添付図面を参照して説明する。

【0016】

図1は、本発明に係る第一の実施形態の電源装置を示している。この実施形態の電源装置は、出力電圧Voutを一定に制御する定電圧出力回路ブロック1の構成を有する。定電圧出力回路ブロック1は、制御対象となるコンバータ2と、コンバータ2に対する電圧帰還ループを形成する電圧検出回路3,マイクロプロセッサ4,ランプ信号生成回路5及びパルス制御回路6とにより構成される。

【0017】

コンバータ2は、入力端子+Vi,−Vi間に印加される直流入力電圧Vinを、直流出力電圧Voutに変換して出力端子+Vo,−Voに供給するもので、出力端子+Vo,−Vo間には図示しない負荷が接続される。ここでのコンバータ2は、入力電圧Vinよりも高い出力電圧Voutに変換するために、チョークコイルL1と、スイッチング素子Q1と、ダイオードD1と、コンデンサC1とによる昇圧チョッパ回路を構成している。より具体的には、入力端子+Vi,−Viの両端間に、チョークコイルL1とスイッチング素子Q1との直列回路が接続され、スイッチング素子Q1の両端間に、ダイオードD1とコンデンサC1との直列回路が接続され、コンデンサC1の両端に出力端子+Vo,−Voが接続される。スイッチング素子Q1はNチャネルのMOS型FETであるが、バイポーラトランジスタなどの別な制御端子付き半導体素子を利用してもよい。

【0018】

電圧検出回路3は、コンバータ2からの出力電圧Voutを検出するもので、出力端子+Vo,−Vo間に分圧用の抵抗R1,R2の直列回路を接続して構成される。抵抗R1,R2の接続点には、出力電圧Voutを分圧した電圧値のアナログ検出電圧が生成される。

【0019】

デジタル回路に相当するマイクロプロセッサ4は、出力電圧Voutを安定化させるための制御指令値をデジタル演算により算出するもので、ADC11と、基準電源12と、CPU14と、PWMユニット15と、動作クロック16と、クロック生成回路17とをそれぞれ内蔵する。

【0020】

ADC11は、電圧検出回路3からの電圧値(アナログ検出電圧)をデジタル値に変換するアナログ−デジタル変換回路に相当する。また基準電源12は、ADC11がアナログ値をデジタル値に変換するときに使用する基準信号を、基準電圧として生成するものである。

【0021】

CPU(中央演算ユニット)14は、ADC11で得られたデジタル信号に基づいてデジタルの制御指令値を算出する演算回路に相当する。またPWM(パルス幅制御)ユニット15は、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を、マイクロプロセッサ4の外部に出力するパルス信号発生回路に相当する。

【0022】

動作クロック16は、CPU14を一定の周期で動作させるための動作クロック信号を出力するものである。またクロック生成回路17は、動作クロック16からの動作クロック信号を分周したクロック信号(同期クロック信号)S1を、マイクロプロセッサ4の外部に出力する分周器として設けられる。本実施形態では、動作クロック16からの例えば8MHzの動作クロック信号を、クロック生成回路17で16分周して、500kHzのクロック信号S1をランプ信号生成回路5に送出する。このクロック信号S1は、後述する駆動信号S5の周波数を決定するものである。

【0023】

マイクロプロセッサ4はその他に、動作クロック16からの動作クロック信号を分周して、クロック信号S1よりも低い周波数のクロック信号をPWMユニット15に出力する別なクロック生成回路(図示せず)を内蔵する。本実施形態では、動作クロック16からの例えば8MHzの動作クロック信号を、別なクロック生成回路で256分周して、31.25kHzのクロック信号をPWMユニット15に送出する。これによりPWMユニット15は、デューティ比が0/256〜255/256の範囲で、周波数が31.25kHzのパルス信号S3を、パルス制御回路6に出力することができる。したがってCPU14も、動作クロック信号の256クロック毎に、新たな制御指令値を決定するようになっている。

【0024】

ランプ信号生成回路5は、マイクロプロセッサ4から出力されるクロック信号S1に基づいて、鋸波状のランプ信号S2を生成するものである。ランプ信号生成回路5からは、クロック信号S1と同じ周波数のランプ信号S2がパルス制御回路6に出力される。

【0025】

図2は、ランプ信号生成回路5の回路例を示したものである。同図において、ランプ信号生成回路5は、スイッチ素子Q2と、コンデンサC2,C3と、ダイオードD2と、抵抗R4,R5,R6とにより構成される。具体的には、クロック信号S1の入力端子21にコンデンサC2の一端を接続し、コンデンサC2の他端にダイオードD2のカソードと抵抗R4の一端を接続し、抵抗R4の他端に抵抗R5の一端とNPN型トランジスタからなるスイッチ素子Q2のベースを接続する。また、図示しない内部電源からの動作電圧Vccのラインに抵抗R6の一端を接続し、抵抗R6の他端にスイッチ素子Q2のコレクタとコンデンサC3の一端を接続する。そして、ダイオードD2のアノード,抵抗R5の他端,スイッチ素子Q2のエミッタ及びコンデンサC3の他端を接地ラインに共通して接続し、抵抗R6とコンデンサC3の接続点であって、スイッチ素子Q2のコレクタを、ランプ信号S2の出力端子22に接続して、ランプ信号生成回路5を構成する。

【0026】

再度図1に戻り、パルス制御回路6は、マイクロプロセッサ4からのパルス信号S3のデューティ比に応じたパルス幅を有する駆動信号S5を、ランプ信号生成回路5から出力されるランプ信号S2と同じ周期で、スイッチング素子Q1の制御端子であるゲートに送出するものである。

【0027】

図3は、パルス制御回路6の回路例を示したものである。同図において、パルス制御回路6は、積分回路28を構成するコンデンサC4及び抵抗R7と、コンパレータCMPとにより構成される。具体的には、ランプ信号S2の入力端子24に、コンパレータCMPの一方の入力端子である反転入力端子を接続し、パルス信号S3の入力端子25に、積分回路28の入力端である抵抗R7の一端を接続し、積分回路28の出力端である抵抗R7の他端とコンデンサC4の一端との接続点に、コンパレータCMPの他方の入力端子である非反転入力端子を接続する。そして、コンデンサC4の他端を接地ラインに接続し、コンパレータCMPの出力端子を駆動信号S5の出力端子26に接続して、パルス制御回路6を構成する。

【0028】

次に、上記構成についてその作用を説明する。この説明では、図4に示す各部のタイミングチャートを参照する。同図において、最上段にあるのは動作クロック16からの動作クロック信号を示しており、以下、クロック信号S1,ランプ信号S2,CPU14で生成される制御指令値,パルス信号S3,前記図3で示したコンデンサC4の両端間電圧S4,駆動信号S5をそれぞれ示している。

【0029】

パルス制御回路6からスイッチング素子Q1のゲートにパルス状の駆動信号S5が与えられると、スイッチング素子Q1はオン・オフ動作を繰り返す。スイッチング素子Q1がオンすると、チョークコイルL1に入力電圧Vinが印加されるので、ダイオードD1はオフ状態となり、平滑用のコンデンサC1の放電電圧が出力端子+Vo,−Voから負荷に出力電圧Voutとして供給される。スイッチング素子Q1がオフすると、入力電圧VinにチョークコイルL1の逆起電圧が重畳されるので、ダイオードD1はオン状態となり、そのダイオードD1を通してコンデンサC1が充電されると共に、入力電圧Vinよりも高い出力電圧Voutが、出力端子+Vo,−Voから負荷に供給される。

【0030】

コンバータ2からの出力電圧Voutは、電圧検出回路3によって監視される。電圧検出回路3は、出力電圧Voutを抵抗R1,R2で分圧して得たアナログ検出電圧を、マイクロプロセッサ4のADC11に送出する。ADC11では、基準電源12からの基準電圧を利用して、前記アナログ検出電圧をデジタル値に変換し、これをCPU14に送出する。

【0031】

CPU14は、電圧検出回路3及びADC11で得られた検出電圧の値に基づいて、制御指令値を算出する。この場合、出力電圧Voutが高くなると制御指令値が低くなり、逆に出力電圧Voutが低くなると制御指令値が高くなる。PWMユニット15は、CPU14で算出した制御指令値に基づいて決定されるデューティ比のパルス信号S3を生成する。この場合、制御指令値が大きくなるとパルス信号S3のデューティ比は大きくなり、逆に制御指令値が小さくなるとパルス信号S3のデューティ比は小さくなる。

【0032】

PWMユニット15は、動作クロック16からの動作クロック信号を256分周した約30kHzのクロック信号が与えられ、このクロック信号と同じ周波数のパルス信号S3を生成する。そのためCPU14は、パルス信号S3と同じ周波数毎に、新たな制御指令値を決定する。図4に示す例では、パルス信号S3の周波数に合わせて、CPU14が「10」,「50」,「128」,「40」,「30」の各制御指令値を順に算出し、その制御指令値に応じたデューティ比のパルス信号S3が、PWMユニット15により生成され、マイクロプロセッサ4からパルス制御回路6に送出される。

【0033】

マイクロプロセッサ4は、前記パルス信号S3の他に、クロック生成回路17からのクロック信号S1をランプ信号生成回路5に送出する。ランプ信号生成回路5は、マイクロプロセッサ4からのクロック信号S1に基いて、図2で示したコンデンサC3の充放電動作により、ランプ信号S2を生成する。より具体的には、入力端子21におけるクロック信号S1は、コンデンサC2を通してトリガ状に波形整形され、抵抗R4,R5で分圧された後に、スイッチ素子Q2のベースに与えられる。このトリガ信号の電圧レベルが立ち上がると、スイッチ素子Q2のエミッタ・コレクタ間がオンすることにより、コンデンサC3を放電する一方で、トリガ信号の電圧レベルが低下すると、スイッチ素子Q2のエミッタ・コレクタ間がオフすることにより、抵抗R6を通して動作電圧VccがコンデンサC3に与えられ、コンデンサC3を充電する。つまり、コンデンサC3の放電は、クロック信号S1の立ち上がりエッジに同期して行われ、その後、コンデンサC3の充電が開始する。したがって、ランプ信号S2は、マイクロプロセッサ4からのクロック信号S1に同期した信号になる。また、クロック信号S1の周波数を変えることにより、ランプ信号S2の周波数を変えることができる。

【0034】

前述したPWMユニット15からのパルス信号S3は、パルス制御回路6の積分回路28に入力される。積分回路28の出力電圧となるコンデンサC4の両端間電圧S4は、パルス信号S3のデューティ比に基づいて上昇又は下降する。この場合、図4に示すように、電圧C4は積分回路28を構成する抵抗R7とコンデンサC4の時定数に依存して、パルス信号S3がH(高)レベルになると上昇し、パルス信号S3がL(低)レベルになると下降して、固定したパルス信号S3の一周期の間で常に変動する。また、パルス信号S3のデューティ比が大きくなるほど、電圧C4が上昇し続ける時間は長くなり、その後の電圧C4が下降し続ける時間は短くなる。

【0035】

ランプ信号生成回路5からのランプ信号S2は、パルス制御回路6のコンパレータCMPの反転入力端子に入力され、積分回路28の出力電圧であるコンデンサC4の両端間電圧S4は、コンパレータCMPの非反転入力端子に入力される。コンパレータCMPは、ランプ信号S2の電圧値とコンデンサC4の両端間電圧S4との比較結果に基づくデューティ比のパルス駆動信号S5を、スイッチング素子Q1のゲートに送出する。これにより、コンバータ2からの出力電圧Voutが一定値となるように、スイッチング素子Q1がオン・オフ動作される。

【0036】

前記駆動信号S5の周波数は、ランプ信号S2の周波数と同じになり、この駆動信号S5のパルス幅は、コンデンサC4の両端間電圧S4により調整される。図3に示す回路では、ランプ信号S2の電圧レベルよりも、コンデンサC4の両端間電圧S4が高くなると、Hレベルの駆動信号が生成される。したがって、コンデンサC4の両端間電圧S4が高くなるに従い、スイッチング素子2をオンにする駆動信号S5のパルス幅も広がる。積分回路28に入力されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよい。

【0037】

本実施形態では、(0〜255)×動作クロック信号の周期(125nS)の範囲で、パルス信号S3のパルス幅が変化する。パルス信号S3は、動作クロック16からの動作クロック信号(8MHz)に基づいて生成されるので、そのパルス幅は125nS単位で段階的に変化する。パルス信号S3のパルス幅が変化することにより、コンデンサC4の両端間電圧S4は絶えず上昇又は減少し、この電圧S4とランプ信号S2がコンパレータCMPにそれぞれ入力される。したがって、コンパレータCMPから出力される駆動信号S5は、コンデンサC4の両端間電圧S4の上昇又は減少に伴って、そのパルス幅を1パルス毎に絶えず変化させることが可能になる。

【0038】

また、駆動信号S5の周波数(500kHz)は、チョークコイルL1のサイズとスイッチング素子Q1のスイッチングロスの双方を考慮して決定される。その理由は、周波数を低くするとチョークコイルL1のサイズが大きくなり、周波数を高くすると、スイッチング素子Q1のスイッチングロスが増加するからである。クロック生成回路17は、CPU14で制御指令値を算出するための処理時間を確保するのに、動作クロック信号を16分周してはおらず、コンバータ2の仕様に基づいて、クロック信号S1の周波数を決定することができる。

【0039】

本実施形態において、動作クロック信号の周波数は例えば500kHzであっても、動作クロック16にクロック生成回路17の機能を兼用させることで、駆動信号S5の周波数を500kHzのままにした回路が実現可能である。この場合、パルス信号S3の周波数は500/256=1.95kHzとなる。またCPU14は、動作クロック信号に対して256クロック毎に新たな制御指令値を算出できればよく、動作クロック信号の周波数に依存しない。

【0040】

以上のように、本実施形態の電源装置は、スイッチング素子Q1のオン・オフ動作により負荷に電力を供給するコンバータ2と、制御指令値をデジタル演算により算出して、コンバータ2からの出力電圧Voutを所定値に制御するデジタル回路としてのマイクロプロセッサ4とを備えている。また、コンバータ2の出力電圧Voutを検出する電圧検出手段としての電圧検出回路3を備え、マイクロプロセッサ4は、電圧検出回路3により検出された電圧値のアナログ検出電圧を、デジタル値に変換する変換回路としてのADC11と、ADC11からのデジタル値に基づいて前記制御指令値を算出する演算回路としてのCPU14と、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を出力するパルス信号発生回路としてのPWMユニット15と、を備える。さらにマイクロプロセッサ4の外部には、CPU14に与えられる動作クロック信号に基づいて生成されたクロック信号S1に同期して、鋸波状のランプ信号S2を出力するランプ信号発生回路5と、パルス信号S3が入力される積分回路28と、ランプ信号S2と積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4との比較結果に基づいて、スイッチング素子Q1をオン・オフ動作させるための駆動信号S5を生成する駆動信号生成回路としてのコンパレータCMPと、を備えている。

【0041】

この場合、コンバータ2の出力電圧Voutを反映したADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4を連続的に上昇又は減少させることで、コンバータ2の出力電圧Voutの安定化を図る。したがって、マイクロプロセッサ4から積分回路28へは、単独のパルス信号S3の出力ラインだけがあればよい。

【0042】

また、コンパレータCMPで生成される駆動信号S5の周波数はランプ信号S2と同一となり、このランプ信号S2の周波数はクロック信号S1に同期したものとなる。したがって、クロック信号S1ひいては駆動信号S5の周波数は、CPU14により制御指令値を算出するための処理時間ではなく、コンバータ2の仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよく、駆動信号S5の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0043】

このように、マイクロプロセッサ4からの出力ライン数を増やすことなく、積分回路28を付加しただけの簡単な構成で、同じ周波数の駆動信号S5を従来よりも低い周波数の動作クロックで生成することが可能になる。

【0044】

次に、本発明に係る第二の実施形態について、図5を参照しながら説明する。本実施形態は、出力端子+Vo,−Vo間に接続する負荷が、特に一乃至複数の発光素子30である発光素子駆動装置に適用される。当該発光素子駆動装置は、発光素子30に流れる出力電流Ioutを一定に制御する定電流出力回路ブロック100の構成を有している。定電流出力回路ブロック100は、制御対象となるコンバータ2と、コンバータ2に対する電流帰還ループを形成する電流検出回路31,マイクロプロセッサ4,ランプ信号生成回路5及びパルス制御回路6とにより構成され、電流検出回路31以外の各部の構成は、第一実施形態の定電圧出力回路ブロック1と全く共通している。

【0045】

電流検出回路31は、前記出力電流Ioutを検出するもので、コンバータ2と発光素子30との間の出力ライン間に電流検出器としての抵抗R3を挿入接続して構成される。抵抗R1の両端間には、出力電流Ioutに比例した電流値のアナログ検出電流が生成される。電流検出器は抵抗R3に限らず、より損失の少ないカレントトランスなどを用いてもよい。

【0046】

発光素子駆動装置としての動作は、負荷が発光素子30に特定され、アナログ検出電圧がアナログ検出電流に置き換わっただけで、第一の実施形態で示した電源装置と共通している。したがって、ここでは再度の説明は行なわない。

【0047】

本実施形態の発光素子駆動装置は、スイッチング素子Q1のオン・オフ動作により電力を供給するコンバータ2と、制御指令値をデジタル演算により算出して、コンバータ2からの出力電圧Voutを所定値に制御するデジタル回路としてのマイクロプロセッサ4とを備え、コンバータ2から供給される電力により発光素子30を駆動する構成を有している。また、発光素子30への出力電流Ioutを検出する電流検出手段としての電流検出回路31を備え、マイクロプロセッサ4は、電流検出回路31により検出された電圧値のアナログ検出電流を、デジタル値に変換する変換回路としてのADC11と、ADC11からのデジタル値に基づいて前記制御指令値を算出する演算回路としてのCPU14と、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を出力するパルス信号発生回路としてのPWMユニット15と、を備える。さらにマイクロプロセッサ4の外部には、CPU14に与えられる動作クロック信号に基づいて生成されたクロック信号S1に同期して、鋸波状のランプ信号S2を出力するランプ信号発生回路5と、パルス信号S3が入力される積分回路28と、ランプ信号S2と積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4との比較結果に基づいて、スイッチング素子Q1をオン・オフ動作させるための駆動信号S5を生成する駆動信号生成回路としてのコンパレータCMPと、を備えている。

【0048】

この場合、発光素子30への出力電流Ioutを反映したADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4を連続的に上昇又は減少させることで、発光素子30への出力電流Ioutの安定化を図る。したがって、マイクロプロセッサ4から積分回路28へは、単独のパルス信号S3の出力ラインだけがあればよい。

【0049】

また、コンパレータCMPで生成される駆動信号S5の周波数はランプ信号S2と同一となり、このランプ信号S2の周波数はクロック信号S1に同期したものとなる。したがって、クロック信号S1ひいては駆動信号S5の周波数は、CPU14により制御指令値を算出するための処理時間ではなく、コンバータ2の仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよく、駆動信号S5の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0050】

このように、マイクロプロセッサ4からの出力ライン数を増やすことなく、積分回路28を付加しただけの簡単な構成で、同じ周波数の駆動信号S5を従来よりも低い周波数の動作クロックで生成することが可能になる。

【0051】

以上、本発明の実施の形態を説明したが、これは本発明の説明のための例示であって、本発明の範囲をこの実施の形態にのみ限定する趣旨ではない。本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。例えばコンバータ2は、図示した昇圧チョッパ回路に限らず、一乃至複数のスイッチング素子を備えたあらゆる回路構成のコンバータに適用できる。また、最終的に出力電圧Voutや出力電流Ioutが安定化するように、各部の信号レベルや論理構成を上記各実施形態に示したものと変更しても構わない。

【符号の説明】

【0052】

2 コンバータ

3 電圧検出回路(電圧検出手段)

4 マイクロプロセッサ(デジタル回路)

5 ランプ信号発生回路

11 ADC(変換回路)

14 CPU(演算回路)

15 PWMユニット(パルス信号発生回路)

28 積分回路

31 電流検出回路(電流検出手段)

CMP コンパレータ(駆動信号生成回路)

Q1 スイッチング素子

【技術分野】

【0001】

本発明は、電源装置及び発光素子駆動装置に関し、特に、マイクロプロセッサを用いてPWM制御を行なう電源装置及び発光素子駆動装置に関する。

【背景技術】

【0002】

特許文献1では、デジタル回路としてのマイクロプロセッサが制御指令値を算出し、その算出値を示すデジタル信号に基づいて、パルス発振器が所定のデューティ比の駆動信号を生成する発光素子駆動装置が開示されている。デジタル信号が10ビットの信号であれば、そのデジタル値0〜1023に基づいて駆動信号のデューティ比が変化する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開平9−331017号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

デューティ比を調整できる段階は、デジタル信号のビット数に依存する。デューティ比を細かく調整したい場合には、デジタル信号のビット数を増やさなければならない。デジタル信号のビット数を増やすと、マイクロプロセッサからの出力信号のライン数が増加する。マイクロコンピュータ内で駆動信号を生成すれば、マイクロコンピュータの出力信号のライン数を減らすことができるが、駆動信号の周波数を高くしたい場合には、マイクロコンピュータの動作クロックの周波数を高くしなければならない。

【0005】

そこで本発明は、デジタル回路からの出力信号のライン数を増やすことなく、簡単な回路構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成できる電源装置及び発光素子駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、スイッチング素子のオン・オフ動作により電力を供給するコンバータと、制御指令値をデジタル演算により算出して、前記コンバータを制御するデジタル回路と、を備えた電源装置であって、前記コンバータの出力電圧を検出する電圧検出手段と、前記電圧検出手段により検出された電圧値をデジタル値に変換する変換回路と、前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、前記パルス信号が入力される積分回路と、前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えて構成される。

【0007】

本発明は、スイッチング素子のオン・オフ動作により電力を供給するコンバータと、制御指令値をデジタル演算により算出し、前記コンバータを制御するデジタル回路とを備え、前記コンバータから供給される電力により発光素子を駆動する発光素子駆動装置であって、前記発光素子に流れる電流を検出する電流検出手段と、前記電流検出手段により検出された電圧値をデジタル値に変換する変換回路と、前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、前記パルス信号が入力される積分回路と、前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えて構成される。

【発明の効果】

【0008】

本発明の電源装置によれば、コンバータの出力電圧を反映した変換回路からのデジタル値に基づいて、演算回路が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、パルス信号発生回路がパルス信号のデューティ比を決定し、積分回路からの出力電圧を連続的に上昇又は減少させることで、コンバータの出力電圧の安定化を図る。したがって、デジタル回路からは単独のパルス信号の出力ラインだけがあればよい。

【0009】

また、駆動信号生成回路で生成される駆動信号の周波数はランプ信号と同一となり、このランプ信号の周波数はクロック信号に同期したものとなる。したがって、クロック信号ひいては駆動信号の周波数は、演算回路により制御指令値を算出するための処理時間ではなく、コンバータの仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号の周波数は、ランプ信号の周波数よりも低くてもよく、駆動信号の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0010】

このように、デジタル回路からの出力ライン数を増やすことなく、積分回路を付加しただけの簡単な構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成することができる。

【0011】

本発明の発光素子駆動装置によれば、発光素子への出力電流を反映した変換回路からのデジタル値に基づいて、演算回路が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、パルス信号発生回路がパルス信号のデューティ比を決定し、積分回路からの出力電圧を連続的に上昇又は減少させることで、発光素子への出力電流の安定化を図る。したがって、デジタル回路からは単独のパルス信号の出力ラインだけがあればよい。

【0012】

また、駆動信号生成回路で生成される駆動信号の周波数はランプ信号と同一となり、このランプ信号の周波数はクロック信号に同期したものとなる。したがって、クロック信号ひいては駆動信号の周波数は、演算回路により制御指令値を算出するための処理時間ではなく、コンバータの仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号の周波数は、ランプ信号の周波数よりも低くてもよく、駆動信号の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0013】

このように、デジタル回路からの出力ライン数を増やすことなく、積分回路を付加しただけの簡単な構成で、同じ周波数の駆動信号を従来よりも低い周波数の動作クロックで生成することができる。

【図面の簡単な説明】

【0014】

【図1】本発明の第一の実施形態に係る電源装置の回路図である。

【図2】同上、ランプ信号生成回路の回路図である。

【図3】同上、パルス制御回路の回路図である。

【図4】同上、各部のタイミングチャートである。

【図5】本発明の第二の実施形態に係る電源装置の回路図である。

【発明を実施するための形態】

【0015】

本発明に係る電源装置及び発光素子駆動装置について、添付図面を参照して説明する。

【0016】

図1は、本発明に係る第一の実施形態の電源装置を示している。この実施形態の電源装置は、出力電圧Voutを一定に制御する定電圧出力回路ブロック1の構成を有する。定電圧出力回路ブロック1は、制御対象となるコンバータ2と、コンバータ2に対する電圧帰還ループを形成する電圧検出回路3,マイクロプロセッサ4,ランプ信号生成回路5及びパルス制御回路6とにより構成される。

【0017】

コンバータ2は、入力端子+Vi,−Vi間に印加される直流入力電圧Vinを、直流出力電圧Voutに変換して出力端子+Vo,−Voに供給するもので、出力端子+Vo,−Vo間には図示しない負荷が接続される。ここでのコンバータ2は、入力電圧Vinよりも高い出力電圧Voutに変換するために、チョークコイルL1と、スイッチング素子Q1と、ダイオードD1と、コンデンサC1とによる昇圧チョッパ回路を構成している。より具体的には、入力端子+Vi,−Viの両端間に、チョークコイルL1とスイッチング素子Q1との直列回路が接続され、スイッチング素子Q1の両端間に、ダイオードD1とコンデンサC1との直列回路が接続され、コンデンサC1の両端に出力端子+Vo,−Voが接続される。スイッチング素子Q1はNチャネルのMOS型FETであるが、バイポーラトランジスタなどの別な制御端子付き半導体素子を利用してもよい。

【0018】

電圧検出回路3は、コンバータ2からの出力電圧Voutを検出するもので、出力端子+Vo,−Vo間に分圧用の抵抗R1,R2の直列回路を接続して構成される。抵抗R1,R2の接続点には、出力電圧Voutを分圧した電圧値のアナログ検出電圧が生成される。

【0019】

デジタル回路に相当するマイクロプロセッサ4は、出力電圧Voutを安定化させるための制御指令値をデジタル演算により算出するもので、ADC11と、基準電源12と、CPU14と、PWMユニット15と、動作クロック16と、クロック生成回路17とをそれぞれ内蔵する。

【0020】

ADC11は、電圧検出回路3からの電圧値(アナログ検出電圧)をデジタル値に変換するアナログ−デジタル変換回路に相当する。また基準電源12は、ADC11がアナログ値をデジタル値に変換するときに使用する基準信号を、基準電圧として生成するものである。

【0021】

CPU(中央演算ユニット)14は、ADC11で得られたデジタル信号に基づいてデジタルの制御指令値を算出する演算回路に相当する。またPWM(パルス幅制御)ユニット15は、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を、マイクロプロセッサ4の外部に出力するパルス信号発生回路に相当する。

【0022】

動作クロック16は、CPU14を一定の周期で動作させるための動作クロック信号を出力するものである。またクロック生成回路17は、動作クロック16からの動作クロック信号を分周したクロック信号(同期クロック信号)S1を、マイクロプロセッサ4の外部に出力する分周器として設けられる。本実施形態では、動作クロック16からの例えば8MHzの動作クロック信号を、クロック生成回路17で16分周して、500kHzのクロック信号S1をランプ信号生成回路5に送出する。このクロック信号S1は、後述する駆動信号S5の周波数を決定するものである。

【0023】

マイクロプロセッサ4はその他に、動作クロック16からの動作クロック信号を分周して、クロック信号S1よりも低い周波数のクロック信号をPWMユニット15に出力する別なクロック生成回路(図示せず)を内蔵する。本実施形態では、動作クロック16からの例えば8MHzの動作クロック信号を、別なクロック生成回路で256分周して、31.25kHzのクロック信号をPWMユニット15に送出する。これによりPWMユニット15は、デューティ比が0/256〜255/256の範囲で、周波数が31.25kHzのパルス信号S3を、パルス制御回路6に出力することができる。したがってCPU14も、動作クロック信号の256クロック毎に、新たな制御指令値を決定するようになっている。

【0024】

ランプ信号生成回路5は、マイクロプロセッサ4から出力されるクロック信号S1に基づいて、鋸波状のランプ信号S2を生成するものである。ランプ信号生成回路5からは、クロック信号S1と同じ周波数のランプ信号S2がパルス制御回路6に出力される。

【0025】

図2は、ランプ信号生成回路5の回路例を示したものである。同図において、ランプ信号生成回路5は、スイッチ素子Q2と、コンデンサC2,C3と、ダイオードD2と、抵抗R4,R5,R6とにより構成される。具体的には、クロック信号S1の入力端子21にコンデンサC2の一端を接続し、コンデンサC2の他端にダイオードD2のカソードと抵抗R4の一端を接続し、抵抗R4の他端に抵抗R5の一端とNPN型トランジスタからなるスイッチ素子Q2のベースを接続する。また、図示しない内部電源からの動作電圧Vccのラインに抵抗R6の一端を接続し、抵抗R6の他端にスイッチ素子Q2のコレクタとコンデンサC3の一端を接続する。そして、ダイオードD2のアノード,抵抗R5の他端,スイッチ素子Q2のエミッタ及びコンデンサC3の他端を接地ラインに共通して接続し、抵抗R6とコンデンサC3の接続点であって、スイッチ素子Q2のコレクタを、ランプ信号S2の出力端子22に接続して、ランプ信号生成回路5を構成する。

【0026】

再度図1に戻り、パルス制御回路6は、マイクロプロセッサ4からのパルス信号S3のデューティ比に応じたパルス幅を有する駆動信号S5を、ランプ信号生成回路5から出力されるランプ信号S2と同じ周期で、スイッチング素子Q1の制御端子であるゲートに送出するものである。

【0027】

図3は、パルス制御回路6の回路例を示したものである。同図において、パルス制御回路6は、積分回路28を構成するコンデンサC4及び抵抗R7と、コンパレータCMPとにより構成される。具体的には、ランプ信号S2の入力端子24に、コンパレータCMPの一方の入力端子である反転入力端子を接続し、パルス信号S3の入力端子25に、積分回路28の入力端である抵抗R7の一端を接続し、積分回路28の出力端である抵抗R7の他端とコンデンサC4の一端との接続点に、コンパレータCMPの他方の入力端子である非反転入力端子を接続する。そして、コンデンサC4の他端を接地ラインに接続し、コンパレータCMPの出力端子を駆動信号S5の出力端子26に接続して、パルス制御回路6を構成する。

【0028】

次に、上記構成についてその作用を説明する。この説明では、図4に示す各部のタイミングチャートを参照する。同図において、最上段にあるのは動作クロック16からの動作クロック信号を示しており、以下、クロック信号S1,ランプ信号S2,CPU14で生成される制御指令値,パルス信号S3,前記図3で示したコンデンサC4の両端間電圧S4,駆動信号S5をそれぞれ示している。

【0029】

パルス制御回路6からスイッチング素子Q1のゲートにパルス状の駆動信号S5が与えられると、スイッチング素子Q1はオン・オフ動作を繰り返す。スイッチング素子Q1がオンすると、チョークコイルL1に入力電圧Vinが印加されるので、ダイオードD1はオフ状態となり、平滑用のコンデンサC1の放電電圧が出力端子+Vo,−Voから負荷に出力電圧Voutとして供給される。スイッチング素子Q1がオフすると、入力電圧VinにチョークコイルL1の逆起電圧が重畳されるので、ダイオードD1はオン状態となり、そのダイオードD1を通してコンデンサC1が充電されると共に、入力電圧Vinよりも高い出力電圧Voutが、出力端子+Vo,−Voから負荷に供給される。

【0030】

コンバータ2からの出力電圧Voutは、電圧検出回路3によって監視される。電圧検出回路3は、出力電圧Voutを抵抗R1,R2で分圧して得たアナログ検出電圧を、マイクロプロセッサ4のADC11に送出する。ADC11では、基準電源12からの基準電圧を利用して、前記アナログ検出電圧をデジタル値に変換し、これをCPU14に送出する。

【0031】

CPU14は、電圧検出回路3及びADC11で得られた検出電圧の値に基づいて、制御指令値を算出する。この場合、出力電圧Voutが高くなると制御指令値が低くなり、逆に出力電圧Voutが低くなると制御指令値が高くなる。PWMユニット15は、CPU14で算出した制御指令値に基づいて決定されるデューティ比のパルス信号S3を生成する。この場合、制御指令値が大きくなるとパルス信号S3のデューティ比は大きくなり、逆に制御指令値が小さくなるとパルス信号S3のデューティ比は小さくなる。

【0032】

PWMユニット15は、動作クロック16からの動作クロック信号を256分周した約30kHzのクロック信号が与えられ、このクロック信号と同じ周波数のパルス信号S3を生成する。そのためCPU14は、パルス信号S3と同じ周波数毎に、新たな制御指令値を決定する。図4に示す例では、パルス信号S3の周波数に合わせて、CPU14が「10」,「50」,「128」,「40」,「30」の各制御指令値を順に算出し、その制御指令値に応じたデューティ比のパルス信号S3が、PWMユニット15により生成され、マイクロプロセッサ4からパルス制御回路6に送出される。

【0033】

マイクロプロセッサ4は、前記パルス信号S3の他に、クロック生成回路17からのクロック信号S1をランプ信号生成回路5に送出する。ランプ信号生成回路5は、マイクロプロセッサ4からのクロック信号S1に基いて、図2で示したコンデンサC3の充放電動作により、ランプ信号S2を生成する。より具体的には、入力端子21におけるクロック信号S1は、コンデンサC2を通してトリガ状に波形整形され、抵抗R4,R5で分圧された後に、スイッチ素子Q2のベースに与えられる。このトリガ信号の電圧レベルが立ち上がると、スイッチ素子Q2のエミッタ・コレクタ間がオンすることにより、コンデンサC3を放電する一方で、トリガ信号の電圧レベルが低下すると、スイッチ素子Q2のエミッタ・コレクタ間がオフすることにより、抵抗R6を通して動作電圧VccがコンデンサC3に与えられ、コンデンサC3を充電する。つまり、コンデンサC3の放電は、クロック信号S1の立ち上がりエッジに同期して行われ、その後、コンデンサC3の充電が開始する。したがって、ランプ信号S2は、マイクロプロセッサ4からのクロック信号S1に同期した信号になる。また、クロック信号S1の周波数を変えることにより、ランプ信号S2の周波数を変えることができる。

【0034】

前述したPWMユニット15からのパルス信号S3は、パルス制御回路6の積分回路28に入力される。積分回路28の出力電圧となるコンデンサC4の両端間電圧S4は、パルス信号S3のデューティ比に基づいて上昇又は下降する。この場合、図4に示すように、電圧C4は積分回路28を構成する抵抗R7とコンデンサC4の時定数に依存して、パルス信号S3がH(高)レベルになると上昇し、パルス信号S3がL(低)レベルになると下降して、固定したパルス信号S3の一周期の間で常に変動する。また、パルス信号S3のデューティ比が大きくなるほど、電圧C4が上昇し続ける時間は長くなり、その後の電圧C4が下降し続ける時間は短くなる。

【0035】

ランプ信号生成回路5からのランプ信号S2は、パルス制御回路6のコンパレータCMPの反転入力端子に入力され、積分回路28の出力電圧であるコンデンサC4の両端間電圧S4は、コンパレータCMPの非反転入力端子に入力される。コンパレータCMPは、ランプ信号S2の電圧値とコンデンサC4の両端間電圧S4との比較結果に基づくデューティ比のパルス駆動信号S5を、スイッチング素子Q1のゲートに送出する。これにより、コンバータ2からの出力電圧Voutが一定値となるように、スイッチング素子Q1がオン・オフ動作される。

【0036】

前記駆動信号S5の周波数は、ランプ信号S2の周波数と同じになり、この駆動信号S5のパルス幅は、コンデンサC4の両端間電圧S4により調整される。図3に示す回路では、ランプ信号S2の電圧レベルよりも、コンデンサC4の両端間電圧S4が高くなると、Hレベルの駆動信号が生成される。したがって、コンデンサC4の両端間電圧S4が高くなるに従い、スイッチング素子2をオンにする駆動信号S5のパルス幅も広がる。積分回路28に入力されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよい。

【0037】

本実施形態では、(0〜255)×動作クロック信号の周期(125nS)の範囲で、パルス信号S3のパルス幅が変化する。パルス信号S3は、動作クロック16からの動作クロック信号(8MHz)に基づいて生成されるので、そのパルス幅は125nS単位で段階的に変化する。パルス信号S3のパルス幅が変化することにより、コンデンサC4の両端間電圧S4は絶えず上昇又は減少し、この電圧S4とランプ信号S2がコンパレータCMPにそれぞれ入力される。したがって、コンパレータCMPから出力される駆動信号S5は、コンデンサC4の両端間電圧S4の上昇又は減少に伴って、そのパルス幅を1パルス毎に絶えず変化させることが可能になる。

【0038】

また、駆動信号S5の周波数(500kHz)は、チョークコイルL1のサイズとスイッチング素子Q1のスイッチングロスの双方を考慮して決定される。その理由は、周波数を低くするとチョークコイルL1のサイズが大きくなり、周波数を高くすると、スイッチング素子Q1のスイッチングロスが増加するからである。クロック生成回路17は、CPU14で制御指令値を算出するための処理時間を確保するのに、動作クロック信号を16分周してはおらず、コンバータ2の仕様に基づいて、クロック信号S1の周波数を決定することができる。

【0039】

本実施形態において、動作クロック信号の周波数は例えば500kHzであっても、動作クロック16にクロック生成回路17の機能を兼用させることで、駆動信号S5の周波数を500kHzのままにした回路が実現可能である。この場合、パルス信号S3の周波数は500/256=1.95kHzとなる。またCPU14は、動作クロック信号に対して256クロック毎に新たな制御指令値を算出できればよく、動作クロック信号の周波数に依存しない。

【0040】

以上のように、本実施形態の電源装置は、スイッチング素子Q1のオン・オフ動作により負荷に電力を供給するコンバータ2と、制御指令値をデジタル演算により算出して、コンバータ2からの出力電圧Voutを所定値に制御するデジタル回路としてのマイクロプロセッサ4とを備えている。また、コンバータ2の出力電圧Voutを検出する電圧検出手段としての電圧検出回路3を備え、マイクロプロセッサ4は、電圧検出回路3により検出された電圧値のアナログ検出電圧を、デジタル値に変換する変換回路としてのADC11と、ADC11からのデジタル値に基づいて前記制御指令値を算出する演算回路としてのCPU14と、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を出力するパルス信号発生回路としてのPWMユニット15と、を備える。さらにマイクロプロセッサ4の外部には、CPU14に与えられる動作クロック信号に基づいて生成されたクロック信号S1に同期して、鋸波状のランプ信号S2を出力するランプ信号発生回路5と、パルス信号S3が入力される積分回路28と、ランプ信号S2と積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4との比較結果に基づいて、スイッチング素子Q1をオン・オフ動作させるための駆動信号S5を生成する駆動信号生成回路としてのコンパレータCMPと、を備えている。

【0041】

この場合、コンバータ2の出力電圧Voutを反映したADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4を連続的に上昇又は減少させることで、コンバータ2の出力電圧Voutの安定化を図る。したがって、マイクロプロセッサ4から積分回路28へは、単独のパルス信号S3の出力ラインだけがあればよい。

【0042】

また、コンパレータCMPで生成される駆動信号S5の周波数はランプ信号S2と同一となり、このランプ信号S2の周波数はクロック信号S1に同期したものとなる。したがって、クロック信号S1ひいては駆動信号S5の周波数は、CPU14により制御指令値を算出するための処理時間ではなく、コンバータ2の仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよく、駆動信号S5の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0043】

このように、マイクロプロセッサ4からの出力ライン数を増やすことなく、積分回路28を付加しただけの簡単な構成で、同じ周波数の駆動信号S5を従来よりも低い周波数の動作クロックで生成することが可能になる。

【0044】

次に、本発明に係る第二の実施形態について、図5を参照しながら説明する。本実施形態は、出力端子+Vo,−Vo間に接続する負荷が、特に一乃至複数の発光素子30である発光素子駆動装置に適用される。当該発光素子駆動装置は、発光素子30に流れる出力電流Ioutを一定に制御する定電流出力回路ブロック100の構成を有している。定電流出力回路ブロック100は、制御対象となるコンバータ2と、コンバータ2に対する電流帰還ループを形成する電流検出回路31,マイクロプロセッサ4,ランプ信号生成回路5及びパルス制御回路6とにより構成され、電流検出回路31以外の各部の構成は、第一実施形態の定電圧出力回路ブロック1と全く共通している。

【0045】

電流検出回路31は、前記出力電流Ioutを検出するもので、コンバータ2と発光素子30との間の出力ライン間に電流検出器としての抵抗R3を挿入接続して構成される。抵抗R1の両端間には、出力電流Ioutに比例した電流値のアナログ検出電流が生成される。電流検出器は抵抗R3に限らず、より損失の少ないカレントトランスなどを用いてもよい。

【0046】

発光素子駆動装置としての動作は、負荷が発光素子30に特定され、アナログ検出電圧がアナログ検出電流に置き換わっただけで、第一の実施形態で示した電源装置と共通している。したがって、ここでは再度の説明は行なわない。

【0047】

本実施形態の発光素子駆動装置は、スイッチング素子Q1のオン・オフ動作により電力を供給するコンバータ2と、制御指令値をデジタル演算により算出して、コンバータ2からの出力電圧Voutを所定値に制御するデジタル回路としてのマイクロプロセッサ4とを備え、コンバータ2から供給される電力により発光素子30を駆動する構成を有している。また、発光素子30への出力電流Ioutを検出する電流検出手段としての電流検出回路31を備え、マイクロプロセッサ4は、電流検出回路31により検出された電圧値のアナログ検出電流を、デジタル値に変換する変換回路としてのADC11と、ADC11からのデジタル値に基づいて前記制御指令値を算出する演算回路としてのCPU14と、CPU14で算出された制御指令値に基づいて決定されるデューティ比のパルス信号S3を出力するパルス信号発生回路としてのPWMユニット15と、を備える。さらにマイクロプロセッサ4の外部には、CPU14に与えられる動作クロック信号に基づいて生成されたクロック信号S1に同期して、鋸波状のランプ信号S2を出力するランプ信号発生回路5と、パルス信号S3が入力される積分回路28と、ランプ信号S2と積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4との比較結果に基づいて、スイッチング素子Q1をオン・オフ動作させるための駆動信号S5を生成する駆動信号生成回路としてのコンパレータCMPと、を備えている。

【0048】

この場合、発光素子30への出力電流Ioutを反映したADC11からのデジタル値に基づいて、CPU14が一定時間毎に制御指令値を算出する。この制御指令値に基づいて、PWMユニット15がパルス信号S3のデューティ比を決定し、積分回路28からの出力電圧であるコンデンサC4の両端間電圧S4を連続的に上昇又は減少させることで、発光素子30への出力電流Ioutの安定化を図る。したがって、マイクロプロセッサ4から積分回路28へは、単独のパルス信号S3の出力ラインだけがあればよい。

【0049】

また、コンパレータCMPで生成される駆動信号S5の周波数はランプ信号S2と同一となり、このランプ信号S2の周波数はクロック信号S1に同期したものとなる。したがって、クロック信号S1ひいては駆動信号S5の周波数は、CPU14により制御指令値を算出するための処理時間ではなく、コンバータ2の仕様を考慮して決定できる。一方、制御指令値に基づいてデューティ比が決定されるパルス信号S3の周波数は、ランプ信号S2の周波数よりも低くてもよく、駆動信号S5の周波数を高くしたい場合に、動作クロックの周波数をわざわざ高くする必要がない。

【0050】

このように、マイクロプロセッサ4からの出力ライン数を増やすことなく、積分回路28を付加しただけの簡単な構成で、同じ周波数の駆動信号S5を従来よりも低い周波数の動作クロックで生成することが可能になる。

【0051】

以上、本発明の実施の形態を説明したが、これは本発明の説明のための例示であって、本発明の範囲をこの実施の形態にのみ限定する趣旨ではない。本発明の要旨を逸脱しない範囲内において種々変更を加え得ることは勿論である。例えばコンバータ2は、図示した昇圧チョッパ回路に限らず、一乃至複数のスイッチング素子を備えたあらゆる回路構成のコンバータに適用できる。また、最終的に出力電圧Voutや出力電流Ioutが安定化するように、各部の信号レベルや論理構成を上記各実施形態に示したものと変更しても構わない。

【符号の説明】

【0052】

2 コンバータ

3 電圧検出回路(電圧検出手段)

4 マイクロプロセッサ(デジタル回路)

5 ランプ信号発生回路

11 ADC(変換回路)

14 CPU(演算回路)

15 PWMユニット(パルス信号発生回路)

28 積分回路

31 電流検出回路(電流検出手段)

CMP コンパレータ(駆動信号生成回路)

Q1 スイッチング素子

【特許請求の範囲】

【請求項1】

スイッチング素子のオン・オフ動作により電力を供給するコンバータと、

制御指令値をデジタル演算により算出して、前記コンバータを制御するデジタル回路と、を備えた電源装置であって、

前記コンバータの出力電圧を検出する電圧検出手段と、

前記電圧検出手段により検出された電圧値をデジタル値に変換する変換回路と、

前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、

前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、

前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、

前記パルス信号が入力される積分回路と、

前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えたことを特徴とする電源装置。

【請求項2】

スイッチング素子のオン・オフ動作により電力を供給するコンバータと、

制御指令値をデジタル演算により算出し、前記コンバータを制御するデジタル回路とを備え、

前記コンバータから供給される電力により発光素子を駆動する発光素子駆動装置であって、

前記発光素子に流れる電流を検出する電流検出手段と、

前記電流検出手段により検出された電流値をデジタル値に変換する変換回路と、

前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、

前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、

前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、

前記パルス信号が入力される積分回路と、

前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えた発光素子駆動装置。

【請求項1】

スイッチング素子のオン・オフ動作により電力を供給するコンバータと、

制御指令値をデジタル演算により算出して、前記コンバータを制御するデジタル回路と、を備えた電源装置であって、

前記コンバータの出力電圧を検出する電圧検出手段と、

前記電圧検出手段により検出された電圧値をデジタル値に変換する変換回路と、

前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、

前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、

前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、

前記パルス信号が入力される積分回路と、

前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えたことを特徴とする電源装置。

【請求項2】

スイッチング素子のオン・オフ動作により電力を供給するコンバータと、

制御指令値をデジタル演算により算出し、前記コンバータを制御するデジタル回路とを備え、

前記コンバータから供給される電力により発光素子を駆動する発光素子駆動装置であって、

前記発光素子に流れる電流を検出する電流検出手段と、

前記電流検出手段により検出された電流値をデジタル値に変換する変換回路と、

前記変換回路からのデジタル値に基づいて前記制御指令値を算出する演算回路と、

前記演算回路で算出された前記制御指令値に基づいて決定されるデューティ比のパルス信号を出力するパルス信号発生回路と、

前記演算回路に与えられる動作クロックに基づいて生成されたクロック信号に同期したランプ信号を出力するランプ信号発生回路と、

前記パルス信号が入力される積分回路と、

前記ランプ信号と前記積分回路からの出力電圧との比較結果に基づいて、前記スイッチング素子をオン・オフ動作させる駆動信号を生成する駆動信号生成回路と、を備えた発光素子駆動装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−70509(P2013−70509A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2011−207211(P2011−207211)

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成23年9月22日(2011.9.22)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]