電源装置

【課題】1つの電源で複数のアンプ及びスピーカ駆動を可能とするD級アンプ用の電源装置を提供する。

【解決手段】トランスの2次側の、第1の巻き線とは異なる第2の巻き線を備える。トランスの1次側の巻き線の漏れインダクタにより直流電源の共振周波数を規定して電流共振する共振部と、第2の巻き線の出力電圧と共振部によって出力される出力電圧とを切り替える切替部を備える。切替部からの出力を受けて、第1のスイッチング素子と第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御部を備える。直流電源変換部から出力される出力電圧と、1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知部を備える。電圧検知部が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、切替部は、PWM制御部によるPWM制御モードから共振部による電流共振モードに切り替える。

【解決手段】トランスの2次側の、第1の巻き線とは異なる第2の巻き線を備える。トランスの1次側の巻き線の漏れインダクタにより直流電源の共振周波数を規定して電流共振する共振部と、第2の巻き線の出力電圧と共振部によって出力される出力電圧とを切り替える切替部を備える。切替部からの出力を受けて、第1のスイッチング素子と第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御部を備える。直流電源変換部から出力される出力電圧と、1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知部を備える。電圧検知部が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、切替部は、PWM制御部によるPWM制御モードから共振部による電流共振モードに切り替える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング電源を用いたフルブリッジ型D級アンプに関するものであり、より詳しくは、電流共振及びPWM制御を用いる電源装置に関するものである。

【背景技術】

【0002】

従来のフルブリッジ型D級アンプの構成を図3に示す。同図において、101は商用のAC電源であり、AC電源101からの電流は、整流用ブリッジダイオード102及び平滑用コンデンサ103によってそれぞれ整流・平滑され直流成分に変換される。104は電源トランスであり、スイッチング制御IC105でスイッチング素子106をON/OFF制御することで電源トランス104の1次側のパルス電圧を2次側へ巻き線比に応じたパルス電圧で出力する。これにより、後述するアンプ回路で必要な電圧レベルに変換されることになる。

【0003】

107は電源トランス104から生成されたパルス電圧を整流する整流ブリッジダイオード、108は整流ブリッジダイオード107で整流された電圧を平滑する平滑コンデンサである。109は音声信号を増幅するオペアンプ、110はオペアンプ109で増幅された音声信号を反転するオペアンプである。111及び112はそれぞれオペアンプ109及び110から出力された信号と三角波信号生成部113より生成された三角波と比較するコンパレータである。コンパレータ111及び112で三角波と比較され出力された信号は、それぞれインバータ114及び115を介するものと、コンパレータ111及び112からの直接の信号のそれぞれが、アンプドライバ116及び117の各々に入力される。アンプドライバ116は、コンパレータ111及びインバータ114から入力された信号を元にスイッチング素子118及び119のON/OFFを制御する。同様に、アンプドライバ117は、コンパレータ112及びインバータ115から入力された信号を元にスイッチング素子120及び121のON/OFFを制御する。

【0004】

スイッチング素子118及び119と、及びスイッチング素子120及び121はそれぞれお互いのON期間が重ならないように、交互にON/OFFを繰り返すように、アンプドライバ116及び117によって制御される。加えて、スイッチング素子118及び121が同時にON/OFFを繰り返し、同様に、スイッチング素子119及び120がスイッチング素子118及び121のスイッチング素子とは逆のタイミングでON/OFFを繰り返す。

【0005】

122及び123はインダクタであり、それぞれコンデンサ124との組み合わせでLPF(Low Pass Filter)を形成する。スイッチング素子118及び119のON/OFFによって作成される方形波は、インダクタ122及びコンデンサ124からなるLPFである。同様に、スイッチング素子120及び121のON/OFFで作成される方形波は、インダクタ123及びコンデンサ124からなるLPFである。これらのLPFそれぞれは、音声信号の定倍の大きさの音声信号となってスピーカ125から出力される。このように、スピーカ125の入力端の両端には、極性の異なる同じ信号が入力されることから、スピーカ125の両端ではグランド(GND)には接地されない。

【0006】

次に、図4に示す従来例(特許文献1)は、図3のスピーカ125の入力端の両端でグランド(GND)に接地できない点を改良した構成である。図中の番号で、図3と同一の構成要素は同一の番号を付けている。図4において図3と異なる点は、コンパレータ111及び112とアンプドライバ116及び117とのそれぞれの間にフォトカプラ126及び127を加えたことである。これにより、フォトカプラ126及び127それぞれの前段と後段でそれぞれの能動素子に供給する電源(不図示)のグランドを分離することができる。

【0007】

また、この分離により、スイッチング素子118と119、スイッチング素子120と121のそれぞれの両端にかかる電圧の片方をグランド(GND)に接地していた構成を非接地にしている。また、スピーカ125の片側をグランド(GND)に接地し、それに伴い、インダクタ123を削除している。スピーカ125の片側をグランド(GND)に接地することにより、LPFを構成するインダクタ122及び123から平滑コンデンサ108への回生電流(逆起電力による電流)がなくなる。さらに、平滑コンデンサ108を小さくすることが可能となる、加えて、負荷となるスピーカの複数接続が可能となる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003-8366号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、スピーカシステムを構築する場合、スピーカは帯域に応じた複数のスピーカを用いるのが普通である。複数のスピーカを構成するシステムにおいて、上記従来例の図3では、スピーカの入力端の両端がグランド(GND)に接地されていない。そのため、複数の帯域のスピーカを1つにまとめることができず、その結果、スペースを多く取り小型化に難点があった。また、図4では、アンプ及びスピーカ1つに対して電源が1つ必要となり(図では、電源、アンプ、スピーカともに1つずつしか記載していないが、実際にはアンプ及びスピーカの数だけ電源が必要となる)、部品点数が多く、実装面積も大きくなる。

【0010】

本発明は上記の課題を解決するためになされたものであり、1つの電源で複数のアンプ及びスピーカ駆動を可能とするD級アンプ用の電源装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記の目的を達成するための本発明による電源装置は以下の構成を備える。即ち、

第1のトランスの1次側の巻き線の両端に加える直流電源を第1のスイッチング素子と第2のスイッチング素子を交互にON/OFF制御することにより、前記第1のトランスの2次側の巻き線に交流電源を発生させる電源装置であって、

前記第1のトランスの2次側の巻き線から出力される交流電源を整流・平滑して直流電源に変換する直流電源変換手段と、

前記第1のトランスの2次側の第1の巻き線から出力される交流電源を、1次側の巻き線に入力する少なくとも1つ以上のトランスと、

前記第1のトランスの2次側の、前記第1の巻き線とは異なる第2の巻き線と、

前記第1のトランスの1次側の巻き線の漏れインダクタにより前記直流電源の共振周波数を規定して電流共振する共振手段と、

前記第2の巻き線の出力電圧と前記共振手段によって出力される出力電圧とを切り替える切替手段と、

前記切替手段からの出力を受けて、前記第1のスイッチング素子と前記第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御手段と、

前記直流電源変換手段から出力される出力電圧と、前記1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知手段とを備え、

前記電圧検知手段が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、前記切替手段は、前記PWM制御手段によるPWM制御モードから前記共振手段による電流共振モードに切り替える。

【発明の効果】

【0012】

本発明によれば、電力を効率よく使用でき、部品点数を削減したD級アンプ用電源装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態のブロック図である。

【図2】本発明の実施形態の電力ロスを表すグラフである。

【図3】従来技術の説明図である。

【図4】従来技術の説明図である。

【発明を実施するための形態】

【0014】

以下、添付の図面を参照して、本発明をその好適な実施形態に基づいて詳細に説明する。尚、以下の実施形態において示す構成は一例に過ぎず、本発明は図示された構成に限定されるものではない。

【0015】

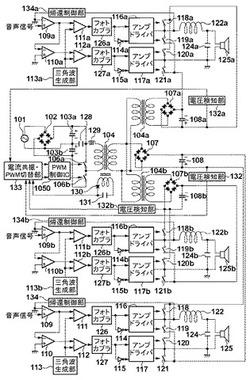

図1は本発明の一実施形態を表すブロック図である。このブロック図は、電源一つとD級アンプとスピーカがそれぞれ3つを有する接続図である。従来例になる図3、図4と同一の構成要素には、同一の参照番号を付して示す。

【0016】

図において、商用のAC電源101からの電流(交流電源)は、整流用ブリッジダイオード102、平滑用コンデンサ103a及び103bによってそれぞれ整流・平滑され直流成分(直流電源変換部)に変換される。PWM制御IC1050は、スイッチング素子106a及び106b(第1のスイッチング素子及び第2のスイッチング素子)を交互にON/OFF制御する。これにより、PWM制御IC1050は、電源トランス104の1次側で発生するパルス電圧を2次側の巻き線比に応じたパルス電圧として出力する。これにより、後述するアンプ回路で必要な電圧レベルに変換される。128は共振用コンデンサ、129は共振用インダクタである。これらは、電源トランス104の1次側の巻線に対して直列に接続される。共振用コンデンサ128と共振用インダクタ129は、独立素子または電源トランス104の1次側の巻き線の漏れインダクタを規定する。この共振用インダクタ129と共振用コンデンサ128の値により本回路における直流電源の共振周波数が決定する。そして、電流共振モードでスイッチングする際、この共振周波数を用いて、PWM制御IC1050がスイッチング素子106a及び106bをON/OFF制御する。

【0017】

整流ブリッジダイオード107による整流、平滑コンデンサ108に平滑により、電源トランス104の2次側に出力されたパルス電圧は直流電圧に変換される。104a及び104bは電源トランス104の2次側出力に接続された電源トランスであり、電源トランス104の2次側から出力されるパルス電圧を入力電圧としてそれぞれ2次側に巻き線比に応じたパルス電圧を出力する。107a及び107bは、電源トランス104a及び104bの2次側出力されたパルス電圧をそれぞれ整流する整流ブリッジダイオードである。108a、108bは整流ブリッジダイオード107a及び107bで整流された電圧を平滑するための平滑コンデンサである。これら整流ブリッジダイオードと平滑コンデンサによってパルス電圧は直流電圧に変換される。

【0018】

130は整流ダイオード、131は平滑コンデンサであり、この2つが接続されている2次側の巻き線の出力電圧を整流、平滑して直流電圧に変えている。

【0019】

尚、電源トランス104の2次側の巻き線(制御巻き線)は本実施形態では2つあり、電源トランス104a及び104bが接続された側(第1の巻き線)と、整流ダイオード130及び平滑コンデンサ131が接続された側(第2の巻き線)である。前者の2次側の巻き線が後者に比して非常に大きく、従って、それぞれに接続される負荷も同様に前者が数百から千ワットクラスなのに対し、後者は数ワットから数十ワット程度である。132、132a及び132bは電圧検知部であり、それぞれ各電源トランス104、104a及び104bの2次側の整流、平滑された後の電圧値を検知し、電流共振・PWM切替部133にその電圧値をフィードバックする。

【0020】

109、109a及び109bは音声信号を増幅するオペアンプである。110、100a及び110bはそれぞれオペアンプ109、109a及び109bで増幅された音声信号を反転するオペアンプである。111、111a及び111bはそれぞれコンパレータであり、オペアンプ109、109a及び109bとから出力された信号と三角波信号生成部113、113a及び113bより生成された三角波と比較する。112、112a及び112bはそれぞれコンパレータであり、オペアンプ110、100a及び110bとから出力された信号と三角波信号生成部113、113a及び113bより生成された三角波と比較する。

【0021】

126、126a及び126bそれぞれコンパレータ111、111a及び111bの出力を後段に絶縁した状態で伝達するためのフォトカプラである。127、127a及び127bはそれぞれコンパレータ112、112a及び112bの出力を後段に絶縁した状態で伝達するためのフォトカプラである。114、114a及び114bはそれぞれインバータであり、それぞれフォトカプラ126、126a及び126bの出力信号を反転する。115、115a及び115bはそれぞれインバータであり、それぞれ127、127a及び127bの出力信号を反転する。

【0022】

116、116a、116b、117、117a及び117bはアンプドライバであり、前段のフォトカプラ及びフォトカプラからの出力をインバータで反転した信号によって後段のスイッチング素子をドライブ、制御する。118、118a、118b、119、119a、119b、120、120a、120b、121、121a及び121bは、スイッチング素子であり、それぞれ前段のアンプドライバによりON/OFFが行われる。122、122a及び122bはコンデンサ、124、124a及び124bはインダクタであり、それぞれコンデンサとインダクタから成る低域通過フィルタ(LPF)である。125、125a及び125bは、スピーカである。134、134a及び134bはそれぞれのアンプドライバでスイッチングされた後の信号を音声信号と比較させるための帰還制御を行う帰還制御部である。

【0023】

以上のようなブロック図において、電源の制御方法及びアンプの制御について詳細に説明する。

【0024】

まず、商用のAC電源101を元に電源トランス104を介して作成されたパルス電圧は、それぞれ平滑コンデンサ108、108a及び108bの両端に直流電圧として表れる。この直流電圧はそれぞれスピーカ125、125a及び125bにかかる電圧をスイッチングするスイッチング素子の両端に供給される。

【0025】

詳しくは、スイッチング素子118と119の両端、及びスイッチング素子120と121の両端にそれぞれ平滑コンデンサ108の両端の電圧がかかる。また、スイッチング素子118aと119aの両端、及びスイッチング素子120aと121aの両端にそれぞれ平滑コンデンサ108aの両端の電圧がかかる。更に、スイッチング素子118bと119bの両端、及びスイッチング素子120bと121bの両端にそれぞれ平滑コンデンサ108bの両端の電圧がかかる。

【0026】

例えば、ここで、オペアンプ109、109a及び109bのそれぞれに入力される音声信号が前段(不図示)の音声信号分割部によって各周波数帯域に分けられた信号であるとする。各音声信号は、各オペアンプによってある一定の値に増幅された後、オペアンプ110、110a及び110bのそれぞれで位相を反転される。位相の異なる音声信号は、それぞれコンパレータ111と112、コンパレータ111aと112a、コンパレータ111bと112bのそれぞれにおいて三角波と比較される。これらコンパレータの各出力はパルス電圧値となりそれぞれのフォトカプラを通ってアンプドライバに入力される。アンプドライバに入力される場合も、位相を反転した信号をインバータにて作成されアンプドライバに入力される。

【0027】

アンプドライバでは音声信号から作成されたパルス信号を元に各スイッチング素子のON/OFF制御を行う。各スイッチング素子において、スイッチング素子118と121が同期してONとなり、その間、スイッチング素子119と120はOFF状態となる。逆に、スイッチング素子119と120がONのとき、スイッチング素子118と121はOFFとなる。また、スイッチング素子118と119、スイッチング素子120と121が同時にONにならないように、デッドタイム期間を設けてある。

【0028】

同様に、スイッチング素子118a、119a、120a、121aと118b、119b、120b、121b間でも同様の制御が行われる。ここで、スイッチング素子118と119、及びスイッチング素子120と121の両端にかかる電圧は平滑コンデンサ108の両端の直流電圧がかかっている。但し、ここでは、平滑コンデンサ108の両端のどちらもグランド(GND)に接地されておらず、GNDにはコンデンサ124のインダクタ122側とは逆の方で接地されている。つまり、平滑コンデンサ108の両端は相対的にみると直流電圧であるが、GNDを基準にすると同じ周期でON/OFFでスイッチングしている。

【0029】

そのため、アンプドライバ116及び117それぞれでスイッチングされた平滑コンデンサ108の両端の電圧は、それぞれ逆位相で出力される。その結果、スピーカ125に出力される電圧はアンプドライバが1つのもの(ハーフブリッジ回路)に対して倍の音量となる(フルブリッジ回路)。もちろん、スピーカ125a及び125bに対する制御もスピーカ125と同様である。このように、スピーカ125、125a及び125bのそれぞれの片端をGNDに接地することが可能で一か所にまとめることができる。

【0030】

ここで、3つの音声信号は必ずしも同じ大きさではあるとは限らず、従って、それぞれの負荷が異なってくる。各スピーカに供給されている電圧は、それぞれはこの負荷の変動によって変動する。負荷が重たくなれば電圧値は下がり、軽くなれば電圧値は予め決められた電圧値に近づくことになる。各電圧のレベルを検知する電圧検知部132、132a及び132bは、電流共振・PWM切替部133に電圧値を送信する。電流共振・PWM切替部133では、電圧検知部132、132a及び132bそれぞれの基準電圧値を予め設定してあり、その基準電圧値と送信されてきた電圧値を比較する。比較した結果、3つのうち1つでも基準電圧値に達していなかったら(つまり、基準電圧値以下に電圧降下していたら)電流共振モードに切り替える。つまり、本実施形態の電源は、負荷が軽い場合はPWM制御モードで動作し、3つのうちの1つでも負荷が重くなった場合に電流共振モードに切り替わる。

【0031】

尚、電流共振モードとPWM制御モードの電源効率の図を図2に示す。効率は当然、各帯域で設定されている電圧値や負荷によって変わってくるので、今回の3つの帯域においても若干異なる。図2はこの3つの帯域における電力ロスが、負荷が軽い場合にはPWM制御モード、負荷が重い場合には電流共振モードの電力ロスが少ないことを示す図である。PWM制御IC1050は電流共振・PWM切替部133から受けた信号により、電流共振モードの場合、予め設定されたON・OFFのデューティー比の固定値でスイッチング素子106a及び106bをON/OFFする。また、PWM制御モードの場合、電流共振・PWM切替部133は整流ダイオード130及び平滑コンデンサ131が接続された2次側の巻き線の電圧値をもらいPWM制御を実行する。すなわち、この電圧値が予め規定された基準値よりも大きければON/OFFのデューティー比のOFFを増加、逆に基準値よりも小さければONを増加させることによって電圧を一定に保つように制御する。

【0032】

以上説明したように、本実施形態によれば、1つの電源において複数のアンプ及びスピーカの駆動を行うことが可能となる。

【0033】

上記実施形態では、一つの電源からアンプ3台へ電源を供給する構成を示している。ここで、3つのアンプとは、4wayスピーカにおいて、本実施形態では、LM用アンプとHM用アンプとTW用のアンプを示している。

【0034】

ここで、第1のトランス(電源トランス104)の出力は第1のアンプ(アンプドライバ116及び117)に電源を供給する。また、第1のトランス(電源トランス104)の出力は、第2のトランス(電源トランス104a)に接続し、その第2のトランスの交流電圧出力を第2のアンプ(アンプドライバ116a及び117a)へ供給する。更に、第1のトランス(電源トランス104)の出力は、第3のトランス(電源トランス104b)に接続し、その第3のトランスの交流電圧出力を第3のアンプ(アンプドライバ116b及び117b)へ供給する。

【0035】

また、3つのアンプにかかる負荷素子(スピーカ125、125a及び125b)のそれぞれが変動することによって各トランスの2次側の電圧が変動する。ここで、3つの電圧低下(検知対象の電圧値)を電圧検知部132、132a及び132bそれぞれ個別に検知してフィードバック制御を行うことにより、PWM制御から共振電流型制御に切り替えることで、電源を効率的に使用することが可能になる。

【技術分野】

【0001】

本発明は、スイッチング電源を用いたフルブリッジ型D級アンプに関するものであり、より詳しくは、電流共振及びPWM制御を用いる電源装置に関するものである。

【背景技術】

【0002】

従来のフルブリッジ型D級アンプの構成を図3に示す。同図において、101は商用のAC電源であり、AC電源101からの電流は、整流用ブリッジダイオード102及び平滑用コンデンサ103によってそれぞれ整流・平滑され直流成分に変換される。104は電源トランスであり、スイッチング制御IC105でスイッチング素子106をON/OFF制御することで電源トランス104の1次側のパルス電圧を2次側へ巻き線比に応じたパルス電圧で出力する。これにより、後述するアンプ回路で必要な電圧レベルに変換されることになる。

【0003】

107は電源トランス104から生成されたパルス電圧を整流する整流ブリッジダイオード、108は整流ブリッジダイオード107で整流された電圧を平滑する平滑コンデンサである。109は音声信号を増幅するオペアンプ、110はオペアンプ109で増幅された音声信号を反転するオペアンプである。111及び112はそれぞれオペアンプ109及び110から出力された信号と三角波信号生成部113より生成された三角波と比較するコンパレータである。コンパレータ111及び112で三角波と比較され出力された信号は、それぞれインバータ114及び115を介するものと、コンパレータ111及び112からの直接の信号のそれぞれが、アンプドライバ116及び117の各々に入力される。アンプドライバ116は、コンパレータ111及びインバータ114から入力された信号を元にスイッチング素子118及び119のON/OFFを制御する。同様に、アンプドライバ117は、コンパレータ112及びインバータ115から入力された信号を元にスイッチング素子120及び121のON/OFFを制御する。

【0004】

スイッチング素子118及び119と、及びスイッチング素子120及び121はそれぞれお互いのON期間が重ならないように、交互にON/OFFを繰り返すように、アンプドライバ116及び117によって制御される。加えて、スイッチング素子118及び121が同時にON/OFFを繰り返し、同様に、スイッチング素子119及び120がスイッチング素子118及び121のスイッチング素子とは逆のタイミングでON/OFFを繰り返す。

【0005】

122及び123はインダクタであり、それぞれコンデンサ124との組み合わせでLPF(Low Pass Filter)を形成する。スイッチング素子118及び119のON/OFFによって作成される方形波は、インダクタ122及びコンデンサ124からなるLPFである。同様に、スイッチング素子120及び121のON/OFFで作成される方形波は、インダクタ123及びコンデンサ124からなるLPFである。これらのLPFそれぞれは、音声信号の定倍の大きさの音声信号となってスピーカ125から出力される。このように、スピーカ125の入力端の両端には、極性の異なる同じ信号が入力されることから、スピーカ125の両端ではグランド(GND)には接地されない。

【0006】

次に、図4に示す従来例(特許文献1)は、図3のスピーカ125の入力端の両端でグランド(GND)に接地できない点を改良した構成である。図中の番号で、図3と同一の構成要素は同一の番号を付けている。図4において図3と異なる点は、コンパレータ111及び112とアンプドライバ116及び117とのそれぞれの間にフォトカプラ126及び127を加えたことである。これにより、フォトカプラ126及び127それぞれの前段と後段でそれぞれの能動素子に供給する電源(不図示)のグランドを分離することができる。

【0007】

また、この分離により、スイッチング素子118と119、スイッチング素子120と121のそれぞれの両端にかかる電圧の片方をグランド(GND)に接地していた構成を非接地にしている。また、スピーカ125の片側をグランド(GND)に接地し、それに伴い、インダクタ123を削除している。スピーカ125の片側をグランド(GND)に接地することにより、LPFを構成するインダクタ122及び123から平滑コンデンサ108への回生電流(逆起電力による電流)がなくなる。さらに、平滑コンデンサ108を小さくすることが可能となる、加えて、負荷となるスピーカの複数接続が可能となる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003-8366号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、スピーカシステムを構築する場合、スピーカは帯域に応じた複数のスピーカを用いるのが普通である。複数のスピーカを構成するシステムにおいて、上記従来例の図3では、スピーカの入力端の両端がグランド(GND)に接地されていない。そのため、複数の帯域のスピーカを1つにまとめることができず、その結果、スペースを多く取り小型化に難点があった。また、図4では、アンプ及びスピーカ1つに対して電源が1つ必要となり(図では、電源、アンプ、スピーカともに1つずつしか記載していないが、実際にはアンプ及びスピーカの数だけ電源が必要となる)、部品点数が多く、実装面積も大きくなる。

【0010】

本発明は上記の課題を解決するためになされたものであり、1つの電源で複数のアンプ及びスピーカ駆動を可能とするD級アンプ用の電源装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記の目的を達成するための本発明による電源装置は以下の構成を備える。即ち、

第1のトランスの1次側の巻き線の両端に加える直流電源を第1のスイッチング素子と第2のスイッチング素子を交互にON/OFF制御することにより、前記第1のトランスの2次側の巻き線に交流電源を発生させる電源装置であって、

前記第1のトランスの2次側の巻き線から出力される交流電源を整流・平滑して直流電源に変換する直流電源変換手段と、

前記第1のトランスの2次側の第1の巻き線から出力される交流電源を、1次側の巻き線に入力する少なくとも1つ以上のトランスと、

前記第1のトランスの2次側の、前記第1の巻き線とは異なる第2の巻き線と、

前記第1のトランスの1次側の巻き線の漏れインダクタにより前記直流電源の共振周波数を規定して電流共振する共振手段と、

前記第2の巻き線の出力電圧と前記共振手段によって出力される出力電圧とを切り替える切替手段と、

前記切替手段からの出力を受けて、前記第1のスイッチング素子と前記第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御手段と、

前記直流電源変換手段から出力される出力電圧と、前記1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知手段とを備え、

前記電圧検知手段が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、前記切替手段は、前記PWM制御手段によるPWM制御モードから前記共振手段による電流共振モードに切り替える。

【発明の効果】

【0012】

本発明によれば、電力を効率よく使用でき、部品点数を削減したD級アンプ用電源装置を提供することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態のブロック図である。

【図2】本発明の実施形態の電力ロスを表すグラフである。

【図3】従来技術の説明図である。

【図4】従来技術の説明図である。

【発明を実施するための形態】

【0014】

以下、添付の図面を参照して、本発明をその好適な実施形態に基づいて詳細に説明する。尚、以下の実施形態において示す構成は一例に過ぎず、本発明は図示された構成に限定されるものではない。

【0015】

図1は本発明の一実施形態を表すブロック図である。このブロック図は、電源一つとD級アンプとスピーカがそれぞれ3つを有する接続図である。従来例になる図3、図4と同一の構成要素には、同一の参照番号を付して示す。

【0016】

図において、商用のAC電源101からの電流(交流電源)は、整流用ブリッジダイオード102、平滑用コンデンサ103a及び103bによってそれぞれ整流・平滑され直流成分(直流電源変換部)に変換される。PWM制御IC1050は、スイッチング素子106a及び106b(第1のスイッチング素子及び第2のスイッチング素子)を交互にON/OFF制御する。これにより、PWM制御IC1050は、電源トランス104の1次側で発生するパルス電圧を2次側の巻き線比に応じたパルス電圧として出力する。これにより、後述するアンプ回路で必要な電圧レベルに変換される。128は共振用コンデンサ、129は共振用インダクタである。これらは、電源トランス104の1次側の巻線に対して直列に接続される。共振用コンデンサ128と共振用インダクタ129は、独立素子または電源トランス104の1次側の巻き線の漏れインダクタを規定する。この共振用インダクタ129と共振用コンデンサ128の値により本回路における直流電源の共振周波数が決定する。そして、電流共振モードでスイッチングする際、この共振周波数を用いて、PWM制御IC1050がスイッチング素子106a及び106bをON/OFF制御する。

【0017】

整流ブリッジダイオード107による整流、平滑コンデンサ108に平滑により、電源トランス104の2次側に出力されたパルス電圧は直流電圧に変換される。104a及び104bは電源トランス104の2次側出力に接続された電源トランスであり、電源トランス104の2次側から出力されるパルス電圧を入力電圧としてそれぞれ2次側に巻き線比に応じたパルス電圧を出力する。107a及び107bは、電源トランス104a及び104bの2次側出力されたパルス電圧をそれぞれ整流する整流ブリッジダイオードである。108a、108bは整流ブリッジダイオード107a及び107bで整流された電圧を平滑するための平滑コンデンサである。これら整流ブリッジダイオードと平滑コンデンサによってパルス電圧は直流電圧に変換される。

【0018】

130は整流ダイオード、131は平滑コンデンサであり、この2つが接続されている2次側の巻き線の出力電圧を整流、平滑して直流電圧に変えている。

【0019】

尚、電源トランス104の2次側の巻き線(制御巻き線)は本実施形態では2つあり、電源トランス104a及び104bが接続された側(第1の巻き線)と、整流ダイオード130及び平滑コンデンサ131が接続された側(第2の巻き線)である。前者の2次側の巻き線が後者に比して非常に大きく、従って、それぞれに接続される負荷も同様に前者が数百から千ワットクラスなのに対し、後者は数ワットから数十ワット程度である。132、132a及び132bは電圧検知部であり、それぞれ各電源トランス104、104a及び104bの2次側の整流、平滑された後の電圧値を検知し、電流共振・PWM切替部133にその電圧値をフィードバックする。

【0020】

109、109a及び109bは音声信号を増幅するオペアンプである。110、100a及び110bはそれぞれオペアンプ109、109a及び109bで増幅された音声信号を反転するオペアンプである。111、111a及び111bはそれぞれコンパレータであり、オペアンプ109、109a及び109bとから出力された信号と三角波信号生成部113、113a及び113bより生成された三角波と比較する。112、112a及び112bはそれぞれコンパレータであり、オペアンプ110、100a及び110bとから出力された信号と三角波信号生成部113、113a及び113bより生成された三角波と比較する。

【0021】

126、126a及び126bそれぞれコンパレータ111、111a及び111bの出力を後段に絶縁した状態で伝達するためのフォトカプラである。127、127a及び127bはそれぞれコンパレータ112、112a及び112bの出力を後段に絶縁した状態で伝達するためのフォトカプラである。114、114a及び114bはそれぞれインバータであり、それぞれフォトカプラ126、126a及び126bの出力信号を反転する。115、115a及び115bはそれぞれインバータであり、それぞれ127、127a及び127bの出力信号を反転する。

【0022】

116、116a、116b、117、117a及び117bはアンプドライバであり、前段のフォトカプラ及びフォトカプラからの出力をインバータで反転した信号によって後段のスイッチング素子をドライブ、制御する。118、118a、118b、119、119a、119b、120、120a、120b、121、121a及び121bは、スイッチング素子であり、それぞれ前段のアンプドライバによりON/OFFが行われる。122、122a及び122bはコンデンサ、124、124a及び124bはインダクタであり、それぞれコンデンサとインダクタから成る低域通過フィルタ(LPF)である。125、125a及び125bは、スピーカである。134、134a及び134bはそれぞれのアンプドライバでスイッチングされた後の信号を音声信号と比較させるための帰還制御を行う帰還制御部である。

【0023】

以上のようなブロック図において、電源の制御方法及びアンプの制御について詳細に説明する。

【0024】

まず、商用のAC電源101を元に電源トランス104を介して作成されたパルス電圧は、それぞれ平滑コンデンサ108、108a及び108bの両端に直流電圧として表れる。この直流電圧はそれぞれスピーカ125、125a及び125bにかかる電圧をスイッチングするスイッチング素子の両端に供給される。

【0025】

詳しくは、スイッチング素子118と119の両端、及びスイッチング素子120と121の両端にそれぞれ平滑コンデンサ108の両端の電圧がかかる。また、スイッチング素子118aと119aの両端、及びスイッチング素子120aと121aの両端にそれぞれ平滑コンデンサ108aの両端の電圧がかかる。更に、スイッチング素子118bと119bの両端、及びスイッチング素子120bと121bの両端にそれぞれ平滑コンデンサ108bの両端の電圧がかかる。

【0026】

例えば、ここで、オペアンプ109、109a及び109bのそれぞれに入力される音声信号が前段(不図示)の音声信号分割部によって各周波数帯域に分けられた信号であるとする。各音声信号は、各オペアンプによってある一定の値に増幅された後、オペアンプ110、110a及び110bのそれぞれで位相を反転される。位相の異なる音声信号は、それぞれコンパレータ111と112、コンパレータ111aと112a、コンパレータ111bと112bのそれぞれにおいて三角波と比較される。これらコンパレータの各出力はパルス電圧値となりそれぞれのフォトカプラを通ってアンプドライバに入力される。アンプドライバに入力される場合も、位相を反転した信号をインバータにて作成されアンプドライバに入力される。

【0027】

アンプドライバでは音声信号から作成されたパルス信号を元に各スイッチング素子のON/OFF制御を行う。各スイッチング素子において、スイッチング素子118と121が同期してONとなり、その間、スイッチング素子119と120はOFF状態となる。逆に、スイッチング素子119と120がONのとき、スイッチング素子118と121はOFFとなる。また、スイッチング素子118と119、スイッチング素子120と121が同時にONにならないように、デッドタイム期間を設けてある。

【0028】

同様に、スイッチング素子118a、119a、120a、121aと118b、119b、120b、121b間でも同様の制御が行われる。ここで、スイッチング素子118と119、及びスイッチング素子120と121の両端にかかる電圧は平滑コンデンサ108の両端の直流電圧がかかっている。但し、ここでは、平滑コンデンサ108の両端のどちらもグランド(GND)に接地されておらず、GNDにはコンデンサ124のインダクタ122側とは逆の方で接地されている。つまり、平滑コンデンサ108の両端は相対的にみると直流電圧であるが、GNDを基準にすると同じ周期でON/OFFでスイッチングしている。

【0029】

そのため、アンプドライバ116及び117それぞれでスイッチングされた平滑コンデンサ108の両端の電圧は、それぞれ逆位相で出力される。その結果、スピーカ125に出力される電圧はアンプドライバが1つのもの(ハーフブリッジ回路)に対して倍の音量となる(フルブリッジ回路)。もちろん、スピーカ125a及び125bに対する制御もスピーカ125と同様である。このように、スピーカ125、125a及び125bのそれぞれの片端をGNDに接地することが可能で一か所にまとめることができる。

【0030】

ここで、3つの音声信号は必ずしも同じ大きさではあるとは限らず、従って、それぞれの負荷が異なってくる。各スピーカに供給されている電圧は、それぞれはこの負荷の変動によって変動する。負荷が重たくなれば電圧値は下がり、軽くなれば電圧値は予め決められた電圧値に近づくことになる。各電圧のレベルを検知する電圧検知部132、132a及び132bは、電流共振・PWM切替部133に電圧値を送信する。電流共振・PWM切替部133では、電圧検知部132、132a及び132bそれぞれの基準電圧値を予め設定してあり、その基準電圧値と送信されてきた電圧値を比較する。比較した結果、3つのうち1つでも基準電圧値に達していなかったら(つまり、基準電圧値以下に電圧降下していたら)電流共振モードに切り替える。つまり、本実施形態の電源は、負荷が軽い場合はPWM制御モードで動作し、3つのうちの1つでも負荷が重くなった場合に電流共振モードに切り替わる。

【0031】

尚、電流共振モードとPWM制御モードの電源効率の図を図2に示す。効率は当然、各帯域で設定されている電圧値や負荷によって変わってくるので、今回の3つの帯域においても若干異なる。図2はこの3つの帯域における電力ロスが、負荷が軽い場合にはPWM制御モード、負荷が重い場合には電流共振モードの電力ロスが少ないことを示す図である。PWM制御IC1050は電流共振・PWM切替部133から受けた信号により、電流共振モードの場合、予め設定されたON・OFFのデューティー比の固定値でスイッチング素子106a及び106bをON/OFFする。また、PWM制御モードの場合、電流共振・PWM切替部133は整流ダイオード130及び平滑コンデンサ131が接続された2次側の巻き線の電圧値をもらいPWM制御を実行する。すなわち、この電圧値が予め規定された基準値よりも大きければON/OFFのデューティー比のOFFを増加、逆に基準値よりも小さければONを増加させることによって電圧を一定に保つように制御する。

【0032】

以上説明したように、本実施形態によれば、1つの電源において複数のアンプ及びスピーカの駆動を行うことが可能となる。

【0033】

上記実施形態では、一つの電源からアンプ3台へ電源を供給する構成を示している。ここで、3つのアンプとは、4wayスピーカにおいて、本実施形態では、LM用アンプとHM用アンプとTW用のアンプを示している。

【0034】

ここで、第1のトランス(電源トランス104)の出力は第1のアンプ(アンプドライバ116及び117)に電源を供給する。また、第1のトランス(電源トランス104)の出力は、第2のトランス(電源トランス104a)に接続し、その第2のトランスの交流電圧出力を第2のアンプ(アンプドライバ116a及び117a)へ供給する。更に、第1のトランス(電源トランス104)の出力は、第3のトランス(電源トランス104b)に接続し、その第3のトランスの交流電圧出力を第3のアンプ(アンプドライバ116b及び117b)へ供給する。

【0035】

また、3つのアンプにかかる負荷素子(スピーカ125、125a及び125b)のそれぞれが変動することによって各トランスの2次側の電圧が変動する。ここで、3つの電圧低下(検知対象の電圧値)を電圧検知部132、132a及び132bそれぞれ個別に検知してフィードバック制御を行うことにより、PWM制御から共振電流型制御に切り替えることで、電源を効率的に使用することが可能になる。

【特許請求の範囲】

【請求項1】

第1のトランスの1次側の巻き線の両端に加える直流電源を第1のスイッチング素子と第2のスイッチング素子を交互にON/OFF制御することにより、前記第1のトランスの2次側の巻き線に交流電源を発生させる電源装置であって、

前記第1のトランスの2次側の巻き線から出力される交流電源を整流・平滑して直流電源に変換する直流電源変換手段と、

前記第1のトランスの2次側の第1の巻き線から出力される交流電源を、1次側の巻き線に入力する少なくとも1つ以上のトランスと、

前記第1のトランスの2次側の、前記第1の巻き線とは異なる第2の巻き線と、

前記第1のトランスの1次側の巻き線の漏れインダクタにより前記直流電源の共振周波数を規定して電流共振する共振手段と、

前記第2の巻き線の出力電圧と前記共振手段によって出力される出力電圧とを切り替える切替手段と、

前記切替手段からの出力を受けて、前記第1のスイッチング素子と前記第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御手段と、

前記直流電源変換手段から出力される出力電圧と、前記1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知手段とを備え、

前記電圧検知手段が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、前記切替手段は、前記PWM制御手段によるPWM制御モードから前記共振手段による電流共振モードに切り替える

ことを特徴とする電源装置。

【請求項2】

前記漏れインダクタは、前記第1のトランスの1次側の巻き線に直列に接続されたコンデンサとインダクタにより規定される

ことを特徴とする請求項1に記載の電源装置。

【請求項3】

前記第1のトランスの後段には、第1のアンプが接続され、

前記少なくとも1つ以上のトランスの内の第2のトランスの後段には、第2のアンプが接続され、

前記少なくとも1つ以上のトランスの内の第3のトランスの後段には、第3のアンプが接続され、

前記第1のアンプ乃至第3のアンプそれぞれの後段には、第1の負荷素子乃至第3の負荷素子が接続され、

前記電圧検知手段は、前記第1の負荷素子乃至第3の負荷素子それぞれの電圧値を前記検知対象の電圧値として個別に検知する

ことを特徴とする請求項1に記載の電源装置。

【請求項1】

第1のトランスの1次側の巻き線の両端に加える直流電源を第1のスイッチング素子と第2のスイッチング素子を交互にON/OFF制御することにより、前記第1のトランスの2次側の巻き線に交流電源を発生させる電源装置であって、

前記第1のトランスの2次側の巻き線から出力される交流電源を整流・平滑して直流電源に変換する直流電源変換手段と、

前記第1のトランスの2次側の第1の巻き線から出力される交流電源を、1次側の巻き線に入力する少なくとも1つ以上のトランスと、

前記第1のトランスの2次側の、前記第1の巻き線とは異なる第2の巻き線と、

前記第1のトランスの1次側の巻き線の漏れインダクタにより前記直流電源の共振周波数を規定して電流共振する共振手段と、

前記第2の巻き線の出力電圧と前記共振手段によって出力される出力電圧とを切り替える切替手段と、

前記切替手段からの出力を受けて、前記第1のスイッチング素子と前記第2のスイッチング素子をON/OFFすることでPWM制御を実行するPWM制御手段と、

前記直流電源変換手段から出力される出力電圧と、前記1つ以上のトランスから出力される出力電圧それぞれの電圧値を検知する電圧検知手段とを備え、

前記電圧検知手段が、検知対象の電圧値のいずれか1つが基準電圧値以下であることを検知した場合、前記切替手段は、前記PWM制御手段によるPWM制御モードから前記共振手段による電流共振モードに切り替える

ことを特徴とする電源装置。

【請求項2】

前記漏れインダクタは、前記第1のトランスの1次側の巻き線に直列に接続されたコンデンサとインダクタにより規定される

ことを特徴とする請求項1に記載の電源装置。

【請求項3】

前記第1のトランスの後段には、第1のアンプが接続され、

前記少なくとも1つ以上のトランスの内の第2のトランスの後段には、第2のアンプが接続され、

前記少なくとも1つ以上のトランスの内の第3のトランスの後段には、第3のアンプが接続され、

前記第1のアンプ乃至第3のアンプそれぞれの後段には、第1の負荷素子乃至第3の負荷素子が接続され、

前記電圧検知手段は、前記第1の負荷素子乃至第3の負荷素子それぞれの電圧値を前記検知対象の電圧値として個別に検知する

ことを特徴とする請求項1に記載の電源装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−116005(P2013−116005A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262651(P2011−262651)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]