電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、例えば、MIS(メタル・インシュレータ・セミコンダクタ)構造のHFET(ヘテロ接合FET)の電界効果トランジスタおよびその製造方法に関する。

【背景技術】

【0002】

従来、特許文献1(特開2009−76673号公報)では、MIS構造のHFET電界効果トランジスタとしてGaN系MOSFETが開示されている。このGaN系MOSFETは、シリコン基板上にAlNバッファ層を介してp型GaN層が形成され、このp型GaN層上にゲート絶縁膜を介してゲート電極が形成されている。このGaN系MOSFETでは、ゲート絶縁膜として、抵抗率が1012Ωcm以上と非常に高いSiO2膜を採用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−76673号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来のGaN系MOSFETでは、ゲート絶縁膜として抵抗率が非常に高いSiO2膜を用いているけれども、耐圧が例えば、100V程度であり、充分なものでない。

【0005】

そこで、この発明の課題は、耐圧をさらに向上できる電界効果トランジスタおよびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

本発明者らは、ゲート絶縁膜は、従来の抵抗率が高い程、耐圧が向上するという従来の常識に反して、抵抗率が1011Ωcm以下の半絶縁膜を用いることで、抵抗率が1012Ωcm以上のSiO2膜を採用した場合に比べて、耐圧が格段に向上することを発見した。

【0007】

ゲート絶縁膜の抵抗率を低くした方が、耐圧が向上するのは、一般に考えられているのと逆であり、予測外の現象であったが、ゲート絶縁膜として、抵抗率が1011Ωcm以下の半絶縁膜を用いることにより、耐圧が大幅に向上することが本発明者らによる実験により判明した。

【0008】

本発明は、このようなゲート絶縁膜を、抵抗率が1×1011Ωcm以下の半絶縁膜とすることで耐圧が大幅に向上するという本発明者らの実験による発見に基づいて創出された。

【0009】

すなわち、この発明の電界効果トランジスタは、窒化物半導体層と、

上記窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されると共に互いに間隔をおいて配置されたソース電極およびドレイン電極と、

上記窒化物半導体層上に形成されると共に上記ソース電極と上記ドレイン電極との間に配置されたゲート電極と、

上記ゲート電極と上記窒化物半導体層との間に形成されたゲート絶縁膜と

を備え、

上記ゲート絶縁膜を、

抵抗率が107Ωcmから1011Ωcmである半絶縁膜としたことを特徴としている。

【0010】

この発明の電界効果トランジスタによれば、ゲート絶縁膜をなす半絶縁膜の抵抗率が、1011Ωcm以下であるという構成によって、図3に示す特性Jのように、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できることが判明した。

【0011】

なお、図3において、縦軸の耐圧(V)は、常温(25℃)で、ソース電極に0Vを印加し、ゲート電極に−10Vを印加した条件において、ドレイン電極‐ソース電極間の電圧Vdsを50V間隔で破壊するまで増加させ、破壊する直前の電圧Vds(V)とした。また、本発明において、ゲート絶縁膜をなす半絶縁膜の抵抗率(107Ωcm〜1011Ωcm)の値は、この半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。

【0012】

また、上記ゲート絶縁膜をなす半絶縁膜の抵抗率が、107Ωcm以上であるという構成によって、上記ゲート絶縁膜の抵抗率が、107Ωcm未満である場合に比べて、ゲートリーク電流を低減できることが判明した。

【0013】

なお、上記ゲートリーク電流は、常温(25℃)で、ソース電極に0Vを印加し、ドレイン電極に600Vを印加し、ゲート電極に−10Vを印加した条件において、測定したゲートリーク電流の値である。

【0014】

また、一実施形態では、上記窒化物半導体層は、GaN系半導体層である。

【0015】

この実施形態によれば、上記GaN系半導体層により、砒化ガリウム(GaAs)系の材料に比べてバンドギャップエネルギーが大きく、しかも耐熱性が優れ高温での動作が可能である。

【0016】

また、一実施形態では、さらに、上記ソース電極と上記ドレイン電極との間で上記窒化物半導体層上に形成されていると共に電流コラプスを抑制するための絶縁膜を備えた。

【0017】

この実施形態によれば、上記絶縁膜により、電流コラプスを抑制することができる。上記電流コラプスとは、GaN系半導体素子において、特に、問題になっているもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0018】

また、この発明の電界効果トランジスタの製造方法は、窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されるように互いに間隔をおいてソース電極およびドレイン電極を形成し、

上記窒化物半導体層上かつ上記ソース電極と上記ドレイン電極との間に抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲート電極を形成することを特徴とする。

【0019】

この発明の電界効果トランジスタの製造方法によれば、抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成するので、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、上記ゲート絶縁膜の抵抗率が107Ωcm未満である場合に比べて、ゲートリーク電流を低減できる。

【0020】

また、一実施形態の電界効果トランジスタの製造方法は、窒化物半導体層上に電流コラプスを抑制するための第1の絶縁膜を形成し、

上記第1の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の予め定められた領域を露出させ、

上記第1の絶縁膜上および上記第1の絶縁膜から露出した上記窒化物半導体層上に第2の絶縁膜を形成し、

上記第2の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の上記予め定められた領域を露出させ、

上記第2の絶縁膜上および上記第2の絶縁膜から露出した上記窒化物半導体層の上記予め定められた領域上に、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲートメタルを蒸着してゲート電極を形成することを特徴としている。

【0021】

この発明の電界効果トランジスタの製造方法によれば、上記第1,第2の絶縁膜を順に形成,エッチング加工した後に、上記ゲート絶縁膜を形成する。したがって、上記第2の絶縁膜にゲート電極のための開口部を形成するために上記第2の絶縁膜をエッチング加工する工程は、上記ゲート絶縁膜を形成する前に行なわれることとなる。よって、上記第2の絶縁膜をエッチング加工する工程を、上記ゲート絶縁膜の形成後に行なう必要がなくなって、上記第2の絶縁膜のエッチング加工に起因して上記ゲート絶縁膜の膜厚がばらつくことを回避できる。ゲート絶縁膜の膜厚は、しきい値を規定する極めて重要なファクターであるので、ゲート絶縁膜の膜厚ばらつきを抑制することが強く求められている。

【0022】

本発明の電界効果トランジスタの製造方法によれば、ゲート絶縁膜の膜厚を精度良く設定でき、安定したしきい値電圧を得ることができる。

【0023】

また、この発明の電界効果トランジスタの製造方法によれば、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成するので、前述の如く、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共にゲートリーク電流を低減できる。

【0024】

また、上記第1の絶縁膜でもって、電流コラプスを抑制することができる。上記電流コラプスとは、GaN系半導体素子において、特に、問題になっているもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。上記第1の絶縁膜は、例えば、SiリッチなSiN膜で構成される。SiリッチなSiN膜とは、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜である。また、上記第1の絶縁膜上に形成された第2の絶縁膜により、ゲートリーク電流をさらに低減できる。この第2の絶縁膜は、例えば、ストイキオメトリなシリコン窒化膜で作製される。

【発明の効果】

【0025】

この発明の電界効果トランジスタによれば、ゲート絶縁膜をなす半絶縁膜の抵抗率が、1011Ωcm以下であるという構成によって、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できることが判明した。

【図面の簡単な説明】

【0026】

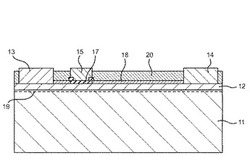

【図1】この発明の電界効果トランジスタの第1実施形態であるGaN系HFETを示す断面図である。

【図2A】上記第1実施形態のGaN系HFETの製造工程を説明する断面図である。

【図2B】図2Aの工程に続く工程を説明する断面図である。

【図2C】図2Bの工程に続く工程を説明する断面図である。

【図3】ゲート絶縁膜の抵抗率と耐圧との関係を示す特性図である。

【図4】上記第1実施形態が備えるゲート絶縁膜をなす半絶縁膜に印加する電界を変化させたときの電流密度の変化を表す特性K1および上記印加電界を変化させたときの抵抗率の変化を表す特性K2を示すI-V特性図である。

【図5】高絶縁膜(SiO2)に印加する電界を変化させたときの電流密度の変化を表す特性K101および上記電界を変化させたときの抵抗率の変化を表す特性K102を示すI-V特性図である。

【図6】この発明の電界効果トランジスタの第2実施形態であるGaN系HFETを示す断面図である。

【図7A】上記第1実施形態のGaN系HFETの製造工程を説明する断面図である。

【図7B】図7Aの工程に続く工程を説明する断面図である。

【図7C】図7Bの工程に続く工程を説明する断面図である。

【図7D】図7Cの工程に続く工程を説明する断面図である。

【発明を実施するための形態】

【0027】

以下、この発明を図示の実施の形態により詳細に説明する。

【0028】

(第1の実施の形態)

図1は、この発明の電界効果トランジスタの第1実施形態であるノーマリーオンタイプのGaN系HFET(ヘテロ接合電界効果トランジスタ)を示す断面図である。

【0029】

この第1実施形態のGaN系HFETは、図1に示すように、Si基板(図示せず)上に、アンドープGaN層11と、アンドープAlGaN層12を順に形成している。このアンドープGaN層11とアンドープAlGaN層12との界面に2DEG(2次元電子ガス)19が発生する。このアンドープGaN層11とアンドープAlGaN層12で窒化物半導体積層体を構成している。なお、上記基板は、Si基板に限らず、サファイヤ基板やSiC基板を用いてもよく、サファイヤ基板やSiC基板上に窒化物半導体層を成長させてもよいし、GaN基板にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。また、上記アンドープGaN層11とアンドープAlGaN層12との間に層厚1nmのAlN層を形成してもよい。

【0030】

上記アンドープAlGaN層12上に、予め設定された間隔をあけてソース電極13とドレイン電極14を形成している。上記アンドープAlGaN層12上のソース電極13とドレイン電極14との間かつソース電極13側にゲート電極15を形成している。ここでは、上記アンドープAlGaN層12の厚さを例えば10nmとしてソース電極13とドレイン電極14をアニールすることでオーミックコンタクト可能にしている。なお、上記アンドープAlGaN層12の厚さを例えば30nmとしてアンドープAlGaN層12のオーミックコンタクト部分に予めSiドープをしてn型化させることで電極のオーミックコンタクトを可能としてもよい。また、アンドープAlGaN層12のソース電極およびドレイン電極下に予め、リセスを形成し、ソース電極およびドレイン電極を蒸着、アニールすることでオーミックコンタクトを可能としてもよい。

【0031】

図1に示すように、上記ゲート電極15とアンドープAlGaN層12との間には、ゲート絶縁膜17が形成されている。このゲート絶縁膜17は、一例として、半絶縁膜としてのSiリッチなシリコン窒化膜で作製される。このSiリッチなシリコン窒化膜とは、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜であり、例えば、SiとNとの組成比Si:N=1.1〜1.9:1である。また、好ましい一例では、SiとNとの組成比Si:N=1.3〜1.5:1である。

【0032】

また、ゲート絶縁膜17とソース電極13との間のアンドープAlGaN層12上およびゲート絶縁膜17とドレイン電極14との間のアンドープAlGaN層12上に保護膜18が形成されている。この保護膜18は、電流コラプスを抑制するための絶縁膜であり、一例として、Siリッチなシリコン窒化膜で作製されている。

【0033】

また、ゲート絶縁膜17とソース電極13との間の保護膜18上およびゲート絶縁膜17とドレイン電極14との間の保護膜18上にプロセス絶縁膜20が形成されている。このプロセス絶縁膜20は、一例として、Si:N=0.75:1のストイキオメトリなシリコン窒化膜で作製されている。

【0034】

この第1実施形態では、一例として、上記ゲート絶縁膜17の膜厚を20nmとし、上記保護膜18の膜厚を30nmとし、プロセス絶縁膜20の膜厚を150nmとした。

【0035】

次に、図2A〜図2Cを順に参照して、上記GaN系HFETの製造方法を説明する。

【0036】

まず、図示しないSi基板上に、図2Aに示すように、MOCVD(有機金属気相成長)法を用いて、アンドープGaN層11、アンドープAlGaN層12、を順に形成する。このアンドープGaN層11とアンドープAlGaN層12が窒化物半導体積層体を構成している。

【0037】

次に、図2Aに示すように、上記アンドープAlGaN層12上に、プラズマCVD法を用いて、保護膜18となるシリコン窒化膜28を形成する。この保護膜18となるシリコン窒化膜28の成長温度は、一例として、225℃としたが、200℃〜400℃の範囲で設定してもよい。また、上記保護膜18となるシリコン窒化膜28の膜厚は、一例として、30nmとしたが、20nm〜250nmの範囲で設定してもよい。

【0038】

また、一例として、上記プラズマCVD法によりシリコン窒化膜28を形成する際のガス流量比は、N2/NH3/SiH4=300sccm/40sccm/35sccmとした。これにより、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなシリコン窒化膜28を形成できる。このシリコン窒化膜28によれば、ストイキオメトリなシリコン窒化膜に比べて、電流コラプスをより抑制できる。また、例えば、保護膜18となるシリコン窒化膜28のSiとNとの組成比Si:N=1.1〜1.9:1にすると、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりも電流コラプスの抑制に有効である。この電流コラプスとは、特に、GaN系半導体素子において顕著に表れるもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0039】

次に、上記保護膜18となるシリコン窒化膜28上にフォトレジスト層(図示せず)を形成し、露光,現像することにより、ソース電極13,ドレイン電極14を形成すべき領域の上記フォトレジスト層、および、ゲート絶縁膜17を形成すべき領域の上記フォトレジスト層を除去し、このフォトレジスト層をマスクとして、ドライエッチングを行なう。これにより、図2Aに示すように、上記保護膜18となるシリコン窒化膜28のうち、ソース電極13,ドレイン電極14を形成すべき領域、および、ゲート絶縁膜17を形成すべき領域を除去して、この領域にアンドープAlGaN層12を露出させる。

【0040】

次に、上記保護膜18となるシリコン窒化膜28を熱処理する。この熱処理の温度は、例えば、500℃で30分間とした。なお、上記熱処理の温度は、一例として、500℃〜700℃の範囲で設定してもよい。

【0041】

その後、図2Bに示すように、上記保護膜18上に、プラズマCVD(化学的気相成長)法により、ゲート絶縁膜17となる半絶縁膜としてのシリコン窒化膜27を形成する。このゲート絶縁膜17となるシリコン窒化膜27は、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率を大きくしている。

【0042】

ここで、上記ゲート絶縁膜17となるシリコン窒化膜27を形成するときのプラズマCVDによる成膜条件としては、一例として、RFパワーを50(W)とし、SiH4とNH3の流量比(SiH4/NH3)を0.92とし、圧力を0.7Torrとし、基板温度を225℃とした。

【0043】

次に、レジストを用いたパターニングにより、上記シリコン窒化膜27のうちの開口22に露出したAlGaN層12および上記開口22の周縁の保護膜18を覆う部分を残して、図2Bに示すように、ゲート絶縁膜17を形成する。

【0044】

次に、図2Cに示すように、プラズマCVD法により、プロセス絶縁膜20となるストイキオメトリなシリコン窒化膜29を形成してから、フォトリソグラフィとエッチングにより、ゲート電極15を形成する部分に開口21を形成する。

【0045】

その後、TiNを全面スパッタし、フォトリソグラフィでゲート電極15を形成すべき電極形成領域にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ドライエッチングまたはウェットエッチングを行なって、上記電極形成領域以外のTiN膜を除去して、図2Cに示すように、TiN電極によるゲート電極15を形成する。このゲート電極15の直下には、ゲート絶縁膜17が位置している。

【0046】

次に、フォトリソグラフィとエッチングにより、図2Cに示すように、ソース電極13,ドレイン電極14を形成する部分のシリコン窒化膜29に開口31,32を形成する。

【0047】

次に、フォトリソグラフィにより、ソース電極13,ドレイン電極14を形成すべき領域(上記開口31,32に露出したAlGaN層12の領域)が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上にTi,Alを順に蒸着し、リフトオフにより、図1に示すように、上記露出したAlGaN層12上にTi/Al電極によるソース電極13,ドレイン電極14を形成する。上記Ti/Al電極は、Ti層,Al層が順に積層された積層構造の電極である。次に、上記ソース電極13,ドレイン電極14を、熱処理してオーミック電極にする。この熱処理(オーミックアニール)の条件は、一例として500℃で30分としたが、上記熱処理の条件は、これに限らず、例えば、上記熱処理温度を、400℃〜600℃の範囲内で設定してもよい。

【0048】

こうして作製した上記第1実施形態のGaN系HFETによれば、ゲート絶縁膜15をなす半絶縁膜の抵抗率ρは、3.9×109Ωcmであった。上記抵抗率ρの値(3.9×109Ωcm)は、上記半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。

【0049】

この第1実施形態では、抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、図3に示すように、1000Vの耐圧が得られた。なお、図3の横軸は抵抗率(Ωcm)であり、横軸目盛1.E+06、1.E+07、1.E+08、1.E+09、…、1.E+13は、それぞれ、106、107(Ωcm)、108(Ωcm)、109(Ωcm)、…、1013(Ωcm)を表す。また、図3において、縦軸の耐圧(V)は、常温(25℃)で、ソース電極に0Vを印加し、ゲート電極に−10Vを印加した条件において、ドレイン電極‐ソース電極間の電圧Vdsを50V間隔で絶縁破壊するまで増加させ、絶縁破壊する直前の電圧Vds(V)とした。

【0050】

図3に示すように、ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると、耐圧が急減していることが分かる。また、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回ると、ゲートリーク電流が増大することが判明した。このゲートリーク電流は、常温(25℃)で、ソース電極に0Vを印加し、ドレイン電極に600Vを印加し、ゲート電極に−10Vを印加した条件において、測定したゲートリーク電流の値である。

【0051】

また、図3において、プロットPは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが約1×1010(Ωcm)である場合に、この半絶縁膜を680℃で1時間アニールした場合の耐圧と抵抗率を示している。プロットPで示すように、ゲート絶縁膜17をアニール(680℃,1時間)することで、アニールしない場合の耐圧800Vに比べて、同じ抵抗率でも耐圧を200V以上向上できた。

【0052】

次に、図4を参照して、上記抵抗率ρ=3.9×109Ωcmの半絶縁膜のI‐V特性K1を説明する。

【0053】

この半絶縁膜のI‐V特性K1は、上記半絶縁膜を2つの電極間に挟んで上記半絶縁膜に印加する電界を変化させたときに上記2つの電極間に流れる電流密度の変化を表わすグラフである。なお、図4の左側の縦軸は電流密度(A/cm2)であり、縦軸目盛の1.E−09、1.E−08、1.E−07、1.E−06、…、1.E+01は、それぞれ、10−9(A/cm2)、10−8(A/cm2)、10−7(A/cm2)、10−6(A/cm2)、…、10+1(A/cm2)を表している。

【0054】

上記半絶縁膜では、I‐V特性K1に示すように、電界が5〜15(MV/cm)の範囲において、電界の増加にほぼ比例して電流密度が増加しているが、電界が15(MV/cm)を超えても絶縁破壊には至っていない。

【0055】

また、図4における特性K2は、横軸の印加電界の変化に対して、右側の縦軸で表す抵抗率(Ωcm)がどの様に変化するのかを表している。なお、図4の右側の縦軸目盛の1.E+05、1.E+06、1.E+07、1.E+08、…、1.E+15は、それぞれ、105(Ωcm)、106(Ωcm)、107(Ωcm)、108(Ωcm)、…、1015(Ωcm)を表している。この特性K2における抵抗率(Ωcm)は、上記I‐V特性K1における電界を電流密度で除算した値としている。上記半絶縁膜は、印加電界を増加させることにより、上記特性K2における抵抗率が減少していることが分かる。

【0056】

次に、図5を参照して、高絶縁膜(SiO2)のI‐V特性K101を説明する。この高絶縁膜(SiO2)のI‐V特性K101は、上記高絶縁膜(SiO2)を2つの電極間に挟んで上記高絶縁膜(SiO2)に印加する電界を変化させたときに上記2つの電極間に流れる電流密度の変化を表わすグラフである。なお、図5の左側の縦軸は電流密度(A/cm2)であり、縦軸目盛の1.E−09、1.E−08、1.E−07、1.E−06、…、1.E+01は、それぞれ、10−9(A/cm2)、10−8(A/cm2)、10−7(A/cm2)、10−6(A/cm2)、…、10+1(A/cm2)を表している。

【0057】

この高絶縁膜(SiO2)では、I‐V特性K101に示すように、印加電界が8(MV/cm)を超えると電流密度が急増し、印加電界が10(MV/cm)を超えると絶縁破壊に至っている。一方、図5の特性K102は、横軸の印加電界の変化に対して、右側の縦軸で表す抵抗率(Ωcm)がどの様に変化するのかを表している。この特性K102における抵抗率(Ωcm)は、上記I‐V特性K101における電界を電流密度で除算した値としている。なお、図5の右側の縦軸目盛の1.E+05、1.E+06、1.E+07、1.E+08、…、1.E+15は、それぞれ、105(Ωcm)、106(Ωcm)、107(Ωcm)、108(Ωcm)、…、1015(Ωcm)を表している。この高絶縁膜(SiO2)は、印加電界が8(MV/cm)までは抵抗率が大きく変化しないが印加電界が8(MV/cm)を超えると抵抗率が急減し、印加電界が10(MV/cm)を超えると絶縁破壊に至っている。

【0058】

このように、高絶縁膜(SiO2)では、図5の特性K101のように、印加電界が10(MV/cm)を超えると絶縁破壊に至っているのに対して、本実施形態でゲート絶縁膜15として採用した上記半絶縁膜(抵抗率ρ=3.9×109Ωcm)では、図4の特性K1のように、印加電界の増加に比例して電流密度が増加するI-V特性を示し、印加電界が15(MV/cm)を超えても絶縁破壊に至っていない。

【0059】

すなわち、本実施形態のGaN系HFETのように、ゲート絶縁膜15として、電流密度が6.25×10−4(A/cm2)であるときの抵抗率が3.9×109Ωcmの半絶縁膜を採用したことで、ゲート絶縁膜として抵抗率が1×1012(Ωcm)を超える高絶縁膜(SiO2)を採用した場合に比べて、耐圧を著しく向上できることが判明した。

【0060】

また、前述の図3に示すように、上記ゲート絶縁膜としての半絶縁膜の抵抗率を、107Ωcm〜1011Ωcmの範囲内に設定することで、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、ゲート絶縁膜の抵抗率が107Ωcm未満である場合に比べて、ゲートリーク電流を低減できる。

【0061】

(第2の実施の形態)

図6は、この発明の電界効果トランジスタの第2実施形態であるノーマリーオンタイプのGaN系HFET(ヘテロ接合電界効果トランジスタ)を示す断面図である。

【0062】

この第2実施形態のGaN系HFETは、図6に示すように、Si基板(図示せず)上に、アンドープGaN層51と、アンドープAlGaN層52を順に形成している。このアンドープGaN層51とアンドープAlGaN層52との界面に2DEG(2次元電子ガス)59が発生する。このアンドープGaN層51とアンドープAlGaN層52で窒化物半導体積層体を構成している。

【0063】

上記アンドープAlGaN層52上に、予め設定された間隔をあけてソース電極53とドレイン電極54を形成している。上記アンドープAlGaN層52上のソース電極53とドレイン電極54との間かつソース電極53側にゲート電極55を形成している。ここでは、上記アンドープAlGaN層52の厚さを例えば10nmとしてソース電極53とドレイン電極54をアニールすることでオーミックコンタクト可能にしている。なお、上記アンドープAlGaN層52の厚さを例えば30nmとしてアンドープAlGaN層52のオーミックコンタクト部分に予めSiドープをしてn型化させることで電極のオーミックコンタクトを可能としてもよい。また、アンドープAlGaN層52のソース電極およびドレイン電極下に予め、リセスを形成し、ソース電極およびドレイン電極を蒸着、アニールすることでオーミックコンタクトを可能としてもよい。

【0064】

この第2実施形態では、図6に示すように、上記ゲート電極55とアンドープAlGaN層52との間には、ゲート絶縁膜57が形成されている。また、上記ゲート電極55と上記アンドープAlGaN層52とで挟まれている上記ゲート絶縁膜57と上記ソース電極53,ドレイン電極54との間で上記アンドープAlGaN層52上に第1の絶縁膜としての保護膜58が形成されている。この保護膜58は、一例として、Siリッチなシリコン窒化膜で作製されていて、電流コラプスを抑制するための絶縁膜である。このSiリッチなシリコン窒化膜とは、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜であり、例えば、SiとNとの組成比Si:N=1.1〜1.9:1である。また、好ましい一例では、SiとNとの組成比Si:N=1.3〜1.5:1である。

【0065】

また、この第2実施形態では、上記保護膜58上に第2の絶縁膜としてのプロセス絶縁膜60が形成されている。このプロセス絶縁膜60上に、上記ゲート絶縁膜57および上記ゲート電極55が形成されている。また、上記ゲート電極55およびゲート絶縁膜57上に層間絶縁膜61が形成されている。また、ソース電極53およびドレイン電極54上には給電用のメタル81,82が形成されている。

【0066】

この第2実施形態では、一例として、上記ゲート絶縁膜57の膜厚を20nmとし、上記保護膜58の膜厚を30nmとし、プロセス絶縁膜60を150nmとした。

【0067】

次に、図7A〜図7Dを順に参照して、上記GaN系HFETの製造方法を説明する。

【0068】

まず、図示しないSi基板上に、図7Aに示すように、MOCVD(有機金属気相成長)法を用いて、アンドープGaN層51、アンドープAlGaN層52、を順に形成する。このアンドープGaN層51とアンドープAlGaN層52が化合物半導体積層体を構成している。なお、上記基板は、Si基板に限らず、サファイヤ基板やSiC基板を用いてもよく、サファイヤ基板やSiC基板上に窒化物半導体層を成長させてもよいし、GaN基板にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。

【0069】

次に、図7Aに示すように、上記アンドープAlGaN層52上に、プラズマCVD法を用いて、第1の絶縁膜としての保護膜58となるシリコン窒化膜68を形成する。この保護膜58となるシリコン窒化膜68の成長温度は、一例として、225℃としたが、200℃〜400℃の範囲で設定してもよい。また、上記保護膜58となるシリコン窒化膜68の膜厚は、一例として、30nmとしたが、20nm〜250nmの範囲で設定してもよい。

【0070】

また、一例として、上記プラズマCVD法によりシリコン窒化膜68を形成する際のガス流量比は、N2/NH3/SiH4=300sccm/40sccm/35sccmとした。これにより、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなシリコン窒化膜68を形成できる。このシリコン窒化膜68によれば、ストイキオメトリなシリコン窒化膜に比べて、電流コラプスをより抑制できる。また、例えば、第1の絶縁膜としての保護膜58となるシリコン窒化膜68のSiとNとの組成比Si:N=1.1〜1.9:1にすると、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりも電流コラプスの抑制に有効である。この電流コラプスとは、特に、GaN系半導体素子において顕著に表れるもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0071】

次に、上記保護膜58となるシリコン窒化膜68上にフォトレジスト層(図示せず)を形成し、露光,現像することにより、ソース電極53,ドレイン電極54を形成すべき領域の上記フォトレジスト層、および、ゲート絶縁膜57を形成すべき領域の上記フォトレジスト層を除去し、このフォトレジスト層をマスクとして、ドライエッチングを行なう。これにより、図7Aに示すように、上記第1の絶縁膜としての保護膜58となるシリコン窒化膜68からソース電極53,ドレイン電極54を形成すべき領域、および、ゲート絶縁膜57を形成すべき領域のアンドープAlGaN層52を露出させる。

【0072】

次に、上記第1の絶縁膜としての保護膜58となるシリコン窒化膜68を熱処理する。この熱処理の温度は、例えば、500℃で30分間とした。なお、上記熱処理の温度は、一例として、500℃〜700℃の範囲で設定してもよい。

【0073】

その後、図7Bに示すように、上記保護膜58から露出したAlGaN層52上に、プラズマCVD(化学的気相成長)法により、第2の絶縁膜としてのプロセス絶縁膜60となるシリコン窒化膜70を形成する。このプロセス絶縁膜60となるシリコン窒化膜70は、ストイキオメトリなシリコン窒化膜とした。次に、フォトリソグラフィによりフォトレジストによるマスクを形成して、上記第2の絶縁膜としてのプロセス絶縁膜60となるシリコン窒化膜70をウェットエッチングにより等方的にエッチングする。これにより、図7Bに示すように、上記シリコン窒化膜70のうちの、ゲート電極55,ゲート絶縁膜57を形成すべき領域を除去して、AlGaN層52に向かって先細形状の開口部77を形成する。

【0074】

次に、図7Cに示すように、上記第2の絶縁膜としてのプロセス絶縁膜60上およびプロセス絶縁膜60の開口部77に露出したAlGaN層52上に、プラズマCVD(化学的気相成長)法により、ゲート絶縁膜57となる半絶縁膜としてのシリコン窒化膜を形成する。このゲート絶縁膜57としてのシリコン窒化膜は、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率を大きくしている。

【0075】

ここで、上記ゲート絶縁膜57となるシリコン窒化膜を形成するときのプラズマCVDによる成膜条件としては、一例として、RFパワーを50(W)とし、SiH4とNH3の流量比(SiH4/NH3)を0.92とし、圧力を0.7Torrとし、基板温度を225℃とした。

【0076】

その後、TiNを全面スパッタし、フォトリソグラフィでゲート電極55を形成すべき電極形成領域にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ドライエッチングまたはウェットエッチングを行なって、上記電極形成領域以外のTiN膜を除去して、図7Dに示すように、TiN電極によるゲート電極55を形成する。このゲート電極55の直下には、ゲート絶縁膜57となるシリコン窒化膜67が位置している。

【0077】

次に、上記ゲート電極55上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、上記ゲート電極55下以外の領域のシリコン窒化膜67をエッチングして、ゲート絶縁膜57とする。

【0078】

次に、フォトリソグラフィでソース電極53,ドレイン電極54を形成すべき領域が開口したレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、上記シリコン窒化膜70をエッチングして、プロセス絶縁膜60とする。

【0079】

次に、フォトリソグラフィにより、ソース電極53,ドレイン電極54を形成すべき領域(露出したAlGaN層52の領域)が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上にTi,Alを順に蒸着し、リフトオフにより、図6に示すように、上記露出したAlGaN層52上にTi/Al電極によるソース電極53,ドレイン電極54を形成する。上記Ti/Al電極は、Ti層,Al層が順に積層された積層構造の電極である。次に、上記ソース電極53,ドレイン電極54を、熱処理してオーミック電極にする。この熱処理(オーミックアニール)の条件は、一例として500℃で30分としたが、上記熱処理の条件は、これに限らず、例えば、上記熱処理温度を、400℃〜600℃の範囲内で設定してもよい。

【0080】

次に、プラズマCVD法により、層間絶縁膜61となるストイキオメトリなシリコン窒化膜を形成し、CMP(化学的機械的研磨)法等の方法で平坦化する。次に、ソース電極53,ドレイン電極54上の領域が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上に給電メタルを順に蒸着して、給電メタル81,82を形成する。上記給電メタルとしては、例えば、Al,Cu等が用いられる。

【0081】

こうして作製した上記第2実施形態のGaN系HFETによれば、ゲート絶縁膜57をなす半絶縁膜の抵抗率ρは、3.9×109Ωcmであった。上記抵抗率ρの値(3.9×109Ωcm)は、上記半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。この半絶縁膜のI‐V特性は、前述の図4に示すI‐V特性K1と同様である。

【0082】

この第2実施形態では、抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜57を備えたことで、図3に示すように、1000Vの耐圧が得られた。

【0083】

すなわち、この第2実施形態によれば、ゲート絶縁膜57をなす半絶縁膜の抵抗率が3.9×109Ωcmであり、上記半絶縁膜の抵抗率が107Ωcm以上かつ1011Ωcm以下であるので、上述の如く、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、ゲート絶縁膜の抵抗率が107Ωcmを下回る場合に比べて、ゲートリーク電流を低減できる。

【0084】

また、図7A〜図7Dを順に参照して説明した上記第2実施形態のGaN系HFETの製造方法によれば、図7A〜図7Cに示すように、上記第1の絶縁膜としての保護膜58と上記第2の絶縁膜としてのプロセス絶縁膜60を順に形成,エッチング加工した後に、上記ゲート絶縁膜57を形成する。したがって、ゲート電極55下のゲート絶縁膜57の厚みは、AlGaN層52が露出した状態でゲート絶縁膜57が堆積され、その後にエッチング工程がないことから、プラズマCVD法によるゲート絶縁膜57の堆積膜厚のみで決定される。

【0085】

よって、エッチング加工に起因して上記ゲート絶縁膜57の膜厚がばらつくことを回避できる。したがって、安定したしきい値電圧を得ることができる。

【0086】

また、上記シリコンリッチなシリコン窒化膜で作製した保護膜58によって、電流コラプスを抑制できると共に、上記ストイキオメトリなシリコン窒化膜で作製したプロセス絶縁膜60によって、ゲートリーク電流をさらに低減できる。

【0087】

尚、上記第1,第2実施形態では、ゲート絶縁膜をなす半絶縁膜を、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなSiN膜としたが、SiON膜としてもよい。また、上記第1,第2実施形態において、ゲート絶縁膜を形成してからゲート絶縁膜をアニールすることで、耐圧をさらに向上できる。

【0088】

また、上記第1,第2実施形態では、このGaN系半導体積層体を、GaN層とAlGaN層で構成したが、AlxInyGa1-x-yN(x≧0、y≧0、0≦x+y<1)で表されるGaN系半導体層を含むものでもよい。すなわち、上記GaN系半導体積層体は、AlGaN、GaN、InGaN等を含むものとしてもよい。また、上記実施形態では、ノーマリオンタイプのHFETについて説明したがノーマリオフタイプでも同様の効果が得られる。

【0089】

また、上記第1,第2実施形態では、基板としてSi基板を用いたが、サファイア基板やSiC基板を用いてもよい。また、上記GaN基板上にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。また、GaN層11,51とAlGaN層12,52との間に、一例として層厚1nm程度のAlNで作製したヘテロ改善層を形成してもよい。また、上記AlGaN層12,52上にGaNキャップ層を形成してもよい。また、上記実施形態では、ゲート電極15,55をTiNで作製したが、WNで作製してもよい。また、ゲート電極15,55をPt/AuやNi/Auで作製してもよい。また、上記ゲート電極材料として、上記窒化物半導体と接合した場合にショットキー接合となる材料を用いるようにしてもよい。

【0090】

また、上記第1,第2実施形態では、上記オーミック電極としてのソース電極13,53とドレイン電極14,54を、Ti層,Al層が順に積層されたTi/Al電極としたが、Ti層,Al層,TiN層が順に積層されたTi/Al/TiN電極としてもよい。また、上記Al層の代わりにAlSi層やAlCu層を用いてもよい。また、ソース電極,ドレイン電極としては、Hf/Al電極としてもよい。また、ソース電極,ドレイン電極としては、Ti/AlまたはHf/Al上にNi/Auを積層したものとしてもよく、Ti/AlまたはHf/Al上にPt/Auを積層したものとしてもよく、Ti/AlまたはHf/Al上にAuを積層したものとしてもよい。

【0091】

この発明の具体的な実施の形態について説明したが、この発明は上記実施形態に限定されるものではなく、この発明の範囲内で種々変更して実施することができる。

【符号の説明】

【0092】

11,51 アンドープGaN層

12,52 アンドープAlGaN層

13,53 ソース電極

14,54 ドレイン電極

15,55 ゲート電極

17,57 ゲート絶縁膜

18,58 保護膜

19,59 2次元電子ガス

20,60 プロセス絶縁膜

22,62,77 開口部

27,28,68,70 シリコン窒化膜

61 層間絶縁膜

【技術分野】

【0001】

この発明は、例えば、MIS(メタル・インシュレータ・セミコンダクタ)構造のHFET(ヘテロ接合FET)の電界効果トランジスタおよびその製造方法に関する。

【背景技術】

【0002】

従来、特許文献1(特開2009−76673号公報)では、MIS構造のHFET電界効果トランジスタとしてGaN系MOSFETが開示されている。このGaN系MOSFETは、シリコン基板上にAlNバッファ層を介してp型GaN層が形成され、このp型GaN層上にゲート絶縁膜を介してゲート電極が形成されている。このGaN系MOSFETでは、ゲート絶縁膜として、抵抗率が1012Ωcm以上と非常に高いSiO2膜を採用している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−76673号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来のGaN系MOSFETでは、ゲート絶縁膜として抵抗率が非常に高いSiO2膜を用いているけれども、耐圧が例えば、100V程度であり、充分なものでない。

【0005】

そこで、この発明の課題は、耐圧をさらに向上できる電界効果トランジスタおよびその製造方法を提供することにある。

【課題を解決するための手段】

【0006】

本発明者らは、ゲート絶縁膜は、従来の抵抗率が高い程、耐圧が向上するという従来の常識に反して、抵抗率が1011Ωcm以下の半絶縁膜を用いることで、抵抗率が1012Ωcm以上のSiO2膜を採用した場合に比べて、耐圧が格段に向上することを発見した。

【0007】

ゲート絶縁膜の抵抗率を低くした方が、耐圧が向上するのは、一般に考えられているのと逆であり、予測外の現象であったが、ゲート絶縁膜として、抵抗率が1011Ωcm以下の半絶縁膜を用いることにより、耐圧が大幅に向上することが本発明者らによる実験により判明した。

【0008】

本発明は、このようなゲート絶縁膜を、抵抗率が1×1011Ωcm以下の半絶縁膜とすることで耐圧が大幅に向上するという本発明者らの実験による発見に基づいて創出された。

【0009】

すなわち、この発明の電界効果トランジスタは、窒化物半導体層と、

上記窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されると共に互いに間隔をおいて配置されたソース電極およびドレイン電極と、

上記窒化物半導体層上に形成されると共に上記ソース電極と上記ドレイン電極との間に配置されたゲート電極と、

上記ゲート電極と上記窒化物半導体層との間に形成されたゲート絶縁膜と

を備え、

上記ゲート絶縁膜を、

抵抗率が107Ωcmから1011Ωcmである半絶縁膜としたことを特徴としている。

【0010】

この発明の電界効果トランジスタによれば、ゲート絶縁膜をなす半絶縁膜の抵抗率が、1011Ωcm以下であるという構成によって、図3に示す特性Jのように、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できることが判明した。

【0011】

なお、図3において、縦軸の耐圧(V)は、常温(25℃)で、ソース電極に0Vを印加し、ゲート電極に−10Vを印加した条件において、ドレイン電極‐ソース電極間の電圧Vdsを50V間隔で破壊するまで増加させ、破壊する直前の電圧Vds(V)とした。また、本発明において、ゲート絶縁膜をなす半絶縁膜の抵抗率(107Ωcm〜1011Ωcm)の値は、この半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。

【0012】

また、上記ゲート絶縁膜をなす半絶縁膜の抵抗率が、107Ωcm以上であるという構成によって、上記ゲート絶縁膜の抵抗率が、107Ωcm未満である場合に比べて、ゲートリーク電流を低減できることが判明した。

【0013】

なお、上記ゲートリーク電流は、常温(25℃)で、ソース電極に0Vを印加し、ドレイン電極に600Vを印加し、ゲート電極に−10Vを印加した条件において、測定したゲートリーク電流の値である。

【0014】

また、一実施形態では、上記窒化物半導体層は、GaN系半導体層である。

【0015】

この実施形態によれば、上記GaN系半導体層により、砒化ガリウム(GaAs)系の材料に比べてバンドギャップエネルギーが大きく、しかも耐熱性が優れ高温での動作が可能である。

【0016】

また、一実施形態では、さらに、上記ソース電極と上記ドレイン電極との間で上記窒化物半導体層上に形成されていると共に電流コラプスを抑制するための絶縁膜を備えた。

【0017】

この実施形態によれば、上記絶縁膜により、電流コラプスを抑制することができる。上記電流コラプスとは、GaN系半導体素子において、特に、問題になっているもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0018】

また、この発明の電界効果トランジスタの製造方法は、窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されるように互いに間隔をおいてソース電極およびドレイン電極を形成し、

上記窒化物半導体層上かつ上記ソース電極と上記ドレイン電極との間に抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲート電極を形成することを特徴とする。

【0019】

この発明の電界効果トランジスタの製造方法によれば、抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成するので、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、上記ゲート絶縁膜の抵抗率が107Ωcm未満である場合に比べて、ゲートリーク電流を低減できる。

【0020】

また、一実施形態の電界効果トランジスタの製造方法は、窒化物半導体層上に電流コラプスを抑制するための第1の絶縁膜を形成し、

上記第1の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の予め定められた領域を露出させ、

上記第1の絶縁膜上および上記第1の絶縁膜から露出した上記窒化物半導体層上に第2の絶縁膜を形成し、

上記第2の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の上記予め定められた領域を露出させ、

上記第2の絶縁膜上および上記第2の絶縁膜から露出した上記窒化物半導体層の上記予め定められた領域上に、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲートメタルを蒸着してゲート電極を形成することを特徴としている。

【0021】

この発明の電界効果トランジスタの製造方法によれば、上記第1,第2の絶縁膜を順に形成,エッチング加工した後に、上記ゲート絶縁膜を形成する。したがって、上記第2の絶縁膜にゲート電極のための開口部を形成するために上記第2の絶縁膜をエッチング加工する工程は、上記ゲート絶縁膜を形成する前に行なわれることとなる。よって、上記第2の絶縁膜をエッチング加工する工程を、上記ゲート絶縁膜の形成後に行なう必要がなくなって、上記第2の絶縁膜のエッチング加工に起因して上記ゲート絶縁膜の膜厚がばらつくことを回避できる。ゲート絶縁膜の膜厚は、しきい値を規定する極めて重要なファクターであるので、ゲート絶縁膜の膜厚ばらつきを抑制することが強く求められている。

【0022】

本発明の電界効果トランジスタの製造方法によれば、ゲート絶縁膜の膜厚を精度良く設定でき、安定したしきい値電圧を得ることができる。

【0023】

また、この発明の電界効果トランジスタの製造方法によれば、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成するので、前述の如く、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共にゲートリーク電流を低減できる。

【0024】

また、上記第1の絶縁膜でもって、電流コラプスを抑制することができる。上記電流コラプスとは、GaN系半導体素子において、特に、問題になっているもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。上記第1の絶縁膜は、例えば、SiリッチなSiN膜で構成される。SiリッチなSiN膜とは、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜である。また、上記第1の絶縁膜上に形成された第2の絶縁膜により、ゲートリーク電流をさらに低減できる。この第2の絶縁膜は、例えば、ストイキオメトリなシリコン窒化膜で作製される。

【発明の効果】

【0025】

この発明の電界効果トランジスタによれば、ゲート絶縁膜をなす半絶縁膜の抵抗率が、1011Ωcm以下であるという構成によって、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できることが判明した。

【図面の簡単な説明】

【0026】

【図1】この発明の電界効果トランジスタの第1実施形態であるGaN系HFETを示す断面図である。

【図2A】上記第1実施形態のGaN系HFETの製造工程を説明する断面図である。

【図2B】図2Aの工程に続く工程を説明する断面図である。

【図2C】図2Bの工程に続く工程を説明する断面図である。

【図3】ゲート絶縁膜の抵抗率と耐圧との関係を示す特性図である。

【図4】上記第1実施形態が備えるゲート絶縁膜をなす半絶縁膜に印加する電界を変化させたときの電流密度の変化を表す特性K1および上記印加電界を変化させたときの抵抗率の変化を表す特性K2を示すI-V特性図である。

【図5】高絶縁膜(SiO2)に印加する電界を変化させたときの電流密度の変化を表す特性K101および上記電界を変化させたときの抵抗率の変化を表す特性K102を示すI-V特性図である。

【図6】この発明の電界効果トランジスタの第2実施形態であるGaN系HFETを示す断面図である。

【図7A】上記第1実施形態のGaN系HFETの製造工程を説明する断面図である。

【図7B】図7Aの工程に続く工程を説明する断面図である。

【図7C】図7Bの工程に続く工程を説明する断面図である。

【図7D】図7Cの工程に続く工程を説明する断面図である。

【発明を実施するための形態】

【0027】

以下、この発明を図示の実施の形態により詳細に説明する。

【0028】

(第1の実施の形態)

図1は、この発明の電界効果トランジスタの第1実施形態であるノーマリーオンタイプのGaN系HFET(ヘテロ接合電界効果トランジスタ)を示す断面図である。

【0029】

この第1実施形態のGaN系HFETは、図1に示すように、Si基板(図示せず)上に、アンドープGaN層11と、アンドープAlGaN層12を順に形成している。このアンドープGaN層11とアンドープAlGaN層12との界面に2DEG(2次元電子ガス)19が発生する。このアンドープGaN層11とアンドープAlGaN層12で窒化物半導体積層体を構成している。なお、上記基板は、Si基板に限らず、サファイヤ基板やSiC基板を用いてもよく、サファイヤ基板やSiC基板上に窒化物半導体層を成長させてもよいし、GaN基板にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。また、上記アンドープGaN層11とアンドープAlGaN層12との間に層厚1nmのAlN層を形成してもよい。

【0030】

上記アンドープAlGaN層12上に、予め設定された間隔をあけてソース電極13とドレイン電極14を形成している。上記アンドープAlGaN層12上のソース電極13とドレイン電極14との間かつソース電極13側にゲート電極15を形成している。ここでは、上記アンドープAlGaN層12の厚さを例えば10nmとしてソース電極13とドレイン電極14をアニールすることでオーミックコンタクト可能にしている。なお、上記アンドープAlGaN層12の厚さを例えば30nmとしてアンドープAlGaN層12のオーミックコンタクト部分に予めSiドープをしてn型化させることで電極のオーミックコンタクトを可能としてもよい。また、アンドープAlGaN層12のソース電極およびドレイン電極下に予め、リセスを形成し、ソース電極およびドレイン電極を蒸着、アニールすることでオーミックコンタクトを可能としてもよい。

【0031】

図1に示すように、上記ゲート電極15とアンドープAlGaN層12との間には、ゲート絶縁膜17が形成されている。このゲート絶縁膜17は、一例として、半絶縁膜としてのSiリッチなシリコン窒化膜で作製される。このSiリッチなシリコン窒化膜とは、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜であり、例えば、SiとNとの組成比Si:N=1.1〜1.9:1である。また、好ましい一例では、SiとNとの組成比Si:N=1.3〜1.5:1である。

【0032】

また、ゲート絶縁膜17とソース電極13との間のアンドープAlGaN層12上およびゲート絶縁膜17とドレイン電極14との間のアンドープAlGaN層12上に保護膜18が形成されている。この保護膜18は、電流コラプスを抑制するための絶縁膜であり、一例として、Siリッチなシリコン窒化膜で作製されている。

【0033】

また、ゲート絶縁膜17とソース電極13との間の保護膜18上およびゲート絶縁膜17とドレイン電極14との間の保護膜18上にプロセス絶縁膜20が形成されている。このプロセス絶縁膜20は、一例として、Si:N=0.75:1のストイキオメトリなシリコン窒化膜で作製されている。

【0034】

この第1実施形態では、一例として、上記ゲート絶縁膜17の膜厚を20nmとし、上記保護膜18の膜厚を30nmとし、プロセス絶縁膜20の膜厚を150nmとした。

【0035】

次に、図2A〜図2Cを順に参照して、上記GaN系HFETの製造方法を説明する。

【0036】

まず、図示しないSi基板上に、図2Aに示すように、MOCVD(有機金属気相成長)法を用いて、アンドープGaN層11、アンドープAlGaN層12、を順に形成する。このアンドープGaN層11とアンドープAlGaN層12が窒化物半導体積層体を構成している。

【0037】

次に、図2Aに示すように、上記アンドープAlGaN層12上に、プラズマCVD法を用いて、保護膜18となるシリコン窒化膜28を形成する。この保護膜18となるシリコン窒化膜28の成長温度は、一例として、225℃としたが、200℃〜400℃の範囲で設定してもよい。また、上記保護膜18となるシリコン窒化膜28の膜厚は、一例として、30nmとしたが、20nm〜250nmの範囲で設定してもよい。

【0038】

また、一例として、上記プラズマCVD法によりシリコン窒化膜28を形成する際のガス流量比は、N2/NH3/SiH4=300sccm/40sccm/35sccmとした。これにより、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなシリコン窒化膜28を形成できる。このシリコン窒化膜28によれば、ストイキオメトリなシリコン窒化膜に比べて、電流コラプスをより抑制できる。また、例えば、保護膜18となるシリコン窒化膜28のSiとNとの組成比Si:N=1.1〜1.9:1にすると、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりも電流コラプスの抑制に有効である。この電流コラプスとは、特に、GaN系半導体素子において顕著に表れるもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0039】

次に、上記保護膜18となるシリコン窒化膜28上にフォトレジスト層(図示せず)を形成し、露光,現像することにより、ソース電極13,ドレイン電極14を形成すべき領域の上記フォトレジスト層、および、ゲート絶縁膜17を形成すべき領域の上記フォトレジスト層を除去し、このフォトレジスト層をマスクとして、ドライエッチングを行なう。これにより、図2Aに示すように、上記保護膜18となるシリコン窒化膜28のうち、ソース電極13,ドレイン電極14を形成すべき領域、および、ゲート絶縁膜17を形成すべき領域を除去して、この領域にアンドープAlGaN層12を露出させる。

【0040】

次に、上記保護膜18となるシリコン窒化膜28を熱処理する。この熱処理の温度は、例えば、500℃で30分間とした。なお、上記熱処理の温度は、一例として、500℃〜700℃の範囲で設定してもよい。

【0041】

その後、図2Bに示すように、上記保護膜18上に、プラズマCVD(化学的気相成長)法により、ゲート絶縁膜17となる半絶縁膜としてのシリコン窒化膜27を形成する。このゲート絶縁膜17となるシリコン窒化膜27は、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率を大きくしている。

【0042】

ここで、上記ゲート絶縁膜17となるシリコン窒化膜27を形成するときのプラズマCVDによる成膜条件としては、一例として、RFパワーを50(W)とし、SiH4とNH3の流量比(SiH4/NH3)を0.92とし、圧力を0.7Torrとし、基板温度を225℃とした。

【0043】

次に、レジストを用いたパターニングにより、上記シリコン窒化膜27のうちの開口22に露出したAlGaN層12および上記開口22の周縁の保護膜18を覆う部分を残して、図2Bに示すように、ゲート絶縁膜17を形成する。

【0044】

次に、図2Cに示すように、プラズマCVD法により、プロセス絶縁膜20となるストイキオメトリなシリコン窒化膜29を形成してから、フォトリソグラフィとエッチングにより、ゲート電極15を形成する部分に開口21を形成する。

【0045】

その後、TiNを全面スパッタし、フォトリソグラフィでゲート電極15を形成すべき電極形成領域にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ドライエッチングまたはウェットエッチングを行なって、上記電極形成領域以外のTiN膜を除去して、図2Cに示すように、TiN電極によるゲート電極15を形成する。このゲート電極15の直下には、ゲート絶縁膜17が位置している。

【0046】

次に、フォトリソグラフィとエッチングにより、図2Cに示すように、ソース電極13,ドレイン電極14を形成する部分のシリコン窒化膜29に開口31,32を形成する。

【0047】

次に、フォトリソグラフィにより、ソース電極13,ドレイン電極14を形成すべき領域(上記開口31,32に露出したAlGaN層12の領域)が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上にTi,Alを順に蒸着し、リフトオフにより、図1に示すように、上記露出したAlGaN層12上にTi/Al電極によるソース電極13,ドレイン電極14を形成する。上記Ti/Al電極は、Ti層,Al層が順に積層された積層構造の電極である。次に、上記ソース電極13,ドレイン電極14を、熱処理してオーミック電極にする。この熱処理(オーミックアニール)の条件は、一例として500℃で30分としたが、上記熱処理の条件は、これに限らず、例えば、上記熱処理温度を、400℃〜600℃の範囲内で設定してもよい。

【0048】

こうして作製した上記第1実施形態のGaN系HFETによれば、ゲート絶縁膜15をなす半絶縁膜の抵抗率ρは、3.9×109Ωcmであった。上記抵抗率ρの値(3.9×109Ωcm)は、上記半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。

【0049】

この第1実施形態では、抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、図3に示すように、1000Vの耐圧が得られた。なお、図3の横軸は抵抗率(Ωcm)であり、横軸目盛1.E+06、1.E+07、1.E+08、1.E+09、…、1.E+13は、それぞれ、106、107(Ωcm)、108(Ωcm)、109(Ωcm)、…、1013(Ωcm)を表す。また、図3において、縦軸の耐圧(V)は、常温(25℃)で、ソース電極に0Vを印加し、ゲート電極に−10Vを印加した条件において、ドレイン電極‐ソース電極間の電圧Vdsを50V間隔で絶縁破壊するまで増加させ、絶縁破壊する直前の電圧Vds(V)とした。

【0050】

図3に示すように、ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると、耐圧が急減していることが分かる。また、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回ると、ゲートリーク電流が増大することが判明した。このゲートリーク電流は、常温(25℃)で、ソース電極に0Vを印加し、ドレイン電極に600Vを印加し、ゲート電極に−10Vを印加した条件において、測定したゲートリーク電流の値である。

【0051】

また、図3において、プロットPは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが約1×1010(Ωcm)である場合に、この半絶縁膜を680℃で1時間アニールした場合の耐圧と抵抗率を示している。プロットPで示すように、ゲート絶縁膜17をアニール(680℃,1時間)することで、アニールしない場合の耐圧800Vに比べて、同じ抵抗率でも耐圧を200V以上向上できた。

【0052】

次に、図4を参照して、上記抵抗率ρ=3.9×109Ωcmの半絶縁膜のI‐V特性K1を説明する。

【0053】

この半絶縁膜のI‐V特性K1は、上記半絶縁膜を2つの電極間に挟んで上記半絶縁膜に印加する電界を変化させたときに上記2つの電極間に流れる電流密度の変化を表わすグラフである。なお、図4の左側の縦軸は電流密度(A/cm2)であり、縦軸目盛の1.E−09、1.E−08、1.E−07、1.E−06、…、1.E+01は、それぞれ、10−9(A/cm2)、10−8(A/cm2)、10−7(A/cm2)、10−6(A/cm2)、…、10+1(A/cm2)を表している。

【0054】

上記半絶縁膜では、I‐V特性K1に示すように、電界が5〜15(MV/cm)の範囲において、電界の増加にほぼ比例して電流密度が増加しているが、電界が15(MV/cm)を超えても絶縁破壊には至っていない。

【0055】

また、図4における特性K2は、横軸の印加電界の変化に対して、右側の縦軸で表す抵抗率(Ωcm)がどの様に変化するのかを表している。なお、図4の右側の縦軸目盛の1.E+05、1.E+06、1.E+07、1.E+08、…、1.E+15は、それぞれ、105(Ωcm)、106(Ωcm)、107(Ωcm)、108(Ωcm)、…、1015(Ωcm)を表している。この特性K2における抵抗率(Ωcm)は、上記I‐V特性K1における電界を電流密度で除算した値としている。上記半絶縁膜は、印加電界を増加させることにより、上記特性K2における抵抗率が減少していることが分かる。

【0056】

次に、図5を参照して、高絶縁膜(SiO2)のI‐V特性K101を説明する。この高絶縁膜(SiO2)のI‐V特性K101は、上記高絶縁膜(SiO2)を2つの電極間に挟んで上記高絶縁膜(SiO2)に印加する電界を変化させたときに上記2つの電極間に流れる電流密度の変化を表わすグラフである。なお、図5の左側の縦軸は電流密度(A/cm2)であり、縦軸目盛の1.E−09、1.E−08、1.E−07、1.E−06、…、1.E+01は、それぞれ、10−9(A/cm2)、10−8(A/cm2)、10−7(A/cm2)、10−6(A/cm2)、…、10+1(A/cm2)を表している。

【0057】

この高絶縁膜(SiO2)では、I‐V特性K101に示すように、印加電界が8(MV/cm)を超えると電流密度が急増し、印加電界が10(MV/cm)を超えると絶縁破壊に至っている。一方、図5の特性K102は、横軸の印加電界の変化に対して、右側の縦軸で表す抵抗率(Ωcm)がどの様に変化するのかを表している。この特性K102における抵抗率(Ωcm)は、上記I‐V特性K101における電界を電流密度で除算した値としている。なお、図5の右側の縦軸目盛の1.E+05、1.E+06、1.E+07、1.E+08、…、1.E+15は、それぞれ、105(Ωcm)、106(Ωcm)、107(Ωcm)、108(Ωcm)、…、1015(Ωcm)を表している。この高絶縁膜(SiO2)は、印加電界が8(MV/cm)までは抵抗率が大きく変化しないが印加電界が8(MV/cm)を超えると抵抗率が急減し、印加電界が10(MV/cm)を超えると絶縁破壊に至っている。

【0058】

このように、高絶縁膜(SiO2)では、図5の特性K101のように、印加電界が10(MV/cm)を超えると絶縁破壊に至っているのに対して、本実施形態でゲート絶縁膜15として採用した上記半絶縁膜(抵抗率ρ=3.9×109Ωcm)では、図4の特性K1のように、印加電界の増加に比例して電流密度が増加するI-V特性を示し、印加電界が15(MV/cm)を超えても絶縁破壊に至っていない。

【0059】

すなわち、本実施形態のGaN系HFETのように、ゲート絶縁膜15として、電流密度が6.25×10−4(A/cm2)であるときの抵抗率が3.9×109Ωcmの半絶縁膜を採用したことで、ゲート絶縁膜として抵抗率が1×1012(Ωcm)を超える高絶縁膜(SiO2)を採用した場合に比べて、耐圧を著しく向上できることが判明した。

【0060】

また、前述の図3に示すように、上記ゲート絶縁膜としての半絶縁膜の抵抗率を、107Ωcm〜1011Ωcmの範囲内に設定することで、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、ゲート絶縁膜の抵抗率が107Ωcm未満である場合に比べて、ゲートリーク電流を低減できる。

【0061】

(第2の実施の形態)

図6は、この発明の電界効果トランジスタの第2実施形態であるノーマリーオンタイプのGaN系HFET(ヘテロ接合電界効果トランジスタ)を示す断面図である。

【0062】

この第2実施形態のGaN系HFETは、図6に示すように、Si基板(図示せず)上に、アンドープGaN層51と、アンドープAlGaN層52を順に形成している。このアンドープGaN層51とアンドープAlGaN層52との界面に2DEG(2次元電子ガス)59が発生する。このアンドープGaN層51とアンドープAlGaN層52で窒化物半導体積層体を構成している。

【0063】

上記アンドープAlGaN層52上に、予め設定された間隔をあけてソース電極53とドレイン電極54を形成している。上記アンドープAlGaN層52上のソース電極53とドレイン電極54との間かつソース電極53側にゲート電極55を形成している。ここでは、上記アンドープAlGaN層52の厚さを例えば10nmとしてソース電極53とドレイン電極54をアニールすることでオーミックコンタクト可能にしている。なお、上記アンドープAlGaN層52の厚さを例えば30nmとしてアンドープAlGaN層52のオーミックコンタクト部分に予めSiドープをしてn型化させることで電極のオーミックコンタクトを可能としてもよい。また、アンドープAlGaN層52のソース電極およびドレイン電極下に予め、リセスを形成し、ソース電極およびドレイン電極を蒸着、アニールすることでオーミックコンタクトを可能としてもよい。

【0064】

この第2実施形態では、図6に示すように、上記ゲート電極55とアンドープAlGaN層52との間には、ゲート絶縁膜57が形成されている。また、上記ゲート電極55と上記アンドープAlGaN層52とで挟まれている上記ゲート絶縁膜57と上記ソース電極53,ドレイン電極54との間で上記アンドープAlGaN層52上に第1の絶縁膜としての保護膜58が形成されている。この保護膜58は、一例として、Siリッチなシリコン窒化膜で作製されていて、電流コラプスを抑制するための絶縁膜である。このSiリッチなシリコン窒化膜とは、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きいSiN膜であり、例えば、SiとNとの組成比Si:N=1.1〜1.9:1である。また、好ましい一例では、SiとNとの組成比Si:N=1.3〜1.5:1である。

【0065】

また、この第2実施形態では、上記保護膜58上に第2の絶縁膜としてのプロセス絶縁膜60が形成されている。このプロセス絶縁膜60上に、上記ゲート絶縁膜57および上記ゲート電極55が形成されている。また、上記ゲート電極55およびゲート絶縁膜57上に層間絶縁膜61が形成されている。また、ソース電極53およびドレイン電極54上には給電用のメタル81,82が形成されている。

【0066】

この第2実施形態では、一例として、上記ゲート絶縁膜57の膜厚を20nmとし、上記保護膜58の膜厚を30nmとし、プロセス絶縁膜60を150nmとした。

【0067】

次に、図7A〜図7Dを順に参照して、上記GaN系HFETの製造方法を説明する。

【0068】

まず、図示しないSi基板上に、図7Aに示すように、MOCVD(有機金属気相成長)法を用いて、アンドープGaN層51、アンドープAlGaN層52、を順に形成する。このアンドープGaN層51とアンドープAlGaN層52が化合物半導体積層体を構成している。なお、上記基板は、Si基板に限らず、サファイヤ基板やSiC基板を用いてもよく、サファイヤ基板やSiC基板上に窒化物半導体層を成長させてもよいし、GaN基板にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。

【0069】

次に、図7Aに示すように、上記アンドープAlGaN層52上に、プラズマCVD法を用いて、第1の絶縁膜としての保護膜58となるシリコン窒化膜68を形成する。この保護膜58となるシリコン窒化膜68の成長温度は、一例として、225℃としたが、200℃〜400℃の範囲で設定してもよい。また、上記保護膜58となるシリコン窒化膜68の膜厚は、一例として、30nmとしたが、20nm〜250nmの範囲で設定してもよい。

【0070】

また、一例として、上記プラズマCVD法によりシリコン窒化膜68を形成する際のガス流量比は、N2/NH3/SiH4=300sccm/40sccm/35sccmとした。これにより、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなシリコン窒化膜68を形成できる。このシリコン窒化膜68によれば、ストイキオメトリなシリコン窒化膜に比べて、電流コラプスをより抑制できる。また、例えば、第1の絶縁膜としての保護膜58となるシリコン窒化膜68のSiとNとの組成比Si:N=1.1〜1.9:1にすると、Si:N=0.75:1のストイキオメトリなシリコン窒化膜よりも電流コラプスの抑制に有効である。この電流コラプスとは、特に、GaN系半導体素子において顕著に表れるもので、低電圧動作でのトランジスタのオン抵抗と比べて、高電圧動作でのトランジスタのオン抵抗が著しく高くなってしまう現象である。

【0071】

次に、上記保護膜58となるシリコン窒化膜68上にフォトレジスト層(図示せず)を形成し、露光,現像することにより、ソース電極53,ドレイン電極54を形成すべき領域の上記フォトレジスト層、および、ゲート絶縁膜57を形成すべき領域の上記フォトレジスト層を除去し、このフォトレジスト層をマスクとして、ドライエッチングを行なう。これにより、図7Aに示すように、上記第1の絶縁膜としての保護膜58となるシリコン窒化膜68からソース電極53,ドレイン電極54を形成すべき領域、および、ゲート絶縁膜57を形成すべき領域のアンドープAlGaN層52を露出させる。

【0072】

次に、上記第1の絶縁膜としての保護膜58となるシリコン窒化膜68を熱処理する。この熱処理の温度は、例えば、500℃で30分間とした。なお、上記熱処理の温度は、一例として、500℃〜700℃の範囲で設定してもよい。

【0073】

その後、図7Bに示すように、上記保護膜58から露出したAlGaN層52上に、プラズマCVD(化学的気相成長)法により、第2の絶縁膜としてのプロセス絶縁膜60となるシリコン窒化膜70を形成する。このプロセス絶縁膜60となるシリコン窒化膜70は、ストイキオメトリなシリコン窒化膜とした。次に、フォトリソグラフィによりフォトレジストによるマスクを形成して、上記第2の絶縁膜としてのプロセス絶縁膜60となるシリコン窒化膜70をウェットエッチングにより等方的にエッチングする。これにより、図7Bに示すように、上記シリコン窒化膜70のうちの、ゲート電極55,ゲート絶縁膜57を形成すべき領域を除去して、AlGaN層52に向かって先細形状の開口部77を形成する。

【0074】

次に、図7Cに示すように、上記第2の絶縁膜としてのプロセス絶縁膜60上およびプロセス絶縁膜60の開口部77に露出したAlGaN層52上に、プラズマCVD(化学的気相成長)法により、ゲート絶縁膜57となる半絶縁膜としてのシリコン窒化膜を形成する。このゲート絶縁膜57としてのシリコン窒化膜は、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率を大きくしている。

【0075】

ここで、上記ゲート絶縁膜57となるシリコン窒化膜を形成するときのプラズマCVDによる成膜条件としては、一例として、RFパワーを50(W)とし、SiH4とNH3の流量比(SiH4/NH3)を0.92とし、圧力を0.7Torrとし、基板温度を225℃とした。

【0076】

その後、TiNを全面スパッタし、フォトリソグラフィでゲート電極55を形成すべき電極形成領域にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、ドライエッチングまたはウェットエッチングを行なって、上記電極形成領域以外のTiN膜を除去して、図7Dに示すように、TiN電極によるゲート電極55を形成する。このゲート電極55の直下には、ゲート絶縁膜57となるシリコン窒化膜67が位置している。

【0077】

次に、上記ゲート電極55上にレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、上記ゲート電極55下以外の領域のシリコン窒化膜67をエッチングして、ゲート絶縁膜57とする。

【0078】

次に、フォトリソグラフィでソース電極53,ドレイン電極54を形成すべき領域が開口したレジストパターン(図示せず)を形成し、このレジストパターンをマスクとして、上記シリコン窒化膜70をエッチングして、プロセス絶縁膜60とする。

【0079】

次に、フォトリソグラフィにより、ソース電極53,ドレイン電極54を形成すべき領域(露出したAlGaN層52の領域)が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上にTi,Alを順に蒸着し、リフトオフにより、図6に示すように、上記露出したAlGaN層52上にTi/Al電極によるソース電極53,ドレイン電極54を形成する。上記Ti/Al電極は、Ti層,Al層が順に積層された積層構造の電極である。次に、上記ソース電極53,ドレイン電極54を、熱処理してオーミック電極にする。この熱処理(オーミックアニール)の条件は、一例として500℃で30分としたが、上記熱処理の条件は、これに限らず、例えば、上記熱処理温度を、400℃〜600℃の範囲内で設定してもよい。

【0080】

次に、プラズマCVD法により、層間絶縁膜61となるストイキオメトリなシリコン窒化膜を形成し、CMP(化学的機械的研磨)法等の方法で平坦化する。次に、ソース電極53,ドレイン電極54上の領域が開口したフォトレジスト(図示せず)を形成し、このフォトレジスト上に給電メタルを順に蒸着して、給電メタル81,82を形成する。上記給電メタルとしては、例えば、Al,Cu等が用いられる。

【0081】

こうして作製した上記第2実施形態のGaN系HFETによれば、ゲート絶縁膜57をなす半絶縁膜の抵抗率ρは、3.9×109Ωcmであった。上記抵抗率ρの値(3.9×109Ωcm)は、上記半絶縁膜を2つの電極間に挟んで測定した値であり、この電極間に流れる電流密度が6.25×10−4(A/cm2)であるときの値である。この半絶縁膜のI‐V特性は、前述の図4に示すI‐V特性K1と同様である。

【0082】

この第2実施形態では、抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜57を備えたことで、図3に示すように、1000Vの耐圧が得られた。

【0083】

すなわち、この第2実施形態によれば、ゲート絶縁膜57をなす半絶縁膜の抵抗率が3.9×109Ωcmであり、上記半絶縁膜の抵抗率が107Ωcm以上かつ1011Ωcm以下であるので、上述の如く、ゲート絶縁膜の抵抗率が1011Ωcmを超える場合に比べて、耐圧を著しく向上できると共に、ゲート絶縁膜の抵抗率が107Ωcmを下回る場合に比べて、ゲートリーク電流を低減できる。

【0084】

また、図7A〜図7Dを順に参照して説明した上記第2実施形態のGaN系HFETの製造方法によれば、図7A〜図7Cに示すように、上記第1の絶縁膜としての保護膜58と上記第2の絶縁膜としてのプロセス絶縁膜60を順に形成,エッチング加工した後に、上記ゲート絶縁膜57を形成する。したがって、ゲート電極55下のゲート絶縁膜57の厚みは、AlGaN層52が露出した状態でゲート絶縁膜57が堆積され、その後にエッチング工程がないことから、プラズマCVD法によるゲート絶縁膜57の堆積膜厚のみで決定される。

【0085】

よって、エッチング加工に起因して上記ゲート絶縁膜57の膜厚がばらつくことを回避できる。したがって、安定したしきい値電圧を得ることができる。

【0086】

また、上記シリコンリッチなシリコン窒化膜で作製した保護膜58によって、電流コラプスを抑制できると共に、上記ストイキオメトリなシリコン窒化膜で作製したプロセス絶縁膜60によって、ゲートリーク電流をさらに低減できる。

【0087】

尚、上記第1,第2実施形態では、ゲート絶縁膜をなす半絶縁膜を、ストイキオメトリなシリコン窒化膜よりもシリコンSiの比率の大きなSiN膜としたが、SiON膜としてもよい。また、上記第1,第2実施形態において、ゲート絶縁膜を形成してからゲート絶縁膜をアニールすることで、耐圧をさらに向上できる。

【0088】

また、上記第1,第2実施形態では、このGaN系半導体積層体を、GaN層とAlGaN層で構成したが、AlxInyGa1-x-yN(x≧0、y≧0、0≦x+y<1)で表されるGaN系半導体層を含むものでもよい。すなわち、上記GaN系半導体積層体は、AlGaN、GaN、InGaN等を含むものとしてもよい。また、上記実施形態では、ノーマリオンタイプのHFETについて説明したがノーマリオフタイプでも同様の効果が得られる。

【0089】

また、上記第1,第2実施形態では、基板としてSi基板を用いたが、サファイア基板やSiC基板を用いてもよい。また、上記GaN基板上にAlGaN層を成長させる等のように、窒化物半導体からなる基板上に窒化物半導体層を成長させてもよい。また、適宜、バッファ層を基板と各層間に形成してもよい。また、GaN層11,51とAlGaN層12,52との間に、一例として層厚1nm程度のAlNで作製したヘテロ改善層を形成してもよい。また、上記AlGaN層12,52上にGaNキャップ層を形成してもよい。また、上記実施形態では、ゲート電極15,55をTiNで作製したが、WNで作製してもよい。また、ゲート電極15,55をPt/AuやNi/Auで作製してもよい。また、上記ゲート電極材料として、上記窒化物半導体と接合した場合にショットキー接合となる材料を用いるようにしてもよい。

【0090】

また、上記第1,第2実施形態では、上記オーミック電極としてのソース電極13,53とドレイン電極14,54を、Ti層,Al層が順に積層されたTi/Al電極としたが、Ti層,Al層,TiN層が順に積層されたTi/Al/TiN電極としてもよい。また、上記Al層の代わりにAlSi層やAlCu層を用いてもよい。また、ソース電極,ドレイン電極としては、Hf/Al電極としてもよい。また、ソース電極,ドレイン電極としては、Ti/AlまたはHf/Al上にNi/Auを積層したものとしてもよく、Ti/AlまたはHf/Al上にPt/Auを積層したものとしてもよく、Ti/AlまたはHf/Al上にAuを積層したものとしてもよい。

【0091】

この発明の具体的な実施の形態について説明したが、この発明は上記実施形態に限定されるものではなく、この発明の範囲内で種々変更して実施することができる。

【符号の説明】

【0092】

11,51 アンドープGaN層

12,52 アンドープAlGaN層

13,53 ソース電極

14,54 ドレイン電極

15,55 ゲート電極

17,57 ゲート絶縁膜

18,58 保護膜

19,59 2次元電子ガス

20,60 プロセス絶縁膜

22,62,77 開口部

27,28,68,70 シリコン窒化膜

61 層間絶縁膜

【特許請求の範囲】

【請求項1】

窒化物半導体層と、

上記窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されると共に互いに間隔をおいて配置されるソース電極およびドレイン電極と、

上記窒化物半導体層上に形成される共に上記ソース電極と上記ドレイン電極との間に配置されたゲート電極と、

上記ゲート電極と上記窒化物半導体層との間に形成されたゲート絶縁膜と

を備え、

上記ゲート絶縁膜は、

抵抗率が107Ωcmから1011Ωcmである半絶縁膜であることを特徴とする電界効果トランジスタ。

【請求項2】

請求項1に記載の電界効果トランジスタにおいて、

上記窒化物半導体層は、GaN系半導体層であることを特徴とする電界効果トランジスタ。

【請求項3】

請求項1または2に記載の電界効果トランジスタにおいて、

さらに、上記ソース電極と上記ドレイン電極との間で上記窒化物半導体層上に形成されていると共に電流コラプスを抑制するための絶縁膜を備えたことを特徴とする電界効果トランジスタ。

【請求項4】

窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されるように互いに間隔をおいてソース電極およびドレイン電極を形成し、

上記窒化物半導体層上かつ上記ソース電極と上記ドレイン電極との間に抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲート電極を形成することを特徴とする電界効果トランジスタの製造方法。

【請求項5】

窒化物半導体層上に電流コラプスを抑制するための第1の絶縁膜を形成し、

上記第1の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の予め定められた領域を露出させ、

上記第1の絶縁膜上および上記第1の絶縁膜から露出した上記窒化物半導体層上に第2の絶縁膜を形成し、

上記第2の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の上記予め定められた領域を露出させ、

上記第2の絶縁膜上および上記第2の絶縁膜から露出した上記窒化物半導体層の上記予め定められた領域上に、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲートメタルを蒸着してゲート電極を形成することを特徴とする電界効果トランジスタの製造方法。

【請求項1】

窒化物半導体層と、

上記窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されると共に互いに間隔をおいて配置されるソース電極およびドレイン電極と、

上記窒化物半導体層上に形成される共に上記ソース電極と上記ドレイン電極との間に配置されたゲート電極と、

上記ゲート電極と上記窒化物半導体層との間に形成されたゲート絶縁膜と

を備え、

上記ゲート絶縁膜は、

抵抗率が107Ωcmから1011Ωcmである半絶縁膜であることを特徴とする電界効果トランジスタ。

【請求項2】

請求項1に記載の電界効果トランジスタにおいて、

上記窒化物半導体層は、GaN系半導体層であることを特徴とする電界効果トランジスタ。

【請求項3】

請求項1または2に記載の電界効果トランジスタにおいて、

さらに、上記ソース電極と上記ドレイン電極との間で上記窒化物半導体層上に形成されていると共に電流コラプスを抑制するための絶縁膜を備えたことを特徴とする電界効果トランジスタ。

【請求項4】

窒化物半導体層上または上記窒化物半導体層内に少なくとも一部が形成されるように互いに間隔をおいてソース電極およびドレイン電極を形成し、

上記窒化物半導体層上かつ上記ソース電極と上記ドレイン電極との間に抵抗率が107Ωcmから1011Ωcmである半絶縁膜でゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲート電極を形成することを特徴とする電界効果トランジスタの製造方法。

【請求項5】

窒化物半導体層上に電流コラプスを抑制するための第1の絶縁膜を形成し、

上記第1の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の予め定められた領域を露出させ、

上記第1の絶縁膜上および上記第1の絶縁膜から露出した上記窒化物半導体層上に第2の絶縁膜を形成し、

上記第2の絶縁膜のうちの予め定められた領域をエッチングで除去して上記窒化物半導体層の上記予め定められた領域を露出させ、

上記第2の絶縁膜上および上記第2の絶縁膜から露出した上記窒化物半導体層の上記予め定められた領域上に、抵抗率が107Ωcmから1011Ωcmである半絶縁膜によるゲート絶縁膜を形成し、

上記ゲート絶縁膜上にゲートメタルを蒸着してゲート電極を形成することを特徴とする電界効果トランジスタの製造方法。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図7C】

【図7D】

【公開番号】特開2013−105863(P2013−105863A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−248222(P2011−248222)

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]