電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体を用いた電界効果トランジスタ(FET)および電界効果トランジスタを用いた半導体装置に関する。

【背景技術】

【0002】

電界効果トランジスタ(FET)とは、半導体にソース、ドレインという領域を設け、それぞれに電極を設けて、電位を与え、絶縁膜あるいはショットキーバリヤを介してゲートと呼ばれる電極より半導体に電界をかけ、半導体の状態を制御することにより、ソースとドレイン間に流れる電流を制御するものである。用いられる半導体としては、珪素やゲルマニウム等のIV族元素(第14族元素)やガリウムヒ素、インジウムリン、窒化ガリウム等のIII−V族化合物、硫化亜鉛、カドミウムテルル等のII−VI族化合物等が挙げられる。

【0003】

近年、酸化亜鉛や酸化インジウムガリウム亜鉛系化合物等の酸化物を半導体として用いたFETが報告された(特許文献1および特許文献2)。これらの酸化物半導体を用いたFETでは、比較的大きな移動度が得られると共に、それらの材料が3電子ボルト以上の大きなバンドギャップを有するが故に、酸化物半導体を用いたFETをディスプレーやパワーデバイス等に応用することが議論されている。

【0004】

例えば、バンドギャップが3電子ボルト以上ということは、可視光に対して透明であるので、ディスプレー用途として用いた場合、FET部分も光を透過でき、開口率が向上することが期待される。

【0005】

また、このような大きなバンドギャップという特徴は、パワーデバイスに用いられる炭化珪素と同じなので、同様にパワーデバイスに用いることが期待される。

【0006】

さらに、バンドギャップが大きいということは、熱励起キャリアが少ないことを意味する。例えば、室温において、珪素では、バンドギャップが1.1電子ボルトであるので、熱励起キャリアは1011/cm3程度であるが、バンドギャップが3.2電子ボルトの半導体では、熱励起キャリアは10−7/cm3程度と計算される。

【0007】

珪素の場合、全く、不純物を含まないものを作っても、熱励起によるキャリアが上記のように存在するため、抵抗率は、105Ωcm以上とできないが、バンドギャップが3.2電子ボルトの半導体では、理論的には、1020Ωcm以上の抵抗率が得られる。このような半導体でFETを作製し、オフ状態(ゲートの電位がソースの電位と同じ状態)における高い抵抗率を用いれば、電荷を半永久的に閉じこめることも可能となると期待される。

【0008】

ところで、特に亜鉛もしくはインジウムを有する酸化物半導体においては、これまで、P型の導電性を示すものはほとんど報告されていない。そのため、珪素のFETのようなPN接合を用いたものは報告されておらず、特許文献1および特許文献2にあるように、N型の酸化物半導体に導体電極を接触させた導体半導体接合によって、ソース、ドレインを形成していた。

【0009】

なお、一般的な半導体関連の学術書においては、「導体半導体接合」は「金属半導体接合」と表記される。この場合、金属とは、導体という意味である。例えば、高濃度にドーピングされ、抵抗率が著しく低下した半導体、あるいは、窒化チタン、窒化タングステン等の金属窒化物、酸化インジウム錫、酸化アルミニウム亜鉛等の金属酸化物等も「金属半導体接合」では金属として扱われる。しかしながら、一般に「金属」という用語では誤解を招きやすい。そのため、本明細書では「金属半導体接合」ではなく「導体半導体接合」と表記する。

【0010】

例えば、特許文献1には図5(A)に示すようなFETが開示されている。すなわち、半導体層102の一方の面に接してソース電極と呼ばれる第1の導体電極103aとドレイン電極と呼ばれる第2の導体電極103bが設けられ、半導体層102の他方の面には、間にゲート絶縁膜104を介して、ゲート105が設けられている。第1の導体電極103aと第2の導体電極103b、ゲート105は導体が用いられる。

【0011】

そして、図5(A)に幅cで示すように、ゲート105と第1の導体電極103a、およびゲート105と第2の導体電極103bは重なる部分を有することが必須とされた。すなわち、c>0であることが必要とされてきた。

【0012】

また、導体半導体接合によって、ソース電極、ドレイン電極を形成したFETでは、用いる半導体のキャリア濃度が大きいと、オフ状態でもソース電極とドレイン電極の間に電流(オフ電流)が流れてしまう。そこで、半導体中のドナーあるいはアクセプタの濃度を低減させて、I型(本明細書では、ドナーあるいはアクセプタに由来するキャリア濃度が1012/cm3以下の半導体をI型という)とすることにより、オフ電流を低減することが望まれる。

【0013】

なお、本明細書ではドナー(あるいはアクセプタ)の濃度とは、ドナー(あるいはアクセプタ)となりうる元素や化学基等の濃度に、そのイオン化率を乗じたものを言う。例えば、あるドナー元素が2%含まれていても、そのイオン化率が0.005%であれば、ドナー濃度は1ppm(=0.02×0.00005)である。

【0014】

ところで、FETを用いた半導体回路で、特にP型とN型のFETのいずれか一方しか用いることができない半導体回路では、基本回路のひとつであるインバータは、例えば、図6(A)に示すように、FETに抵抗を直列に接続したものを用いる。

【0015】

あるいは、図6(B)に示すように、FETを2つ直列に接続し、一方(通常は、VH側)のFETのドレインとゲートを短絡させて、ダイオードとしたものを用いることもある。しかしながら、図6(B)の形態のインバータは、FETのドレインとゲートを短絡させるに際し、図中にXで示す部分でコンタクトを形成する必要から集積度を上げられないという点で不利である。

【0016】

図6(A)のタイプのインバータにおいては、FETのオン時の抵抗をRON、オフ時ROFFとするとき、RON<<R<<ROFFとなるような、抵抗値Rを有する抵抗をFETに接続する。ここで、R>10RON、R<ROFF/10、好ましくは、R>100RON、R<ROFF/100とすることが望まれる。

【0017】

このタイプのインバータでは、入力がハイであれば、この抵抗とオン状態となっているFETを通って電流が流れる。インバータのVHとVLの間の抵抗は、R+RONであるが、R>>RONであれば、インバータの抵抗はRと近似できる。したがって、インバータの電源電圧をVddとすれば、消費電力は、Vdd2/R、となる。また、出力電圧は0と近似できる。

【0018】

また、入力がローでも、この抵抗とFETを通って電流が流れる。インバータの抵抗は、R+ROFFであるが、R<<ROFFであれば、インバータの抵抗はROFFと近似できる。したがって、インバータの消費電力は、Vdd2/ROFF、となる。また、出力電圧はVddと近似できる。

【0019】

上記の関係から明らかなように、RおよびROFFが大きな値であれば消費電力は抑制される。また、出力電圧は、RがRONとROFFの中間の値であることが望まれ、理想的には、R=(RON×ROFF)1/2であるとよい。また、それらの結果として、ROFF/RONが大きな値であることが望まれる。

【0020】

従来の半導体回路で、このようにP型とN型のFETのいずれか一方しか用いることができない半導体回路としては、アモルファスシリコンFETを用いた回路が知られている。

【0021】

アモルファスシリコンFETを用いたインバータ回路では、抵抗として、N型のアモルファスシリコンを用いている。N型のアモルファスシリコンは、FETのソースやドレインの材料として用いられるものであり、その一部を加工して抵抗として使うものである。N型のアモルファスシリコンの抵抗率はあまり高くはないため、抵抗の大きさはFETの大きさよりも大きくなる。

【0022】

ところで、バンドギャップが2電子ボルト以上のI型の半導体を用いてキャリア濃度を低減させたFETは、極めてオフ電流が低い、すなわち、ROFFが極めて大きく、また、移動度もアモルファスシリコンに比べればはるかに大きいため、RONも小さく、すなわち、ROFF/RONが1010以上もの大きな値となる。これだけ大きいと抵抗を形成する上で、あるいは設計する上でのマージンも大きくなる。

【0023】

しかしながら、特許文献1あるいは特許文献2のように、半導体に直接、導体を接触させて形成されるFETでは、アモルファスシリコンのFETの場合のような、抵抗とするのに適当な材料は見あたらなかった。特に、半導体のキャリア濃度を低減し、I型とした場合は、その抵抗率は極めて大きいものと考えられていたため、それを抵抗に用いることは想定されていなかった。

【先行技術文献】

【特許文献】

【0024】

【特許文献1】米国特許公開2005/0199879号公報

【特許文献2】米国特許公開2007/0194379号公報

【発明の概要】

【発明が解決しようとする課題】

【0025】

本発明は、上記に説明したような導体半導体接合を有するFETの回路設計を工夫することより優れたFETあるいは半導体装置、半導体回路、あるいはそれらの作製方法を提供することを課題とする。また、導体半導体接合の特性を生かして、優れた特性を示すFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。あるいは、作製の簡単なFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。あるいは、より集積度の高いFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。本発明は上記課題の少なくとも1つを解決する。

【課題を解決するための手段】

【0026】

以下、本発明の説明をおこなうが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、Nチャネル型FETにおいては、高い電位が与えられる方をドレイン、他方をソースとし、Pチャネル型FETにおいては、低い電位が与えられる方をドレイン、他方をソースとする。いずれの電位も同じであれば、いずれか一方をソース、他方をドレインとする。

【0027】

また、ソース電極、ドレイン電極という用語のかわりに第1の導体電極、第2の導体電極とも表現することがある。その場合は、電位の高低によって呼び名を変えない。

【0028】

本発明の第1は、半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有するFETである。

【0029】

本発明の第2は、半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、同じ面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有するFETである。

【0030】

上記の本発明の第1および第2においては、オフセット領域の幅は、10nm以上100nm以下、好ましくは、10nm以上50nm以下、より好ましくは、10nm以上20nm以下とするとよい。また、半導体層の厚さは、オフセット領域の幅以下、好ましくは、オフセット領域の幅の半分以下とするとよい。また、ゲートの幅は、オフセット領域の幅と同じもしくは大きくするとよい。

【0031】

本発明の第3は、半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、半導体層の他方の面に設けられたゲートとを有する半導体装置である。

【0032】

本発明の第4は、半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、同じ面に設けられたゲートとを有する半導体装置である。

【0033】

上記本発明の第1乃至第4において、第1乃至第3の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和(すなわち、電子親和力+0.3電子ボルト)よりも小さい、あるいは、第1および第2の導体電極と半導体層はオーミック接合であることが好ましい。

【0034】

上記本発明の第1乃至第4において、ゲートの、半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和(すなわち、電子親和力+0.6電子ボルト)よりも大きいことが好ましい。また、半導体層はI型であることが好ましい。

【0035】

上記本発明の第1乃至第4において、FETあるいは半導体回路は、適切な基板上に設けられてもよい。その際、ゲートと基板の間に半導体層を設けるか、あるいは、半導体層と基板の間にゲートを設けるとよい。

【0036】

基板に用いられる材料としては、単結晶シリコン等の半導体、各種ガラス、石英、サファイヤ、各種セラミックス等の絶縁体、アルミニウム、ステンレス鋼、銅等の導体等が挙げられる。特に半導体や導体を基板として用いるに際しては、その表面に絶縁層を設けることが好ましい。

【0037】

さらに、半導体層とゲートとの間にはゲート絶縁膜を設けてもよい。あるいは、半導体層とゲートとの間をショットキーバリヤ型接合してもよい。また、第1乃至第3の導体電極は同じ材料で構成される必要はない。すべて異なる材料で形成してもよいし、そのうちの2つを同じ材料で構成してもよい。

【0038】

なお、半導体層の種類は、酸化物に限らず、硫化物等のII−VI族化合物でもよい。また、上述のように熱励起によるキャリアを減らすためにも、半導体のバンドギャップは2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【発明の効果】

【0039】

上記の構成のいずれかを採用することにより、前記課題の少なくとも1つを解決できる。本発明は、導体半導体接合の性質を利用して、適度な抵抗領域を形成し、それを、FETのオフセット領域や半導体回路あるいは半導体装置に利用するものである。

【0040】

特許文献1あるいは特許文献2にあるようなFETにおいては、ソース電極、ドレイン電極、ゲートに導体が使用されていたが、導体による半導体への影響については、これまで、十分に考察されてこなかった。

【0041】

この点に関して、本発明者の考察によれば、導体半導体接合において、導体の仕事関数が、半導体層の電子親和力より小さな場合には、半導体層中に電子が流入し、そのためオーミック接合が形成されることが明らかとなった。

【0042】

FETにおいて、ソース電極と半導体あるいはドレイン電極と半導体との接合は、電流が流れやすいことが好ましいので、オーミック接合となるようにソース電極あるいはドレイン電極の材料が選択される。例えば、チタンや窒化チタン等である。電極と半導体との接合がオーミック接合であると、得られるFETの特性が安定し、良品率が高くなるというメリットもある。

【0043】

そのような導体半導体接合において、導体に近いほど電子の濃度が高く、大雑把な計算では、電子濃度は、導体半導体接合界面から数nmでは1020/cm3、数十nmでは1018/cm3、数百nmでは1016/cm3、数μmでも1014/cm3である。すなわち、半導体自体がI型であっても、導体との接触によって、キャリア濃度の高い領域ができてしまう。このようなキャリアの多い領域が導体半導体接合界面近傍にできることにより、導体半導体接合はオーミック接合となる。

【0044】

また、ゲートの材料としては、仕事関数が半導体層の電子親和力より大きな導体を用いれば、半導体の電子を排除する作用を有することも明らかとなった。例えば、タングステンや白金等である。このような材料を用いることによって、オフ電流を極めて小さくすることができることが解明できた。

【0045】

上記の考察によれば、図5(A)に示されるFETの半導体層102における、第1の導体電極103a、第2の導体電極103b、ゲート105を同電位とした場合での、キャリア濃度の分布は、概念的には図5(B)のように示される。ここで、第1の導体電極103a、第2の導体電極103bの仕事関数をWm、ゲート105の仕事関数をWg、半導体層102の電子親和力をφ、としたとき、Wm<φ+0.3電子ボルト、Wg>φ+0.6電子ボルトという条件を満たすものとする。

【0046】

図5(B)に示されるように、第1の導体電極103a、第2の導体電極103bから電子が注入されることにより、第1の導体電極103a、第2の導体電極103bの近傍は、極めて電子濃度の高い領域102aとなる。一方で、ゲート105に近い部分では、電子濃度が極めて低い領域102eとなる。その間の部分では、電子濃度は、第1の導体電極103a、第2の導体電極103bから離れるほど、あるいは、ゲート105に近づくほど低くなる。

【0047】

図5(B)では、領域102bの電子濃度は、領域102aより電子濃度が1桁程度低く、領域102cの電子濃度は、領域102bより電子濃度が1桁程度低く、領域102dの電子濃度は、領域102cより電子濃度が1桁程度低いことを示している。電子濃度が高いほど導電性が高まり、逆に、電子濃度が低くなると、導電性が低下し、例えば、領域102eでは絶縁体となる。

【0048】

図5(B)で示されるFETのオフ電流は、第1の導体電極103a、第2の導体電極103bの中間部分に形成される領域102eによって決定される。一方、第1の導体電極103aとゲート105、第2の導体電極103bとゲート105の重なる部分やその周辺は、オフ電流を下げる上ではほとんど関係がないことが明らかとなった。

【0049】

なお、図5(A)に示されるFETの、第1の導体電極103aと第2の導体電極103bの間隔をさらに狭めると、領域102eが狭まり、それよりも電子濃度の高い領域が多くなってしまう。こうなると、オフ電流が増大するため好ましくない。すなわち、第1の導体電極103aと第2の導体電極103bの間隔は、オフ電流を一定の値以下とするために、ある値を保つ必要がある。

【0050】

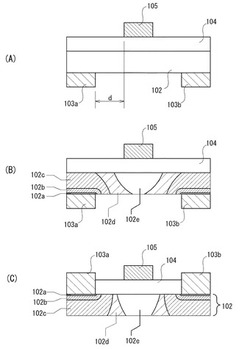

本発明者は、図5(B)に示されるような電子濃度分布は、図5(A)以外の、例えば、図1(A)のような構造でも得られることに気がついた。図1(A)の構造のFETでは、第1の導体電極103aとゲート105、あるいは、第2の導体電極103bとゲート105が重ならないように設けられ、図1(A)では、第1の導体電極103aとゲート105の間に、幅dのオフセット領域が設けられている。

【0051】

図1(A)に示すFETは適切な材料の基板の上に形成されてもよい。また、その場合、基板は図のゲート105の上の方にあっても、第1の導体電極103aの下の方にあってもよい。

【0052】

通常、このようなオフセット領域はFETに直列に抵抗を挿入した場合と同じ効果をもたらすが、本発明者の考察によれば、そのようなオフセット領域を設けても、dが100nm以下、好ましくは50nm以下、より好ましくは20nm以下であれば、FETの動作に及ぼす影響は軽微であることが明らかとなった。

【0053】

それは、オフセット領域とはいえ、上記に説明したように、第1の導体電極103a、第2の導体電極103bから半導体層102に電子が流入し、電子濃度の高い部分(例えば、領域102c)が存在するためである。FETがNチャネル型の場合、ゲート105に正の電位を与えると図1(B)の領域102eや領域102dのオフセット領域直下にある部分も電子濃度の高い領域となり、第1の導体電極103aと第2の導体電極103bを結ぶ経路が形成される。

【0054】

また、このような構造とすると、ゲート105と第1の導体電極103aあるいは第2の導体電極103bとの間の寄生容量を十分に削減することができる。この効果を享受するには、オフセット領域の幅dは10nm以上であることが好ましい。オフセット領域の幅dが10nm未満では、第1の導体電極103aあるいは第2の導体電極103bとの間の寄生容量が著しく増加する。

【0055】

図1(A)で示されるFETは、第1の導体電極103aと第2の導体電極103bが、ゲート105と異なる面に形成されるが、第1の導体電極103aと第2の導体電極103bが、ゲート105と同じ面に形成されるFETも作製できる。

【0056】

図1(C)に示すFETは、半導体層102上の同じ面に第1の導体電極103aと第2の導体電極103b、ゲート絶縁膜104,ゲート105を有するFETを示す。ゲート105と第1の導体電極103a、ゲート105と第2の導体電極103bの間には、オフセット領域を設ける。

【0057】

半導体層102は、第1の導体電極103aや第2の導体電極103bと接触することにより、電子が供給され、図1(C)に示すように、電子濃度のさまざまな領域が形成される。電子濃度の分布は、第1の導体電極103aと第2の導体電極103bがゲート105と同じ面にあることにより、図1(B)とは若干、異なる。

【0058】

図1(C)の構造では、特に、半導体層102のゲートの反対側の部分において、第1の導体電極103aや第2の導体電極103bの影響力が相対的に低下するため、その部分の電子濃度が、図1(B)の場合よりも低下する。その結果、オフ電流がより少なくなる。

【0059】

このような構造のFETは、従来の珪素のMOSFETと同じような構造であるため、多層配線等のプロセスが、図1(A)の構造のFETよりも簡便にでき、集積度も高められるという利点がある。また、従来のシリコンMOSFETで必要なイオン注入によるドーピングプロセスが不要という特色もある。すなわち、ゲートを設けた部分は自動的に電子濃度の極めて低いチャネルとなり、その他の部分は適度な電子濃度のエクステンション領域に相当する部分となる。

【0060】

また、第1の導体電極103a、第2の導体電極103bから半導体層102に電子が流入し、適度な電子濃度の部分ができるということは、その部分はFETのオン状態とオフ状態の中間の抵抗値であることを意味する。

【0061】

図5に戻って、図5(A)のFETの、ゲート105を取り去ってしまうと、半導体層102のキャリア濃度の分布は、概念的には図5(C)のようになる。この場合には、ゲートによって電子を排除する作用が無くなるため、第1の導体電極103a、第2の導体電極103bから注入された電子により、電子濃度の高い領域が、図5(B)よりも広く形成される。

【0062】

図5(B)はFETのオフ状態であり、また、FETのオン状態では、ゲート105によって、半導体層102の多くの部分により電子濃度の高い領域ができることを考えると、図5(C)は、まさに、オン状態とオフ状態の中間の状態である。

【0063】

このような状態では、その抵抗値(第1の導体電極103aと第2の導体電極103bとの間の抵抗値)も、FETのオン状態とオフ状態の中間となる。抵抗値は、キャリア濃度に反比例するが、図5(A)のFETからゲート105を取り去った構造の素子(以下、抵抗素子、という)の半導体層の抵抗率は、同じ厚さの半導体層を用いるFETのオフ状態の半導体層の抵抗率より3−8桁低い。

【0064】

このような抵抗素子は、上記で説明したように、図6(A)で示されるインバータの抵抗として用いるのに好ましい。特に、第1の導体電極103aと第2の導体電極103bの間隔Lを100nm以上10μm以下とすることで、同じ程度(Lの1/2以上5倍以下)のチャネル長を有するFETのオン抵抗RON、オフ抵抗ROFFの間で、RON<<R<<ROFFの関係を満たすことができる。

【0065】

この際、FETのチャネル幅は抵抗素子の幅の50%以上200%以下、FETの半導体層の厚さは抵抗素子の半導体層の厚さの50%以上200%以下とするとよい。もちろん、それ以外の条件でも上記の関係を満たすことは可能である。

【0066】

なお、上記の説明で、導体の仕事関数について議論した。もっとも簡単な仮定では、導体の仕事関数は半導体との界面で決定される値を用いればよいが、現実には界面は、化学的反応により半導体と導体の化合物が生成されたり、あるいは界面に電荷や異種元素がトラップされたりして複雑な物性を示すことも多い。

【0067】

また、例えば、半導体層に厚さが数nm以下の極めて薄い第1の導体層と、それに重なる、ある程度の厚みのある第2の導体層が積層している場合は、第1の導体層の仕事関数の影響度がかなり低下する。したがって、本発明を適用するに当たっては、界面から5nm離れた部分での各種材料の値が、本発明で好ましいとする条件を満たすように設計してもよい。

【0068】

本発明は、キャリアとして、実質的に、電子あるいはホールの一方しか用いられない半導体材料において効果が顕著である。すなわち、電子あるいはホールの一方の移動度は、1cm2/Vs以上であるのに対し、他方の移動度が0.01cm2/Vs以下であるとか、他方がキャリアとして存在しない、あるいは、他方の有効質量が自由電子の100倍以上である、という場合において好ましい結果が得られる。

【図面の簡単な説明】

【0069】

【図1】本発明の電界効果トランジスタの動作原理を示す図である。

【図2】本発明の半導体回路の例を示す図である。

【図3】本発明の半導体回路の例を示す図である。

【図4】本発明の半導体回路の作製工程の例を示す図である。

【図5】本発明の原理を説明する図である。

【図6】従来のインバータ回路図である。

【発明を実施するための形態】

【0070】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0071】

(実施の形態1)

本実施の形態では、図2に示す半導体回路について説明する。図2(A)は半導体回路の断面の概念図、図2(B)は、図2(A)の下側からこの半導体回路を見た様子を示す。この半導体回路は、図2(A)に示すように、半導体層102の一方の面に接して、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを有する。また、半導体層102の他方の面にはゲート105を有する。ゲート105と半導体層102の間にはゲート絶縁膜104を有する。

【0072】

基板は、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cの下に設けても、ゲート105の上に設けてもよい。また、この半導体回路の、半導体層102は、図2(B)に示すように、概略長方形の形状をし、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cが設けられる。さらに、半導体層102はI型で、バンドギャップが2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【0073】

ゲート105は、半導体層102の第1の導体電極103aと第2の導体電極103bの間の領域(ただし、第1の導体電極103aと第2の導体電極103bは含まない)と重なるように設けられるが、半導体層102の第2の導体電極103bと第3の導体電極103cの間の領域(ただし、第2の導体電極103bと第3の導体電極103cは含まない)とは重ならないように設けられる。

【0074】

このような構造とすることにより、第1の導体電極103aと第2の導体電極103b、ゲート105およびそれらに囲まれた部分の半導体層102によって、FETが形成される。また、第2の導体電極103bと第3の導体電極103cおよびその間の部分の半導体層102によって、抵抗が形成される。

【0075】

すなわち、図2(A)に示すように、前者が、トランジスタ部、後者が抵抗部となり、半導体層102の電子濃度の分布状態は、それぞれ、図5(B)、図5(C)で示されるのとおおよそ同等のものとなる。したがって、図2(C)に回路図で示すように、図6(A)のタイプのインバータとなる。

【0076】

また、図2(B)に示されるように、トランジスタ部のチャネル幅方向の長さと、抵抗部のそれに相当する長さは概略同じとなる。図2に示す構造のインバータが、図6(B)で示されるインバータに比較して、集積度が高いことは以下の理由からも明らかである。

【0077】

例えば、同じように図6(B)のタイプのインバータを形成しようとすれば、第2の導体電極103bと第3の導体電極103cの間にもゲートを設けなければならない。しかし、その場合、ゲート105と隣接するゲートとの絶縁を確実なものとするため、最小加工線幅以上の間隔を設ける必要がある。その分、第2の導体電極103bの幅を広くする必要がある。

【0078】

図2において、最小加工線幅は、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cの幅である。ということは、図6(B)のタイプのインバータにおいて、第2の導体電極103bは図2の2倍の幅を必要とするということである。これに対し、図6(A)のタイプのインバータでは、第2の導体電極103bと第3の導体電極103cの間にゲートを設ける必要がないので、第2の導体電極103bの幅を最小線幅とすることができる。

【0079】

図2のような半導体装置を作製するには、基板上に、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成し、その後、半導体層102,ゲート絶縁膜104,ゲート105を形成すればよい。

【0080】

あるいは、基板上に、ゲート105を形成し、その後、ゲート絶縁膜104、半導体層102、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成すればよい。

【0081】

なお、図2においては、第1の導体電極103aと第2の導体電極103bの間隔、第2の導体電極103bと第3の導体電極103cの間隔を概略等しくしたが、前者を後者よりも広く、あるいは狭くしてもよい。

【0082】

(実施の形態2)

本実施の形態では、図3に示す半導体回路について説明する。図3(A)は半導体回路の断面の概念図、図3(B)は、図3(A)の下側から、この半導体回路を見た様子を示す。図3(A)に示すように、この半導体回路も図2の半導体装置と同様に、半導体層102の一方の面に接して、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを有する。また、半導体層102の他方の面にはゲート105を有する。ゲート105と半導体層102の間にはゲート絶縁膜104を有する。半導体層102はI型で、バンドギャップが2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【0083】

また、ゲート105は、半導体層102の第1の導体電極103aと第2の導体電極103bの間の領域A(ただし、第1の導体電極103aと第2の導体電極103bは含まない)の少なくとも1部分と重なるように設けられるが、半導体層102の第2の導体電極103bと第3の導体電極103cの間の領域B(ただし、第2の導体電極103bと第3の導体電極103cは含まない)とは重ならないように設けられる。

【0084】

図2の半導体装置と異なるのは、ゲート105が第1の導体電極103a、第2の導体電極103bと重ならず、オフセット領域を有することである。すなわち、ゲート105と第1の導体電極103a、第2の導体電極103bの間には長さdのオフセット領域を有する。

【0085】

また、この半導体回路の、半導体層102は、図3(B)に示すように、複雑な形状をしている。すなわち、左側の部分(領域Aを含む部分)の幅を広く、右側の部分(領域Bを含む部分)の幅を狭くする。こうすることにより、右側の部分の抵抗を高くして、左側の部分の抵抗との比率を調整する。

【0086】

この半導体装置でも、実施の形態1と同様に、第1の導体電極103aと第2の導体電極103b、ゲート105およびそれらに囲まれた部分の半導体層102によって、図1(A)に示されるのと同等なFETが形成される。また、第2の導体電極103bと第3の導体電極103cおよびその間の部分の半導体層102によって、図5(C)に示されるのと同等な抵抗が形成される。

【0087】

すなわち、図3(A)に示すように、前者が、トランジスタ部、後者が抵抗部となり、半導体層102の電子濃度の分布状態は、それぞれ、図1(B)、図5(C)で示されるのとおおよそ同等のものとなる。回路図は図3(C)に示される。すなわち、図6(A)に示されるインバータとして用いることができる。この半導体装置の抵抗部の抵抗は、実施の形態1のものに比較して大きなものとなる。

【0088】

また、本実施の形態のインバータはトランジスタの入力がローのときの抵抗を高くできるので、消費電力をより低くできる。また、同じ理由から、貫通電流による素子破壊も防止でき、信頼性を高めることができる。

【0089】

ところで、本実施の形態で示すようなオフセット領域を有するFETであれば、図6(B)のタイプのインバータを形成する上で、実施の形態1で指摘した集積度の低下は克服できる。すなわち、オフセットがあるため、ゲート間の間隔は最小線幅より広い。すなわち、第2の導体電極103bを最小線幅で形成しても、ゲート105に隣接するゲートを第2の導体電極103bと第3の導体電極103cの間に設けることができる。

【0090】

しかしながら、先に示したような、ゲートと導体電極とのコンタクトを設ける必要があるため、図6(A)のタイプに比較すると集積度は低下する。

【0091】

(実施の形態3)

本実施の形態では、半導体装置の作製方法について、図4を用いて説明する。まず、図4(A)に示すように、基板101上に、半導体層102、ゲート絶縁膜104を形成する。基板101としては、様々なものが用いられるが、その後の処理に耐えられる物性を有していることが必要である。また、その表面は絶縁性であることが好ましい。すなわち、基板101は絶縁体単独、あるいは絶縁体や金属や半導体の表面に絶縁層を形成したもの等であることが好ましい。

【0092】

基板101に絶縁体を用いる場合には、各種ガラスやサファイヤ、石英、セラミックス等を用いることができる。金属を用いる場合には、アルミニウム、銅、ステンレス鋼、銀等を用いることができる。半導体を用いる場合には、珪素、ゲルマニウム、炭化珪素、窒化ガリウム等を用いることができる。本実施の形態では、基板101としてバリウム硼珪酸ガラスを用いる。

【0093】

半導体層102の半導体材料としては、インジウムと亜鉛を有する酸化物半導体を用いる。酸化物半導体としては、上記以外にも各種のものが用いられる。本実施の形態では、インジウムと亜鉛が等しく含まれる酸化物ターゲットを用いたスパッタリング法によって、厚さ30nmのインジウム亜鉛酸化物膜を形成し、これをパターニングして半導体層102に用いる。

【0094】

ゲート絶縁膜104としては、スパッタリング法により形成した絶縁膜を用いる。絶縁膜の材料としては、酸化珪素、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ランタン、酸化イットリウム等を用いることができる。本実施の形態では、ゲート絶縁膜104として、スパッタリング法により形成した厚さ100nmの酸化アルミニウムを用いる。

【0095】

半導体層102を形成後、あるいは、ゲート絶縁膜104を形成後のいずれか一方、もしくは双方で、適切な熱処理をおこなうとよい。これは、半導体層102中の水素濃度や酸素欠損を低減させるためであり、可能であれば、半導体層102形成直後におこなうとよい。

【0096】

その際、最初に還元雰囲気で熱処理をおこなった後、酸化雰囲気で熱処理をおこなうとよい。最初の還元雰囲気での熱処理により、水素が酸素と共に効率よく放出され、その後の酸化雰囲気での熱処理により、酸素欠陥を埋めることができる。

【0097】

その後、図4(B)に示すようにゲート105を形成する。ゲート105の材料としては、白金、金、タングステン等の仕事関数の大きな金属を用いることができる。あるいは窒化インジウムのように電子親和力が5電子ボルト以上の化合物を用いてもよい。ゲート105はそのような材料単独で構成してもよいし、多層構造とし、ゲート絶縁膜104に接する部分を、上記の材料で構成してもよい。本実施の形態では、厚さ100nmの白金膜と厚さ100nmのアルミニウム膜をスパッタリング法で形成し、これをエッチングして、ゲート105を形成する。

【0098】

さらに、スパッタリング法により、層間絶縁物106を形成する。層間絶縁物106としては、誘電率の低い材料を用いることが好ましい。本実施の形態では、層間絶縁物106として、CVD法により形成した厚さ300nmの酸化珪素を用いる。そして、図4(C)に示すように、層間絶縁物106を化学的機械的研磨(CMP)法により平坦化する。

【0099】

さらに半導体層102に達するコンタクトホールを形成し、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成する。本実施の形態では、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cは、厚さ50nmの窒化チタン膜と厚さ150nmのチタン膜を、スパッタリング法で連続的に形成して、これをパターニングして形成する。このようにして、図4(D)に示される半導体回路が形成される。

【0100】

半導体層102のうち、ゲート105の設けられた図の左側の部分は、FETの活性層として機能し、ゲート105の設けられていない図の右側の部分は抵抗として機能する。この回路も図6(A)に示したインバータとして用いることができる。

【0101】

(実施の形態4)

上記実施の形態1乃至3で示した半導体装置は、さまざまな電子機器に用いることができる。例えば、液晶ディスプレー、EL(Electro Luminescence)ディスプレー、FE(Field Emission)ディスプレー等の表示装置の駆動回路、イメージセンサの駆動回路、半導体メモリ等である。また、それらを用いた各種電子機器、例えば、テレビジョン、パーソナルコンピュータ、携帯電話等の通信機器、電子手帳、携帯音楽プレーヤ等である。

【符号の説明】

【0102】

101 基板

102 半導体層

103a 第1の導体電極

103b 第2の導体電極

103c 第3の導体電極

104 ゲート絶縁膜

105 ゲート

106 層間絶縁物

【技術分野】

【0001】

本発明は、半導体を用いた電界効果トランジスタ(FET)および電界効果トランジスタを用いた半導体装置に関する。

【背景技術】

【0002】

電界効果トランジスタ(FET)とは、半導体にソース、ドレインという領域を設け、それぞれに電極を設けて、電位を与え、絶縁膜あるいはショットキーバリヤを介してゲートと呼ばれる電極より半導体に電界をかけ、半導体の状態を制御することにより、ソースとドレイン間に流れる電流を制御するものである。用いられる半導体としては、珪素やゲルマニウム等のIV族元素(第14族元素)やガリウムヒ素、インジウムリン、窒化ガリウム等のIII−V族化合物、硫化亜鉛、カドミウムテルル等のII−VI族化合物等が挙げられる。

【0003】

近年、酸化亜鉛や酸化インジウムガリウム亜鉛系化合物等の酸化物を半導体として用いたFETが報告された(特許文献1および特許文献2)。これらの酸化物半導体を用いたFETでは、比較的大きな移動度が得られると共に、それらの材料が3電子ボルト以上の大きなバンドギャップを有するが故に、酸化物半導体を用いたFETをディスプレーやパワーデバイス等に応用することが議論されている。

【0004】

例えば、バンドギャップが3電子ボルト以上ということは、可視光に対して透明であるので、ディスプレー用途として用いた場合、FET部分も光を透過でき、開口率が向上することが期待される。

【0005】

また、このような大きなバンドギャップという特徴は、パワーデバイスに用いられる炭化珪素と同じなので、同様にパワーデバイスに用いることが期待される。

【0006】

さらに、バンドギャップが大きいということは、熱励起キャリアが少ないことを意味する。例えば、室温において、珪素では、バンドギャップが1.1電子ボルトであるので、熱励起キャリアは1011/cm3程度であるが、バンドギャップが3.2電子ボルトの半導体では、熱励起キャリアは10−7/cm3程度と計算される。

【0007】

珪素の場合、全く、不純物を含まないものを作っても、熱励起によるキャリアが上記のように存在するため、抵抗率は、105Ωcm以上とできないが、バンドギャップが3.2電子ボルトの半導体では、理論的には、1020Ωcm以上の抵抗率が得られる。このような半導体でFETを作製し、オフ状態(ゲートの電位がソースの電位と同じ状態)における高い抵抗率を用いれば、電荷を半永久的に閉じこめることも可能となると期待される。

【0008】

ところで、特に亜鉛もしくはインジウムを有する酸化物半導体においては、これまで、P型の導電性を示すものはほとんど報告されていない。そのため、珪素のFETのようなPN接合を用いたものは報告されておらず、特許文献1および特許文献2にあるように、N型の酸化物半導体に導体電極を接触させた導体半導体接合によって、ソース、ドレインを形成していた。

【0009】

なお、一般的な半導体関連の学術書においては、「導体半導体接合」は「金属半導体接合」と表記される。この場合、金属とは、導体という意味である。例えば、高濃度にドーピングされ、抵抗率が著しく低下した半導体、あるいは、窒化チタン、窒化タングステン等の金属窒化物、酸化インジウム錫、酸化アルミニウム亜鉛等の金属酸化物等も「金属半導体接合」では金属として扱われる。しかしながら、一般に「金属」という用語では誤解を招きやすい。そのため、本明細書では「金属半導体接合」ではなく「導体半導体接合」と表記する。

【0010】

例えば、特許文献1には図5(A)に示すようなFETが開示されている。すなわち、半導体層102の一方の面に接してソース電極と呼ばれる第1の導体電極103aとドレイン電極と呼ばれる第2の導体電極103bが設けられ、半導体層102の他方の面には、間にゲート絶縁膜104を介して、ゲート105が設けられている。第1の導体電極103aと第2の導体電極103b、ゲート105は導体が用いられる。

【0011】

そして、図5(A)に幅cで示すように、ゲート105と第1の導体電極103a、およびゲート105と第2の導体電極103bは重なる部分を有することが必須とされた。すなわち、c>0であることが必要とされてきた。

【0012】

また、導体半導体接合によって、ソース電極、ドレイン電極を形成したFETでは、用いる半導体のキャリア濃度が大きいと、オフ状態でもソース電極とドレイン電極の間に電流(オフ電流)が流れてしまう。そこで、半導体中のドナーあるいはアクセプタの濃度を低減させて、I型(本明細書では、ドナーあるいはアクセプタに由来するキャリア濃度が1012/cm3以下の半導体をI型という)とすることにより、オフ電流を低減することが望まれる。

【0013】

なお、本明細書ではドナー(あるいはアクセプタ)の濃度とは、ドナー(あるいはアクセプタ)となりうる元素や化学基等の濃度に、そのイオン化率を乗じたものを言う。例えば、あるドナー元素が2%含まれていても、そのイオン化率が0.005%であれば、ドナー濃度は1ppm(=0.02×0.00005)である。

【0014】

ところで、FETを用いた半導体回路で、特にP型とN型のFETのいずれか一方しか用いることができない半導体回路では、基本回路のひとつであるインバータは、例えば、図6(A)に示すように、FETに抵抗を直列に接続したものを用いる。

【0015】

あるいは、図6(B)に示すように、FETを2つ直列に接続し、一方(通常は、VH側)のFETのドレインとゲートを短絡させて、ダイオードとしたものを用いることもある。しかしながら、図6(B)の形態のインバータは、FETのドレインとゲートを短絡させるに際し、図中にXで示す部分でコンタクトを形成する必要から集積度を上げられないという点で不利である。

【0016】

図6(A)のタイプのインバータにおいては、FETのオン時の抵抗をRON、オフ時ROFFとするとき、RON<<R<<ROFFとなるような、抵抗値Rを有する抵抗をFETに接続する。ここで、R>10RON、R<ROFF/10、好ましくは、R>100RON、R<ROFF/100とすることが望まれる。

【0017】

このタイプのインバータでは、入力がハイであれば、この抵抗とオン状態となっているFETを通って電流が流れる。インバータのVHとVLの間の抵抗は、R+RONであるが、R>>RONであれば、インバータの抵抗はRと近似できる。したがって、インバータの電源電圧をVddとすれば、消費電力は、Vdd2/R、となる。また、出力電圧は0と近似できる。

【0018】

また、入力がローでも、この抵抗とFETを通って電流が流れる。インバータの抵抗は、R+ROFFであるが、R<<ROFFであれば、インバータの抵抗はROFFと近似できる。したがって、インバータの消費電力は、Vdd2/ROFF、となる。また、出力電圧はVddと近似できる。

【0019】

上記の関係から明らかなように、RおよびROFFが大きな値であれば消費電力は抑制される。また、出力電圧は、RがRONとROFFの中間の値であることが望まれ、理想的には、R=(RON×ROFF)1/2であるとよい。また、それらの結果として、ROFF/RONが大きな値であることが望まれる。

【0020】

従来の半導体回路で、このようにP型とN型のFETのいずれか一方しか用いることができない半導体回路としては、アモルファスシリコンFETを用いた回路が知られている。

【0021】

アモルファスシリコンFETを用いたインバータ回路では、抵抗として、N型のアモルファスシリコンを用いている。N型のアモルファスシリコンは、FETのソースやドレインの材料として用いられるものであり、その一部を加工して抵抗として使うものである。N型のアモルファスシリコンの抵抗率はあまり高くはないため、抵抗の大きさはFETの大きさよりも大きくなる。

【0022】

ところで、バンドギャップが2電子ボルト以上のI型の半導体を用いてキャリア濃度を低減させたFETは、極めてオフ電流が低い、すなわち、ROFFが極めて大きく、また、移動度もアモルファスシリコンに比べればはるかに大きいため、RONも小さく、すなわち、ROFF/RONが1010以上もの大きな値となる。これだけ大きいと抵抗を形成する上で、あるいは設計する上でのマージンも大きくなる。

【0023】

しかしながら、特許文献1あるいは特許文献2のように、半導体に直接、導体を接触させて形成されるFETでは、アモルファスシリコンのFETの場合のような、抵抗とするのに適当な材料は見あたらなかった。特に、半導体のキャリア濃度を低減し、I型とした場合は、その抵抗率は極めて大きいものと考えられていたため、それを抵抗に用いることは想定されていなかった。

【先行技術文献】

【特許文献】

【0024】

【特許文献1】米国特許公開2005/0199879号公報

【特許文献2】米国特許公開2007/0194379号公報

【発明の概要】

【発明が解決しようとする課題】

【0025】

本発明は、上記に説明したような導体半導体接合を有するFETの回路設計を工夫することより優れたFETあるいは半導体装置、半導体回路、あるいはそれらの作製方法を提供することを課題とする。また、導体半導体接合の特性を生かして、優れた特性を示すFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。あるいは、作製の簡単なFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。あるいは、より集積度の高いFETあるいは半導体装置、あるいはそれらの作製方法を提供することを課題とする。本発明は上記課題の少なくとも1つを解決する。

【課題を解決するための手段】

【0026】

以下、本発明の説明をおこなうが、本明細書で用いる用語について簡単に説明する。まず、トランジスタのソースとドレインについては、本明細書においては、Nチャネル型FETにおいては、高い電位が与えられる方をドレイン、他方をソースとし、Pチャネル型FETにおいては、低い電位が与えられる方をドレイン、他方をソースとする。いずれの電位も同じであれば、いずれか一方をソース、他方をドレインとする。

【0027】

また、ソース電極、ドレイン電極という用語のかわりに第1の導体電極、第2の導体電極とも表現することがある。その場合は、電位の高低によって呼び名を変えない。

【0028】

本発明の第1は、半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有するFETである。

【0029】

本発明の第2は、半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、同じ面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有するFETである。

【0030】

上記の本発明の第1および第2においては、オフセット領域の幅は、10nm以上100nm以下、好ましくは、10nm以上50nm以下、より好ましくは、10nm以上20nm以下とするとよい。また、半導体層の厚さは、オフセット領域の幅以下、好ましくは、オフセット領域の幅の半分以下とするとよい。また、ゲートの幅は、オフセット領域の幅と同じもしくは大きくするとよい。

【0031】

本発明の第3は、半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、半導体層の他方の面に設けられたゲートとを有する半導体装置である。

【0032】

本発明の第4は、半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、同じ面に設けられたゲートとを有する半導体装置である。

【0033】

上記本発明の第1乃至第4において、第1乃至第3の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和(すなわち、電子親和力+0.3電子ボルト)よりも小さい、あるいは、第1および第2の導体電極と半導体層はオーミック接合であることが好ましい。

【0034】

上記本発明の第1乃至第4において、ゲートの、半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和(すなわち、電子親和力+0.6電子ボルト)よりも大きいことが好ましい。また、半導体層はI型であることが好ましい。

【0035】

上記本発明の第1乃至第4において、FETあるいは半導体回路は、適切な基板上に設けられてもよい。その際、ゲートと基板の間に半導体層を設けるか、あるいは、半導体層と基板の間にゲートを設けるとよい。

【0036】

基板に用いられる材料としては、単結晶シリコン等の半導体、各種ガラス、石英、サファイヤ、各種セラミックス等の絶縁体、アルミニウム、ステンレス鋼、銅等の導体等が挙げられる。特に半導体や導体を基板として用いるに際しては、その表面に絶縁層を設けることが好ましい。

【0037】

さらに、半導体層とゲートとの間にはゲート絶縁膜を設けてもよい。あるいは、半導体層とゲートとの間をショットキーバリヤ型接合してもよい。また、第1乃至第3の導体電極は同じ材料で構成される必要はない。すべて異なる材料で形成してもよいし、そのうちの2つを同じ材料で構成してもよい。

【0038】

なお、半導体層の種類は、酸化物に限らず、硫化物等のII−VI族化合物でもよい。また、上述のように熱励起によるキャリアを減らすためにも、半導体のバンドギャップは2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【発明の効果】

【0039】

上記の構成のいずれかを採用することにより、前記課題の少なくとも1つを解決できる。本発明は、導体半導体接合の性質を利用して、適度な抵抗領域を形成し、それを、FETのオフセット領域や半導体回路あるいは半導体装置に利用するものである。

【0040】

特許文献1あるいは特許文献2にあるようなFETにおいては、ソース電極、ドレイン電極、ゲートに導体が使用されていたが、導体による半導体への影響については、これまで、十分に考察されてこなかった。

【0041】

この点に関して、本発明者の考察によれば、導体半導体接合において、導体の仕事関数が、半導体層の電子親和力より小さな場合には、半導体層中に電子が流入し、そのためオーミック接合が形成されることが明らかとなった。

【0042】

FETにおいて、ソース電極と半導体あるいはドレイン電極と半導体との接合は、電流が流れやすいことが好ましいので、オーミック接合となるようにソース電極あるいはドレイン電極の材料が選択される。例えば、チタンや窒化チタン等である。電極と半導体との接合がオーミック接合であると、得られるFETの特性が安定し、良品率が高くなるというメリットもある。

【0043】

そのような導体半導体接合において、導体に近いほど電子の濃度が高く、大雑把な計算では、電子濃度は、導体半導体接合界面から数nmでは1020/cm3、数十nmでは1018/cm3、数百nmでは1016/cm3、数μmでも1014/cm3である。すなわち、半導体自体がI型であっても、導体との接触によって、キャリア濃度の高い領域ができてしまう。このようなキャリアの多い領域が導体半導体接合界面近傍にできることにより、導体半導体接合はオーミック接合となる。

【0044】

また、ゲートの材料としては、仕事関数が半導体層の電子親和力より大きな導体を用いれば、半導体の電子を排除する作用を有することも明らかとなった。例えば、タングステンや白金等である。このような材料を用いることによって、オフ電流を極めて小さくすることができることが解明できた。

【0045】

上記の考察によれば、図5(A)に示されるFETの半導体層102における、第1の導体電極103a、第2の導体電極103b、ゲート105を同電位とした場合での、キャリア濃度の分布は、概念的には図5(B)のように示される。ここで、第1の導体電極103a、第2の導体電極103bの仕事関数をWm、ゲート105の仕事関数をWg、半導体層102の電子親和力をφ、としたとき、Wm<φ+0.3電子ボルト、Wg>φ+0.6電子ボルトという条件を満たすものとする。

【0046】

図5(B)に示されるように、第1の導体電極103a、第2の導体電極103bから電子が注入されることにより、第1の導体電極103a、第2の導体電極103bの近傍は、極めて電子濃度の高い領域102aとなる。一方で、ゲート105に近い部分では、電子濃度が極めて低い領域102eとなる。その間の部分では、電子濃度は、第1の導体電極103a、第2の導体電極103bから離れるほど、あるいは、ゲート105に近づくほど低くなる。

【0047】

図5(B)では、領域102bの電子濃度は、領域102aより電子濃度が1桁程度低く、領域102cの電子濃度は、領域102bより電子濃度が1桁程度低く、領域102dの電子濃度は、領域102cより電子濃度が1桁程度低いことを示している。電子濃度が高いほど導電性が高まり、逆に、電子濃度が低くなると、導電性が低下し、例えば、領域102eでは絶縁体となる。

【0048】

図5(B)で示されるFETのオフ電流は、第1の導体電極103a、第2の導体電極103bの中間部分に形成される領域102eによって決定される。一方、第1の導体電極103aとゲート105、第2の導体電極103bとゲート105の重なる部分やその周辺は、オフ電流を下げる上ではほとんど関係がないことが明らかとなった。

【0049】

なお、図5(A)に示されるFETの、第1の導体電極103aと第2の導体電極103bの間隔をさらに狭めると、領域102eが狭まり、それよりも電子濃度の高い領域が多くなってしまう。こうなると、オフ電流が増大するため好ましくない。すなわち、第1の導体電極103aと第2の導体電極103bの間隔は、オフ電流を一定の値以下とするために、ある値を保つ必要がある。

【0050】

本発明者は、図5(B)に示されるような電子濃度分布は、図5(A)以外の、例えば、図1(A)のような構造でも得られることに気がついた。図1(A)の構造のFETでは、第1の導体電極103aとゲート105、あるいは、第2の導体電極103bとゲート105が重ならないように設けられ、図1(A)では、第1の導体電極103aとゲート105の間に、幅dのオフセット領域が設けられている。

【0051】

図1(A)に示すFETは適切な材料の基板の上に形成されてもよい。また、その場合、基板は図のゲート105の上の方にあっても、第1の導体電極103aの下の方にあってもよい。

【0052】

通常、このようなオフセット領域はFETに直列に抵抗を挿入した場合と同じ効果をもたらすが、本発明者の考察によれば、そのようなオフセット領域を設けても、dが100nm以下、好ましくは50nm以下、より好ましくは20nm以下であれば、FETの動作に及ぼす影響は軽微であることが明らかとなった。

【0053】

それは、オフセット領域とはいえ、上記に説明したように、第1の導体電極103a、第2の導体電極103bから半導体層102に電子が流入し、電子濃度の高い部分(例えば、領域102c)が存在するためである。FETがNチャネル型の場合、ゲート105に正の電位を与えると図1(B)の領域102eや領域102dのオフセット領域直下にある部分も電子濃度の高い領域となり、第1の導体電極103aと第2の導体電極103bを結ぶ経路が形成される。

【0054】

また、このような構造とすると、ゲート105と第1の導体電極103aあるいは第2の導体電極103bとの間の寄生容量を十分に削減することができる。この効果を享受するには、オフセット領域の幅dは10nm以上であることが好ましい。オフセット領域の幅dが10nm未満では、第1の導体電極103aあるいは第2の導体電極103bとの間の寄生容量が著しく増加する。

【0055】

図1(A)で示されるFETは、第1の導体電極103aと第2の導体電極103bが、ゲート105と異なる面に形成されるが、第1の導体電極103aと第2の導体電極103bが、ゲート105と同じ面に形成されるFETも作製できる。

【0056】

図1(C)に示すFETは、半導体層102上の同じ面に第1の導体電極103aと第2の導体電極103b、ゲート絶縁膜104,ゲート105を有するFETを示す。ゲート105と第1の導体電極103a、ゲート105と第2の導体電極103bの間には、オフセット領域を設ける。

【0057】

半導体層102は、第1の導体電極103aや第2の導体電極103bと接触することにより、電子が供給され、図1(C)に示すように、電子濃度のさまざまな領域が形成される。電子濃度の分布は、第1の導体電極103aと第2の導体電極103bがゲート105と同じ面にあることにより、図1(B)とは若干、異なる。

【0058】

図1(C)の構造では、特に、半導体層102のゲートの反対側の部分において、第1の導体電極103aや第2の導体電極103bの影響力が相対的に低下するため、その部分の電子濃度が、図1(B)の場合よりも低下する。その結果、オフ電流がより少なくなる。

【0059】

このような構造のFETは、従来の珪素のMOSFETと同じような構造であるため、多層配線等のプロセスが、図1(A)の構造のFETよりも簡便にでき、集積度も高められるという利点がある。また、従来のシリコンMOSFETで必要なイオン注入によるドーピングプロセスが不要という特色もある。すなわち、ゲートを設けた部分は自動的に電子濃度の極めて低いチャネルとなり、その他の部分は適度な電子濃度のエクステンション領域に相当する部分となる。

【0060】

また、第1の導体電極103a、第2の導体電極103bから半導体層102に電子が流入し、適度な電子濃度の部分ができるということは、その部分はFETのオン状態とオフ状態の中間の抵抗値であることを意味する。

【0061】

図5に戻って、図5(A)のFETの、ゲート105を取り去ってしまうと、半導体層102のキャリア濃度の分布は、概念的には図5(C)のようになる。この場合には、ゲートによって電子を排除する作用が無くなるため、第1の導体電極103a、第2の導体電極103bから注入された電子により、電子濃度の高い領域が、図5(B)よりも広く形成される。

【0062】

図5(B)はFETのオフ状態であり、また、FETのオン状態では、ゲート105によって、半導体層102の多くの部分により電子濃度の高い領域ができることを考えると、図5(C)は、まさに、オン状態とオフ状態の中間の状態である。

【0063】

このような状態では、その抵抗値(第1の導体電極103aと第2の導体電極103bとの間の抵抗値)も、FETのオン状態とオフ状態の中間となる。抵抗値は、キャリア濃度に反比例するが、図5(A)のFETからゲート105を取り去った構造の素子(以下、抵抗素子、という)の半導体層の抵抗率は、同じ厚さの半導体層を用いるFETのオフ状態の半導体層の抵抗率より3−8桁低い。

【0064】

このような抵抗素子は、上記で説明したように、図6(A)で示されるインバータの抵抗として用いるのに好ましい。特に、第1の導体電極103aと第2の導体電極103bの間隔Lを100nm以上10μm以下とすることで、同じ程度(Lの1/2以上5倍以下)のチャネル長を有するFETのオン抵抗RON、オフ抵抗ROFFの間で、RON<<R<<ROFFの関係を満たすことができる。

【0065】

この際、FETのチャネル幅は抵抗素子の幅の50%以上200%以下、FETの半導体層の厚さは抵抗素子の半導体層の厚さの50%以上200%以下とするとよい。もちろん、それ以外の条件でも上記の関係を満たすことは可能である。

【0066】

なお、上記の説明で、導体の仕事関数について議論した。もっとも簡単な仮定では、導体の仕事関数は半導体との界面で決定される値を用いればよいが、現実には界面は、化学的反応により半導体と導体の化合物が生成されたり、あるいは界面に電荷や異種元素がトラップされたりして複雑な物性を示すことも多い。

【0067】

また、例えば、半導体層に厚さが数nm以下の極めて薄い第1の導体層と、それに重なる、ある程度の厚みのある第2の導体層が積層している場合は、第1の導体層の仕事関数の影響度がかなり低下する。したがって、本発明を適用するに当たっては、界面から5nm離れた部分での各種材料の値が、本発明で好ましいとする条件を満たすように設計してもよい。

【0068】

本発明は、キャリアとして、実質的に、電子あるいはホールの一方しか用いられない半導体材料において効果が顕著である。すなわち、電子あるいはホールの一方の移動度は、1cm2/Vs以上であるのに対し、他方の移動度が0.01cm2/Vs以下であるとか、他方がキャリアとして存在しない、あるいは、他方の有効質量が自由電子の100倍以上である、という場合において好ましい結果が得られる。

【図面の簡単な説明】

【0069】

【図1】本発明の電界効果トランジスタの動作原理を示す図である。

【図2】本発明の半導体回路の例を示す図である。

【図3】本発明の半導体回路の例を示す図である。

【図4】本発明の半導体回路の作製工程の例を示す図である。

【図5】本発明の原理を説明する図である。

【図6】従来のインバータ回路図である。

【発明を実施するための形態】

【0070】

以下、実施の形態について図面を参照しながら説明する。但し、実施の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

【0071】

(実施の形態1)

本実施の形態では、図2に示す半導体回路について説明する。図2(A)は半導体回路の断面の概念図、図2(B)は、図2(A)の下側からこの半導体回路を見た様子を示す。この半導体回路は、図2(A)に示すように、半導体層102の一方の面に接して、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを有する。また、半導体層102の他方の面にはゲート105を有する。ゲート105と半導体層102の間にはゲート絶縁膜104を有する。

【0072】

基板は、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cの下に設けても、ゲート105の上に設けてもよい。また、この半導体回路の、半導体層102は、図2(B)に示すように、概略長方形の形状をし、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cが設けられる。さらに、半導体層102はI型で、バンドギャップが2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【0073】

ゲート105は、半導体層102の第1の導体電極103aと第2の導体電極103bの間の領域(ただし、第1の導体電極103aと第2の導体電極103bは含まない)と重なるように設けられるが、半導体層102の第2の導体電極103bと第3の導体電極103cの間の領域(ただし、第2の導体電極103bと第3の導体電極103cは含まない)とは重ならないように設けられる。

【0074】

このような構造とすることにより、第1の導体電極103aと第2の導体電極103b、ゲート105およびそれらに囲まれた部分の半導体層102によって、FETが形成される。また、第2の導体電極103bと第3の導体電極103cおよびその間の部分の半導体層102によって、抵抗が形成される。

【0075】

すなわち、図2(A)に示すように、前者が、トランジスタ部、後者が抵抗部となり、半導体層102の電子濃度の分布状態は、それぞれ、図5(B)、図5(C)で示されるのとおおよそ同等のものとなる。したがって、図2(C)に回路図で示すように、図6(A)のタイプのインバータとなる。

【0076】

また、図2(B)に示されるように、トランジスタ部のチャネル幅方向の長さと、抵抗部のそれに相当する長さは概略同じとなる。図2に示す構造のインバータが、図6(B)で示されるインバータに比較して、集積度が高いことは以下の理由からも明らかである。

【0077】

例えば、同じように図6(B)のタイプのインバータを形成しようとすれば、第2の導体電極103bと第3の導体電極103cの間にもゲートを設けなければならない。しかし、その場合、ゲート105と隣接するゲートとの絶縁を確実なものとするため、最小加工線幅以上の間隔を設ける必要がある。その分、第2の導体電極103bの幅を広くする必要がある。

【0078】

図2において、最小加工線幅は、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cの幅である。ということは、図6(B)のタイプのインバータにおいて、第2の導体電極103bは図2の2倍の幅を必要とするということである。これに対し、図6(A)のタイプのインバータでは、第2の導体電極103bと第3の導体電極103cの間にゲートを設ける必要がないので、第2の導体電極103bの幅を最小線幅とすることができる。

【0079】

図2のような半導体装置を作製するには、基板上に、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成し、その後、半導体層102,ゲート絶縁膜104,ゲート105を形成すればよい。

【0080】

あるいは、基板上に、ゲート105を形成し、その後、ゲート絶縁膜104、半導体層102、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成すればよい。

【0081】

なお、図2においては、第1の導体電極103aと第2の導体電極103bの間隔、第2の導体電極103bと第3の導体電極103cの間隔を概略等しくしたが、前者を後者よりも広く、あるいは狭くしてもよい。

【0082】

(実施の形態2)

本実施の形態では、図3に示す半導体回路について説明する。図3(A)は半導体回路の断面の概念図、図3(B)は、図3(A)の下側から、この半導体回路を見た様子を示す。図3(A)に示すように、この半導体回路も図2の半導体装置と同様に、半導体層102の一方の面に接して、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを有する。また、半導体層102の他方の面にはゲート105を有する。ゲート105と半導体層102の間にはゲート絶縁膜104を有する。半導体層102はI型で、バンドギャップが2電子ボルト以上4電子ボルト未満、好ましくは、2.9電子ボルト以上3.5電子ボルト未満とするとよい。

【0083】

また、ゲート105は、半導体層102の第1の導体電極103aと第2の導体電極103bの間の領域A(ただし、第1の導体電極103aと第2の導体電極103bは含まない)の少なくとも1部分と重なるように設けられるが、半導体層102の第2の導体電極103bと第3の導体電極103cの間の領域B(ただし、第2の導体電極103bと第3の導体電極103cは含まない)とは重ならないように設けられる。

【0084】

図2の半導体装置と異なるのは、ゲート105が第1の導体電極103a、第2の導体電極103bと重ならず、オフセット領域を有することである。すなわち、ゲート105と第1の導体電極103a、第2の導体電極103bの間には長さdのオフセット領域を有する。

【0085】

また、この半導体回路の、半導体層102は、図3(B)に示すように、複雑な形状をしている。すなわち、左側の部分(領域Aを含む部分)の幅を広く、右側の部分(領域Bを含む部分)の幅を狭くする。こうすることにより、右側の部分の抵抗を高くして、左側の部分の抵抗との比率を調整する。

【0086】

この半導体装置でも、実施の形態1と同様に、第1の導体電極103aと第2の導体電極103b、ゲート105およびそれらに囲まれた部分の半導体層102によって、図1(A)に示されるのと同等なFETが形成される。また、第2の導体電極103bと第3の導体電極103cおよびその間の部分の半導体層102によって、図5(C)に示されるのと同等な抵抗が形成される。

【0087】

すなわち、図3(A)に示すように、前者が、トランジスタ部、後者が抵抗部となり、半導体層102の電子濃度の分布状態は、それぞれ、図1(B)、図5(C)で示されるのとおおよそ同等のものとなる。回路図は図3(C)に示される。すなわち、図6(A)に示されるインバータとして用いることができる。この半導体装置の抵抗部の抵抗は、実施の形態1のものに比較して大きなものとなる。

【0088】

また、本実施の形態のインバータはトランジスタの入力がローのときの抵抗を高くできるので、消費電力をより低くできる。また、同じ理由から、貫通電流による素子破壊も防止でき、信頼性を高めることができる。

【0089】

ところで、本実施の形態で示すようなオフセット領域を有するFETであれば、図6(B)のタイプのインバータを形成する上で、実施の形態1で指摘した集積度の低下は克服できる。すなわち、オフセットがあるため、ゲート間の間隔は最小線幅より広い。すなわち、第2の導体電極103bを最小線幅で形成しても、ゲート105に隣接するゲートを第2の導体電極103bと第3の導体電極103cの間に設けることができる。

【0090】

しかしながら、先に示したような、ゲートと導体電極とのコンタクトを設ける必要があるため、図6(A)のタイプに比較すると集積度は低下する。

【0091】

(実施の形態3)

本実施の形態では、半導体装置の作製方法について、図4を用いて説明する。まず、図4(A)に示すように、基板101上に、半導体層102、ゲート絶縁膜104を形成する。基板101としては、様々なものが用いられるが、その後の処理に耐えられる物性を有していることが必要である。また、その表面は絶縁性であることが好ましい。すなわち、基板101は絶縁体単独、あるいは絶縁体や金属や半導体の表面に絶縁層を形成したもの等であることが好ましい。

【0092】

基板101に絶縁体を用いる場合には、各種ガラスやサファイヤ、石英、セラミックス等を用いることができる。金属を用いる場合には、アルミニウム、銅、ステンレス鋼、銀等を用いることができる。半導体を用いる場合には、珪素、ゲルマニウム、炭化珪素、窒化ガリウム等を用いることができる。本実施の形態では、基板101としてバリウム硼珪酸ガラスを用いる。

【0093】

半導体層102の半導体材料としては、インジウムと亜鉛を有する酸化物半導体を用いる。酸化物半導体としては、上記以外にも各種のものが用いられる。本実施の形態では、インジウムと亜鉛が等しく含まれる酸化物ターゲットを用いたスパッタリング法によって、厚さ30nmのインジウム亜鉛酸化物膜を形成し、これをパターニングして半導体層102に用いる。

【0094】

ゲート絶縁膜104としては、スパッタリング法により形成した絶縁膜を用いる。絶縁膜の材料としては、酸化珪素、酸化アルミニウム、窒化アルミニウム、酸化ハフニウム、酸化ランタン、酸化イットリウム等を用いることができる。本実施の形態では、ゲート絶縁膜104として、スパッタリング法により形成した厚さ100nmの酸化アルミニウムを用いる。

【0095】

半導体層102を形成後、あるいは、ゲート絶縁膜104を形成後のいずれか一方、もしくは双方で、適切な熱処理をおこなうとよい。これは、半導体層102中の水素濃度や酸素欠損を低減させるためであり、可能であれば、半導体層102形成直後におこなうとよい。

【0096】

その際、最初に還元雰囲気で熱処理をおこなった後、酸化雰囲気で熱処理をおこなうとよい。最初の還元雰囲気での熱処理により、水素が酸素と共に効率よく放出され、その後の酸化雰囲気での熱処理により、酸素欠陥を埋めることができる。

【0097】

その後、図4(B)に示すようにゲート105を形成する。ゲート105の材料としては、白金、金、タングステン等の仕事関数の大きな金属を用いることができる。あるいは窒化インジウムのように電子親和力が5電子ボルト以上の化合物を用いてもよい。ゲート105はそのような材料単独で構成してもよいし、多層構造とし、ゲート絶縁膜104に接する部分を、上記の材料で構成してもよい。本実施の形態では、厚さ100nmの白金膜と厚さ100nmのアルミニウム膜をスパッタリング法で形成し、これをエッチングして、ゲート105を形成する。

【0098】

さらに、スパッタリング法により、層間絶縁物106を形成する。層間絶縁物106としては、誘電率の低い材料を用いることが好ましい。本実施の形態では、層間絶縁物106として、CVD法により形成した厚さ300nmの酸化珪素を用いる。そして、図4(C)に示すように、層間絶縁物106を化学的機械的研磨(CMP)法により平坦化する。

【0099】

さらに半導体層102に達するコンタクトホールを形成し、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cを形成する。本実施の形態では、第1の導体電極103a、第2の導体電極103b、第3の導体電極103cは、厚さ50nmの窒化チタン膜と厚さ150nmのチタン膜を、スパッタリング法で連続的に形成して、これをパターニングして形成する。このようにして、図4(D)に示される半導体回路が形成される。

【0100】

半導体層102のうち、ゲート105の設けられた図の左側の部分は、FETの活性層として機能し、ゲート105の設けられていない図の右側の部分は抵抗として機能する。この回路も図6(A)に示したインバータとして用いることができる。

【0101】

(実施の形態4)

上記実施の形態1乃至3で示した半導体装置は、さまざまな電子機器に用いることができる。例えば、液晶ディスプレー、EL(Electro Luminescence)ディスプレー、FE(Field Emission)ディスプレー等の表示装置の駆動回路、イメージセンサの駆動回路、半導体メモリ等である。また、それらを用いた各種電子機器、例えば、テレビジョン、パーソナルコンピュータ、携帯電話等の通信機器、電子手帳、携帯音楽プレーヤ等である。

【符号の説明】

【0102】

101 基板

102 半導体層

103a 第1の導体電極

103b 第2の導体電極

103c 第3の導体電極

104 ゲート絶縁膜

105 ゲート

106 層間絶縁物

【特許請求の範囲】

【請求項1】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有し、前記半導体層のバンドギャップは2電子ボルト以上4電子ボルト未満であることが特徴の電界効果トランジスタ。

【請求項2】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有する電界効果トランジスタ。

【請求項3】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、同じ面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有する電界効果トランジスタ。

【請求項4】

半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、半導体層の他方の面に設けられたゲートとを有し、前記ゲートは前記第1の導体電極と前記第2の導体電極の間の領域の少なくとも一部と重なり、かつ、第2の導体電極と第3の導体電極の間の領域とは重ならないことを特徴とする半導体装置。

【請求項5】

半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、同じ面に設けられたゲートとを有し、前記ゲートは前記第1の導体電極と前記第2の導体電極の間の領域の少なくとも一部と重なり、かつ、第2の導体電極と第3の導体電極の間の領域とは重ならないことを特徴とする半導体装置。

【請求項6】

前記第1の導体電極および前記第2の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和よりも小さいことを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項7】

前記第1の導体電極および前記第2の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和よりも小さいことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項8】

前記第1の導体電極および第2の導体電極と半導体層はオーミック接合であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項9】

前記第1の導体電極および第2の導体電極と半導体層はオーミック接合であることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項10】

前記半導体層と前記ゲートとの間にはゲート絶縁膜を有する請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項11】

前記半導体層と前記ゲートとの間にはゲート絶縁膜を有する請求項4または5のいずれかに記載の半導体装置。

【請求項12】

前記ゲートの、前記半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和よりも大きいことを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項13】

前記ゲートの、前記半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和よりも大きいことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項14】

前記オフセット領域の幅は、10nm以上100nm以下であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項15】

前記第1の導体電極と前記第2の導体電極の間における前記半導体層の幅は、前記第2の導体電極と前記第3の導体電極の間における前記半導体層の幅よりも広いことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項16】

前記半導体層はI型であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項17】

前記半導体層はI型であることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項18】

前記ゲートは、白金、金、タングステン、窒化インジウムのいずれかからなることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項19】

前記ゲートは、白金、金、タングステン、窒化インジウムのいずれかからなることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項1】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有し、前記半導体層のバンドギャップは2電子ボルト以上4電子ボルト未満であることが特徴の電界効果トランジスタ。

【請求項2】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、半導体層の他方の面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有する電界効果トランジスタ。

【請求項3】

半導体層と、その一方の面に接して設けられた第1および第2の導体電極と、同じ面に設けられたゲートとを有し、第1の導体電極とゲートとの間、あるいは第2の導体電極とゲートとの間の少なくとも一方にオフセット領域を有する電界効果トランジスタ。

【請求項4】

半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、半導体層の他方の面に設けられたゲートとを有し、前記ゲートは前記第1の導体電極と前記第2の導体電極の間の領域の少なくとも一部と重なり、かつ、第2の導体電極と第3の導体電極の間の領域とは重ならないことを特徴とする半導体装置。

【請求項5】

半導体層と、その一方の面に接して設けられた第1乃至第3の導体電極と、同じ面に設けられたゲートとを有し、前記ゲートは前記第1の導体電極と前記第2の導体電極の間の領域の少なくとも一部と重なり、かつ、第2の導体電極と第3の導体電極の間の領域とは重ならないことを特徴とする半導体装置。

【請求項6】

前記第1の導体電極および前記第2の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和よりも小さいことを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項7】

前記第1の導体電極および前記第2の導体電極の半導体層と接する部分の仕事関数は、半導体層の電子親和力と0.3電子ボルトの和よりも小さいことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項8】

前記第1の導体電極および第2の導体電極と半導体層はオーミック接合であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項9】

前記第1の導体電極および第2の導体電極と半導体層はオーミック接合であることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項10】

前記半導体層と前記ゲートとの間にはゲート絶縁膜を有する請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項11】

前記半導体層と前記ゲートとの間にはゲート絶縁膜を有する請求項4または5のいずれかに記載の半導体装置。

【請求項12】

前記ゲートの、前記半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和よりも大きいことを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項13】

前記ゲートの、前記半導体層に最も近い部分の材料の仕事関数は、半導体層の電子親和力と0.6電子ボルトの和よりも大きいことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項14】

前記オフセット領域の幅は、10nm以上100nm以下であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項15】

前記第1の導体電極と前記第2の導体電極の間における前記半導体層の幅は、前記第2の導体電極と前記第3の導体電極の間における前記半導体層の幅よりも広いことを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項16】

前記半導体層はI型であることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項17】

前記半導体層はI型であることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【請求項18】

前記ゲートは、白金、金、タングステン、窒化インジウムのいずれかからなることを特徴とする請求項1乃至3のいずれか一に記載の電界効果トランジスタ。

【請求項19】

前記ゲートは、白金、金、タングステン、窒化インジウムのいずれかからなることを特徴とする請求項4または5のいずれかに記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2011−181918(P2011−181918A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2011−22507(P2011−22507)

【出願日】平成23年2月4日(2011.2.4)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成23年2月4日(2011.2.4)

【出願人】(000153878)株式会社半導体エネルギー研究所 (5,264)

【Fターム(参考)】

[ Back to top ]