電界効果トランジスタの製造方法

【構成】 高速動作の可能なGaAsショットキー電界効果を用いたLDD構造の自己整合型FETにおいて、ゲート電極23a形成時のGaAs基板21へのダメージを少なくするために、該ゲート電極23aを薄膜とし、代わってSiO2 膜24を、サイドウォール26aの幅L11が充分な太さに形成され短チャネル効果を抑制することができるように、充分な厚さとする。前記サイドウォール26aは、SiO2 膜24よりもウエットエッチングによる速度が1/10以下と充分小さく、したがってエッチング後、引出配線28aを低抵抗に接合することができる。

【効果】 ゲート電極23aと引出配線28aとの接合にあたって、ゲート電極23aの表面に、ドライエッチングでは酸素などの不純物が導入されて高抵抗となってしまうのに対して、そのような不具合を防止することができる。

【効果】 ゲート電極23aと引出配線28aとの接合にあたって、ゲート電極23aの表面に、ドライエッチングでは酸素などの不純物が導入されて高抵抗となってしまうのに対して、そのような不具合を防止することができる。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、高速スイッチング動作が可能な、ガリウム砒素(GaAs)ショットキー電界効果を利用するLDD(Light Doped Drain )構造の自己整合型電界効果トランジスタの製造方法に関する。

【0002】

【従来の技術】近年、通信用高速デバイスやデジタルゲートアレイなどのために、高速スイッチング動作が可能なGaAsショットキー電界効果を利用したトランジスタの集積化が進められている。

【0003】前記ショットキー電界効果トランジスタにおいて、特にノーマリーオフ型のトランジスタでは、前記集積化に伴い、ゲート長が短くなると、ゲート端子へのバイアス電圧が0Vであっても、ソース−ドレイン間のリーク電流が増加し、またスレッショルド電圧も変化する短チャネル効果が発生してしまうという問題がある。このような短チャネル効果の抑制ならびにソース抵抗およびゲート抵抗の低減を実現するために、能動層においてゲート直下からソースおよびドレイン方向となるにつれて、段階的に不純物の濃度が高くなるように形成され、寄生抵抗の少ない前記LDD構造の電界効果トランジスタが従来から用いられている。

【0004】上述のようなLDD構造の自己整合型GaAsMESFETの典型的な従来技術の製造方法は、電子技術学会発表論文ED87−140P37〜42(極太サイドウォールを用いた0.5μmゲートGaAsMESFETプロセス技術)に示されており、その従来技術の製造工程を図3に示す。

【0005】図3(a)で示すように、GaAs基板1上にシリコン(Si)をイオン注入およびアニール処理することによって能動層2を形成し、さらにその能動層2上にタングステン−アルミ(W−Al)合金によるW−Al層3をスパッタ法によって積層した後、酸化シリコン(SiO2 )膜から成るフォトレジスト4を積層し、ゲート電極に対応したパターニングを行う。さらにそのフォトレジスト4上にチタン/アルミ(Ti/Al)層5を、Al層がGaAs基板1側となるように積層する。

【0006】こうしてゲート電極部分にTi/Al層5が形成されると、電子サイクロトロン共鳴(ECR)式のエッチャーによってW−Al層3をエッチングし、図3R>3(b)で示されるような注入マスクを形成する。その後、図3(c)で示すようにLDD注入を行い、前記能動層にn層2aを形成する。

【0007】続いて、図3(d)で示すように、SiO2 膜6を積層しながら、スルー注入によって前記LDD注入を行い、n+ 層2bを形成する。さらにLDD注入を停止した後も、図3(e)で示すように、SiO2 膜6の積層を行う。前記SiO2 膜6の積層が終了すると、図3(f)で示すように、エッチングによって、前記W−Al層3の側方にサイドウォール6aを形成する。前記サイドウォール6aおよびTi/Al層5をマスクとして、図3(g)で示すようにさらにイオン注入を行い、n++層2cを形成する。

【0008】こうしてイオン注入が終了すると、図3(h)で示すように、通常のフォトリソ技術によって、前記サイドウォール6aの幅L1よりも小さい開口7aを有するフォトレジスト7が形成される。このフォトレジスト7を用いて、図3(i)で示されるように、低抵抗の金属膜8が真空蒸着等によって成膜される。その後、前記フォトレジスト7をエッチングによって除去すると、図3(j)で示すように、前記開口7a部分の金属膜8がゲート引出配線8aとして残存する。

【0009】さらに前記フォトリソ技術によって、図3(k)で示すように、フォトレジスト9が形成され、そのフォトレジスト9がソース電極およびドレイン電極の領域に対応してパターニングされた後、金属膜10が積層される。したがって、前記フォトレジスト9をエッチングによって除去すると、図3(l)で示すように、ソース電極10aおよびドレイン電極10bが形成され、FET11が完成する。

【0010】また、他の従来技術による前記LDD構造の自己整合型GaAsMESFETの製造方法は、特公平6−66336号公報で示されており、その製造工程を図4に示す。まず、図4(a)で示すように、前記GaAs基板1上にSiイオンが注入され、アニール処理が施されて、能動層12が形成される。次に、図4(b)で示すように、WSiから成る耐熱性のゲート13がドライエッチングによって形成される。続いて、前記ゲート13をマスクとして、図4(c)で示されるようにSiイオン注入を行って、コンタクト層12a,12bが形成される。

【0011】その後、図4(d)で示されるように、メッキ時の給電用のニッケル(Ni)膜14が蒸着法によって積層される。さらに、その上に図4(e)で示されるように、表面が平坦になりやすいフォトレジスト等の樹脂層15によって、ゲート13部分が残余の部分よりも薄くなるように被覆を行う。その樹脂層15およびNi膜14を酸素の反応性イオンエッチングによって図4(f)で示すように、上方から一様にエッチングしてゆき、前記ゲート13上に形成されたNi膜14のみを露出させる。

【0012】続いて、前記Ni膜14に給電して、前記ゲート13上の部分に図4(g)で示すように、金(Au)メッキ層16を形成する。そして、図4(h)で示すように、前記Ni膜14のゲート13上以外の部分および樹脂層15がエッチングによって除去された後、低抵抗金属の金属膜17が蒸着されて、ソース電極17aおよびドレイン電極17bが形成され、FET20が完成する。

【0013】

【発明が解決しようとする課題】前述の図3で示す従来技術では、前記短チャネル効果を抑制するために、サイドウォール6aによってゲート長を再現性良く所望とする長さに形成することができる。しかしながら、W−Al層3を直接ドライエッチングしてゲート電極に形成するようにした場合には、W−Al層3をオーバーエッチングする必要がある。このオーバーエッチングによっては、GaAs基板1の表面がプラズマによるダメージをうけてしまい、結晶欠陥等が発生し、素子特性に悪影響を与える虞がある。このため、この図3で示すように、ゲート電極となるW−Al層3を薄膜として、該W−Al層3上にTi/Al層5を積層して、このTi/Al層5をマスクとしてW−Al層3のエッチングを行うことによって、オーバーエッチング量が少なくなるように工夫されている。また、プラズマダメージの少ない前記ECRエッチングを用いて、さらにGaAs基板1へのダメージを抑えるように工夫されている。

【0014】しかしながらこの従来技術では、サイドウォール6aとなるべきSiO2 膜6の気相成長を行う際に、前記Ti/Al層5が高温の雰囲気に曝されてしまい、該Ti/Al層5の表面が酸化し、ゲート引出配線8aとの接触抵抗が高くなるという問題がある。

【0015】また、上述の図4で示す従来技術では、配線抵抗を低減するために、W合金から成るゲート13上に、ゲート引出配線としてAuメッキ層16を形成している。しかしながら、このAuメッキ層16をメッキするためのNi膜14を樹脂層15から露出させるためのプラズマエッチング時に、Ni膜14の表面に酸素プラズマ中から酸素等の不純物が導入されてしまい、高抵抗層を形成してしまう虞がある。

【0016】本発明の目的は、ゲート電極からの引出配線形成時に、ゲート電極表面への不純物の導入を防止することができる電界効果トランジスタの製造方法を提供することである。

【0017】

【課題を解決するための手段】請求項1の発明に係る電界効果トランジスタは、基板上に能動層を形成し、前記能動層上に、所望とする膜厚の第1の絶縁膜をマスクとして薄膜のゲート電極を形成し、前記ゲート電極および第1の絶縁膜の膜厚に対応して、該第1の絶縁膜が露出する厚さとなるように、該第1の絶縁膜よりもエッチング速度が小さい材料によって第2の絶縁膜を形成し、前記第1および第2の絶縁膜を自己整合マスクとして、前記能動層へイオン注入を行い、前記第1の絶縁膜をウエットエッチングによって除去し、前記ウエットエッチングによって第2の絶縁膜に形成された開口に、前記ゲート電極に接続される引出配線を形成し、前記能動層上で前記ゲート電極を挟んで、ソース電極およびドレイン電極を形成することを特徴とする。

【0018】また請求項2の発明に係る電界効果トランジスタの製造方法では、前記第2の絶縁膜のエッチング速度は、第1の絶縁膜のエッチング速度の1/10以下であることを特徴とする。

【0019】さらにまた請求項3の発明に係る電界効果トランジスタの製造方法では、前記第1の絶縁膜は、SiO2 膜、PSG膜、BPSG膜のいずれかであり、前記第2の絶縁膜は、前記第1の絶縁膜と異なる膜であって、かつSiN膜、AlN膜、SiO2 膜のいずれかであることを特徴とする。

【0020】また請求項4の発明に係る電界効果トランジスタの製造方法では、前記ゲート電極がWN膜であり、前記ゲート引出配線がAu、Al、Ti/Al、Ti/Au、Pt/Auのいずれかであることを特徴とする。

【0021】さらにまた請求項5の発明に係る電界効果トランジスタの製造方法では、前記ソース電極およびドレイン電極は、AuGe/Ni/Auであることを特徴とする。

【0022】また請求項6の発明に係る電界効果トランジスタの製造方法では、前記ウエットエッチングによって第2の絶縁膜に形成された開口ならびにソース電極およびドレイン電極の領域が露出するようにフォトレジストを形成し、前記ゲート引出配線ならびにソース電極およびドレイン電極を一括形成することを特徴とする。

【0023】

【作用】請求項1の発明に従えば、GaAsなどの半絶縁性基板上にSiイオン注入などによって能動層が形成され、その能動層上に、たとえば請求項3で示すような、SiO2 、PSG、BPSGのいずれかから成る第1の絶縁膜をマスクとして、耐熱性を有する、たとえば請求項4で示すようなWNなどのW合金によって薄膜のゲート電極が形成される。すなわち、前記ゲート電極となる薄膜がスパッタなどによって積層形成された後、前記SiO2 などから成る第1の絶縁膜がプラズマCVD法などによって積層され、その第1の絶縁膜がパターニングされた後、ドライエッチングが行われて前記ゲート電極が形成される。このとき、前記第1の絶縁膜の膜厚は、後述するようなサイドウォールの幅に対応して決定される。

【0024】こうして、ゲート電極が形成されると、前記第1の絶縁膜よりもエッチング速度が小さい、たとえば請求項2で示されるように1/10以下となるような材料、たとえば請求項3で示すような前記第1の絶縁膜とは異なる材料で、SiN、AlN、SiO2 のいずれかから成る第2の絶縁膜がプラズマCVD法などによってゲート電極および第1の絶縁膜の膜厚の和程度に積層された後、ドライエッチングなでによって一様にエッチングされる。これによって、前記ゲート電極の側方には、前記第1の絶縁膜とゲート電極との膜厚との和にほぼ対応した幅のサイドウォールが形成される。その後、前記能動層には前記第1および第2の絶縁膜を自己整合マスクとして、イオン注入が行われ、高濃度動作領域が形成される。

【0025】その後は、前記ゲート電極上には、第1の絶縁膜がウエットエッチングによって除去された後、第2の絶縁膜に残された開口から、請求項4で示すような、Au、Al、Ti/Al、Ti/Au、Pt/Auなどの低抵抗金属が真空蒸着などによって積層されて、ゲート引出配線が形成される。また、前記能動層上には、通常のフォトリソ技術などを用いて、前記ゲート電極を挟んで、請求項5で示すような、AuGe/Ni/Auなどの低抵抗金属が真空蒸着などによって積層されて、ソース電極およびドレイン電極が形成される。

【0026】したがって、短チャネル効果を抑制することができる所望とするサイドウォールの幅に対応した該サイドウォールの高さを得るにあたって、薄膜のゲート電極に対して第1の絶縁膜の厚さによって対応し、またその第1の絶縁膜はウエットエッチングによって除去されるので、ゲート電極への不純物の導入を抑制することができ、引出配線との接触抵抗を低減することができる。

【0027】さらにまた請求項6の発明に従えば、前記第1の絶縁膜のエッチングによって第2の絶縁膜に形成された開口部分ならびにソース電極およびドレイン電極となるべき領域が露出するように、フォトレジストを形成した後、これらの部分に低抵抗金属を真空蒸着などによって一括形成する。

【0028】したがって、ゲート引出配線の形成とソース電極およびドレイン電極の形成とを同一工程で行うことができ、工程を簡略化することができる。

【0029】

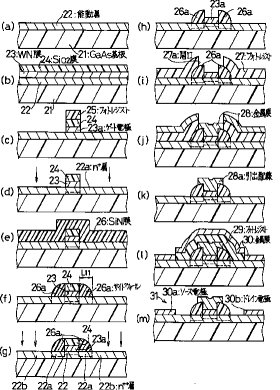

【実施例】本発明の一実施例について、図1に基づいて説明すれば以下のとおりである。

【0030】図1は、本発明の一実施例の電界効果トランジスタの製造工程を説明するための断面図である。まず、図1(a)で示されるように、絶縁性のGaAs基板21上に、Siイオン注入およびアニール処理によって、能動層22が形成される。次に、図1(b)で示すように、耐熱性を有する、たとえばW合金であるWN膜23がマグネトロンスパッタ法によって100nm積層され、さらに第1の絶縁膜であるSiO2 膜24がプラズマCVD法によって400nm積層される。続いて、通常のフォトリソ技術によって、図1(c)で示すように、ゲート電極パターンに対応したフォトレジスト25が形成され、このフォトレジスト25をマスクとして、前記SiO2 膜24がRIE法などによってドライエッチングされ、引続き、そのSiO2 膜24をマスクとしてWN膜23が前記RIE法などでドライエッチングされて、ゲート電極23aが形成される。

【0031】こうして、ゲート電極23aが形成されると、前記ゲート電極23aおよびSiO2 膜24をマスクとして、図1(d)で示されるように、ドナー用のSiイオンが注入されて、n+ 層22aが形成される。

【0032】続いて、前記SiO2 膜24を残したまま、図1(e)で示されるように、第2の絶縁膜であるSiN膜26がプラズマCVD法などによって600nm積層される。このSiN膜26をRIE法などでドライエッチングすると、図1(f)で示されるように該SiN膜26は上方から一様にエッチングされ、ゲート電極23aの側方に、幅L11が500nm程度のサイドウォール26aが形成される。

【0033】前記サイドウォール26aが自己整合マスクとして用いられて、図1(g)で示されるように、後述するソース電極領域およびドレイン電極領域にドナー用のSiイオンが注入され、さらに900℃程度で活性化アニール処理されて、n++層22bが形成される。

【0034】こうしてイオン注入が終了すると、図1(h)で示されるように、前記SiO2 膜24のみが、フッ酸溶液によるウエットエッチング処理によって除去されて、ゲート電極23aの上面が露出される。ここで、SiO2 膜24は、SiN膜26に対してエッチング速度を10倍程度以上確保することができ、したがって前記ウエットエッチング時にサイドウォール26a部分は残存し、このSiO2膜24部分のみが除去されることになる。

【0035】その後、図1(i)で示すように、サイドウォール26aの幅L12よりも内方に開口27aを有するフォトレジスト27を通常のフォトリソ技術によって形成し、図1(j)で示すように、Auなどの低抵抗金属膜28が真空蒸着法などによって成膜される。したがって、前記フォトレジスト27を除去することによって、図1(k)で示すように、前記金属膜28はゲート電極23a上のみが残存し、引出配線28aとなる。

【0036】続いて、通常のフォトリソ技術によって、図1(l)で示すように、前記ソース電極領域およびドレイン電極領域のみが開口するようにパターニングされたフォトレジスト29が形成され、さらにその上に、たとえばAuGe/Ni/Auなどの低抵抗の金属膜30が真空蒸着法などによって成膜される。前記フォトレジスト29が除去されると、図1(n)で示すように、残存した前記金属膜30がソース電極30aおよびドレイン電極30bとなり、FET31が完成する。

【0037】したがって、本発明に従う製造方法では、上述のようにゲート電極23aを薄膜としているので、WN膜23をドライエッチングする際のオーバーエッチング量を少なくすることができ、GaAs基板21へのダメージを抑えることができる。また、このようにゲート電極23aを薄膜に形成しても、該ゲート電極23aのマスクとなるSiO2 膜24の膜厚を厚くして、該ゲート電極23aおよびSiO2 膜24の膜厚によって決定されてしまうサイドウォール26aの幅L11を、短チャネル効果を抑制することができる充分な太さとするこができる。さらにまた、ゲート電極23aをマスクするSiO2 膜24は、ウエットエッチングによって除去されるので、該ゲート電極23aの表面への不純物の導入がなく、引出配線28aと極めて小さい接触抵抗で電気的に接続することが可能となる。

【0038】本発明の第2の実施例について、図2に基づいて説明すれば以下のとおりである。

【0039】図2は、本発明の他の実施例の電界効果トランジスタの製造工程の一部分を説明するための断面図である。上述のような図1(a)〜図1(g)までの工程によって、SiO2 膜24およびサイドウォール26aをマスクとしてイオン注入が終了すると、図2(a)で示されるように、通常のフォトリソ技術によって前記サイドウォール26aの幅よりも狭い開口32aを有するとともに、ソース電極領域およびドレイン電極領域に対応した開口を有するフォトレジスト32が形成される。続いて、図2(b)で示されるように、一様に前記AuGe/Ni/Auなどの低抵抗の金属膜33が真空蒸着法などによって成膜された後、前記フォトレジスト32が除去されると、図2(c)で示されるように、前記図1(m)と同様な構造のFET41が完成する。

【0040】したがって、この図2で示す実施例では、ゲート電極23aの引出配線33aならびにソース電極33bおよびドレイン電極33cを同一の工程で形成することができ、工程を簡略化してコストを低減することができる。

【0041】なお、上述の実施例では、ゲート電極23aのマスクとなる第1の絶縁膜およびサイドウォール26aとなる第2の絶縁膜には、それぞれSiO2 膜24およびSiN膜26が用いられたけれども、エッチング速度が10倍程度以上得ることができる膜質であれば、上述の組合せに限定されるものではない。たとえば、表1で示すように、第1の絶縁膜としてリンケイガラスであるPSG膜またはBPSG膜などを用い、第2の絶縁膜としてSiO2 膜、SiN膜またはAlN膜などを用いても、前記フッ酸溶液で所望とするエッチング速度の比を得ることができる。

【0042】

【表1】

【0043】また、前記金属膜28,30,33は、上述の材料と同程度の抵抗率の金属材料であればよく、たとえばAl,Ti/Al,Ti/AuまたはPt/Auなどが用いられてもよい。

【0044】

【発明の効果】本発明に係る電界効果トランジスタの製造方法は、以上のように、ゲート電極を薄膜として、そのゲート電極のエッチング時のマスクとなる第1の絶縁膜を所望とする厚さとして、能動層へのイオン注入時に自己整合マスクとして機能する第2の絶縁膜から成るサイドウォールの幅を、短チャネル効果が抑制することができる値とする厚さに選び、かつ第2の絶縁膜を第1の絶縁膜よりも、エッチング速度がたとえば1/10以下の充分小さい材料に選ぶ。それゆえ、ゲート電極を覆っていた第1の絶縁膜は、ウエットエッチングによって除去され、ドライエッチングを用いる場合に比べて、電極表面への不純物の導入を抑制し、引出配線との接触抵抗を低減することができる。

【図面の簡単な説明】

【図1】本発明の一実施例の電界効果トランジスタの製造工程を説明するための断面図である。

【図2】本発明の他の実施例の電界効果トランジスタの製造工程の一部分を説明するための断面図である。

【図3】典型的な従来技術の電界効果トランジスタの製造工程を説明するための断面図である。

【図4】他の従来技術の電界効果トランジスタの製造工程を説明するための断面図である。

【符号の説明】

21 GaAs基板

22 能動層

22a n+ 層

22b n++層

23 WN膜

23a ゲート電極

24 SiO2 膜(第1の絶縁膜)

25 フォトレジスト

26 SiN膜

26a サイドウォール(第2の絶縁膜)

27 フォトレジスト

28 金属膜

28a 引出配線

29 フォトレジスト

30 金属膜

30a ソース電極

30b ドレイン電極

31 FET

32 フォトレジスト

33 金属膜

33a 引出配線

33b ソース電極

33c ドレイン電極

41 FET

【0001】

【産業上の利用分野】本発明は、高速スイッチング動作が可能な、ガリウム砒素(GaAs)ショットキー電界効果を利用するLDD(Light Doped Drain )構造の自己整合型電界効果トランジスタの製造方法に関する。

【0002】

【従来の技術】近年、通信用高速デバイスやデジタルゲートアレイなどのために、高速スイッチング動作が可能なGaAsショットキー電界効果を利用したトランジスタの集積化が進められている。

【0003】前記ショットキー電界効果トランジスタにおいて、特にノーマリーオフ型のトランジスタでは、前記集積化に伴い、ゲート長が短くなると、ゲート端子へのバイアス電圧が0Vであっても、ソース−ドレイン間のリーク電流が増加し、またスレッショルド電圧も変化する短チャネル効果が発生してしまうという問題がある。このような短チャネル効果の抑制ならびにソース抵抗およびゲート抵抗の低減を実現するために、能動層においてゲート直下からソースおよびドレイン方向となるにつれて、段階的に不純物の濃度が高くなるように形成され、寄生抵抗の少ない前記LDD構造の電界効果トランジスタが従来から用いられている。

【0004】上述のようなLDD構造の自己整合型GaAsMESFETの典型的な従来技術の製造方法は、電子技術学会発表論文ED87−140P37〜42(極太サイドウォールを用いた0.5μmゲートGaAsMESFETプロセス技術)に示されており、その従来技術の製造工程を図3に示す。

【0005】図3(a)で示すように、GaAs基板1上にシリコン(Si)をイオン注入およびアニール処理することによって能動層2を形成し、さらにその能動層2上にタングステン−アルミ(W−Al)合金によるW−Al層3をスパッタ法によって積層した後、酸化シリコン(SiO2 )膜から成るフォトレジスト4を積層し、ゲート電極に対応したパターニングを行う。さらにそのフォトレジスト4上にチタン/アルミ(Ti/Al)層5を、Al層がGaAs基板1側となるように積層する。

【0006】こうしてゲート電極部分にTi/Al層5が形成されると、電子サイクロトロン共鳴(ECR)式のエッチャーによってW−Al層3をエッチングし、図3R>3(b)で示されるような注入マスクを形成する。その後、図3(c)で示すようにLDD注入を行い、前記能動層にn層2aを形成する。

【0007】続いて、図3(d)で示すように、SiO2 膜6を積層しながら、スルー注入によって前記LDD注入を行い、n+ 層2bを形成する。さらにLDD注入を停止した後も、図3(e)で示すように、SiO2 膜6の積層を行う。前記SiO2 膜6の積層が終了すると、図3(f)で示すように、エッチングによって、前記W−Al層3の側方にサイドウォール6aを形成する。前記サイドウォール6aおよびTi/Al層5をマスクとして、図3(g)で示すようにさらにイオン注入を行い、n++層2cを形成する。

【0008】こうしてイオン注入が終了すると、図3(h)で示すように、通常のフォトリソ技術によって、前記サイドウォール6aの幅L1よりも小さい開口7aを有するフォトレジスト7が形成される。このフォトレジスト7を用いて、図3(i)で示されるように、低抵抗の金属膜8が真空蒸着等によって成膜される。その後、前記フォトレジスト7をエッチングによって除去すると、図3(j)で示すように、前記開口7a部分の金属膜8がゲート引出配線8aとして残存する。

【0009】さらに前記フォトリソ技術によって、図3(k)で示すように、フォトレジスト9が形成され、そのフォトレジスト9がソース電極およびドレイン電極の領域に対応してパターニングされた後、金属膜10が積層される。したがって、前記フォトレジスト9をエッチングによって除去すると、図3(l)で示すように、ソース電極10aおよびドレイン電極10bが形成され、FET11が完成する。

【0010】また、他の従来技術による前記LDD構造の自己整合型GaAsMESFETの製造方法は、特公平6−66336号公報で示されており、その製造工程を図4に示す。まず、図4(a)で示すように、前記GaAs基板1上にSiイオンが注入され、アニール処理が施されて、能動層12が形成される。次に、図4(b)で示すように、WSiから成る耐熱性のゲート13がドライエッチングによって形成される。続いて、前記ゲート13をマスクとして、図4(c)で示されるようにSiイオン注入を行って、コンタクト層12a,12bが形成される。

【0011】その後、図4(d)で示されるように、メッキ時の給電用のニッケル(Ni)膜14が蒸着法によって積層される。さらに、その上に図4(e)で示されるように、表面が平坦になりやすいフォトレジスト等の樹脂層15によって、ゲート13部分が残余の部分よりも薄くなるように被覆を行う。その樹脂層15およびNi膜14を酸素の反応性イオンエッチングによって図4(f)で示すように、上方から一様にエッチングしてゆき、前記ゲート13上に形成されたNi膜14のみを露出させる。

【0012】続いて、前記Ni膜14に給電して、前記ゲート13上の部分に図4(g)で示すように、金(Au)メッキ層16を形成する。そして、図4(h)で示すように、前記Ni膜14のゲート13上以外の部分および樹脂層15がエッチングによって除去された後、低抵抗金属の金属膜17が蒸着されて、ソース電極17aおよびドレイン電極17bが形成され、FET20が完成する。

【0013】

【発明が解決しようとする課題】前述の図3で示す従来技術では、前記短チャネル効果を抑制するために、サイドウォール6aによってゲート長を再現性良く所望とする長さに形成することができる。しかしながら、W−Al層3を直接ドライエッチングしてゲート電極に形成するようにした場合には、W−Al層3をオーバーエッチングする必要がある。このオーバーエッチングによっては、GaAs基板1の表面がプラズマによるダメージをうけてしまい、結晶欠陥等が発生し、素子特性に悪影響を与える虞がある。このため、この図3で示すように、ゲート電極となるW−Al層3を薄膜として、該W−Al層3上にTi/Al層5を積層して、このTi/Al層5をマスクとしてW−Al層3のエッチングを行うことによって、オーバーエッチング量が少なくなるように工夫されている。また、プラズマダメージの少ない前記ECRエッチングを用いて、さらにGaAs基板1へのダメージを抑えるように工夫されている。

【0014】しかしながらこの従来技術では、サイドウォール6aとなるべきSiO2 膜6の気相成長を行う際に、前記Ti/Al層5が高温の雰囲気に曝されてしまい、該Ti/Al層5の表面が酸化し、ゲート引出配線8aとの接触抵抗が高くなるという問題がある。

【0015】また、上述の図4で示す従来技術では、配線抵抗を低減するために、W合金から成るゲート13上に、ゲート引出配線としてAuメッキ層16を形成している。しかしながら、このAuメッキ層16をメッキするためのNi膜14を樹脂層15から露出させるためのプラズマエッチング時に、Ni膜14の表面に酸素プラズマ中から酸素等の不純物が導入されてしまい、高抵抗層を形成してしまう虞がある。

【0016】本発明の目的は、ゲート電極からの引出配線形成時に、ゲート電極表面への不純物の導入を防止することができる電界効果トランジスタの製造方法を提供することである。

【0017】

【課題を解決するための手段】請求項1の発明に係る電界効果トランジスタは、基板上に能動層を形成し、前記能動層上に、所望とする膜厚の第1の絶縁膜をマスクとして薄膜のゲート電極を形成し、前記ゲート電極および第1の絶縁膜の膜厚に対応して、該第1の絶縁膜が露出する厚さとなるように、該第1の絶縁膜よりもエッチング速度が小さい材料によって第2の絶縁膜を形成し、前記第1および第2の絶縁膜を自己整合マスクとして、前記能動層へイオン注入を行い、前記第1の絶縁膜をウエットエッチングによって除去し、前記ウエットエッチングによって第2の絶縁膜に形成された開口に、前記ゲート電極に接続される引出配線を形成し、前記能動層上で前記ゲート電極を挟んで、ソース電極およびドレイン電極を形成することを特徴とする。

【0018】また請求項2の発明に係る電界効果トランジスタの製造方法では、前記第2の絶縁膜のエッチング速度は、第1の絶縁膜のエッチング速度の1/10以下であることを特徴とする。

【0019】さらにまた請求項3の発明に係る電界効果トランジスタの製造方法では、前記第1の絶縁膜は、SiO2 膜、PSG膜、BPSG膜のいずれかであり、前記第2の絶縁膜は、前記第1の絶縁膜と異なる膜であって、かつSiN膜、AlN膜、SiO2 膜のいずれかであることを特徴とする。

【0020】また請求項4の発明に係る電界効果トランジスタの製造方法では、前記ゲート電極がWN膜であり、前記ゲート引出配線がAu、Al、Ti/Al、Ti/Au、Pt/Auのいずれかであることを特徴とする。

【0021】さらにまた請求項5の発明に係る電界効果トランジスタの製造方法では、前記ソース電極およびドレイン電極は、AuGe/Ni/Auであることを特徴とする。

【0022】また請求項6の発明に係る電界効果トランジスタの製造方法では、前記ウエットエッチングによって第2の絶縁膜に形成された開口ならびにソース電極およびドレイン電極の領域が露出するようにフォトレジストを形成し、前記ゲート引出配線ならびにソース電極およびドレイン電極を一括形成することを特徴とする。

【0023】

【作用】請求項1の発明に従えば、GaAsなどの半絶縁性基板上にSiイオン注入などによって能動層が形成され、その能動層上に、たとえば請求項3で示すような、SiO2 、PSG、BPSGのいずれかから成る第1の絶縁膜をマスクとして、耐熱性を有する、たとえば請求項4で示すようなWNなどのW合金によって薄膜のゲート電極が形成される。すなわち、前記ゲート電極となる薄膜がスパッタなどによって積層形成された後、前記SiO2 などから成る第1の絶縁膜がプラズマCVD法などによって積層され、その第1の絶縁膜がパターニングされた後、ドライエッチングが行われて前記ゲート電極が形成される。このとき、前記第1の絶縁膜の膜厚は、後述するようなサイドウォールの幅に対応して決定される。

【0024】こうして、ゲート電極が形成されると、前記第1の絶縁膜よりもエッチング速度が小さい、たとえば請求項2で示されるように1/10以下となるような材料、たとえば請求項3で示すような前記第1の絶縁膜とは異なる材料で、SiN、AlN、SiO2 のいずれかから成る第2の絶縁膜がプラズマCVD法などによってゲート電極および第1の絶縁膜の膜厚の和程度に積層された後、ドライエッチングなでによって一様にエッチングされる。これによって、前記ゲート電極の側方には、前記第1の絶縁膜とゲート電極との膜厚との和にほぼ対応した幅のサイドウォールが形成される。その後、前記能動層には前記第1および第2の絶縁膜を自己整合マスクとして、イオン注入が行われ、高濃度動作領域が形成される。

【0025】その後は、前記ゲート電極上には、第1の絶縁膜がウエットエッチングによって除去された後、第2の絶縁膜に残された開口から、請求項4で示すような、Au、Al、Ti/Al、Ti/Au、Pt/Auなどの低抵抗金属が真空蒸着などによって積層されて、ゲート引出配線が形成される。また、前記能動層上には、通常のフォトリソ技術などを用いて、前記ゲート電極を挟んで、請求項5で示すような、AuGe/Ni/Auなどの低抵抗金属が真空蒸着などによって積層されて、ソース電極およびドレイン電極が形成される。

【0026】したがって、短チャネル効果を抑制することができる所望とするサイドウォールの幅に対応した該サイドウォールの高さを得るにあたって、薄膜のゲート電極に対して第1の絶縁膜の厚さによって対応し、またその第1の絶縁膜はウエットエッチングによって除去されるので、ゲート電極への不純物の導入を抑制することができ、引出配線との接触抵抗を低減することができる。

【0027】さらにまた請求項6の発明に従えば、前記第1の絶縁膜のエッチングによって第2の絶縁膜に形成された開口部分ならびにソース電極およびドレイン電極となるべき領域が露出するように、フォトレジストを形成した後、これらの部分に低抵抗金属を真空蒸着などによって一括形成する。

【0028】したがって、ゲート引出配線の形成とソース電極およびドレイン電極の形成とを同一工程で行うことができ、工程を簡略化することができる。

【0029】

【実施例】本発明の一実施例について、図1に基づいて説明すれば以下のとおりである。

【0030】図1は、本発明の一実施例の電界効果トランジスタの製造工程を説明するための断面図である。まず、図1(a)で示されるように、絶縁性のGaAs基板21上に、Siイオン注入およびアニール処理によって、能動層22が形成される。次に、図1(b)で示すように、耐熱性を有する、たとえばW合金であるWN膜23がマグネトロンスパッタ法によって100nm積層され、さらに第1の絶縁膜であるSiO2 膜24がプラズマCVD法によって400nm積層される。続いて、通常のフォトリソ技術によって、図1(c)で示すように、ゲート電極パターンに対応したフォトレジスト25が形成され、このフォトレジスト25をマスクとして、前記SiO2 膜24がRIE法などによってドライエッチングされ、引続き、そのSiO2 膜24をマスクとしてWN膜23が前記RIE法などでドライエッチングされて、ゲート電極23aが形成される。

【0031】こうして、ゲート電極23aが形成されると、前記ゲート電極23aおよびSiO2 膜24をマスクとして、図1(d)で示されるように、ドナー用のSiイオンが注入されて、n+ 層22aが形成される。

【0032】続いて、前記SiO2 膜24を残したまま、図1(e)で示されるように、第2の絶縁膜であるSiN膜26がプラズマCVD法などによって600nm積層される。このSiN膜26をRIE法などでドライエッチングすると、図1(f)で示されるように該SiN膜26は上方から一様にエッチングされ、ゲート電極23aの側方に、幅L11が500nm程度のサイドウォール26aが形成される。

【0033】前記サイドウォール26aが自己整合マスクとして用いられて、図1(g)で示されるように、後述するソース電極領域およびドレイン電極領域にドナー用のSiイオンが注入され、さらに900℃程度で活性化アニール処理されて、n++層22bが形成される。

【0034】こうしてイオン注入が終了すると、図1(h)で示されるように、前記SiO2 膜24のみが、フッ酸溶液によるウエットエッチング処理によって除去されて、ゲート電極23aの上面が露出される。ここで、SiO2 膜24は、SiN膜26に対してエッチング速度を10倍程度以上確保することができ、したがって前記ウエットエッチング時にサイドウォール26a部分は残存し、このSiO2膜24部分のみが除去されることになる。

【0035】その後、図1(i)で示すように、サイドウォール26aの幅L12よりも内方に開口27aを有するフォトレジスト27を通常のフォトリソ技術によって形成し、図1(j)で示すように、Auなどの低抵抗金属膜28が真空蒸着法などによって成膜される。したがって、前記フォトレジスト27を除去することによって、図1(k)で示すように、前記金属膜28はゲート電極23a上のみが残存し、引出配線28aとなる。

【0036】続いて、通常のフォトリソ技術によって、図1(l)で示すように、前記ソース電極領域およびドレイン電極領域のみが開口するようにパターニングされたフォトレジスト29が形成され、さらにその上に、たとえばAuGe/Ni/Auなどの低抵抗の金属膜30が真空蒸着法などによって成膜される。前記フォトレジスト29が除去されると、図1(n)で示すように、残存した前記金属膜30がソース電極30aおよびドレイン電極30bとなり、FET31が完成する。

【0037】したがって、本発明に従う製造方法では、上述のようにゲート電極23aを薄膜としているので、WN膜23をドライエッチングする際のオーバーエッチング量を少なくすることができ、GaAs基板21へのダメージを抑えることができる。また、このようにゲート電極23aを薄膜に形成しても、該ゲート電極23aのマスクとなるSiO2 膜24の膜厚を厚くして、該ゲート電極23aおよびSiO2 膜24の膜厚によって決定されてしまうサイドウォール26aの幅L11を、短チャネル効果を抑制することができる充分な太さとするこができる。さらにまた、ゲート電極23aをマスクするSiO2 膜24は、ウエットエッチングによって除去されるので、該ゲート電極23aの表面への不純物の導入がなく、引出配線28aと極めて小さい接触抵抗で電気的に接続することが可能となる。

【0038】本発明の第2の実施例について、図2に基づいて説明すれば以下のとおりである。

【0039】図2は、本発明の他の実施例の電界効果トランジスタの製造工程の一部分を説明するための断面図である。上述のような図1(a)〜図1(g)までの工程によって、SiO2 膜24およびサイドウォール26aをマスクとしてイオン注入が終了すると、図2(a)で示されるように、通常のフォトリソ技術によって前記サイドウォール26aの幅よりも狭い開口32aを有するとともに、ソース電極領域およびドレイン電極領域に対応した開口を有するフォトレジスト32が形成される。続いて、図2(b)で示されるように、一様に前記AuGe/Ni/Auなどの低抵抗の金属膜33が真空蒸着法などによって成膜された後、前記フォトレジスト32が除去されると、図2(c)で示されるように、前記図1(m)と同様な構造のFET41が完成する。

【0040】したがって、この図2で示す実施例では、ゲート電極23aの引出配線33aならびにソース電極33bおよびドレイン電極33cを同一の工程で形成することができ、工程を簡略化してコストを低減することができる。

【0041】なお、上述の実施例では、ゲート電極23aのマスクとなる第1の絶縁膜およびサイドウォール26aとなる第2の絶縁膜には、それぞれSiO2 膜24およびSiN膜26が用いられたけれども、エッチング速度が10倍程度以上得ることができる膜質であれば、上述の組合せに限定されるものではない。たとえば、表1で示すように、第1の絶縁膜としてリンケイガラスであるPSG膜またはBPSG膜などを用い、第2の絶縁膜としてSiO2 膜、SiN膜またはAlN膜などを用いても、前記フッ酸溶液で所望とするエッチング速度の比を得ることができる。

【0042】

【表1】

【0043】また、前記金属膜28,30,33は、上述の材料と同程度の抵抗率の金属材料であればよく、たとえばAl,Ti/Al,Ti/AuまたはPt/Auなどが用いられてもよい。

【0044】

【発明の効果】本発明に係る電界効果トランジスタの製造方法は、以上のように、ゲート電極を薄膜として、そのゲート電極のエッチング時のマスクとなる第1の絶縁膜を所望とする厚さとして、能動層へのイオン注入時に自己整合マスクとして機能する第2の絶縁膜から成るサイドウォールの幅を、短チャネル効果が抑制することができる値とする厚さに選び、かつ第2の絶縁膜を第1の絶縁膜よりも、エッチング速度がたとえば1/10以下の充分小さい材料に選ぶ。それゆえ、ゲート電極を覆っていた第1の絶縁膜は、ウエットエッチングによって除去され、ドライエッチングを用いる場合に比べて、電極表面への不純物の導入を抑制し、引出配線との接触抵抗を低減することができる。

【図面の簡単な説明】

【図1】本発明の一実施例の電界効果トランジスタの製造工程を説明するための断面図である。

【図2】本発明の他の実施例の電界効果トランジスタの製造工程の一部分を説明するための断面図である。

【図3】典型的な従来技術の電界効果トランジスタの製造工程を説明するための断面図である。

【図4】他の従来技術の電界効果トランジスタの製造工程を説明するための断面図である。

【符号の説明】

21 GaAs基板

22 能動層

22a n+ 層

22b n++層

23 WN膜

23a ゲート電極

24 SiO2 膜(第1の絶縁膜)

25 フォトレジスト

26 SiN膜

26a サイドウォール(第2の絶縁膜)

27 フォトレジスト

28 金属膜

28a 引出配線

29 フォトレジスト

30 金属膜

30a ソース電極

30b ドレイン電極

31 FET

32 フォトレジスト

33 金属膜

33a 引出配線

33b ソース電極

33c ドレイン電極

41 FET

【特許請求の範囲】

【請求項1】基板上に能動層を形成し、前記能動層上に、所望とする膜厚の第1の絶縁膜をマスクとして薄膜のゲート電極を形成し、前記ゲート電極および第1の絶縁膜の膜厚に対応して、該第1の絶縁膜が露出する厚さとなるように、該第1の絶縁膜よりもエッチング速度が小さい材料によって第2の絶縁膜を形成し、前記第1および第2の絶縁膜を自己整合マスクとして、前記能動層へイオン注入を行い、前記第1の絶縁膜をウエットエッチングによって除去し、前記ウエットエッチングによって第2の絶縁膜に形成された開口に、前記ゲート電極に接続される引出配線を形成し、前記能動層上で前記ゲート電極を挟んで、ソース電極およびドレイン電極を形成することを特徴とする電界トランジスタの製造方法。

【請求項2】前記第2の絶縁膜のエッチング速度は、第1の絶縁膜のエッチング速度の1/10以下であることを特徴とする請求項1記載の電界効果トランジスタの製造方法。

【請求項3】前記第1の絶縁膜は、SiO2 膜、PSG膜、BPSG膜のいずれかであり、前記第2の絶縁膜は、前記第1の絶縁膜と異なる膜であって、かつSiN膜、AlN膜、SiO2 膜のいずれかであることを特徴とする請求項1または2記載の電界効果トランジスタの製造方法。

【請求項4】前記ゲート電極がWN膜であり、前記ゲート引出配線がAu、Al、Ti/Al、Ti/Au、Pt/Auのいずれかであることを特徴とする請求項1〜3のいずれかに記載の電界効果トランジスタの製造方法。

【請求項5】前記ソース電極およびドレイン電極は、AuGe/Ni/Auであることを特徴とする請求項1〜4のいずれかに記載の電界効果トランジスタの製造方法。

【請求項6】前記ウエットエッチングによって第2の絶縁膜に形成された開口ならびにソース電極およびドレイン電極の領域が露出するようにフォトレジストを形成し、前記ゲート引出配線ならびにソース電極およびドレイン電極を一括形成することを特徴とする請求項1〜5のいずれかに記載の電界効果トランジスタの製造方法。

【請求項1】基板上に能動層を形成し、前記能動層上に、所望とする膜厚の第1の絶縁膜をマスクとして薄膜のゲート電極を形成し、前記ゲート電極および第1の絶縁膜の膜厚に対応して、該第1の絶縁膜が露出する厚さとなるように、該第1の絶縁膜よりもエッチング速度が小さい材料によって第2の絶縁膜を形成し、前記第1および第2の絶縁膜を自己整合マスクとして、前記能動層へイオン注入を行い、前記第1の絶縁膜をウエットエッチングによって除去し、前記ウエットエッチングによって第2の絶縁膜に形成された開口に、前記ゲート電極に接続される引出配線を形成し、前記能動層上で前記ゲート電極を挟んで、ソース電極およびドレイン電極を形成することを特徴とする電界トランジスタの製造方法。

【請求項2】前記第2の絶縁膜のエッチング速度は、第1の絶縁膜のエッチング速度の1/10以下であることを特徴とする請求項1記載の電界効果トランジスタの製造方法。

【請求項3】前記第1の絶縁膜は、SiO2 膜、PSG膜、BPSG膜のいずれかであり、前記第2の絶縁膜は、前記第1の絶縁膜と異なる膜であって、かつSiN膜、AlN膜、SiO2 膜のいずれかであることを特徴とする請求項1または2記載の電界効果トランジスタの製造方法。

【請求項4】前記ゲート電極がWN膜であり、前記ゲート引出配線がAu、Al、Ti/Al、Ti/Au、Pt/Auのいずれかであることを特徴とする請求項1〜3のいずれかに記載の電界効果トランジスタの製造方法。

【請求項5】前記ソース電極およびドレイン電極は、AuGe/Ni/Auであることを特徴とする請求項1〜4のいずれかに記載の電界効果トランジスタの製造方法。

【請求項6】前記ウエットエッチングによって第2の絶縁膜に形成された開口ならびにソース電極およびドレイン電極の領域が露出するようにフォトレジストを形成し、前記ゲート引出配線ならびにソース電極およびドレイン電極を一括形成することを特徴とする請求項1〜5のいずれかに記載の電界効果トランジスタの製造方法。

【図2】

【図4】

【図1】

【図3】

【図4】

【図1】

【図3】

【公開番号】特開平8−288308

【公開日】平成8年(1996)11月1日

【国際特許分類】

【出願番号】特願平7−87189

【出願日】平成7年(1995)4月12日

【出願人】(000005049)シャープ株式会社 (33,933)

【公開日】平成8年(1996)11月1日

【国際特許分類】

【出願日】平成7年(1995)4月12日

【出願人】(000005049)シャープ株式会社 (33,933)

[ Back to top ]