電界効果トランジスタ

【課題】 ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供する。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

【解決手段】 電界効果トランジスタの下面または上面にボディ電極8を設ける。下面にボディ電極8を設ける場合、p型Si基板2上にAlN層31およびGaN層32の繰り返しによるバッファ層3を介してp−GaN層4を設け、バッファ層3の最上層のAlN層31を薄くし、p型Si基板の下面にボディ電極8を形成する。上面にボディ電極8を設ける場合、サファイア基板21上にp−GaN層4を設け、ソース電極5およびドレイン電極6下の部分にAlGaN層13を設け、AlGaN層13上にボディ電極8を設ける。アバランシェにより生じる正孔20をボディ電極8より引き抜く。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、III族窒化物半導体を使用した電界効果トランジスタに関し、更に詳しくは、ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタに関する。

【背景技術】

【0002】

GaNなどのIII族窒化物半導体は、材料の本質的特性から、シリコン半導体に比べ耐圧が高く、高電流密度が得られ、高温動作が可能なことからパワーデバイスとして期待されている。

【0003】

III族窒化物を用いた電界効果トランジスタとしては、例えば、GaN系MOSFET(Metal Oxide Silicon Field Effect Transistor)(例えば、非特許文献1)やAlGaN/GaN系HFET(Hetero-junction Field Effect Transistor)(例えば、非特許文献2)が提案されている。

【0004】

これらGaN系の電界効果トランジスタは、Si半導体や、従来のGaAs、InPなどのIII族化合物半導体よりも高い絶縁破壊電界や飽和移動度を有することから、特にパワーデバイスに適している。

【0005】

また、GaN系MOSFETはノーマリーオフを容易に実現できるため、電源回路に不調が起こった際、安全な方向に進む、いわゆるフェールセーフの面からもパワーデバイスに適している。

非特許文献1に示されるGaN系MOSFETは、半導体層に表面電界を緩和するリサーフ(RESURF:REduced SURface Field)層を設けることにより、940Vの耐圧を実現している。

【0006】

また、非特許文献2に示されるAlGaN/GaN系HFETは、半導体層として、ノンドープのAlGaNキャリア走行層上に、キャリア走行層よりも格子定数の小さいノンドープまたはn型のAlGaN障壁層と、キャリア走行層と格子定数の等しいAlGaN閾値制御層と、キャリア走行層よりも格子定数の小さいノンドープまたはn型のAlGaNキャリア誘起層を順に積層した構造であり、通常、AlGaN系HFETではノーマリーオフ動作が難しいが、キャリア誘起層全部と障壁層の一部を除去したリセス構造中にゲート電極を形成し、障壁層の膜厚を臨界膜厚以下にすることによりノーマリーオフ動作を実現するとともに、障壁層の膜厚を原子層レベルに制御することにより、閾値電圧のばらつきを小さく抑えることを可能にしている。また、キャリア誘起層を設けたことによりオン抵抗を低減している。

【0007】

Si系のパワーデバイスの場合は、高い耐圧を実現するために、p+層にボディ電極を配置する方法が知られている。このボディ電極から、ドレイン電圧を高くしたときに起きるアバランシェ現象で発生する電子・正孔対のうちの正孔を引き抜くことで、耐圧を向上することができる。しかし、GaNの場合は、高濃度のp+層をイオン注入法などにより選択的に形成することが非常に難しい。イオン注入でp層を形成した報告では、正孔のシートキャリア密度で7×1012cm−2程度である(非特許文献3)。

【先行技術文献】

【非特許文献】

【0008】

【非特許文献1】W.Huang,T.Khan,T.P.Chow,“Enhancement−Mode n−Channel GaN MOSFETs on p and n− GaN/Sapphire Substrates,”18th International Symposium on Power Semiconductor Devices and ICs(ISPSD) 2006(Italy),10−1.

【非特許文献2】M.Kuraguchi et al.,“Normally−off GaN−MISFET with well−controlled threshold voltage,”International Workshop on Nitride Semiconductors 2006(IWN2006),Oct.22−27,2006,Kyoto,Japan,WeED1−4.

【非特許文献3】Wilson R.G. et al.,“Redistribution and activation of implanted S,Se,Te,Be,Mg,and C in GaN,”Journal of Vacuum Science and Technology,A17,1226(1999).

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、パワーデバイスでは、耐圧をより高く、また、ゲート電極の閾値電圧をより高くし、ノーマリーオフ動作を可能する必要がある。例えば、自動車用電源回路等に適用するためには、約1200Vのドレイン耐圧と+3V以上の閾値電圧が要求される。

非特許文献1のGaN系MOSFETは、940Vの耐圧を実現しているが、自動車用電源回路の用途では更に高い耐圧が必要という問題がある。

【0010】

また、非特許文献2のAlGaN/GaN系HFETは、ノーマリーオフ動作を実現し、閾値電圧をばらつき少なく制御することが可能であるが、閾値電圧が+1V程度であり、パワーデバイスの閾値電圧として必要な+3Vを満たさないという問題がある。

【0011】

また、Si系パワーデバイスと同様にp+層に電極を配置し、正孔を引き抜く方法をGaN系パワーデバイスで実現するためには、1015cm−2レベルのシートキャリア密度のp+層を形成する必要があるが、GaNで形成可能なp+層のシートキャリア密度は、非特許文献3に示されるように7×1012cm−2程度と低すぎるという問題がある。また、高濃度のp+層を選択的に形成することは更に難しい。

【0012】

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、ノーマリーオフ動作、高耐圧、大電流を実現するIII族窒化物半導体電界効果トランジスタを提供することである。

【課題を解決するための手段】

【0013】

前述した課題を解決するための本発明は、III族窒化物半導体を用いた電界効果トランジスタにおいて、前記III族窒化物半導体の上面または下面のいずれかにボディ電極が形成されることを特徴とする電界効果トランジスタである。

この電界効果トランジスタは、半導体層として、少なくともp型GaN層を1層含む。これにより、ノーマリーオフ動作を容易に実現することが可能になる。

【0014】

ここで、電界効果トランジスタの下面にボディ電極を形成する場合、半導体基板をp型シリコンとすることが好ましい。

また、前記半導体基板と前記半導体層の間にバッファ層が形成され、前記バッファ層は複数の層で構成され、前記バッファ層の各層は、AlNまたは/およびGaNまたは/およびBN、または、AlN、GaN、BNを組み合わせた化合物よりなることが好ましい。

さらに、前記バッファ層の最上層はAlNであり、1nm以上40nm以下であることが好ましい。

【0015】

このように、p型シリコン基板上に多層から成るバッファ層を介してp型GaN層を少なくとも1層含む半導体層を設け、p型シリコン基板の下面にボディ電極を配置することにより、アバランシェ発生時の正孔をこのボディ電極から引き抜くことが可能になり、耐圧を向上することが可能になる。

【0016】

一方、電界効果トランジスタの上面にボディ電極を形成する場合、サファイア基板上に形成したp型GaN層上にAlGaN層が形成され、AlGaN層上に直接ボディ電極が形成されることが望ましい。

このように、AlGaN層上に直接ボディ電極を形成することにより、アバランシェ発生時の正孔をこのボディ電極から引き抜くことが可能になり、耐圧を向上することが可能になる。

【発明の効果】

【0017】

本発明によれば、ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供することが可能になる。

【図面の簡単な説明】

【0018】

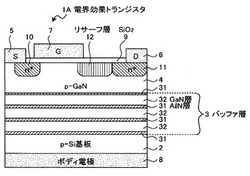

【図1】本発明の第1の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Aの概略構成を示す断面図

【図2】本発明の第2の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの概略構成を示す断面図

【図3】トンネル効果による正孔の引き抜き方法の説明図

【図4】第2の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの耐圧の測定結果を示す図

【発明を実施するための形態】

【0019】

以下、図面に基づいて本発明の好適な実施形態について詳細に説明する。

(第1の実施形態)

図1は、本発明の第1の実施形態に係る電界効果トランジスタ1Aの概略構成を示す断面図である。III族窒化物としてGaNとAlNを使用する。

【0020】

この電界効果トランジスタ1Aは、p型Si基板2を半導体基板とし、その上にバッファ層3を介してp型GaN4からなる半導体層を備える。p型Si基板2の下面にボディ電極8が設けられる。

また、p型GaN半導体層4表面のソース電極(S)5下およびドレイン電極(D)6下の領域にはコンタクト層であるn+層10および11が形成される。また、p型GaN半導体層4表面のゲート電極(G)7とドレイン電極6間の下部領域には、電界集中を緩和するためのリサーフ層(RESURF層)12を備える。またp型GaN半導体層4上のソース電極5およびゲート電極6間の領域にはゲート酸化膜であるSiO29が形成され、SiO29上にゲート電極7が設けられる。

【0021】

バッファ層3は、例えば、AlN層31とGaN層32が交互に複数層形成された積層構造であり、p型Si基板2上にp型GaN半導体層4を形成する際のSiとGaNの格子定数および熱膨張係数の差を緩和する役目を果たす。

バッファ層3としては、図1に示したAlN、GaNの他、BNや、これらのIII族窒化物の組み合わせによる化合物、例えば、AlGaNやBGaN等を使用することが可能である。

【0022】

バッファ層3の最上層はAlN層31であり、この最上層のAlN層31はバッファ層3の他のAlN層31よりも薄く形成する。すなわち、最上層のAlN層の膜厚は1nm以上40nm以下にする。

後述するが、この最上層のAlN層を薄くし、p型Si基板の下面にボディ電極を設けることにより、アバランシェ現象によりp型GaN半導体層4あるいはリサーフ層12内に生じる正孔をトンネル効果によりバッファ層3を透過させ引き抜くことが可能になる。これにより、耐圧の向上が可能になる。

【0023】

次に、図1に示した構成を持つ第1の実施形態の電界効果トランジスタ1Aの作用効果を説明する。

【0024】

図1に示すように、電界効果トランジスタ1Aは、p型Si基板2の下面にボディ電極8を形成するとともに、バッファ層3の最上層のAlN層31の膜厚を薄くすることで、アバランシェ現象により発生する正孔をバッファ層3、p-Si基板2を介してボディ電極から引き抜くことにより、耐圧の向上を可能にする。

【0025】

電界効果トランジスタ1Aのゲート電圧VgをVg=0(V)とし、ソース−ドレイン間に高いドレイン電圧Vd(例えばVd=1000V)をかけた場合、リサーフ層12のゲート電極7寄り、および、n+コンタクト層11のゲート電極7寄りに電界の集中ポイントができ、アバランシェ現象により電子・正孔対が発生する。発生した電子・正孔対の電子はドレイン電極6に逃げるが、正孔はpGaN半導体層4に溜まってしまう。

耐圧を上げるためには、この正孔を外部に引き抜く必要がある。

【0026】

従来のSi半導体による電界効果トランジスタの場合は、基板をp+Siとして下面にボディ電極を形成することにより正孔を積極的に引き抜くことができる。しかし、本発明の第1の実施の形態のIII族窒化物(GaN)を用いた電界効果トランジスタ1Aの場合、図1に示すように、p−Si基板2上にGaN半導体層4を形成するために、SiとGaNの格子定数および熱膨張係数の差を緩和するバッファ層3が形成されている。

アバランシェ現象によって発生した正孔をバッファ層3、p−Si基板2を通してボディ電極8から引き抜くために、バッファ層3の最上層のAlN層31の膜厚を薄くすることにより、トンネル効果で正孔がAlN層31を通り抜けるようになる。

【0027】

次に、図3を参照しながら、このトンネル効果による正孔の引き抜きについて説明する。

図3(a)は、p−GaN半導体層4−バッファ層3の最上層のAlN層31−その下層のGaN層32の価電子帯のエネルギ構造Evを模式的に示した図である。

p−GaN半導体層4に生じた正孔20は、p−GaN半導体層4/AlN層31界面のエネルギ障壁によりバッファ層3内には入らない。しかし、AlN層31の膜厚x1を、例えばx1=10nm以下まで薄くすると、量子力学的なトンネル効果により、正孔20はp−GaN半導体層4/AlN層31界面のエネルギ障壁を通り抜けることができる。

【0028】

しかし、実際には膜厚10nm以下のAlN層31でなくてもトンネル効果は起きる。

図3(b)は、ドレイン−ソース間にドレイン電圧Vd(例えば、Vd=1000V)をかけた場合のp−GaN半導体層4−バッファ層3の最上層のAlN層31−その下層のGaN層32の価電子帯のエネルギ構造Evを模式的に示した図である。

【0029】

ソース電極5およびボディ電極8は接地されており、ソース電極の電圧Vsおよびボディ電極8の電圧Vbは0であり、ドレイン電圧Vdのみが高電圧なので、エネルギ構造Evは傾く。

バッファ層3の最上層のAlN層の膜厚x2が、例えばx2=40nmであるとする。

図3(b)に示すように、ドレイン電圧Vdによりエネルギ構造Evが傾くため、AlN層31の価電子帯のエネルギ構造も傾き、最上層のAlN層31の膜厚がx2=40nmであっても、トンネル効果が起きるx1=10nmと等価の三角ポテンシャル部分が存在する。これにより、正孔20は最上層のAlN層31を通り抜けることができる。

【0030】

また、最上層のAlN層31を通り抜けた正孔20は、エネルギ構造Evの傾きにより、その下層にあるGaN層32およびAlN層31を容易に通り抜けることができ、p−Si基板2に達し、ボディ電極8から引き抜くことができる。

よって、最上層のAlN層31の膜厚はできるだけ薄く(1nm以上40nm以下に)形成する必要があるが、それ以外のAlN層31の膜厚はこの範囲に限らず、厚くてもよい。

【0031】

以上のように、p−Si基板2の下面にボディ電極8を設け、バッファ層3の最上位のAlN層31の膜厚を40nm以下に制御することにより、アバランシェ現象により発生した正孔を引き抜くことが可能となり、III族窒化物(GaN)電界効果トランジスタ1Aの耐圧を向上することが可能になる。

【0032】

また、p型GaN半導体層4表面のゲート電極(G)7とドレイン電極6間の下部領域に、電界集中を緩和するためのリサーフ層(RESURF層)12を備えることで、高いドレイン電圧Vd(例えばVd=1000V)をかけた場合にSiO2層9のドレイン電極6よりに集中する電界を緩和し、耐圧の向上を可能にしている。

【0033】

以上のように、本発明の第1の実施形態に係る電界効果トランジスタ1Aにより、ノーマリーオフ動作し、高耐圧の電界効果トランジスタを得ることが可能になる。

【0034】

(電界効果トランジスタ1Aの製造方法)

次に、電界効果トランジスタ1Aの製造方法の一例を説明する。

【0035】

(結晶成長)

まず、p型Si基板2上に、例えばMOCVD(Metal Organic Chemical Vapor Deposition:有機金属化学気相成長)法によりAlN層を40nm成長させる。次に、その上にGaNを200nm成長させ、さらにAlNを20nm成長させ、これを12回繰り返してバッファ層3を形成する。

【0036】

次に、MgをドープしたGaNを1.5μmの厚さに成長させ、p−GaN半導体層4を形成する。ドーパントMgの濃度は、例えば、1×1017cm−3に制御する。

次に、SiをドープしたGaNを50nmの厚さに成長させる。ドーパントSiの濃度は、例えば、7×1017cm−3に制御する。

【0037】

尚、MOCVD法に代えて、HVPE(Hydride Vapor Phase Epitaxy:ハイドライド気相成長)法、MBE(Molecular Beam Epitaxy:分子線エピタキシー)法等を用いてもよい。

また、成長用基板として、例えば、SiC、ZrB2等を用いてもよい。

また、ドーパントは、Mgに代えてBeやZn等を、Siに代えてC等を使用してもよい。

【0038】

(素子分離)

次に、p−GaN半導体層4の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施す。

次に、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)やRIE(Reactive Ion Etching:反応性イオンエッチング)等のドライエッチング装置を用いて、p−GaN半導体層4を深さ200nmエッチングし、フォトレジストをアセトンにより除去し、素子分離を完了する。

【0039】

(ゲート酸化膜堆積)

次に、素子分離を完了したp−GaN半導体層4上の全面にPECVD(Plasma Enhanced Chemical Vapor Deposition:プラズマ化学気相成長)法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成する。

【0040】

(オーミック電極形成)

次に、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用の開口部を形成する。これは、素子分離の場合と同様のフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって形成される。

2つの開口部はp−GaN半導体層4が露出しており、このp−GaN半導体層4上に例えばTi/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成する。

尚、電極の素材は、オーミック接合が実現できるならばTi/Al以外であってもよい。

【0041】

(ゲート電極形成)

次にゲート電極7を形成する。

すなわち、まず、電極材料であるpoly−Si(poly−crystalline

Si)をLPCVD(Low Pressure CVD:低圧CVD)やスパッタ法等により素子上面全面に堆積させる。

次に、素子をPOCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pのドーピングを行う。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施す。これによりゲート電極7が形成される。

【0042】

尚、poly−SiへのPドーピングは、poly−Si上にPを蒸着し、熱拡散させて行ってもよい。

また、ゲート電極としてAu、Pt、Ni等を用いてもよい。

【0043】

(ボディ電極形成)

ボディ電極8として、例えば、AuGa合金を使用し、p−Si基板2の下面に蒸着する。

【0044】

以上の製造工程により、図1に示したノーマリーオフ動作、高耐圧のIII族窒化物(GaN)電界効果トランジスタ1Aが製造される。

【0045】

(第2の実施形態)

図2は、第2の実施形態に係る電界効果トランジスタ1Bの概略構成を示す断面図である。III族窒化物半導体電界効果トランジスタ1Bの場合、ボディ電極8はIII族窒化物半導体電界効果トランジスタ1Bの上面に形成される。

【0046】

図2に示すように、電界効果トランジスタ1Bは、基板にサファイア基板21を用い、サファイア基板21上にp型GaNからなるp型GaN半導体層4が形成される。

さらに、p型GaN半導体層4の上部、ソース電極(S)5およびドレイン電極(D)6、ボディ電極8の下部にはAlGaN層13が形成される。ここで、このAlGaN層31の膜厚は20nm程度である。AlGaNのバンドギャップはGaNより大きいが、膜厚が薄いので、金属電極からの電子をトンネル効果によりP−GaNへ透過し、電極-AlGaN層界面、AlGaN層13、AlGaN層13-P−GaN層4界面の抵抗を小さく抑えることを可能とし、低オン抵抗により大電流を得ることが可能になる。

【0047】

AlGaN層13上に、ソース電極5、ドレイン電極6、ボディ電極8が直接形成される。

一方、AlGaN層13上のソース電極5、ドレイン電極6、ボディ電極8以外の部分にはゲート酸化膜SiO2が形成され、ゲート部分はゲートリセス構造によりp−GaN半導体層4上のSiO2上に形成される。

ゲート電極とドレイン電極間のAlGaN/GaN領域はリサーフ層の働きをし、所定の抵抗を有することから電圧降下が起こり、ゲート酸化膜SiO29に発生する電界を緩和する効果がある。

【0048】

次に、図2に示した構成を持つ第2の実施形態の電界効果トランジスタ1Bの作用効果を説明する。

【0049】

図2に示すように、電界効果トランジスタ1Bは、p型GaN半導体層4上のAlGaN層13上にボディ電極8を形成することにより、アバランシェ現象により発生する正孔を引き抜き、耐圧の向上を可能にする。

【0050】

電界効果トランジスタ1Bのゲート電圧VgをVg=0(V)とし、ソース−ドレイン間に高いドレイン電圧Vd(例えばVd=1000V)をかけた場合、p−GaN半導体層4内のドレイン電極6左部分と、ゲート電極6右部分に電界の集中ポイントができ、アバランシェ現象により電子・正孔対が発生する。発生した電子・正孔対の電子はドレイン電極6に逃げる。

【0051】

正孔は、AlGaN層13上にボディ電極8を形成し、ボディ電極を設置することにより、pGaN半導体層4のドレイン電極6側からボディ電極8側に向かってエネルギ傾斜ができるため、正孔はボディ電極側に流れ、AlGaN層13の膜厚が薄いことによりトンネル効果によりボディ電極8に向かって透過し、引き抜かれる。

このように、アバランシェ現象により生じた正孔をボディ電極8から引き抜くことが可能であり、耐圧を向上することができる。

【0052】

以上のように、本発明の第2の実施形態の電界効果トランジスタ1Bにより、ノーマリーオフ動作し、高耐圧、高電流の電界効果トランジスタを得ることが可能になる。

【0053】

(電界効果トランジスタ1Bの製造方法)

次に、第2の実施形態の電界効果トランジスタ1Bの製造方法の一例を説明する。

【0054】

(結晶成長)

まず、サファイア基板21の基板温度を1000℃とし、例えばMOCVD法により基板21にGaN層4を1μm成長させる。

次に、基板温度を1050℃に昇温し、MgドープGaNを2μm成長させる。ドーパントにはMgを用い、Mg濃度を1×1017cm−3に制御する。

次に、AlGaN(Al組成25%)を25nm成長させる。これによりAlGaN層13が形成される。

【0055】

尚、MOCVD法の代わりに、HVPE法、MBE法等を用いてもよい。

また、成長用基板として、例えば、SiC、ZrB2等を用いてもよい。

また、ドーパントは、Mgに代えてBeやZn、C等を使用してもよい。

【0056】

(素子分離)

次に、AlGaN層13の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施す。

次に、ICP、RIE等のドライエッチング装置を用いて、AlGaN層13およびMgドープのp−GaN半導体層4を深さ200nmエッチングし、フォトレジストをアセトンにより除去し、素子分離を完了する。

【0057】

(ゲートリセス形成)

次に、ゲートを形成するためのリセス構造を形成する。

すなわち、まず、PCVD(Plasma CVD)法により、p−GaN層4上にSiO2を300nm堆積する。

次に、ゲート領域のSiO2をBHF(Buffer HydrogenFluoride)によりエッチングし開口する。

【0058】

次に、ICPドライエッチング装置によってAlGaN層を完全にエッチングし、その後、pGaN層を100nmエッチングする。

次に、p−GaN上のSiO2をBHFによって全て除去する。

【0059】

(ゲート酸化膜堆積)

次に、素子分離を完了した半導体層4、13上の全面にPECVD法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成する。

【0060】

(オーミック電極形成)

次に、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用、ボディ電極8用の開口部を形成する。これは、素子分離の場合と同様のフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって形成される。

【0061】

3つの開口部はAlGaN半導体層13が露出しており、ソース電極5の領域およびドレイン電極6の領域には、例えばTi/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成する。

尚、電極の素材は、オーミック接合が実現できるならばTi/Al以外であってもよい。

また、ボディ電極8の領域には、例えば、ボディ電極としてNi/Auを蒸着させる。

【0062】

(ゲート形成)

次に、ゲート電極7を形成する。

すなわち、まず、電極材料であるpoly−SiをLPCVD法やスパッタ法等により素子上面全面に堆積させる。

次に、素子をPOCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pのドーピングを行う。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施す。これによりゲート電極7が形成される。

【0063】

尚、poly−SiへのPドーピングは、poly−Si上にPを蒸着し、熱拡散させて行ってもよい。

また、ゲート電極としてAu、Pt、Ni等を用いてもよい。

【0064】

以上の製造工程により、図2に示したIII族窒化物(GaN)電界効果トランジスタ1Bが製造される。

【実施例】

【0065】

以下、本発明の第2の実施の形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの実施例と比較例を用いて耐圧の実験結果を説明する。

[実施例]第2の実施の形態に対応

1.結晶成長

サファイア基板21の基板温度を1000℃とし、例えばMOCVD法により基板21にGaN層4を1μm成長させ、次に、基板温度を1050℃に昇温し、MgドープGaNを2μm成長させた。ドーパントにはMgを用い、Mg濃度を1×1017cm−3とした。

次に、AlGaN(Al組成25%)を25nm成長させ、AlGaN層13を形成した。

【0066】

2.素子分離

次に、AlGaN層13の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施し、ドライエッチング装置を用いて、AlGaN層13およびMgドープのp−GaN半導体層4を深さ200nmエッチングした。フォトレジストをアセトンにより除去した。

【0067】

3.ゲートリセス形成

次に、ゲート用のリセス構造を形成するために、PCVD法により、p−GaN層4上にSiO2を300nm堆積し、ゲート領域のSiO2をBHFによりエッチングし開口した。

次に、ICPドライエッチング装置によってAlGaN層を完全にエッチングし、その後、pGaN層を100nmエッチングし、その後、p−GaN上のSiO2をBHFによって全て除去した。

【0068】

4.ゲート酸化膜堆積

次に、素子分離を完了したp−GaN半導体4上の全面にPECVD法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成した。

【0069】

5.オーミック電極形成

次に、フォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用、ボディ電極8用の開口部を形成した。

ソース電極5の領域およびドレイン電極6の領域には、Ti/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成し、ボディ電極8の領域には、ボディ電極としてNi/Auを蒸着させた。

【0070】

6.ゲート形成

次に、電極材料であるpoly−SiをLPCVD法やスパッタ法等により素子上面全面に堆積させ、POCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pをドーピングした。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施し、ゲート電極7を形成した。

【0071】

以上のIII族窒化物(GaN)を用いた電界効果トランジスタ1B製造において、チャネル長等をさまざまな値にした32種類のIII族窒化物(GaN)電界効果トランジスタを製造し、耐圧を測定した。

【0072】

[比較例]

実施例に対応する電界効果トランジスタ1Bで、ボディ電極8のない電界効果トランジスタを製造した。

すなわち、実施例と同様の方法で、結晶成長、素子分離、ゲートリセス形成、ゲート酸化膜堆積の各工程を実施した。

【0073】

次に、オーミック電極形成の工程において、ボディ電極8を除いて、実施例と同様の方法でソース電極5およびドレイン電極6を形成した。

最後に、実施例と同様の方法で、ゲート電極7を形成した。

【0074】

また、実施例と同様に、チャネル長等をさまざまな値にした32種類のIII族窒化物(GaN)を用いた電界効果トランジスタを製造し、耐圧を測定した。

【0075】

図4は、実施例と比較例の測定結果を示す図である。

図4(a)は、製造した実施例(ボディ電極あり)および比較例(ボディ電極なし)の各電界効果トランジスタの耐圧を示す図である。

条件によって、ボディ電極がないもの(比較例)の耐圧が高い場合があるが、多くの条件でボディ電極を設けたもの(実施例)で高い耐圧が得られ、ボディ電極を設けることによる耐圧の向上が確認された。

特にボディ電極がある場合には、条件によって約1350Vの高耐圧が得られた。

【0076】

図4(b)は、製造した実施例(ボディ電極あり)および比較例(ボディ電極なし)の32種類の電界効果トランジスタの耐圧の幅と中央値(メディアン)を示す図である。

同図に示すように、ボディ電極なし(比較例)の場合、中央値が約430V、最高耐圧は約750Vであったのに対し、ボディ電極あり(実施例)の場合、中央値が約500V、最高耐圧は約1350Vだった。

【0077】

以上に示したように、ボディ電極を設けることにより、高耐圧のIII族窒化物(GaN)を用いた電界効果トランジスタが実現可能になる。また、本実施の形態の電界効果トランジスタ1Aおよび1Bにより、ノーマリーオフ動作の高耐圧、高電流の電界効果トランジスタを得ることが可能になる。

【0078】

尚、本発明は、前述した実施の形態に限定されるものではなく、種々の改変が可能であり、それらも、本発明の技術範囲に含まれる。

【符号の説明】

【0079】

1A、1B………電界効果トランジスタ

2………p−Si基板

3………バッファ層

4………p−GaN半導体層

5………ソース電極(S)

6………ドレイン電極(D)

7………ゲート電極(G)

8………ボディ電極

9………SiO2ゲート酸化膜

10、11………n+コンタクト層

12………リサーフ(RESURF)層

13………AlGaN層

20………正孔

21………サファイア基板

31………AlN層

32………GaN層

【技術分野】

【0001】

本発明は、III族窒化物半導体を使用した電界効果トランジスタに関し、更に詳しくは、ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタに関する。

【背景技術】

【0002】

GaNなどのIII族窒化物半導体は、材料の本質的特性から、シリコン半導体に比べ耐圧が高く、高電流密度が得られ、高温動作が可能なことからパワーデバイスとして期待されている。

【0003】

III族窒化物を用いた電界効果トランジスタとしては、例えば、GaN系MOSFET(Metal Oxide Silicon Field Effect Transistor)(例えば、非特許文献1)やAlGaN/GaN系HFET(Hetero-junction Field Effect Transistor)(例えば、非特許文献2)が提案されている。

【0004】

これらGaN系の電界効果トランジスタは、Si半導体や、従来のGaAs、InPなどのIII族化合物半導体よりも高い絶縁破壊電界や飽和移動度を有することから、特にパワーデバイスに適している。

【0005】

また、GaN系MOSFETはノーマリーオフを容易に実現できるため、電源回路に不調が起こった際、安全な方向に進む、いわゆるフェールセーフの面からもパワーデバイスに適している。

非特許文献1に示されるGaN系MOSFETは、半導体層に表面電界を緩和するリサーフ(RESURF:REduced SURface Field)層を設けることにより、940Vの耐圧を実現している。

【0006】

また、非特許文献2に示されるAlGaN/GaN系HFETは、半導体層として、ノンドープのAlGaNキャリア走行層上に、キャリア走行層よりも格子定数の小さいノンドープまたはn型のAlGaN障壁層と、キャリア走行層と格子定数の等しいAlGaN閾値制御層と、キャリア走行層よりも格子定数の小さいノンドープまたはn型のAlGaNキャリア誘起層を順に積層した構造であり、通常、AlGaN系HFETではノーマリーオフ動作が難しいが、キャリア誘起層全部と障壁層の一部を除去したリセス構造中にゲート電極を形成し、障壁層の膜厚を臨界膜厚以下にすることによりノーマリーオフ動作を実現するとともに、障壁層の膜厚を原子層レベルに制御することにより、閾値電圧のばらつきを小さく抑えることを可能にしている。また、キャリア誘起層を設けたことによりオン抵抗を低減している。

【0007】

Si系のパワーデバイスの場合は、高い耐圧を実現するために、p+層にボディ電極を配置する方法が知られている。このボディ電極から、ドレイン電圧を高くしたときに起きるアバランシェ現象で発生する電子・正孔対のうちの正孔を引き抜くことで、耐圧を向上することができる。しかし、GaNの場合は、高濃度のp+層をイオン注入法などにより選択的に形成することが非常に難しい。イオン注入でp層を形成した報告では、正孔のシートキャリア密度で7×1012cm−2程度である(非特許文献3)。

【先行技術文献】

【非特許文献】

【0008】

【非特許文献1】W.Huang,T.Khan,T.P.Chow,“Enhancement−Mode n−Channel GaN MOSFETs on p and n− GaN/Sapphire Substrates,”18th International Symposium on Power Semiconductor Devices and ICs(ISPSD) 2006(Italy),10−1.

【非特許文献2】M.Kuraguchi et al.,“Normally−off GaN−MISFET with well−controlled threshold voltage,”International Workshop on Nitride Semiconductors 2006(IWN2006),Oct.22−27,2006,Kyoto,Japan,WeED1−4.

【非特許文献3】Wilson R.G. et al.,“Redistribution and activation of implanted S,Se,Te,Be,Mg,and C in GaN,”Journal of Vacuum Science and Technology,A17,1226(1999).

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、パワーデバイスでは、耐圧をより高く、また、ゲート電極の閾値電圧をより高くし、ノーマリーオフ動作を可能する必要がある。例えば、自動車用電源回路等に適用するためには、約1200Vのドレイン耐圧と+3V以上の閾値電圧が要求される。

非特許文献1のGaN系MOSFETは、940Vの耐圧を実現しているが、自動車用電源回路の用途では更に高い耐圧が必要という問題がある。

【0010】

また、非特許文献2のAlGaN/GaN系HFETは、ノーマリーオフ動作を実現し、閾値電圧をばらつき少なく制御することが可能であるが、閾値電圧が+1V程度であり、パワーデバイスの閾値電圧として必要な+3Vを満たさないという問題がある。

【0011】

また、Si系パワーデバイスと同様にp+層に電極を配置し、正孔を引き抜く方法をGaN系パワーデバイスで実現するためには、1015cm−2レベルのシートキャリア密度のp+層を形成する必要があるが、GaNで形成可能なp+層のシートキャリア密度は、非特許文献3に示されるように7×1012cm−2程度と低すぎるという問題がある。また、高濃度のp+層を選択的に形成することは更に難しい。

【0012】

本発明は、このような問題に鑑みてなされたもので、その目的とするところは、ノーマリーオフ動作、高耐圧、大電流を実現するIII族窒化物半導体電界効果トランジスタを提供することである。

【課題を解決するための手段】

【0013】

前述した課題を解決するための本発明は、III族窒化物半導体を用いた電界効果トランジスタにおいて、前記III族窒化物半導体の上面または下面のいずれかにボディ電極が形成されることを特徴とする電界効果トランジスタである。

この電界効果トランジスタは、半導体層として、少なくともp型GaN層を1層含む。これにより、ノーマリーオフ動作を容易に実現することが可能になる。

【0014】

ここで、電界効果トランジスタの下面にボディ電極を形成する場合、半導体基板をp型シリコンとすることが好ましい。

また、前記半導体基板と前記半導体層の間にバッファ層が形成され、前記バッファ層は複数の層で構成され、前記バッファ層の各層は、AlNまたは/およびGaNまたは/およびBN、または、AlN、GaN、BNを組み合わせた化合物よりなることが好ましい。

さらに、前記バッファ層の最上層はAlNであり、1nm以上40nm以下であることが好ましい。

【0015】

このように、p型シリコン基板上に多層から成るバッファ層を介してp型GaN層を少なくとも1層含む半導体層を設け、p型シリコン基板の下面にボディ電極を配置することにより、アバランシェ発生時の正孔をこのボディ電極から引き抜くことが可能になり、耐圧を向上することが可能になる。

【0016】

一方、電界効果トランジスタの上面にボディ電極を形成する場合、サファイア基板上に形成したp型GaN層上にAlGaN層が形成され、AlGaN層上に直接ボディ電極が形成されることが望ましい。

このように、AlGaN層上に直接ボディ電極を形成することにより、アバランシェ発生時の正孔をこのボディ電極から引き抜くことが可能になり、耐圧を向上することが可能になる。

【発明の効果】

【0017】

本発明によれば、ノーマリーオフ動作、高耐圧、大電流を実現する電界効果トランジスタを提供することが可能になる。

【図面の簡単な説明】

【0018】

【図1】本発明の第1の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Aの概略構成を示す断面図

【図2】本発明の第2の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの概略構成を示す断面図

【図3】トンネル効果による正孔の引き抜き方法の説明図

【図4】第2の実施形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの耐圧の測定結果を示す図

【発明を実施するための形態】

【0019】

以下、図面に基づいて本発明の好適な実施形態について詳細に説明する。

(第1の実施形態)

図1は、本発明の第1の実施形態に係る電界効果トランジスタ1Aの概略構成を示す断面図である。III族窒化物としてGaNとAlNを使用する。

【0020】

この電界効果トランジスタ1Aは、p型Si基板2を半導体基板とし、その上にバッファ層3を介してp型GaN4からなる半導体層を備える。p型Si基板2の下面にボディ電極8が設けられる。

また、p型GaN半導体層4表面のソース電極(S)5下およびドレイン電極(D)6下の領域にはコンタクト層であるn+層10および11が形成される。また、p型GaN半導体層4表面のゲート電極(G)7とドレイン電極6間の下部領域には、電界集中を緩和するためのリサーフ層(RESURF層)12を備える。またp型GaN半導体層4上のソース電極5およびゲート電極6間の領域にはゲート酸化膜であるSiO29が形成され、SiO29上にゲート電極7が設けられる。

【0021】

バッファ層3は、例えば、AlN層31とGaN層32が交互に複数層形成された積層構造であり、p型Si基板2上にp型GaN半導体層4を形成する際のSiとGaNの格子定数および熱膨張係数の差を緩和する役目を果たす。

バッファ層3としては、図1に示したAlN、GaNの他、BNや、これらのIII族窒化物の組み合わせによる化合物、例えば、AlGaNやBGaN等を使用することが可能である。

【0022】

バッファ層3の最上層はAlN層31であり、この最上層のAlN層31はバッファ層3の他のAlN層31よりも薄く形成する。すなわち、最上層のAlN層の膜厚は1nm以上40nm以下にする。

後述するが、この最上層のAlN層を薄くし、p型Si基板の下面にボディ電極を設けることにより、アバランシェ現象によりp型GaN半導体層4あるいはリサーフ層12内に生じる正孔をトンネル効果によりバッファ層3を透過させ引き抜くことが可能になる。これにより、耐圧の向上が可能になる。

【0023】

次に、図1に示した構成を持つ第1の実施形態の電界効果トランジスタ1Aの作用効果を説明する。

【0024】

図1に示すように、電界効果トランジスタ1Aは、p型Si基板2の下面にボディ電極8を形成するとともに、バッファ層3の最上層のAlN層31の膜厚を薄くすることで、アバランシェ現象により発生する正孔をバッファ層3、p-Si基板2を介してボディ電極から引き抜くことにより、耐圧の向上を可能にする。

【0025】

電界効果トランジスタ1Aのゲート電圧VgをVg=0(V)とし、ソース−ドレイン間に高いドレイン電圧Vd(例えばVd=1000V)をかけた場合、リサーフ層12のゲート電極7寄り、および、n+コンタクト層11のゲート電極7寄りに電界の集中ポイントができ、アバランシェ現象により電子・正孔対が発生する。発生した電子・正孔対の電子はドレイン電極6に逃げるが、正孔はpGaN半導体層4に溜まってしまう。

耐圧を上げるためには、この正孔を外部に引き抜く必要がある。

【0026】

従来のSi半導体による電界効果トランジスタの場合は、基板をp+Siとして下面にボディ電極を形成することにより正孔を積極的に引き抜くことができる。しかし、本発明の第1の実施の形態のIII族窒化物(GaN)を用いた電界効果トランジスタ1Aの場合、図1に示すように、p−Si基板2上にGaN半導体層4を形成するために、SiとGaNの格子定数および熱膨張係数の差を緩和するバッファ層3が形成されている。

アバランシェ現象によって発生した正孔をバッファ層3、p−Si基板2を通してボディ電極8から引き抜くために、バッファ層3の最上層のAlN層31の膜厚を薄くすることにより、トンネル効果で正孔がAlN層31を通り抜けるようになる。

【0027】

次に、図3を参照しながら、このトンネル効果による正孔の引き抜きについて説明する。

図3(a)は、p−GaN半導体層4−バッファ層3の最上層のAlN層31−その下層のGaN層32の価電子帯のエネルギ構造Evを模式的に示した図である。

p−GaN半導体層4に生じた正孔20は、p−GaN半導体層4/AlN層31界面のエネルギ障壁によりバッファ層3内には入らない。しかし、AlN層31の膜厚x1を、例えばx1=10nm以下まで薄くすると、量子力学的なトンネル効果により、正孔20はp−GaN半導体層4/AlN層31界面のエネルギ障壁を通り抜けることができる。

【0028】

しかし、実際には膜厚10nm以下のAlN層31でなくてもトンネル効果は起きる。

図3(b)は、ドレイン−ソース間にドレイン電圧Vd(例えば、Vd=1000V)をかけた場合のp−GaN半導体層4−バッファ層3の最上層のAlN層31−その下層のGaN層32の価電子帯のエネルギ構造Evを模式的に示した図である。

【0029】

ソース電極5およびボディ電極8は接地されており、ソース電極の電圧Vsおよびボディ電極8の電圧Vbは0であり、ドレイン電圧Vdのみが高電圧なので、エネルギ構造Evは傾く。

バッファ層3の最上層のAlN層の膜厚x2が、例えばx2=40nmであるとする。

図3(b)に示すように、ドレイン電圧Vdによりエネルギ構造Evが傾くため、AlN層31の価電子帯のエネルギ構造も傾き、最上層のAlN層31の膜厚がx2=40nmであっても、トンネル効果が起きるx1=10nmと等価の三角ポテンシャル部分が存在する。これにより、正孔20は最上層のAlN層31を通り抜けることができる。

【0030】

また、最上層のAlN層31を通り抜けた正孔20は、エネルギ構造Evの傾きにより、その下層にあるGaN層32およびAlN層31を容易に通り抜けることができ、p−Si基板2に達し、ボディ電極8から引き抜くことができる。

よって、最上層のAlN層31の膜厚はできるだけ薄く(1nm以上40nm以下に)形成する必要があるが、それ以外のAlN層31の膜厚はこの範囲に限らず、厚くてもよい。

【0031】

以上のように、p−Si基板2の下面にボディ電極8を設け、バッファ層3の最上位のAlN層31の膜厚を40nm以下に制御することにより、アバランシェ現象により発生した正孔を引き抜くことが可能となり、III族窒化物(GaN)電界効果トランジスタ1Aの耐圧を向上することが可能になる。

【0032】

また、p型GaN半導体層4表面のゲート電極(G)7とドレイン電極6間の下部領域に、電界集中を緩和するためのリサーフ層(RESURF層)12を備えることで、高いドレイン電圧Vd(例えばVd=1000V)をかけた場合にSiO2層9のドレイン電極6よりに集中する電界を緩和し、耐圧の向上を可能にしている。

【0033】

以上のように、本発明の第1の実施形態に係る電界効果トランジスタ1Aにより、ノーマリーオフ動作し、高耐圧の電界効果トランジスタを得ることが可能になる。

【0034】

(電界効果トランジスタ1Aの製造方法)

次に、電界効果トランジスタ1Aの製造方法の一例を説明する。

【0035】

(結晶成長)

まず、p型Si基板2上に、例えばMOCVD(Metal Organic Chemical Vapor Deposition:有機金属化学気相成長)法によりAlN層を40nm成長させる。次に、その上にGaNを200nm成長させ、さらにAlNを20nm成長させ、これを12回繰り返してバッファ層3を形成する。

【0036】

次に、MgをドープしたGaNを1.5μmの厚さに成長させ、p−GaN半導体層4を形成する。ドーパントMgの濃度は、例えば、1×1017cm−3に制御する。

次に、SiをドープしたGaNを50nmの厚さに成長させる。ドーパントSiの濃度は、例えば、7×1017cm−3に制御する。

【0037】

尚、MOCVD法に代えて、HVPE(Hydride Vapor Phase Epitaxy:ハイドライド気相成長)法、MBE(Molecular Beam Epitaxy:分子線エピタキシー)法等を用いてもよい。

また、成長用基板として、例えば、SiC、ZrB2等を用いてもよい。

また、ドーパントは、Mgに代えてBeやZn等を、Siに代えてC等を使用してもよい。

【0038】

(素子分離)

次に、p−GaN半導体層4の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施す。

次に、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)やRIE(Reactive Ion Etching:反応性イオンエッチング)等のドライエッチング装置を用いて、p−GaN半導体層4を深さ200nmエッチングし、フォトレジストをアセトンにより除去し、素子分離を完了する。

【0039】

(ゲート酸化膜堆積)

次に、素子分離を完了したp−GaN半導体層4上の全面にPECVD(Plasma Enhanced Chemical Vapor Deposition:プラズマ化学気相成長)法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成する。

【0040】

(オーミック電極形成)

次に、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用の開口部を形成する。これは、素子分離の場合と同様のフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって形成される。

2つの開口部はp−GaN半導体層4が露出しており、このp−GaN半導体層4上に例えばTi/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成する。

尚、電極の素材は、オーミック接合が実現できるならばTi/Al以外であってもよい。

【0041】

(ゲート電極形成)

次にゲート電極7を形成する。

すなわち、まず、電極材料であるpoly−Si(poly−crystalline

Si)をLPCVD(Low Pressure CVD:低圧CVD)やスパッタ法等により素子上面全面に堆積させる。

次に、素子をPOCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pのドーピングを行う。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施す。これによりゲート電極7が形成される。

【0042】

尚、poly−SiへのPドーピングは、poly−Si上にPを蒸着し、熱拡散させて行ってもよい。

また、ゲート電極としてAu、Pt、Ni等を用いてもよい。

【0043】

(ボディ電極形成)

ボディ電極8として、例えば、AuGa合金を使用し、p−Si基板2の下面に蒸着する。

【0044】

以上の製造工程により、図1に示したノーマリーオフ動作、高耐圧のIII族窒化物(GaN)電界効果トランジスタ1Aが製造される。

【0045】

(第2の実施形態)

図2は、第2の実施形態に係る電界効果トランジスタ1Bの概略構成を示す断面図である。III族窒化物半導体電界効果トランジスタ1Bの場合、ボディ電極8はIII族窒化物半導体電界効果トランジスタ1Bの上面に形成される。

【0046】

図2に示すように、電界効果トランジスタ1Bは、基板にサファイア基板21を用い、サファイア基板21上にp型GaNからなるp型GaN半導体層4が形成される。

さらに、p型GaN半導体層4の上部、ソース電極(S)5およびドレイン電極(D)6、ボディ電極8の下部にはAlGaN層13が形成される。ここで、このAlGaN層31の膜厚は20nm程度である。AlGaNのバンドギャップはGaNより大きいが、膜厚が薄いので、金属電極からの電子をトンネル効果によりP−GaNへ透過し、電極-AlGaN層界面、AlGaN層13、AlGaN層13-P−GaN層4界面の抵抗を小さく抑えることを可能とし、低オン抵抗により大電流を得ることが可能になる。

【0047】

AlGaN層13上に、ソース電極5、ドレイン電極6、ボディ電極8が直接形成される。

一方、AlGaN層13上のソース電極5、ドレイン電極6、ボディ電極8以外の部分にはゲート酸化膜SiO2が形成され、ゲート部分はゲートリセス構造によりp−GaN半導体層4上のSiO2上に形成される。

ゲート電極とドレイン電極間のAlGaN/GaN領域はリサーフ層の働きをし、所定の抵抗を有することから電圧降下が起こり、ゲート酸化膜SiO29に発生する電界を緩和する効果がある。

【0048】

次に、図2に示した構成を持つ第2の実施形態の電界効果トランジスタ1Bの作用効果を説明する。

【0049】

図2に示すように、電界効果トランジスタ1Bは、p型GaN半導体層4上のAlGaN層13上にボディ電極8を形成することにより、アバランシェ現象により発生する正孔を引き抜き、耐圧の向上を可能にする。

【0050】

電界効果トランジスタ1Bのゲート電圧VgをVg=0(V)とし、ソース−ドレイン間に高いドレイン電圧Vd(例えばVd=1000V)をかけた場合、p−GaN半導体層4内のドレイン電極6左部分と、ゲート電極6右部分に電界の集中ポイントができ、アバランシェ現象により電子・正孔対が発生する。発生した電子・正孔対の電子はドレイン電極6に逃げる。

【0051】

正孔は、AlGaN層13上にボディ電極8を形成し、ボディ電極を設置することにより、pGaN半導体層4のドレイン電極6側からボディ電極8側に向かってエネルギ傾斜ができるため、正孔はボディ電極側に流れ、AlGaN層13の膜厚が薄いことによりトンネル効果によりボディ電極8に向かって透過し、引き抜かれる。

このように、アバランシェ現象により生じた正孔をボディ電極8から引き抜くことが可能であり、耐圧を向上することができる。

【0052】

以上のように、本発明の第2の実施形態の電界効果トランジスタ1Bにより、ノーマリーオフ動作し、高耐圧、高電流の電界効果トランジスタを得ることが可能になる。

【0053】

(電界効果トランジスタ1Bの製造方法)

次に、第2の実施形態の電界効果トランジスタ1Bの製造方法の一例を説明する。

【0054】

(結晶成長)

まず、サファイア基板21の基板温度を1000℃とし、例えばMOCVD法により基板21にGaN層4を1μm成長させる。

次に、基板温度を1050℃に昇温し、MgドープGaNを2μm成長させる。ドーパントにはMgを用い、Mg濃度を1×1017cm−3に制御する。

次に、AlGaN(Al組成25%)を25nm成長させる。これによりAlGaN層13が形成される。

【0055】

尚、MOCVD法の代わりに、HVPE法、MBE法等を用いてもよい。

また、成長用基板として、例えば、SiC、ZrB2等を用いてもよい。

また、ドーパントは、Mgに代えてBeやZn、C等を使用してもよい。

【0056】

(素子分離)

次に、AlGaN層13の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施す。

次に、ICP、RIE等のドライエッチング装置を用いて、AlGaN層13およびMgドープのp−GaN半導体層4を深さ200nmエッチングし、フォトレジストをアセトンにより除去し、素子分離を完了する。

【0057】

(ゲートリセス形成)

次に、ゲートを形成するためのリセス構造を形成する。

すなわち、まず、PCVD(Plasma CVD)法により、p−GaN層4上にSiO2を300nm堆積する。

次に、ゲート領域のSiO2をBHF(Buffer HydrogenFluoride)によりエッチングし開口する。

【0058】

次に、ICPドライエッチング装置によってAlGaN層を完全にエッチングし、その後、pGaN層を100nmエッチングする。

次に、p−GaN上のSiO2をBHFによって全て除去する。

【0059】

(ゲート酸化膜堆積)

次に、素子分離を完了した半導体層4、13上の全面にPECVD法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成する。

【0060】

(オーミック電極形成)

次に、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用、ボディ電極8用の開口部を形成する。これは、素子分離の場合と同様のフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって形成される。

【0061】

3つの開口部はAlGaN半導体層13が露出しており、ソース電極5の領域およびドレイン電極6の領域には、例えばTi/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成する。

尚、電極の素材は、オーミック接合が実現できるならばTi/Al以外であってもよい。

また、ボディ電極8の領域には、例えば、ボディ電極としてNi/Auを蒸着させる。

【0062】

(ゲート形成)

次に、ゲート電極7を形成する。

すなわち、まず、電極材料であるpoly−SiをLPCVD法やスパッタ法等により素子上面全面に堆積させる。

次に、素子をPOCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pのドーピングを行う。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施す。これによりゲート電極7が形成される。

【0063】

尚、poly−SiへのPドーピングは、poly−Si上にPを蒸着し、熱拡散させて行ってもよい。

また、ゲート電極としてAu、Pt、Ni等を用いてもよい。

【0064】

以上の製造工程により、図2に示したIII族窒化物(GaN)電界効果トランジスタ1Bが製造される。

【実施例】

【0065】

以下、本発明の第2の実施の形態に係るIII族窒化物(GaN)を用いた電界効果トランジスタ1Bの実施例と比較例を用いて耐圧の実験結果を説明する。

[実施例]第2の実施の形態に対応

1.結晶成長

サファイア基板21の基板温度を1000℃とし、例えばMOCVD法により基板21にGaN層4を1μm成長させ、次に、基板温度を1050℃に昇温し、MgドープGaNを2μm成長させた。ドーパントにはMgを用い、Mg濃度を1×1017cm−3とした。

次に、AlGaN(Al組成25%)を25nm成長させ、AlGaN層13を形成した。

【0066】

2.素子分離

次に、AlGaN層13の表面にフォトレジストを塗布し、露光・現像工程を経て、素子分離用のパターニングを施し、ドライエッチング装置を用いて、AlGaN層13およびMgドープのp−GaN半導体層4を深さ200nmエッチングした。フォトレジストをアセトンにより除去した。

【0067】

3.ゲートリセス形成

次に、ゲート用のリセス構造を形成するために、PCVD法により、p−GaN層4上にSiO2を300nm堆積し、ゲート領域のSiO2をBHFによりエッチングし開口した。

次に、ICPドライエッチング装置によってAlGaN層を完全にエッチングし、その後、pGaN層を100nmエッチングし、その後、p−GaN上のSiO2をBHFによって全て除去した。

【0068】

4.ゲート酸化膜堆積

次に、素子分離を完了したp−GaN半導体4上の全面にPECVD法によりSiO2を60nm堆積させ、ゲート酸化膜であるSiO2層9を形成した。

【0069】

5.オーミック電極形成

次に、フォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程によって、ゲート酸化膜SiO29にソース電極5およびドレイン電極6用、ボディ電極8用の開口部を形成した。

ソース電極5の領域およびドレイン電極6の領域には、Ti/Alから成るオーミック電極を、それぞれ、ソース電極5およびドレイン電極6として形成し、ボディ電極8の領域には、ボディ電極としてNi/Auを蒸着させた。

【0070】

6.ゲート形成

次に、電極材料であるpoly−SiをLPCVD法やスパッタ法等により素子上面全面に堆積させ、POCl3ガスが封入された熱拡散炉で900℃、20分間熱処理し、不純物Pをドーピングした。

次にPドープ済みのpoly−Siに対して、ソース電極5−ドレイン電極6間のゲート部分にPドープpoly−Siが残るようにフォトレジスト塗布・露光・現像・エッチング・フォトレジスト除去の工程を施し、ゲート電極7を形成した。

【0071】

以上のIII族窒化物(GaN)を用いた電界効果トランジスタ1B製造において、チャネル長等をさまざまな値にした32種類のIII族窒化物(GaN)電界効果トランジスタを製造し、耐圧を測定した。

【0072】

[比較例]

実施例に対応する電界効果トランジスタ1Bで、ボディ電極8のない電界効果トランジスタを製造した。

すなわち、実施例と同様の方法で、結晶成長、素子分離、ゲートリセス形成、ゲート酸化膜堆積の各工程を実施した。

【0073】

次に、オーミック電極形成の工程において、ボディ電極8を除いて、実施例と同様の方法でソース電極5およびドレイン電極6を形成した。

最後に、実施例と同様の方法で、ゲート電極7を形成した。

【0074】

また、実施例と同様に、チャネル長等をさまざまな値にした32種類のIII族窒化物(GaN)を用いた電界効果トランジスタを製造し、耐圧を測定した。

【0075】

図4は、実施例と比較例の測定結果を示す図である。

図4(a)は、製造した実施例(ボディ電極あり)および比較例(ボディ電極なし)の各電界効果トランジスタの耐圧を示す図である。

条件によって、ボディ電極がないもの(比較例)の耐圧が高い場合があるが、多くの条件でボディ電極を設けたもの(実施例)で高い耐圧が得られ、ボディ電極を設けることによる耐圧の向上が確認された。

特にボディ電極がある場合には、条件によって約1350Vの高耐圧が得られた。

【0076】

図4(b)は、製造した実施例(ボディ電極あり)および比較例(ボディ電極なし)の32種類の電界効果トランジスタの耐圧の幅と中央値(メディアン)を示す図である。

同図に示すように、ボディ電極なし(比較例)の場合、中央値が約430V、最高耐圧は約750Vであったのに対し、ボディ電極あり(実施例)の場合、中央値が約500V、最高耐圧は約1350Vだった。

【0077】

以上に示したように、ボディ電極を設けることにより、高耐圧のIII族窒化物(GaN)を用いた電界効果トランジスタが実現可能になる。また、本実施の形態の電界効果トランジスタ1Aおよび1Bにより、ノーマリーオフ動作の高耐圧、高電流の電界効果トランジスタを得ることが可能になる。

【0078】

尚、本発明は、前述した実施の形態に限定されるものではなく、種々の改変が可能であり、それらも、本発明の技術範囲に含まれる。

【符号の説明】

【0079】

1A、1B………電界効果トランジスタ

2………p−Si基板

3………バッファ層

4………p−GaN半導体層

5………ソース電極(S)

6………ドレイン電極(D)

7………ゲート電極(G)

8………ボディ電極

9………SiO2ゲート酸化膜

10、11………n+コンタクト層

12………リサーフ(RESURF)層

13………AlGaN層

20………正孔

21………サファイア基板

31………AlN層

32………GaN層

【特許請求の範囲】

【請求項1】

III族窒化物半導体を用いた電界効果トランジスタにおいて、

前記III族窒化物半導体の上面または下面のいずれかにボディ電極が形成されることを特徴とする電界効果トランジスタ。

【請求項2】

半導体層として、少なくともp型GaN層を1層含むことを特徴とする請求項1記載の電界効果トランジスタ。

【請求項3】

半導体基板をp型シリコンとし、前記半導体基板の下面にボディ電極を形成することを特徴とする請求項1または請求項2のいずれかに記載の電界効果トランジスタ。

【請求項4】

前記半導体基板と前記半導体層の間にバッファ層が形成され、

前記バッファ層は複数の層で構成され、前記バッファ層の各層は、AlNまたは/およびGaNまたは/およびBN、または、AlN、GaN、BNを組み合わせた化合物よりなることを特徴とする請求項3記載の電界効果トランジスタ。

【請求項5】

前記バッファ層の最上層はAlNであることを特徴とする請求項4記載の

電界効果トランジスタ。

【請求項6】

前記バッファ層の最上層AlN層の膜厚は1nm以上40nm以下であることを特徴とする請求項5記載の電界効果トランジスタ。

【請求項7】

サファイア基板上に形成したp型GaN層上にAlGaN層が形成され、AlGaN層上に直接ボディ電極が形成されることを特徴とする請求項1または請求項2のいずれかに記載の電界効果トランジスタ。

【請求項1】

III族窒化物半導体を用いた電界効果トランジスタにおいて、

前記III族窒化物半導体の上面または下面のいずれかにボディ電極が形成されることを特徴とする電界効果トランジスタ。

【請求項2】

半導体層として、少なくともp型GaN層を1層含むことを特徴とする請求項1記載の電界効果トランジスタ。

【請求項3】

半導体基板をp型シリコンとし、前記半導体基板の下面にボディ電極を形成することを特徴とする請求項1または請求項2のいずれかに記載の電界効果トランジスタ。

【請求項4】

前記半導体基板と前記半導体層の間にバッファ層が形成され、

前記バッファ層は複数の層で構成され、前記バッファ層の各層は、AlNまたは/およびGaNまたは/およびBN、または、AlN、GaN、BNを組み合わせた化合物よりなることを特徴とする請求項3記載の電界効果トランジスタ。

【請求項5】

前記バッファ層の最上層はAlNであることを特徴とする請求項4記載の

電界効果トランジスタ。

【請求項6】

前記バッファ層の最上層AlN層の膜厚は1nm以上40nm以下であることを特徴とする請求項5記載の電界効果トランジスタ。

【請求項7】

サファイア基板上に形成したp型GaN層上にAlGaN層が形成され、AlGaN層上に直接ボディ電極が形成されることを特徴とする請求項1または請求項2のいずれかに記載の電界効果トランジスタ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−232279(P2010−232279A)

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願番号】特願2009−76047(P2009−76047)

【出願日】平成21年3月26日(2009.3.26)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願日】平成21年3月26日(2009.3.26)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]