電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電界効果型トランジスタ、その製造方法及びスパッタリングターゲットに関する。

【背景技術】

【0002】

電界効果型トランジスタは、半導体メモリ集積回路の単位電子素子、高周波信号増幅素子、液晶駆動用素子等として広く用いられており、現在、最も多く実用化されている電子デバイスである。

そのなかでも、近年における表示装置のめざましい発展に伴い、液晶表示装置(LCD)のみならず、エレクトロルミネッセンス表示装置(EL)や、フィールドエミッションディスプレイ(FED)等の各種の表示装置において、表示素子に駆動電圧を印加して表示装置を駆動させるスイッチング素子として、薄膜トランジスタ(TFT)が多用されている。

【0003】

薄膜トランジスタの材料としては、シリコン系半導体が広く用いられている。一般に、高速動作が必要な高周波増幅素子、集積回路用素子等には、結晶系シリコンが用いられ、液晶駆動用素子等には、大面積化の要求からアモルファスシリコンが用いられている。

しかしながら、結晶系シリコンは、結晶化を図る際に、例えば、800℃以上の高温やエキシマーレーザーによる加熱が必要となり、大面積基板への構成が困難で、製造に際して多大なエネルギーと工程数を要する等の問題があった。さらに、結晶系シリコンは通常TFTの素子構成がトップゲート構成に限定されるためマスク枚数の削減等コストダウンが困難であった。

【0004】

一方、比較的低温で形成できる非晶性のシリコン半導体(アモルファスシリコン)は、移動度(電界効果移動度)が0.5cm2/Vs程度と小さく、結晶系のものに比べてスイッチング速度が遅いため、大画面・高精細・高周波数の動画の表示に追従できない場合がある。また、アモルファスシリコンを用いた電界効果トランジスタは直流電流ストレスに対する安定性(信頼性)が低く、直流電流駆動を行う有機EL等の自発光表示素子の駆動への応用が困難であるという問題点があった。

【0005】

尚、現在、表示装置を駆動させるスイッチング素子としては、シリコン系の半導体膜を用いた素子が主流を占めているが、それは、シリコン薄膜の安定性、加工性の良さの他、スイッチング速度が速い等、種々の性能が良好なためである。そして、このようなシリコン系薄膜は、一般に化学蒸気析出法(CVD)法により製造されている。

【0006】

また、従来のTFTには、ガラス等の基板上にゲ−ト電極、ゲ−ト絶縁層、水素化アモルファスシリコン(a−Si:H)等の半導体層、ソ−ス及びドレイン電極を積層した逆スタガ構造のものがある。このTFTは、イメ−ジセンサを始め、大面積デバイスの分野において、アクティブマトリクス型の液晶ディスプレイに代表されるフラットパネルディスプレイ等の駆動素子として用いられている。これらの用途では、高機能化(大画面・高精細・高周波数対応)に伴い、さらなる作動の高速化が求められている。

【0007】

このような状況下、トランジスタ性能(移動度、安定性)と大面積化の両立が期待できる半導体として、酸化物を用いた酸化物半導体が注目されている。

しかしながら、このような酸化物半導体のうち、従来からある酸化亜鉛を用いたものは、移動度が低い、オンオフ比が低い、漏れ電流が大きい、ピンチオフが不明瞭、ノーマリーオンになりやすい等、TFTの性能が低い。また、耐薬品性が劣るため、ウェットエッチングが難しい等、製造プロセスや使用環境の制限があった。

さらに、性能を上げるためには、酸化物半導体を高い圧力で成膜する必要があるため、成膜速度が遅く、また、700℃以上の高温処理が必要であった。また、トップゲート構成では酸化物半導体の膜厚を50nm以上にする必要がある等、実用上の制限が多かった。

【0008】

このような問題を解決するために、酸化インジウム及び酸化亜鉛からなる非晶質酸化物半導体、又は酸化インジウム、酸化亜鉛及び酸化ガリウムからなる非晶質酸化物半導体を用いた電界効果型トランジスタが検討されている。しかしながら、ガリウム(Ga)を添加しないと耐湿性等の環境安定性が不足する一方、Gaの添加量が増えると移動度やS値等のTFT特性が低下するおそれがあった。また、Gaはレアメタルであるためコストが高く、安定供給に問題があった。

【0009】

そこで、Gaを用いないものとして、酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体を用いた電界効果型トランジスタが検討されている(例えば、特許文献1参照。)。

酸化錫を用いた電界効果型トランジスタは古くから検討されていたが、オフ電流が高く移動度が低いため実用化されなかった。これは、酸化錫では絶縁体である低級酸化物(SnO等)が生成しやすいためであると考えられていた。このことから酸化錫は半導体材料として適しないと考えられていた。実際、錫を主成分とした酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体を用いた電界効果トランジスタでは、オフ電流やヒステリシスが大きく、閾値電圧(Vth)が大きく負となっていた。さらに、熱処理により移動度は向上できるが、熱処理温度に応じ閾値電圧が負方向に大きくシフトするため、各トランジスタの性能のばらつきが大きい、信頼性が低い等、実用化を妨げる問題があった(例えば、非特許文献1参照)。

【0010】

また、コスパッタを用いた錫を主成分としない酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体の検討されている。この半導体では、亜鉛が25原子%以上含まれると移動度が低下し、閾値電圧が大きくなり、一方亜鉛が25原子%未満含まれるとS値が大きくなり閾値電圧が負となり、トランジスタ特性のよい電界効果トランジスタが作製できる組成比を見出すことは困難と考えられていた(例えば、非特許文献2参照)。

【0011】

このような状況であったため、酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体ではディスプレイ用パネル等の実用に適した電界効果型トランジスタの作製は困難と思われていた。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】WO2005/088726 A1

【非特許文献】

【0013】

【非特許文献1】M.S.Grover et al.,J.Phys.D.40,1335(2007)

【非特許文献2】Kachirayil J.Saji et al., JOURNAL OF THE ELECTROCHEMICAL SOCIETY,155(6),H390−395(2008)

【発明の概要】

【0014】

本発明の目的は、トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供することである。

【0015】

本発明によれば、以下の電界効果型トランジスタ等が提供される。

1.基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、

前記ソース電極とドレイン電極が、半導体層を介して接続してあり、

前記ゲート電極と前記半導体層の間にゲート絶縁膜があり、

前記半導体層の少なくとも一面側に保護層を有し、

前記半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満

であることを特徴とする電界効果型トランジスタ。

2.前記半導体層が下記条件1を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件1

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上23原子%未満

3.前記半導体層が下記条件2を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件2

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が1原子%以上10原子%未満

4.前記半導体層が下記条件3を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件3

(1)Zn/(In+Sn+Zn)で表される原子組成比率が50原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が23原子%以上30原子%以下

5.前記半導体層が下記条件4を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件4

(1)Zn/(In+Sn+Zn)で表される原子組成比率が65原子%超75原子%以下

6.前記保護層が酸化物からなることを特徴とする1〜5のいずれかに記載の電界効果型トランジスタ。

7.前記保護層が、酸化物からなる第一の保護層と、窒化物からなる第二の保護層とからなることを特徴とする1〜5のいずれかに記載の電界効果型トランジスタ。

8.電界効果移動度が3cm2/Vs以上、オフ電流が2×10−12A以下、閾値電圧(Vth)が−1V以上5V以下であることを特徴とする1〜7のいずれかに記載の電界効果型トランジスタ。

9.In原子、Sn原子及びZn原子を含有する酸化物であり、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上70原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタの半導体層形成用スパッタリングターゲット。

10.In原子、Sn原子及びZn原子を含有する酸化物であり、

Zn/(In+Sn+Zn)で表される原子組成比率が70原子%以下であり、

In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であり、

Sn/(In+Sn+Zn)で表される原子組成比率が5原子%以上15原子%未満であることを特徴とする電界効果型トランジスタの半導体層形成用スパッタリングターゲット。

11.9又は10のスパッタリングターゲットを用いて半導体層を成膜する工程を含むことを特徴とする1〜8のいずれかに記載の電界効果型トランジスタの製造方法。

12.半導体層を形成する工程、半導体層上に保護層を形成する工程、及びそれらの工程の後に150〜350℃で熱処理する工程を含むことを特徴とする11に記載の電界効果型トランジスタの製造方法。

13.半導体層の一部を低抵抗化させソース電極又はドレイン電極とする工程を含むことを特徴とする11又は12に記載の電界効果型トランジスタの製造方法。

14.1〜8のいずれかに記載の電界効果型トランジスタを具備したことを特徴とするディスプレイ用パネル。

15.In原子、Sn原子及びZn原子を含む酸化物であり、かつ、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満

であり、

Snの平均価数が+3.2以上であることを特徴とする半導体膜。

【0016】

本発明によれば、半導体層がIn、Sn及びZnを特定の組成比で含み、半導体層の少なくとも一面側に保護層を有することで、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)が高く実用性の高い電界効果トランジスタが得られる。

また、レアメタルであるGaを添加しなくともトランジスタ特性に優れた電界効果型トランジスタの提供が可能になった。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施形態の電界効果型トランジスタの概略断面図である。

【図2】本発明における半導体層の好ましい組成条件(領域)を示す図である。

【図3a】実施例1で作製した電界効果型トランジスタの製造工程を示す図である。

【図3b】実施例1で作製した電界効果型トランジスタの製造工程を示す図である。

【図4】昇電圧時及び降電圧時の伝達曲線(I−V特性)の例であり、(a)はヒステリシスの少ない例であり、(b)はヒステリシスの大きい例を示す図である。

【図5】(a)実施例40で作製したボトムゲートエッチストッパー型の電界効果型トランジスタの概略断面図であり、(b)は同トランジスタの概略上面図である。

【図6】実施例47で作製したボトムゲート構造のバックチャンネルエッチ(BCH)型の電界効果型トランジスタの概略断面図である。

【図7】実施例52で作製したコプラナー構造電界効果型トランジスタの製造工程を示す図である。

【図8】酸化物半導体の、温度と移動度の関係を示す図である。

【図9】実施例54で作製したトップゲート構造電界効果型トランジスタの概略断面図である。

【図10】実施例55で作製した電界効果型トランジスタの概略断面図である。

【図11】コスパッタによる薄膜形成の概念図である。

【図12】(a)は半導体層のZn量と移動度の関係を示す図であり、(b)は半導体層のZn量とオフ電流の関係を示す図である。

【図13】(a)は半導体層のIn量と移動度の関係を示す図であり、(b)は半導体層のIn量とオフ電流の関係を示す図である。

【発明を実施するための形態】

【0018】

本発明の電界効果型トランジスタは、基板上に、少なくとも半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極と、ゲート絶縁膜と、ゲート電極とを有する。

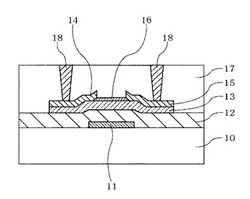

図1は、本発明の一実施形態の電界効果型トランジスタの概略断面図である。

この電界効果型トランジスタでは、基板10上に、ゲート電極11がストライプ状に形成されている。このゲート電極11を覆うようにゲート絶縁膜12を有し、このゲート絶縁膜12上であって、かつ、ゲート電極12の上方に半導体層13(活性層)が形成されている。

半導体層13の一端側に、ゲート電極11と直交する方向にソース電極14が接続されている。また、半導体層13の一端に対向する他端側にドレイン電極15が接続されている。

半導体層13、ソース電極14及びドレイン電極15の中間の位置に第一の保護層16が形成されている。

ゲート絶縁膜12、ソース電極14、ドレイン電極15及び第一の保護層16を覆うように、第二の保護層17が形成されている。

第二の保護層17にはコンタクトホール18があり、外部電極と、ソース電極14又はドレイン電極15が接続されている。

尚、第二の保護層17は必ずしも必須ではないが、形成することが好ましい。

【0019】

本発明の電界効果型トランジスタでは、半導体層13がIn原子、Sn原子及びZn原子を含んでおり、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする。

【0020】

Zn/(In+Sn+Zn)を25原子%以上とすることにより、Znにより酸素欠損が抑制され、適性な閾値電圧(Vth)の電界効果トランジスタが得られる。また、75原子%以下とすることにより、酸化亜鉛(ZnO)の結晶の生成によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

Zn/(In+Sn+Zn)は30原子%以上がより好ましく、35原子%以上がさらに好ましい。

【0021】

また、Sn/(In+Sn+Zn)を50原子%未満とすることにより、酸化錫の低級酸化物の生成(Sn平均価数の低下)によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

Sn/(In+Sn+Zn)は33原子%以下が好ましく、28原子%以下がより好ましく、23原子%未満がさらに好ましく、20原子%以下が特に好ましい。33原子%以下とすることにより、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)が良好な電界効果トランジスタが得られる。また、PECVD時のプラズマ照射等、プロセス上で還元雰囲気に曝された際の、移動度等のトランジスタ特性の低下を防ぐことが出来る。これは、錫の低級酸化物の生成(Sn平均価数の低下)を抑制することができるためと思われる。

【0022】

本発明では、半導体層13がSn原子を含むことで、耐湿性の向上や、耐薬品性の向上(耐PAN性の向上含む)、雰囲気温度に対する安定性が期待できる。さらに、Snを含有することでレアメタルであるInの含有量を低減することができる。

Sn/(In+Sn+Zn)は1原子%以上であることが好ましく、3原子%以上がより好ましく、5原子%以上がさらに好ましく、10原子%以上が特に好ましい。

【0023】

半導体層の組成においては、下記の条件1〜4のいずれかを満たすことが好ましい。

・条件1

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上23原子%未満

・条件2

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が1原子%以上10原子%未満

・条件3

(1)Zn/(In+Sn+Zn)で表される原子組成比率が50原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が23原子%以上30原子%以下

・条件4

(1)Zn/(In+Sn+Zn)で表される原子組成比率が65原子%超75原子%以下

【0024】

図2に本発明における半導体層の好ましい組成条件(領域)を示す。

半導体層の組成が領域1内にあると、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)に非常に優れた電界効果トランジスタが得られる。また、半導体層及びソース・ドレイン電極の形成にウェットエッチングを採用できるため、大型パネルを低いコストで製造できる。有機ELディスプレイや液晶ディスプレイ用途に特に適している。

【0025】

領域1のうち、特に下記の範囲が最も好ましい。

(1) Zn/(In+Sn+Zn)で表される原子組成比率が57原子%以上65原子%以下

(2) Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上18原子%未満

前記範囲内だと、移動度(cm2/Vs)及びオンオフ比が高く、オフ電流及びS値が小さく、かつ閾値電圧のシフトΔVth(V)が小さい良好な電界効果トランジスタが得られる。さらに、前記範囲内だと、希少資源であるIn(インジウム)の含有量も少ないため、低い原料比で良好なターゲット及び良好な電界効果トランジスタが得られ工業的に最適である。

【0026】

半導体層の組成が領域3内にあると、プロセス耐性が高くプロセス温度が高くとも劣化の危険性が少ない。また、耐湿性に優れた電界効果トランジスタが得られる。そのため、プロセス温度が高い無機ELディスプレイ用途に特に適している。

【0027】

半導体層の組成が領域2内にあると、低温の熱処理で高い特性が得られる。耐熱性の低い樹脂基板等を用いる用途(例えばフレキシブルディスプレイ)に特に適している。

【0028】

半導体層の組成が領域4内にあると、オフ電流が低い電界効果トランジスタが得られる。また、亜鉛が主成分のため原料コストが低く、製品から原料を回収する必要性がない。そのため、ディスポーザルな用途(ICタグ等)に特に適している。

【0029】

半導体層の組成において、Sn原子とIn原子の原子比(Sn/In)は、0.41以上0.69以下が特に好ましい。0.41以上だと耐湿性が向上し、0.69以下だと低温プロセスで優れたトランジスタ特性が得られる。また、酸化錫の低級酸化物の生成(Sn平均価数の低下)によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

【0030】

半導体層は、In,Sn及びZnの他に、Ga、Al、B、Sc、Y、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbから選ばれた元素を0〜20原子%含んでいてもよい。

また、Na含有量が100ppm未満であることが好ましい。Naの含有量が100ppm未満であると、電圧による可動イオンの量が少ないため電圧ストレスに対する信頼性が向上する(ΔVthが小さくなる)。

以下、本発明の電界効果型トランジスタを構成する部材の例について説明する。

【0031】

1.基板

特に制限はなく、本技術分野で公知のものを使用できる。例えば、ケイ酸アルカリ系ガラス、無アルカリガラス、石英ガラス等のガラス基板、シリコン基板、アクリル、ポリカーボネート、ポリエチレンナフタレート(PEN)等の樹脂基板、ポリエチレンテレフタレート(PET)、ポリアミド等の高分子フィルム基材等が使用できる。基板や基材の厚さは0.1〜10mmが一般的であり、0.3〜5mmが好ましい。ガラス基板の場合は、化学的に、或いは熱的に強化させたものが好ましい。透明性や平滑性が求められる場合は、ガラス基板、樹脂基板が好ましく、ガラス基板が特に好ましい。軽量化が求められる場合は樹脂基板や高分子機材が好ましい。

【0032】

2.半導体層

半導体層は、上述したとおり、In、Zn及びSnの各原子を含む複合酸化物からなる。このような半導体層は、例えば、後述する本発明の複合酸化物ターゲット(半導体層用ターゲット)を使用して薄膜を形成することで作製できる。

また、半導体層は、粒子状の酸化物半導体を溶媒に溶かし、その酸化物半導体溶液を塗布又は印刷し、その後、加熱処理で溶媒を蒸発させることにより形成することもできる。この方法は、設備コストが低くエネルギー効率も高いため好ましい。

ゾルゲル法等の溶液の利用やCVDも利用できるが、大面積に均一に成膜するには半導体用ターゲットを用いスパッタリングで形成することが、トランジスタ特性が高くなることから最も好ましい。

【0033】

本発明において、半導体層は非晶質膜であることが好ましい。非晶質膜であることにより、絶縁膜や保護層との密着性が改善される、大面積でも均一なトランジスタ特性が容易に得られることとなる。ここで、半導体層が非晶質膜であるかは、X線結晶構造解析により確認できる。明確なピークが観測されない場合が非晶質である。

【0034】

また、半導体層の電子キャリア濃度が1013〜1018/cm3であることが好ましく、特に1014〜1017/cm3であることが好ましい。電子キャリア濃度が上記の範囲であれば、非縮退半導体となりやすく、トランジスタとして用いた際に移動度とオンオフ比のバランスが良好となり好ましい。キャリア密度が1018cm−3以下だとオフ電流を小さくでき、ノーマリーオフとしやすくなる。1013cm−3以上だと移動度を向上させることができる。

また、比抵抗は10−1〜109Ωcmであることが好ましい。より好ましくは10〜107Ωcmである。特に好ましくは、102〜105Ωcmである。10−1Ωcm以上だとオフ電流を小さくすることができる。109Ωcm以下だと移動度を高くし、閾値電圧を小さくできる。

また、バンドギャップが2.0〜6.0eVであることが好ましく、特に、2.8〜5.0eVがより好ましい。バンドギャップは、2.0eVより小さいと可視光を吸収し電界効果型トランジスタが誤動作するおそれがある。一方、6.0eVより大きいとキャリアが供給されにくくなり電界効果型トランジスタが機能しなくなるおそれがある。

【0035】

半導体層は、熱活性型を示す非縮退半導体であることが好ましい。縮退半導体であるとキャリアが多すぎてオフ電流・ゲートリーク電流が増加する、閾値が負になりノーマリーオンとなるおそれがある。半導体層が非縮退半導体であるかは、ホール効果を用いた移動度とキャリア密度の温度変化の測定を行うことにより判断できる。また、半導体層を非縮退半導体とするには、成膜時の酸素分圧を調整する、後処理をすることで酸素欠陥量を制御しキャリア密度を最適化することで達成できる。

【0036】

半導体層の表面粗さ(RMS)は、1nm以下が好ましく、0.6nm以下がさらに好ましく、0.3nm以下が特に好ましい。1nmより大きいと、移動度が低下するおそれがある。

半導体層は、酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持している非晶質膜であることが好ましい。酸化インジウムを含む非晶質膜が酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持しているかどうかは、高輝度のシンクロトロン放射等を用いた微小角入射X線散乱(GIXS)によって求めた動径分布関数(RDF)により、In−X(Xは,In,Zn)を表すピークが0.30から0.36nmの間にあることで確認できる(詳細については、下記の文献を参照すればよい。F.Utsuno, et al.,Thin Solid Films,Volume 496, 2006, Pages 95−98)。

【0037】

さらに、原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合に、A/B>0.7の関係を満たすことが好ましく、A/B>0.85がより好ましく、A/B>1がさらに好ましく、A/B>1.2が特に好ましい。

A/Bが0.7以下だと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。A/Bが小さいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0038】

また、In−Inの平均結合距離が0.3〜0.322nmであることが好ましく、0.31〜0.32nmであることが特に好ましい。In−Inの平均結合距離はX線吸収分光法により求めることができる。X線吸収分光法による測定では、立ち上がりから数百eVも高いエネルギーのところまで広がったX線吸収広域微細構造(EXAFS)を示す。EXAFSは励起された原子の周囲の原子による電子の後方散乱によって引き起こされる。飛び出していく電子波と後方散乱された波との干渉効果が起こる。干渉は電子状態の波長と周囲の原子へ行き来する光路長に依存する。EXAFSをフーリエ変換することで動径分布関数(RDF)が得られる。RDFのピークから平均結合距離を見積もることができる。

【0039】

半導体層の膜厚は、通常0.5〜500nm、好ましくは1〜150nm、より好ましくは3〜80nm、特に好ましくは10〜60nmである。0.5nmより薄いと工業的に均一に成膜することが難しい。一方、500nmより厚いと成膜時間が長くなり工業的に採用できない。また、3〜80nmの範囲内にあると、移動度やオンオフ比等TFT特性が特に良好である。

【0040】

本発明では、非局在準位のエネルギー幅(E0)が14meV以下であることが好ましい。半導体層の非局在準位のエネルギー幅(E0)は10meV以下がより好ましく、8meV以下がさらに好ましく6meV以下が特に好ましい。非局在準位のエネルギー幅(E0)が14meVより大きいと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。半導体層の非局在準位のエネルギー幅(E0)が大きいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0041】

X線光電子分光法(XPS)で測定したSn平均価数は、+3.2以上が好ましく、+3.6以上がより好ましく、+3.8以上がさらに好ましい。上限は特に限定されないが通常+4.0以下である。XPS価電子帯スペクトルでは、Sn5sに起因するバンドは、低級酸化物であるSnO(Sn+2:4d105s2の電子配置)のスペクトルのみにみられ、SnO2(Sn+4:4d10の電子配置)にはみられない。そのため、Sn5sバンドの相対強度からSn平均価数を求めることができる(参照:X線光電子分光法、1998年、丸善株式会社刊)。通常、スパッタで作製したSnO2膜のSn平均価数は、+2.8程度である。

【0042】

X線局所構造解析(XAFS)法を用いたIn、Sn、Zn各金属元素周辺の局所構造解析において、Sn元素周りの構造はSnO2と同様の構造を有していると、散乱による移動度の低下が抑制できて好ましい。またIn、Zn元素周りの構造はIZO薄膜と同様の構造を有しているとZnにより非晶質が安定化され好ましい。

なお、前記解析を行うに際し、一般的な蛍光法では解析に十分なデータを得ることができないので、多素子SSD検出器を用い、且つ薄膜試料基板を微小角度に傾けて放射光を入射させる斜入射法を用いて測定を行うことが好ましい。

【0043】

3.第一及び第二の保護層

保護層により、真空中や低圧下で半導体の表面層の酸素が脱離し、オフ電流が高くなる、閾値電圧が負になることを防ぐことが出来る。また、大気下でも湿度等周囲の影響を受けず、閾値電圧等のトランジスタ特性のばらつきの発生を防ぐことが出来る。

【0044】

保護層を形成する材料は特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。保護層は酸化物からなることが特に好ましく、SiO2,Y2O3,Hf2O3,CaHfO3等の酸化物が好ましい。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

このような保護層は、異なる2層以上の絶縁膜を積層した構造でもよい。

【0045】

また、保護層は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。尚、保護層が非晶質であることが特に好ましい。非晶質膜であると界面の平滑性が良好で、移動度の向上、閾値電圧の抑制、S値の抑制効果が期待できる。また、ゲートリーク電流を抑制できる。

【0046】

半導体層の保護層は、非晶質酸化物あるいは非晶質窒化物であることが好ましく、非晶質酸化物であることが特に好ましい。また、保護層が酸化物でないと半導体中の酸素が保護層側に移動し、オフ電流が高くなったり、閾値電圧が負になりノーマリーオフを示すおそれがある。また、半導体層の保護層は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、半導体層の保護層は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

特に、半導体層に大きく接する第一の保護層を酸化物で、第二の保護層をSiNx等の窒化物で構成することが好ましい。このような構成をとると良好なトランジスタ特性と耐湿性を持たせることが容易である。

【0047】

保護層の形成は、PECVD、TEOSCVD、Cat−CVD、スパッタリング、スピンコート、印刷法等が利用できるが、工業的にはPECVDあるいはスパッタリングが好ましく、PECVDが特に好ましい。

【0048】

4.ゲート絶縁膜

ゲート絶縁膜を形成する材料にも特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0049】

このようなゲート絶縁膜は、異なる2層以上の絶縁膜を積層した構造でもよい。また、ゲート絶縁膜は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。

また、ゲート絶縁膜は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、ゲート絶縁膜は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

ゲート絶縁膜の形成は、PECVD、TEOSCVD、Cat−CVD、スパッタリング、スピンコート、印刷法等が利用できるが、工業的にはPECVDあるいはスパッタリングが好ましく、PECVDが特に好ましい。

【0050】

6.電極

ゲート電極、ソ−ス電極及びドレイン電極の各電極を形成する材料に特に制限はなく、本発明の効果を失わない範囲で一般に用いられているものを任意に選択することができる。

例えば、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物、ZnO、SnO2等の透明電極や、Al,Ag,Cr,Ni,Mo,Au,Ti,Ta、Cu等の金属電極、又はこれらを含む合金の金属電極を用いることができる。また、それらを2層以上積層して接触抵抗を低減したり、界面強度を向上させることが好ましい。また、ソ−ス電極、ドレイン電極の接触抵抗を低減させるため半導体の電極との界面をプラズマ処理、オゾン処理等で抵抗を調整してもよい。

【0051】

本発明では、半導体層の一部を低抵抗化させてソース電極又はドレイン電極を形成してもよい。

半導体層の一部を低抵抗化させるには、例えば、低酸素分圧下、不活性ガス下、低圧下又は真空下で、熱処理あるいは紫外線光等のエネルギー線を照射する方法や、水素、窒素又はアルゴン等の不活性ガス環境下でプラズマを照射する方法等がある。

また、プラズマCVDにてSiNx等で保護層を積層する際に、水素量等のプラズマ条件を調整することで低抵抗化してもよい。

【0052】

本発明の電界効果型トランジスタは、半導体層を遮光する構造を持つことが好ましい。半導体層を遮光する構造(例えば、遮光層)を持っていないと、光が半導体層に入射した場合にキャリア電子が励起されオフ電流が高くなるおそれがある。遮光層は、300〜800nmに吸収を持つ薄膜が好ましい。遮光層は半導体層の上部、下部どちらかでも構わないが、上部及び下部の両方にあることが好ましい。また、遮光層はゲート絶縁膜やブラックマトリックス等と兼用されていても構わない。遮光層が片側だけにある場合、遮光層が無い側から光が半導体層に照射しないよう構造上工夫する必要がある。

【0053】

本発明の電界効果型トランジスタでは、半導体層とソース電極・ドレイン電極との間にコンタクト層を設けてもよい。コンタクト層は半導体層よりも抵抗が低いことが好ましい。コンタクト層の形成材料は、上述した半導体層と同様な組成の複合酸化物が使用できる。即ち、コンタクト層はIn,Zn等の各元素を含むことが好ましい。これらの元素を含まないと、コンタクト層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

【0054】

コンタクト層の作製方法に特に制約はないが、成膜条件を変えて半導体層と同じ組成比のコンタクト層を成膜したり、半導体層と組成比の異なる層を成膜したり、半導体の電極とのコンタクト部分をプラズマ処理やオゾン処理により抵抗を高めることで構成したり、半導体層を成膜する際に酸素分圧等の成膜条件により抵抗を高くなる層を構成してもよい。また、本発明の電界効果型トランジスタでは、半導体層とゲート絶縁膜との間、及び/又は半導体層と保護層との間に、半導体層よりも抵抗の高い酸化物抵抗層を有することが好ましい。酸化物抵抗層が無いとオフ電流が発生する、閾値電圧が負となりノーマリーオンとなる、保護層成膜やエッチング等の後処理工程時に半導体層が変質し特性が劣化するおそれがある。

【0055】

続いて、本発明の電界効果型トランジスタの製造方法について説明する。

本発明の製造方法では、後述する本発明のターゲットを用い、半導体層を成膜する工程を含む。

また、半導体層を成膜する工程、半導体層上に保護層を形成する工程を有し、保護層を形成した後に150〜350℃で熱処理する工程を含むことを特徴とする。尚、上述した電界効果型トランジスタの各構成部材(層)は、本技術分野で公知の手法で形成できる。

【0056】

具体的に、成膜方法としては、スプレー法、ディップ法、CVD法等の化学的成膜方法、又はスパッタ法、真空蒸着法、イオンプレーティング法、パルスレーザーディポジション法等の物理的成膜方法を用いることができる。キャリア密度が制御し易い、及び膜質向上が容易であることから、好ましくは物理的成膜方法を用い、より好ましくは生産性が高いことからスパッタ法を用いる。

スパッタリングでは、複合酸化物の焼結ターゲットを用いる方法、複数の焼結ターゲットを用いコスパッタを用いる方法、合金ターゲットを用い反応性スパッタを用いる方法等が利用できる。但し、複合酸化物の焼結ターゲットを用いる方法では、複数の焼結ターゲットを用いコスパッタを用いる方法や、合金ターゲットを用い反応性スパッタを用いる方法に比べ、均一性や再現性が向上し、非局在準位のエネルギー幅(E0)が低減させ、移動度の向上、S値の低減、閾値電圧の低減等、トランジスタ特性を向上させることができる。好ましくは、複合酸化物の焼結ターゲットを用いる。RF、DCあるいはACスパッタリング等公知のものが利用できるが、均一性や量産性(設備コスト、成膜速度)からDCあるいはACスパッタリングが好ましい。X線光電子分光法(XPS)で測定したSn平均価数は、+3.2以上にする観点からはRFスパッタリングが好ましい。

【0057】

成膜時の基板温度は、室温(30℃)以上250℃以下が好ましく、50℃以上200℃以下がより好ましい。250℃以下だとTFTを作製した際にオフ電流の低減が期待できる。室温(30℃)以上だと連続成膜時の基板温度上昇による成膜条件の変動の低減が期待できる。

また、成膜時に酸素の取組みを増加させるような処置を取ることが好ましい。成膜時に酸素の取組みを増加させるような処置としては、不活性ガス(アルゴン等)と酸素の混合気体を流入させる、オゾンアシストやRFスパッタリングによって酸素ラジカル(オゾン)量を増加させる、基板間距離・投入電力・全圧の調整等があげられる。

【0058】

成膜時の酸素分圧は、10−3Pa〜10−1Paで行うことが好ましく、5×10−3Pa〜10−1Paで行うことがより好ましい。酸素分圧10−3Pa以上だと酸化錫の低級酸化物の生成を抑えることができる。10−1Pa以下だと成膜速度が速くなることが期待できる。

形成した膜を各種エッチング法によりパターニングできる。

【0059】

本発明では半導体層を、本発明のターゲットを用い、DC又はACスパッタリングにより成膜することがより好ましい。DC又はACスパッタリングを用いることにより、RFスパッタリングの場合と比べて、成膜時のダメージを低減できる。XPSで測定したSn平均価数を高くしたい場合は、RFスパッタリングを用いてもよい。RFスパッタリングを用いることで、XPSで測定したSn平均価数を制御しやすい。このため、電界効果型トランジスタにおいて、閾値電圧シフトの低減、移動度の向上、閾値電圧の減少、S値の減少等の効果が期待できる。

【0060】

また、本発明では半導体層成膜後150〜350℃で熱処理することが好ましい。特に、半導体層と半導体の保護層を形成した後に、150〜350℃で熱処理することが好ましい。150℃より低いと得られるトランジスタの熱安定性や耐熱性が低下したり、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、350℃より高いと耐熱性のない基板が使用できない、熱処理用の設備費用がかかるおそれがある。

【0061】

熱処理温度は160〜300℃がより好ましく、170〜260℃がさらに好ましく、180〜240℃が特に好ましい。特に、熱処理温度が180℃以下であれば、基板としてPEN等の耐熱性の低い樹脂基板を利用できるため好ましい。

熱処理時間は、通常1秒〜24時間が好ましいが、処理温度により調整することが好ましい。例えば、70〜180℃では、10分から24時間がより好ましく、20分から6時間がさらに好ましく、30分〜3時間が特に好ましい。180〜260℃では、6分から4時間がより好ましく、15分から2時間がさらに好ましい。260〜300℃では、30秒から4時間がより好ましく、1分から2時間が特に好ましい。300〜350℃では、1秒から1時間がより好ましく、2秒から30分が特に好ましい。

熱処理は、不活性ガス中で酸素分圧が10−3Pa以下の環境下で行うか、あるいは半導体層を保護層で覆った後に行うことが好ましい。上記条件下だと再現性が向上する。

半導体層を形成した後に150〜350℃で熱処理し、さらに半導体の保護層を形成した後に、150〜350℃で熱処理すると特に好ましい。前記のようにすると半導体特性が改善することに加え再現性及び均一性が向上し、半導体膜の成膜条件に対する依存性も小さくなる。

【0062】

典型的な電界効果型トランジスタでは、ソース・ドレイン電極間に、5〜20V程度の電圧Vdを印加したとき、ゲート電圧Vgを、0Vと5〜20Vの間でスイッチすることで、ソース・ドレイン電極間の電流Idを制御する(オンオフする)ことができる。

トランジスタ特性の評価項目としては、さまざまなものがあるが、たとえば、電界効果移動度μ、閾値電圧(Vth)、オンオフ比、S値等が上げられる。

電界効果移動度は、線形領域や飽和領域の特性から求めることができる。たとえば、トランスファ特性の結果から、√Id―Vgのグラフを作製し、この傾きから電界効果移度を導く方法が挙げられる。本明細書では特にこだわらない限り、この手法で評価している。

閾値電圧の求め方はいくつかの方法があるが、たとえば√Id―Vgのグラフのx切片から閾値電圧Vthを導くことが挙げられる。

オンオフ比はトランスファ特性における、最も大きなIdと、最も小さなIdの値の比から求めることができる。

【0063】

そして、S値は、トランスファ特性の結果から、Log(Id)―Vdのグラフを作製し、この傾きの逆数から導出することができる。

S値の単位は、V/decadeであり、小さな値であることが好ましい。S値は1.0V/dec以下が好ましく、0.5V/dec以下がより好ましく、0.3V/dec以下がさらに好ましく、0.1V/dec以下が特に好ましい。0.8V/dec以下だと駆動電圧が小さくなり消費電力を低減できる可能性がある。特に、有機ELディスプレイで用いる場合は、直流駆動のためS値を0.3V/dec以下にすると消費電力を大幅に低減できるため好ましい。尚、S値(Swing Factor)とは、オフ状態からゲート電圧を増加させた際に、オフ状態からオン状態にかけてドレイン電流が急峻に立ち上がるが、この急峻さを示す値である。下記式で定義されるように、ドレイン電流が1桁(10倍)上昇するときのゲート電圧の増分をS値とする。

S値=dVg/dlog(Ids)

S値が小さいほど急峻な立ち上がりとなる(「薄膜トランジスタ技術のすべて」、鵜飼育弘著、2007年刊、工業調査会)。S値が大きいと、オンからオフに切り替える際に高いゲート電圧をかける必要があり、消費電力が大きくなるおそれがある。

【0064】

本発明の電界効果トランジスタでは、移動度は3cm2/Vs以上が好ましく、8cm2/Vs以上がより好ましく、10cm2/Vs以上がさらに好ましく、16cm2/Vs以上が特に好ましい。3cm2/Vsより小さいとスイッチング速度が遅くなり大画面高精細のディスプレイに用いることができないおそれがある。

オンオフ比は、107以上が好ましく、108以上がより好ましく、109以上が特に好ましい。

オフ電流は、2×10−12A(2pA)以下が好ましく、1pA以下がより好ましく、0.1pA以下が特に好ましい。オフ電流が2pAより小さいとディスプレイのTFTとして用いた場合にコントラストが良好となり、画面の均一性が向上することが期待できる。

【0065】

ゲートリーク電流は1pA以下が好ましい。1pAより小さいとディスプレイのTFTとして用いた場合にコントラストの低下を抑制できる。

閾値電圧は、通常−1〜5Vであるが、−0.5〜3Vが好ましく、0〜2Vがより好ましく、0〜1Vが特に好ましい。−1Vより大きいとオフ時にかける電圧が小さくなり消費電力を低減できる可能性がある。5Vより小さいと駆動電圧が小さくなり消費電力を低減できる可能性がある。

また、10μAの直流電圧50℃で100時間加えた前後の閾値電圧のシフト量は、1.0V以下が好ましく、0.5V以下がより好ましい。1Vより小さいと有機ELディスプレイのトランジスタとして利用した場合、画質の経時変化を低減できる。

【0066】

また、伝達曲線でゲート電圧を昇降させた場合のヒステリシスが小さい方が好ましい。ヒストリシスが小さいと駆動電圧を低減できる可能性がある。

また、チャンネル幅Wとチャンネル長Lの比W/Lは、通常0.1〜100、好ましくは0.5〜20、特に好ましくは1〜8である。W/Lが100を越えると漏れ電流が増えたり、on−off比が低下したりするおそれがある。0.1より小さいと電界効果移動度が低下したり、ピンチオフが不明瞭になったりするおそれがある。また、チャンネル長Lは通常0.1〜1000μm、好ましくは1〜100μm、さらに好ましくは2〜10μmである。0.1μm未満では工業的に製造が難しくまた漏れ電流が大きくなるおそれがある、1000μmを超えると素子が大きくなりすぎて好ましくない。

【0067】

続いて、本発明の半導体層形成用スパッタリングターゲットについて説明する。

本発明のスパッタリングターゲットは、通常In原子、Sn原子及びZnを含有し、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上70原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満である。

【0068】

さらに、In原子、Sn原子及びZn原子を含有する酸化物焼結体であり、Zn/(In+Sn+Zn)で表される原子組成比率が70原子%以下であり、In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であり、Sn/(In+Sn+Zn)で表される原子組成比率が5原子%以上15原子%未満であることがより好ましい。

【0069】

Zn/(In+Sn+Zn)が70原子%以下であると、Zn酸化物の生成による相対密度の低下やバルク抵抗の高抵抗化を防げる。In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であると、原料コストの増加によるコストアップを防ぎやすい。Sn/(In+Sn+Zn)が5原子%以上だとSnとZnの価数バランスがとれターゲットの相対密度が上がりバルク抵抗を下げやすく、15原子%未満であるとSnの低級酸化物の生成によるバルク抵抗の高抵抗化を防ぎやすい。すなわち、前記範囲内であると、相対密度が高く、抵抗の低いターゲットを安定して作製できる。また、そのターゲットを用いて特性(移動度、オンオフ比、S値、ΔVthシフト)の良好な電界効果トランジスタが得られる。また、希少資源であるIn(インジウム)の含有量も少なく、安い原料比で良好なターゲットが得られ工業的に最適である。

【0070】

さらに、Zn/(In+Sn+Zn)で表される原子組成比率が60原子%以上67原子%以下であり、In/(In+Sn+Zn)で表される原子組成比率が18原子%以上28原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が7原子%以上14原子%以下であることが特に好ましい。

【0071】

ターゲットの出発原料としては、一般的に酸化インジウム粉末と、酸化亜鉛粉末と、酸化錫粉末の粉末を用いるが、これらの単体、化合物、複合酸化物等を原料としてもよい。

各原料粉の純度は、通常99.9%(3N)以上、好ましくは99.99%(4N)以上、さらに好ましくは99.995%以上、特に好ましくは99.999%(5N)以上である。各原料粉の純度が99.9%(3N)未満だと、不純物により半導体特性が低下する、信頼性が低下する等のおそれがある。特にNa含有量が100ppm未満であると薄膜トランジスタを作製した際に信頼性が向上し好ましい。

【0072】

原料粉について、比表面積が3〜16m2/gである酸化インジウム粉、酸化錫粉、亜鉛粉あるいは複合酸化物粉を含み、粉体全体の比表面積が3〜16m2/gである混合粉体を原料とすることが好ましい。尚、各酸化物粉末の比表面積が、ほぼ同じである粉末を使用することが好ましい。これにより、より効率的に粉砕混合できる。具体的には、比表面積の比が1/4〜4倍以内にすることが好まく、1/2〜2倍以内が特に好ましい。比表面積が違いすぎると、効率的な粉砕混合が出来ず、焼結体中に酸化物の粒子が残る場合がある。ただし、酸化亜鉛の比表面積は酸化インジウム、酸化錫の比表面積よりも小さいことが好ましい。このことによりターゲットの色むらを抑えることができる。

【0073】

混合粉体を、例えば、湿式媒体撹拌ミルを使用して混合粉砕する。このとき、粉砕後の比表面積が原料混合粉体の比表面積より1.0〜3.0m2/g増加する程度か、又は粉砕後の平均メジアン径が0.6〜1μmとなる程度に粉砕することが好ましい。このように調整した原料粉を使用することにより、仮焼工程を全く必要とせずに、高密度の酸化物焼結体を得ることができる。また、還元工程も不要となる。

【0074】

尚、原料混合粉体の比表面積の増加分が1.0m2/g未満又は粉砕後の原料混合粉の平均メジアン径が1μmを超えると、焼結密度が十分に大きくならない場合がある。一方、原料混合粉体の比表面積の増加分が3.0m2/gを超える場合又は粉砕後の平均メジアン径が0.6μm未満にすると、粉砕時の粉砕器機等からのコンタミ(不純物混入量)が増加する場合がある。

【0075】

ここで、各粉体の比表面積はBET法で測定した値である。各粉体の粒度分布のメジアン径は、粒度分布計で測定した値である。これらの値は、粉体を乾式粉砕法、湿式粉砕法等により粉砕することにより調整できる。

原料粉の所望の配合割合、混合方法、成形する方法は特に限定されず、従来から公知の各種湿式法又は乾式法を用いることができる。

【0076】

乾式法としては、コールドプレス(Cold Press)法やホットプレス(Hot Press)法等を挙げることができる。コールドプレス法では、混合粉を成形型に充填して成形体を作製し、焼結させる。ホットプレス法では、混合粉を成形型内で、通常700〜1000℃で1〜48時間、好ましくは800〜950℃で3〜24時間にて直接焼結させる。

乾式法のコールドプレス(Cold Press)法としては、粉砕工程後の原料をスプレードライヤー等で乾燥した後、成形する。成形は公知の方法、例えば、加圧成形、冷間静水圧加圧、金型成形、鋳込み成形射出成形が採用できる。焼結密度の高い焼結体(ターゲット)を得るためには、冷間静水圧(CIP)等加圧を伴う方法で成形するのが好ましい。尚、成形処理に際しては、ポリビニルアルコールやメチルセルロース、ポリワックス、オレイン酸等の成形助剤を用いてもよい。

【0077】

次いで、得られた成形物を焼結して焼結体を得る。また、焼結は酸素を流通することにより酸素雰囲気中で焼結するか、加圧下にて焼結するのがよい。これにより亜鉛の蒸散を抑えることができ、ボイド(空隙)のない焼結体が得られる。このようにして製造した焼結体は、密度が高いため、使用時におけるノジュールやパーティクルの発生が少ないことから、膜特性に優れた酸化物半導体膜を作製することができる。

1000℃以上での昇温速度を30℃/h以上、冷却時の降温速度を30℃/h以上とするのが好ましい。昇温速度を30℃/h未満であると酸化物の分解が進行しピンホール数が多くなり、また冷却時の降温速度を30℃/h未満とするとInの組成比が変化するおそれがある。

【0078】

湿式法としては、例えば、濾過式成形法(特開平11−286002号公報参照)を用いるのが好ましい。この濾過式成形法は、セラミックス原料スラリーから水分を減圧排水して成形体を得るための非水溶性材料からなる濾過式成形型であって、1個以上の水抜き孔を有する成形用下型と、この成形用下型の上に載置した通水性を有するフィルターと、このフィルターをシールするためのシール材を介して上面側から挟持する成形用型枠からなり、前記成形用下型、成形用型枠、シール材、及びフィルターが各々分解できるように組立てられており、該フィルター面側からのみスラリー中の水分を減圧排水する濾過式成形型を用い、混合粉、イオン交換水と有機添加剤からなるスラリーを調製し、このスラリーを濾過式成形型に注入し、該フィルター面側からのみスラリー中の水分を減圧排水して成形体を作製し、得られたセラミックス成形体を乾燥脱脂後、焼成する。

【0079】

乾式法あるいは湿式法で得られた焼結体のバルク抵抗をターゲット全体として均一化するために還元処理ことが好ましい。還元工程は、必要に応じて設けられる工程である。適用することができる還元方法としては、例えば、還元性ガスによる方法や真空焼成又は不活性ガスによる還元等が挙げられる。

還元性ガスによる還元処理の場合、水素、メタン、一酸化炭素や、これらのガスと酸素との混合ガス等を用いることができる。

不活性ガス中での焼成による還元処理の場合、窒素、アルゴンや、これらのガスと酸素との混合ガス等を用いることができる。

尚、還元処理時の温度は、通常300〜1200℃、好ましくは500〜800℃である。また、還元処理の時間は、通常0.01〜10時間、好ましくは0.05〜5時間である。

【0080】

酸化物焼結体に、研磨等の加工を施すことによりターゲットとなる。具体的には、焼結体を、例えば、平面研削盤で研削して表面粗さRaを5μm以下とする。表面粗さは、Ra≦0.3μmであることがより好ましく、Ra≦0.1μmであることが特に好ましい。さらに、ターゲットのスパッタ面に鏡面加工を施して、平均表面粗さRaが1000オングストローム以下としてもよい。この鏡面加工(研磨)は機械的な研磨、化学研磨、メカノケミカル研磨(機械的な研磨と化学研磨の併用)等の、すでに知られている研磨技術を用いることができる。例えば、固定砥粒ポリッシャー(ポリッシュ液:水)で#2000以上にポリッシングしたり、又は遊離砥粒ラップ(研磨材:SiCペースト等)にてラッピング後、研磨材をダイヤモンドペーストに換えてラッピングすることによって得ることができる。このような研磨方法には特に制限はない。

【0081】

尚、ターゲットの清浄処理には、エアーブローや流水洗浄等を使用できる。エアーブローで異物を除去する際には、ノズルの向い側から集塵機で吸気を行なうとより有効に除去できる。エアーブローや流水洗浄の他に、超音波洗浄等を行なうこともできる。超音波洗浄では、周波数25〜300KHzの間で多重発振させて行なう方法が有効である。例えば周波数25〜300KHzの間で、25KHz刻みに12種類の周波数を多重発振させて超音波洗浄を行なうのがよい。

【0082】

得られたターゲットを加工後、バッキングプレートへボンディングすることにより、成膜装置に装着して使用できるスパッタリングターゲットとなる。バッキングプレートは銅製が好ましい。ボンディングにはインジウム半田を用いることが好ましい。

【0083】

加工工程は、上記のようにして焼結して得られた焼結体を、さらにスパッタリング装置への装着に適した形状に切削加工し、またバッキングプレート等の装着用治具を取り付けるための、必要に応じて設けられる工程である。ターゲットの厚みは通常2〜20mm、好ましくは3〜12mm、特に好ましくは4〜6mmである。また、複数のターゲットを一つのバッキングプレートに取り付け、実質一つのターゲットとしてもよい。また、表面は200〜10,000番のダイヤモンド砥石により仕上げを行うことが好ましく、400〜5,000番のダイヤモンド砥石により仕上げを行うことが特に好ましい。200番より小さい、あるいは10,000番より大きいダイヤモンド砥石を使用するとターゲットが割れやすくなるおそれがある。

【0084】

ターゲット中における各化合物の粒径は、それぞれ20μm以下が好ましく、10μm以下がさらに好ましく、5μm以下が特に好ましい。尚、粒径は電子プローブマイクロアナライザ(EPMA)で測定した平均粒径である。結晶粒径は、例えば、原料である酸化インジウム、酸化スズ、酸化亜鉛の各粉体の配合比や原料粉体の粒径、純度、昇温時間、焼結温度、焼結時間、焼結雰囲気、降温時間を調製することにより得られる。化合物の粒径が20μmより大きいとスパッタ時にノジュールが発生するおそれがある。

【0085】

ターゲットの相対密度は、理論密度の95%以上が好ましく、98%以上がより好ましく、99%以上が特に好ましい。ターゲットの密度が95%より小さいと強度が不十分となり成膜時にターゲットが破損するおそれがある。また、トランジスタを作製した際に性能が不均一になるおそれがある。相対密度とは、加重平均より算出した理論密度に対して相対的に算出した密度である。各原料の密度の加重平均より算出した密度が理論密度であり、これを100%とする。

ターゲットのバルク抵抗は、20mΩ以下が好ましく、10mΩ以下がより好ましく、5mΩ以下が特に好ましい。20mΩより大きいとDCスパッタでの成膜時にターゲットが破損するおそれがある。また、異常放電によりスパークが発生し、ターゲットが割れたり、スパークにより飛び出した粒子が成膜基板に付着し、酸化物半導体膜としての性能を低下させたりする場合がある。また、放電時にターゲットが割れるおそれもある。尚、バルク抵抗は抵抗率計を使用し、四探針法により測定した値である。

【0086】

ターゲットの抗折力は、8kg/mm2以上であることが好ましく、10kg/mm2以上であることがより好ましく、12kg/mm2以上であることが特に好ましい。ターゲットの運搬、取り付け時に荷重がかかり、ターゲットが破損するおそれがあるという理由で、ターゲットには、一定以上の抗折力が要求され、8kg/mm2未満では、ターゲットとしての使用に耐えられないおそれがある。ターゲットの抗折力は、JIS R 1601に準じて測定することができる。

【0087】

ターゲット内における亜鉛以外の、陽性元素のばらつきの範囲が0.5%以内であることが好ましい。ターゲット内における密度のばらつきの範囲が3%以内であることが好ましい。

ターゲットの表面粗さRa≦0.5μmであり、方向性のない研削面を備えていることが好ましい。Raが0.5μmより大きかったり、研磨面に方向性があると、異常放電が起きたり、パーティクルが発生するおそれがある。

ターゲット内におけるフェレー径2μm以上のピンホール数が単位面積当たり50個/mm2以下が好ましく、20個/mm2以下がより好ましく、5個/mm2以下がさらに好ましい。尚、ターゲット内部のフェレー径2μm以上のピンホール数が50個/mm2より多いと、ターゲット使用初期から末期までに異常放電が多発する傾向になって好ましくなく、また、得られるスパッタ膜の平滑性も低下する傾向にある。ターゲット内部のフェレー径2μm以上のピンホールが5個/mm2以下だと、ターゲット使用初期から末期まで異常放電を抑制でき、また、得られるスパッタ膜は非常に平滑である。ここで、フェレー径とは、ピンホールを粒子として見立てた場合に、粒子を挟むある一定方向の平行線間隔のことをいう。例えば、倍率100倍のSEM像による観察で計測できる。

【0088】

本発明の半導体膜は、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であり、Snの平均価数が+3.2以上であることを特徴とする。Snの平均価数は+3.6以上が好ましく、+3.8以上がさらに好ましい。

本発明の半導体膜は、上述した本発明のスパッタリングターゲットを使用して、成膜することで作製できる。電界効果型トランジスタの半導体層等に好適に使用できる。

尚、Snの平均価数は、X線光電子分光法(XPS)で測定した値である。

【実施例】

【0089】

電界効果型トランジストを作製する前に、トランジスタの半導体層となる酸化物半導体膜を成膜し、エッチング性等、薄膜の特性を評価した。

【0090】

評価例1

(1)スパッタリングターゲットの製造

原料として、酸化インジウム、酸化亜鉛及び酸化錫の粉末を、原子比〔In/(In+Sn+Zn)〕が0.38、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/((In+Sn+Zn)〕が0.47となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。酸化インジウム、酸化亜鉛及び酸化錫の原料粉末の比表面積はそれぞれ15m2/g、4m2/g、8m2/gであった。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形し、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体を得た。焼結体のバルク抵抗は3mΩ、理論相対密度は0.99であった。尚、理論相対密度は各酸化物の比重とその量比から計算した密度を、アルキメデス法で測定した密度との比率を計算して求めた。また、組成を分析したところ原子比〔In/(In+Sn+Zn)〕が0.38、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/((In+Sn+Zn)〕が0.47であり、Na含有量が100ppm未満であった。X線回折で構造解析をしたところ、焼結体はビックスバイト構造化合物とスピネル構造化合物を含んでいた。電子プローブマイクロアナライザ(EPMA)で測定した平均粒径は、ビックスバイト構造化合物及びスピネル構造化合物ともに10μm以下であった。

焼結体を加工・清浄処理した後、バッキングプレートにボンディングしてスパッタリングターゲットとした。

【0091】

(2)薄膜作製と評価

ガラス基板(コーニング1737)上に、上記(1)で製造したターゲットを使用して半導体層に相当する膜を形成し評価した。

スパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar97%及び酸素3%、スパッタ圧力(全圧);5×10−1Pa、投入電力100W、S−T距離100mmとした。

得られた薄膜をICP法で分析した。原子比〔In/(In+Sn+Zn)〕が0.40、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/(In+Sn+Zn)〕が0.45であった。

上記薄膜を大気下で、280℃で1時間の熱処理を行った。

得た薄膜について、XPSで測定したSn平均価数は、+3.8以上であった。尚、平均価数は、Snの5sバンドの相対強度から求めることができる。

また、X線局所構造解析(XAFS)法を用いたIn、Sn、Zn各金属元素周辺の局所構造解析において、Sn元素周りの構造はSnO2と同様の構造を有しており、In、Zn元素周りの構造はIZO薄膜と同様の構造を有していることが確認できた。

また、比抵抗は10Ωcm、キャリア密度は1016cm−3であった。さらに、ホール効果の温度変化測定から非縮退半導体であることを確認した。

また、以下の項目について評価した。結果を表1に示す。

【0092】

(1)結晶性

X線結晶構造解析により、ハローパターンが観測されたものを非晶質であると判断した。

(2)PAN耐性

PANによるエッチング速度が10nm/分以上のものを×とし、それ以外のものを○とした。

ここで、PAN耐性の評価には、40℃のPANエッチング液(リン酸87wt%、硝酸3wt%、酢酸10wt%)を用いた。PANエッチング液(リン酸、硝酸、酢酸を含むエッチング液)は、通常リン酸が20〜95wt%、硝酸0.5〜5wt%、酢酸3〜50wt%の範囲にあるものが用いられる。

(3)蓚酸に対するエッチング性

蓚酸系エッチング液として、35℃のITO−06N(関東化学(株))を用いエッチング速度を測定した。尚、150%オーバーエッチング後に顕微鏡観察して残渣の有無を確認した。○は残渣が少ないときであり、×は残渣が多いときである。

エッチング性の評価において、◎が最も良好で、○は良好で、×は不良を示す。

(4)ドライエッチング性

反応性イオンエッチング(RIE)のエッチングレートを測定した。エッチングレート1nm/分以上でエッチング可能であったものをドライエッチング可能(○)と判定した。

【0093】

評価例2−24

原料粉末を配合比、成膜条件を、表1〜3に示すように変更した他は、評価例1と同様にして、酸化物半導体膜を形成し、評価した。

尚、評価例18で作製したターゲットのバルク抵抗は2mΩ、理論相対密度は0.99であった。また、評価例1と同様にして得た薄膜についてXPSで測定したSn平均価数は、+3.8以上であった。

【0094】

評価例25−27

原料粉末を配合比、成膜条件を、表3に示すように変更した他は、評価例1と同様にして、酸化物半導体膜を形成し、評価した。

【0095】

【表1】

【0096】

【表2】

【0097】

【表3】

【0098】

[電界効果トランジスタの作製]

実施例1−17

図1に示すボトムゲート構造のエッチストッパー(ES)型の電界効果トランジスタを作製した。以下、図面を参照しながら製造過程を説明する。

図3a及び図3bは電界効果トランジスタの製造工程を示す図である。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した(図3a(a))。

次に、ゲート電極11を作製した基板に、プラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした(図3a(b))。

次に、評価例1−17で製造した半導体層用ターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜12上に半導体層13(膜厚30nm)を成膜した(図3a(c))。スパッタ条件は、上述した評価例と同様とした。

次に、280℃で1時間(後述する保護層形成後の熱処理と同じ条件)熱処理した。

【0099】

次に、PECVDにてSiOxを成膜し、薄膜16を形成した(図3a(d))。続けて、レジスト膜21を成膜し(図3a(e))、パターニングした(図3a(f))。

ドライエッチ(RIE)で薄膜16をパターニングして第一の保護層16(エッチストッパー)を形成した(図3b(g))。

レジスト膜21を除去した(図3b(h))。その後、ソース電極及びドレイン電極となる薄膜22を形成した(図3b(i))。薄膜22は、DCスパッタリングでTi/Al/Ti積層膜とした。成膜後、ドライエッチ(RIE)でパターニングしてソース電極14、ドレイン電極15を形成した。同時に半導体層13もエッチングした(図3b(j))。

さらに、PECVD(PECVD SiNx:H)にてSiNxを成膜し第二の保護層17とした(図3b(k))。コンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理して、W=20μm、L=5μmのボトムゲート構造エッチストッパー型電界効果型トランジスタを製造した(図3b(l))。

【0100】

電界効果型トランジスタについて、下記の評価を行った。

(1)電界効果移動度(μ)、オンオフ比、オフ電流、S値、閾値電圧(Vth)

半導体パラメーターアナライザー(ケースレー4200)を用い、室温、遮光環境下で測定した。

(2)ヒステリシス

半導体パラメーターアナライザーを用い、昇電圧時の伝達曲線(I−V特性)と降電圧時の伝達曲線(I−V特性)を測定し、昇降時の電圧の差をΔVgとする。ΔVgの最大値が0.5V以下であるものを「少ない」、0.5〜3Vであるものを「ある」、3V以上であるものを「大きい」とした。

尚、図4は、昇電圧時及び降電圧時の伝達曲線(I−V特性)の例であり、(a)はヒステリシスの少ない例であり、(b)はヒステリシスの大きい例を示す。

(3)閾値電圧のシフト(ストレス試験)

ストレス条件は、ゲート電圧20Vで10μAの直流電圧を50℃で105秒加えることとした。ストレスをかける前後のVthを比較し、閾値電圧のシフト量(ΔVth)を測定した。

(4)耐湿性

湿度85%環境下に120時間放置し、閾値電圧のシフトを評価した。

◎:変化量が0.5V未満、○:変化量が0.5V以上2V未満、△:変化量が2V以上5V以下、×:変化量が5V以上

実施例1及び実施例1と同じ形状トランジスタの実施例2−39について、電界効果型トランジスタの素子構成を表4−6に示す。

また、評価結果を表7、8に示す。

【0101】

【表4】

【0102】

【表5】

【0103】

【表6】

【0104】

【表7】

【0105】

【表8】

【0106】

実施例18−25

半導体層形成時の条件を表4、5に示す評価例と同様にした他は、実施例1と同様にトランジスタを作製し、評価した。結果を表7に示す。

【0107】

実施例26−32

表4、5に示すように、半導体層の形成、ソース・ドレイン電極を変更し、半導体層の形成とソース・ドレイン電極の形成をウェットエッチングで行った以外は、実施例1と同様に作製・評価した。

尚、半導体層は修酸系エッチング液を用いパターニングし、ソース電極・ドレイン電極は、PAN系エッチング液を用いパターニングした。

【0108】

実施例33,34

表6に示したようにTFTの構造、製造プロセスを変えた以外は、実施例1と同様にトランジスタを作製し、評価した。

【0109】

実施例35−37

表6に示したように、TFTの構造、製造プロセスを変えた以外は、実施例1と同様にトランジスタを作製し、評価した。

【0110】

実施例38,39

表6に示したように、半導体層成膜時の酸素分圧を変更した以外は実施例1と同様にトランジスタを作製・評価した。

【0111】

実施例40

図5に示す、ボトムゲートエッチストッパー電界効果型トランジスタを作製し、実施例1同様に評価した。尚、図5(a)は実施例40で作製した電界効果型トランジスタの概略断面図であり、(b)は各部材の位置関係を示した概略上面図である。図5(a)は、図5(b)のA−A断面図である。各部材の付番は図1と同様とし、説明を省略する。

本実施例では、熱酸化膜11’(SiOx、100nm)付Si基板10’を用い、表9に示したTFTの構造、製造プロセスでトランジスタを作製した。Si基板10’がゲート電極を兼ねている。

実施例40及び実施例40と同じ形状トランジスタの実施例41−46について、電界効果型トランジスタの素子構成を表9に示す。

また、評価結果を表10に示す。

【0112】

【表9】

【0113】

【表10】

【0114】

実施例41

第一の保護層をHfOxとした他は、実施例40と同様にボトムゲート構造エッチストッパー型電界効果型トランジスタを作製・評価した。

【0115】

実施例42−46

表9に示すように、各電極、第一の保護層及び第二の保護層、作製プロセスを変更した他は、実施例40と同様の構造の電界効果型トランジスタを作製し、評価した。

【0116】

実施例47

図6に示すボトムゲート構造のバックチャンネルエッチ(BCH)型の電界効果トランジスタを作製した。尚、各部材の付番は図1と同様とし、説明を省略する。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した。

次に、ゲート電極11を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした。

次に、評価例18で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜した。スパッタ条件は、評価例18と同様とした。

【0117】

その後、修酸系エッチング液を用い、ウェットエッチでパターニングして半導体層13(膜厚30nm)を形成した。

続いて、DCスパッタリングでAl−Nd合金膜を成膜した。成膜後、PAN系エッチング液を用い、ウェットエッチでパターニングしてソース電極・ドレイン電極14,15を形成した。

次に、PECVDにて、SiOxを成膜して、第一の保護層16とした。

さらに、第二の保護層17として、PECVD(PECVD SiNx:H)にてSiNxを成膜したのちコンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理してW=20μm、L=5μmのボトムゲート構造バックチャンネルエッチ型電界効果型トランジスタを製造した。

実施例47及び実施例47と同じ形状トランジスタの実施例48−51について、電界効果型トランジスタの素子構成を表11に示す。

また、評価結果を表12に示す。

【0118】

【表11】

【0119】

【表12】

【0120】

実施例48−51

表11に示すように、各電極、第一の保護層及び第二の保護層、作製プロセスを変更した他は、実施例47と同様の構造の電界効果型トランジスタを作製し、評価した。

【0121】

実施例52及び53

表13に示す条件で、図7に示すコプラナー構造電界効果型トランジスタを作製し、評価した。尚、各部材の付番は図1と同様とし、説明を省略する。

ガラス基板10上にゲート電極11及びゲート絶縁膜12を形成した(図7(a)(b))。半導体層13を形成した後、第一の保護層16’を成膜した(図7(c))。

第一の保護層16’上にレジスト膜21を形成した(図7(d))。基板10側から光を照射し、ゲート電極11をマスクとするようにして、レジスト膜の一部21’を露光し、除去した(図7(e)(f))。その後、第一の保護層16’をゲート電極11と整合するようパターニングし第一の保護層16とした(図7(g))。

PECVD(PECVD SiNx:H)にてSiNxを成膜し、第二の保護層17を形成すると同時に、半導体層部分13の第一の保護層16で覆われていない部分13aを低抵抗化させ、低抵抗化した半導体層部分13aとした(図7(h))。コンタクトホール18を形成し、ドレイン電極14及びソース電極15と接続して、コプラナー構造電界効果型トランジスタを作製した(図7(i))。

評価結果を表14に示す。

【0122】

【表13】

【0123】

【表14】

【0124】

尚、実施例52の半導体層、ソース・ドレイン電極と同様の条件でガラス基板上に薄膜を作製し、ホール効果の温度特性を評価した。半導体層と同一条件で作製した薄膜は温度依存性を示し非縮退半導体、ソース・ドレイン電極と同一条件で作製した薄膜は温度依存性を示さず縮退半導体であった。

図8に移動度の温度依存性を示す。直線の傾きから活性化エネルギーを計算できる。図中(1)がソース・ドレイン電極に相当し、(2)が半導体層に相当する。半導体層に相当する膜は活性化エネルギー約35meVで熱活性型を示し非縮退半導体であること、ソース・ドレイン電極に相当する膜は活性化エネルギー3meV未満で縮退半導体であることが確認できた。

【0125】

実施例54

表13に示す条件で、図9に示すトップゲート構造電界効果型トランジスタを作製し、評価した。尚、第一の保護層を積層構造とし、半導体層13成膜前に形成した。基板10側にPECVDでSiNxを成膜した第一の保護層16bを、その上にPECVDでSiO2を成膜した第一の保護層16aを形成した。

トランジスタの評価結果を表14に示す。

【0126】

実施例55

表13に示す条件で、図10に示す電界効果トランジスタを作製した。このトランジスタは、図1に示すボトムゲート構造のエッチストッパー(ES)型の電界効果トランジスタにおいて、ソース電極及びドレイン電極を、半導体層の一部を低抵抗化することで形成したものである。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした。

次に、評価例18で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜した。スパッタ条件は、評価例18と同じとした。

その後蓚酸系のウェットエッチング液でパターニングして半導体層13(膜厚40nm)を形成した。

【0127】

次に、PECVDにて、SiOxを成膜、ドライエッチ(RIE)でパターニングして、第一の保護層16(エッチストッパー)とした。

ここまでの工程で、図3b(h)に示す、第一の保護層16が形成された基板を得た。

その後、第二の保護層17として、PECVD(PECVD SiNx:H)にてSiNxを成膜すると同時に、半導体層13の一部を低抵抗化させソース電極14・ドレイン電極15を形成した。尚、SiNxを成膜した際の水素プラズマにより半導体層の一部が低抵抗化する。

その後、コンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理してW=20μm、L=5μmのボトムゲート構造コプラナー型電界効果型トランジスタを製造した。

トランジスタの評価結果を表14に示す。

【0128】

実施例56−58

表13に示すように、半導体層の形成、ソース・ドレイン電極を変更し、半導体層の形成とソース・ドレイン電極の形成をウェットエッチングで行った以外は、実施例1と同様に作製・評価した。

尚、半導体層は修酸系エッチング液を用いパターニングし、ソース電極・ドレイン電極は、PAN系エッチング液を用いパターニングした。

【0129】

比較例1−5

表15に示す構成のボトムゲート構造バックチャンネルエッチ型電界効果型トランジスタを作製した。

半導体層は、表16に示す条件で、2種のターゲット(ZnOとIn2O3−SnO2(原子比In:Sn=1:1))を用いコスパッタで形成した。

図11は、コスパッタによる薄膜形成の概念図である。

回転台31に基板10を固定し、スパッタ処理中に軸32によって回転台31を回転させる。これにより、In2O3−SnO2ターゲット33及びZnOターゲット34の両者を使用した成膜ができる。

尚、ZnOターゲットはRFスパッタ、In2O3−SnO2(原子比In:Sn=1:1)ターゲットはDCスパッタを用い成膜した。

実施例1と同様に、XPSで測定した比較例1及び5のSn平均価数は、それぞれ+2.9、+3.0であった。

尚、比較例で作製した電界効果型トランジスタの素子構成を表15に示す。また、比較例で使用した半導体層の成膜条件、半導体層の組成、特性を表16、17に示す。さらに、比較例のトランジスタの評価結果を表18に示す。

【0130】

【表15】

【0131】

【表16】

【0132】

【表17】

【0133】

【表18】

【0134】

比較例6−14

半導体層の組成比を表16、17に示すように変えた他は、実施例1と同様にして、電界効果型トランジスタを製造し、評価した。

【0135】

比較例15−19

表17に示す条件で半導体層を形成し、表15に示したTFT構造及び製造プロセスとした他は、実施例1と同様にして、電界効果型トランジスタを製造し、評価した。

【0136】

比較例20

組成比を変更し、半導体層をドライエッチした他は、実施例55と同様に電界効果型トランジスタを作製し、評価した。

その結果、半導体層の組成比が同じである比較例13と比べて、トランジスタ特性が大幅に低下した。半導体の一部を低抵抗化させる際に錫の低級酸化物が生成してしまいコンタクト抵抗が大きくなったためと考えられる。これは錫の量が多く、Sn/Zn比も大きいことが原因と考えられる。

【0137】

[実施例及び比較例の検討]

(1)半導体層におけるZn量(Zn/(In+Sn+Zn))

図12にInとSn比を一定にした時のZn量(Zn/(In+Sn+Zn))と移動度(a)、オフ電流(b)の関係を示した。図12において、実施例の測定値に基づく線をAで、比較例の測定値に基づく線をBで示してある。

保護層の無い比較例1〜5に比べ、保護層を形成した後に熱処理を加えたものは、Zn量が増えても移動度が低下しなかった。Zn/(In+Sn+Zn)=0.6付近で非常に高い移動度と低いオフ電流を示し、実用的なTFTが構成できることが分かる。

【0138】

(2)In量(In/(In+Sn+Zn))、あるいはSn量(Sn/(In+Sn+Zn))

図13にZn量を一定にした時のIn量(In/(In+Sn+Zn))と移動度(a)、オフ電流(b)の関係を示す。図13は、実施例18−25から得られた結果を、図2に示す組成領域1−3について、熱処理温度を変えて比較した結果を示している。350℃で熱処理した場合は、移動度が高いオフ電流が低いなど領域3の特性が良好で、200℃で熱処理した場合は、移動度が高いなど領域2の特性が良好であった。

また、保護層を付けた後に280℃熱処理を加えたものはSn/In比が0.33から1付近で非常に高い移動度と低いオフ電流を示し、実用的なTFTが構成できることが分かる。

また、熱処理温度の比較からSn/In比が小さいと(Sn量が少ないと)、低温の熱処理でも良好なTFT特性が得られ、適正な錫量で低温プロセスに対応できることが分かる。

【0139】

(3)保護層

比較例18と実施例42の比較から、第一の保護層の形成後に熱処理をすることで、トランジスタ特性の向上(オンオフ比の向上、オフ電流の低減、S値の低減、閾値電圧の低減)と耐湿性の向上の効果が確認できた。

実施例42と実施例40の比較から、第二の保護層の形成後に熱処理をすることで、さらに耐湿性やS値が向上することが分かった。

同様に、実施例1と比較例19の比較から、第一、第二の保護層により、トランジスタ特性の向上(オンオフ比の向上、オフ電流の低減、S値の低減、閾値電圧の低減)と耐湿性の向上の効果が分かった。

【0140】

(4)錫原子の添加

比較例17と19の比較から、保護層が無い状態でも錫の添加により耐湿性が向上することが分かった。

また、実施例15、12、8、比較例8の雰囲気温度による閾値電圧のシフト量(ΔVth(temp))を比較した。Snを含まない比較例8はΔVth(temp)が12V以上であったのに対して、Snを含む実施例15、12、8はΔVth(temp)が6V以下であった。Snが含まれることにより雰囲気温度に対する安定性も改良されていることが確認できた。

尚、雰囲気温度25℃と80℃でのVthの差(Vth(25℃)−Vth(80℃))を雰囲気温度による閾値電圧のシフト量(ΔVth(temp))とした。

【0141】

(5)成膜時の酸素分圧

実施例1,38,39から、酸素分圧5×10−3Paから2.5×10−2Paで良好な特性が得られることが分かった。

【0142】

(6)半導体層の組成領域によるプロセス上の特徴

図2に示す各領域は、下記のプロセスが適用できることが確認できた。尚、図2中、○で示した点は実施例の組成を示し、×で示した点は比較例の組成を示す。

領域1:半導体層の蓚酸等によるウェットエッチングが可能、ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域2:半導体層の蓚酸等によるウェットエッチングが可能

領域3:半導体層の蓚酸等によるウェットエッチングが可能、ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域4:ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域外:ソース・ドレイン電極のPAN等によるウェットエッチングが可能

尚、領域1〜4及びそれらの領域外ともにドライエッチングが可能であった。

【0143】

(7)ターゲット

なお、評価例1、7、19、25、26、27、比較例6、12、15のターゲットの性状を表19にまとめた。

Zn/(In+Sn+Zn)で表される原子組成比率が70原子%以下であり、In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であり、Sn/(In+Sn+Zn)で表される原子組成比率が5原子%以上15原子%未満であるターゲット(評価例7、25、26、27)の性状が、In(インジウム)含有量が少なく、Zn2SnO4で表されるスピネル構造化合物を主成分として、ターゲット性状が特に良好であった。また、電界効果トランジスタを作製した際の特性も良好であった。

【0144】

【表19】

【産業上の利用可能性】

【0145】

本発明の電界効果型トランジスタは、ディスプレイ用パネル、RFIDタグ、

X線ディテクタパネル・指紋センサ・フォトセンサ等のセンサ等に好適に使用できる。

上記に本発明の実施形態及び/又は実施例を幾つか詳細に説明したが、当業者は、本発明の新規な教示及び効果から実質的に離れることなく、これら例示である実施形態及び/又は実施例に多くの変更を加えることが容易である。従って、これらの多くの変更は本発明の範囲に含まれる。

この明細書に記載の文献の内容を全てここに援用する。

【技術分野】

【0001】

本発明は、電界効果型トランジスタ、その製造方法及びスパッタリングターゲットに関する。

【背景技術】

【0002】

電界効果型トランジスタは、半導体メモリ集積回路の単位電子素子、高周波信号増幅素子、液晶駆動用素子等として広く用いられており、現在、最も多く実用化されている電子デバイスである。

そのなかでも、近年における表示装置のめざましい発展に伴い、液晶表示装置(LCD)のみならず、エレクトロルミネッセンス表示装置(EL)や、フィールドエミッションディスプレイ(FED)等の各種の表示装置において、表示素子に駆動電圧を印加して表示装置を駆動させるスイッチング素子として、薄膜トランジスタ(TFT)が多用されている。

【0003】

薄膜トランジスタの材料としては、シリコン系半導体が広く用いられている。一般に、高速動作が必要な高周波増幅素子、集積回路用素子等には、結晶系シリコンが用いられ、液晶駆動用素子等には、大面積化の要求からアモルファスシリコンが用いられている。

しかしながら、結晶系シリコンは、結晶化を図る際に、例えば、800℃以上の高温やエキシマーレーザーによる加熱が必要となり、大面積基板への構成が困難で、製造に際して多大なエネルギーと工程数を要する等の問題があった。さらに、結晶系シリコンは通常TFTの素子構成がトップゲート構成に限定されるためマスク枚数の削減等コストダウンが困難であった。

【0004】

一方、比較的低温で形成できる非晶性のシリコン半導体(アモルファスシリコン)は、移動度(電界効果移動度)が0.5cm2/Vs程度と小さく、結晶系のものに比べてスイッチング速度が遅いため、大画面・高精細・高周波数の動画の表示に追従できない場合がある。また、アモルファスシリコンを用いた電界効果トランジスタは直流電流ストレスに対する安定性(信頼性)が低く、直流電流駆動を行う有機EL等の自発光表示素子の駆動への応用が困難であるという問題点があった。

【0005】

尚、現在、表示装置を駆動させるスイッチング素子としては、シリコン系の半導体膜を用いた素子が主流を占めているが、それは、シリコン薄膜の安定性、加工性の良さの他、スイッチング速度が速い等、種々の性能が良好なためである。そして、このようなシリコン系薄膜は、一般に化学蒸気析出法(CVD)法により製造されている。

【0006】

また、従来のTFTには、ガラス等の基板上にゲ−ト電極、ゲ−ト絶縁層、水素化アモルファスシリコン(a−Si:H)等の半導体層、ソ−ス及びドレイン電極を積層した逆スタガ構造のものがある。このTFTは、イメ−ジセンサを始め、大面積デバイスの分野において、アクティブマトリクス型の液晶ディスプレイに代表されるフラットパネルディスプレイ等の駆動素子として用いられている。これらの用途では、高機能化(大画面・高精細・高周波数対応)に伴い、さらなる作動の高速化が求められている。

【0007】

このような状況下、トランジスタ性能(移動度、安定性)と大面積化の両立が期待できる半導体として、酸化物を用いた酸化物半導体が注目されている。

しかしながら、このような酸化物半導体のうち、従来からある酸化亜鉛を用いたものは、移動度が低い、オンオフ比が低い、漏れ電流が大きい、ピンチオフが不明瞭、ノーマリーオンになりやすい等、TFTの性能が低い。また、耐薬品性が劣るため、ウェットエッチングが難しい等、製造プロセスや使用環境の制限があった。

さらに、性能を上げるためには、酸化物半導体を高い圧力で成膜する必要があるため、成膜速度が遅く、また、700℃以上の高温処理が必要であった。また、トップゲート構成では酸化物半導体の膜厚を50nm以上にする必要がある等、実用上の制限が多かった。

【0008】

このような問題を解決するために、酸化インジウム及び酸化亜鉛からなる非晶質酸化物半導体、又は酸化インジウム、酸化亜鉛及び酸化ガリウムからなる非晶質酸化物半導体を用いた電界効果型トランジスタが検討されている。しかしながら、ガリウム(Ga)を添加しないと耐湿性等の環境安定性が不足する一方、Gaの添加量が増えると移動度やS値等のTFT特性が低下するおそれがあった。また、Gaはレアメタルであるためコストが高く、安定供給に問題があった。

【0009】

そこで、Gaを用いないものとして、酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体を用いた電界効果型トランジスタが検討されている(例えば、特許文献1参照。)。

酸化錫を用いた電界効果型トランジスタは古くから検討されていたが、オフ電流が高く移動度が低いため実用化されなかった。これは、酸化錫では絶縁体である低級酸化物(SnO等)が生成しやすいためであると考えられていた。このことから酸化錫は半導体材料として適しないと考えられていた。実際、錫を主成分とした酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体を用いた電界効果トランジスタでは、オフ電流やヒステリシスが大きく、閾値電圧(Vth)が大きく負となっていた。さらに、熱処理により移動度は向上できるが、熱処理温度に応じ閾値電圧が負方向に大きくシフトするため、各トランジスタの性能のばらつきが大きい、信頼性が低い等、実用化を妨げる問題があった(例えば、非特許文献1参照)。

【0010】

また、コスパッタを用いた錫を主成分としない酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体の検討されている。この半導体では、亜鉛が25原子%以上含まれると移動度が低下し、閾値電圧が大きくなり、一方亜鉛が25原子%未満含まれるとS値が大きくなり閾値電圧が負となり、トランジスタ特性のよい電界効果トランジスタが作製できる組成比を見出すことは困難と考えられていた(例えば、非特許文献2参照)。

【0011】

このような状況であったため、酸化インジウム、酸化亜鉛及び酸化錫からなる非晶質酸化物半導体ではディスプレイ用パネル等の実用に適した電界効果型トランジスタの作製は困難と思われていた。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】WO2005/088726 A1

【非特許文献】

【0013】

【非特許文献1】M.S.Grover et al.,J.Phys.D.40,1335(2007)

【非特許文献2】Kachirayil J.Saji et al., JOURNAL OF THE ELECTROCHEMICAL SOCIETY,155(6),H390−395(2008)

【発明の概要】

【0014】

本発明の目的は、トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供することである。

【0015】

本発明によれば、以下の電界効果型トランジスタ等が提供される。

1.基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、

前記ソース電極とドレイン電極が、半導体層を介して接続してあり、

前記ゲート電極と前記半導体層の間にゲート絶縁膜があり、

前記半導体層の少なくとも一面側に保護層を有し、

前記半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満

であることを特徴とする電界効果型トランジスタ。

2.前記半導体層が下記条件1を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件1

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上23原子%未満

3.前記半導体層が下記条件2を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件2

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が1原子%以上10原子%未満

4.前記半導体層が下記条件3を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件3

(1)Zn/(In+Sn+Zn)で表される原子組成比率が50原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が23原子%以上30原子%以下

5.前記半導体層が下記条件4を満たすことを特徴とする1記載の電界効果型トランジスタ。

・条件4

(1)Zn/(In+Sn+Zn)で表される原子組成比率が65原子%超75原子%以下

6.前記保護層が酸化物からなることを特徴とする1〜5のいずれかに記載の電界効果型トランジスタ。

7.前記保護層が、酸化物からなる第一の保護層と、窒化物からなる第二の保護層とからなることを特徴とする1〜5のいずれかに記載の電界効果型トランジスタ。

8.電界効果移動度が3cm2/Vs以上、オフ電流が2×10−12A以下、閾値電圧(Vth)が−1V以上5V以下であることを特徴とする1〜7のいずれかに記載の電界効果型トランジスタ。

9.In原子、Sn原子及びZn原子を含有する酸化物であり、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上70原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタの半導体層形成用スパッタリングターゲット。

10.In原子、Sn原子及びZn原子を含有する酸化物であり、

Zn/(In+Sn+Zn)で表される原子組成比率が70原子%以下であり、

In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であり、

Sn/(In+Sn+Zn)で表される原子組成比率が5原子%以上15原子%未満であることを特徴とする電界効果型トランジスタの半導体層形成用スパッタリングターゲット。

11.9又は10のスパッタリングターゲットを用いて半導体層を成膜する工程を含むことを特徴とする1〜8のいずれかに記載の電界効果型トランジスタの製造方法。

12.半導体層を形成する工程、半導体層上に保護層を形成する工程、及びそれらの工程の後に150〜350℃で熱処理する工程を含むことを特徴とする11に記載の電界効果型トランジスタの製造方法。

13.半導体層の一部を低抵抗化させソース電極又はドレイン電極とする工程を含むことを特徴とする11又は12に記載の電界効果型トランジスタの製造方法。

14.1〜8のいずれかに記載の電界効果型トランジスタを具備したことを特徴とするディスプレイ用パネル。

15.In原子、Sn原子及びZn原子を含む酸化物であり、かつ、

Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、

Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満

であり、

Snの平均価数が+3.2以上であることを特徴とする半導体膜。

【0016】

本発明によれば、半導体層がIn、Sn及びZnを特定の組成比で含み、半導体層の少なくとも一面側に保護層を有することで、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)が高く実用性の高い電界効果トランジスタが得られる。

また、レアメタルであるGaを添加しなくともトランジスタ特性に優れた電界効果型トランジスタの提供が可能になった。

【図面の簡単な説明】

【0017】

【図1】本発明の一実施形態の電界効果型トランジスタの概略断面図である。

【図2】本発明における半導体層の好ましい組成条件(領域)を示す図である。

【図3a】実施例1で作製した電界効果型トランジスタの製造工程を示す図である。

【図3b】実施例1で作製した電界効果型トランジスタの製造工程を示す図である。

【図4】昇電圧時及び降電圧時の伝達曲線(I−V特性)の例であり、(a)はヒステリシスの少ない例であり、(b)はヒステリシスの大きい例を示す図である。

【図5】(a)実施例40で作製したボトムゲートエッチストッパー型の電界効果型トランジスタの概略断面図であり、(b)は同トランジスタの概略上面図である。

【図6】実施例47で作製したボトムゲート構造のバックチャンネルエッチ(BCH)型の電界効果型トランジスタの概略断面図である。

【図7】実施例52で作製したコプラナー構造電界効果型トランジスタの製造工程を示す図である。

【図8】酸化物半導体の、温度と移動度の関係を示す図である。

【図9】実施例54で作製したトップゲート構造電界効果型トランジスタの概略断面図である。

【図10】実施例55で作製した電界効果型トランジスタの概略断面図である。

【図11】コスパッタによる薄膜形成の概念図である。

【図12】(a)は半導体層のZn量と移動度の関係を示す図であり、(b)は半導体層のZn量とオフ電流の関係を示す図である。

【図13】(a)は半導体層のIn量と移動度の関係を示す図であり、(b)は半導体層のIn量とオフ電流の関係を示す図である。

【発明を実施するための形態】

【0018】

本発明の電界効果型トランジスタは、基板上に、少なくとも半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極と、ゲート絶縁膜と、ゲート電極とを有する。

図1は、本発明の一実施形態の電界効果型トランジスタの概略断面図である。

この電界効果型トランジスタでは、基板10上に、ゲート電極11がストライプ状に形成されている。このゲート電極11を覆うようにゲート絶縁膜12を有し、このゲート絶縁膜12上であって、かつ、ゲート電極12の上方に半導体層13(活性層)が形成されている。

半導体層13の一端側に、ゲート電極11と直交する方向にソース電極14が接続されている。また、半導体層13の一端に対向する他端側にドレイン電極15が接続されている。

半導体層13、ソース電極14及びドレイン電極15の中間の位置に第一の保護層16が形成されている。

ゲート絶縁膜12、ソース電極14、ドレイン電極15及び第一の保護層16を覆うように、第二の保護層17が形成されている。

第二の保護層17にはコンタクトホール18があり、外部電極と、ソース電極14又はドレイン電極15が接続されている。

尚、第二の保護層17は必ずしも必須ではないが、形成することが好ましい。

【0019】

本発明の電界効果型トランジスタでは、半導体層13がIn原子、Sn原子及びZn原子を含んでおり、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする。

【0020】

Zn/(In+Sn+Zn)を25原子%以上とすることにより、Znにより酸素欠損が抑制され、適性な閾値電圧(Vth)の電界効果トランジスタが得られる。また、75原子%以下とすることにより、酸化亜鉛(ZnO)の結晶の生成によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

Zn/(In+Sn+Zn)は30原子%以上がより好ましく、35原子%以上がさらに好ましい。

【0021】

また、Sn/(In+Sn+Zn)を50原子%未満とすることにより、酸化錫の低級酸化物の生成(Sn平均価数の低下)によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

Sn/(In+Sn+Zn)は33原子%以下が好ましく、28原子%以下がより好ましく、23原子%未満がさらに好ましく、20原子%以下が特に好ましい。33原子%以下とすることにより、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)が良好な電界効果トランジスタが得られる。また、PECVD時のプラズマ照射等、プロセス上で還元雰囲気に曝された際の、移動度等のトランジスタ特性の低下を防ぐことが出来る。これは、錫の低級酸化物の生成(Sn平均価数の低下)を抑制することができるためと思われる。

【0022】

本発明では、半導体層13がSn原子を含むことで、耐湿性の向上や、耐薬品性の向上(耐PAN性の向上含む)、雰囲気温度に対する安定性が期待できる。さらに、Snを含有することでレアメタルであるInの含有量を低減することができる。

Sn/(In+Sn+Zn)は1原子%以上であることが好ましく、3原子%以上がより好ましく、5原子%以上がさらに好ましく、10原子%以上が特に好ましい。

【0023】

半導体層の組成においては、下記の条件1〜4のいずれかを満たすことが好ましい。

・条件1

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上23原子%未満

・条件2

(1)Zn/(In+Sn+Zn)で表される原子組成比率が40原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が1原子%以上10原子%未満

・条件3

(1)Zn/(In+Sn+Zn)で表される原子組成比率が50原子%以上65原子%以下

(2)Sn/(In+Sn+Zn)で表される原子組成比率が23原子%以上30原子%以下

・条件4

(1)Zn/(In+Sn+Zn)で表される原子組成比率が65原子%超75原子%以下

【0024】

図2に本発明における半導体層の好ましい組成条件(領域)を示す。

半導体層の組成が領域1内にあると、トランジスタ特性(移動度、オンオフ比、オフ電流、S値、閾値電圧(Vth)、ヒステリシス、閾値電圧のシフト、耐湿性)に非常に優れた電界効果トランジスタが得られる。また、半導体層及びソース・ドレイン電極の形成にウェットエッチングを採用できるため、大型パネルを低いコストで製造できる。有機ELディスプレイや液晶ディスプレイ用途に特に適している。

【0025】

領域1のうち、特に下記の範囲が最も好ましい。

(1) Zn/(In+Sn+Zn)で表される原子組成比率が57原子%以上65原子%以下

(2) Sn/(In+Sn+Zn)で表される原子組成比率が10原子%以上18原子%未満

前記範囲内だと、移動度(cm2/Vs)及びオンオフ比が高く、オフ電流及びS値が小さく、かつ閾値電圧のシフトΔVth(V)が小さい良好な電界効果トランジスタが得られる。さらに、前記範囲内だと、希少資源であるIn(インジウム)の含有量も少ないため、低い原料比で良好なターゲット及び良好な電界効果トランジスタが得られ工業的に最適である。

【0026】

半導体層の組成が領域3内にあると、プロセス耐性が高くプロセス温度が高くとも劣化の危険性が少ない。また、耐湿性に優れた電界効果トランジスタが得られる。そのため、プロセス温度が高い無機ELディスプレイ用途に特に適している。

【0027】

半導体層の組成が領域2内にあると、低温の熱処理で高い特性が得られる。耐熱性の低い樹脂基板等を用いる用途(例えばフレキシブルディスプレイ)に特に適している。

【0028】

半導体層の組成が領域4内にあると、オフ電流が低い電界効果トランジスタが得られる。また、亜鉛が主成分のため原料コストが低く、製品から原料を回収する必要性がない。そのため、ディスポーザルな用途(ICタグ等)に特に適している。

【0029】

半導体層の組成において、Sn原子とIn原子の原子比(Sn/In)は、0.41以上0.69以下が特に好ましい。0.41以上だと耐湿性が向上し、0.69以下だと低温プロセスで優れたトランジスタ特性が得られる。また、酸化錫の低級酸化物の生成(Sn平均価数の低下)によるトランジスタ性能の低下(移動度の低下、オフ電流の増加、S値の増加等)を避けることが出来る。

【0030】

半導体層は、In,Sn及びZnの他に、Ga、Al、B、Sc、Y、ランタノイド類(La、Ce、Pr、Nd、Sm、Eu、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu)、Zr、Hf、Ge、Si、Ti、Mn、W、Mo、V、Cu、Ni、Co、Fe、Cr及びNbから選ばれた元素を0〜20原子%含んでいてもよい。

また、Na含有量が100ppm未満であることが好ましい。Naの含有量が100ppm未満であると、電圧による可動イオンの量が少ないため電圧ストレスに対する信頼性が向上する(ΔVthが小さくなる)。

以下、本発明の電界効果型トランジスタを構成する部材の例について説明する。

【0031】

1.基板

特に制限はなく、本技術分野で公知のものを使用できる。例えば、ケイ酸アルカリ系ガラス、無アルカリガラス、石英ガラス等のガラス基板、シリコン基板、アクリル、ポリカーボネート、ポリエチレンナフタレート(PEN)等の樹脂基板、ポリエチレンテレフタレート(PET)、ポリアミド等の高分子フィルム基材等が使用できる。基板や基材の厚さは0.1〜10mmが一般的であり、0.3〜5mmが好ましい。ガラス基板の場合は、化学的に、或いは熱的に強化させたものが好ましい。透明性や平滑性が求められる場合は、ガラス基板、樹脂基板が好ましく、ガラス基板が特に好ましい。軽量化が求められる場合は樹脂基板や高分子機材が好ましい。

【0032】

2.半導体層

半導体層は、上述したとおり、In、Zn及びSnの各原子を含む複合酸化物からなる。このような半導体層は、例えば、後述する本発明の複合酸化物ターゲット(半導体層用ターゲット)を使用して薄膜を形成することで作製できる。

また、半導体層は、粒子状の酸化物半導体を溶媒に溶かし、その酸化物半導体溶液を塗布又は印刷し、その後、加熱処理で溶媒を蒸発させることにより形成することもできる。この方法は、設備コストが低くエネルギー効率も高いため好ましい。

ゾルゲル法等の溶液の利用やCVDも利用できるが、大面積に均一に成膜するには半導体用ターゲットを用いスパッタリングで形成することが、トランジスタ特性が高くなることから最も好ましい。

【0033】

本発明において、半導体層は非晶質膜であることが好ましい。非晶質膜であることにより、絶縁膜や保護層との密着性が改善される、大面積でも均一なトランジスタ特性が容易に得られることとなる。ここで、半導体層が非晶質膜であるかは、X線結晶構造解析により確認できる。明確なピークが観測されない場合が非晶質である。

【0034】

また、半導体層の電子キャリア濃度が1013〜1018/cm3であることが好ましく、特に1014〜1017/cm3であることが好ましい。電子キャリア濃度が上記の範囲であれば、非縮退半導体となりやすく、トランジスタとして用いた際に移動度とオンオフ比のバランスが良好となり好ましい。キャリア密度が1018cm−3以下だとオフ電流を小さくでき、ノーマリーオフとしやすくなる。1013cm−3以上だと移動度を向上させることができる。

また、比抵抗は10−1〜109Ωcmであることが好ましい。より好ましくは10〜107Ωcmである。特に好ましくは、102〜105Ωcmである。10−1Ωcm以上だとオフ電流を小さくすることができる。109Ωcm以下だと移動度を高くし、閾値電圧を小さくできる。

また、バンドギャップが2.0〜6.0eVであることが好ましく、特に、2.8〜5.0eVがより好ましい。バンドギャップは、2.0eVより小さいと可視光を吸収し電界効果型トランジスタが誤動作するおそれがある。一方、6.0eVより大きいとキャリアが供給されにくくなり電界効果型トランジスタが機能しなくなるおそれがある。

【0035】

半導体層は、熱活性型を示す非縮退半導体であることが好ましい。縮退半導体であるとキャリアが多すぎてオフ電流・ゲートリーク電流が増加する、閾値が負になりノーマリーオンとなるおそれがある。半導体層が非縮退半導体であるかは、ホール効果を用いた移動度とキャリア密度の温度変化の測定を行うことにより判断できる。また、半導体層を非縮退半導体とするには、成膜時の酸素分圧を調整する、後処理をすることで酸素欠陥量を制御しキャリア密度を最適化することで達成できる。

【0036】

半導体層の表面粗さ(RMS)は、1nm以下が好ましく、0.6nm以下がさらに好ましく、0.3nm以下が特に好ましい。1nmより大きいと、移動度が低下するおそれがある。

半導体層は、酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持している非晶質膜であることが好ましい。酸化インジウムを含む非晶質膜が酸化インジウムのビックスバイト構造の稜共有構造の少なくとも一部を維持しているかどうかは、高輝度のシンクロトロン放射等を用いた微小角入射X線散乱(GIXS)によって求めた動径分布関数(RDF)により、In−X(Xは,In,Zn)を表すピークが0.30から0.36nmの間にあることで確認できる(詳細については、下記の文献を参照すればよい。F.Utsuno, et al.,Thin Solid Films,Volume 496, 2006, Pages 95−98)。

【0037】

さらに、原子間距離が0.30から0.36nmの間のRDFの最大値をA、原子間距離が0.36から0.42の間のRDFの最大値をBとした場合に、A/B>0.7の関係を満たすことが好ましく、A/B>0.85がより好ましく、A/B>1がさらに好ましく、A/B>1.2が特に好ましい。

A/Bが0.7以下だと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。A/Bが小さいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0038】

また、In−Inの平均結合距離が0.3〜0.322nmであることが好ましく、0.31〜0.32nmであることが特に好ましい。In−Inの平均結合距離はX線吸収分光法により求めることができる。X線吸収分光法による測定では、立ち上がりから数百eVも高いエネルギーのところまで広がったX線吸収広域微細構造(EXAFS)を示す。EXAFSは励起された原子の周囲の原子による電子の後方散乱によって引き起こされる。飛び出していく電子波と後方散乱された波との干渉効果が起こる。干渉は電子状態の波長と周囲の原子へ行き来する光路長に依存する。EXAFSをフーリエ変換することで動径分布関数(RDF)が得られる。RDFのピークから平均結合距離を見積もることができる。

【0039】

半導体層の膜厚は、通常0.5〜500nm、好ましくは1〜150nm、より好ましくは3〜80nm、特に好ましくは10〜60nmである。0.5nmより薄いと工業的に均一に成膜することが難しい。一方、500nmより厚いと成膜時間が長くなり工業的に採用できない。また、3〜80nmの範囲内にあると、移動度やオンオフ比等TFT特性が特に良好である。

【0040】

本発明では、非局在準位のエネルギー幅(E0)が14meV以下であることが好ましい。半導体層の非局在準位のエネルギー幅(E0)は10meV以下がより好ましく、8meV以下がさらに好ましく6meV以下が特に好ましい。非局在準位のエネルギー幅(E0)が14meVより大きいと、半導体層をトランジスタの活性層として用いた場合、移動度が低下したり、閾値やS値が大きくなりすぎるおそれがある。半導体層の非局在準位のエネルギー幅(E0)が大きいことは、非晶質膜の近距離秩序性が悪いことを反映しているものと考えられる。

【0041】

X線光電子分光法(XPS)で測定したSn平均価数は、+3.2以上が好ましく、+3.6以上がより好ましく、+3.8以上がさらに好ましい。上限は特に限定されないが通常+4.0以下である。XPS価電子帯スペクトルでは、Sn5sに起因するバンドは、低級酸化物であるSnO(Sn+2:4d105s2の電子配置)のスペクトルのみにみられ、SnO2(Sn+4:4d10の電子配置)にはみられない。そのため、Sn5sバンドの相対強度からSn平均価数を求めることができる(参照:X線光電子分光法、1998年、丸善株式会社刊)。通常、スパッタで作製したSnO2膜のSn平均価数は、+2.8程度である。

【0042】

X線局所構造解析(XAFS)法を用いたIn、Sn、Zn各金属元素周辺の局所構造解析において、Sn元素周りの構造はSnO2と同様の構造を有していると、散乱による移動度の低下が抑制できて好ましい。またIn、Zn元素周りの構造はIZO薄膜と同様の構造を有しているとZnにより非晶質が安定化され好ましい。

なお、前記解析を行うに際し、一般的な蛍光法では解析に十分なデータを得ることができないので、多素子SSD検出器を用い、且つ薄膜試料基板を微小角度に傾けて放射光を入射させる斜入射法を用いて測定を行うことが好ましい。

【0043】

3.第一及び第二の保護層

保護層により、真空中や低圧下で半導体の表面層の酸素が脱離し、オフ電流が高くなる、閾値電圧が負になることを防ぐことが出来る。また、大気下でも湿度等周囲の影響を受けず、閾値電圧等のトランジスタ特性のばらつきの発生を防ぐことが出来る。

【0044】

保護層を形成する材料は特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。保護層は酸化物からなることが特に好ましく、SiO2,Y2O3,Hf2O3,CaHfO3等の酸化物が好ましい。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

このような保護層は、異なる2層以上の絶縁膜を積層した構造でもよい。

【0045】

また、保護層は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。尚、保護層が非晶質であることが特に好ましい。非晶質膜であると界面の平滑性が良好で、移動度の向上、閾値電圧の抑制、S値の抑制効果が期待できる。また、ゲートリーク電流を抑制できる。

【0046】

半導体層の保護層は、非晶質酸化物あるいは非晶質窒化物であることが好ましく、非晶質酸化物であることが特に好ましい。また、保護層が酸化物でないと半導体中の酸素が保護層側に移動し、オフ電流が高くなったり、閾値電圧が負になりノーマリーオフを示すおそれがある。また、半導体層の保護層は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、半導体層の保護層は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

特に、半導体層に大きく接する第一の保護層を酸化物で、第二の保護層をSiNx等の窒化物で構成することが好ましい。このような構成をとると良好なトランジスタ特性と耐湿性を持たせることが容易である。

【0047】

保護層の形成は、PECVD、TEOSCVD、Cat−CVD、スパッタリング、スピンコート、印刷法等が利用できるが、工業的にはPECVDあるいはスパッタリングが好ましく、PECVDが特に好ましい。

【0048】

4.ゲート絶縁膜

ゲート絶縁膜を形成する材料にも特に制限はない。本発明の効果を失わない範囲で一般に用いられているものを任意に選択できる。例えば、SiO2,SiNx,Al2O3,Ta2O5,TiO2,MgO,ZrO2,CeO2,K2O,Li2O,Na2O,Rb2O,Sc2O3,Y2O3,Hf2O3,CaHfO3,PbTi3,BaTa2O6,SrTiO3,AlN等を用いることができる。これらのなかでも、SiO2,SiNx,Al2O3,Y2O3,Hf2O3,CaHfO3を用いるのが好ましく、より好ましくはSiO2,SiNx,Y2O3,Hf2O3,CaHfO3である。これらの酸化物の酸素数は、必ずしも化学量論比と一致していなくともよい(例えば、SiO2でもSiOxでもよい)。また、SiNxは水素元素を含んでいても良い。

【0049】

このようなゲート絶縁膜は、異なる2層以上の絶縁膜を積層した構造でもよい。また、ゲート絶縁膜は、結晶質、多結晶質、非晶質のいずれであってもよいが、工業的に製造しやすい多結晶質か、非晶質であるのが好ましい。

また、ゲート絶縁膜は、ポリ(4−ビニルフェノール)(PVP)、パリレン等の有機絶縁膜を用いてもよい。さらに、ゲート絶縁膜は無機絶縁膜及び有機絶縁膜の2層以上積層構造を有してもよい。

ゲート絶縁膜の形成は、PECVD、TEOSCVD、Cat−CVD、スパッタリング、スピンコート、印刷法等が利用できるが、工業的にはPECVDあるいはスパッタリングが好ましく、PECVDが特に好ましい。

【0050】

6.電極

ゲート電極、ソ−ス電極及びドレイン電極の各電極を形成する材料に特に制限はなく、本発明の効果を失わない範囲で一般に用いられているものを任意に選択することができる。

例えば、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物、ZnO、SnO2等の透明電極や、Al,Ag,Cr,Ni,Mo,Au,Ti,Ta、Cu等の金属電極、又はこれらを含む合金の金属電極を用いることができる。また、それらを2層以上積層して接触抵抗を低減したり、界面強度を向上させることが好ましい。また、ソ−ス電極、ドレイン電極の接触抵抗を低減させるため半導体の電極との界面をプラズマ処理、オゾン処理等で抵抗を調整してもよい。

【0051】

本発明では、半導体層の一部を低抵抗化させてソース電極又はドレイン電極を形成してもよい。

半導体層の一部を低抵抗化させるには、例えば、低酸素分圧下、不活性ガス下、低圧下又は真空下で、熱処理あるいは紫外線光等のエネルギー線を照射する方法や、水素、窒素又はアルゴン等の不活性ガス環境下でプラズマを照射する方法等がある。

また、プラズマCVDにてSiNx等で保護層を積層する際に、水素量等のプラズマ条件を調整することで低抵抗化してもよい。

【0052】

本発明の電界効果型トランジスタは、半導体層を遮光する構造を持つことが好ましい。半導体層を遮光する構造(例えば、遮光層)を持っていないと、光が半導体層に入射した場合にキャリア電子が励起されオフ電流が高くなるおそれがある。遮光層は、300〜800nmに吸収を持つ薄膜が好ましい。遮光層は半導体層の上部、下部どちらかでも構わないが、上部及び下部の両方にあることが好ましい。また、遮光層はゲート絶縁膜やブラックマトリックス等と兼用されていても構わない。遮光層が片側だけにある場合、遮光層が無い側から光が半導体層に照射しないよう構造上工夫する必要がある。

【0053】

本発明の電界効果型トランジスタでは、半導体層とソース電極・ドレイン電極との間にコンタクト層を設けてもよい。コンタクト層は半導体層よりも抵抗が低いことが好ましい。コンタクト層の形成材料は、上述した半導体層と同様な組成の複合酸化物が使用できる。即ち、コンタクト層はIn,Zn等の各元素を含むことが好ましい。これらの元素を含まないと、コンタクト層と半導体層の間で元素の移動が発生し、ストレス試験等を行った際に閾値電圧のシフトが大きくなるおそれがある。

【0054】

コンタクト層の作製方法に特に制約はないが、成膜条件を変えて半導体層と同じ組成比のコンタクト層を成膜したり、半導体層と組成比の異なる層を成膜したり、半導体の電極とのコンタクト部分をプラズマ処理やオゾン処理により抵抗を高めることで構成したり、半導体層を成膜する際に酸素分圧等の成膜条件により抵抗を高くなる層を構成してもよい。また、本発明の電界効果型トランジスタでは、半導体層とゲート絶縁膜との間、及び/又は半導体層と保護層との間に、半導体層よりも抵抗の高い酸化物抵抗層を有することが好ましい。酸化物抵抗層が無いとオフ電流が発生する、閾値電圧が負となりノーマリーオンとなる、保護層成膜やエッチング等の後処理工程時に半導体層が変質し特性が劣化するおそれがある。

【0055】

続いて、本発明の電界効果型トランジスタの製造方法について説明する。

本発明の製造方法では、後述する本発明のターゲットを用い、半導体層を成膜する工程を含む。

また、半導体層を成膜する工程、半導体層上に保護層を形成する工程を有し、保護層を形成した後に150〜350℃で熱処理する工程を含むことを特徴とする。尚、上述した電界効果型トランジスタの各構成部材(層)は、本技術分野で公知の手法で形成できる。

【0056】

具体的に、成膜方法としては、スプレー法、ディップ法、CVD法等の化学的成膜方法、又はスパッタ法、真空蒸着法、イオンプレーティング法、パルスレーザーディポジション法等の物理的成膜方法を用いることができる。キャリア密度が制御し易い、及び膜質向上が容易であることから、好ましくは物理的成膜方法を用い、より好ましくは生産性が高いことからスパッタ法を用いる。

スパッタリングでは、複合酸化物の焼結ターゲットを用いる方法、複数の焼結ターゲットを用いコスパッタを用いる方法、合金ターゲットを用い反応性スパッタを用いる方法等が利用できる。但し、複合酸化物の焼結ターゲットを用いる方法では、複数の焼結ターゲットを用いコスパッタを用いる方法や、合金ターゲットを用い反応性スパッタを用いる方法に比べ、均一性や再現性が向上し、非局在準位のエネルギー幅(E0)が低減させ、移動度の向上、S値の低減、閾値電圧の低減等、トランジスタ特性を向上させることができる。好ましくは、複合酸化物の焼結ターゲットを用いる。RF、DCあるいはACスパッタリング等公知のものが利用できるが、均一性や量産性(設備コスト、成膜速度)からDCあるいはACスパッタリングが好ましい。X線光電子分光法(XPS)で測定したSn平均価数は、+3.2以上にする観点からはRFスパッタリングが好ましい。

【0057】

成膜時の基板温度は、室温(30℃)以上250℃以下が好ましく、50℃以上200℃以下がより好ましい。250℃以下だとTFTを作製した際にオフ電流の低減が期待できる。室温(30℃)以上だと連続成膜時の基板温度上昇による成膜条件の変動の低減が期待できる。

また、成膜時に酸素の取組みを増加させるような処置を取ることが好ましい。成膜時に酸素の取組みを増加させるような処置としては、不活性ガス(アルゴン等)と酸素の混合気体を流入させる、オゾンアシストやRFスパッタリングによって酸素ラジカル(オゾン)量を増加させる、基板間距離・投入電力・全圧の調整等があげられる。

【0058】

成膜時の酸素分圧は、10−3Pa〜10−1Paで行うことが好ましく、5×10−3Pa〜10−1Paで行うことがより好ましい。酸素分圧10−3Pa以上だと酸化錫の低級酸化物の生成を抑えることができる。10−1Pa以下だと成膜速度が速くなることが期待できる。

形成した膜を各種エッチング法によりパターニングできる。

【0059】

本発明では半導体層を、本発明のターゲットを用い、DC又はACスパッタリングにより成膜することがより好ましい。DC又はACスパッタリングを用いることにより、RFスパッタリングの場合と比べて、成膜時のダメージを低減できる。XPSで測定したSn平均価数を高くしたい場合は、RFスパッタリングを用いてもよい。RFスパッタリングを用いることで、XPSで測定したSn平均価数を制御しやすい。このため、電界効果型トランジスタにおいて、閾値電圧シフトの低減、移動度の向上、閾値電圧の減少、S値の減少等の効果が期待できる。

【0060】

また、本発明では半導体層成膜後150〜350℃で熱処理することが好ましい。特に、半導体層と半導体の保護層を形成した後に、150〜350℃で熱処理することが好ましい。150℃より低いと得られるトランジスタの熱安定性や耐熱性が低下したり、移動度が低くなったり、S値が大きくなったり、閾値電圧が高くなるおそれがある。一方、350℃より高いと耐熱性のない基板が使用できない、熱処理用の設備費用がかかるおそれがある。

【0061】

熱処理温度は160〜300℃がより好ましく、170〜260℃がさらに好ましく、180〜240℃が特に好ましい。特に、熱処理温度が180℃以下であれば、基板としてPEN等の耐熱性の低い樹脂基板を利用できるため好ましい。

熱処理時間は、通常1秒〜24時間が好ましいが、処理温度により調整することが好ましい。例えば、70〜180℃では、10分から24時間がより好ましく、20分から6時間がさらに好ましく、30分〜3時間が特に好ましい。180〜260℃では、6分から4時間がより好ましく、15分から2時間がさらに好ましい。260〜300℃では、30秒から4時間がより好ましく、1分から2時間が特に好ましい。300〜350℃では、1秒から1時間がより好ましく、2秒から30分が特に好ましい。

熱処理は、不活性ガス中で酸素分圧が10−3Pa以下の環境下で行うか、あるいは半導体層を保護層で覆った後に行うことが好ましい。上記条件下だと再現性が向上する。

半導体層を形成した後に150〜350℃で熱処理し、さらに半導体の保護層を形成した後に、150〜350℃で熱処理すると特に好ましい。前記のようにすると半導体特性が改善することに加え再現性及び均一性が向上し、半導体膜の成膜条件に対する依存性も小さくなる。

【0062】

典型的な電界効果型トランジスタでは、ソース・ドレイン電極間に、5〜20V程度の電圧Vdを印加したとき、ゲート電圧Vgを、0Vと5〜20Vの間でスイッチすることで、ソース・ドレイン電極間の電流Idを制御する(オンオフする)ことができる。

トランジスタ特性の評価項目としては、さまざまなものがあるが、たとえば、電界効果移動度μ、閾値電圧(Vth)、オンオフ比、S値等が上げられる。

電界効果移動度は、線形領域や飽和領域の特性から求めることができる。たとえば、トランスファ特性の結果から、√Id―Vgのグラフを作製し、この傾きから電界効果移度を導く方法が挙げられる。本明細書では特にこだわらない限り、この手法で評価している。

閾値電圧の求め方はいくつかの方法があるが、たとえば√Id―Vgのグラフのx切片から閾値電圧Vthを導くことが挙げられる。

オンオフ比はトランスファ特性における、最も大きなIdと、最も小さなIdの値の比から求めることができる。

【0063】

そして、S値は、トランスファ特性の結果から、Log(Id)―Vdのグラフを作製し、この傾きの逆数から導出することができる。

S値の単位は、V/decadeであり、小さな値であることが好ましい。S値は1.0V/dec以下が好ましく、0.5V/dec以下がより好ましく、0.3V/dec以下がさらに好ましく、0.1V/dec以下が特に好ましい。0.8V/dec以下だと駆動電圧が小さくなり消費電力を低減できる可能性がある。特に、有機ELディスプレイで用いる場合は、直流駆動のためS値を0.3V/dec以下にすると消費電力を大幅に低減できるため好ましい。尚、S値(Swing Factor)とは、オフ状態からゲート電圧を増加させた際に、オフ状態からオン状態にかけてドレイン電流が急峻に立ち上がるが、この急峻さを示す値である。下記式で定義されるように、ドレイン電流が1桁(10倍)上昇するときのゲート電圧の増分をS値とする。

S値=dVg/dlog(Ids)

S値が小さいほど急峻な立ち上がりとなる(「薄膜トランジスタ技術のすべて」、鵜飼育弘著、2007年刊、工業調査会)。S値が大きいと、オンからオフに切り替える際に高いゲート電圧をかける必要があり、消費電力が大きくなるおそれがある。

【0064】

本発明の電界効果トランジスタでは、移動度は3cm2/Vs以上が好ましく、8cm2/Vs以上がより好ましく、10cm2/Vs以上がさらに好ましく、16cm2/Vs以上が特に好ましい。3cm2/Vsより小さいとスイッチング速度が遅くなり大画面高精細のディスプレイに用いることができないおそれがある。

オンオフ比は、107以上が好ましく、108以上がより好ましく、109以上が特に好ましい。

オフ電流は、2×10−12A(2pA)以下が好ましく、1pA以下がより好ましく、0.1pA以下が特に好ましい。オフ電流が2pAより小さいとディスプレイのTFTとして用いた場合にコントラストが良好となり、画面の均一性が向上することが期待できる。

【0065】

ゲートリーク電流は1pA以下が好ましい。1pAより小さいとディスプレイのTFTとして用いた場合にコントラストの低下を抑制できる。

閾値電圧は、通常−1〜5Vであるが、−0.5〜3Vが好ましく、0〜2Vがより好ましく、0〜1Vが特に好ましい。−1Vより大きいとオフ時にかける電圧が小さくなり消費電力を低減できる可能性がある。5Vより小さいと駆動電圧が小さくなり消費電力を低減できる可能性がある。

また、10μAの直流電圧50℃で100時間加えた前後の閾値電圧のシフト量は、1.0V以下が好ましく、0.5V以下がより好ましい。1Vより小さいと有機ELディスプレイのトランジスタとして利用した場合、画質の経時変化を低減できる。

【0066】

また、伝達曲線でゲート電圧を昇降させた場合のヒステリシスが小さい方が好ましい。ヒストリシスが小さいと駆動電圧を低減できる可能性がある。

また、チャンネル幅Wとチャンネル長Lの比W/Lは、通常0.1〜100、好ましくは0.5〜20、特に好ましくは1〜8である。W/Lが100を越えると漏れ電流が増えたり、on−off比が低下したりするおそれがある。0.1より小さいと電界効果移動度が低下したり、ピンチオフが不明瞭になったりするおそれがある。また、チャンネル長Lは通常0.1〜1000μm、好ましくは1〜100μm、さらに好ましくは2〜10μmである。0.1μm未満では工業的に製造が難しくまた漏れ電流が大きくなるおそれがある、1000μmを超えると素子が大きくなりすぎて好ましくない。

【0067】

続いて、本発明の半導体層形成用スパッタリングターゲットについて説明する。

本発明のスパッタリングターゲットは、通常In原子、Sn原子及びZnを含有し、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上70原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満である。

【0068】

さらに、In原子、Sn原子及びZn原子を含有する酸化物焼結体であり、Zn/(In+Sn+Zn)で表される原子組成比率が70原子%以下であり、In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であり、Sn/(In+Sn+Zn)で表される原子組成比率が5原子%以上15原子%未満であることがより好ましい。

【0069】

Zn/(In+Sn+Zn)が70原子%以下であると、Zn酸化物の生成による相対密度の低下やバルク抵抗の高抵抗化を防げる。In/(In+Sn+Zn)で表される原子組成比率が33原子%未満であると、原料コストの増加によるコストアップを防ぎやすい。Sn/(In+Sn+Zn)が5原子%以上だとSnとZnの価数バランスがとれターゲットの相対密度が上がりバルク抵抗を下げやすく、15原子%未満であるとSnの低級酸化物の生成によるバルク抵抗の高抵抗化を防ぎやすい。すなわち、前記範囲内であると、相対密度が高く、抵抗の低いターゲットを安定して作製できる。また、そのターゲットを用いて特性(移動度、オンオフ比、S値、ΔVthシフト)の良好な電界効果トランジスタが得られる。また、希少資源であるIn(インジウム)の含有量も少なく、安い原料比で良好なターゲットが得られ工業的に最適である。

【0070】

さらに、Zn/(In+Sn+Zn)で表される原子組成比率が60原子%以上67原子%以下であり、In/(In+Sn+Zn)で表される原子組成比率が18原子%以上28原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が7原子%以上14原子%以下であることが特に好ましい。

【0071】

ターゲットの出発原料としては、一般的に酸化インジウム粉末と、酸化亜鉛粉末と、酸化錫粉末の粉末を用いるが、これらの単体、化合物、複合酸化物等を原料としてもよい。

各原料粉の純度は、通常99.9%(3N)以上、好ましくは99.99%(4N)以上、さらに好ましくは99.995%以上、特に好ましくは99.999%(5N)以上である。各原料粉の純度が99.9%(3N)未満だと、不純物により半導体特性が低下する、信頼性が低下する等のおそれがある。特にNa含有量が100ppm未満であると薄膜トランジスタを作製した際に信頼性が向上し好ましい。

【0072】

原料粉について、比表面積が3〜16m2/gである酸化インジウム粉、酸化錫粉、亜鉛粉あるいは複合酸化物粉を含み、粉体全体の比表面積が3〜16m2/gである混合粉体を原料とすることが好ましい。尚、各酸化物粉末の比表面積が、ほぼ同じである粉末を使用することが好ましい。これにより、より効率的に粉砕混合できる。具体的には、比表面積の比が1/4〜4倍以内にすることが好まく、1/2〜2倍以内が特に好ましい。比表面積が違いすぎると、効率的な粉砕混合が出来ず、焼結体中に酸化物の粒子が残る場合がある。ただし、酸化亜鉛の比表面積は酸化インジウム、酸化錫の比表面積よりも小さいことが好ましい。このことによりターゲットの色むらを抑えることができる。

【0073】

混合粉体を、例えば、湿式媒体撹拌ミルを使用して混合粉砕する。このとき、粉砕後の比表面積が原料混合粉体の比表面積より1.0〜3.0m2/g増加する程度か、又は粉砕後の平均メジアン径が0.6〜1μmとなる程度に粉砕することが好ましい。このように調整した原料粉を使用することにより、仮焼工程を全く必要とせずに、高密度の酸化物焼結体を得ることができる。また、還元工程も不要となる。

【0074】

尚、原料混合粉体の比表面積の増加分が1.0m2/g未満又は粉砕後の原料混合粉の平均メジアン径が1μmを超えると、焼結密度が十分に大きくならない場合がある。一方、原料混合粉体の比表面積の増加分が3.0m2/gを超える場合又は粉砕後の平均メジアン径が0.6μm未満にすると、粉砕時の粉砕器機等からのコンタミ(不純物混入量)が増加する場合がある。

【0075】

ここで、各粉体の比表面積はBET法で測定した値である。各粉体の粒度分布のメジアン径は、粒度分布計で測定した値である。これらの値は、粉体を乾式粉砕法、湿式粉砕法等により粉砕することにより調整できる。

原料粉の所望の配合割合、混合方法、成形する方法は特に限定されず、従来から公知の各種湿式法又は乾式法を用いることができる。

【0076】

乾式法としては、コールドプレス(Cold Press)法やホットプレス(Hot Press)法等を挙げることができる。コールドプレス法では、混合粉を成形型に充填して成形体を作製し、焼結させる。ホットプレス法では、混合粉を成形型内で、通常700〜1000℃で1〜48時間、好ましくは800〜950℃で3〜24時間にて直接焼結させる。

乾式法のコールドプレス(Cold Press)法としては、粉砕工程後の原料をスプレードライヤー等で乾燥した後、成形する。成形は公知の方法、例えば、加圧成形、冷間静水圧加圧、金型成形、鋳込み成形射出成形が採用できる。焼結密度の高い焼結体(ターゲット)を得るためには、冷間静水圧(CIP)等加圧を伴う方法で成形するのが好ましい。尚、成形処理に際しては、ポリビニルアルコールやメチルセルロース、ポリワックス、オレイン酸等の成形助剤を用いてもよい。

【0077】

次いで、得られた成形物を焼結して焼結体を得る。また、焼結は酸素を流通することにより酸素雰囲気中で焼結するか、加圧下にて焼結するのがよい。これにより亜鉛の蒸散を抑えることができ、ボイド(空隙)のない焼結体が得られる。このようにして製造した焼結体は、密度が高いため、使用時におけるノジュールやパーティクルの発生が少ないことから、膜特性に優れた酸化物半導体膜を作製することができる。

1000℃以上での昇温速度を30℃/h以上、冷却時の降温速度を30℃/h以上とするのが好ましい。昇温速度を30℃/h未満であると酸化物の分解が進行しピンホール数が多くなり、また冷却時の降温速度を30℃/h未満とするとInの組成比が変化するおそれがある。

【0078】

湿式法としては、例えば、濾過式成形法(特開平11−286002号公報参照)を用いるのが好ましい。この濾過式成形法は、セラミックス原料スラリーから水分を減圧排水して成形体を得るための非水溶性材料からなる濾過式成形型であって、1個以上の水抜き孔を有する成形用下型と、この成形用下型の上に載置した通水性を有するフィルターと、このフィルターをシールするためのシール材を介して上面側から挟持する成形用型枠からなり、前記成形用下型、成形用型枠、シール材、及びフィルターが各々分解できるように組立てられており、該フィルター面側からのみスラリー中の水分を減圧排水する濾過式成形型を用い、混合粉、イオン交換水と有機添加剤からなるスラリーを調製し、このスラリーを濾過式成形型に注入し、該フィルター面側からのみスラリー中の水分を減圧排水して成形体を作製し、得られたセラミックス成形体を乾燥脱脂後、焼成する。

【0079】

乾式法あるいは湿式法で得られた焼結体のバルク抵抗をターゲット全体として均一化するために還元処理ことが好ましい。還元工程は、必要に応じて設けられる工程である。適用することができる還元方法としては、例えば、還元性ガスによる方法や真空焼成又は不活性ガスによる還元等が挙げられる。

還元性ガスによる還元処理の場合、水素、メタン、一酸化炭素や、これらのガスと酸素との混合ガス等を用いることができる。

不活性ガス中での焼成による還元処理の場合、窒素、アルゴンや、これらのガスと酸素との混合ガス等を用いることができる。

尚、還元処理時の温度は、通常300〜1200℃、好ましくは500〜800℃である。また、還元処理の時間は、通常0.01〜10時間、好ましくは0.05〜5時間である。

【0080】

酸化物焼結体に、研磨等の加工を施すことによりターゲットとなる。具体的には、焼結体を、例えば、平面研削盤で研削して表面粗さRaを5μm以下とする。表面粗さは、Ra≦0.3μmであることがより好ましく、Ra≦0.1μmであることが特に好ましい。さらに、ターゲットのスパッタ面に鏡面加工を施して、平均表面粗さRaが1000オングストローム以下としてもよい。この鏡面加工(研磨)は機械的な研磨、化学研磨、メカノケミカル研磨(機械的な研磨と化学研磨の併用)等の、すでに知られている研磨技術を用いることができる。例えば、固定砥粒ポリッシャー(ポリッシュ液:水)で#2000以上にポリッシングしたり、又は遊離砥粒ラップ(研磨材:SiCペースト等)にてラッピング後、研磨材をダイヤモンドペーストに換えてラッピングすることによって得ることができる。このような研磨方法には特に制限はない。

【0081】

尚、ターゲットの清浄処理には、エアーブローや流水洗浄等を使用できる。エアーブローで異物を除去する際には、ノズルの向い側から集塵機で吸気を行なうとより有効に除去できる。エアーブローや流水洗浄の他に、超音波洗浄等を行なうこともできる。超音波洗浄では、周波数25〜300KHzの間で多重発振させて行なう方法が有効である。例えば周波数25〜300KHzの間で、25KHz刻みに12種類の周波数を多重発振させて超音波洗浄を行なうのがよい。

【0082】

得られたターゲットを加工後、バッキングプレートへボンディングすることにより、成膜装置に装着して使用できるスパッタリングターゲットとなる。バッキングプレートは銅製が好ましい。ボンディングにはインジウム半田を用いることが好ましい。

【0083】

加工工程は、上記のようにして焼結して得られた焼結体を、さらにスパッタリング装置への装着に適した形状に切削加工し、またバッキングプレート等の装着用治具を取り付けるための、必要に応じて設けられる工程である。ターゲットの厚みは通常2〜20mm、好ましくは3〜12mm、特に好ましくは4〜6mmである。また、複数のターゲットを一つのバッキングプレートに取り付け、実質一つのターゲットとしてもよい。また、表面は200〜10,000番のダイヤモンド砥石により仕上げを行うことが好ましく、400〜5,000番のダイヤモンド砥石により仕上げを行うことが特に好ましい。200番より小さい、あるいは10,000番より大きいダイヤモンド砥石を使用するとターゲットが割れやすくなるおそれがある。

【0084】

ターゲット中における各化合物の粒径は、それぞれ20μm以下が好ましく、10μm以下がさらに好ましく、5μm以下が特に好ましい。尚、粒径は電子プローブマイクロアナライザ(EPMA)で測定した平均粒径である。結晶粒径は、例えば、原料である酸化インジウム、酸化スズ、酸化亜鉛の各粉体の配合比や原料粉体の粒径、純度、昇温時間、焼結温度、焼結時間、焼結雰囲気、降温時間を調製することにより得られる。化合物の粒径が20μmより大きいとスパッタ時にノジュールが発生するおそれがある。

【0085】

ターゲットの相対密度は、理論密度の95%以上が好ましく、98%以上がより好ましく、99%以上が特に好ましい。ターゲットの密度が95%より小さいと強度が不十分となり成膜時にターゲットが破損するおそれがある。また、トランジスタを作製した際に性能が不均一になるおそれがある。相対密度とは、加重平均より算出した理論密度に対して相対的に算出した密度である。各原料の密度の加重平均より算出した密度が理論密度であり、これを100%とする。

ターゲットのバルク抵抗は、20mΩ以下が好ましく、10mΩ以下がより好ましく、5mΩ以下が特に好ましい。20mΩより大きいとDCスパッタでの成膜時にターゲットが破損するおそれがある。また、異常放電によりスパークが発生し、ターゲットが割れたり、スパークにより飛び出した粒子が成膜基板に付着し、酸化物半導体膜としての性能を低下させたりする場合がある。また、放電時にターゲットが割れるおそれもある。尚、バルク抵抗は抵抗率計を使用し、四探針法により測定した値である。

【0086】

ターゲットの抗折力は、8kg/mm2以上であることが好ましく、10kg/mm2以上であることがより好ましく、12kg/mm2以上であることが特に好ましい。ターゲットの運搬、取り付け時に荷重がかかり、ターゲットが破損するおそれがあるという理由で、ターゲットには、一定以上の抗折力が要求され、8kg/mm2未満では、ターゲットとしての使用に耐えられないおそれがある。ターゲットの抗折力は、JIS R 1601に準じて測定することができる。

【0087】

ターゲット内における亜鉛以外の、陽性元素のばらつきの範囲が0.5%以内であることが好ましい。ターゲット内における密度のばらつきの範囲が3%以内であることが好ましい。

ターゲットの表面粗さRa≦0.5μmであり、方向性のない研削面を備えていることが好ましい。Raが0.5μmより大きかったり、研磨面に方向性があると、異常放電が起きたり、パーティクルが発生するおそれがある。

ターゲット内におけるフェレー径2μm以上のピンホール数が単位面積当たり50個/mm2以下が好ましく、20個/mm2以下がより好ましく、5個/mm2以下がさらに好ましい。尚、ターゲット内部のフェレー径2μm以上のピンホール数が50個/mm2より多いと、ターゲット使用初期から末期までに異常放電が多発する傾向になって好ましくなく、また、得られるスパッタ膜の平滑性も低下する傾向にある。ターゲット内部のフェレー径2μm以上のピンホールが5個/mm2以下だと、ターゲット使用初期から末期まで異常放電を抑制でき、また、得られるスパッタ膜は非常に平滑である。ここで、フェレー径とは、ピンホールを粒子として見立てた場合に、粒子を挟むある一定方向の平行線間隔のことをいう。例えば、倍率100倍のSEM像による観察で計測できる。

【0088】

本発明の半導体膜は、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であり、Snの平均価数が+3.2以上であることを特徴とする。Snの平均価数は+3.6以上が好ましく、+3.8以上がさらに好ましい。

本発明の半導体膜は、上述した本発明のスパッタリングターゲットを使用して、成膜することで作製できる。電界効果型トランジスタの半導体層等に好適に使用できる。

尚、Snの平均価数は、X線光電子分光法(XPS)で測定した値である。

【実施例】

【0089】

電界効果型トランジストを作製する前に、トランジスタの半導体層となる酸化物半導体膜を成膜し、エッチング性等、薄膜の特性を評価した。

【0090】

評価例1

(1)スパッタリングターゲットの製造

原料として、酸化インジウム、酸化亜鉛及び酸化錫の粉末を、原子比〔In/(In+Sn+Zn)〕が0.38、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/((In+Sn+Zn)〕が0.47となるように混合した。これを湿式ボールミルに供給し、72時間混合粉砕して原料微粉末を得た。酸化インジウム、酸化亜鉛及び酸化錫の原料粉末の比表面積はそれぞれ15m2/g、4m2/g、8m2/gであった。

得られた原料微粉末を造粒した後、直径10cm、厚さ5mmの寸法にプレス成形し、これを焼成炉に入れ、1400℃で12時間焼成して、焼結体を得た。焼結体のバルク抵抗は3mΩ、理論相対密度は0.99であった。尚、理論相対密度は各酸化物の比重とその量比から計算した密度を、アルキメデス法で測定した密度との比率を計算して求めた。また、組成を分析したところ原子比〔In/(In+Sn+Zn)〕が0.38、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/((In+Sn+Zn)〕が0.47であり、Na含有量が100ppm未満であった。X線回折で構造解析をしたところ、焼結体はビックスバイト構造化合物とスピネル構造化合物を含んでいた。電子プローブマイクロアナライザ(EPMA)で測定した平均粒径は、ビックスバイト構造化合物及びスピネル構造化合物ともに10μm以下であった。

焼結体を加工・清浄処理した後、バッキングプレートにボンディングしてスパッタリングターゲットとした。

【0091】

(2)薄膜作製と評価

ガラス基板(コーニング1737)上に、上記(1)で製造したターゲットを使用して半導体層に相当する膜を形成し評価した。

スパッタ条件は、基板温度;25℃、到達圧力;1×10−6Pa、雰囲気ガス;Ar97%及び酸素3%、スパッタ圧力(全圧);5×10−1Pa、投入電力100W、S−T距離100mmとした。

得られた薄膜をICP法で分析した。原子比〔In/(In+Sn+Zn)〕が0.40、原子比〔Sn/(In+Sn+Zn)〕が0.15、原子比〔Zn/(In+Sn+Zn)〕が0.45であった。

上記薄膜を大気下で、280℃で1時間の熱処理を行った。

得た薄膜について、XPSで測定したSn平均価数は、+3.8以上であった。尚、平均価数は、Snの5sバンドの相対強度から求めることができる。

また、X線局所構造解析(XAFS)法を用いたIn、Sn、Zn各金属元素周辺の局所構造解析において、Sn元素周りの構造はSnO2と同様の構造を有しており、In、Zn元素周りの構造はIZO薄膜と同様の構造を有していることが確認できた。

また、比抵抗は10Ωcm、キャリア密度は1016cm−3であった。さらに、ホール効果の温度変化測定から非縮退半導体であることを確認した。

また、以下の項目について評価した。結果を表1に示す。

【0092】

(1)結晶性

X線結晶構造解析により、ハローパターンが観測されたものを非晶質であると判断した。

(2)PAN耐性

PANによるエッチング速度が10nm/分以上のものを×とし、それ以外のものを○とした。

ここで、PAN耐性の評価には、40℃のPANエッチング液(リン酸87wt%、硝酸3wt%、酢酸10wt%)を用いた。PANエッチング液(リン酸、硝酸、酢酸を含むエッチング液)は、通常リン酸が20〜95wt%、硝酸0.5〜5wt%、酢酸3〜50wt%の範囲にあるものが用いられる。

(3)蓚酸に対するエッチング性

蓚酸系エッチング液として、35℃のITO−06N(関東化学(株))を用いエッチング速度を測定した。尚、150%オーバーエッチング後に顕微鏡観察して残渣の有無を確認した。○は残渣が少ないときであり、×は残渣が多いときである。

エッチング性の評価において、◎が最も良好で、○は良好で、×は不良を示す。

(4)ドライエッチング性

反応性イオンエッチング(RIE)のエッチングレートを測定した。エッチングレート1nm/分以上でエッチング可能であったものをドライエッチング可能(○)と判定した。

【0093】

評価例2−24

原料粉末を配合比、成膜条件を、表1〜3に示すように変更した他は、評価例1と同様にして、酸化物半導体膜を形成し、評価した。

尚、評価例18で作製したターゲットのバルク抵抗は2mΩ、理論相対密度は0.99であった。また、評価例1と同様にして得た薄膜についてXPSで測定したSn平均価数は、+3.8以上であった。

【0094】

評価例25−27

原料粉末を配合比、成膜条件を、表3に示すように変更した他は、評価例1と同様にして、酸化物半導体膜を形成し、評価した。

【0095】

【表1】

【0096】

【表2】

【0097】

【表3】

【0098】

[電界効果トランジスタの作製]

実施例1−17

図1に示すボトムゲート構造のエッチストッパー(ES)型の電界効果トランジスタを作製した。以下、図面を参照しながら製造過程を説明する。

図3a及び図3bは電界効果トランジスタの製造工程を示す図である。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した(図3a(a))。

次に、ゲート電極11を作製した基板に、プラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした(図3a(b))。

次に、評価例1−17で製造した半導体層用ターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜12上に半導体層13(膜厚30nm)を成膜した(図3a(c))。スパッタ条件は、上述した評価例と同様とした。

次に、280℃で1時間(後述する保護層形成後の熱処理と同じ条件)熱処理した。

【0099】

次に、PECVDにてSiOxを成膜し、薄膜16を形成した(図3a(d))。続けて、レジスト膜21を成膜し(図3a(e))、パターニングした(図3a(f))。

ドライエッチ(RIE)で薄膜16をパターニングして第一の保護層16(エッチストッパー)を形成した(図3b(g))。

レジスト膜21を除去した(図3b(h))。その後、ソース電極及びドレイン電極となる薄膜22を形成した(図3b(i))。薄膜22は、DCスパッタリングでTi/Al/Ti積層膜とした。成膜後、ドライエッチ(RIE)でパターニングしてソース電極14、ドレイン電極15を形成した。同時に半導体層13もエッチングした(図3b(j))。

さらに、PECVD(PECVD SiNx:H)にてSiNxを成膜し第二の保護層17とした(図3b(k))。コンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理して、W=20μm、L=5μmのボトムゲート構造エッチストッパー型電界効果型トランジスタを製造した(図3b(l))。

【0100】

電界効果型トランジスタについて、下記の評価を行った。

(1)電界効果移動度(μ)、オンオフ比、オフ電流、S値、閾値電圧(Vth)

半導体パラメーターアナライザー(ケースレー4200)を用い、室温、遮光環境下で測定した。

(2)ヒステリシス

半導体パラメーターアナライザーを用い、昇電圧時の伝達曲線(I−V特性)と降電圧時の伝達曲線(I−V特性)を測定し、昇降時の電圧の差をΔVgとする。ΔVgの最大値が0.5V以下であるものを「少ない」、0.5〜3Vであるものを「ある」、3V以上であるものを「大きい」とした。

尚、図4は、昇電圧時及び降電圧時の伝達曲線(I−V特性)の例であり、(a)はヒステリシスの少ない例であり、(b)はヒステリシスの大きい例を示す。

(3)閾値電圧のシフト(ストレス試験)

ストレス条件は、ゲート電圧20Vで10μAの直流電圧を50℃で105秒加えることとした。ストレスをかける前後のVthを比較し、閾値電圧のシフト量(ΔVth)を測定した。

(4)耐湿性

湿度85%環境下に120時間放置し、閾値電圧のシフトを評価した。

◎:変化量が0.5V未満、○:変化量が0.5V以上2V未満、△:変化量が2V以上5V以下、×:変化量が5V以上

実施例1及び実施例1と同じ形状トランジスタの実施例2−39について、電界効果型トランジスタの素子構成を表4−6に示す。

また、評価結果を表7、8に示す。

【0101】

【表4】

【0102】

【表5】

【0103】

【表6】

【0104】

【表7】

【0105】

【表8】

【0106】

実施例18−25

半導体層形成時の条件を表4、5に示す評価例と同様にした他は、実施例1と同様にトランジスタを作製し、評価した。結果を表7に示す。

【0107】

実施例26−32

表4、5に示すように、半導体層の形成、ソース・ドレイン電極を変更し、半導体層の形成とソース・ドレイン電極の形成をウェットエッチングで行った以外は、実施例1と同様に作製・評価した。

尚、半導体層は修酸系エッチング液を用いパターニングし、ソース電極・ドレイン電極は、PAN系エッチング液を用いパターニングした。

【0108】

実施例33,34

表6に示したようにTFTの構造、製造プロセスを変えた以外は、実施例1と同様にトランジスタを作製し、評価した。

【0109】

実施例35−37

表6に示したように、TFTの構造、製造プロセスを変えた以外は、実施例1と同様にトランジスタを作製し、評価した。

【0110】

実施例38,39

表6に示したように、半導体層成膜時の酸素分圧を変更した以外は実施例1と同様にトランジスタを作製・評価した。

【0111】

実施例40

図5に示す、ボトムゲートエッチストッパー電界効果型トランジスタを作製し、実施例1同様に評価した。尚、図5(a)は実施例40で作製した電界効果型トランジスタの概略断面図であり、(b)は各部材の位置関係を示した概略上面図である。図5(a)は、図5(b)のA−A断面図である。各部材の付番は図1と同様とし、説明を省略する。

本実施例では、熱酸化膜11’(SiOx、100nm)付Si基板10’を用い、表9に示したTFTの構造、製造プロセスでトランジスタを作製した。Si基板10’がゲート電極を兼ねている。

実施例40及び実施例40と同じ形状トランジスタの実施例41−46について、電界効果型トランジスタの素子構成を表9に示す。

また、評価結果を表10に示す。

【0112】

【表9】

【0113】

【表10】

【0114】

実施例41

第一の保護層をHfOxとした他は、実施例40と同様にボトムゲート構造エッチストッパー型電界効果型トランジスタを作製・評価した。

【0115】

実施例42−46

表9に示すように、各電極、第一の保護層及び第二の保護層、作製プロセスを変更した他は、実施例40と同様の構造の電界効果型トランジスタを作製し、評価した。

【0116】

実施例47

図6に示すボトムゲート構造のバックチャンネルエッチ(BCH)型の電界効果トランジスタを作製した。尚、各部材の付番は図1と同様とし、説明を省略する。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した。

次に、ゲート電極11を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした。

次に、評価例18で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜した。スパッタ条件は、評価例18と同様とした。

【0117】

その後、修酸系エッチング液を用い、ウェットエッチでパターニングして半導体層13(膜厚30nm)を形成した。

続いて、DCスパッタリングでAl−Nd合金膜を成膜した。成膜後、PAN系エッチング液を用い、ウェットエッチでパターニングしてソース電極・ドレイン電極14,15を形成した。

次に、PECVDにて、SiOxを成膜して、第一の保護層16とした。

さらに、第二の保護層17として、PECVD(PECVD SiNx:H)にてSiNxを成膜したのちコンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理してW=20μm、L=5μmのボトムゲート構造バックチャンネルエッチ型電界効果型トランジスタを製造した。

実施例47及び実施例47と同じ形状トランジスタの実施例48−51について、電界効果型トランジスタの素子構成を表11に示す。

また、評価結果を表12に示す。

【0118】

【表11】

【0119】

【表12】

【0120】

実施例48−51

表11に示すように、各電極、第一の保護層及び第二の保護層、作製プロセスを変更した他は、実施例47と同様の構造の電界効果型トランジスタを作製し、評価した。

【0121】

実施例52及び53

表13に示す条件で、図7に示すコプラナー構造電界効果型トランジスタを作製し、評価した。尚、各部材の付番は図1と同様とし、説明を省略する。

ガラス基板10上にゲート電極11及びゲート絶縁膜12を形成した(図7(a)(b))。半導体層13を形成した後、第一の保護層16’を成膜した(図7(c))。

第一の保護層16’上にレジスト膜21を形成した(図7(d))。基板10側から光を照射し、ゲート電極11をマスクとするようにして、レジスト膜の一部21’を露光し、除去した(図7(e)(f))。その後、第一の保護層16’をゲート電極11と整合するようパターニングし第一の保護層16とした(図7(g))。

PECVD(PECVD SiNx:H)にてSiNxを成膜し、第二の保護層17を形成すると同時に、半導体層部分13の第一の保護層16で覆われていない部分13aを低抵抗化させ、低抵抗化した半導体層部分13aとした(図7(h))。コンタクトホール18を形成し、ドレイン電極14及びソース電極15と接続して、コプラナー構造電界効果型トランジスタを作製した(図7(i))。

評価結果を表14に示す。

【0122】

【表13】

【0123】

【表14】

【0124】

尚、実施例52の半導体層、ソース・ドレイン電極と同様の条件でガラス基板上に薄膜を作製し、ホール効果の温度特性を評価した。半導体層と同一条件で作製した薄膜は温度依存性を示し非縮退半導体、ソース・ドレイン電極と同一条件で作製した薄膜は温度依存性を示さず縮退半導体であった。

図8に移動度の温度依存性を示す。直線の傾きから活性化エネルギーを計算できる。図中(1)がソース・ドレイン電極に相当し、(2)が半導体層に相当する。半導体層に相当する膜は活性化エネルギー約35meVで熱活性型を示し非縮退半導体であること、ソース・ドレイン電極に相当する膜は活性化エネルギー3meV未満で縮退半導体であることが確認できた。

【0125】

実施例54

表13に示す条件で、図9に示すトップゲート構造電界効果型トランジスタを作製し、評価した。尚、第一の保護層を積層構造とし、半導体層13成膜前に形成した。基板10側にPECVDでSiNxを成膜した第一の保護層16bを、その上にPECVDでSiO2を成膜した第一の保護層16aを形成した。

トランジスタの評価結果を表14に示す。

【0126】

実施例55

表13に示す条件で、図10に示す電界効果トランジスタを作製した。このトランジスタは、図1に示すボトムゲート構造のエッチストッパー(ES)型の電界効果トランジスタにおいて、ソース電極及びドレイン電極を、半導体層の一部を低抵抗化することで形成したものである。

ガラス基板10上に、室温のRFスパッタリングでモリブデン金属を200nm積層した後、ウェットエッチングでパターニングし、ゲート電極11を作製した。

次に、ゲート電極を作製した基板にプラズマ化学気相成長装置(PECVD)にて、SiOxを成膜し、ゲート絶縁膜12とした。

次に、評価例18で製造したターゲットを、DCスパッタ法の一つであるDCマグネトロンスパッタリング法の成膜装置に装着し、ゲート絶縁膜上に成膜した。スパッタ条件は、評価例18と同じとした。

その後蓚酸系のウェットエッチング液でパターニングして半導体層13(膜厚40nm)を形成した。

【0127】

次に、PECVDにて、SiOxを成膜、ドライエッチ(RIE)でパターニングして、第一の保護層16(エッチストッパー)とした。

ここまでの工程で、図3b(h)に示す、第一の保護層16が形成された基板を得た。

その後、第二の保護層17として、PECVD(PECVD SiNx:H)にてSiNxを成膜すると同時に、半導体層13の一部を低抵抗化させソース電極14・ドレイン電極15を形成した。尚、SiNxを成膜した際の水素プラズマにより半導体層の一部が低抵抗化する。

その後、コンタクトホール18を形成し、外部配線と接続した。

その後、大気下、280℃で1時間熱処理してW=20μm、L=5μmのボトムゲート構造コプラナー型電界効果型トランジスタを製造した。

トランジスタの評価結果を表14に示す。

【0128】

実施例56−58

表13に示すように、半導体層の形成、ソース・ドレイン電極を変更し、半導体層の形成とソース・ドレイン電極の形成をウェットエッチングで行った以外は、実施例1と同様に作製・評価した。

尚、半導体層は修酸系エッチング液を用いパターニングし、ソース電極・ドレイン電極は、PAN系エッチング液を用いパターニングした。

【0129】

比較例1−5

表15に示す構成のボトムゲート構造バックチャンネルエッチ型電界効果型トランジスタを作製した。

半導体層は、表16に示す条件で、2種のターゲット(ZnOとIn2O3−SnO2(原子比In:Sn=1:1))を用いコスパッタで形成した。

図11は、コスパッタによる薄膜形成の概念図である。

回転台31に基板10を固定し、スパッタ処理中に軸32によって回転台31を回転させる。これにより、In2O3−SnO2ターゲット33及びZnOターゲット34の両者を使用した成膜ができる。

尚、ZnOターゲットはRFスパッタ、In2O3−SnO2(原子比In:Sn=1:1)ターゲットはDCスパッタを用い成膜した。

実施例1と同様に、XPSで測定した比較例1及び5のSn平均価数は、それぞれ+2.9、+3.0であった。

尚、比較例で作製した電界効果型トランジスタの素子構成を表15に示す。また、比較例で使用した半導体層の成膜条件、半導体層の組成、特性を表16、17に示す。さらに、比較例のトランジスタの評価結果を表18に示す。

【0130】

【表15】

【0131】

【表16】

【0132】

【表17】

【0133】

【表18】

【0134】

比較例6−14

半導体層の組成比を表16、17に示すように変えた他は、実施例1と同様にして、電界効果型トランジスタを製造し、評価した。

【0135】

比較例15−19

表17に示す条件で半導体層を形成し、表15に示したTFT構造及び製造プロセスとした他は、実施例1と同様にして、電界効果型トランジスタを製造し、評価した。

【0136】

比較例20

組成比を変更し、半導体層をドライエッチした他は、実施例55と同様に電界効果型トランジスタを作製し、評価した。

その結果、半導体層の組成比が同じである比較例13と比べて、トランジスタ特性が大幅に低下した。半導体の一部を低抵抗化させる際に錫の低級酸化物が生成してしまいコンタクト抵抗が大きくなったためと考えられる。これは錫の量が多く、Sn/Zn比も大きいことが原因と考えられる。

【0137】

[実施例及び比較例の検討]

(1)半導体層におけるZn量(Zn/(In+Sn+Zn))

図12にInとSn比を一定にした時のZn量(Zn/(In+Sn+Zn))と移動度(a)、オフ電流(b)の関係を示した。図12において、実施例の測定値に基づく線をAで、比較例の測定値に基づく線をBで示してある。

保護層の無い比較例1〜5に比べ、保護層を形成した後に熱処理を加えたものは、Zn量が増えても移動度が低下しなかった。Zn/(In+Sn+Zn)=0.6付近で非常に高い移動度と低いオフ電流を示し、実用的なTFTが構成できることが分かる。

【0138】

(2)In量(In/(In+Sn+Zn))、あるいはSn量(Sn/(In+Sn+Zn))

図13にZn量を一定にした時のIn量(In/(In+Sn+Zn))と移動度(a)、オフ電流(b)の関係を示す。図13は、実施例18−25から得られた結果を、図2に示す組成領域1−3について、熱処理温度を変えて比較した結果を示している。350℃で熱処理した場合は、移動度が高いオフ電流が低いなど領域3の特性が良好で、200℃で熱処理した場合は、移動度が高いなど領域2の特性が良好であった。

また、保護層を付けた後に280℃熱処理を加えたものはSn/In比が0.33から1付近で非常に高い移動度と低いオフ電流を示し、実用的なTFTが構成できることが分かる。

また、熱処理温度の比較からSn/In比が小さいと(Sn量が少ないと)、低温の熱処理でも良好なTFT特性が得られ、適正な錫量で低温プロセスに対応できることが分かる。

【0139】

(3)保護層

比較例18と実施例42の比較から、第一の保護層の形成後に熱処理をすることで、トランジスタ特性の向上(オンオフ比の向上、オフ電流の低減、S値の低減、閾値電圧の低減)と耐湿性の向上の効果が確認できた。

実施例42と実施例40の比較から、第二の保護層の形成後に熱処理をすることで、さらに耐湿性やS値が向上することが分かった。

同様に、実施例1と比較例19の比較から、第一、第二の保護層により、トランジスタ特性の向上(オンオフ比の向上、オフ電流の低減、S値の低減、閾値電圧の低減)と耐湿性の向上の効果が分かった。

【0140】

(4)錫原子の添加

比較例17と19の比較から、保護層が無い状態でも錫の添加により耐湿性が向上することが分かった。

また、実施例15、12、8、比較例8の雰囲気温度による閾値電圧のシフト量(ΔVth(temp))を比較した。Snを含まない比較例8はΔVth(temp)が12V以上であったのに対して、Snを含む実施例15、12、8はΔVth(temp)が6V以下であった。Snが含まれることにより雰囲気温度に対する安定性も改良されていることが確認できた。

尚、雰囲気温度25℃と80℃でのVthの差(Vth(25℃)−Vth(80℃))を雰囲気温度による閾値電圧のシフト量(ΔVth(temp))とした。

【0141】

(5)成膜時の酸素分圧

実施例1,38,39から、酸素分圧5×10−3Paから2.5×10−2Paで良好な特性が得られることが分かった。

【0142】

(6)半導体層の組成領域によるプロセス上の特徴

図2に示す各領域は、下記のプロセスが適用できることが確認できた。尚、図2中、○で示した点は実施例の組成を示し、×で示した点は比較例の組成を示す。

領域1:半導体層の蓚酸等によるウェットエッチングが可能、ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域2:半導体層の蓚酸等によるウェットエッチングが可能

領域3:半導体層の蓚酸等によるウェットエッチングが可能、ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域4:ソース・ドレイン電極のPAN等によるウェットエッチングが可能

領域外:ソース・ドレイン電極のPAN等によるウェットエッチングが可能