電解メッキ液、電解メッキ方法、および半導体装置の製造方法

【課題】銅配線層を電解メッキ法で形成する際に電極となるシード層の溶解に起因する銅メッキ層の欠陥の発生を抑制する電解メッキ液及び該メッキ液を用いた電解メッキ方法を提供する。

【解決手段】電解メッキ液として、極性溶媒と、前記極性溶媒中に溶解した硫酸銅を含み、さらに添加剤として、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤とを添加した電解メッキ液を使う。

【解決手段】電解メッキ液として、極性溶媒と、前記極性溶媒中に溶解した硫酸銅を含み、さらに添加剤として、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤とを添加した電解メッキ液を使う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特に電解メッキ法、および電解メッキ法を使った半導体装置の製造方法に関する。

【背景技術】

【0002】

今日の超微細化半導体集積回路装置では、基板上に形成された莫大な数の半導体素子を相互接続するために、低抵抗金属を配線パターンとした多層配線構造が使われている。特に銅(Cu)を配線パターンとした多層配線構造では、シリコン酸化膜、あるいはより比誘電率の低い、いわゆる低誘電率(low−K)材料よりなる層間絶縁膜中に配線溝あるいはビアホールをあらかじめ形成しておく。このビアホールに抵抗率が低くエレクトロマイグレーション耐性の高いCu層で充填し、余剰のCu層部分を化学機械研磨(CMP)により除去するダマシン法あるいはデュアルダマシン法が一般に使われている。

【0003】

ダマシン法あるいはデュアルダマシン法では、層間絶縁膜中に形成された配線溝あるいはビアホールの表面を、典型的にはTaやTaNなどの高融点金属あるいはその窒化物よりなるバリアメタル膜で覆う。その上に薄いCuシード層をPVD法あるいはCVD法により形成し、かかるCuシード層を電極として電解メッキを行うことにより、前記配線溝あるいはビアホールをCu層により充填している。

【特許文献1】特開2002−146585号公報

【特許文献2】特開2001−240995号公報

【特許文献3】特開2002−317274号公報

【特許文献4】特開2001−230252号公報

【特許文献5】特開2001−49491号公報

【特許文献6】特開2000−173949号公報

【特許文献7】特開2006−261268号公報

【特許文献8】特開2007−220882号公報

【特許文献9】特許第3208410号

【特許文献10】特開2006−299366号公報

【特許文献11】特開2001−251085号公報

【特許文献12】特許第3332668号

【特許文献13】特開2002−4081号公報

【特許文献14】特開2001−35812号公報

【特許文献15】特開2001−271196号公報

【特許文献16】特開2003−105584号公報

【特許文献17】特許第3367655号

【特許文献18】特許第3381170号

【特許文献19】特許第3938356号

【特許文献20】特開2007−197809号公報

【特許文献21】特開2004−225159号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

Cu層の電解メッキ工程では、一般的に硫酸銅などの銅塩を水などの極性溶媒に溶解した硫酸銅水溶液などの電解メッキ液が使われる。電解メッキ液には一般に微細な配線溝やビアホールを充填するため、数種類の添加物が組みあわせて添加される。これらの添加物には、配線溝やビアホールを、積極的に底部から上部に向かって充填(ボトムアップ充填)するために、硫黄系化合物よりなるアクセラレータ(ブライトナ、光沢剤とも呼ばれる)と、ポリエチレングリコールやポリプロピレングリコールなど、分子量が1000〜6000程度のポリマよりなるサプレッサ(抑制剤とも呼ばれる)とが添加されている。これにさらに、分子量が10000を超え、多くは環状構造を有するポリマよりなるレベラが添加されることもある。アクセラレータとサプレッサは、いずれが欠けても、所望のボトムアップ充填は得られない。

【0005】

図1A〜1Eは、典型的なダマシン法によるCu配線パターンの形成工程を、図2は、かかるCu配線パターン形成の際の理想的なボトムアップ充填の例を示す。

【0006】

図1Aにおいて、絶縁膜11に配線溝あるいはビアホールを構成する凹部12を形成する。次に図1Bに示すように、前記凹部12の側壁面および底面に、典型的にはTaやTiなどの高融点金属、あるいはTaNやTiNなど、その導電性窒化物よりなるバリアメタル膜13が、前記凹部12に整合した形状で形成される。

【0007】

さらに図1Cに示すように、前記バリアメタル膜13の表面にはCuシード層14が、PVD法あるいはCVD法により、前記凹部12に整合した形状で形成される。さらに図1Dに示すように、前記Cuシード層14を電極とした電解メッキにより、前記凹部12にCu層15を充填する。

【0008】

その際、使われる電解メッキ液に、先に説明したアクセラレータとサプレッサを添加する。これにより、図2に示すように、Cu層15の充填が、前記凹部12の底部から上方に向かって生じる(ボトムアップ充填)。

【0009】

さらに図1Eに示すように、前記層間絶縁膜11表面の不要なCu層15をCMP法により除去する。これにより、ボイドの少ない、ストレスマイグレーションやエレクトロマイグレーションに対する耐性の高いCu配線パターン15Aが得られる。

【0010】

ところが、最近の最小ビアあるいは溝径が90nm、あるいはそれ以下の超微細化多層配線構造を有する半導体装置では、電解メッキ液として、pH1以下の強酸性の液が使われるのが一般的である。この場合、薄いCuシード層14がメッキ液の作用により、溶解してしまう問題が生じることが知られている。

【0011】

図4は、図3Aおよび3Bに示すシード層14の、前記図1Dに示す電解メッキ工程初期における状態を示す。ただし図4は、前記図3Aの構造において前記凹部12の側壁面を覆うシード層14を、図3Bに矢印で示す方向から見た図である。図4では、10秒間の電解メッキ工程により、前記シード層14上に薄いCu層が形成されている。

【0012】

図4を参照するに、(A),(B)の図では前記凹部12の下部においてシード層14が溶解している。また図4(C)の図では中央部のシード層14が溶解しているのがわかる。なお図4の(A)〜(C)において、凹部12の下部に見える明るい部分は、前記凹部12の底部を覆うシード層14の断面を示す。試料作成時のへき開の結果、前記シード層14が塑性変形しているのがわかる。

【0013】

このように図1Cの構造においてシード層14が部分的に溶解すると、かかるシード層14を電極に図1Dの工程で電解メッキを行った場合、前記シード層14が欠如している部分にはCu層15の成膜は生じない。このため、図5に示すように、前記凹部12を充填するCu配線パターン15Aにボイドなどの欠陥が発生してしまう。

【0014】

従来、前記メッキシード層14の電解メッキ工程における溶解を抑制するため、被処理基板を電解メッキ液に浸漬する際に、予め被処理基板に電圧を印加することが行われている。一方、被処理基板を電解メッキ液に浸漬する場合には、気泡の発生を抑制するため、被処理基板を電解メッキ液の液面に対して斜めに傾けた状態で浸漬している。そこで、このようにバイアス電圧を印加した被処理基板を液面に対して斜めに傾けた状態で浸漬すると、浸漬された部分からCu層の堆積が直ちに開始されてしまう。その結果、図1Dに示すCu層15の成膜を最適に制御することが困難になってしまう。この問題は、特にビア径が70nm以下の超微細化半導体装置製造において顕著になる。

【0015】

また従来、このようなメッキシード層14の電解メッキ工程における溶解を抑制するため、特許文献1には、pH値の大きい弱酸性、あるいはアルカリ性のメッキ液を使う提案もなされている。しかし、このような技術では、特殊なメッキ液を使う必要がある。また最適な成膜条件も限られる。このため、超微細化半導体装置の製造に一般的に使用するのは困難である。

【0016】

また、上記Cuシード層の電解メッキ工程における溶解を抑制するため、電解メッキ液に高濃度のサプレッサを添加する技術も提案されている。

【0017】

図6(A)は、前記図1Cの構造に対し、アクセラレータもサプレッサも含まない硫酸銅水溶液よりなる電解メッキ液(バージンメークアップソリューション:VMS)を使ってCu層15の成膜を10秒程度行った場合についての、前記Cuシード層14の状態を示す図である。

【0018】

図6(B)は、前記図1Cの構造に対し、前記VMSにアクセラレータとして一般的に使われているジスルフィドプロパンスルホン酸(SPS)のみを添加して同様な電解メッキを短時間行った場合についての、前記Cuシード層14の状態を示す図である。

【0019】

図6(C)は、前記図1Cの構造に対し、前記VMSにサプレッサとして一般的に使われているポリエチレングリコール(PEG)のみを添加して同様な電解メッキを短時間行った場合についての、前記Cuシード層14の状態を示す図である。

【0020】

図6(A)〜(C)は、前記図4(A)〜(C)と同様に、前記凹部12の側壁面を見た状態の図となっている。

【0021】

図6(A)〜(C)を参照するに、VMSを使った図6(A)の場合には、前記凹部12の下部においてCuシード層14の溶解が認められ、これにアクセラレータを添加した図6(B)の場合、前記Cuシード層14の溶解がさらに促進されていることがわかる。一方、図(C)に示すサプレッサのみを添加した場合には、Cuシード層14の溶解が減少しているのがわかる。ただし、溶解の問題は、図6(C)の場合でも、完全に解消しているわけではない。そこで、前記Cuシード層14の溶解の問題だけを解消するためには、電解メッキ中に高濃度のサプレッサを添加することが考えられる。しかし、サプレッサだけを添加した場合には、先に図2で説明したようなCu層による凹部12のボトムアップ充填が不可能となる。また、前記凹部12の幅が70nm以下になると、図7(A),(B)に示すように、電解メッキ液にサプレッサを添加していても、凹部12の底部におけるCuシード層14の溶解は回避できない。ただし図7(A),(B)は、前記Cuシード層14の、図1Dの工程において短時間Cu層15の電解メッキを行った状態を、異なった倍率で示す。

【課題を解決するための手段】

【0022】

一の側面によれば、電解メッキ液は、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【0023】

他の側面によれば、電解メッキ方法は、銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、前記電解メッキ液が、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【0024】

他の側面によれば半導体装置の製造方法は、被処理基板上の絶縁膜中に凹部を形成する工程と、前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、を含み、前記銅層形成に用いる電解メッキ液が、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【発明の効果】

【0025】

本発明によれば、電解メッキ液を使った銅層の電解メッキ工程において、電極として使われる銅シード層に生じる溶解の問題が、前記電解メッキ液に添加された、分子量がアクセラレータの分子量よりも小さい還元剤により効果的に抑制される。その結果、前記銅層により微細な凹部を下部から上部へと、順次充填することが可能となる。

【発明を実施するための最良の形態】

【0026】

[第1の実施形態]

本発明の発明者は、本発明の基礎となる研究において、先に説明したCuシード層14の溶解の問題に対するアクセラレータおよびサプレッサの効果について検討した。その結果、電解メッキ液に、さらに前記アクセラレータとして使われる化合物よりも分子量の小さい例えばグルコースを還元剤として添加した場合に、前記Cuシード層14の溶解が非常に効果的に抑制されることが見出された。

【0027】

以下、本発明を実施例について説明する。

【実施例】

【0028】

図8は、実験に使われた電解メッキ装置1の概略的構成を、図9A〜9Dは、本発明の発明者が行った実験の概要を示す。

【0029】

最初に図8を参照する。

【0030】

前記電解メッキ装置1は電解液2A中にアノード2Bを保持する容器2を備え、前記電解液2A中には被処理基板Wが浸漬される。

【0031】

前記容器2にはタンク3が配管3A,3Bを介して接続され、前記電解液2Aは、前記容器2とタンク3の間を、前記配管3A,3Bを通って循環している。

【0032】

さらに前記タンク3にはVMSを供給するユニット4Aと、アクセラレータを供給するユニット4Bと、サプレッサを供給するユニット4Cと、レベラを供給するユニット4Dと、還元剤を供給するユニット4Eが、それぞれのラインを介して接続されている。また前記タンク3中における電解液2Aの濃度を測定する濃度測定器5が結合されている。さらに電解メッキ処理の際には、前記被処理基板Wとアノード2Bに直流電源DCが接続される。

【0033】

図9Aを参照するに、絶縁膜21中には配線溝あるいはビアホールを構成する凹部22が70nmの幅および深さで形成される。さらに前記凹部22の側壁面および底面には図9Bに示すように、Ta膜よりなるバリアメタル膜23が、前記凹部22に整合した形状で、5〜6nmの膜厚で形成される。さらに図9Cに示すように、前記バリアメタル膜23の表面にはCuシード層24が、PVD法により、前記凹部12に整合した形状で、40〜100nmの膜厚で形成される。

【0034】

さらに図9Dの工程において、前記Cuシード層24を電極とした電解メッキを短時間、前記電解メッキ装置1を使って典型的には10秒間行う。これにより、前記Cuシード層24の表面にCu層25を約10nmの膜厚に形成する。このようにCuシード層24の表面に薄くCu層25を形成することにより、Cuシード層24中の欠陥を、より鮮明に検出することが可能となる。

【0035】

実施例1において本発明の発明者は、前記電解液2Aとして、Cuイオンを60g/Lの濃度で、また硫酸(H2SO4)を10g/Lの濃度で含み、さらに塩素(Cl)を50ppmの濃度で含む硫酸銅水溶液をVMSとして作製した。その際、実施例1ではさらに前記VMSに、アクセラレータとして化学式HO3S−CH2CH2CH2−S−S−CH2CH2CH2−SO3Hを有する分子量Mが310のジスルフィドプロパンスルホン酸(SPS)を20mg/Lの濃度で添加し、またサプレッサとして分子量が400,2000または6000のポリエチレングリコール(PEG)を添加し、サプレッサの重合度がそれぞれ異なった三種類の電解メッキ液を作製した。一方、実施例1の実施例では、Cu層による凹部22の埋込には余り影響しないため、レベラは使用していない。

【0036】

さらに実施例1においては、前記電解液2Aに前記還元剤として、分子量が180のD(+)グルコースを10〜20ppmの割合で添加している。

【0037】

図10(A),(B)は、前記図8の電解メッキ装置1において前記図9Cの構造上にCu層25を約10nmの膜厚に形成した試料を、図9Dに示すように矢印の方向から観察した図を示す。ここで図10(A)の試料は、グルコースを添加しなかった対照標準を示すのに対し、図10(B)の試料は、グルコースを添加した実施例1の試料を示している。ただし図10(A),(B)のいずれの試料でも、サプレッサとして分子量が2000のポリエチレングリコールを、300g/Lの割合で添加している。

【0038】

また図10(A),(B)の実験では、前記図8の装置1において、前記被処理基板Wを前記電解メッキ液2Aに浸漬する際にはバイアス電圧を印加せず、浸漬された後、5〜10mA/cm2の電流密度で通電を行っている。メッキ液の温度は25℃(常温:室温)に設定している。

【0039】

図10(A),(B)を比較すると、グルコースを添加しなかった場合には、前記Cuシード層24の溶解が、先に図4(A)〜(C)で説明したのと同様に生じているのに対し、グルコースを添加することにより、かかるCuシード層24の溶解が完全に止まっていることがわかる。

【0040】

図10(A),(B)の結果は、Cuシード層の溶解について、以下のメカニズムを示唆している。

【0041】

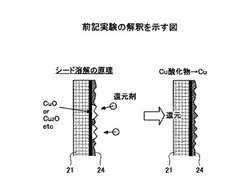

図11Aに概略的に示すように、電解メッキ液2A中にグルコースなどの還元剤が含まれてない場合、電解メッキ液2A中の溶存酸素によりCuシード層24が酸化され、形成されたCuOあるいはCu2Oなどの銅酸化物が、電解メッキ液2Aにより溶解される。その際、前記電解メッキ液2Aにアクセラレータが含まれていると、前記Cuシード層24の酸化が促進され、結果として、Cuシード層24の溶解が促進される。

【0042】

ところが電解メッキ液2A中にグルコースなどの還元剤が存在する場合、図11Bに概略的に示すように、電解メッキ液中の溶存酸素により形成された銅酸化物は直ちにCuに還元され、このため、電解メッキ液2A中にアクセラレータが含まれていても、Cuシード層24の溶解が抑制される。

【0043】

このようなメカニズムから考えて、前記還元剤はグルコースに限定されるものではなく、アルデヒド基あるいはケトン基を含み還元作用を示す糖類、アルデヒド基類、ケトン基類であってもよいことが考えられる。

【0044】

そこで、前記図11A,11Bの考察からは、前記電解メッキ液22A中に、アクセラレータに加えて還元剤を添加することで、Cuシード層24の電解メッキ液による溶解を抑制することが考えられる。

【0045】

しかし、微細な、例えば図12に示す最小線幅Wが70nm以下の凹部22をCu層の電解メッキにより充填するような場合を考えると、上に説明したメカニズムでは、前記還元剤は、アクセラレータよりも前記凹部22の破線で囲んだ底部22Aに、同等か、より高い効率で輸送されることが望ましい。このためには、前記還元剤は、アクセラレータと同等、あるいはそれ以下の分子量を有する化合物であることが望ましいことになる。なお図12の例では、前記絶縁膜21の下には、バリアメタル膜32を介して、下層の絶縁膜31が形成されている。本実施例で使われているアクセラレータSPSは、約310の分子量を有している。このため、前記還元剤は、例えば300以下の分子量を有するのが望ましい。グルコースは、約180の分子量を有しており、上記の条件を満たしている。

【0046】

このようなアルデヒド基あるいはケトン基を有し、300以下の分子量を有する還元剤としては、分子量が180のグルコースの他に、分子量が90のグリセルアルデヒド、分子量が120のエリトロース、分子量が120のトレオース、分子量が150のリボース、分子量が150のアラビノース、分子量が150のキシロース、分子量が150のリキソース、分子量が180のアロース、分子量が180のアルトロース、分子量が180のマンノース、分子量が180のグロース、分子量が180のイドース、分子量が180のガラクトース、分子量が180のタロースなどの単糖類が挙げられる。

【0047】

さらに前記還元剤としては、分子量が30のホルムアルデヒド、分子量が44のアセトアルデヒド、分子量が58のプロピオンアルデヒド、分子量が56のビニルアルデヒド、分子量が106のベンズアルデヒド、分子量が132のシンナムアルデヒド、分子量が150のペリルアルデヒドなどのアルデヒド基類、さらに分子量が59のアセトン、分子量が72のメチルエチルケトン、分子量が86のジエチルケトンなどのケトン基類が挙げられる。

【0048】

特にアクセラレータとして、SPSの代わりに分子量が155のメルカプトプロパンスルホン酸(MPS)を使うような場合には、上記の分子量が155以下の還元剤を使うことにより、先に説明したのと同様な効果を得ることが可能である。

【0049】

次に、本発明の発明者は、上記還元剤の作用・効果を確認するため、電解メッキ液2Aに、前記グルコースの代わりに、還元性を有さないポリエチレングリコールを、様々な分子量(400,2000,6000)および濃度(300mg/L,3000mg/L)で添加し、Cuシード層24の溶解抑制効果が生じるか否かを、先の図10(A),(B)の実験と同じ条件での実験により検討した。その結果を図13に示す。

【0050】

図13を参照するに、いずれの場合においても、前記Cuシード層24に顕著な溶解が生じているのがわかる。

【0051】

図13より、単にアクセラレータの分子量よりも小さい分子量の添加剤を電解メッキ液2Aに添加しても、その添加剤が還元作用を示さないならば、先に図10(A),(B)で得られたCuシード層24の溶解抑制効果は得られないことが結論される。

【0052】

さらに本発明の発明者は、上記還元剤の作用・効果を確認するため、サプレッサとして分子量が2000あるいは6000のポリエチレングリコールを使い、さらに還元剤の代わりに分子量が200のポリエチレングリコールを添加した電解メッキ液2Aを使い、Cuシード層24の溶解抑制効果が生じるか否かを、先の図10(A),(B)の実験と同じ条件での実験により検討した。その結果を図14に示す。

【0053】

図14中、(A)は前記分子量200のポリエチレングリコールを添加しない対照標準を、(B)は、前記分子量200のポリエチレングリコールを添加した例を示す。

【0054】

図10(A),(B)を参照するに、分子量200のポリエチレングリコールを添加しても、Cuシード層24には穴が形成されており、電解メッキ液による溶解を十分に抑制することができないことを示している。

【0055】

以上より、アクセラレータを添加された電解メッキ液によるCuシード層の溶解の問題は、前記電解メッキ液にさらに還元剤を添加し、その際、前記還元剤として、前記アクセラレータの分子量以下の分子量のものを選んで使うことにより、解決できるとの知見が示された。

【0056】

なお、このように電解メッキ液に還元剤を添加して、例えば図9Dの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層24の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。すなわち、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部22のCu層25による充填を最適な電流条件下で行うことが可能となる。その結果、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

【0057】

なお、本実施例の電解メッキ液2Aにおいて、硫酸銅を溶解する溶媒は水に限定されるものではなく、他の極性溶媒、例えばメタノール、エタノールなどのアルコール類、エチレンカーボネート、プロピレンカーボネートなどの環状カーボネート類、ジメチルカーボネート、エチルメチルカーボネート、ジエチルカーボネートなどの直鎖状カーボネート類、またはこれらの混合溶媒を使うことも可能である。

[第2の実施形態]

図15A〜15Eは、本発明の第2の実施形態によるCu配線パターンの形成方法を示す。

【0058】

図15Aを参照する。

【0059】

絶縁膜41中には配線溝あるいはビアホールを構成する凹部42が70nmの幅および深さで形成される。前記凹部42の側壁面および底面には図15Bに示すように、Ta膜よりなるバリアメタル膜43が、前記凹部42に整合した形状で、例えば5〜6nmの膜厚で形成される。さらに図10Cに示すように、前記バリアメタル膜43の表面にはCuシード層44が、PVD法により、前記凹部42に整合した形状で、40〜100nmの膜厚で形成される。

【0060】

さらに図15Dの工程において、前記Cuシード層44を電極とした電解メッキを、前記電解メッキ装置1において行い、前記Cuシード層24の表面から前記凹部22をCu層25により、ボトムアップ充填する。その際、前記電解メッキ液2Aとして、先の実施形態で説明したように、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを添加し、さらに還元剤としてグルコースを添加したものを使う。

【0061】

さらに図15Eの工程において、前記層間絶縁膜41表面の不要なCu層45をCMP法により除去することにより、ボイドの少ない、従ってストレスマイグレーションやエレクトロマイグレーションに対する耐性の高いCu配線パターン45Aが得られる。

【0062】

本実施形態では、電解メッキ液2Aにグルコースが還元剤として添加されている。このため、電解メッキ液2AにSPSなどのアクセラレータが添加さいれていてもCuシード層44の溶解が抑制される。その結果、図15Dの電解メッキ工程において前記凹部42をCu層45により、ボトムアップ充填することができ、Cu配線パターン45A中のボイドなどの欠陥発生を効果的に抑制することができる。

【0063】

また先に説明したように、図15Dの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層44の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。すなわち、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部42のCu層45による充填を最適な電流条件下で行うことが可能となる。よって、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

【0064】

なお、本実施形態では、前記電解メッキ液2Aに、必要に応じて例えばATMI社より商品名Viaform Levelerで市販されているレベラを添加してもよい。

[第3の実施形態]

次に、本発明の第3の実施形態による多層配線構造を有する半導体装置の製造工程を、図16A〜図16Lを参照しながら説明する。

【0065】

図16Aを参照するに、シリコン基板(図示せず)上の絶縁膜301上にはSiN膜302を介してSiO2などよりなる層間絶縁膜303が形成されている。前記層間絶縁膜303上には、所望の配線パターンに対応したレジストパターンR1が形成されている。

【0066】

次に図16Bの工程において前記層間絶縁膜303が前記レジストパターンR1をマスクにパターニングされる。その結果、前記層間絶縁膜303中には所望の配線パターニングに対応した配線溝が形成される。さらにこのようにパターニングされた層間絶縁膜303をTaバリアメタル膜304で覆った後、前記図15A〜15Dの工程を実行する。これにより銅層305が、前記配線溝を充填するように、電解めっき法により形成される。この電解メッキ法では、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを、還元剤としてグルコースを添加した電解メッキ液を使う。

【0067】

さらに図16Cの工程において前記銅層305およびその下のバリアメタル膜304が、前記層間絶縁膜303の表面が露出するまでCMP法により研磨・除去される。さらにこのようにして形成された構造上にSiNバリア膜305を介してSiO2などよりなる次の層間絶縁膜306が形成される。

【0068】

図16Cの工程ではさらに前記層間絶縁膜306上にSiNバリア膜307を介してSiO2などよりなる次の層間絶縁膜308が形成されている。さらに前記層間絶縁膜308上には所望のコンタクトホールに対応したレジストパターンR2が形成されている。

【0069】

次に図16Dの工程において前記レジストパターンR2をマスクに前記層間絶縁膜308,バリア膜307および層間絶縁膜306を順次パターニングしてコンタクトホール308Cを前記SiNバリア膜305が低部において露出するように形成する。その後、非感光性樹脂膜を塗布することにより、前記コンタクトホール308Cを前記樹脂膜により充填する。さらに前記層間絶縁膜308上の樹脂膜を溶解除去することにより、前記コンタクトホール308C中に樹脂保護部308Rを残す。

【0070】

さらに図16Dの工程では、前記層間絶縁膜308上に、前記層間絶縁膜308中に形成したい配線溝に対応したレジストパターンR3を形成する。

【0071】

次に図16Eの工程において前記樹脂保護部308Rによりコンタクトホール308Cの内壁面を保護した状態で前記レジストパターンR3をマスクに前記層間絶縁膜308を前記SiNバリア膜307が露出するまでパターニングする。これにより、前記層間絶縁膜308中に所望の配線溝308Gを形成する。

【0072】

さらに図16Eの工程では前記層間絶縁膜308のパターニングの後、前記樹脂保護部308Rをアッシングプロセスにより除去する。

【0073】

さらに図16Fの工程で、前記層間絶縁膜308を自己整合マスクに前記SiNバリア膜307および305を、それぞれ前記配線溝308Gおよびコンタクトホール308Cの底部から除去する。さらにこのようにして得られた構造の表面をTaバリアメタル膜309で覆った後、前記コンタクトホール308Cおよび配線溝308Gを充填するように銅層310を、先の図15A〜15Dの工程を実行する。これにより、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを、還元剤としてグルコースを添加した電解メッキ液を使った電解めっき法により形成する。

【0074】

次に図16Gの工程において図16Fの銅層310およびその下のTaバリアメタル膜309を、前記層間絶縁膜308の表面が露出するまでCMP法により除去する。さらにこのようにして得られた構造上にSiNバリア膜311とSiO2などよりなる層間絶縁膜312を形成する。

【0075】

さらに図16Gの工程では前記層間絶縁膜312上に、前記層間絶縁膜312中に形成したいビアホールに対応したレジストパターンR4が形成されている。

【0076】

さらに図16Hの工程において前記層間絶縁膜312およびその下のSiNバリア膜311が前記レジストパターンR4をマスクにパターニングされる。その結果、前記層間絶縁膜312中に所望のビアホール312Vが形成される。

【0077】

さらに図16Iの工程において、前記図16Hの構造に、TaN膜よりなるバリアメタル層313が、前記層間絶縁膜312上に前記ビアホール312Vの側壁面および底面を連続して覆うように、反応性スパッタにより形成される。さらに前記TaNバリアメタル膜313上にTiNバリアメタル膜314がやはり反応性スパッタにより形成される。さらに図16Jの工程において前記図16Iの構造上にタングステン膜315をCVD法により、前記タングステン膜315が前記ビアホール312Vを充填するように形成する。

【0078】

さらに図16(K)の工程において前記タングステン膜315およびその下のTiN膜314、TaN313を前記層間絶縁膜312の表面が露出するまでCMP法により研磨・除去し、前記ビアホール312V中にタングステンビアプラグ315Wを形成する。

【0079】

さらに図16Kの工程では前記層間絶縁膜312上にTiNバリアメタル膜316aを介してアルミニウムあるいはアルミニウム−銅合金よりなる導体膜316bを形成する。さらに前記導体膜316b上に別のTiNバリアメタル膜316cを形成する。前記導体膜316bは、前記TiNバリアメタル膜316aおよび316cとともに、配線層316を形成する。

【0080】

図16Kの状態では、さらに形成したい配線パターンに対応したレジストパターンR5が前記配線層316上に形成されている。さらに図16Lの工程において前記配線層316が前記レジストパターンR5をマスクにドライエッチング等によりパターニングされ、配線パターン316A,316Bが、前記タングステンプラグ315W上に形成される。

【0081】

さらに図16Lの工程では、前記層間絶縁膜312上に前記配線パターン316A,316Bを覆うようにSiO2などの層間絶縁膜317が堆積され、前記層間絶縁膜317の表面にはSiNなどのパッシベーション膜318が形成されている。

【0082】

本実施形態においては、前記図16Bあるいは図16FのCu層305あるいは310の電解メッキ工程を、先に図15A〜15Dで説明したように硫酸銅水溶液よりなり、アクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを添加され、さらに還元剤としてグルコースを添加した電解メッキ液を使って実行する。これにより、前記Cu層305あるいは310により配線溝を、図示していないCuシード層を溶解することなくボトムアップ充填することができる。その結果、ボイドなどの欠陥の発生を効果的に抑制することができる。

【0083】

本実施形態においても、図16Bあるいは図16Fの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。このため、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部のCu層305あるいは310による充填を最適な電流条件下で行うことが可能となる。これにより、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

[第4の実施形態]

図17は、このようにして形成された多層配線構造を有する本発明の第4の実施形態による半導体装置の構成を示す図である。

【0084】

図17を参照するに、シリコン基板401上にはSTI構造402により素子領域401Aが画成されている。前記素子領域401A中には前記シリコン基板401上にゲート電極403がゲート絶縁膜403Aを介して形成されている。

【0085】

前記ゲート電極403の両側壁面上には側壁絶縁膜が形成されている。さらに前記シリコン基板401中には前記ゲート電極403の両側にLDD領域401a,401bが形成されている。また前記シリコン基板401中には前記側壁絶縁膜の外側にソース領域あるいはドレイン領域を形成する拡散領域401c、401dが形成されている。また前記シリコン基板401の表面は、前記ゲート電極403およびその側壁絶縁膜の形成部分を除き、SiN膜404により一様に覆われている。

【0086】

さらに前記SiN膜404上には前記ゲート電極403および側壁絶縁膜を覆うようにSiO2などよりなる層間絶縁膜405が形成されている。前記層間絶縁膜405中には前記拡散領域401c,401dを露出するコンタクトホール405A,405Bが形成されている。

【0087】

前記コンタクトホール405A,405Bの側壁面および底面はTaN膜およびTiN膜を積層したバリアメタル膜406により覆われている。さらに前記コンタクトホール405A,405Bは前記バリアメタル膜を介してタングステンプラグ407により充填されている。

【0088】

さらに前記層間絶縁膜405上には先の実施例で説明したようなダマシン法あるいはデュアルダマシン法により、層間絶縁膜中に銅配線パターンが埋め込まれた銅配線構造408,409,410が順次形成されている。前記銅配線構造410上には層間絶縁膜411中にTaN膜とTiN膜とを積層した導電性窒化物膜よりなるバリアメタル膜412で側壁面および底面が連続的に覆われたビアホール中に、タングステンよりなる導電性プラグ413が形成されている。

【0089】

さらに前記層間絶縁膜411上にはアルミニウムあるいはアルミニウム合金よりなる導体膜をTiNバリアメタル膜で狭持した構成の配線パターン414A,414Bが形成されておいる。さらに前記層間絶縁膜411上には前記配線パターン414A,414Bを覆うように層間絶縁膜415が形成されている。

【0090】

さらに前記層間絶縁膜415の表面は、SiNなどよりなるパッシベーション膜416により覆われている。

【0091】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【0092】

(付記1)

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ液。

(付記2)

前記還元剤は、水溶性のアルデヒド基あるいはケトン基を持つ化合物であることを特徴とする付記1記載の電解メッキ液。

(付記3)

前記還元剤は、300以下の分子量を有する付記1または2記載の電解メッキ液。

(付記4)

前記還元剤は、単糖類である付記1〜3のうち、いずれか一項記載の電解メッキ液。

(付記5)

前記還元剤は、グルコースを含む付記1〜4のうち、いずれか一項記載の電解メッキ液。

(付記6)

前記アクセラレータは、ジスルフィドプロパンスルホン酸を含む付記1〜5のうち、いずれか一項記載の電解メッキ液。

(付記7)

さらにポリエチレングリコールをサプレッサとして添加した付記1〜6のうち、いずれか一項記載の電解メッキ液。

(付記8)

銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、

前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、

前記電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ方法。

(付記9)

前記通電は、前記被処理基板が前記電解メッキ液に浸漬された後で開始されることを特徴とする付記8記載の電解メッキ方法。

(付記10)

被処理基板上の絶縁膜中に凹部を形成する工程と、

前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、

前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、

前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、

前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、

を含み、

前記銅層形成に用いる電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む半導体装置の製造方法。

(付記11)

前記電解メッキ法は、前記被処理基板を前記電解メッキ液中に浸漬する工程と、前記電解メッキ液中において前記銅シード層を電極に通電を行う工程とを含み、前記通電は、前記被処理基板が前記電解メッキ液中に浸漬した後で開始されることを特徴とする付記10記載の半導体装置の製造方法。

【図面の簡単な説明】

【0093】

【図1A】ダマシン法によるCu配線パターンの形成工程を説明する図(その1)である。

【図1B】ダマシン法によるCu配線パターンの形成工程を説明する図(その2)である。

【図1C】ダマシン法によるCu配線パターンの形成工程を説明する図(その3)である。

【図1D】ダマシン法によるCu配線パターンの形成工程を説明する図(その4)である。

【図1E】ダマシン法によるCu配線パターンの形成工程を説明する図(その5)である。

【図2】理想的なボトムアップ充填の例を示す図である。

【図3A】本発明の課題を説明する図(その1)である。

【図3B】本発明の課題を説明する図(その2)である。

【図4】本発明の課題を説明する図である。

【図5】本発明の課題を説明する図である。

【図6】本発明の課題を説明する図である。

【図7】本発明の課題を説明する図である。

【図8】本発明の実施形態で使われる電解メッキ装置の構成を示す図である。

【図9A】第1の実施形態において行われた実験を説明する図(その1)である。

【図9B】第1の実施形態において行われた実験を説明する図(その2)である。

【図9C】第1の実施形態において行われた実験を説明する図(その3)である。

【図9D】第1の実施形態において行われた実験を説明する図(その4)である。

【図10】前記実験の結果を示す図である。

【図11A】前記実験の解釈を示す図である。

【図11B】前記実験の解釈を示す図である。

【図12】前記実験の解釈を示す図である。

【図13】前記実験についてさらに説明する図である。

【図14】前記実験についてさらに説明する図である。

【図15A】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その1)である。

【図15B】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その2)である。

【図15C】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その3)である。

【図15D】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その4)である。

【図15E】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その5)である。

【図16A】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その1)である。

【図16B】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その2)である。

【図16C】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その3)である。

【図16D】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その4)である。

【図16E】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その5)である。

【図16F】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その6)である。

【図16G】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その7)である。

【図16H】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その8)である。

【図16I】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その9)である。

【図16J】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その10)である。

【図16K】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その11)である。

【図16L】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その12)である。

【図17】第3の実施形態による半導体装置の構成を示す図である。

【符号の説明】

【0094】

1 電解メッキ装置

2 容器

2A 電解メッキ液

2B アノード

3 タンク

3A,3B 配管

4A バージンメークアップソリューション

4B アクセラレータ

4C サプレッサ

4D レベラ

4E 還元剤

5 濃度測定部

11,21,41 絶縁膜

12,22,42 凹部

13,23,43 バリアメタル膜

14,24,44 Cuシード層

15,25,45 Cu層

301 絶縁膜

302,305,307 SiN膜

303,306,308,312,317,405,411,415 層間絶縁膜

304,309 Taバリアメタル膜

305,310 銅層

308C コンタクトホール

308G 配線溝

308R 樹脂保護部

312V ビアホール

313 TaNバリアメタル膜

314 TiNバリアメタル膜

315 タングステン膜

315W タングステンプラグ

316 配線層

316A,316B,414A,414B アルミニウム配線パターン

316a,316c TiNバリアメタル膜

316b アルミニウム膜

318,416 パッシベーション膜

401 シリコン基板

401A 素子領域

401a,401b LDD構造

401c,401d ソース・ドレイン拡散領域

402 素子分離構造

403 ゲート電極

403A ゲート絶縁膜

404 SiN膜

405 絶縁膜

405A,405B コンタクトホール

406,412 TaN/TiNバリアメタル膜

407,413 タングステンプラグ

408〜410 銅配線層

R1〜R5 レジストパターン

【技術分野】

【0001】

本発明は一般に半導体装置に係り、特に電解メッキ法、および電解メッキ法を使った半導体装置の製造方法に関する。

【背景技術】

【0002】

今日の超微細化半導体集積回路装置では、基板上に形成された莫大な数の半導体素子を相互接続するために、低抵抗金属を配線パターンとした多層配線構造が使われている。特に銅(Cu)を配線パターンとした多層配線構造では、シリコン酸化膜、あるいはより比誘電率の低い、いわゆる低誘電率(low−K)材料よりなる層間絶縁膜中に配線溝あるいはビアホールをあらかじめ形成しておく。このビアホールに抵抗率が低くエレクトロマイグレーション耐性の高いCu層で充填し、余剰のCu層部分を化学機械研磨(CMP)により除去するダマシン法あるいはデュアルダマシン法が一般に使われている。

【0003】

ダマシン法あるいはデュアルダマシン法では、層間絶縁膜中に形成された配線溝あるいはビアホールの表面を、典型的にはTaやTaNなどの高融点金属あるいはその窒化物よりなるバリアメタル膜で覆う。その上に薄いCuシード層をPVD法あるいはCVD法により形成し、かかるCuシード層を電極として電解メッキを行うことにより、前記配線溝あるいはビアホールをCu層により充填している。

【特許文献1】特開2002−146585号公報

【特許文献2】特開2001−240995号公報

【特許文献3】特開2002−317274号公報

【特許文献4】特開2001−230252号公報

【特許文献5】特開2001−49491号公報

【特許文献6】特開2000−173949号公報

【特許文献7】特開2006−261268号公報

【特許文献8】特開2007−220882号公報

【特許文献9】特許第3208410号

【特許文献10】特開2006−299366号公報

【特許文献11】特開2001−251085号公報

【特許文献12】特許第3332668号

【特許文献13】特開2002−4081号公報

【特許文献14】特開2001−35812号公報

【特許文献15】特開2001−271196号公報

【特許文献16】特開2003−105584号公報

【特許文献17】特許第3367655号

【特許文献18】特許第3381170号

【特許文献19】特許第3938356号

【特許文献20】特開2007−197809号公報

【特許文献21】特開2004−225159号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

Cu層の電解メッキ工程では、一般的に硫酸銅などの銅塩を水などの極性溶媒に溶解した硫酸銅水溶液などの電解メッキ液が使われる。電解メッキ液には一般に微細な配線溝やビアホールを充填するため、数種類の添加物が組みあわせて添加される。これらの添加物には、配線溝やビアホールを、積極的に底部から上部に向かって充填(ボトムアップ充填)するために、硫黄系化合物よりなるアクセラレータ(ブライトナ、光沢剤とも呼ばれる)と、ポリエチレングリコールやポリプロピレングリコールなど、分子量が1000〜6000程度のポリマよりなるサプレッサ(抑制剤とも呼ばれる)とが添加されている。これにさらに、分子量が10000を超え、多くは環状構造を有するポリマよりなるレベラが添加されることもある。アクセラレータとサプレッサは、いずれが欠けても、所望のボトムアップ充填は得られない。

【0005】

図1A〜1Eは、典型的なダマシン法によるCu配線パターンの形成工程を、図2は、かかるCu配線パターン形成の際の理想的なボトムアップ充填の例を示す。

【0006】

図1Aにおいて、絶縁膜11に配線溝あるいはビアホールを構成する凹部12を形成する。次に図1Bに示すように、前記凹部12の側壁面および底面に、典型的にはTaやTiなどの高融点金属、あるいはTaNやTiNなど、その導電性窒化物よりなるバリアメタル膜13が、前記凹部12に整合した形状で形成される。

【0007】

さらに図1Cに示すように、前記バリアメタル膜13の表面にはCuシード層14が、PVD法あるいはCVD法により、前記凹部12に整合した形状で形成される。さらに図1Dに示すように、前記Cuシード層14を電極とした電解メッキにより、前記凹部12にCu層15を充填する。

【0008】

その際、使われる電解メッキ液に、先に説明したアクセラレータとサプレッサを添加する。これにより、図2に示すように、Cu層15の充填が、前記凹部12の底部から上方に向かって生じる(ボトムアップ充填)。

【0009】

さらに図1Eに示すように、前記層間絶縁膜11表面の不要なCu層15をCMP法により除去する。これにより、ボイドの少ない、ストレスマイグレーションやエレクトロマイグレーションに対する耐性の高いCu配線パターン15Aが得られる。

【0010】

ところが、最近の最小ビアあるいは溝径が90nm、あるいはそれ以下の超微細化多層配線構造を有する半導体装置では、電解メッキ液として、pH1以下の強酸性の液が使われるのが一般的である。この場合、薄いCuシード層14がメッキ液の作用により、溶解してしまう問題が生じることが知られている。

【0011】

図4は、図3Aおよび3Bに示すシード層14の、前記図1Dに示す電解メッキ工程初期における状態を示す。ただし図4は、前記図3Aの構造において前記凹部12の側壁面を覆うシード層14を、図3Bに矢印で示す方向から見た図である。図4では、10秒間の電解メッキ工程により、前記シード層14上に薄いCu層が形成されている。

【0012】

図4を参照するに、(A),(B)の図では前記凹部12の下部においてシード層14が溶解している。また図4(C)の図では中央部のシード層14が溶解しているのがわかる。なお図4の(A)〜(C)において、凹部12の下部に見える明るい部分は、前記凹部12の底部を覆うシード層14の断面を示す。試料作成時のへき開の結果、前記シード層14が塑性変形しているのがわかる。

【0013】

このように図1Cの構造においてシード層14が部分的に溶解すると、かかるシード層14を電極に図1Dの工程で電解メッキを行った場合、前記シード層14が欠如している部分にはCu層15の成膜は生じない。このため、図5に示すように、前記凹部12を充填するCu配線パターン15Aにボイドなどの欠陥が発生してしまう。

【0014】

従来、前記メッキシード層14の電解メッキ工程における溶解を抑制するため、被処理基板を電解メッキ液に浸漬する際に、予め被処理基板に電圧を印加することが行われている。一方、被処理基板を電解メッキ液に浸漬する場合には、気泡の発生を抑制するため、被処理基板を電解メッキ液の液面に対して斜めに傾けた状態で浸漬している。そこで、このようにバイアス電圧を印加した被処理基板を液面に対して斜めに傾けた状態で浸漬すると、浸漬された部分からCu層の堆積が直ちに開始されてしまう。その結果、図1Dに示すCu層15の成膜を最適に制御することが困難になってしまう。この問題は、特にビア径が70nm以下の超微細化半導体装置製造において顕著になる。

【0015】

また従来、このようなメッキシード層14の電解メッキ工程における溶解を抑制するため、特許文献1には、pH値の大きい弱酸性、あるいはアルカリ性のメッキ液を使う提案もなされている。しかし、このような技術では、特殊なメッキ液を使う必要がある。また最適な成膜条件も限られる。このため、超微細化半導体装置の製造に一般的に使用するのは困難である。

【0016】

また、上記Cuシード層の電解メッキ工程における溶解を抑制するため、電解メッキ液に高濃度のサプレッサを添加する技術も提案されている。

【0017】

図6(A)は、前記図1Cの構造に対し、アクセラレータもサプレッサも含まない硫酸銅水溶液よりなる電解メッキ液(バージンメークアップソリューション:VMS)を使ってCu層15の成膜を10秒程度行った場合についての、前記Cuシード層14の状態を示す図である。

【0018】

図6(B)は、前記図1Cの構造に対し、前記VMSにアクセラレータとして一般的に使われているジスルフィドプロパンスルホン酸(SPS)のみを添加して同様な電解メッキを短時間行った場合についての、前記Cuシード層14の状態を示す図である。

【0019】

図6(C)は、前記図1Cの構造に対し、前記VMSにサプレッサとして一般的に使われているポリエチレングリコール(PEG)のみを添加して同様な電解メッキを短時間行った場合についての、前記Cuシード層14の状態を示す図である。

【0020】

図6(A)〜(C)は、前記図4(A)〜(C)と同様に、前記凹部12の側壁面を見た状態の図となっている。

【0021】

図6(A)〜(C)を参照するに、VMSを使った図6(A)の場合には、前記凹部12の下部においてCuシード層14の溶解が認められ、これにアクセラレータを添加した図6(B)の場合、前記Cuシード層14の溶解がさらに促進されていることがわかる。一方、図(C)に示すサプレッサのみを添加した場合には、Cuシード層14の溶解が減少しているのがわかる。ただし、溶解の問題は、図6(C)の場合でも、完全に解消しているわけではない。そこで、前記Cuシード層14の溶解の問題だけを解消するためには、電解メッキ中に高濃度のサプレッサを添加することが考えられる。しかし、サプレッサだけを添加した場合には、先に図2で説明したようなCu層による凹部12のボトムアップ充填が不可能となる。また、前記凹部12の幅が70nm以下になると、図7(A),(B)に示すように、電解メッキ液にサプレッサを添加していても、凹部12の底部におけるCuシード層14の溶解は回避できない。ただし図7(A),(B)は、前記Cuシード層14の、図1Dの工程において短時間Cu層15の電解メッキを行った状態を、異なった倍率で示す。

【課題を解決するための手段】

【0022】

一の側面によれば、電解メッキ液は、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【0023】

他の側面によれば、電解メッキ方法は、銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、前記電解メッキ液が、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【0024】

他の側面によれば半導体装置の製造方法は、被処理基板上の絶縁膜中に凹部を形成する工程と、前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、を含み、前記銅層形成に用いる電解メッキ液が、極性溶媒と、前記極性溶媒中に溶解した硫酸銅と、硫黄化合物よりなるアクセラレータと、前記アクセラレータよりも小さい分子量を有する還元剤と、を含む。

【発明の効果】

【0025】

本発明によれば、電解メッキ液を使った銅層の電解メッキ工程において、電極として使われる銅シード層に生じる溶解の問題が、前記電解メッキ液に添加された、分子量がアクセラレータの分子量よりも小さい還元剤により効果的に抑制される。その結果、前記銅層により微細な凹部を下部から上部へと、順次充填することが可能となる。

【発明を実施するための最良の形態】

【0026】

[第1の実施形態]

本発明の発明者は、本発明の基礎となる研究において、先に説明したCuシード層14の溶解の問題に対するアクセラレータおよびサプレッサの効果について検討した。その結果、電解メッキ液に、さらに前記アクセラレータとして使われる化合物よりも分子量の小さい例えばグルコースを還元剤として添加した場合に、前記Cuシード層14の溶解が非常に効果的に抑制されることが見出された。

【0027】

以下、本発明を実施例について説明する。

【実施例】

【0028】

図8は、実験に使われた電解メッキ装置1の概略的構成を、図9A〜9Dは、本発明の発明者が行った実験の概要を示す。

【0029】

最初に図8を参照する。

【0030】

前記電解メッキ装置1は電解液2A中にアノード2Bを保持する容器2を備え、前記電解液2A中には被処理基板Wが浸漬される。

【0031】

前記容器2にはタンク3が配管3A,3Bを介して接続され、前記電解液2Aは、前記容器2とタンク3の間を、前記配管3A,3Bを通って循環している。

【0032】

さらに前記タンク3にはVMSを供給するユニット4Aと、アクセラレータを供給するユニット4Bと、サプレッサを供給するユニット4Cと、レベラを供給するユニット4Dと、還元剤を供給するユニット4Eが、それぞれのラインを介して接続されている。また前記タンク3中における電解液2Aの濃度を測定する濃度測定器5が結合されている。さらに電解メッキ処理の際には、前記被処理基板Wとアノード2Bに直流電源DCが接続される。

【0033】

図9Aを参照するに、絶縁膜21中には配線溝あるいはビアホールを構成する凹部22が70nmの幅および深さで形成される。さらに前記凹部22の側壁面および底面には図9Bに示すように、Ta膜よりなるバリアメタル膜23が、前記凹部22に整合した形状で、5〜6nmの膜厚で形成される。さらに図9Cに示すように、前記バリアメタル膜23の表面にはCuシード層24が、PVD法により、前記凹部12に整合した形状で、40〜100nmの膜厚で形成される。

【0034】

さらに図9Dの工程において、前記Cuシード層24を電極とした電解メッキを短時間、前記電解メッキ装置1を使って典型的には10秒間行う。これにより、前記Cuシード層24の表面にCu層25を約10nmの膜厚に形成する。このようにCuシード層24の表面に薄くCu層25を形成することにより、Cuシード層24中の欠陥を、より鮮明に検出することが可能となる。

【0035】

実施例1において本発明の発明者は、前記電解液2Aとして、Cuイオンを60g/Lの濃度で、また硫酸(H2SO4)を10g/Lの濃度で含み、さらに塩素(Cl)を50ppmの濃度で含む硫酸銅水溶液をVMSとして作製した。その際、実施例1ではさらに前記VMSに、アクセラレータとして化学式HO3S−CH2CH2CH2−S−S−CH2CH2CH2−SO3Hを有する分子量Mが310のジスルフィドプロパンスルホン酸(SPS)を20mg/Lの濃度で添加し、またサプレッサとして分子量が400,2000または6000のポリエチレングリコール(PEG)を添加し、サプレッサの重合度がそれぞれ異なった三種類の電解メッキ液を作製した。一方、実施例1の実施例では、Cu層による凹部22の埋込には余り影響しないため、レベラは使用していない。

【0036】

さらに実施例1においては、前記電解液2Aに前記還元剤として、分子量が180のD(+)グルコースを10〜20ppmの割合で添加している。

【0037】

図10(A),(B)は、前記図8の電解メッキ装置1において前記図9Cの構造上にCu層25を約10nmの膜厚に形成した試料を、図9Dに示すように矢印の方向から観察した図を示す。ここで図10(A)の試料は、グルコースを添加しなかった対照標準を示すのに対し、図10(B)の試料は、グルコースを添加した実施例1の試料を示している。ただし図10(A),(B)のいずれの試料でも、サプレッサとして分子量が2000のポリエチレングリコールを、300g/Lの割合で添加している。

【0038】

また図10(A),(B)の実験では、前記図8の装置1において、前記被処理基板Wを前記電解メッキ液2Aに浸漬する際にはバイアス電圧を印加せず、浸漬された後、5〜10mA/cm2の電流密度で通電を行っている。メッキ液の温度は25℃(常温:室温)に設定している。

【0039】

図10(A),(B)を比較すると、グルコースを添加しなかった場合には、前記Cuシード層24の溶解が、先に図4(A)〜(C)で説明したのと同様に生じているのに対し、グルコースを添加することにより、かかるCuシード層24の溶解が完全に止まっていることがわかる。

【0040】

図10(A),(B)の結果は、Cuシード層の溶解について、以下のメカニズムを示唆している。

【0041】

図11Aに概略的に示すように、電解メッキ液2A中にグルコースなどの還元剤が含まれてない場合、電解メッキ液2A中の溶存酸素によりCuシード層24が酸化され、形成されたCuOあるいはCu2Oなどの銅酸化物が、電解メッキ液2Aにより溶解される。その際、前記電解メッキ液2Aにアクセラレータが含まれていると、前記Cuシード層24の酸化が促進され、結果として、Cuシード層24の溶解が促進される。

【0042】

ところが電解メッキ液2A中にグルコースなどの還元剤が存在する場合、図11Bに概略的に示すように、電解メッキ液中の溶存酸素により形成された銅酸化物は直ちにCuに還元され、このため、電解メッキ液2A中にアクセラレータが含まれていても、Cuシード層24の溶解が抑制される。

【0043】

このようなメカニズムから考えて、前記還元剤はグルコースに限定されるものではなく、アルデヒド基あるいはケトン基を含み還元作用を示す糖類、アルデヒド基類、ケトン基類であってもよいことが考えられる。

【0044】

そこで、前記図11A,11Bの考察からは、前記電解メッキ液22A中に、アクセラレータに加えて還元剤を添加することで、Cuシード層24の電解メッキ液による溶解を抑制することが考えられる。

【0045】

しかし、微細な、例えば図12に示す最小線幅Wが70nm以下の凹部22をCu層の電解メッキにより充填するような場合を考えると、上に説明したメカニズムでは、前記還元剤は、アクセラレータよりも前記凹部22の破線で囲んだ底部22Aに、同等か、より高い効率で輸送されることが望ましい。このためには、前記還元剤は、アクセラレータと同等、あるいはそれ以下の分子量を有する化合物であることが望ましいことになる。なお図12の例では、前記絶縁膜21の下には、バリアメタル膜32を介して、下層の絶縁膜31が形成されている。本実施例で使われているアクセラレータSPSは、約310の分子量を有している。このため、前記還元剤は、例えば300以下の分子量を有するのが望ましい。グルコースは、約180の分子量を有しており、上記の条件を満たしている。

【0046】

このようなアルデヒド基あるいはケトン基を有し、300以下の分子量を有する還元剤としては、分子量が180のグルコースの他に、分子量が90のグリセルアルデヒド、分子量が120のエリトロース、分子量が120のトレオース、分子量が150のリボース、分子量が150のアラビノース、分子量が150のキシロース、分子量が150のリキソース、分子量が180のアロース、分子量が180のアルトロース、分子量が180のマンノース、分子量が180のグロース、分子量が180のイドース、分子量が180のガラクトース、分子量が180のタロースなどの単糖類が挙げられる。

【0047】

さらに前記還元剤としては、分子量が30のホルムアルデヒド、分子量が44のアセトアルデヒド、分子量が58のプロピオンアルデヒド、分子量が56のビニルアルデヒド、分子量が106のベンズアルデヒド、分子量が132のシンナムアルデヒド、分子量が150のペリルアルデヒドなどのアルデヒド基類、さらに分子量が59のアセトン、分子量が72のメチルエチルケトン、分子量が86のジエチルケトンなどのケトン基類が挙げられる。

【0048】

特にアクセラレータとして、SPSの代わりに分子量が155のメルカプトプロパンスルホン酸(MPS)を使うような場合には、上記の分子量が155以下の還元剤を使うことにより、先に説明したのと同様な効果を得ることが可能である。

【0049】

次に、本発明の発明者は、上記還元剤の作用・効果を確認するため、電解メッキ液2Aに、前記グルコースの代わりに、還元性を有さないポリエチレングリコールを、様々な分子量(400,2000,6000)および濃度(300mg/L,3000mg/L)で添加し、Cuシード層24の溶解抑制効果が生じるか否かを、先の図10(A),(B)の実験と同じ条件での実験により検討した。その結果を図13に示す。

【0050】

図13を参照するに、いずれの場合においても、前記Cuシード層24に顕著な溶解が生じているのがわかる。

【0051】

図13より、単にアクセラレータの分子量よりも小さい分子量の添加剤を電解メッキ液2Aに添加しても、その添加剤が還元作用を示さないならば、先に図10(A),(B)で得られたCuシード層24の溶解抑制効果は得られないことが結論される。

【0052】

さらに本発明の発明者は、上記還元剤の作用・効果を確認するため、サプレッサとして分子量が2000あるいは6000のポリエチレングリコールを使い、さらに還元剤の代わりに分子量が200のポリエチレングリコールを添加した電解メッキ液2Aを使い、Cuシード層24の溶解抑制効果が生じるか否かを、先の図10(A),(B)の実験と同じ条件での実験により検討した。その結果を図14に示す。

【0053】

図14中、(A)は前記分子量200のポリエチレングリコールを添加しない対照標準を、(B)は、前記分子量200のポリエチレングリコールを添加した例を示す。

【0054】

図10(A),(B)を参照するに、分子量200のポリエチレングリコールを添加しても、Cuシード層24には穴が形成されており、電解メッキ液による溶解を十分に抑制することができないことを示している。

【0055】

以上より、アクセラレータを添加された電解メッキ液によるCuシード層の溶解の問題は、前記電解メッキ液にさらに還元剤を添加し、その際、前記還元剤として、前記アクセラレータの分子量以下の分子量のものを選んで使うことにより、解決できるとの知見が示された。

【0056】

なお、このように電解メッキ液に還元剤を添加して、例えば図9Dの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層24の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。すなわち、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部22のCu層25による充填を最適な電流条件下で行うことが可能となる。その結果、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

【0057】

なお、本実施例の電解メッキ液2Aにおいて、硫酸銅を溶解する溶媒は水に限定されるものではなく、他の極性溶媒、例えばメタノール、エタノールなどのアルコール類、エチレンカーボネート、プロピレンカーボネートなどの環状カーボネート類、ジメチルカーボネート、エチルメチルカーボネート、ジエチルカーボネートなどの直鎖状カーボネート類、またはこれらの混合溶媒を使うことも可能である。

[第2の実施形態]

図15A〜15Eは、本発明の第2の実施形態によるCu配線パターンの形成方法を示す。

【0058】

図15Aを参照する。

【0059】

絶縁膜41中には配線溝あるいはビアホールを構成する凹部42が70nmの幅および深さで形成される。前記凹部42の側壁面および底面には図15Bに示すように、Ta膜よりなるバリアメタル膜43が、前記凹部42に整合した形状で、例えば5〜6nmの膜厚で形成される。さらに図10Cに示すように、前記バリアメタル膜43の表面にはCuシード層44が、PVD法により、前記凹部42に整合した形状で、40〜100nmの膜厚で形成される。

【0060】

さらに図15Dの工程において、前記Cuシード層44を電極とした電解メッキを、前記電解メッキ装置1において行い、前記Cuシード層24の表面から前記凹部22をCu層25により、ボトムアップ充填する。その際、前記電解メッキ液2Aとして、先の実施形態で説明したように、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを添加し、さらに還元剤としてグルコースを添加したものを使う。

【0061】

さらに図15Eの工程において、前記層間絶縁膜41表面の不要なCu層45をCMP法により除去することにより、ボイドの少ない、従ってストレスマイグレーションやエレクトロマイグレーションに対する耐性の高いCu配線パターン45Aが得られる。

【0062】

本実施形態では、電解メッキ液2Aにグルコースが還元剤として添加されている。このため、電解メッキ液2AにSPSなどのアクセラレータが添加さいれていてもCuシード層44の溶解が抑制される。その結果、図15Dの電解メッキ工程において前記凹部42をCu層45により、ボトムアップ充填することができ、Cu配線パターン45A中のボイドなどの欠陥発生を効果的に抑制することができる。

【0063】

また先に説明したように、図15Dの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層44の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。すなわち、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部42のCu層45による充填を最適な電流条件下で行うことが可能となる。よって、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

【0064】

なお、本実施形態では、前記電解メッキ液2Aに、必要に応じて例えばATMI社より商品名Viaform Levelerで市販されているレベラを添加してもよい。

[第3の実施形態]

次に、本発明の第3の実施形態による多層配線構造を有する半導体装置の製造工程を、図16A〜図16Lを参照しながら説明する。

【0065】

図16Aを参照するに、シリコン基板(図示せず)上の絶縁膜301上にはSiN膜302を介してSiO2などよりなる層間絶縁膜303が形成されている。前記層間絶縁膜303上には、所望の配線パターンに対応したレジストパターンR1が形成されている。

【0066】

次に図16Bの工程において前記層間絶縁膜303が前記レジストパターンR1をマスクにパターニングされる。その結果、前記層間絶縁膜303中には所望の配線パターニングに対応した配線溝が形成される。さらにこのようにパターニングされた層間絶縁膜303をTaバリアメタル膜304で覆った後、前記図15A〜15Dの工程を実行する。これにより銅層305が、前記配線溝を充填するように、電解めっき法により形成される。この電解メッキ法では、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを、還元剤としてグルコースを添加した電解メッキ液を使う。

【0067】

さらに図16Cの工程において前記銅層305およびその下のバリアメタル膜304が、前記層間絶縁膜303の表面が露出するまでCMP法により研磨・除去される。さらにこのようにして形成された構造上にSiNバリア膜305を介してSiO2などよりなる次の層間絶縁膜306が形成される。

【0068】

図16Cの工程ではさらに前記層間絶縁膜306上にSiNバリア膜307を介してSiO2などよりなる次の層間絶縁膜308が形成されている。さらに前記層間絶縁膜308上には所望のコンタクトホールに対応したレジストパターンR2が形成されている。

【0069】

次に図16Dの工程において前記レジストパターンR2をマスクに前記層間絶縁膜308,バリア膜307および層間絶縁膜306を順次パターニングしてコンタクトホール308Cを前記SiNバリア膜305が低部において露出するように形成する。その後、非感光性樹脂膜を塗布することにより、前記コンタクトホール308Cを前記樹脂膜により充填する。さらに前記層間絶縁膜308上の樹脂膜を溶解除去することにより、前記コンタクトホール308C中に樹脂保護部308Rを残す。

【0070】

さらに図16Dの工程では、前記層間絶縁膜308上に、前記層間絶縁膜308中に形成したい配線溝に対応したレジストパターンR3を形成する。

【0071】

次に図16Eの工程において前記樹脂保護部308Rによりコンタクトホール308Cの内壁面を保護した状態で前記レジストパターンR3をマスクに前記層間絶縁膜308を前記SiNバリア膜307が露出するまでパターニングする。これにより、前記層間絶縁膜308中に所望の配線溝308Gを形成する。

【0072】

さらに図16Eの工程では前記層間絶縁膜308のパターニングの後、前記樹脂保護部308Rをアッシングプロセスにより除去する。

【0073】

さらに図16Fの工程で、前記層間絶縁膜308を自己整合マスクに前記SiNバリア膜307および305を、それぞれ前記配線溝308Gおよびコンタクトホール308Cの底部から除去する。さらにこのようにして得られた構造の表面をTaバリアメタル膜309で覆った後、前記コンタクトホール308Cおよび配線溝308Gを充填するように銅層310を、先の図15A〜15Dの工程を実行する。これにより、硫酸銅水溶液にアクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを、還元剤としてグルコースを添加した電解メッキ液を使った電解めっき法により形成する。

【0074】

次に図16Gの工程において図16Fの銅層310およびその下のTaバリアメタル膜309を、前記層間絶縁膜308の表面が露出するまでCMP法により除去する。さらにこのようにして得られた構造上にSiNバリア膜311とSiO2などよりなる層間絶縁膜312を形成する。

【0075】

さらに図16Gの工程では前記層間絶縁膜312上に、前記層間絶縁膜312中に形成したいビアホールに対応したレジストパターンR4が形成されている。

【0076】

さらに図16Hの工程において前記層間絶縁膜312およびその下のSiNバリア膜311が前記レジストパターンR4をマスクにパターニングされる。その結果、前記層間絶縁膜312中に所望のビアホール312Vが形成される。

【0077】

さらに図16Iの工程において、前記図16Hの構造に、TaN膜よりなるバリアメタル層313が、前記層間絶縁膜312上に前記ビアホール312Vの側壁面および底面を連続して覆うように、反応性スパッタにより形成される。さらに前記TaNバリアメタル膜313上にTiNバリアメタル膜314がやはり反応性スパッタにより形成される。さらに図16Jの工程において前記図16Iの構造上にタングステン膜315をCVD法により、前記タングステン膜315が前記ビアホール312Vを充填するように形成する。

【0078】

さらに図16(K)の工程において前記タングステン膜315およびその下のTiN膜314、TaN313を前記層間絶縁膜312の表面が露出するまでCMP法により研磨・除去し、前記ビアホール312V中にタングステンビアプラグ315Wを形成する。

【0079】

さらに図16Kの工程では前記層間絶縁膜312上にTiNバリアメタル膜316aを介してアルミニウムあるいはアルミニウム−銅合金よりなる導体膜316bを形成する。さらに前記導体膜316b上に別のTiNバリアメタル膜316cを形成する。前記導体膜316bは、前記TiNバリアメタル膜316aおよび316cとともに、配線層316を形成する。

【0080】

図16Kの状態では、さらに形成したい配線パターンに対応したレジストパターンR5が前記配線層316上に形成されている。さらに図16Lの工程において前記配線層316が前記レジストパターンR5をマスクにドライエッチング等によりパターニングされ、配線パターン316A,316Bが、前記タングステンプラグ315W上に形成される。

【0081】

さらに図16Lの工程では、前記層間絶縁膜312上に前記配線パターン316A,316Bを覆うようにSiO2などの層間絶縁膜317が堆積され、前記層間絶縁膜317の表面にはSiNなどのパッシベーション膜318が形成されている。

【0082】

本実施形態においては、前記図16Bあるいは図16FのCu層305あるいは310の電解メッキ工程を、先に図15A〜15Dで説明したように硫酸銅水溶液よりなり、アクセラレータとしてSPSを、サプレッサとしてポリエチレングリコールを添加され、さらに還元剤としてグルコースを添加した電解メッキ液を使って実行する。これにより、前記Cu層305あるいは310により配線溝を、図示していないCuシード層を溶解することなくボトムアップ充填することができる。その結果、ボイドなどの欠陥の発生を効果的に抑制することができる。

【0083】

本実施形態においても、図16Bあるいは図16Fの電解メッキ工程を、図8の電解メッキ装置1を使って行う場合、従来Cuシード層の溶解を抑制するために行われていた、電解メッキ液2Aへの浸漬前の被処理基板Wに電圧印加を行うことが必要なくなる。このため、前記被処理基板Wへの通電を、前記電解メッキ液2Aに被処理基板Wが浸漬された後で開始することが可能となる。その結果、前記凹部のCu層305あるいは310による充填を最適な電流条件下で行うことが可能となる。これにより、最小線幅が70nm以下の微細なビアホールは配線溝を、図2で示したようなボトムアッププロセスにより、欠陥なく形成することが可能となる。

[第4の実施形態]

図17は、このようにして形成された多層配線構造を有する本発明の第4の実施形態による半導体装置の構成を示す図である。

【0084】

図17を参照するに、シリコン基板401上にはSTI構造402により素子領域401Aが画成されている。前記素子領域401A中には前記シリコン基板401上にゲート電極403がゲート絶縁膜403Aを介して形成されている。

【0085】

前記ゲート電極403の両側壁面上には側壁絶縁膜が形成されている。さらに前記シリコン基板401中には前記ゲート電極403の両側にLDD領域401a,401bが形成されている。また前記シリコン基板401中には前記側壁絶縁膜の外側にソース領域あるいはドレイン領域を形成する拡散領域401c、401dが形成されている。また前記シリコン基板401の表面は、前記ゲート電極403およびその側壁絶縁膜の形成部分を除き、SiN膜404により一様に覆われている。

【0086】

さらに前記SiN膜404上には前記ゲート電極403および側壁絶縁膜を覆うようにSiO2などよりなる層間絶縁膜405が形成されている。前記層間絶縁膜405中には前記拡散領域401c,401dを露出するコンタクトホール405A,405Bが形成されている。

【0087】

前記コンタクトホール405A,405Bの側壁面および底面はTaN膜およびTiN膜を積層したバリアメタル膜406により覆われている。さらに前記コンタクトホール405A,405Bは前記バリアメタル膜を介してタングステンプラグ407により充填されている。

【0088】

さらに前記層間絶縁膜405上には先の実施例で説明したようなダマシン法あるいはデュアルダマシン法により、層間絶縁膜中に銅配線パターンが埋め込まれた銅配線構造408,409,410が順次形成されている。前記銅配線構造410上には層間絶縁膜411中にTaN膜とTiN膜とを積層した導電性窒化物膜よりなるバリアメタル膜412で側壁面および底面が連続的に覆われたビアホール中に、タングステンよりなる導電性プラグ413が形成されている。

【0089】

さらに前記層間絶縁膜411上にはアルミニウムあるいはアルミニウム合金よりなる導体膜をTiNバリアメタル膜で狭持した構成の配線パターン414A,414Bが形成されておいる。さらに前記層間絶縁膜411上には前記配線パターン414A,414Bを覆うように層間絶縁膜415が形成されている。

【0090】

さらに前記層間絶縁膜415の表面は、SiNなどよりなるパッシベーション膜416により覆われている。

【0091】

以上、本発明を好ましい実施形態について説明したが、本発明はかかる特定の実施形態に限定されるものではなく、特許請求の範囲に記載した要旨内において様々な変形・変更が可能である。

【0092】

(付記1)

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ液。

(付記2)

前記還元剤は、水溶性のアルデヒド基あるいはケトン基を持つ化合物であることを特徴とする付記1記載の電解メッキ液。

(付記3)

前記還元剤は、300以下の分子量を有する付記1または2記載の電解メッキ液。

(付記4)

前記還元剤は、単糖類である付記1〜3のうち、いずれか一項記載の電解メッキ液。

(付記5)

前記還元剤は、グルコースを含む付記1〜4のうち、いずれか一項記載の電解メッキ液。

(付記6)

前記アクセラレータは、ジスルフィドプロパンスルホン酸を含む付記1〜5のうち、いずれか一項記載の電解メッキ液。

(付記7)

さらにポリエチレングリコールをサプレッサとして添加した付記1〜6のうち、いずれか一項記載の電解メッキ液。

(付記8)

銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、

前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、

前記電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ方法。

(付記9)

前記通電は、前記被処理基板が前記電解メッキ液に浸漬された後で開始されることを特徴とする付記8記載の電解メッキ方法。

(付記10)

被処理基板上の絶縁膜中に凹部を形成する工程と、

前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、

前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、

前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、

前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、

を含み、

前記銅層形成に用いる電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む半導体装置の製造方法。

(付記11)

前記電解メッキ法は、前記被処理基板を前記電解メッキ液中に浸漬する工程と、前記電解メッキ液中において前記銅シード層を電極に通電を行う工程とを含み、前記通電は、前記被処理基板が前記電解メッキ液中に浸漬した後で開始されることを特徴とする付記10記載の半導体装置の製造方法。

【図面の簡単な説明】

【0093】

【図1A】ダマシン法によるCu配線パターンの形成工程を説明する図(その1)である。

【図1B】ダマシン法によるCu配線パターンの形成工程を説明する図(その2)である。

【図1C】ダマシン法によるCu配線パターンの形成工程を説明する図(その3)である。

【図1D】ダマシン法によるCu配線パターンの形成工程を説明する図(その4)である。

【図1E】ダマシン法によるCu配線パターンの形成工程を説明する図(その5)である。

【図2】理想的なボトムアップ充填の例を示す図である。

【図3A】本発明の課題を説明する図(その1)である。

【図3B】本発明の課題を説明する図(その2)である。

【図4】本発明の課題を説明する図である。

【図5】本発明の課題を説明する図である。

【図6】本発明の課題を説明する図である。

【図7】本発明の課題を説明する図である。

【図8】本発明の実施形態で使われる電解メッキ装置の構成を示す図である。

【図9A】第1の実施形態において行われた実験を説明する図(その1)である。

【図9B】第1の実施形態において行われた実験を説明する図(その2)である。

【図9C】第1の実施形態において行われた実験を説明する図(その3)である。

【図9D】第1の実施形態において行われた実験を説明する図(その4)である。

【図10】前記実験の結果を示す図である。

【図11A】前記実験の解釈を示す図である。

【図11B】前記実験の解釈を示す図である。

【図12】前記実験の解釈を示す図である。

【図13】前記実験についてさらに説明する図である。

【図14】前記実験についてさらに説明する図である。

【図15A】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その1)である。

【図15B】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その2)である。

【図15C】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その3)である。

【図15D】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その4)である。

【図15E】第1の実施形態によるCu配線パターンのダマシン法による形成工程を説明する図(その5)である。

【図16A】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その1)である。

【図16B】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その2)である。

【図16C】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その3)である。

【図16D】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その4)である。

【図16E】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その5)である。

【図16F】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その6)である。

【図16G】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その7)である。

【図16H】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その8)である。

【図16I】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その9)である。

【図16J】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その10)である。

【図16K】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その11)である。

【図16L】第2の実施形態によるCu配線パターンのデュアルダマシン法による形成工程を説明する図(その12)である。

【図17】第3の実施形態による半導体装置の構成を示す図である。

【符号の説明】

【0094】

1 電解メッキ装置

2 容器

2A 電解メッキ液

2B アノード

3 タンク

3A,3B 配管

4A バージンメークアップソリューション

4B アクセラレータ

4C サプレッサ

4D レベラ

4E 還元剤

5 濃度測定部

11,21,41 絶縁膜

12,22,42 凹部

13,23,43 バリアメタル膜

14,24,44 Cuシード層

15,25,45 Cu層

301 絶縁膜

302,305,307 SiN膜

303,306,308,312,317,405,411,415 層間絶縁膜

304,309 Taバリアメタル膜

305,310 銅層

308C コンタクトホール

308G 配線溝

308R 樹脂保護部

312V ビアホール

313 TaNバリアメタル膜

314 TiNバリアメタル膜

315 タングステン膜

315W タングステンプラグ

316 配線層

316A,316B,414A,414B アルミニウム配線パターン

316a,316c TiNバリアメタル膜

316b アルミニウム膜

318,416 パッシベーション膜

401 シリコン基板

401A 素子領域

401a,401b LDD構造

401c,401d ソース・ドレイン拡散領域

402 素子分離構造

403 ゲート電極

403A ゲート絶縁膜

404 SiN膜

405 絶縁膜

405A,405B コンタクトホール

406,412 TaN/TiNバリアメタル膜

407,413 タングステンプラグ

408〜410 銅配線層

R1〜R5 レジストパターン

【特許請求の範囲】

【請求項1】

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ液。

【請求項2】

前記還元剤は、グルコースを含む請求項1記載の電解メッキ液。

【請求項3】

前記アクセラレータは、ジスルフィドプロパンスルホン酸を含む請求項1または2記載の電解メッキ液。

【請求項4】

さらにポリエチレングリコールをサプレッサとして添加した請求項1〜3のうち、いずれか一項記載の電解メッキ液。

【請求項5】

銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、

前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、

前記電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ方法。

【請求項6】

被処理基板上の絶縁膜中に凹部を形成する工程と、

前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、

前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、

前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、

前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、

を含み、

前記銅層形成に用いる電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む半導体装置の製造方法。

【請求項7】

前記電解メッキ法は、前記被処理基板を前記電解メッキ液中に浸漬する工程と、前記電解メッキ液中において前記銅シード層を電極に通電を行う工程とを含み、前記通電は、前記被処理基板が前記電解メッキ液中に浸漬した後で開始される請求項6記載の半導体装置の製造方法。

【請求項1】

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ液。

【請求項2】

前記還元剤は、グルコースを含む請求項1記載の電解メッキ液。

【請求項3】

前記アクセラレータは、ジスルフィドプロパンスルホン酸を含む請求項1または2記載の電解メッキ液。

【請求項4】

さらにポリエチレングリコールをサプレッサとして添加した請求項1〜3のうち、いずれか一項記載の電解メッキ液。

【請求項5】

銅シード層を形成された被処理基板を、電解メッキ液中に浸漬する工程と、

前記電解メッキ液に浸漬された被処理基板に銅層を電解メッキにより堆積する工程と、を含み、

前記電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む電解メッキ方法。

【請求項6】

被処理基板上の絶縁膜中に凹部を形成する工程と、

前記絶縁膜上に、前記凹部の側壁面および底面を連続して覆うようにバリアメタル膜を、前記凹部の形状に整合した形状で成膜する工程と、

前記絶縁膜上に、前記バリアメタル膜を覆って銅シード層を、前記凹部の形状に整合した形状で成膜する工程と、

前記銅シード層を電極とした電解メッキ法により、前記凹部を銅層により充填する工程と、

前記絶縁膜上において前記銅層を、前記絶縁膜表面が露出するまで化学機械研磨法により除去する工程と、

を含み、

前記銅層形成に用いる電解メッキ液が、

極性溶媒と、

前記極性溶媒中に溶解した硫酸銅と、

硫黄化合物よりなるアクセラレータと、

前記アクセラレータよりも小さい分子量を有する還元剤と、

を含む半導体装置の製造方法。

【請求項7】

前記電解メッキ法は、前記被処理基板を前記電解メッキ液中に浸漬する工程と、前記電解メッキ液中において前記銅シード層を電極に通電を行う工程とを含み、前記通電は、前記被処理基板が前記電解メッキ液中に浸漬した後で開始される請求項6記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図3B】

【図8】

【図9A】

【図9B】

【図9C】

【図9D】

【図11B】

【図12】

【図15A】

【図15B】

【図15C】

【図15D】

【図15E】

【図16A】

【図16B】

【図16C】

【図16D】

【図16E】

【図16F】

【図16G】

【図16H】

【図16I】

【図16J】

【図16K】

【図16L】

【図17】

【図2】

【図3A】

【図4】

【図5】

【図6】

【図7】

【図10】

【図11A】

【図13】

【図14】

【図1B】

【図1C】

【図1D】

【図1E】

【図3B】

【図8】

【図9A】

【図9B】

【図9C】

【図9D】

【図11B】

【図12】

【図15A】

【図15B】

【図15C】

【図15D】

【図15E】

【図16A】

【図16B】

【図16C】

【図16D】

【図16E】

【図16F】

【図16G】

【図16H】

【図16I】

【図16J】

【図16K】

【図16L】

【図17】

【図2】

【図3A】

【図4】

【図5】

【図6】

【図7】

【図10】

【図11A】

【図13】

【図14】

【公開番号】特開2009−228078(P2009−228078A)

【公開日】平成21年10月8日(2009.10.8)

【国際特許分類】

【出願番号】特願2008−76681(P2008−76681)

【出願日】平成20年3月24日(2008.3.24)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成21年10月8日(2009.10.8)

【国際特許分類】

【出願日】平成20年3月24日(2008.3.24)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]