静電型アクチュエータ装置

【課題】短時間で静電型アクチュエータの駆動に必要な高電圧を生成する。

【解決手段】静電型アクチュエータ装置10は、電圧Vpp1を生成する電圧生成回路13−1と、電圧生成回路13−1とノードN1との間に接続されたスイッチSW1と、電圧Vpp2を生成する電圧生成回路13−2と、電圧生成回路13−2とノードN2との間に接続されたスイッチSW2と、ノードN1とノードN2との間に接続されたキャパシタCbと、ノードN1に駆動電極が接続された静電型アクチュエータ16とを含む。そして、静電型アクチュエータ16の駆動時に、スイッチSW1がオン、スイッチSW1がオフ、スイッチSW2がオンの順に動作する。

【解決手段】静電型アクチュエータ装置10は、電圧Vpp1を生成する電圧生成回路13−1と、電圧生成回路13−1とノードN1との間に接続されたスイッチSW1と、電圧Vpp2を生成する電圧生成回路13−2と、電圧生成回路13−2とノードN2との間に接続されたスイッチSW2と、ノードN1とノードN2との間に接続されたキャパシタCbと、ノードN1に駆動電極が接続された静電型アクチュエータ16とを含む。そして、静電型アクチュエータ16の駆動時に、スイッチSW1がオン、スイッチSW1がオフ、スイッチSW2がオンの順に動作する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、静電型アクチュエータ装置に関する。

【背景技術】

【0002】

MEMS(Micro-Electro-Mechanical Systems)技術を用いた高周波(RF:Radio Frequency)−MEMS可変容量やRF−MEMSスイッチが開発されており、これらMEMS可変容量やMEMSスイッチには静電型アクチュエータが使用されている(例えば、特許文献1を参照)。

【0003】

静電型アクチュエータの駆動電圧は、半導体装置内に設けられた昇圧回路により生成される(例えば、特許文献2及び3を参照)。静電型アクチュエータを駆動させるには、例えば10V以上の高い電圧が必要である。この高電圧を昇圧回路で生成するには時間がかかり、この結果、MEMSのスイッチング速度が遅くなってしまう。また、高電圧を生成する昇圧回路は回路面積が大きくなり、製造コストが高くなってしまう。

【0004】

また、高い電圧で静電型アクチュエータを駆動した場合、チャージングによるスティクションが増加し、不良が起きやすくなる。したがって、短時間で静電型アクチュエータを駆動するために必要な高電圧を生成でき、チャージングを起きにくくすることが望まれている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−123110号公報

【特許文献2】特開平7−160215号公報

【特許文献3】特開2004−336904号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、短時間で静電型アクチュエータの駆動に必要な高電圧を生成することが可能な静電型アクチュエータ装置を提供する。

【課題を解決するための手段】

【0007】

本発明の一態様に係る静電型アクチュエータ装置は、第1の電圧を生成する第1の電圧生成回路と、前記第1の電圧生成回路と第1のノードとの間に接続された第1のスイッチと、第2の電圧を生成する第2の電圧生成回路と、前記第2の電圧生成回路と第2のノードとの間に接続された第2のスイッチと、前記第1のノードと前記第2のノードとの間に接続されたキャパシタと、前記第1のノードに駆動電極が接続された静電型アクチュエータとを具備し、前記静電型アクチュエータの駆動時に、前記第1のスイッチがオン、前記第1のスイッチがオフ、前記第2のスイッチがオンの順に動作する。

【発明の効果】

【0008】

本発明によれば、短時間で静電型アクチュエータの駆動に必要な高電圧を生成することが可能な静電型アクチュエータ装置を提供することができる。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図。

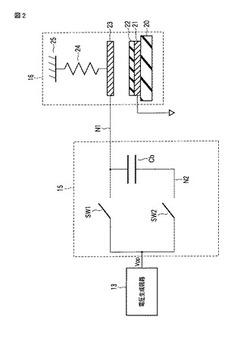

【図2】1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図。

【図3】可変容量デバイス26の構成を示す断面図。

【図4】複数個の静電型アクチュエータ16を示す概略図。

【図5】スイッチユニット15の具体的な構成例を示す回路図。

【図6】静電型アクチュエータ装置10の他の構成を示す回路図。

【図7】ローパスフィルタ31の構成例を示す回路図。

【図8】静電型アクチュエータ16のアップ状態とダウン状態とを示す概略図。

【図9】静電型アクチュエータ16に印加される電圧を説明するタイミングチャート。

【図10】図5に示したローカルブースタ30−1の構成を示す回路ブロック図。

【図11】昇圧回路32の構成例を示す回路図。

【図12】第2の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図

【図13】1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図。

【図14】第3の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図。

【図15】第4の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図。

【図16】ゲートキャパシタCbの特性を示すグラフ。

【図17】MOSキャパシタCbの構成を示す断面図。

【図18】MOSキャパシタCbの特性を示すグラフ。

【発明を実施するための形態】

【0010】

以下、本発明の実施形態について図面を参照して説明する。なお、以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0011】

[第1の実施形態]

図1は、本発明の第1の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図である。静電型アクチュエータ装置10は、n(nは1以上の整数)個の静電型アクチュエータ16と、静電型アクチュエータ16を駆動する駆動回路11と、駆動回路11の動作を制御する制御回路17とを備えている。駆動回路11は、発振器(OSC)12、電圧生成回路13、リミッタ(LIM)14、及びn個(静電型アクチュエータ16と同じ数)のスイッチユニット15を備えている。駆動回路11と静電型アクチュエータ16とは、例えば同一基板上に形成される。

【0012】

電圧生成回路13は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vppを生成する。昇圧回路は、例えばチャージポンプにより構成される。このチャージポンプは、発振器12から供給されるクロックCLKを用いてポンプ動作を実行する。

【0013】

電圧生成回路13には、リミッタ14が接続されている。リミッタ14は、電圧生成回路13の出力が所定電圧より高くなるのを防ぐ。これにより、電圧生成回路13は、安定した電圧を出力することができる。

【0014】

図2は、1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図である。

【0015】

静電型アクチュエータ16は、例えば絶縁性の基板20上に設けられた第1の電極21と、第1の電極21上に設けられた絶縁膜22と、絶縁膜22の上方に設けられかつ上下に移動可能である第2の電極23とを備えている。第2の電極23は、弾性体(例えばバネ)24を介して固定部25に接続されている。絶縁性の基板20は、ガラス基板や、シリコン基板上に形成された絶縁層等からなる。なお、絶縁膜22は、第1の電極21と第2の電極23とが電気的に接触するのを防ぐ役割を果たせばよく、従って、絶縁膜22は、第1の電極21と第2の電極23との間に設けられていればよい。例えば、絶縁膜22は、第2の電極23の下のみに設けられていてもよいし、第1の電極21上及び第2の電極23の下の両方に設けられていてもよい。

【0016】

第1の電極21は接地されており、すなわち、第1の電極21には、接地電圧Vssが供給される。第2の電極23は、ノードN1を介してスイッチユニット15に接続されている。よって、第2の電極23は、これに印加される電圧に応じて上下に移動することが可能となる。

【0017】

静電型アクチュエータは、例えば図3のような可変容量デバイス26の一部を構成していてもよい。第1の静電型アクチュエータ16Aは、第1の電極21A、絶縁膜22A、第2の電極23A、バネ24A、及び固定部25Aから構成されている。第2の静電型アクチュエータ16Bは、第1の電極21B、絶縁膜22B、第2の電極23B、バネ24B、及び固定部25Bから構成されている。可変容量16Cは、基板20上に設けられた第1の電極21Cと、第1の電極21C上に設けられた絶縁膜22Cと、絶縁膜22Cの上方に設けられかつ上下に移動可能である第2の電極23Cとを備えている。

【0018】

第2の電極23Cは、その両側がそれぞれ絶縁層を介して第2の電極23A及び23Bに固定されており、第2の電極23A及び第2の電極23Bの動きに合わせて上下に移動することができる。よって、第1の電極21C、絶縁膜22C、及び第2の電極23Cは、可変容量として機能する。なお、静電型アクチュエータは、可変容量デバイス以外のデバイスにも適用することが可能であり、例えばスイッチにも適用できる。

【0019】

スイッチユニット15は、スイッチSW1及びSW2と、キャパシタCbとを備えている。スイッチSW1の一端は、電圧生成回路13の出力に接続され、スイッチSW1の他端は、ノードN1を介してキャパシタCbの第1の電極に接続されている。スイッチSW2の一端は、電圧生成回路13の出力に接続され、スイッチSW2の他端は、ノードN2を介してキャパシタCbの第2の電極に接続されている。スイッチユニット15は、スイッチSW1及びSW2の動作を制御することで、静電型アクチュエータ16の第2の電極23に駆動電圧を供給することができる。

【0020】

静電型アクチュエータ16の数は、複数であっても勿論構わない。図4は、複数個の静電型アクチュエータ16を示す概略図である。この場合、静電型アクチュエータ装置10は、複数個の静電型アクチュエータ16−1〜16−nに対応する複数個のスイッチユニット15−1〜15−nを備えている。1個のスイッチユニット15は、これに接続される1個の静電型アクチュエータ16にのみ駆動電圧を供給する役割をもつ。電圧生成回路13は、複数個の静電型アクチュエータ16−1〜16−nに対して1個のみ設けられる。なお、以下の説明では、1個の静電型アクチュエータ16の構成及び動作について説明するが、他の静電型アクチュエータの構成及び動作も以下の説明と同じである。

【0021】

図5は、スイッチユニット15の具体的な構成例を示す回路図である。スイッチSW1及びSW2としては、高耐圧用のMOSFET(Metal Semiconductor Field Effect Transistor)が用いられ、例えばNチャネルMOSFET(NMOSFET)が用いられる。

【0022】

NMOSFET(SW1)のドレインは、電圧生成回路13の出力に接続され、NMOSFET(SW1)のソースは、ノードN1を介してキャパシタCbの第1の電極に接続されている。NMOSFET(SW1)のゲート電圧は、ローカルブースタ30−1によって制御される。

【0023】

NMOSFET(SW2)のドレインは、電圧生成回路13の出力に接続され、NMOSFET(SW2)のソースは、ノードN2を介してキャパシタCbの第2の電極に接続されている。NMOSFET(SW2)のゲート電圧は、ローカルブースタ30−2によって制御される。

【0024】

ノードN1は、第1の放電回路D1に接続されている。第1の放電回路D1は、制御回路17からの制御信号CS1に基づいてノードN1を放電する。ノードN2は、第2の放電回路D2に接続されている。第2の放電回路D2は、制御回路17からの制御信号CS2に基づいてノードN2を放電する。第1の放電回路D1及び第2の放電回路D2の各々は、例えばNチャネルMOSFETから構成される。

【0025】

ノードN1に接続されたキャパシタCparaは配線の寄生容量を示しており、Cactは静電型アクチュエータ16の容量である。CparaとCactとを合わせてCLと表記する。

【0026】

図6に示すように、スイッチユニット15と静電型アクチュエータ16との間にローパスフィルタ(LPF)31を挿入してもよい。図7は、ローパスフィルタ31の構成例を示す回路図である。ローパスフィルタ31は、2個の抵抗31−1及び31−2と、キャパシタ31−3から構成されている。ローパスフィルタ31を用いることで、電圧生成回路13からのノイズやリップル(ripple)を低減できるため、静電型アクチュエータ16の動作が安定する。

【0027】

本実施形態では、スイッチユニット15と静電型アクチュエータ16との間、具体的には、キャパシタCbの第1の電極と静電型アクチュエータ16との間には、抵抗素子以外のものは接続されていない。これは、スイッチユニット15からの出力電圧をそのまま静電型アクチュエータ16に伝えるために必要な条件である。

【0028】

(動作)

次に、このように構成された静電型アクチュエータ装置10の動作について説明する。静電型アクチュエータ16は、第2の電極23に印加される電圧に応じて、アップ状態とダウン状態とを取り得る。スイッチユニット15からの出力が静電型アクチュエータ16の駆動電圧以上になった場合に、静電型アクチュエータ16は、アップ状態からダウン状態に遷移する。

【0029】

図8は、静電型アクチュエータ16のアップ状態とダウン状態とを示す概略図である。アップ状態とは、静電型アクチュエータ16が駆動していない状態であり、アップ状態時の第2の電極23の電圧は、接地電圧Vss以上かつプルイン電圧未満である。プルイン電圧とは、第2の電極23が下に駆動するために要する電圧であり、第2の電極23が第1の電極21に引き付けられる静電引力がバネ24の復元力よりも大きくなる電圧である。

【0030】

静電型アクチュエータ16を駆動する、すなわちアップ状態からダウン状態にするには、次の順番でスイッチSW1及びSW2を動作させる。

【0031】

(1)SW1:オン

(2)SW1:オフ

(3)SW2:オン

図9は、静電型アクチュエータ16に印加される電圧を説明するタイミングチャートである。図9には、図5のノードN1及びN2の電圧を示している。電圧生成回路13の出力電圧をVpp、静電型アクチュエータ16のアップ状態及びダウン状態における容量値をそれぞれCact[up]及びCact[down]とする。

【0032】

スイッチSW1をオンすると、静電型アクチュエータ16には電圧Vppが供給される。この電圧Vppは、静電型アクチュエータ16のホールド電圧以上、静電型アクチュエータ16のプルイン電圧未満に設定される。したがって、この時点では、静電型アクチュエータ16はアップ状態のままである。ホールド電圧とは、第2の電極23が下に駆動して絶縁膜22と接触した後、この状態を保持するのに要する電圧である。ホールド電圧は、プルイン電圧未満である。

【0033】

ついで、スイッチSW1をオフした後に、スイッチSW2をオンする。ノードN2に電圧Vppが供給されると、キャパシタCbの容量結合によりノードN1が電圧Vpp及びプルイン電圧の各々より高い駆動電圧Vact1まで上昇する。駆動電圧Vact1は、次式で表される。

【0034】

Vact1={(2Cb+Cpara+Cact[up])/(Cb+Cpara+Cact[up])}・Vpp

Vpp=22V、Cb=CL(=Cpara+Cact)とすると、Vact1=33Vである。この電圧Vact1により静電型アクチュエータ16を駆動させ、静電型アクチュエータ16をダウン状態にできる。この方式によれば、電圧Vact1よりも低い電圧Vppを生成する電圧生成回路13を用いて静電型アクチュエータ16を駆動できる。このため、直接駆動電圧Vact1を生成する場合に比べて、電圧生成回路13の面積を縮小できる。また、電圧生成回路13は、駆動電圧Vact1より低い電圧Vppを生成すればよいため、昇圧時間も短縮できる。

【0035】

さらに、本方式では、静電型アクチュエータ16のチャージングも抑制できる。チャージングとは、静電型アクチュエータ16が駆動を繰り返すことで、絶縁膜22に電荷が蓄えられ、この電荷に起因して第2の電極23が絶縁膜22から離れにくくなる現象である。このチャージングは、駆動電圧が高くなるほどその影響が大きくなる。以下に、チャージングを抑制できる理由を説明する。

【0036】

静電型アクチュエータ16に駆動電圧Vact1が供給されるとアップ状態からダウン状態に遷移するが、その前後でノードN1の電荷量は保持される。一方、静電型アクチュエータ16の容量値はCact[up]からCact[down]に増加する。この結果、ノードN1の電圧は、Vact1からVact2に減少する。電圧Vact2は、静電型アクチュエータ16のホールド電圧以上、電圧Vact1未満に設定される。電圧Vact2は、次式で表される。

【0037】

Vact2={(Cb+Cpara+Cact[up])/(Cb+Cpara+Cact[down])}・Vact1

これにより、静電型アクチュエータ16の絶縁膜22に印加される電界が緩和され、チャージングが抑制される。静電型アクチュエータ16をアップ状態に戻す場合には、第1の放電回路D1及び第2の放電回路D2によりノードN1及びノードN2をそれぞれ放電する。

【0038】

ここで、図9の動作を実現するためには、スイッチユニット15の出力電圧(駆動電圧)を、この出力電圧がドロップすることなく、静電型アクチュエータ16に直接印加することが必要である。このため、スイッチユニット15と静電型アクチュエータ16との間には、スイッチユニット15の出力電圧を変化させる素子(例えば、スイッチや電源)が挿入されていない。抵抗素子を含むローパスフィルタ31は、電圧のノイズやリップルを低減する回路であり、スイッチユニット15と静電型アクチュエータ16との間にローパスフィルタ31が接続されている場合でも、スイッチユニット15の出力電圧を静電型アクチュエータ16に直接印加することが可能である。換言すると、スイッチユニット15と静電型アクチュエータ16との間には、抵抗素子以外の電圧を変化させる素子が挿入されていない。

【0039】

なお、スイッチSW2がオンとなりノードN1が駆動電圧Vact1に上昇したときは、スイッチSW1を構成するNMOSFETのゲート−ソース間に大きな電位差が印加される。この動作が何度も繰り返されると、NMOSFET(SW1)のゲート絶縁膜が劣化する。これを防ぐため、スイッチSW2をオンさせるときはNMOSFET(SW1)のゲート電圧を0Vとせず、0より大きくかつ電圧Vppより低い中間電圧に設定する。この動作を実現するためのローカルブースタ30−1の構成例について説明する。図10は、図5に示したローカルブースタ30−1の構成を示す回路ブロック図である。ローカルブースタ30−2の構成も、図10と同じである。

【0040】

ローカルブースタ30−1は、昇圧回路32、リミッタ(LIM)33、第1の放電回路34、及び第2の放電回路35を備えている。昇圧回路32は、電源電圧Vddを用いて、スイッチSW1を構成するNMOSFETをオンさせるゲート電圧を生成する。昇圧回路32の出力は、ノードN3を介してスイッチSW1に接続されている。昇圧回路32は、例えばチャージポンプにより構成される。このチャージポンプは、発振器12から供給されるクロックCLKを用いてポンプ動作を実行する。

【0041】

昇圧回路32には、リミッタ33が接続されている。リミッタ33は、昇圧回路32の出力が所定電圧より高くなるのを防ぐ。これにより、昇圧回路32は、安定した電圧を出力することができる。

【0042】

ノードN3には、第1の放電回路34が接続されている。第1の放電回路34は、NMOSFETから構成される。NMOSFET34のドレインは、ノードN3に接続され、NMOSFET34のソースは接地され、NMOSFET34のゲートには、制御回路17から制御信号CS3が供給されている。第1の放電回路34は、ノードN3をほぼ0Vまで放電する。

【0043】

ノードN3には、第2の放電回路35が接続されている。第2の放電回路35は、複数のダイオード35Aが直列接続(縦続接続)されたダイオード群と、スイッチ素子としてのNMOSFET35Bとから構成される。各ダイオード35Aは、例えば、NMOSFETがダイオード接続されて構成される。1段目のダイオード35Aのアノードは、ノードN3に接続されている。

【0044】

NMOSFET35Bのドレインは、最終段のダイオード35Aのカソードに接続され、NMOSFET35Bのソースは接地され、NMOSFET35Bのゲートには、制御回路17から制御信号CS4が供給されている。第2の放電回路35は、ノードN3を複数のダイオード35Aの電圧降下分の電圧付近まで放電する。よって、ダイオード35Aの数を最適に設定することで、ノードN3の電圧を0Vより高い所望の電圧まで放電することが可能となる。

【0045】

図11は、昇圧回路32の構成例を示す回路図である。NAND回路NDの第1の入力端子には、発振器12からクロックCLKが供給され、NAND回路NDの第2の入力端子には、制御回路17からイネーブル信号ENが供給されている。NAND回路NDの出力は、インバータ回路INV1の入力に接続されている。インバータ回路INV1の出力は、インバータ回路INV2の入力に接続されている。

【0046】

インバータ回路INV1は、イネーブル信号ENがハイレベルの間、クロックCLKを出力する。インバータ回路INV2は、イネーブル信号ENがハイレベルの間、クロックCLKを反転したクロックbCLKを出力する。

【0047】

キャパシタ32Aの第1の電極は、ダイオード32Bのアノードに接続されている。ダイオード32Bのカソードは、次段のダイオードのアノードに接続されている。このような関係を維持しつつ、1個のキャパシタ32Aと1個のダイオード32Bとからなるユニットが、ダイオード32Bが直列接続されるようにして、複数個接続されている。

【0048】

ダイオード32Bは、例えば、I(intrinsic)タイプのNMOSFETがダイオード接続されて構成されている。IタイプNMOSFETは、そのしきい値電圧がほぼ0Vであるため、ダイオード32Bの電圧降下もほぼ0Vに抑えることができる。

【0049】

1段目のダイオード32Bのアノードには、電圧生成回路13から電圧Vppが供給されている。最終段のダイオード32Bのカソードは、ノードN3に接続されている。複数のキャパシタ32Aには、クロックCLK及びbCLKが交互に供給されている。これにより、昇圧回路32は、キャパシタ32Aに蓄えられた電荷を次段のキャパシタに転送することで、電圧Vppより高い電圧を生成することができる。

【0050】

このように構成されたローカルブースタ30−1の動作について説明する。スイッチSW1をオンさせるときは、昇圧回路32によってスイッチSW1にオン電圧を供給する。ついで、スイッチSW1をオフさせるときは、ローカルブースタ30−1の第1の放電回路34によりノードN3を放電する。これにより、スイッチSW1のNMOSFETのゲート電圧はほぼ0Vになり、スイッチSW1はオフする。

【0051】

ついで、スイッチSW2をオンさせるときは、ローカルブースタ30−1の第2の放電回路35のNMOSFET35Bをオンさせる。この時、ローカルブースタ30−1の第1の放電回路34は、オフである。これにより、ノードN3は、接地電圧Vssから複数のダイオード35Aの電圧降下分だけ高い電圧、例えば10V程度に設定される。例えばVact1=33Vとすると、スイッチSW1のNMOSFETのゲート−ソース間の電位差は23V程度となり、ゲート電圧を0Vにした場合より10V程度低い電位差に設定される。この結果、スイッチSW1のゲート絶縁膜が劣化するのを抑制することができる。

【0052】

(効果)

以上詳述したように第1の実施形態では、電圧Vppを生成する電圧生成回路13と静電型アクチュエータ16との間にスイッチユニット15を接続し、このスイッチユニット15が、電圧Vppより高い、静電型アクチュエータ16の駆動電圧Vact1を生成するようにしている。スイッチユニット15は、キャパシタCbと、電圧生成回路13とキャパシタCbの第1の電極との間に接続されたスイッチSW1と、電圧生成回路13とキャパシタCbの第2の電極との間に接続されたスイッチSW2とを備えている。そして、静電型アクチュエータ16の駆動時に、スイッチSW1がオン、スイッチSW1がオフ、スイッチSW2がオンの順に動作するようにしている。

【0053】

従って第1の実施形態によれば、スイッチユニット15を用いて、電圧生成回路13が生成する電圧Vppより高い駆動電圧Vact1を静電型アクチュエータ16に供給することができる。これにより、電圧生成回路13の面積を縮小することが可能となり、製造コストの低減が可能である。

【0054】

また、非常に短い時間で駆動電圧Vact1を生成することができる。これにより、静電型アクチュエータ16のスイッチング速度を速くすることが可能となる。

【0055】

また、静電型アクチュエータ16を駆動させる際、静電型アクチュエータ16に駆動電圧Vact1を印加した後、静電型アクチュエータ16をダウン状態に維持しつつ、Vact1より低い電圧Vact2に自動的に低くすることが可能である。これにより、静電型アクチュエータ16のチャージングを抑制することができ、ひいてはスティクション不良を低減することができる。

【0056】

また、スイッチSW1がオフ、及びスイッチSW2がオン時に、ローカルブースタ30−1を用いて、スイッチSW1のNMOSFETのゲート−ソース間の電位差を小さくするようにしている。これにより、スイッチSW1のNMOSFETのゲート絶縁膜が劣化するのを防ぐことができる。

【0057】

[第2の実施形態]

第1の実施形態では、スイッチSW1及びSW2に供給される電圧は共に、電圧生成回路13が生成した電圧Vppであるが、これに限定されるものではなく、スイッチSW1に供給される電圧とスイッチSW2に供給される電圧とが異なっていてもよい。第2の実施形態は、異なる電圧Vpp1及びVpp2をそれぞれ生成する第1の電圧生成回路13−1及び第2の電圧生成回路13−2を駆動回路11が備え、第1の電圧生成回路13−1は、スイッチSW1に電圧Vpp1を供給し、第2の電圧生成回路13−2は、スイッチSW2に電圧Vpp2を供給するようにしている。

【0058】

図12は、本発明の第2の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図である。駆動回路11は、第1の電圧生成回路13−1及び第2の電圧生成回路13−2を備えている。第1の電圧生成回路13−1にはリミッタ14−1が接続され、第2の電圧生成回路13−2にはリミッタ14−2が接続されている。

【0059】

第1の電圧生成回路13−1は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vpp1を生成する。第2の電圧生成回路13−2は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vpp2を生成する。

【0060】

図13は、1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図である。第1の電圧生成回路13−1の電圧Vpp1は、スイッチSW1の一端に供給される。第2の電圧生成回路13−2の電圧Vpp2は、スイッチSW2の一端に供給される。その他の構成は、図2と同じである。

【0061】

電圧Vpp1は、静電型アクチュエータ16のホールド電圧以上、静電型アクチュエータ16のプルイン電圧未満に設定される。駆動電圧Vact1は、次式で表される。

【0062】

Vact1=Vpp1+{Cb/(Cb+Cpara+Cact[up])}・Vpp2

電圧Vact2の式は、第1の実施形態と同じである。電圧Vpp2は、駆動電圧Vact1が静電型アクチュエータ16のプルイン電圧以上になるように設定される。具体的には、電圧Vpp2は、以下の式で表される。Vpiは、静電型アクチュエータ16のプルイン電圧である。

【0063】

Vpp2≧{(Cb+Cpara+Cact[up])/Cb}・(Vpi−Vpp1)

このように、前述した電圧条件を満たしつつ、スイッチSW1及びSW2に異なる電圧を印加した場合でも、第1の実施形態と同じ動作を実現できる。よって、第2の実施形態の静電型アクチュエータ装置10は、第1の実施形態と同じ効果を得ることができる。

【0064】

[第3の実施形態]

第3の実施形態は、静電型アクチュエータ16の第1の電極21及び第2の電極23のそれぞれにスイッチユニットを接続する。そして、2個のスイッチユニットを用いて、第1の電極21及び第2の電極23の電圧を制御するようにしている。

【0065】

図14は、第3の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図である。

【0066】

電圧生成回路13の出力は、スイッチユニット15A及び15Bに接続されている。スイッチユニット15Aの出力は、ローパスフィルタ(LPF)31Aを介して、静電型アクチュエータ16の第2の電極23に接続されている。スイッチユニット15Bの出力は、ローパスフィルタ(LPF)31Bを介して、静電型アクチュエータ16の第1の電極21に接続されている。スイッチユニット15A及び15Bの各々の構成は、図5に示したスイッチユニット15と同じである。

【0067】

次に、このように構成された静電型アクチュエータ装置10の動作について説明する。静電型アクチュエータ16の第2の電極23に駆動電圧Vact1及び電圧Vact2を印加する場合、スイッチユニット15Aが第1の実施形態で説明した動作を実行する。この時、スイッチユニット15Bは、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。具体的には、スイッチSW1及びSW2をオフし、かつ、ノードN1及びN2をそれぞれ放電回路D1及びD2によって放電することで、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。

【0068】

一方、静電型アクチュエータ16の第1の電極21に駆動電圧Vact1及び電圧Vact2を印加する場合、スイッチユニット15Bが第1の実施形態で説明した動作を実行する。この時、スイッチユニット15Aは、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。

【0069】

従って第3の実施形態では、静電型アクチュエータ16をアップ状態からダウン状態に遷移する動作を実現しつつ、第1の電極21及び第2の電極23間の電界の向きを反転させることができる。例えば、一方向のみの電界を印加し続けると、静電型アクチュエータ16の絶縁膜22に電荷が蓄えられ、チャージングの問題が発生する。しかし、第3の実施形態では、例えば所定時間ごとに第1の電極21及び第2の電極23間の電界の向きを変えることで、絶縁膜22に蓄えられた電荷を抜くことができる。これにより、チャージングを抑制することができる。その他の効果は、第1の実施形態と同じである。

【0070】

また、第3の実施形態を第2の実施形態に適用することも可能である。

【0071】

[第4の実施形態]

第4の実施形態は、図2のキャパシタCbに変えて、ノードN1及びノードN2間の電位差に依存して容量値が変化する容量素子を用いるようにしている。具体的には、ノードN1及びノードN2間の電位差が小さくなると、容量値が減少する特性を有する容量素子を用いることができる。このような特性を有する容量素子としては、(1)正のしきい値を有するNMOSFETを用いたゲートキャパシタ、(2)MOSキャパシタなどが挙げられる。

【0072】

(ゲートキャパシタ)

図15は、第4の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図である。図2のキャパシタCbがゲートキャパシタに入れ替わった以外は、第1の実施形態の静電型アクチュエータ装置10と同じである。

【0073】

ゲートキャパシタCbは、正のしきい値電圧を有するNMOSFETのドレインとソースとを接続して構成される。ゲートキャパシタCbのゲートは、ノードN1に接続され、ゲートキャパシタCbのドレイン及びソースは、ノードN2に接続されている。

【0074】

図16は、ゲートキャパシタCbの特性を示すグラフである。図16において、横軸はゲート電圧Vg[V]、縦軸は容量値Cb[fF]である。図16には、しきい値電圧の異なる2種類のゲートキャパシタの特性を示している。

【0075】

図16に示す通り、ゲートキャパシタCbは、ゲート電圧がフラットバンド電圧としきい値電圧との間で、その容量値が小さくなる。よって、ゲートキャパシタCbのゲート電圧(すなわち、ノードN1の電圧)がしきい値電圧より小さくなると、ゲートキャパシタCbの容量値が小さくなる。この結果、ノードN1の電圧、すなわち静電型アクチュエータの駆動電圧Vactを大きくすることができる。

【0076】

従って第4の実施形態によれば、電圧生成回路13の電圧Vppを低くすることができるため、電圧生成回路13のサイズを小さくできる。また、静電型アクチュエータ装置10の消費電力を低減することができる。

【0077】

(MOSキャパシタ)

キャパシタCbとしてMOSキャパシタを用いることも可能である。図17は、MOSキャパシタCbの構成を示す断面図である。

【0078】

P型半導体基板(図示せず)内には、N型ウェル(N−well)40が形成されている。N型ウェル40内には、互いに離間して設けられた不純物領域41及び42が設けられている。不純物領域41及び42は、N型ウェル40と同じ導電型であり、高濃度のN+型不純物をN型ウェル40内に導入して形成される。不純物領域41及び42間かつN型ウェル40上には、ゲート絶縁膜43が設けられ、ゲート絶縁膜43上にはゲート電極44が設けられている。ゲート電極44は、例えば、N型不純物が導入された多結晶シリコンから構成される。

【0079】

ゲート電極44に接続された端子T1は、ノードN1に接続され、不純物領域41及び42に接続された端子T2は、ノードN2に接続される。

【0080】

MOSキャパシタCbは、N型ウェル40の不純物濃度を制御することで、その容量値が変化する。図18は、MOSキャパシタCbの特性を示すグラフである。図18において、横軸はゲート電圧Vg[V]、縦軸は容量値Cb[fF]である。

【0081】

図18に示す通り、不純物のインプラ条件を変えることで、MOSキャパシタCbの容量値を変化させることができる。具体的には、不純物濃度を低くするに従って、MOSキャパシタCbの容量値の変動量を大きくすることができる。このMOSキャパシタCbを用いた場合でも、ゲートキャパシタと同じ効果を得ることができる。

【0082】

本発明は、上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲内で、構成要素を変形して具体化することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、1つの実施形態に開示される複数の構成要素の適宜な組み合わせ、若しくは異なる実施形態に開示される構成要素の適宜な組み合わせにより種々の発明を構成することができる。例えば、実施形態に開示される全構成要素から幾つかの構成要素が削除されても、発明が解決しようとする課題が解決でき、発明の効果が得られる場合には、これらの構成要素が削除された実施形態が発明として抽出されうる。

【符号の説明】

【0083】

Cb…キャパシタ、SW1,SW2…スイッチ、D1,D2…放電回路、10…静電型アクチュエータ装置、11…駆動回路、12…発振器、13…電圧生成回路、14…リミッタ、15…スイッチユニット、16…静電型アクチュエータ、16C…可変容量、17…制御回路、20…基板、21,23…電極、22…絶縁膜、24…弾性体、25…固定部、26…可変容量デバイス、30…ローカルブースタ、31…ローパスフィルタ、32…昇圧回路、32A…キャパシタ、32B…ダイオード、33…リミッタ、34,35…放電回路、40…N型ウェル、41,42…不純物領域、43…ゲート絶縁膜、44…ゲート電極、ND…NAND回路、INV1,INV2…インバータ回路。

【技術分野】

【0001】

本発明は、静電型アクチュエータ装置に関する。

【背景技術】

【0002】

MEMS(Micro-Electro-Mechanical Systems)技術を用いた高周波(RF:Radio Frequency)−MEMS可変容量やRF−MEMSスイッチが開発されており、これらMEMS可変容量やMEMSスイッチには静電型アクチュエータが使用されている(例えば、特許文献1を参照)。

【0003】

静電型アクチュエータの駆動電圧は、半導体装置内に設けられた昇圧回路により生成される(例えば、特許文献2及び3を参照)。静電型アクチュエータを駆動させるには、例えば10V以上の高い電圧が必要である。この高電圧を昇圧回路で生成するには時間がかかり、この結果、MEMSのスイッチング速度が遅くなってしまう。また、高電圧を生成する昇圧回路は回路面積が大きくなり、製造コストが高くなってしまう。

【0004】

また、高い電圧で静電型アクチュエータを駆動した場合、チャージングによるスティクションが増加し、不良が起きやすくなる。したがって、短時間で静電型アクチュエータを駆動するために必要な高電圧を生成でき、チャージングを起きにくくすることが望まれている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−123110号公報

【特許文献2】特開平7−160215号公報

【特許文献3】特開2004−336904号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は、短時間で静電型アクチュエータの駆動に必要な高電圧を生成することが可能な静電型アクチュエータ装置を提供する。

【課題を解決するための手段】

【0007】

本発明の一態様に係る静電型アクチュエータ装置は、第1の電圧を生成する第1の電圧生成回路と、前記第1の電圧生成回路と第1のノードとの間に接続された第1のスイッチと、第2の電圧を生成する第2の電圧生成回路と、前記第2の電圧生成回路と第2のノードとの間に接続された第2のスイッチと、前記第1のノードと前記第2のノードとの間に接続されたキャパシタと、前記第1のノードに駆動電極が接続された静電型アクチュエータとを具備し、前記静電型アクチュエータの駆動時に、前記第1のスイッチがオン、前記第1のスイッチがオフ、前記第2のスイッチがオンの順に動作する。

【発明の効果】

【0008】

本発明によれば、短時間で静電型アクチュエータの駆動に必要な高電圧を生成することが可能な静電型アクチュエータ装置を提供することができる。

【図面の簡単な説明】

【0009】

【図1】第1の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図。

【図2】1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図。

【図3】可変容量デバイス26の構成を示す断面図。

【図4】複数個の静電型アクチュエータ16を示す概略図。

【図5】スイッチユニット15の具体的な構成例を示す回路図。

【図6】静電型アクチュエータ装置10の他の構成を示す回路図。

【図7】ローパスフィルタ31の構成例を示す回路図。

【図8】静電型アクチュエータ16のアップ状態とダウン状態とを示す概略図。

【図9】静電型アクチュエータ16に印加される電圧を説明するタイミングチャート。

【図10】図5に示したローカルブースタ30−1の構成を示す回路ブロック図。

【図11】昇圧回路32の構成例を示す回路図。

【図12】第2の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図

【図13】1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図。

【図14】第3の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図。

【図15】第4の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図。

【図16】ゲートキャパシタCbの特性を示すグラフ。

【図17】MOSキャパシタCbの構成を示す断面図。

【図18】MOSキャパシタCbの特性を示すグラフ。

【発明を実施するための形態】

【0010】

以下、本発明の実施形態について図面を参照して説明する。なお、以下の説明において、同一の機能及び構成を有する要素については、同一符号を付し、重複説明は必要な場合にのみ行う。

【0011】

[第1の実施形態]

図1は、本発明の第1の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図である。静電型アクチュエータ装置10は、n(nは1以上の整数)個の静電型アクチュエータ16と、静電型アクチュエータ16を駆動する駆動回路11と、駆動回路11の動作を制御する制御回路17とを備えている。駆動回路11は、発振器(OSC)12、電圧生成回路13、リミッタ(LIM)14、及びn個(静電型アクチュエータ16と同じ数)のスイッチユニット15を備えている。駆動回路11と静電型アクチュエータ16とは、例えば同一基板上に形成される。

【0012】

電圧生成回路13は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vppを生成する。昇圧回路は、例えばチャージポンプにより構成される。このチャージポンプは、発振器12から供給されるクロックCLKを用いてポンプ動作を実行する。

【0013】

電圧生成回路13には、リミッタ14が接続されている。リミッタ14は、電圧生成回路13の出力が所定電圧より高くなるのを防ぐ。これにより、電圧生成回路13は、安定した電圧を出力することができる。

【0014】

図2は、1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図である。

【0015】

静電型アクチュエータ16は、例えば絶縁性の基板20上に設けられた第1の電極21と、第1の電極21上に設けられた絶縁膜22と、絶縁膜22の上方に設けられかつ上下に移動可能である第2の電極23とを備えている。第2の電極23は、弾性体(例えばバネ)24を介して固定部25に接続されている。絶縁性の基板20は、ガラス基板や、シリコン基板上に形成された絶縁層等からなる。なお、絶縁膜22は、第1の電極21と第2の電極23とが電気的に接触するのを防ぐ役割を果たせばよく、従って、絶縁膜22は、第1の電極21と第2の電極23との間に設けられていればよい。例えば、絶縁膜22は、第2の電極23の下のみに設けられていてもよいし、第1の電極21上及び第2の電極23の下の両方に設けられていてもよい。

【0016】

第1の電極21は接地されており、すなわち、第1の電極21には、接地電圧Vssが供給される。第2の電極23は、ノードN1を介してスイッチユニット15に接続されている。よって、第2の電極23は、これに印加される電圧に応じて上下に移動することが可能となる。

【0017】

静電型アクチュエータは、例えば図3のような可変容量デバイス26の一部を構成していてもよい。第1の静電型アクチュエータ16Aは、第1の電極21A、絶縁膜22A、第2の電極23A、バネ24A、及び固定部25Aから構成されている。第2の静電型アクチュエータ16Bは、第1の電極21B、絶縁膜22B、第2の電極23B、バネ24B、及び固定部25Bから構成されている。可変容量16Cは、基板20上に設けられた第1の電極21Cと、第1の電極21C上に設けられた絶縁膜22Cと、絶縁膜22Cの上方に設けられかつ上下に移動可能である第2の電極23Cとを備えている。

【0018】

第2の電極23Cは、その両側がそれぞれ絶縁層を介して第2の電極23A及び23Bに固定されており、第2の電極23A及び第2の電極23Bの動きに合わせて上下に移動することができる。よって、第1の電極21C、絶縁膜22C、及び第2の電極23Cは、可変容量として機能する。なお、静電型アクチュエータは、可変容量デバイス以外のデバイスにも適用することが可能であり、例えばスイッチにも適用できる。

【0019】

スイッチユニット15は、スイッチSW1及びSW2と、キャパシタCbとを備えている。スイッチSW1の一端は、電圧生成回路13の出力に接続され、スイッチSW1の他端は、ノードN1を介してキャパシタCbの第1の電極に接続されている。スイッチSW2の一端は、電圧生成回路13の出力に接続され、スイッチSW2の他端は、ノードN2を介してキャパシタCbの第2の電極に接続されている。スイッチユニット15は、スイッチSW1及びSW2の動作を制御することで、静電型アクチュエータ16の第2の電極23に駆動電圧を供給することができる。

【0020】

静電型アクチュエータ16の数は、複数であっても勿論構わない。図4は、複数個の静電型アクチュエータ16を示す概略図である。この場合、静電型アクチュエータ装置10は、複数個の静電型アクチュエータ16−1〜16−nに対応する複数個のスイッチユニット15−1〜15−nを備えている。1個のスイッチユニット15は、これに接続される1個の静電型アクチュエータ16にのみ駆動電圧を供給する役割をもつ。電圧生成回路13は、複数個の静電型アクチュエータ16−1〜16−nに対して1個のみ設けられる。なお、以下の説明では、1個の静電型アクチュエータ16の構成及び動作について説明するが、他の静電型アクチュエータの構成及び動作も以下の説明と同じである。

【0021】

図5は、スイッチユニット15の具体的な構成例を示す回路図である。スイッチSW1及びSW2としては、高耐圧用のMOSFET(Metal Semiconductor Field Effect Transistor)が用いられ、例えばNチャネルMOSFET(NMOSFET)が用いられる。

【0022】

NMOSFET(SW1)のドレインは、電圧生成回路13の出力に接続され、NMOSFET(SW1)のソースは、ノードN1を介してキャパシタCbの第1の電極に接続されている。NMOSFET(SW1)のゲート電圧は、ローカルブースタ30−1によって制御される。

【0023】

NMOSFET(SW2)のドレインは、電圧生成回路13の出力に接続され、NMOSFET(SW2)のソースは、ノードN2を介してキャパシタCbの第2の電極に接続されている。NMOSFET(SW2)のゲート電圧は、ローカルブースタ30−2によって制御される。

【0024】

ノードN1は、第1の放電回路D1に接続されている。第1の放電回路D1は、制御回路17からの制御信号CS1に基づいてノードN1を放電する。ノードN2は、第2の放電回路D2に接続されている。第2の放電回路D2は、制御回路17からの制御信号CS2に基づいてノードN2を放電する。第1の放電回路D1及び第2の放電回路D2の各々は、例えばNチャネルMOSFETから構成される。

【0025】

ノードN1に接続されたキャパシタCparaは配線の寄生容量を示しており、Cactは静電型アクチュエータ16の容量である。CparaとCactとを合わせてCLと表記する。

【0026】

図6に示すように、スイッチユニット15と静電型アクチュエータ16との間にローパスフィルタ(LPF)31を挿入してもよい。図7は、ローパスフィルタ31の構成例を示す回路図である。ローパスフィルタ31は、2個の抵抗31−1及び31−2と、キャパシタ31−3から構成されている。ローパスフィルタ31を用いることで、電圧生成回路13からのノイズやリップル(ripple)を低減できるため、静電型アクチュエータ16の動作が安定する。

【0027】

本実施形態では、スイッチユニット15と静電型アクチュエータ16との間、具体的には、キャパシタCbの第1の電極と静電型アクチュエータ16との間には、抵抗素子以外のものは接続されていない。これは、スイッチユニット15からの出力電圧をそのまま静電型アクチュエータ16に伝えるために必要な条件である。

【0028】

(動作)

次に、このように構成された静電型アクチュエータ装置10の動作について説明する。静電型アクチュエータ16は、第2の電極23に印加される電圧に応じて、アップ状態とダウン状態とを取り得る。スイッチユニット15からの出力が静電型アクチュエータ16の駆動電圧以上になった場合に、静電型アクチュエータ16は、アップ状態からダウン状態に遷移する。

【0029】

図8は、静電型アクチュエータ16のアップ状態とダウン状態とを示す概略図である。アップ状態とは、静電型アクチュエータ16が駆動していない状態であり、アップ状態時の第2の電極23の電圧は、接地電圧Vss以上かつプルイン電圧未満である。プルイン電圧とは、第2の電極23が下に駆動するために要する電圧であり、第2の電極23が第1の電極21に引き付けられる静電引力がバネ24の復元力よりも大きくなる電圧である。

【0030】

静電型アクチュエータ16を駆動する、すなわちアップ状態からダウン状態にするには、次の順番でスイッチSW1及びSW2を動作させる。

【0031】

(1)SW1:オン

(2)SW1:オフ

(3)SW2:オン

図9は、静電型アクチュエータ16に印加される電圧を説明するタイミングチャートである。図9には、図5のノードN1及びN2の電圧を示している。電圧生成回路13の出力電圧をVpp、静電型アクチュエータ16のアップ状態及びダウン状態における容量値をそれぞれCact[up]及びCact[down]とする。

【0032】

スイッチSW1をオンすると、静電型アクチュエータ16には電圧Vppが供給される。この電圧Vppは、静電型アクチュエータ16のホールド電圧以上、静電型アクチュエータ16のプルイン電圧未満に設定される。したがって、この時点では、静電型アクチュエータ16はアップ状態のままである。ホールド電圧とは、第2の電極23が下に駆動して絶縁膜22と接触した後、この状態を保持するのに要する電圧である。ホールド電圧は、プルイン電圧未満である。

【0033】

ついで、スイッチSW1をオフした後に、スイッチSW2をオンする。ノードN2に電圧Vppが供給されると、キャパシタCbの容量結合によりノードN1が電圧Vpp及びプルイン電圧の各々より高い駆動電圧Vact1まで上昇する。駆動電圧Vact1は、次式で表される。

【0034】

Vact1={(2Cb+Cpara+Cact[up])/(Cb+Cpara+Cact[up])}・Vpp

Vpp=22V、Cb=CL(=Cpara+Cact)とすると、Vact1=33Vである。この電圧Vact1により静電型アクチュエータ16を駆動させ、静電型アクチュエータ16をダウン状態にできる。この方式によれば、電圧Vact1よりも低い電圧Vppを生成する電圧生成回路13を用いて静電型アクチュエータ16を駆動できる。このため、直接駆動電圧Vact1を生成する場合に比べて、電圧生成回路13の面積を縮小できる。また、電圧生成回路13は、駆動電圧Vact1より低い電圧Vppを生成すればよいため、昇圧時間も短縮できる。

【0035】

さらに、本方式では、静電型アクチュエータ16のチャージングも抑制できる。チャージングとは、静電型アクチュエータ16が駆動を繰り返すことで、絶縁膜22に電荷が蓄えられ、この電荷に起因して第2の電極23が絶縁膜22から離れにくくなる現象である。このチャージングは、駆動電圧が高くなるほどその影響が大きくなる。以下に、チャージングを抑制できる理由を説明する。

【0036】

静電型アクチュエータ16に駆動電圧Vact1が供給されるとアップ状態からダウン状態に遷移するが、その前後でノードN1の電荷量は保持される。一方、静電型アクチュエータ16の容量値はCact[up]からCact[down]に増加する。この結果、ノードN1の電圧は、Vact1からVact2に減少する。電圧Vact2は、静電型アクチュエータ16のホールド電圧以上、電圧Vact1未満に設定される。電圧Vact2は、次式で表される。

【0037】

Vact2={(Cb+Cpara+Cact[up])/(Cb+Cpara+Cact[down])}・Vact1

これにより、静電型アクチュエータ16の絶縁膜22に印加される電界が緩和され、チャージングが抑制される。静電型アクチュエータ16をアップ状態に戻す場合には、第1の放電回路D1及び第2の放電回路D2によりノードN1及びノードN2をそれぞれ放電する。

【0038】

ここで、図9の動作を実現するためには、スイッチユニット15の出力電圧(駆動電圧)を、この出力電圧がドロップすることなく、静電型アクチュエータ16に直接印加することが必要である。このため、スイッチユニット15と静電型アクチュエータ16との間には、スイッチユニット15の出力電圧を変化させる素子(例えば、スイッチや電源)が挿入されていない。抵抗素子を含むローパスフィルタ31は、電圧のノイズやリップルを低減する回路であり、スイッチユニット15と静電型アクチュエータ16との間にローパスフィルタ31が接続されている場合でも、スイッチユニット15の出力電圧を静電型アクチュエータ16に直接印加することが可能である。換言すると、スイッチユニット15と静電型アクチュエータ16との間には、抵抗素子以外の電圧を変化させる素子が挿入されていない。

【0039】

なお、スイッチSW2がオンとなりノードN1が駆動電圧Vact1に上昇したときは、スイッチSW1を構成するNMOSFETのゲート−ソース間に大きな電位差が印加される。この動作が何度も繰り返されると、NMOSFET(SW1)のゲート絶縁膜が劣化する。これを防ぐため、スイッチSW2をオンさせるときはNMOSFET(SW1)のゲート電圧を0Vとせず、0より大きくかつ電圧Vppより低い中間電圧に設定する。この動作を実現するためのローカルブースタ30−1の構成例について説明する。図10は、図5に示したローカルブースタ30−1の構成を示す回路ブロック図である。ローカルブースタ30−2の構成も、図10と同じである。

【0040】

ローカルブースタ30−1は、昇圧回路32、リミッタ(LIM)33、第1の放電回路34、及び第2の放電回路35を備えている。昇圧回路32は、電源電圧Vddを用いて、スイッチSW1を構成するNMOSFETをオンさせるゲート電圧を生成する。昇圧回路32の出力は、ノードN3を介してスイッチSW1に接続されている。昇圧回路32は、例えばチャージポンプにより構成される。このチャージポンプは、発振器12から供給されるクロックCLKを用いてポンプ動作を実行する。

【0041】

昇圧回路32には、リミッタ33が接続されている。リミッタ33は、昇圧回路32の出力が所定電圧より高くなるのを防ぐ。これにより、昇圧回路32は、安定した電圧を出力することができる。

【0042】

ノードN3には、第1の放電回路34が接続されている。第1の放電回路34は、NMOSFETから構成される。NMOSFET34のドレインは、ノードN3に接続され、NMOSFET34のソースは接地され、NMOSFET34のゲートには、制御回路17から制御信号CS3が供給されている。第1の放電回路34は、ノードN3をほぼ0Vまで放電する。

【0043】

ノードN3には、第2の放電回路35が接続されている。第2の放電回路35は、複数のダイオード35Aが直列接続(縦続接続)されたダイオード群と、スイッチ素子としてのNMOSFET35Bとから構成される。各ダイオード35Aは、例えば、NMOSFETがダイオード接続されて構成される。1段目のダイオード35Aのアノードは、ノードN3に接続されている。

【0044】

NMOSFET35Bのドレインは、最終段のダイオード35Aのカソードに接続され、NMOSFET35Bのソースは接地され、NMOSFET35Bのゲートには、制御回路17から制御信号CS4が供給されている。第2の放電回路35は、ノードN3を複数のダイオード35Aの電圧降下分の電圧付近まで放電する。よって、ダイオード35Aの数を最適に設定することで、ノードN3の電圧を0Vより高い所望の電圧まで放電することが可能となる。

【0045】

図11は、昇圧回路32の構成例を示す回路図である。NAND回路NDの第1の入力端子には、発振器12からクロックCLKが供給され、NAND回路NDの第2の入力端子には、制御回路17からイネーブル信号ENが供給されている。NAND回路NDの出力は、インバータ回路INV1の入力に接続されている。インバータ回路INV1の出力は、インバータ回路INV2の入力に接続されている。

【0046】

インバータ回路INV1は、イネーブル信号ENがハイレベルの間、クロックCLKを出力する。インバータ回路INV2は、イネーブル信号ENがハイレベルの間、クロックCLKを反転したクロックbCLKを出力する。

【0047】

キャパシタ32Aの第1の電極は、ダイオード32Bのアノードに接続されている。ダイオード32Bのカソードは、次段のダイオードのアノードに接続されている。このような関係を維持しつつ、1個のキャパシタ32Aと1個のダイオード32Bとからなるユニットが、ダイオード32Bが直列接続されるようにして、複数個接続されている。

【0048】

ダイオード32Bは、例えば、I(intrinsic)タイプのNMOSFETがダイオード接続されて構成されている。IタイプNMOSFETは、そのしきい値電圧がほぼ0Vであるため、ダイオード32Bの電圧降下もほぼ0Vに抑えることができる。

【0049】

1段目のダイオード32Bのアノードには、電圧生成回路13から電圧Vppが供給されている。最終段のダイオード32Bのカソードは、ノードN3に接続されている。複数のキャパシタ32Aには、クロックCLK及びbCLKが交互に供給されている。これにより、昇圧回路32は、キャパシタ32Aに蓄えられた電荷を次段のキャパシタに転送することで、電圧Vppより高い電圧を生成することができる。

【0050】

このように構成されたローカルブースタ30−1の動作について説明する。スイッチSW1をオンさせるときは、昇圧回路32によってスイッチSW1にオン電圧を供給する。ついで、スイッチSW1をオフさせるときは、ローカルブースタ30−1の第1の放電回路34によりノードN3を放電する。これにより、スイッチSW1のNMOSFETのゲート電圧はほぼ0Vになり、スイッチSW1はオフする。

【0051】

ついで、スイッチSW2をオンさせるときは、ローカルブースタ30−1の第2の放電回路35のNMOSFET35Bをオンさせる。この時、ローカルブースタ30−1の第1の放電回路34は、オフである。これにより、ノードN3は、接地電圧Vssから複数のダイオード35Aの電圧降下分だけ高い電圧、例えば10V程度に設定される。例えばVact1=33Vとすると、スイッチSW1のNMOSFETのゲート−ソース間の電位差は23V程度となり、ゲート電圧を0Vにした場合より10V程度低い電位差に設定される。この結果、スイッチSW1のゲート絶縁膜が劣化するのを抑制することができる。

【0052】

(効果)

以上詳述したように第1の実施形態では、電圧Vppを生成する電圧生成回路13と静電型アクチュエータ16との間にスイッチユニット15を接続し、このスイッチユニット15が、電圧Vppより高い、静電型アクチュエータ16の駆動電圧Vact1を生成するようにしている。スイッチユニット15は、キャパシタCbと、電圧生成回路13とキャパシタCbの第1の電極との間に接続されたスイッチSW1と、電圧生成回路13とキャパシタCbの第2の電極との間に接続されたスイッチSW2とを備えている。そして、静電型アクチュエータ16の駆動時に、スイッチSW1がオン、スイッチSW1がオフ、スイッチSW2がオンの順に動作するようにしている。

【0053】

従って第1の実施形態によれば、スイッチユニット15を用いて、電圧生成回路13が生成する電圧Vppより高い駆動電圧Vact1を静電型アクチュエータ16に供給することができる。これにより、電圧生成回路13の面積を縮小することが可能となり、製造コストの低減が可能である。

【0054】

また、非常に短い時間で駆動電圧Vact1を生成することができる。これにより、静電型アクチュエータ16のスイッチング速度を速くすることが可能となる。

【0055】

また、静電型アクチュエータ16を駆動させる際、静電型アクチュエータ16に駆動電圧Vact1を印加した後、静電型アクチュエータ16をダウン状態に維持しつつ、Vact1より低い電圧Vact2に自動的に低くすることが可能である。これにより、静電型アクチュエータ16のチャージングを抑制することができ、ひいてはスティクション不良を低減することができる。

【0056】

また、スイッチSW1がオフ、及びスイッチSW2がオン時に、ローカルブースタ30−1を用いて、スイッチSW1のNMOSFETのゲート−ソース間の電位差を小さくするようにしている。これにより、スイッチSW1のNMOSFETのゲート絶縁膜が劣化するのを防ぐことができる。

【0057】

[第2の実施形態]

第1の実施形態では、スイッチSW1及びSW2に供給される電圧は共に、電圧生成回路13が生成した電圧Vppであるが、これに限定されるものではなく、スイッチSW1に供給される電圧とスイッチSW2に供給される電圧とが異なっていてもよい。第2の実施形態は、異なる電圧Vpp1及びVpp2をそれぞれ生成する第1の電圧生成回路13−1及び第2の電圧生成回路13−2を駆動回路11が備え、第1の電圧生成回路13−1は、スイッチSW1に電圧Vpp1を供給し、第2の電圧生成回路13−2は、スイッチSW2に電圧Vpp2を供給するようにしている。

【0058】

図12は、本発明の第2の実施形態に係る静電型アクチュエータ装置10の構成を示すブロック図である。駆動回路11は、第1の電圧生成回路13−1及び第2の電圧生成回路13−2を備えている。第1の電圧生成回路13−1にはリミッタ14−1が接続され、第2の電圧生成回路13−2にはリミッタ14−2が接続されている。

【0059】

第1の電圧生成回路13−1は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vpp1を生成する。第2の電圧生成回路13−2は、例えば昇圧回路から構成され、電源電圧Vddを昇圧して、電源電圧Vddより高い電圧Vpp2を生成する。

【0060】

図13は、1個のスイッチユニット15と1個の静電型アクチュエータ16との構成を示す概略図である。第1の電圧生成回路13−1の電圧Vpp1は、スイッチSW1の一端に供給される。第2の電圧生成回路13−2の電圧Vpp2は、スイッチSW2の一端に供給される。その他の構成は、図2と同じである。

【0061】

電圧Vpp1は、静電型アクチュエータ16のホールド電圧以上、静電型アクチュエータ16のプルイン電圧未満に設定される。駆動電圧Vact1は、次式で表される。

【0062】

Vact1=Vpp1+{Cb/(Cb+Cpara+Cact[up])}・Vpp2

電圧Vact2の式は、第1の実施形態と同じである。電圧Vpp2は、駆動電圧Vact1が静電型アクチュエータ16のプルイン電圧以上になるように設定される。具体的には、電圧Vpp2は、以下の式で表される。Vpiは、静電型アクチュエータ16のプルイン電圧である。

【0063】

Vpp2≧{(Cb+Cpara+Cact[up])/Cb}・(Vpi−Vpp1)

このように、前述した電圧条件を満たしつつ、スイッチSW1及びSW2に異なる電圧を印加した場合でも、第1の実施形態と同じ動作を実現できる。よって、第2の実施形態の静電型アクチュエータ装置10は、第1の実施形態と同じ効果を得ることができる。

【0064】

[第3の実施形態]

第3の実施形態は、静電型アクチュエータ16の第1の電極21及び第2の電極23のそれぞれにスイッチユニットを接続する。そして、2個のスイッチユニットを用いて、第1の電極21及び第2の電極23の電圧を制御するようにしている。

【0065】

図14は、第3の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図である。

【0066】

電圧生成回路13の出力は、スイッチユニット15A及び15Bに接続されている。スイッチユニット15Aの出力は、ローパスフィルタ(LPF)31Aを介して、静電型アクチュエータ16の第2の電極23に接続されている。スイッチユニット15Bの出力は、ローパスフィルタ(LPF)31Bを介して、静電型アクチュエータ16の第1の電極21に接続されている。スイッチユニット15A及び15Bの各々の構成は、図5に示したスイッチユニット15と同じである。

【0067】

次に、このように構成された静電型アクチュエータ装置10の動作について説明する。静電型アクチュエータ16の第2の電極23に駆動電圧Vact1及び電圧Vact2を印加する場合、スイッチユニット15Aが第1の実施形態で説明した動作を実行する。この時、スイッチユニット15Bは、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。具体的には、スイッチSW1及びSW2をオフし、かつ、ノードN1及びN2をそれぞれ放電回路D1及びD2によって放電することで、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。

【0068】

一方、静電型アクチュエータ16の第1の電極21に駆動電圧Vact1及び電圧Vact2を印加する場合、スイッチユニット15Bが第1の実施形態で説明した動作を実行する。この時、スイッチユニット15Aは、静電型アクチュエータ16の第1の電極21をほぼ0Vに設定する。

【0069】

従って第3の実施形態では、静電型アクチュエータ16をアップ状態からダウン状態に遷移する動作を実現しつつ、第1の電極21及び第2の電極23間の電界の向きを反転させることができる。例えば、一方向のみの電界を印加し続けると、静電型アクチュエータ16の絶縁膜22に電荷が蓄えられ、チャージングの問題が発生する。しかし、第3の実施形態では、例えば所定時間ごとに第1の電極21及び第2の電極23間の電界の向きを変えることで、絶縁膜22に蓄えられた電荷を抜くことができる。これにより、チャージングを抑制することができる。その他の効果は、第1の実施形態と同じである。

【0070】

また、第3の実施形態を第2の実施形態に適用することも可能である。

【0071】

[第4の実施形態]

第4の実施形態は、図2のキャパシタCbに変えて、ノードN1及びノードN2間の電位差に依存して容量値が変化する容量素子を用いるようにしている。具体的には、ノードN1及びノードN2間の電位差が小さくなると、容量値が減少する特性を有する容量素子を用いることができる。このような特性を有する容量素子としては、(1)正のしきい値を有するNMOSFETを用いたゲートキャパシタ、(2)MOSキャパシタなどが挙げられる。

【0072】

(ゲートキャパシタ)

図15は、第4の実施形態に係る静電型アクチュエータ装置10の主要部を示すブロック図である。図2のキャパシタCbがゲートキャパシタに入れ替わった以外は、第1の実施形態の静電型アクチュエータ装置10と同じである。

【0073】

ゲートキャパシタCbは、正のしきい値電圧を有するNMOSFETのドレインとソースとを接続して構成される。ゲートキャパシタCbのゲートは、ノードN1に接続され、ゲートキャパシタCbのドレイン及びソースは、ノードN2に接続されている。

【0074】

図16は、ゲートキャパシタCbの特性を示すグラフである。図16において、横軸はゲート電圧Vg[V]、縦軸は容量値Cb[fF]である。図16には、しきい値電圧の異なる2種類のゲートキャパシタの特性を示している。

【0075】

図16に示す通り、ゲートキャパシタCbは、ゲート電圧がフラットバンド電圧としきい値電圧との間で、その容量値が小さくなる。よって、ゲートキャパシタCbのゲート電圧(すなわち、ノードN1の電圧)がしきい値電圧より小さくなると、ゲートキャパシタCbの容量値が小さくなる。この結果、ノードN1の電圧、すなわち静電型アクチュエータの駆動電圧Vactを大きくすることができる。

【0076】

従って第4の実施形態によれば、電圧生成回路13の電圧Vppを低くすることができるため、電圧生成回路13のサイズを小さくできる。また、静電型アクチュエータ装置10の消費電力を低減することができる。

【0077】

(MOSキャパシタ)

キャパシタCbとしてMOSキャパシタを用いることも可能である。図17は、MOSキャパシタCbの構成を示す断面図である。

【0078】

P型半導体基板(図示せず)内には、N型ウェル(N−well)40が形成されている。N型ウェル40内には、互いに離間して設けられた不純物領域41及び42が設けられている。不純物領域41及び42は、N型ウェル40と同じ導電型であり、高濃度のN+型不純物をN型ウェル40内に導入して形成される。不純物領域41及び42間かつN型ウェル40上には、ゲート絶縁膜43が設けられ、ゲート絶縁膜43上にはゲート電極44が設けられている。ゲート電極44は、例えば、N型不純物が導入された多結晶シリコンから構成される。

【0079】

ゲート電極44に接続された端子T1は、ノードN1に接続され、不純物領域41及び42に接続された端子T2は、ノードN2に接続される。

【0080】

MOSキャパシタCbは、N型ウェル40の不純物濃度を制御することで、その容量値が変化する。図18は、MOSキャパシタCbの特性を示すグラフである。図18において、横軸はゲート電圧Vg[V]、縦軸は容量値Cb[fF]である。

【0081】

図18に示す通り、不純物のインプラ条件を変えることで、MOSキャパシタCbの容量値を変化させることができる。具体的には、不純物濃度を低くするに従って、MOSキャパシタCbの容量値の変動量を大きくすることができる。このMOSキャパシタCbを用いた場合でも、ゲートキャパシタと同じ効果を得ることができる。

【0082】

本発明は、上記実施形態に限定されるものではなく、その要旨を逸脱しない範囲内で、構成要素を変形して具体化することが可能である。さらに、上記実施形態には種々の段階の発明が含まれており、1つの実施形態に開示される複数の構成要素の適宜な組み合わせ、若しくは異なる実施形態に開示される構成要素の適宜な組み合わせにより種々の発明を構成することができる。例えば、実施形態に開示される全構成要素から幾つかの構成要素が削除されても、発明が解決しようとする課題が解決でき、発明の効果が得られる場合には、これらの構成要素が削除された実施形態が発明として抽出されうる。

【符号の説明】

【0083】

Cb…キャパシタ、SW1,SW2…スイッチ、D1,D2…放電回路、10…静電型アクチュエータ装置、11…駆動回路、12…発振器、13…電圧生成回路、14…リミッタ、15…スイッチユニット、16…静電型アクチュエータ、16C…可変容量、17…制御回路、20…基板、21,23…電極、22…絶縁膜、24…弾性体、25…固定部、26…可変容量デバイス、30…ローカルブースタ、31…ローパスフィルタ、32…昇圧回路、32A…キャパシタ、32B…ダイオード、33…リミッタ、34,35…放電回路、40…N型ウェル、41,42…不純物領域、43…ゲート絶縁膜、44…ゲート電極、ND…NAND回路、INV1,INV2…インバータ回路。

【特許請求の範囲】

【請求項1】

第1の電圧を生成する第1の電圧生成回路と、

前記第1の電圧生成回路と第1のノードとの間に接続された第1のスイッチと、

第2の電圧を生成する第2の電圧生成回路と、

前記第2の電圧生成回路と第2のノードとの間に接続された第2のスイッチと、

前記第1のノードと前記第2のノードとの間に接続されたキャパシタと、

前記第1のノードに駆動電極が接続された静電型アクチュエータと、

を具備し、

前記静電型アクチュエータの駆動時に、前記第1のスイッチがオン、前記第1のスイッチがオフ、前記第2のスイッチがオンの順に動作することを特徴とする静電型アクチュエータ装置。

【請求項2】

前記第1の電圧は、前記静電型アクチュエータの駆動電圧より低いことを特徴とする請求項1に記載の静電型アクチュエータ装置。

【請求項3】

前記第1のスイッチは、第1のMOSFETと、前記第1のMOSFETのゲート電圧を制御する第1のローカルブースタとを含み、

前記第2のスイッチは、第2のMOSFETと、前記第2のMOSFETのゲート電圧を制御する第2のローカルブースタとを含むことを特徴とする請求項1又は2に記載の静電型アクチュエータ装置。

【請求項4】

前記第1のローカルブースタは、前記第1のMOSFETがオフ時に、前記第1のMOSFETのゲート電圧を、接地電圧より高い第3の電圧に設定することを特徴とする請求項3に記載の静電型アクチュエータ装置。

【請求項5】

前記第1の電圧は、前記第2の電圧と同じであることを特徴とする請求項1乃至4のいずれかに記載の静電型アクチュエータ装置。

【請求項1】

第1の電圧を生成する第1の電圧生成回路と、

前記第1の電圧生成回路と第1のノードとの間に接続された第1のスイッチと、

第2の電圧を生成する第2の電圧生成回路と、

前記第2の電圧生成回路と第2のノードとの間に接続された第2のスイッチと、

前記第1のノードと前記第2のノードとの間に接続されたキャパシタと、

前記第1のノードに駆動電極が接続された静電型アクチュエータと、

を具備し、

前記静電型アクチュエータの駆動時に、前記第1のスイッチがオン、前記第1のスイッチがオフ、前記第2のスイッチがオンの順に動作することを特徴とする静電型アクチュエータ装置。

【請求項2】

前記第1の電圧は、前記静電型アクチュエータの駆動電圧より低いことを特徴とする請求項1に記載の静電型アクチュエータ装置。

【請求項3】

前記第1のスイッチは、第1のMOSFETと、前記第1のMOSFETのゲート電圧を制御する第1のローカルブースタとを含み、

前記第2のスイッチは、第2のMOSFETと、前記第2のMOSFETのゲート電圧を制御する第2のローカルブースタとを含むことを特徴とする請求項1又は2に記載の静電型アクチュエータ装置。

【請求項4】

前記第1のローカルブースタは、前記第1のMOSFETがオフ時に、前記第1のMOSFETのゲート電圧を、接地電圧より高い第3の電圧に設定することを特徴とする請求項3に記載の静電型アクチュエータ装置。

【請求項5】

前記第1の電圧は、前記第2の電圧と同じであることを特徴とする請求項1乃至4のいずれかに記載の静電型アクチュエータ装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2011−172325(P2011−172325A)

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願番号】特願2010−31820(P2010−31820)

【出願日】平成22年2月16日(2010.2.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願日】平成22年2月16日(2010.2.16)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]