静電容量検出回路及び電子機器

【課題】静電容量をリセットし再充電してセンスアンプで読み出すための処理時間を短縮する。

【解決手段】静電容量検出回路1は、電圧の印加により静電容量C1〜C4に蓄積された電荷を読み出すセンスアンプ2と、駆動回路8が電圧を印加している間に、センスアンプ2の出力を複数回サンプリングし、デジタル値に変換するAD変換器3と、変換された複数のデジタル値を平均化するデジタル演算回路4とを備える。

【解決手段】静電容量検出回路1は、電圧の印加により静電容量C1〜C4に蓄積された電荷を読み出すセンスアンプ2と、駆動回路8が電圧を印加している間に、センスアンプ2の出力を複数回サンプリングし、デジタル値に変換するAD変換器3と、変換された複数のデジタル値を平均化するデジタル演算回路4とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端がセンスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路、及びこれを備えた電子機器に関する。

【背景技術】

【0002】

マトリックス状に分布した静電容量値を検出する装置、例えば、M本のドライブラインとL本のセンスラインとの間に形成される静電容量行列の静電容量値の分布を検出する容量検出装置が、特許文献1に開示されている。この容量検出装置は、指やペンでタッチパネルに触れると、触れられた静電容量の容量値が小さくなるので、容量値が小さくなった変化を検出して、指やペンのタッチを検出する。

【0003】

(従来の静電容量検出回路91の構成)

図10は、従来の静電容量検出回路91の構成を示す回路図である。静電容量検出回路91は、センスラインSLに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、他端がセンスラインSLに接続された静電容量C1〜C4の容量値を推定するためのデータを取得する。

【0004】

静電容量検出回路91は、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLには、センスライン寄生容量Cpが存在する。センスライン寄生容量Cpには、外部からノイズNZが印加される。静電容量検出回路91には、センスアンプ2が設けられている。センスアンプ2は、電圧Vin1〜Vin4の印加により静電容量C1〜C4に蓄積された電荷を、センスラインSLを通して読み出す。

【0005】

センスアンプ2は、オペアンプ10を有している。オペアンプ10の非反転入力端子はセンスラインSLに接続されており、反転入力端子は基準電圧Vrに接続されている。センスアンプ2には、オペアンプ10の非反転入力端子とオペアンプ10の出力とに接続された積分容量Cf及びスイッチSWRが互いに並列に設けられている。

【0006】

(従来の静電容量検出回路91の動作)

例えば、液晶ディスプレイ上に形成されたタッチパネルの場合、液晶ディスプレイの表面上に検出対象容量が形成されるため、センスラインSLは液晶の画素を駆動する配線との間にセンスライン寄生容量Cpが形成され、液晶の画素を駆動する電圧が該寄生容量に印加されセンスアンプの出力Voutにノイズとして重畳される。

【0007】

今、図10の静電容量検出回路91が、駆動電圧Vin1=Vin2=Vin3=Vin4=0とした状態でリセット用スイッチSWRを閉じて、時刻t0においてスイッチSWRを開いたとする。その後ドライブラインDL1〜DL4が駆動電圧Vin1、Vin2、Vin3、及びVin4で駆動されている時刻tにおけるセンスアンプ2の出力電圧Vout(t)は、以下の式(1)で表わされる。

【0008】

Vout(t)=−(Vin1・C1+Vin2・C2+Vin3・C3+Vin4・C4+(Vn(t)−Vn(t0))・Cp)/Cf+Vr …式(1)

ここで、ノイズNZの時刻tにおける電圧をVn(t)と表わしている。

【0009】

式(1)から判るように、ノイズ電圧の差{Vn(t)−Vn(t0)}とセンスライン寄生容量Cpとの積の絶対値が、{Vin1・C1+Vin2・C2+Vin3・C3+Vin4・C4}の絶対値に比べて十分小さくなければ、出力電圧Vout(t)を用いて静電容量C1、C2、C3、及びC4を推定する場合に誤差が生じる。

【0010】

誤差を小さくするためリセット、駆動電圧Vin1、Vin2、Vin3、及びVin4の印加、及び出力Voutの読み出しという動作を複数回繰り返して行い出力を平均化することが知られている。この場合、出力Voutの読み出しごとに{Vn(t)−Vn(t0)}の値が無相関に分布すれば、平均化によりサンプル個数の平方根に反比例してノイズの値が減少する。

【0011】

また、特許文献1には、検出対象静電容量を駆動電圧で充電して、充電された電荷を積分アンプに積分して放電させるという過程を繰り返すことで積分アンプの出力の信号対ノイズ比が改善することが記載されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2010-250522号公報(2010年11月4日公開)

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、静電容量C1〜C4をリセットし、駆動電圧Vin1〜Vin4により静電容量C1〜C4を再充電して静電容量C1〜C4の電荷をセンスアンプ2で読み出すという処理は、ドライブラインDL1〜DL4、センスラインSLの電圧を変化させるため、この電圧変化が収束するまでにはそれらのラインの持つ時定数で律捉された時間がかかり、容量値の推測に求められる限られた時間内に行える平均化の回数が不足するという課題があった。

【0014】

本発明の目的は、静電容量をリセットし、駆動電圧により再充電してセンスアンプで読み出すための処理時間を短縮することができる静電容量検出回路及び電子機器を提供することにある。

【課題を解決するための手段】

【0015】

本発明に係る静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする。

【0016】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能である。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。

【0017】

本発明に係る他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の出力を平均化するアナログ演算回路とを備えたことを特徴とする。

【0018】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能である。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずにアナログ回路により平均化するため、量子化ノイズの混入を排除することができる。

【0019】

本発明に係るさらに他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする。

【0020】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するので、駆動端子を第1の駆動電圧または電圧の組と、第2の駆動電圧または電圧の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。

【0021】

本発明に係るさらに他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた複数の第1サンプリング値を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた複数の第2サンプリング値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする。

【0022】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するので、駆動端子を第1の駆動電圧または電圧の組と、第2の駆動電圧または電圧の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずにアナログ回路により平均化するため、量子化ノイズの混入を排除することができる。

【0023】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする。

【0024】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理を短縮することができる。

【0025】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通してそれぞれ読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の差動出力を平均化するアナログ演算回路とを備えたことを特徴とする。

【0026】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずに平均化するため、量子化ノイズの混入を排除することができる。

【0027】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする。

【0028】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するので、駆動端子を第1の駆動電圧対または電圧対の組と、第2の駆動電圧対または電圧対の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。

【0029】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第1差動出力を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第2差動出力を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする。

【0030】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にCpAおよびCpBを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするので、駆動端子を第1の駆動電圧対または電圧対の組と、第2の駆動電圧対または電圧対の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずに平均化するため、量子化ノイズの混入を排除することができる。

【0031】

本発明に係る静電容量検出回路では、前記AD変換器は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングすることが好ましく、前記サンプリング容量回路は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングすることが好ましい。

【0032】

上記構成により、平均化により効果的にノイズを削減することができる。

【0033】

本発明に係る静電容量検出回路では、前記センスアンプは、集積化されており、前記センスラインに接続された入力端子を有することが好ましい。

【0034】

上記構成により、センスアンプが集積化されるので、よりコンパクトな静電容量検出回路を得ることができる。

【0035】

本発明に係る電子機器は、本発明に係る静電容量検出回路を備え、前記センスラインと前記ドライブラインと前記静電容量とは、タッチパネルを構成し、前記タッチパネルに重ねられているか、前記タッチパネルを内蔵した表示パネルをさらに備えたことを特徴とする。

【0036】

この特徴により、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも静電容量検出の処理時間を短縮した電子機器を得ることができる。

【発明の効果】

【0037】

本発明に係る静電容量検出回路は、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換する。このため、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。

【図面の簡単な説明】

【0038】

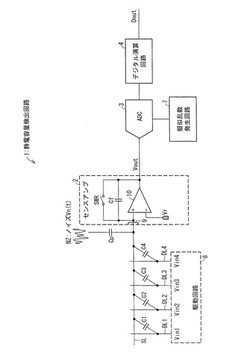

【図1】実施の形態1に係る静電容量検出回路の構成を示す回路図である。

【図2】実施の形態1に係る他の静電容量検出回路の構成を示す回路図である。

【図3】実施の形態2に係る静電容量検出回路の構成を示す回路図である。

【図4】実施の形態2に係る他の静電容量検出回路の構成を示す回路図である。

【図5】実施の形態3に係る静電容量検出回路の構成を示す回路図である。

【図6】実施の形態3に係る他の静電容量検出回路の構成を示す回路図である。

【図7】実施の形態4に係る静電容量検出回路の構成を示す回路図である。

【図8】実施の形態4に係る他の静電容量検出回路の構成を示す回路図である。

【図9】実施の形態5に係る携帯電話機の構成を示すブロック図である。

【図10】従来の静電容量検出回路の構成を示す回路図である。

【発明を実施するための形態】

【0039】

本発明の静電容量検出回路に関する実施の一形態について図1〜図9に基づいて説明すれば以下のとおりである。

【0040】

(実施の形態1)

(静電容量検出回路1の構成(シングルエンド、シングルサンプリング))

図1は、実施の形態1に係る静電容量検出回路1の構成を示す回路図である。静電容量検出回路1は、センスラインSLに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、他端がセンスラインSLに接続された静電容量C1〜C4の容量値を推定するためのデータを取得する。

【0041】

静電容量検出回路1は、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLには、センスライン寄生容量Cpが存在する。センスライン寄生容量Cpには、外部からノイズNZが印加される。静電容量検出回路1には、センスアンプ2が設けられている。センスアンプ2は、電圧Vin1〜Vin4の印加により静電容量C1〜C4に蓄積された電荷を、センスラインSLを通して読み出す。

【0042】

センスアンプ2は、オペアンプ10を有している。オペアンプ10の非反転入力端子はセンスラインSLに接続されており、反転入力端子は基準電圧Vrに接続されている。センスアンプ2には、オペアンプ10の非反転入力端子とオペアンプ10の出力とに接続された積分容量Cf及びスイッチSWRが互いに並列に設けられている。

【0043】

センスアンプ2は、集積化されており、センスラインSLに接続された入力端子9を有している。

【0044】

静電容量検出回路1は、AD変換器3を備えている。AD変換器3は、駆動回路8がドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加している間に、センスアンプ2の出力を複数回繰り返してサンプリングし、サンプリング毎にデジタル値に変換する。AD変換器3には、擬似乱数発生回路7が接続されている。擬似乱数発生回路7は、AD変換器3のサンプリング周期を制御するために、予め定められた範囲内の乱数を生成してAD変換器3に供給する。

【0045】

静電容量検出回路1には、デジタル演算回路4が設けられている。デジタル演算回路4は、AD変換器3により変換された複数のデジタル値を平均化する。

【0046】

(静電容量検出回路1の動作)

静電容量C1、C2、C3、及びC4のセンスラインSLと繋がらない方の端子に、ドライブラインDL1〜DL4を通して電圧Vin1、Vin2、Vin3、及びVin4を印加して、そのときのセンスアンプ2の出力電圧をAD変換器3により複数回繰り返して読み出すことで容量C1、C2、C3、及びC4の値を推定するためのデータを得る。センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。

【0047】

AD変換器3による読み出しの繰り返し回数は、実際には、駆動方式や外来ノイズの状況、必要とされるS/Nにより、数回から1000回以上まで多様な数値を取り得る。指やペンのタッチ位置を検出するために必要とされるS/N比を実現でき、かつ一回のタッチ位置検出に許容される時間内に完了できる適切な繰り返し回数を選ぶ。

【0048】

その後、時刻t0においてスイッチSWRを開き、さらにその後、駆動電圧をVin1=Vd、Vin2=Vin3=Vin4=0にして出力が収束した後の時刻tにおける出力電圧値は、

Vout(t)=−{Vd・C1+(Vn(t)−Vn(t0))・Cp}/Cf+Vr …式(1)、

となり、Vn(t)−Vn(t0)というノイズで決まる誤差を許容すると静電容量C1の値を推定できる。ノイズ電圧Vnのrms(二乗平均平方根、Root Mean Square)値をVn_rmsとすると、Vn(t)−Vn(t0)のrms値は2Vn_rmsである。ここで、ノイズによる誤差を削減するために、駆動電圧をVin1=Vd、Vin2=Vin3=Vin4=0にして、出力が収束した後の出力電圧を時刻t11、t12、…t1nにおいてAD変換器3によりn回繰り返してサンプリングしてデジタル値に変換し、デジタル演算回路4によりそれらのデジタル値の加算平均Vout_aveを求めると、

Vout_ave=−{n・Vd・C1+(Vn(t11)+Vn(t12)+・・・+Vn(t1n)−n・Vn(t0))・Cp}/(n・Cf)+Vr、

となる。この加算平均値に含まれるノイズの項、(Vn(t11)+Vn(t12)+ ・・・+Vn(t1n))/nはサンプル間のノイズ電圧Vn(t11)、Vn(t12)、…Vn(t1n)に相関が無ければ、rms値においてノイズ電圧Vnのrms値の1/sqrt(n)に小さくなるため、Vout(t)では2Vn_rmsであったノイズのrms値が、Vn_aveではサンプリング回数nを大きくすると、Vn_rmsまで削減可能である。

【0049】

一般に寄生容量Cpを介してセンスラインSLに影響するノイズ電圧Vnは、液晶ディスプレイの表示画面に依存してランダムな変化があり、サンプル間の相関は小さいことが期待される。しかしながら、ノイズ電圧が液晶ディスプレイの画面走査の周期で周期的に変動したり、あるいは、タッチパネルを操作する人体を介して混入する外部の周期的変動ノイズの場合には、周期的なサンプリングではサンプル間の相関が大きくなることもあり得る。この様な場合でも、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7によりサンプリングの時刻を非周期的にすることが推奨される。

【0050】

(静電容量検出回路1の他の駆動方法)

静電容量検出回路1の他の駆動方法による容量値の推定方法を以下に説明する。上述した駆動方法と同様に、センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t01においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、Vd、Vd、Vd)を印加した時の出力を時刻t1でサンプリングした値をVout(t1)とすると、

Vout(t1)=−Vd(C1+C2+C3+C4)/Cf−(Vn(t1)−Vn(t01))Cp/Cf+Vr …式(2)、

となる。

【0051】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t02においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、−Vd、Vd、−Vd)を印加した時の出力を時刻t2でサンプリングした値をVout(t2)とすると、

Vout(t2)=−Vd(C1−C2+C3−C4)/Cf−(Vn(t2)−Vn(t02))Cp/Cf+Vr …式(3)、

となる。

【0052】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t03においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、Vd、−Vd、−Vd)を印加した時の出力を時刻t3でサンプリングした値をVout(t3)とすると、

Vout(t3)=−Vd(C1+C2−C3−C4)/Cf−(Vn(t3)−Vn(t03))Cp/Cf+Vr …式(4)、

となる。

【0053】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t04においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、−Vd、−Vd、Vd)を印加した時の出力を時刻t4でサンプリングした値をVout(t4)とすると、

Vout(t4)=−Vd(C1−C2−C3+C4)/Cf−(Vn(t4)−Vn(t04))Cp/Cf+Vr …式(5)、

となる。

【0054】

そして、式(2)、式(3)、式(4)、及び式(5)で得られた電圧値の4つの線形和を以下のように求める。

【0055】

Vout(t1)+Vout(t2)+Vout(t3)+Vout(t4)

=−4Vd・C1/Cf−(Vn(t1)+Vn(t2)+Vn(t3)+Vn(t4))・Cp/Cf+(Vn(t01)+Vn(t02)+Vn(t03)+Vn(t04))・Cp/Cf+4Vr …式(6)、

Vout(t1)−Vout(t2)+Vout(t3)−Vout(t4)

=−4Vd・C2/Cf−(Vn(t1)−Vn(t2)+Vn(t3)−Vn(t4))・Cp/Cf+(Vn(t01)−Vn(t02)+Vn(t03)−Vn(t04))・Cp/Cf …式(7)、

Vout(t1)+Vout(t2)−Vout(t3)−Vout(t4)

=−4Vd・C3/Cf−(Vn(t1)+Vn(t2)−Vn(t3)−Vn(t4))・Cp/Cf+(Vn(t01)+Vn(t02)−Vn(t03)−Vn(t04))・Cp/Cf …式(8)、

Vout(t1)−Vout(t2)−Vout(t3)+Vout(t4)

=−4Vd・C4/Cf−(Vn(t1)−Vn(t2)−Vn(t3)+Vn(t4))・Cp/Cf+(Vn(t01)−Vn(t02)−Vn(t03)+Vn(t04))・Cp/Cf …式(9)、

これらの演算結果により、ノイズ電圧Vn(t)に依存した誤差を許容すれば、静電容量C1、C2、C3、C4を推定することが可能である。ノイズ電圧を削減するためには、出力Vout(t1)、Vout(t2)、Vout(t3)、及びVout(t4)を得るためのサンプリングをそれぞれAD変換器3により複数回繰り返し行ってデジタル値に変換し、デジタル演算回路4によりそれらのデジタル値の加算平均Vout_ave1、Vout_ave2、Vout_ave3、及びVout_ave4を求めて、式(6)、式(7)、式(8)、及び式(9)における出力Vout(t1)、Vout(t2)、Vout(t3)、Vout(t4)を置き換えることでノイズを小さくすることが可能である。この場合も、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7によりサンプリングの時刻をランダム化することが推奨される。

(静電容量検出回路1Aの構成(シングルエンド、シングルサンプリング))

図2は、実施の形態1に係る他の静電容量検出回路1Aの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0056】

静電容量検出回路1Aは、複数個のサンプリング電圧の加算平均をアナログ回路により求める場合の回路例を示しており、AD変換器3、デジタル演算回路4の代わりにサンプリング容量回路5A、積分器6Aを備えている。

【0057】

サンプリング容量回路5Aは、サンプリング容量Csを有している。サンプリング容量Csの一方の端子にはスイッチSW1及びSW3が接続されており、他方の端子にはスイッチSW2及びSW4が接続されている。スイッチSW1は、サンプリング容量Csの一方の端子の接続を、センスアンプ2の出力と基準電圧Vrとの間で切り替える。スイッチSW2は、サンプリング容量Csの他方の端子の接続を、基準電圧Vrとセンスアンプ2の出力との間で切り替える。スイッチSW3は、サンプリング容量Csの一方の端子と積分器6Aとの間の接続をオンオフする。スイッチSW4は、サンプリング容量Csの他方の端子と積分器6Aとの間の接続をオンオフする。

【0058】

サンプリング容量回路5Aには、擬似乱数発生回路7Aが設けられている。擬似乱数発生回路7Aは、スイッチSW1〜SW4の動作周期を制御するために、予め定められた範囲内の擬似乱数を生成してサンプリング容量回路5Aに供給する。

【0059】

積分器6Aは、オペアンプ11を有している。オペアンプ11の非反転入力端子は、サンプリング容量回路5AのスイッチSW3に接続されている。オペアンプ11の反転入力端子は、基準電圧Vr及びサンプリング容量回路5AのスイッチSW4に接続されている。積分器6Aには、オペアンプ11の非反転入力端子及びオペアンプ11の出力に接続されて互いに並列に配置された積分容量Cint及びスイッチSWR_intが設けられている。

【0060】

(静電容量検出回路1Aの動作)

サンプリング容量回路5Aに設けられたサンプリング容量Csが、センスアンプ2の出力電圧Voutを、時刻t1、t2、…tnにおいてサンプリングして積分容量Cintに積分することで、平均化された出力電圧

Vout_ave={Vout(t1)+Vout(t2)+・・・+Vout(tn)}Cs/Cint、

が得られる。AD変換でデジタル化する図1に示す構成と比較して、量子化ノイズの混入が無いという優位性がある。

【0061】

(実施の形態2)

(静電容量検出回路1Bの構成(シングルエンド、CDS))

図3は、実施の形態2に係る静電容量検出回路1Bの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0062】

静電容量検出回路1Bは、駆動回路8Bとセンスアンプ2BとAD変換器3Bとデジタル演算回路4Bとを備えている。

【0063】

(静電容量検出回路1Bの動作)

静電容量C1、C2、C3、C4のセンスラインSLと繋がらない方の端子に電圧Vin1、Vin2、Vin3、Vin4を印加して、そのときのセンスアンプ2Bの出力電圧を複数回繰り返して読み出すことで静電容量C1、C2、C3、及びC4を推定するためのデータを得る。センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRを開き、さらにその後、駆動電圧を第1の駆動電圧の組Vin1=Vin11、Vin2=Vin21、Vin3=Vin31、Vin4=Vin41にして、出力が収束した後の時刻t1における出力電圧値は、

Vout(t1)=−(Vin11・C1+Vin21・C2+Vin31・C3+Vin41・C4)/Cf−(Vn(t1)−Vn(t01))・Cp/Cf+Vr+Voff …式(10)、

となる。ここで、Voffはセンスアンプ2Bの入力オフセット電圧である。

【0064】

次に、駆動電圧を第2の駆動電圧の組Vin1=Vin12、Vin2=Vin22、Vin3=Vin32、Vin4=Vin42にして、出力が収束した後の時刻t2における出力電圧値は、

Vout(t2)=−(Vin12・C1+Vin22・C2+Vin32・C3+Vin42・C4)/Cf−(Vn(t2)−Vn(t01))・Cp/Cf+Vr+Voff …式(11)、

となる。

【0065】

式(10)と式(11)とより、

Vout_cds=Vout(t2)−Vout(t1)

=−{(Vin12−Vin11)・C1+(Vin22−Vin21)・C2+(Vin32−Vin31)・C3+(Vin42−Vin41)・C4−(Vn(t2)−Vn(t1))・Cp/Cf、

となる。

【0066】

これは、相関2重サンプリングの原理により、時刻t1におけるノイズと時刻t2におけるノイズとに含まれる相関成分をキャンセルすることを目的としている。Vout_cdsに含まれるノイズの項であるVn(t2)−Vn(t1)は、時刻t1と時刻t2におけるノイズに相関があればキャンセルされる。また、上の式には表記していないが、センスアンプ2Bのノイズも時刻t1と時刻t2で相関のある部分はキャンセルされる。特に、センスアンプ2Bの入力オフセットのように時間変動のないノイズは完全にキャンセルされる。複数のセンスアンプ2Bを並列して使う場合には、個々のセンスアンプ2Bの入力オフセット電圧のばらつきが問題になるため、相関2重サンプリングの採用が望ましい。

【0067】

ここで、第1の駆動電圧を加えた時の出力電圧をAD変換器3Bにより複数回繰り返してサンプリングしてデジタル演算回路4Bにより加算平均を取ると、式(10)より、加算平均値は、

Vout_ave1=−(Vin11・C1+Vin21・C2+Vin31・C3+Vin41・C4)/Cf−(Vn(t1)_ave−Vn(t01))・Cp/Cf+Vr+Voff …式(12)、

となる。ここでVn(t1)_aveは、第1の印加電圧を加えた状態で複数回サンプリングした時のノイズVn(t)の加算平均を表す。

【0068】

さらに、第2の印加電圧を加えた時の出力電圧をAD変換器3Bにより複数回サンプリングしてデジタル演算回路4Bにより加算平均を取ると、式(11)より、加算平均値は、

Vout_ave2=−(Vin12・C1+Vin22・C2+Vin32・C3+Vin42・C4)/Cf−(Vn(t2)_ave−Vn(t01))・Cp/Cf+Vr+Voff …式(13)、

となる。ここでVn(t2)_aveは、第2の印加電圧を加えた状態で複数回サンプリングした時のノイズVn(t)の加算平均を表す。

【0069】

デジタル演算回路4Bにより式(12)、式(13)で表わされる加算平均値の差をとると、

Vout_cds_ave=Vout_ave2−Vout_ave1

=−{(Vin12−Vin11)・C1+(Vin22−Vin21)・C2+(Vin32−Vin31)・C3+(Vin42−Vin41)・C4−(Vn(t2)_ave−Vn(t1)_ave)・Cp/Cf、

となる。

【0070】

Vn(t1)_ave、Vn(t2)_aveともに、サンプル間の相関が小さければVn(t1)、Vn(t2)と比較して小さくなることが期待される。この場合でも、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7により、サンプリングの時刻をランダム化することが推奨される。

(静電容量検出回路1Cの構成(シングルエンド、CDS))

AD変換によるノイズの混入を排除するためには、加算平均値の求める演算と二つの加算平均の差を求める演算とをアナログ回路で行うことも好ましい。これは図4に示す回路により以下のような動作で実現が可能である。

【0071】

図4は、実施の形態2に係る他の静電容量検出回路1Cの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0072】

静電容量検出回路1Cは、AD変換器3B、デジタル演算回路4Bの代わりにサンプリング容量回路5C、積分器6Cを備えている。

【0073】

(静電容量検出回路1Cの動作)

まず、第1の駆動電圧の組でドライブラインDL1〜DL4を駆動している状態でのセンスアンプ2Bの出力をサンプリング容量Csにより複数回繰り返してサンプリングして積分器6Cにより積分容量Cintで積分する。この時のサンプリングは、スイッチSW1をセンスアンプ2Bの出力Voutに接続し、スイッチSW2を基準電圧Vrに接続することで行う。

【0074】

次に、第2の駆動電圧の組でドライブラインDL1〜DL4を駆動している状態でのセンスアンプ2Bの出力をサンプリング容量Csにより複数回繰り返してサンプリングするが、この時のサンプリングは、スイッチSW1を基準電圧Vrに接続し、スイッチSW2を出力Voutに接続することで行う。この結果として、積分器6Cの出力は下記のように表わされ、第1の駆動電圧印加時のセンスアンプ2Bの出力の加算平均と、第2の駆動電圧印加時のセンスアンプ2Bの出力の加算平均との差が得られる。

【0075】

Vout_cds_ave=[{Vout(t11)+Vout(t12)+…+Vout(t1n)}−{Vout(t21)+Vout(t22)+…+Vout(t2n)}]・Cs/(n・Cint)

(実施の形態3)

(静電容量検出回路1Dの構成(差動))

図5は、実施の形態3に係る静電容量検出回路1Dの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0076】

静電容量検出回路1Dは、センスラインSLA・SLBに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、それぞれ他端がセンスラインSLA・SLBに接続された静電容量C1A〜C4A、C1B〜C4Bの容量値を推定するためのデータを取得する。

【0077】

静電容量検出回路1Dは、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLA・SLBには、それぞれセンスライン寄生容量CpA・CpBが存在する。センスライン寄生容量CpA・CpBには、それぞれ外部からノイズNZA・NZBが印加される。静電容量検出回路1Dには、センスアンプ2Dが設けられている。センスアンプ2Dは、電圧Vin1〜Vin4の印加により静電容量C1A〜C4Aに蓄積された電荷及び静電容量C1B〜C4Bに蓄積された電荷を、センスラインSLA・SLBを通して読み出す。

【0078】

センスアンプ2Dは、差動オペアンプ11Dを有している。差動オペアンプ11Dの非反転入力端子はセンスラインSLBに接続されており、反転入力端子はセンスラインSLAに接続されている。

【0079】

センスアンプ2Dには、差動オペアンプ11Dの非反転入力端子と差動オペアンプ11Dの一方の出力とに接続された積分容量CfB及びスイッチSWRBが互いに並列に設けられており、差動オペアンプ11Dの反転入力端子と差動オペアンプ11Dの他方の出力とに接続された積分容量CfA及びスイッチSWRAが互いに並列に設けられている。

【0080】

静電容量検出回路1Dは、AD変換器3Dを備えている。AD変換器3Dは、駆動回路8がドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加している間に、センスアンプ2Dの一対の出力を複数回繰り返してサンプリングし、サンプリング毎にデジタル値に変換する。AD変換器3Dには、擬似乱数発生回路7が接続されている。擬似乱数発生回路7は、AD変換器3Dのサンプリング周期を制御するために、予め定められた範囲内の乱数を生成してAD変換器3Dに供給する。

【0081】

静電容量検出回路1Dには、デジタル演算回路4Dが設けられている。デジタル演算回路4Dは、AD変換器3Dにより変換された複数のデジタル値を平均化する。

【0082】

(静電容量検出回路1Dの動作(差動))

図5は、センスラインSLAとセンスラインSLBとに繋がった静電容量対(C1A、C1B)、(C2A、C2B)、(C3A、C3B)、(C4A、C4B)の容量差C1A−C1B、C2A−C2B、C3A−C3B、C4A−C4Bを推定する場合の回路例を示している。

【0083】

センスラインSLAとセンスラインSLBとの電荷をリセットするため、スイッチSWRAとSWRBとを閉じて、ドライブラインDL1〜DL4への印加電圧をVin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRAとスイッチSWRBとを開き、さらにその後、駆動電圧Vin1、Vin2、Vin3、Vin4を与えて出力が収束した後のセンスアンプ2Dの出力電圧値をAD変換器3Dで複数回繰り返してサンプリングしてデジタル化し、それをデジタル演算回路4Dにより平均化して出力の推定値を得る。この平均化により、センスラインSLA・SLBに形成された寄生容量CpAおよびCpBを介したノイズ電圧Vn、Vn’の影響を軽減することができる。

【0084】

具体的には、サンプリング時刻tにおけるセンスアンプ2Dの差動出力電圧Vout_d(t)は、

Vout_d(t)=−{Vin1・(C1A−C1B)+Vin2・(C2A−C2B)+Vin3・(C3A−C3B)+Vin4・(C4A−C4B)+(Vn(t)−Vn(t0))・Cp−(Vn’(t)−Vn’(t0))・Cp’}/CfA、

と表される。ただし、CfA=CfBとしている。

【0085】

従って、n回サンプリングしたVout_dを加算平均すると、サンプル毎のノイズ電圧Vnに相関が無く、かつサンプル毎のノイズ電圧Vn’に相関が無ければVn(t)・Cp−Vn’(t)・Cp’は1/sqrt(n)に小さくなり、信号対ノイズ比が改善する。この場合も、平均化により効果的にノイズ量を削減するために、サンプリングの時刻をランダム化することが推奨される。

【0086】

(静電容量検出回路1Eの構成(差動))

図6は、実施の形態3に係る他の静電容量検出回路1Eの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0087】

静電容量検出回路1Eは、AD変換器3D、デジタル演算回路4Dの代わりにサンプリング容量回路5E、積分器6Eを備えている。サンプリング容量回路5Eは、サンプリング容量CsA・CsBを有している。サンプリング容量CsAの一方の端子は、スイッチSW2と基準電圧Vcとの接続を切り替えるスイッチSW4に接続されている。スイッチSW2は、オペアンプ11Dの一方の出力と他方の出力とのいずれかにスイッチSW4を接続する。サンプリング容量CsAの他方の端子は、基準電圧Vcと積分器6Eとのいずれかに接続を切り替えるスイッチSW6に接続されている。

【0088】

サンプリング容量CsBの一方の端子は、スイッチSW1と基準電圧Vcとの接続を切り替えるスイッチSW3に接続されている。スイッチSW1は、オペアンプ11Dの一方の出力と他方の出力とのいずれかにスイッチSW3を接続する。サンプリング容量CsBの他方の端子は、基準電圧Vcと積分器6Eとのいずれかに接続を切り替えるスイッチSW5に接続されている。

【0089】

積分器6Eは、オペアンプ11Eを有している。オペアンプ11Eの非反転入力端子は、サンプリング容量回路5EのスイッチSW5に接続されている。オペアンプ11Eの反転入力端子は、サンプリング容量回路5EのスイッチSW6に接続されている。積分器6Eには、オペアンプ11Eの非反転入力端子及びオペアンプ11の一方の出力に接続されて互いに並列に配置された積分容量CintB及びスイッチSWR_intBと、オペアンプ11Eの反転入力端子及びオペアンプ11の他の出力に接続されて互いに並列に配置された積分容量CintA及びスイッチSWR_intAとが設けられている。

【0090】

(静電容量検出回路1Eの動作(差動))

図6は、加算平均を求める演算を、AD変換器3Dを使わずに行う回路の例を示している。センスアンプ2Dの差動出力をサンプリング容量対CsA・CsBにより複数回繰り返してサンプリングし、積分器6Eで積分することで加算平均された電圧が出力として得られる。

【0091】

(実施の形態4)

(静電容量検出回路1Fの構成(差動CDL))

図7は、実施の形態4に係る静電容量検出回路1Fの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0092】

静電容量検出回路1Fは、AD変換器3D、デジタル演算回路4Dの代わりにAD変換器3F、デジタル演算回路4Fを備えている。

【0093】

(静電容量検出回路1Fの動作(差動CDL))

図7は、センスラインSLAとセンスラインSLBとに繋がった静電容量対(C1A、C1B)、(C2A、C2B)、(C3A、C3B)、(C4A、C4B)の容量差C1A−C1B、C2A−C2B、C3A−C3B、C4A−C4Bを推定する場合の回路例を示している。

【0094】

センスラインSLAとセンスラインSLBとの電荷をリセットするため、スイッチSWRAとSWRBとを閉じて、ドライブラインDL1〜DL4への印加電圧をVin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRAとSWRBとを開き、さらにその後、第1の駆動電圧Vin1=Vin11、Vin2=Vin21、Vin3=Vin31、Vin4=Vin41でドライブラインDL1〜DL4を駆動してセンスアンプ2Dの差動出力の収束値をAD変換器3Fで複数回繰り返してサンプリングおよびデジタル化して、それらをデジタル演算回路4Fにより加算平均してデジタル出力

Dout_1=−{Vin11(C1A−C1B)+Vin21(C2A−C2B)+Vin31(C3A−C3B)+Vin41(C4A−C4B)+(Vn(t1)_ave−Vn(t0))Cp−(Vn’(t1)_ave−Vn’(t0))Cp’}/Cf+Voff、

を得る。

【0095】

ここで、Voffはセンスアンプ2Dの入力オフセット電圧であり、Vn(t1)_aveは第1の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn(t)の加算平均、Vn’(t1)_aveは第1の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn’(t)の加算平均を表す。

【0096】

次に、第2の駆動電圧Vin1=Vin12、Vin2=Vin22、Vin3=Vin32、Vin4=Vin42でドライブラインDL1〜DL4を駆動してセンスアンプ2Dの差動出力の収束値をAD変換器3Fで複数回サンプリングおよびデジタル化して、それらをデジタル演算回路4Fにより加算平均してデジタル出力

Dout_2=−{Vin12(C1A−C1B)+Vin22(C2A−C2B)+Vin32(C3A−C3B)+Vin42(C4A−C4B)+(Vn(t2)_ave−Vn(t0))Cp−(Vn’(t2)_ave−Vn’(t0))・Cp’}/CfA+Voff

を得る。

【0097】

ここで、Vn(t2)_aveは第2の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn(t)の加算平均、Vn’(t2)_aveは第2の駆動電圧を加えた状態で複数回サンプリングした時のノイズVn’(t)の加算平均を表す。デジタル演算回路4Fにより、Dout_2からDout_1を減算して、

Dout_2−Dout_1=−{(Vin12−Vin11)(C1A−C1B)+(Vin22−Vin21)・(C2A−C2B)+(Vin32−Vin31)(C3A−C3B)+(Vin42−Vin41)(C4A−C4B)}+(Vn(t2)_ave−Vn(t1)_ave)CpA−(Vn’(t2)_ave−Vn’(t1)_ave)CpB}/CfA、

となる。したがって、相関2重サンプリングと加算平均によりノイズが有効に減少することが期待できる。

【0098】

(静電容量検出回路1Gの構成(差動CDL))

図8は、実施の形態4に係る他の静電容量検出回路1Gの構成を示す回路図である。静電容量検出回路1Gは、AD変換器3F、デジタル演算回路4Fの代わりにサンプリング容量回路5G、積分器6Gを備えている。

【0099】

(静電容量検出回路1Eの動作(差動))

図8は加算平均と相関2重サンプリングにかかわる演算処理をAD変換器を使わずにアナログ回路で行う場合の回路例を示している。センスアンプ2Dの差動出力をサンプリング容量対CsA・CsBにより複数回繰り返してサンプリングし、積分器6Gで積分することで加算平均された電圧が出力として得られる。

【0100】

(実施の形態5)

(携帯電話機60の構成)

図9は、実施の形態5に係る携帯電話機60の構成を示すブロック図である。携帯電話機60は、CPU65と、RAM73と、ROM72と、カメラ66と、マイクロフォン67と、スピーカ68と、操作キー69と、表示パネル70と、表示制御回路71と、タッチパネルシステム61とを備えている。各構成要素は、相互にデータバスによって接続されている。

【0101】

CPU65は、携帯電話機70の動作を制御する。CPU65は、たとえばROM72に格納されたプログラムを実行する。操作キー69は、携帯電話機60のユーザによる指示の入力を受ける。RAM73は、CPU65によるプログラムの実行により生成されたデータ、または操作キー69を介して入力されたデータを揮発的に格納する。ROM72は、データを不揮発的に格納する。

【0102】

また、ROM72は、EPROM(Erasable Programmable Read-Only Memory)やフラッシュメモリなどの書込みおよび消去が可能なROMである。なお、図9には示していないが、携帯電話機60が、他の電子機器に有線により接続するためのインターフェイス(IF)を備える構成としてもよい。

【0103】

カメラ66は、ユーザの操作キー69の操作に応じて、被写体を撮影する。なお、撮影された被写体の画像データは、RAM73や外部メモリ(たとえば、メモリカード)に格納される。マイクロフォン67は、ユーザの音声の入力を受付ける。携帯電話機60は、当該入力された音声(アナログデータ)をデジタル化する。そして、携帯電話機60は、通信相手(たとえば、他の携帯電話機)にデジタル化した音声を送る。スピーカ68は、たとえば、RAM73に記憶された音楽データなどに基づく音を出力する。

【0104】

タッチパネルシステム61は、タッチパネル62と静電容量または静電容量差を検出する静電容量検出回路1とタッチ位置検出回路64とを有している。CPU65は、タッチパネルシステム61の動作を制御する。CPU65は、例えばROM72に記憶されたプログラムを実行する。RAM73は、CPU65によるプログラムの実行により生成されたデータを揮発的に格納する。ROM72は、データを不揮発的に格納する。

【0105】

表示パネル70は、表示制御回路71により、ROM72、RAM73に格納されている画像を表示する。表示パネル70は、タッチパネル62に重ねられているか、タッチパネル62を内蔵している。

【0106】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0107】

本発明は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端がセンスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路、及びこれを備えた電子機器に利用することができる。

【符号の説明】

【0108】

1 静電容量検出回路

2 センスアンプ

3 AD変換器

4 デジタル演算回路

5A サンプリング容量回路

6A 積分器(アナログ演算回路)

7 擬似乱数発生回路

9 入力端子

10 オペアンプ

11 オペアンプ

【技術分野】

【0001】

本発明は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端がセンスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路、及びこれを備えた電子機器に関する。

【背景技術】

【0002】

マトリックス状に分布した静電容量値を検出する装置、例えば、M本のドライブラインとL本のセンスラインとの間に形成される静電容量行列の静電容量値の分布を検出する容量検出装置が、特許文献1に開示されている。この容量検出装置は、指やペンでタッチパネルに触れると、触れられた静電容量の容量値が小さくなるので、容量値が小さくなった変化を検出して、指やペンのタッチを検出する。

【0003】

(従来の静電容量検出回路91の構成)

図10は、従来の静電容量検出回路91の構成を示す回路図である。静電容量検出回路91は、センスラインSLに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、他端がセンスラインSLに接続された静電容量C1〜C4の容量値を推定するためのデータを取得する。

【0004】

静電容量検出回路91は、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLには、センスライン寄生容量Cpが存在する。センスライン寄生容量Cpには、外部からノイズNZが印加される。静電容量検出回路91には、センスアンプ2が設けられている。センスアンプ2は、電圧Vin1〜Vin4の印加により静電容量C1〜C4に蓄積された電荷を、センスラインSLを通して読み出す。

【0005】

センスアンプ2は、オペアンプ10を有している。オペアンプ10の非反転入力端子はセンスラインSLに接続されており、反転入力端子は基準電圧Vrに接続されている。センスアンプ2には、オペアンプ10の非反転入力端子とオペアンプ10の出力とに接続された積分容量Cf及びスイッチSWRが互いに並列に設けられている。

【0006】

(従来の静電容量検出回路91の動作)

例えば、液晶ディスプレイ上に形成されたタッチパネルの場合、液晶ディスプレイの表面上に検出対象容量が形成されるため、センスラインSLは液晶の画素を駆動する配線との間にセンスライン寄生容量Cpが形成され、液晶の画素を駆動する電圧が該寄生容量に印加されセンスアンプの出力Voutにノイズとして重畳される。

【0007】

今、図10の静電容量検出回路91が、駆動電圧Vin1=Vin2=Vin3=Vin4=0とした状態でリセット用スイッチSWRを閉じて、時刻t0においてスイッチSWRを開いたとする。その後ドライブラインDL1〜DL4が駆動電圧Vin1、Vin2、Vin3、及びVin4で駆動されている時刻tにおけるセンスアンプ2の出力電圧Vout(t)は、以下の式(1)で表わされる。

【0008】

Vout(t)=−(Vin1・C1+Vin2・C2+Vin3・C3+Vin4・C4+(Vn(t)−Vn(t0))・Cp)/Cf+Vr …式(1)

ここで、ノイズNZの時刻tにおける電圧をVn(t)と表わしている。

【0009】

式(1)から判るように、ノイズ電圧の差{Vn(t)−Vn(t0)}とセンスライン寄生容量Cpとの積の絶対値が、{Vin1・C1+Vin2・C2+Vin3・C3+Vin4・C4}の絶対値に比べて十分小さくなければ、出力電圧Vout(t)を用いて静電容量C1、C2、C3、及びC4を推定する場合に誤差が生じる。

【0010】

誤差を小さくするためリセット、駆動電圧Vin1、Vin2、Vin3、及びVin4の印加、及び出力Voutの読み出しという動作を複数回繰り返して行い出力を平均化することが知られている。この場合、出力Voutの読み出しごとに{Vn(t)−Vn(t0)}の値が無相関に分布すれば、平均化によりサンプル個数の平方根に反比例してノイズの値が減少する。

【0011】

また、特許文献1には、検出対象静電容量を駆動電圧で充電して、充電された電荷を積分アンプに積分して放電させるという過程を繰り返すことで積分アンプの出力の信号対ノイズ比が改善することが記載されている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2010-250522号公報(2010年11月4日公開)

【発明の概要】

【発明が解決しようとする課題】

【0013】

しかしながら、静電容量C1〜C4をリセットし、駆動電圧Vin1〜Vin4により静電容量C1〜C4を再充電して静電容量C1〜C4の電荷をセンスアンプ2で読み出すという処理は、ドライブラインDL1〜DL4、センスラインSLの電圧を変化させるため、この電圧変化が収束するまでにはそれらのラインの持つ時定数で律捉された時間がかかり、容量値の推測に求められる限られた時間内に行える平均化の回数が不足するという課題があった。

【0014】

本発明の目的は、静電容量をリセットし、駆動電圧により再充電してセンスアンプで読み出すための処理時間を短縮することができる静電容量検出回路及び電子機器を提供することにある。

【課題を解決するための手段】

【0015】

本発明に係る静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする。

【0016】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能である。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。

【0017】

本発明に係る他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の出力を平均化するアナログ演算回路とを備えたことを特徴とする。

【0018】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能である。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずにアナログ回路により平均化するため、量子化ノイズの混入を排除することができる。

【0019】

本発明に係るさらに他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする。

【0020】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するので、駆動端子を第1の駆動電圧または電圧の組と、第2の駆動電圧または電圧の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。

【0021】

本発明に係るさらに他の静電容量検出回路は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた複数の第1サンプリング値を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた複数の第2サンプリング値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする。

【0022】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量Cpを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するので、駆動端子を第1の駆動電圧または電圧の組と、第2の駆動電圧または電圧の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずにアナログ回路により平均化するため、量子化ノイズの混入を排除することができる。

【0023】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする。

【0024】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理を短縮することができる。

【0025】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の電圧を印加する駆動回路と、前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通してそれぞれ読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の差動出力を平均化するアナログ演算回路とを備えたことを特徴とする。

【0026】

この特徴により、出力をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずに平均化するため、量子化ノイズの混入を排除することができる。

【0027】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする。

【0028】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するので、駆動端子を第1の駆動電圧対または電圧対の組と、第2の駆動電圧対または電圧対の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。

【0029】

本発明に係るさらに他の静電容量検出回路は、第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするサンプリング容量回路と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第1差動出力を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第2差動出力を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする。

【0030】

この特徴により、第1の検出電圧をサンプリングする瞬間にセンスライン寄生容量CpAおよびCpBを介して混入するノイズ成分が平均化され、さらに第2の検出電圧をサンプリングする瞬間にCpAおよびCpBを介して混入するノイズ成分も平均化されるため、第1の検出電圧と第2の検出電圧の差に含まれるノイズ成分が減少し、信号対ノイズ比の向上が可能になる。そして、前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするので、駆動端子を第1の駆動電圧対または電圧対の組と、第2の駆動電圧対または電圧対の組により駆動することを複数回繰り返す構成よりも処理時間を短縮することができる。また、AD変換を介さずに平均化するため、量子化ノイズの混入を排除することができる。

【0031】

本発明に係る静電容量検出回路では、前記AD変換器は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングすることが好ましく、前記サンプリング容量回路は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングすることが好ましい。

【0032】

上記構成により、平均化により効果的にノイズを削減することができる。

【0033】

本発明に係る静電容量検出回路では、前記センスアンプは、集積化されており、前記センスラインに接続された入力端子を有することが好ましい。

【0034】

上記構成により、センスアンプが集積化されるので、よりコンパクトな静電容量検出回路を得ることができる。

【0035】

本発明に係る電子機器は、本発明に係る静電容量検出回路を備え、前記センスラインと前記ドライブラインと前記静電容量とは、タッチパネルを構成し、前記タッチパネルに重ねられているか、前記タッチパネルを内蔵した表示パネルをさらに備えたことを特徴とする。

【0036】

この特徴により、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するので、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも静電容量検出の処理時間を短縮した電子機器を得ることができる。

【発明の効果】

【0037】

本発明に係る静電容量検出回路は、前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換する。このため、容量をリセットして駆動電圧を与えてセンスアンプで読み出すという処理を繰り返す構成よりも処理時間を短縮することができる。

【図面の簡単な説明】

【0038】

【図1】実施の形態1に係る静電容量検出回路の構成を示す回路図である。

【図2】実施の形態1に係る他の静電容量検出回路の構成を示す回路図である。

【図3】実施の形態2に係る静電容量検出回路の構成を示す回路図である。

【図4】実施の形態2に係る他の静電容量検出回路の構成を示す回路図である。

【図5】実施の形態3に係る静電容量検出回路の構成を示す回路図である。

【図6】実施の形態3に係る他の静電容量検出回路の構成を示す回路図である。

【図7】実施の形態4に係る静電容量検出回路の構成を示す回路図である。

【図8】実施の形態4に係る他の静電容量検出回路の構成を示す回路図である。

【図9】実施の形態5に係る携帯電話機の構成を示すブロック図である。

【図10】従来の静電容量検出回路の構成を示す回路図である。

【発明を実施するための形態】

【0039】

本発明の静電容量検出回路に関する実施の一形態について図1〜図9に基づいて説明すれば以下のとおりである。

【0040】

(実施の形態1)

(静電容量検出回路1の構成(シングルエンド、シングルサンプリング))

図1は、実施の形態1に係る静電容量検出回路1の構成を示す回路図である。静電容量検出回路1は、センスラインSLに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、他端がセンスラインSLに接続された静電容量C1〜C4の容量値を推定するためのデータを取得する。

【0041】

静電容量検出回路1は、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLには、センスライン寄生容量Cpが存在する。センスライン寄生容量Cpには、外部からノイズNZが印加される。静電容量検出回路1には、センスアンプ2が設けられている。センスアンプ2は、電圧Vin1〜Vin4の印加により静電容量C1〜C4に蓄積された電荷を、センスラインSLを通して読み出す。

【0042】

センスアンプ2は、オペアンプ10を有している。オペアンプ10の非反転入力端子はセンスラインSLに接続されており、反転入力端子は基準電圧Vrに接続されている。センスアンプ2には、オペアンプ10の非反転入力端子とオペアンプ10の出力とに接続された積分容量Cf及びスイッチSWRが互いに並列に設けられている。

【0043】

センスアンプ2は、集積化されており、センスラインSLに接続された入力端子9を有している。

【0044】

静電容量検出回路1は、AD変換器3を備えている。AD変換器3は、駆動回路8がドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加している間に、センスアンプ2の出力を複数回繰り返してサンプリングし、サンプリング毎にデジタル値に変換する。AD変換器3には、擬似乱数発生回路7が接続されている。擬似乱数発生回路7は、AD変換器3のサンプリング周期を制御するために、予め定められた範囲内の乱数を生成してAD変換器3に供給する。

【0045】

静電容量検出回路1には、デジタル演算回路4が設けられている。デジタル演算回路4は、AD変換器3により変換された複数のデジタル値を平均化する。

【0046】

(静電容量検出回路1の動作)

静電容量C1、C2、C3、及びC4のセンスラインSLと繋がらない方の端子に、ドライブラインDL1〜DL4を通して電圧Vin1、Vin2、Vin3、及びVin4を印加して、そのときのセンスアンプ2の出力電圧をAD変換器3により複数回繰り返して読み出すことで容量C1、C2、C3、及びC4の値を推定するためのデータを得る。センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。

【0047】

AD変換器3による読み出しの繰り返し回数は、実際には、駆動方式や外来ノイズの状況、必要とされるS/Nにより、数回から1000回以上まで多様な数値を取り得る。指やペンのタッチ位置を検出するために必要とされるS/N比を実現でき、かつ一回のタッチ位置検出に許容される時間内に完了できる適切な繰り返し回数を選ぶ。

【0048】

その後、時刻t0においてスイッチSWRを開き、さらにその後、駆動電圧をVin1=Vd、Vin2=Vin3=Vin4=0にして出力が収束した後の時刻tにおける出力電圧値は、

Vout(t)=−{Vd・C1+(Vn(t)−Vn(t0))・Cp}/Cf+Vr …式(1)、

となり、Vn(t)−Vn(t0)というノイズで決まる誤差を許容すると静電容量C1の値を推定できる。ノイズ電圧Vnのrms(二乗平均平方根、Root Mean Square)値をVn_rmsとすると、Vn(t)−Vn(t0)のrms値は2Vn_rmsである。ここで、ノイズによる誤差を削減するために、駆動電圧をVin1=Vd、Vin2=Vin3=Vin4=0にして、出力が収束した後の出力電圧を時刻t11、t12、…t1nにおいてAD変換器3によりn回繰り返してサンプリングしてデジタル値に変換し、デジタル演算回路4によりそれらのデジタル値の加算平均Vout_aveを求めると、

Vout_ave=−{n・Vd・C1+(Vn(t11)+Vn(t12)+・・・+Vn(t1n)−n・Vn(t0))・Cp}/(n・Cf)+Vr、

となる。この加算平均値に含まれるノイズの項、(Vn(t11)+Vn(t12)+ ・・・+Vn(t1n))/nはサンプル間のノイズ電圧Vn(t11)、Vn(t12)、…Vn(t1n)に相関が無ければ、rms値においてノイズ電圧Vnのrms値の1/sqrt(n)に小さくなるため、Vout(t)では2Vn_rmsであったノイズのrms値が、Vn_aveではサンプリング回数nを大きくすると、Vn_rmsまで削減可能である。

【0049】

一般に寄生容量Cpを介してセンスラインSLに影響するノイズ電圧Vnは、液晶ディスプレイの表示画面に依存してランダムな変化があり、サンプル間の相関は小さいことが期待される。しかしながら、ノイズ電圧が液晶ディスプレイの画面走査の周期で周期的に変動したり、あるいは、タッチパネルを操作する人体を介して混入する外部の周期的変動ノイズの場合には、周期的なサンプリングではサンプル間の相関が大きくなることもあり得る。この様な場合でも、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7によりサンプリングの時刻を非周期的にすることが推奨される。

【0050】

(静電容量検出回路1の他の駆動方法)

静電容量検出回路1の他の駆動方法による容量値の推定方法を以下に説明する。上述した駆動方法と同様に、センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t01においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、Vd、Vd、Vd)を印加した時の出力を時刻t1でサンプリングした値をVout(t1)とすると、

Vout(t1)=−Vd(C1+C2+C3+C4)/Cf−(Vn(t1)−Vn(t01))Cp/Cf+Vr …式(2)、

となる。

【0051】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t02においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、−Vd、Vd、−Vd)を印加した時の出力を時刻t2でサンプリングした値をVout(t2)とすると、

Vout(t2)=−Vd(C1−C2+C3−C4)/Cf−(Vn(t2)−Vn(t02))Cp/Cf+Vr …式(3)、

となる。

【0052】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t03においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、Vd、−Vd、−Vd)を印加した時の出力を時刻t3でサンプリングした値をVout(t3)とすると、

Vout(t3)=−Vd(C1+C2−C3−C4)/Cf−(Vn(t3)−Vn(t03))Cp/Cf+Vr …式(4)、

となる。

【0053】

次に、センスラインSLの電荷をリセットするため、スイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t04においてスイッチSWRを開き、さらにその後、(Vin1、Vin2、Vin3、Vin4)=(Vd、−Vd、−Vd、Vd)を印加した時の出力を時刻t4でサンプリングした値をVout(t4)とすると、

Vout(t4)=−Vd(C1−C2−C3+C4)/Cf−(Vn(t4)−Vn(t04))Cp/Cf+Vr …式(5)、

となる。

【0054】

そして、式(2)、式(3)、式(4)、及び式(5)で得られた電圧値の4つの線形和を以下のように求める。

【0055】

Vout(t1)+Vout(t2)+Vout(t3)+Vout(t4)

=−4Vd・C1/Cf−(Vn(t1)+Vn(t2)+Vn(t3)+Vn(t4))・Cp/Cf+(Vn(t01)+Vn(t02)+Vn(t03)+Vn(t04))・Cp/Cf+4Vr …式(6)、

Vout(t1)−Vout(t2)+Vout(t3)−Vout(t4)

=−4Vd・C2/Cf−(Vn(t1)−Vn(t2)+Vn(t3)−Vn(t4))・Cp/Cf+(Vn(t01)−Vn(t02)+Vn(t03)−Vn(t04))・Cp/Cf …式(7)、

Vout(t1)+Vout(t2)−Vout(t3)−Vout(t4)

=−4Vd・C3/Cf−(Vn(t1)+Vn(t2)−Vn(t3)−Vn(t4))・Cp/Cf+(Vn(t01)+Vn(t02)−Vn(t03)−Vn(t04))・Cp/Cf …式(8)、

Vout(t1)−Vout(t2)−Vout(t3)+Vout(t4)

=−4Vd・C4/Cf−(Vn(t1)−Vn(t2)−Vn(t3)+Vn(t4))・Cp/Cf+(Vn(t01)−Vn(t02)−Vn(t03)+Vn(t04))・Cp/Cf …式(9)、

これらの演算結果により、ノイズ電圧Vn(t)に依存した誤差を許容すれば、静電容量C1、C2、C3、C4を推定することが可能である。ノイズ電圧を削減するためには、出力Vout(t1)、Vout(t2)、Vout(t3)、及びVout(t4)を得るためのサンプリングをそれぞれAD変換器3により複数回繰り返し行ってデジタル値に変換し、デジタル演算回路4によりそれらのデジタル値の加算平均Vout_ave1、Vout_ave2、Vout_ave3、及びVout_ave4を求めて、式(6)、式(7)、式(8)、及び式(9)における出力Vout(t1)、Vout(t2)、Vout(t3)、Vout(t4)を置き換えることでノイズを小さくすることが可能である。この場合も、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7によりサンプリングの時刻をランダム化することが推奨される。

(静電容量検出回路1Aの構成(シングルエンド、シングルサンプリング))

図2は、実施の形態1に係る他の静電容量検出回路1Aの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0056】

静電容量検出回路1Aは、複数個のサンプリング電圧の加算平均をアナログ回路により求める場合の回路例を示しており、AD変換器3、デジタル演算回路4の代わりにサンプリング容量回路5A、積分器6Aを備えている。

【0057】

サンプリング容量回路5Aは、サンプリング容量Csを有している。サンプリング容量Csの一方の端子にはスイッチSW1及びSW3が接続されており、他方の端子にはスイッチSW2及びSW4が接続されている。スイッチSW1は、サンプリング容量Csの一方の端子の接続を、センスアンプ2の出力と基準電圧Vrとの間で切り替える。スイッチSW2は、サンプリング容量Csの他方の端子の接続を、基準電圧Vrとセンスアンプ2の出力との間で切り替える。スイッチSW3は、サンプリング容量Csの一方の端子と積分器6Aとの間の接続をオンオフする。スイッチSW4は、サンプリング容量Csの他方の端子と積分器6Aとの間の接続をオンオフする。

【0058】

サンプリング容量回路5Aには、擬似乱数発生回路7Aが設けられている。擬似乱数発生回路7Aは、スイッチSW1〜SW4の動作周期を制御するために、予め定められた範囲内の擬似乱数を生成してサンプリング容量回路5Aに供給する。

【0059】

積分器6Aは、オペアンプ11を有している。オペアンプ11の非反転入力端子は、サンプリング容量回路5AのスイッチSW3に接続されている。オペアンプ11の反転入力端子は、基準電圧Vr及びサンプリング容量回路5AのスイッチSW4に接続されている。積分器6Aには、オペアンプ11の非反転入力端子及びオペアンプ11の出力に接続されて互いに並列に配置された積分容量Cint及びスイッチSWR_intが設けられている。

【0060】

(静電容量検出回路1Aの動作)

サンプリング容量回路5Aに設けられたサンプリング容量Csが、センスアンプ2の出力電圧Voutを、時刻t1、t2、…tnにおいてサンプリングして積分容量Cintに積分することで、平均化された出力電圧

Vout_ave={Vout(t1)+Vout(t2)+・・・+Vout(tn)}Cs/Cint、

が得られる。AD変換でデジタル化する図1に示す構成と比較して、量子化ノイズの混入が無いという優位性がある。

【0061】

(実施の形態2)

(静電容量検出回路1Bの構成(シングルエンド、CDS))

図3は、実施の形態2に係る静電容量検出回路1Bの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0062】

静電容量検出回路1Bは、駆動回路8Bとセンスアンプ2BとAD変換器3Bとデジタル演算回路4Bとを備えている。

【0063】

(静電容量検出回路1Bの動作)

静電容量C1、C2、C3、C4のセンスラインSLと繋がらない方の端子に電圧Vin1、Vin2、Vin3、Vin4を印加して、そのときのセンスアンプ2Bの出力電圧を複数回繰り返して読み出すことで静電容量C1、C2、C3、及びC4を推定するためのデータを得る。センスラインSLの電荷をリセットするため、まずスイッチSWRを閉じて、ドライブラインDL1〜DL4への印加電圧Vin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRを開き、さらにその後、駆動電圧を第1の駆動電圧の組Vin1=Vin11、Vin2=Vin21、Vin3=Vin31、Vin4=Vin41にして、出力が収束した後の時刻t1における出力電圧値は、

Vout(t1)=−(Vin11・C1+Vin21・C2+Vin31・C3+Vin41・C4)/Cf−(Vn(t1)−Vn(t01))・Cp/Cf+Vr+Voff …式(10)、

となる。ここで、Voffはセンスアンプ2Bの入力オフセット電圧である。

【0064】

次に、駆動電圧を第2の駆動電圧の組Vin1=Vin12、Vin2=Vin22、Vin3=Vin32、Vin4=Vin42にして、出力が収束した後の時刻t2における出力電圧値は、

Vout(t2)=−(Vin12・C1+Vin22・C2+Vin32・C3+Vin42・C4)/Cf−(Vn(t2)−Vn(t01))・Cp/Cf+Vr+Voff …式(11)、

となる。

【0065】

式(10)と式(11)とより、

Vout_cds=Vout(t2)−Vout(t1)

=−{(Vin12−Vin11)・C1+(Vin22−Vin21)・C2+(Vin32−Vin31)・C3+(Vin42−Vin41)・C4−(Vn(t2)−Vn(t1))・Cp/Cf、

となる。

【0066】

これは、相関2重サンプリングの原理により、時刻t1におけるノイズと時刻t2におけるノイズとに含まれる相関成分をキャンセルすることを目的としている。Vout_cdsに含まれるノイズの項であるVn(t2)−Vn(t1)は、時刻t1と時刻t2におけるノイズに相関があればキャンセルされる。また、上の式には表記していないが、センスアンプ2Bのノイズも時刻t1と時刻t2で相関のある部分はキャンセルされる。特に、センスアンプ2Bの入力オフセットのように時間変動のないノイズは完全にキャンセルされる。複数のセンスアンプ2Bを並列して使う場合には、個々のセンスアンプ2Bの入力オフセット電圧のばらつきが問題になるため、相関2重サンプリングの採用が望ましい。

【0067】

ここで、第1の駆動電圧を加えた時の出力電圧をAD変換器3Bにより複数回繰り返してサンプリングしてデジタル演算回路4Bにより加算平均を取ると、式(10)より、加算平均値は、

Vout_ave1=−(Vin11・C1+Vin21・C2+Vin31・C3+Vin41・C4)/Cf−(Vn(t1)_ave−Vn(t01))・Cp/Cf+Vr+Voff …式(12)、

となる。ここでVn(t1)_aveは、第1の印加電圧を加えた状態で複数回サンプリングした時のノイズVn(t)の加算平均を表す。

【0068】

さらに、第2の印加電圧を加えた時の出力電圧をAD変換器3Bにより複数回サンプリングしてデジタル演算回路4Bにより加算平均を取ると、式(11)より、加算平均値は、

Vout_ave2=−(Vin12・C1+Vin22・C2+Vin32・C3+Vin42・C4)/Cf−(Vn(t2)_ave−Vn(t01))・Cp/Cf+Vr+Voff …式(13)、

となる。ここでVn(t2)_aveは、第2の印加電圧を加えた状態で複数回サンプリングした時のノイズVn(t)の加算平均を表す。

【0069】

デジタル演算回路4Bにより式(12)、式(13)で表わされる加算平均値の差をとると、

Vout_cds_ave=Vout_ave2−Vout_ave1

=−{(Vin12−Vin11)・C1+(Vin22−Vin21)・C2+(Vin32−Vin31)・C3+(Vin42−Vin41)・C4−(Vn(t2)_ave−Vn(t1)_ave)・Cp/Cf、

となる。

【0070】

Vn(t1)_ave、Vn(t2)_aveともに、サンプル間の相関が小さければVn(t1)、Vn(t2)と比較して小さくなることが期待される。この場合でも、平均化により効果的にノイズ量を削減するために、擬似乱数発生回路7により、サンプリングの時刻をランダム化することが推奨される。

(静電容量検出回路1Cの構成(シングルエンド、CDS))

AD変換によるノイズの混入を排除するためには、加算平均値の求める演算と二つの加算平均の差を求める演算とをアナログ回路で行うことも好ましい。これは図4に示す回路により以下のような動作で実現が可能である。

【0071】

図4は、実施の形態2に係る他の静電容量検出回路1Cの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0072】

静電容量検出回路1Cは、AD変換器3B、デジタル演算回路4Bの代わりにサンプリング容量回路5C、積分器6Cを備えている。

【0073】

(静電容量検出回路1Cの動作)

まず、第1の駆動電圧の組でドライブラインDL1〜DL4を駆動している状態でのセンスアンプ2Bの出力をサンプリング容量Csにより複数回繰り返してサンプリングして積分器6Cにより積分容量Cintで積分する。この時のサンプリングは、スイッチSW1をセンスアンプ2Bの出力Voutに接続し、スイッチSW2を基準電圧Vrに接続することで行う。

【0074】

次に、第2の駆動電圧の組でドライブラインDL1〜DL4を駆動している状態でのセンスアンプ2Bの出力をサンプリング容量Csにより複数回繰り返してサンプリングするが、この時のサンプリングは、スイッチSW1を基準電圧Vrに接続し、スイッチSW2を出力Voutに接続することで行う。この結果として、積分器6Cの出力は下記のように表わされ、第1の駆動電圧印加時のセンスアンプ2Bの出力の加算平均と、第2の駆動電圧印加時のセンスアンプ2Bの出力の加算平均との差が得られる。

【0075】

Vout_cds_ave=[{Vout(t11)+Vout(t12)+…+Vout(t1n)}−{Vout(t21)+Vout(t22)+…+Vout(t2n)}]・Cs/(n・Cint)

(実施の形態3)

(静電容量検出回路1Dの構成(差動))

図5は、実施の形態3に係る静電容量検出回路1Dの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0076】

静電容量検出回路1Dは、センスラインSLA・SLBに交差するドライブラインDL1〜DL4にそれぞれ一端が接続され、それぞれ他端がセンスラインSLA・SLBに接続された静電容量C1A〜C4A、C1B〜C4Bの容量値を推定するためのデータを取得する。

【0077】

静電容量検出回路1Dは、駆動回路8を備えている。駆動回路8は、ドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加する。センスラインSLA・SLBには、それぞれセンスライン寄生容量CpA・CpBが存在する。センスライン寄生容量CpA・CpBには、それぞれ外部からノイズNZA・NZBが印加される。静電容量検出回路1Dには、センスアンプ2Dが設けられている。センスアンプ2Dは、電圧Vin1〜Vin4の印加により静電容量C1A〜C4Aに蓄積された電荷及び静電容量C1B〜C4Bに蓄積された電荷を、センスラインSLA・SLBを通して読み出す。

【0078】

センスアンプ2Dは、差動オペアンプ11Dを有している。差動オペアンプ11Dの非反転入力端子はセンスラインSLBに接続されており、反転入力端子はセンスラインSLAに接続されている。

【0079】

センスアンプ2Dには、差動オペアンプ11Dの非反転入力端子と差動オペアンプ11Dの一方の出力とに接続された積分容量CfB及びスイッチSWRBが互いに並列に設けられており、差動オペアンプ11Dの反転入力端子と差動オペアンプ11Dの他方の出力とに接続された積分容量CfA及びスイッチSWRAが互いに並列に設けられている。

【0080】

静電容量検出回路1Dは、AD変換器3Dを備えている。AD変換器3Dは、駆動回路8がドライブラインDL1〜DL4に電圧Vin1〜Vin4を印加している間に、センスアンプ2Dの一対の出力を複数回繰り返してサンプリングし、サンプリング毎にデジタル値に変換する。AD変換器3Dには、擬似乱数発生回路7が接続されている。擬似乱数発生回路7は、AD変換器3Dのサンプリング周期を制御するために、予め定められた範囲内の乱数を生成してAD変換器3Dに供給する。

【0081】

静電容量検出回路1Dには、デジタル演算回路4Dが設けられている。デジタル演算回路4Dは、AD変換器3Dにより変換された複数のデジタル値を平均化する。

【0082】

(静電容量検出回路1Dの動作(差動))

図5は、センスラインSLAとセンスラインSLBとに繋がった静電容量対(C1A、C1B)、(C2A、C2B)、(C3A、C3B)、(C4A、C4B)の容量差C1A−C1B、C2A−C2B、C3A−C3B、C4A−C4Bを推定する場合の回路例を示している。

【0083】

センスラインSLAとセンスラインSLBとの電荷をリセットするため、スイッチSWRAとSWRBとを閉じて、ドライブラインDL1〜DL4への印加電圧をVin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRAとスイッチSWRBとを開き、さらにその後、駆動電圧Vin1、Vin2、Vin3、Vin4を与えて出力が収束した後のセンスアンプ2Dの出力電圧値をAD変換器3Dで複数回繰り返してサンプリングしてデジタル化し、それをデジタル演算回路4Dにより平均化して出力の推定値を得る。この平均化により、センスラインSLA・SLBに形成された寄生容量CpAおよびCpBを介したノイズ電圧Vn、Vn’の影響を軽減することができる。

【0084】

具体的には、サンプリング時刻tにおけるセンスアンプ2Dの差動出力電圧Vout_d(t)は、

Vout_d(t)=−{Vin1・(C1A−C1B)+Vin2・(C2A−C2B)+Vin3・(C3A−C3B)+Vin4・(C4A−C4B)+(Vn(t)−Vn(t0))・Cp−(Vn’(t)−Vn’(t0))・Cp’}/CfA、

と表される。ただし、CfA=CfBとしている。

【0085】

従って、n回サンプリングしたVout_dを加算平均すると、サンプル毎のノイズ電圧Vnに相関が無く、かつサンプル毎のノイズ電圧Vn’に相関が無ければVn(t)・Cp−Vn’(t)・Cp’は1/sqrt(n)に小さくなり、信号対ノイズ比が改善する。この場合も、平均化により効果的にノイズ量を削減するために、サンプリングの時刻をランダム化することが推奨される。

【0086】

(静電容量検出回路1Eの構成(差動))

図6は、実施の形態3に係る他の静電容量検出回路1Eの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0087】

静電容量検出回路1Eは、AD変換器3D、デジタル演算回路4Dの代わりにサンプリング容量回路5E、積分器6Eを備えている。サンプリング容量回路5Eは、サンプリング容量CsA・CsBを有している。サンプリング容量CsAの一方の端子は、スイッチSW2と基準電圧Vcとの接続を切り替えるスイッチSW4に接続されている。スイッチSW2は、オペアンプ11Dの一方の出力と他方の出力とのいずれかにスイッチSW4を接続する。サンプリング容量CsAの他方の端子は、基準電圧Vcと積分器6Eとのいずれかに接続を切り替えるスイッチSW6に接続されている。

【0088】

サンプリング容量CsBの一方の端子は、スイッチSW1と基準電圧Vcとの接続を切り替えるスイッチSW3に接続されている。スイッチSW1は、オペアンプ11Dの一方の出力と他方の出力とのいずれかにスイッチSW3を接続する。サンプリング容量CsBの他方の端子は、基準電圧Vcと積分器6Eとのいずれかに接続を切り替えるスイッチSW5に接続されている。

【0089】

積分器6Eは、オペアンプ11Eを有している。オペアンプ11Eの非反転入力端子は、サンプリング容量回路5EのスイッチSW5に接続されている。オペアンプ11Eの反転入力端子は、サンプリング容量回路5EのスイッチSW6に接続されている。積分器6Eには、オペアンプ11Eの非反転入力端子及びオペアンプ11の一方の出力に接続されて互いに並列に配置された積分容量CintB及びスイッチSWR_intBと、オペアンプ11Eの反転入力端子及びオペアンプ11の他の出力に接続されて互いに並列に配置された積分容量CintA及びスイッチSWR_intAとが設けられている。

【0090】

(静電容量検出回路1Eの動作(差動))

図6は、加算平均を求める演算を、AD変換器3Dを使わずに行う回路の例を示している。センスアンプ2Dの差動出力をサンプリング容量対CsA・CsBにより複数回繰り返してサンプリングし、積分器6Eで積分することで加算平均された電圧が出力として得られる。

【0091】

(実施の形態4)

(静電容量検出回路1Fの構成(差動CDL))

図7は、実施の形態4に係る静電容量検出回路1Fの構成を示す回路図である。前述した構成要素と同一の構成要素には同一の参照符号を付している。これらの構成要素の詳細な説明は省略する。

【0092】

静電容量検出回路1Fは、AD変換器3D、デジタル演算回路4Dの代わりにAD変換器3F、デジタル演算回路4Fを備えている。

【0093】

(静電容量検出回路1Fの動作(差動CDL))

図7は、センスラインSLAとセンスラインSLBとに繋がった静電容量対(C1A、C1B)、(C2A、C2B)、(C3A、C3B)、(C4A、C4B)の容量差C1A−C1B、C2A−C2B、C3A−C3B、C4A−C4Bを推定する場合の回路例を示している。

【0094】

センスラインSLAとセンスラインSLBとの電荷をリセットするため、スイッチSWRAとSWRBとを閉じて、ドライブラインDL1〜DL4への印加電圧をVin1=Vin2=Vin3=Vin4=0とする。その後、時刻t0においてスイッチSWRAとSWRBとを開き、さらにその後、第1の駆動電圧Vin1=Vin11、Vin2=Vin21、Vin3=Vin31、Vin4=Vin41でドライブラインDL1〜DL4を駆動してセンスアンプ2Dの差動出力の収束値をAD変換器3Fで複数回繰り返してサンプリングおよびデジタル化して、それらをデジタル演算回路4Fにより加算平均してデジタル出力

Dout_1=−{Vin11(C1A−C1B)+Vin21(C2A−C2B)+Vin31(C3A−C3B)+Vin41(C4A−C4B)+(Vn(t1)_ave−Vn(t0))Cp−(Vn’(t1)_ave−Vn’(t0))Cp’}/Cf+Voff、

を得る。

【0095】

ここで、Voffはセンスアンプ2Dの入力オフセット電圧であり、Vn(t1)_aveは第1の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn(t)の加算平均、Vn’(t1)_aveは第1の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn’(t)の加算平均を表す。

【0096】

次に、第2の駆動電圧Vin1=Vin12、Vin2=Vin22、Vin3=Vin32、Vin4=Vin42でドライブラインDL1〜DL4を駆動してセンスアンプ2Dの差動出力の収束値をAD変換器3Fで複数回サンプリングおよびデジタル化して、それらをデジタル演算回路4Fにより加算平均してデジタル出力

Dout_2=−{Vin12(C1A−C1B)+Vin22(C2A−C2B)+Vin32(C3A−C3B)+Vin42(C4A−C4B)+(Vn(t2)_ave−Vn(t0))Cp−(Vn’(t2)_ave−Vn’(t0))・Cp’}/CfA+Voff

を得る。

【0097】

ここで、Vn(t2)_aveは第2の駆動電圧を加えた状態で複数回繰り返してサンプリングした時のノイズVn(t)の加算平均、Vn’(t2)_aveは第2の駆動電圧を加えた状態で複数回サンプリングした時のノイズVn’(t)の加算平均を表す。デジタル演算回路4Fにより、Dout_2からDout_1を減算して、

Dout_2−Dout_1=−{(Vin12−Vin11)(C1A−C1B)+(Vin22−Vin21)・(C2A−C2B)+(Vin32−Vin31)(C3A−C3B)+(Vin42−Vin41)(C4A−C4B)}+(Vn(t2)_ave−Vn(t1)_ave)CpA−(Vn’(t2)_ave−Vn’(t1)_ave)CpB}/CfA、

となる。したがって、相関2重サンプリングと加算平均によりノイズが有効に減少することが期待できる。

【0098】

(静電容量検出回路1Gの構成(差動CDL))

図8は、実施の形態4に係る他の静電容量検出回路1Gの構成を示す回路図である。静電容量検出回路1Gは、AD変換器3F、デジタル演算回路4Fの代わりにサンプリング容量回路5G、積分器6Gを備えている。

【0099】

(静電容量検出回路1Eの動作(差動))

図8は加算平均と相関2重サンプリングにかかわる演算処理をAD変換器を使わずにアナログ回路で行う場合の回路例を示している。センスアンプ2Dの差動出力をサンプリング容量対CsA・CsBにより複数回繰り返してサンプリングし、積分器6Gで積分することで加算平均された電圧が出力として得られる。

【0100】

(実施の形態5)

(携帯電話機60の構成)

図9は、実施の形態5に係る携帯電話機60の構成を示すブロック図である。携帯電話機60は、CPU65と、RAM73と、ROM72と、カメラ66と、マイクロフォン67と、スピーカ68と、操作キー69と、表示パネル70と、表示制御回路71と、タッチパネルシステム61とを備えている。各構成要素は、相互にデータバスによって接続されている。

【0101】

CPU65は、携帯電話機70の動作を制御する。CPU65は、たとえばROM72に格納されたプログラムを実行する。操作キー69は、携帯電話機60のユーザによる指示の入力を受ける。RAM73は、CPU65によるプログラムの実行により生成されたデータ、または操作キー69を介して入力されたデータを揮発的に格納する。ROM72は、データを不揮発的に格納する。

【0102】

また、ROM72は、EPROM(Erasable Programmable Read-Only Memory)やフラッシュメモリなどの書込みおよび消去が可能なROMである。なお、図9には示していないが、携帯電話機60が、他の電子機器に有線により接続するためのインターフェイス(IF)を備える構成としてもよい。

【0103】

カメラ66は、ユーザの操作キー69の操作に応じて、被写体を撮影する。なお、撮影された被写体の画像データは、RAM73や外部メモリ(たとえば、メモリカード)に格納される。マイクロフォン67は、ユーザの音声の入力を受付ける。携帯電話機60は、当該入力された音声(アナログデータ)をデジタル化する。そして、携帯電話機60は、通信相手(たとえば、他の携帯電話機)にデジタル化した音声を送る。スピーカ68は、たとえば、RAM73に記憶された音楽データなどに基づく音を出力する。

【0104】

タッチパネルシステム61は、タッチパネル62と静電容量または静電容量差を検出する静電容量検出回路1とタッチ位置検出回路64とを有している。CPU65は、タッチパネルシステム61の動作を制御する。CPU65は、例えばROM72に記憶されたプログラムを実行する。RAM73は、CPU65によるプログラムの実行により生成されたデータを揮発的に格納する。ROM72は、データを不揮発的に格納する。

【0105】

表示パネル70は、表示制御回路71により、ROM72、RAM73に格納されている画像を表示する。表示パネル70は、タッチパネル62に重ねられているか、タッチパネル62を内蔵している。

【0106】

本発明は上述した各実施形態に限定されるものではなく、請求項に示した範囲で種々の変更が可能であり、異なる実施形態にそれぞれ開示された技術的手段を適宜組み合わせて得られる実施形態についても本発明の技術的範囲に含まれる。

【産業上の利用可能性】

【0107】

本発明は、センスラインに交差する1本以上のドライブラインに一端が接続され、他端がセンスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路、及びこれを備えた電子機器に利用することができる。

【符号の説明】

【0108】

1 静電容量検出回路

2 センスアンプ

3 AD変換器

4 デジタル演算回路

5A サンプリング容量回路

6A 積分器(アナログ演算回路)

7 擬似乱数発生回路

9 入力端子

10 オペアンプ

11 オペアンプ

【特許請求の範囲】

【請求項1】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、

前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項2】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の出力を平均化するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項3】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、

前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項4】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた複数の第1サンプリング値を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた複数の第2サンプリング値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項5】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、

前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項6】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通してそれぞれ読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の差動出力を平均化するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項7】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、

前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項8】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第1差動出力を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第2差動出力を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項9】

前記AD変換器は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングする請求項1、3、5及び7のいずれかに記載の静電容量検出回路。

【請求項10】

前記サンプリング容量回路は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングする請求項2、4、6及び8のいずれかに記載の静電容量検出回路。

【請求項11】

前記センスアンプは、集積化されており、前記センスラインに接続された入力端子を有する請求項1〜8の何れかに記載の静電容量検出回路。

【請求項12】

請求項11に記載の静電容量検出回路を備え、

前記センスラインと前記ドライブラインと前記静電容量とは、タッチパネルを構成し、

前記タッチパネルに重ねられているか、前記タッチパネルを内蔵した表示パネルをさらに備えたことを特徴とする電子機器。

【請求項1】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、

前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項2】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の出力を平均化するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項3】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、

前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項4】

センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記センスラインに接続された1個以上の静電容量の容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記静電容量に蓄積された電荷を、前記センスラインを通して読み出した後、前記第2電圧の印加により前記静電容量に蓄積された電荷を前記センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第1サンプリング値を生成し、前記駆動回路が前記ドライブラインに前記第2電圧を印加している間に、前記センスアンプの出力を複数回サンプリングした複数の第2サンプリング値を生成するサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた複数の第1サンプリング値を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた複数の第2サンプリング値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項5】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎にデジタル値に変換するAD変換器と、

前記AD変換器により変換された複数のデジタル値を平均化するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項6】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の電圧を印加する駆動回路と、

前記電圧の印加により前記第1及び第2静電容量に蓄積された電荷を前記第1及び第2センスラインを通してそれぞれ読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の差動出力を平均化するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項7】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第1デジタル値に変換した後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの差動出力を複数回サンプリングし、サンプリング毎に第2デジタル値に変換するAD変換器と、

前記AD変換器により変換された複数の第1デジタル値を平均化した第1検出電圧と、前記複数の第2デジタル値を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するデジタル演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項8】

第1センスラインに交差する1本以上のドライブラインに一端が接続され、他端が前記第1センスラインに接続された1個以上の第1静電容量と、第2センスラインに交差する前記ドライブラインに一端が接続され、他端が前記第2センスラインに接続された1個以上の第2静電容量との容量値を推定するためのデータを取得する静電容量検出回路であって、

前記ドライブラインに所定の第1電圧及び第2電圧をこの順番で印加する駆動回路と、

前記第1電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出した後、前記第2電圧の印加により前記第1及び第2静電容量に蓄積された電荷をそれぞれ前記第1及び第2センスラインを通して読み出すセンスアンプと、

前記駆動回路が前記ドライブラインに前記第1電圧を印加している間に、前記センスアンプの第1差動出力を複数回サンプリングした後、前記駆動回路が前記第2電圧を印加している間に、前記センスアンプの第2差動出力を複数回サンプリングするサンプリング容量回路と、

前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第1差動出力を平均化した第1検出電圧と、前記サンプリング容量回路によりサンプリングされた前記センスアンプの複数の第2差動出力を平均化した第2検出電圧との差を求めることにより前記静電容量の容量値を推定するアナログ演算回路とを備えたことを特徴とする静電容量検出回路。

【請求項9】

前記AD変換器は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングする請求項1、3、5及び7のいずれかに記載の静電容量検出回路。

【請求項10】

前記サンプリング容量回路は、非周期的なサンプリングタイミングにより前記センスアンプの出力または差動出力をサンプリングする請求項2、4、6及び8のいずれかに記載の静電容量検出回路。

【請求項11】

前記センスアンプは、集積化されており、前記センスラインに接続された入力端子を有する請求項1〜8の何れかに記載の静電容量検出回路。

【請求項12】

請求項11に記載の静電容量検出回路を備え、

前記センスラインと前記ドライブラインと前記静電容量とは、タッチパネルを構成し、

前記タッチパネルに重ねられているか、前記タッチパネルを内蔵した表示パネルをさらに備えたことを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−97401(P2013−97401A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−236525(P2011−236525)

【出願日】平成23年10月27日(2011.10.27)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月27日(2011.10.27)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]