静電容量素子、及び共振回路

【課題】電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、電気的特性を向上させることを目的とする。また、その静電容量素子を用いることにより、信頼性に優れた共振回路を提供することを目的する。

【解決手段】誘電体層3と、誘電体層3を介して積層され、静電容量をなす電極本体の中心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサにより容量素子本体2を構成する。この容量素子本体2では、該2つ以上のコンデンサが内部電極の積層方向に直列接続される。そして、容量素子本体2の側面に、静電容量をなす電極本体に電気的に接続された外部端子20〜23を形成する。

【解決手段】誘電体層3と、誘電体層3を介して積層され、静電容量をなす電極本体の中心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサにより容量素子本体2を構成する。この容量素子本体2では、該2つ以上のコンデンサが内部電極の積層方向に直列接続される。そして、容量素子本体2の側面に、静電容量をなす電極本体に電気的に接続された外部端子20〜23を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、静電容量素子に関し、特に、電極の積層方向に直列接続して配置された複数のコンデンサを備える静電容量素子に関する。また、その静電容量素子を備える共振回路に関する。

【背景技術】

【0002】

従来、本願発明者らは、内部電極の積層方向に直列接続された複数の可変容量コンデンサからなる可変容量デバイスを提案した(特許文献1)。特許文献1に記載の技術では、誘電体層を介して各可変容量コンデンサを構成する内部電極を積層する構成とすることにより、一層当たりの内部電極の数を減らすことができ、電極や容量値などの設計自由度を広げることが可能となる。

【0003】

一方、本願発明者らは、複数の内部電極を積層して形成した容量素子において、応力制御部として、静電容量を形成する容量素子本体には無関係な内部電極を設け、焼成時に生じる残留応力によって電気的特性を向上させる技術を提案している(特許文献2)。特許文献2に記載の技術では、容量素子本体の上下に内部電極を積層させて形成した応力制御部を設けることで、容量素子の焼成時における誘電体層の収縮に起因した内部応力を容量素子本体の誘電体層に発生させることができる。この結果、容量素子本体の誘電体層の比誘電率を高めることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−119482号公報

【特許文献2】WO2011/013658号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献1に記載された可変容量デバイスにおいても焼結時における誘電体層の収縮により内部応力は発生する。しかしながら、各層における内部電極の形状は、静電容量によって適宜設定されるものであり、内部応力を考慮した形状とはされていない。また、特許文献1では、直列接続された各可変容量コンデンサを構成する内部電極の面積積を変えることで、直列接続される各可変容量コンデンサ間にコンデンサを形成しない電極部分が形成され、この電極部分による電極抵抗が余分に増える問題がある。

【0006】

上述の点に鑑み、本開示は、電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、電気的特性を向上させることを目的とする。また、その静電容量素子を用いることにより、信頼性に優れた共振回路を提供することを目的する。

【課題を解決するための手段】

【0007】

本開示の静電容量素子は、容量素子本体と、外部端子とを備える。容量素子本体は、誘電体層と、誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とを備える。そして、容量素子本体では、これらの内部電極により2つ以上のコンデンサが形成され、該2つ以上のコンデンサが内部電極の積層方向に直列接続されている。また、外部端子は、容量素子本体の側面に形成され、静電容量をなす電極本体に電気的に接続されている。

【0008】

本開示の静電容量素子では、静電容量をなす電極本体の重心が積層方向の直線上に配置されるため、容量素子本体の焼成時における電極材料や誘電体材料の収縮方向が、その重心が配置された直線に向かうように発生する。これにより、内部に形成されるコンデンサの中心に残留応力が集中する。

【0009】

本開示の共振回路は、上述した静電容量素子を含む共振コンデンサと、共振コンデンサに接続された共振コイルを備える。

【発明の効果】

【0010】

本開示によれば、電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、製造時における焼成処理において発生する残留応力を増大させることができるため電気的特性の向上が図られる。

【図面の簡単な説明】

【0011】

【図1】図1Aは、本開示の第1の実施形態に係る可変容量素子の概略斜視図であり、図1Bは、可変容量素子の断面構成図である。

【図2】本開示の第1の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図3】図3Aは第1電極を上面から見たときの平面構成図であり、図3Bは、第1電極を一方の側面から見たときの構成図である。

【図4】図4Aは第2電極を上面から見たときの平面構成図であり、図4Bは第2電極を一方の側面から見たときの構成図である

【図5】図5Aは、第3電極を上面から見たときの平面構成図であり、図5Bは第3電極を一方の側面から見たときの構成図である。

【図6】本開示の第1の実施形態に係る可変容量素子の等価回路図である。

【図7】図7Aは、比較例に係る可変容量素子の外観斜視図であり、図7Bは、比較例に係る可変容量素子の断面構成である。

【図8】図8Aは、比較例の可変容量素子における第1電極を上面から見たときの平面構成図であり、図8Bは、比較例の可変容量素子における第2電極を上面から見たときの平面構成図であり、図8Cは、比較例の可変容量素子における第3電極を上面から見たときの平面構成図である。

【図9】比較例に係る可変容量素子の等価回路図である。

【図10】図10Aは、本開示の第2の実施形態に係る可変容量素子の斜視図であり、図10Bは、本開示の第2の実施形態に係る可変容量素子の断面構成図である。

【図11】本開示の第2の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図12】図12Aは第4電極を上面から見たときの平面構成図であり、図12Bは第1電極を一方の側面から見たときの構成図である。

【図13】本開示の第2の実施形態に係る可変容量素子の等価回路図である。

【図14】図14Aは、本開示の第3の実施形態に係る可変容量素子の斜視図であり、図14Bは、本開示の第3の実施形態に係る可変容量素子の断面構成図である。

【図15】本開示の第3の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図16】図16Aは第5電極を上面から見たときの平面構成図であり、図16Bは第5電極を一方の側面から見たときの構成図である。

【図17】本開示の第3の実施形態に係る可変容量素子の等価回路図である。

【図18】図18Aは、本開示の第4の実施形態に係る可変容量素子の斜視図であり、図18Bは本開示の第4の実施形態に係る可変容量素子の断面構成図である。

【図19】本開示の第4の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図20】図20Aは第6電極を上面から見たときの平面構成図であり、図20Bは第1電極を一方の側面から見たときの構成図である。

【図21】本開示の第4の実施形態に係る可変容量素子の等価回路図である。

【図22】図22Aは、本開示の第5の実施形態に係る可変容量素子の斜視図であり、図22Bは、本開示の第5の実施形態に係る可変容量素子の断面構成図である。

【図23】本開示の第5の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図24】図24Aは第7電極を上面から見たときの平面構成図であり、図24Bは、第7電極を一方の側面から見たときの構成図である。

【図25】本開示の第5の実施形態に係る可変容量素子の等価回路図である。

【図26】図26Aは、本開示の第6の実施形態に係る可変容量素子の斜視図であり、図26Bは、本開示の第6の実施形態に係る可変容量素子の断面構成図である。

【図27】本開示の第6の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図28】図28Aは第8電極を上面から見たときの平面構成図であり、図28Bは第8電極を一方の側面から見たときの構成図である。

【図29】本開示の第6の実施形態に係る可変容量素子の等価回路図である。

【図30】図30Aは、本開示の第7の実施形態に係る可変容量素子の斜視図であり、図30Bは、本開示の第7の実施形態に係る可変容量素子の断面構成図である。

【図31】本開示の第7の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図32】図32Aは本開示の第7の実施形態に係る可変容量素子の内部の回路構成図であり、図32Bは本開示の第7の実施形態に係る可変容量素子の等価回路図である。

【図33】図33Aは、本開示の第8の実施形態に係る可変容量素子の斜視図であり、図33Bは、本開示の第8の実施形態に係る可変容量素子の断面構成図である。

【図34】本開示の第8の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図35】図35Aは、本開示の第9の実施形態に係る可変容量素子の斜視図であり、図35Bは、本開示の第9の実施形態に係る可変容量素子の断面構成図である。

【図36】本開示の第10の実施形態に係る共振回路を用いた非接触ICカードの受信系回路部のブロック構成図である

【発明を実施するための形態】

【0012】

以下に、本開示の実施形態に係る静電容量素子及びそれを備える共振回路の一例を、図面を参照しながら説明する。本開示の実施形態は以下の順で説明する。また、以下に説明する実施形態では、印加電圧によって容量値が変化する可変容量素子を例として説明する。なお、本開示は以下の例に限定されるものではない。

1.第1の実施形態:直列接続した2つのコンデンサを備える可変容量素子の一例

1−1 可変容量素子の構成

1−2 製造方法

1−3 回路構成

2.第2の実施形態:直列接続した3つのコンデンサを備える可変容量素子の一例

3.第3の実施形態:直列接続した4つのコンデンサを備える可変容量素子の一例

4.第4の実施形態:直列接続した5つのコンデンサを備える可変容量素子の一例

5.第5の実施形態:直列接続した6つのコンデンサを備える可変容量素子の一例

6.第6の実施形態:直列接続した7つのコンデンサを備える可変容量素子の一例

7.第7の実施形態:並列接続及び直列接続したコンデンサを備える可変容量素子の一例

8.第8の実施形態:並列接続及び直列接続したコンデンサを備える可変容量素子の一例

9.第9の実施形態:応力制御部を備える可変容量素子の一例

10.第10の実施形態:本開示の可変容量素子を適用した共振回路の一例

【0013】

〈1.第1の実施形態〉

[1−1 可変容量素子の構成]

図1Aは、本開示の第1の実施形態に係る可変容量素子1の概略斜視図であり、図1Bは、可変容量素子1の断面構成図である。以下では、後述する内部電極の積層方向をz方向、積層方向に直交する可変容量素子1の長辺方向をx方向、積層方向に直交する可変容量素子1の短辺方向をy方向として説明する。また、可変容量素子1のxy面で構成される一方の面を「上面」、xy面で構成される他方の面を「下面」として説明する。また、可変容量素子1の上面及び下面に垂直な面を「側面」として説明する。

【0014】

図1Aに示すように、本実施形態例の可変容量素子1は、xy面が長方形とされた直方体部材で構成された可変容量素子本体2と6つの外部端子(以下、それぞれ第1外部端子20〜第3外部端子22という)とで構成されている。

【0015】

第1外部端子20及び第3外部端子22は、可変容量素子本体2のxz面で構成される長辺方向の一方の側面に互いに離間して形成されている。また、第2外部端子21は、可変容量素子本体2のxz面で構成される長辺方向の他方の側面に形成され、第1外部端子20に対向する位置に形成されている。第1外部端子20〜第3外部端子22のx方向の幅は、それぞれ、後述する第1接続電極30b〜第3接続電極32bの幅と同等の幅に形成されている。また、第1外部端子20〜第3外部端子22は、それぞれz方向において可変容量素子本体2の側面を被覆すると共に、可変容量素子本体2の上面及び下面に張り出すように形成されている。

【0016】

可変容量素子本体2は、図1Bに示すように、誘電体層3と、誘電体層3を介して積層された3つの内部電極とで構成されている。以下の説明では、便宜上、3つの内部電極をそれぞれ第1電極30〜第3電極32と称する。本実施形態例の可変容量素子本体2は、第1電極30、第2電極31、第3電極32がこの順に積層された構成とされており、第1電極30の下層に下部誘電体層4が積層され、第3電極32の上層に上部誘電体層5が積層された構成とされている。

【0017】

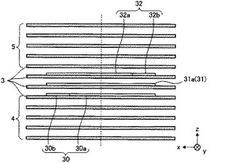

図2は、可変容量素子本体2を長辺方向の一方の側面から見たときの分解図である。また、図3Aは第1電極30を上面から見たときの平面構成図であり、図3Bは、第1電極30を一方の側面から見たときの構成図である。また、図4Aは第2電極31を上面から見たときの平面構成図であり、図4Bは第2電極31を一方の側面から見たときの構成図である。また、図5Aは、第3電極32を上面から見たときの平面構成図であり、図5Bは第3電極32を一方の側面から見たときの構成図である。図2〜図5では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0018】

図2に示すように、可変容量素子本体2は、一方の面に電極が形成されたシート状の誘電体層3が積層された構造とされており、本実施形態例では、第1電極30、第2電極31、第3電極32が下面側から上面側にかけてこの順に積層された構成とされている。シート状に形成された各誘電体層3は、平面形状が長方形とされ、長方形を為す平面上に各電極が形成された構成とされている。

【0019】

また、本実施形態例では、第1電極30の下層、及び第3電極32の上層には、電極が形成されていない誘電体層3が複数層ずつ設けられており、この誘電体層3が下部誘電体層4と上部誘電体層5を構成している。この複数層の誘電体層3で構成された下部誘電体層4及び上部誘電体層5により、可変容量素子本体2の上面及び下面に電極が露出することを防ぐことができる。

【0020】

本実施形態例では、印加電圧に応じて容量が変化する可変容量素子1を構成するため、誘電体層3は強誘電体材料で構成されている。そのような強誘電体材料としては、具体的には、イオン分極を生じる誘電体材料を用いることができる。イオン分極を生じる強誘電体材料は、イオン結晶材料からなり、プラスのイオンとマイナスのイオンの原子が変位することで電気的に分極する強誘電体材料である。このイオン分極を生じる強誘電体材料は、一般に、所定の2つの元素をA及びBとすると、化学式ABO3(Oは酸素元素)で表され、ペロブスカイト構造を有する。このような強誘電体材料としては、例えば、チタン酸バリウム(BaTiO3)、ニオブ酸カリウム(KNbO3)、チタン酸鉛(PbTiO3)等があげられる。また、誘電体層3の形成材料として、チタン酸鉛(PbTiO3)にジルコン酸鉛(PbZrO3)を混ぜ合わせたPZT(チタン酸ジルコン酸鉛)を用いてもよい。

【0021】

また、強誘電体材料として、電子分極を生じる強誘電体材料を用いてもよい。この強誘電体材料では、プラスの電荷に偏った部分と、マイナスの電荷に偏った部分とに分かれて電気双極子モーメントが生じ、分極が生じる。そのような材料として、従来、Fe2+の電荷面と、Fe3+の電荷面の形成により、分極を形成して強誘電体的特性を示す希土類鉄酸化物が報告されている。この系においては、希土類元素をREとし、鉄族元素をTMとしたときに、分子式(RE)・(TM)2・O4(O:酸素元素)で表される材料が高誘電率を有することが報告されている。なお、希土類元素としては、例えば、Y、Er、Yb、Lu(特にYと重希土類元素)が挙げられ、鉄族元素としては、例えば、Fe、Co、Ni(特にFe)が挙げられる。また、(RE)・(TM)2・O4としては、例えば、ErFe2O4、LuFe2O4、YFe2O4が挙げられる。

【0022】

第1電極30は、図3A及び図3Bに示すように、第1電極本体30aと第1接続電極30bとで構成されている。第1電極本体30aは平面形状が長方形とされ、シート状に形成された誘電体層3の面積、すなわち、可変容量素子本体2のxy面の面積よりも小さく、可変容量素子本体2の側面に露出しないように形成されている。また、第1電極本体30aは、その中心が、誘電体層3の中心に一致するように形成されている。

【0023】

第1接続電極30bは、第1電極本体30aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第1接続電極30bは、可変容量素子本体2の焼結時において第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。

【0024】

ところで、ここでいう残留応力は、可変容量素子本体2の製造時における焼成処理での電極材料と誘電体材料の収縮率の違いで発生する。したがって、第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさないためには、第1接続電極30bの面積は第1電極本体30aの面積よりも十分に小さく形成されるのが好ましい。本実施形態例では、第1接続電極30bのx方向の幅を、第1電極本体30aのx方向の幅よりも十分に小さく形成している。

そして、可変容量素子本体2の側面に露出した第1接続電極30bの端部は、第1外部端子20に電気的に接続されている。

【0025】

ここで、第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさない程度とするため、第1接続電極30aのx方向の幅は第1電極本体30aのx方向の幅の4分の1以下に設定するのが好ましい。

【0026】

第2電極31は、図4A及び図4Bに示すように、第2電極本体31aと、第2接続電極31bとで構成されている。第2電極本体31aは第1電極30を構成する第1電極本体30aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0027】

第2接続電極31bは、第2電極本体31aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第2接続電極31bは、可変容量素子本体2の焼成時において第2接続電極31b周辺に発生する残留応力が、第2電極本体31a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第2接続電極31bの面積は第2電極本体31aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第2接続電極31bのx方向の幅を、第2電極本体31aのx方向の幅よりも十分に小さく形成している。

【0028】

また、本実施形態例では、第2電極31は第1電極30をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第2接続電極31bは第1接続電極30bの対角上に位置するように形成される。そして、可変容量素子本体2の側面に露出した第2接続電極31bの端部は、第2外部端子21に電気的に接続されている。

【0029】

第3電極32は、図5A及び図5Bに示すように、第3電極本体32aと、第3接続電極32bとで構成されている。第3電極本体32aは第1電極本体30a、及び第2電極本体31aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0030】

第3接続電極32bは、第3電極本体32aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第3接続電極32bは、可変容量素子本体2の焼結時において第3接続電極32b周辺に発生する残留応力が、第3電極本体32a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第3接続電極32bの面積は第3電極本体32aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第3接続電極32bのx方向の幅を、第3電極本体32aのx方向の幅よりも十分に小さく形成している。

【0031】

また、本実施形態例では、第3電極32は第1電極30をy方向の軸を中心に180度回転させた構成とされている。すなわち、第3接続電極32bと第1接続電極30bは、可変容量素子本体2の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体2の側面に露出した第3接続電極32bの端部は、第3外部端子22に電気的に接続されている。

【0032】

第1電極30〜第3電極32は、例えば金属微粉末(Pd、Pd/Ag、Ni等)を含む導電ペーストを用いて形成することができる。なお、本実施形態例では、第1電極30〜第3電極32は同じ材料で形成する。ただし、本開示はこれに限定されず、例えば用途等に応じて、第1電極30〜第3電極32を互いに異なる材料で形成してもよい。

【0033】

以上の構成により、第1電極30〜第3電極32は、図2に示すように、同一形状の第1電極本体30a〜第3電極本体32aの各辺、及び中心がz方向に重なるように積層されている。これにより、第1電極本体30a〜第3電極本体32aの中心(重心)がz方向の延びる直線上に配置される。また、本実施形態例では、第1電極本体30a〜第3電極本体32aは、その中心が誘電体層3の中心となるように形成されている。このため、第1電極本体30a〜第3電極本体32aの中心(重心)が、可変容量素子本体2の重心を通るz方向の軸上に配置される。

【0034】

[1−2 製造方法]

以上の構成を有する可変容量素子1の製造方法の一例を説明する。まず、所望の誘電体材料からなる誘電体シートを用意する。誘電体シートは、可変容量素子本体2において各誘電体層3を構成するものであり、例えば厚さ約2.5μmとされている。これらの誘電体シートは、ペースト状にした誘電体材料をPET(ポリエチレンテレフタレート)フィルム上に所望の厚さに塗布して形成することができる。また、図3〜図5に示した第1電極30〜第3電極32の形成領域に対応する領域が開口されたマスクを用意する。

【0035】

次に、例えば、Pt、Pd、Pd/Ag、Ni、Ni合金等の金属微粉末をペースト化した導電ペーストを調整する。そして、その導電ペーストを、前段で用意したそれぞれのマスクを介して誘電体シートの一方の表面に塗布(シルク印刷)する。これにより、一方の表面に第1電極30〜第3電極32が形成された誘電体シートを作成する。このとき、各電極の電極本体の中心が誘電体シートの中心に一致するように形成する。

【0036】

そして、第1電極30〜第3電極32が形成されたそれぞれの誘電体シートを、各電極が印刷された面の向きを揃えて、所望の順番に積層する。このとき、第1電極本体30a〜第3電極本体32aの各辺、及び中心がz方向に重なるように積層する。さらに、この積層体の上下に、電極が印刷されていない誘電体シートを積層させて圧着する。

【0037】

そして、圧着した部材を還元性の雰囲気中で高温焼成して、誘電体シートと導電ペーストで形成された各電極とを一体化する。これにより、可変容量素子本体2が作製される。その後、可変容量素子本体2の側面の所定位置に、第1外部端子20〜第3外部端子22を取り付ける。本実施形態例では、このようにして可変容量素子1を作製する。

【0038】

[1−3 回路構成]

図6に、本実施形態例の可変容量素子1の等価回路を示す。本実施形態例の可変容量素子1では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。そして、第1電極30〜第3電極32は、それぞれ異なる外部端子(第1外部端子20〜第3外部端子22)に接続されている。したがって本実施形態例の可変容量素子1では、第1コンデンサC1及び第2コンデンサC2が電極の積層方向に直列接続された構成とされている。

このような構成の可変容量素子1では、第1外部端子20〜第3外部端子22に所望のDC電圧を印加することにより、第1コンデンサC1〜第3コンデンサC3の容量が可変される。

【0039】

ところで、本実施形態例の可変容量素子1では、誘電体材料と電極材料の焼結時の収縮率の違いにより残留応力が発生する。この残留応力は、各層において電極材料及び誘電体材料が収縮する方向に発生する。一方、本実施形態例の可変容量素子1では、第1コンデンサC1、及び第2コンデンサC2を構成する第1電極本体30a〜第3電極本体32aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。さらに、第1電極本体30a〜第3電極本体32aは、その中心が誘電体層3の中心に一致するように形成されている。このため、本実施形態例の可変容量素子1では、焼成時に、各電極及び誘電体層は可変容量素子本体2の重心を通るz方向の軸方向に収縮する。これにより、焼結時において発生する残留応力を、第1コンデンサC1及び第2コンデンサC2の中心に集中して発生させることができる。

【0040】

[1−3 比較例]

図7Aは、比較例に係る可変容量素子200の外観斜視図であり、図7Bは、比較例に係る可変容量素子200の断面構成である。比較例に係る可変容量素子200は、内部電極の積層方向に直列接続されたコンデンサを備える可変容量素子であり、用途や必要とする容量などに応じて各内部電極の面積を自由に変化させる構成を採用した可変容量素子である。図7A、図7Bにおいても、後述する内部電極の積層方向をz方向、積層方向に直交する可変容量素子200の長辺方向をx方向、積層方向に直交する可変容量素子200の短辺方向をy方向として説明する。

【0041】

比較例に係る可変容量素子200は、直方体部材で構成された可変容量素子本体201と3つの外部端子(以下、それぞれ第1外部端子202〜第3外部端子204という)とで構成されている。

【0042】

第1外部端子202及び第3外部端子204は、可変容量素子本体201のxz面で構成される長辺方向の一方の側面に互いに離間して形成されている。また、第2外部端子203は、可変容量素子本体201のxz面で構成される長辺方向の他方の側面に形成され、第1外部端子202に対向する位置に形成されている。

【0043】

可変容量素子本体201は、誘電体層3を介して積層された3つの内部電極(以下、第1電極206〜第3電極208という)で構成されている。比較例に係る可変容量素子本体201においても、第1電極206、第2電極207、第3電極208がこの順に積層された構成とされている。

【0044】

図8Aは、第1電極206を上面から見たときの平面構成図であり、図8Bは、第2電極207を上面から見たときの平面構成図であり、図8Cは、第3電極208を上面から見たときの平面構成図である。

【0045】

第1電極206は、図8Aに示すように矩形状に形成され、一方の端部が可変容量素子本体201のx方向の一方の側面に露出するように形成されている。そして、第1電極206は、第1外部端子202に電気的に接続されている。

【0046】

第2電極207は、図8Bに示すように、第1電極206よりも大きい面積を有する矩形状に形成され、z方向において、第1電極206と一部重なるように形成されている。また、第2電極207の一方の端部は、可変容量素子本体201のx方向の他方の側面に露出するように形成されている。そして、第2電極207は第2外部端子203に電気的に接続されている。

【0047】

第3電極208は、図8Cに示すように矩形状に形成され、一方の端部が可変容量素子本体201のx方向の一方の側面に露出するように形成されている。また、このとき、第3電極208は、第1電極206とz方向に重ならない位置であって、第2電極207の一部に重なる領域に形成されている。そして、第3電極208は、第3外部端子204に電気的に接続されている。

【0048】

比較例に係る可変容量素子200においても、第1電極206〜第3電極208や誘電体層205を、本実施形態例の可変容量素子1における電極材料及び誘電体材料で構成する。そして、比較例に係る可変容量素子1においても、z方向に積層される第1電極206〜第3電極208は、それぞれ異なる外部端子(第1外部端子202〜第3外部端子204)に接続される。このため、内部電極の積層方向に直列接続されたコンデンサが形成される。

【0049】

図9は、比較例に係る可変容量素子200の等価回路図である。図9に示すように、比較例では、第1電極206と第2電極207とにより第1コンデンサCaが形成され、第2電極207と第3電極208とにより第2コンデンサCbが形成される。そして、比較例に係る可変容量素子200では、第1電極206〜第3電極208の面積を用途や必要とする容量に応じて適宜変えることで所望の容量を得る構成とされている。

【0050】

一方、比較例に係る可変容量素子200では、第1電極206及び第3電極208が第2電極207よりも小さい面積とされ、それぞれ第2電極207の一部にのみ重なるように形成されている。したがって、このような構成の可変容量素子200では、等価回路において、図7Bのx1で示す部分の電極抵抗が余分に増えてしまう。

【0051】

さらに、比較例に係る可変容量素子200では、第1電極206〜第3電極208が異なる面積に形成され、かつ、各電極の中心位置が積層方向の異なる軸上に配置されている。したがって、焼結時の電極材料及び誘電体材料の収縮に起因して発生する残留応力は、可変容量素子本体201内部で様々な方向に向くように発生する。このため、残留応力に起因する静電容量の増大などの効果が得られない。

【0052】

これに比較して、本実施形態例の可変容量素子1では、第1コンデンサC1及び第2コンデンサC2を構成する第1電極本体30a〜第3電極本体32aは全て同一形状とされ、かつ、各辺及び中心位置が積層方向に重なるように積層されている。したがって、各コンデンサ間の抵抗は、各電極層の厚さ方向に発生する抵抗のみとなり、隣接するコンデンサ間の抵抗値を最小に抑えることができる。

【0053】

また、本実施形態例では、第1電極本体30a〜第3電極本体32aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、本実施形態例の可変容量素子1では、焼結時において発生する残留応力を、第1コンデンサC1及び第2コンデンサC2の中心に集中して発生させることができる。この結果、残留応力により静電容量の増大や、容量可変率の増加など、電気的特性の向上が図られる。

【0054】

本実施形態例の可変容量素子1では、第1電極本体30a〜第3電極本体32aの中心が誘電体層3の中心に一致するように形成されている。これにより、第1電極本体30a〜第3電極本体32aの中心は、誘電体層205と内部電極との積層体である可変容量素子本体201の重心を通る直線上にくる。このように、第1電極本体30a〜第3電極本体32aの重心を可変容量素子本体201の重心を通る直線上となるように設計することで、より大きな残留応力を発生させることができる。

【0055】

〈2.第2の実施形態〉

次に、本開示の第2の実施形態に係る可変容量素子について説明する。図10Aは、本実施形態例の可変容量素子51の斜視図であり、図10Bは、本実施形態例の可変容量素子51の断面構成図である。本実施形態例の可変容量素子51は、第1の実施形態に係る可変容量素子1の第3電極32上部に、さらに第4電極を備える構成とされている。

図10A及び図10Bにおいて、図1A及び図1Bに対応する部分には同一符号を付し重複説明を省略する。

【0056】

図10Aに示すように、本実施形態例の可変容量素子51は、直方体部材で構成された可変容量素子本体52と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

【0057】

第4外部端子23は、可変容量素子本体52のxz面で構成される長辺方向の他方の側面に形成され、xy面でみたときに、第1外部端子20に対向する位置に形成されている。第4外部端子23のx方向の幅は、後述する第4接続電極33bの幅と同等の幅に形成されている。また、第4外部端子23は、第1外部端子20〜第3外部端子22と同様、z方向において可変容量素子本体52の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0058】

図11は、可変容量素子本体52を長辺方向の一方の側面から見たときの分解図である。また、図12Aは第4電極33を上面から見たときの平面構成図であり、図12Bは、第1電極30を一方の側面から見たときの構成図である。図11及び図12では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0059】

可変容量素子本体52は、第1電極30〜第4電極33が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第4電極33の上層に上部誘電体層5が積層された構成とされている。

【0060】

第4電極33は、図12A及び図12Bに示すように、第4電極本体33aと、第4接続電極33bとで構成されている。第4電極本体33aは第1電極本体30a〜第3電極本体32aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0061】

第4接続電極33bは、第4電極本体33aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体52の側面に露出するように形成されている。また、第4接続電極33bは、可変容量素子本体52の焼結時において第4接続電極33b周辺に発生する残留応力が、第4電極本体33a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第4接続電極33bの面積は第4電極本体33aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第4接続電極33bのx方向の幅を、第4電極本体33aのx方向の幅よりも十分に小さく形成している。

【0062】

また、本実施形態例では、第4電極33は第3電極32をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第4接続電極33bは第3接続電極32bの対角上に位置し、また、第4接続電極33bと第2接続電極31bは可変容量素子本体52の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体52の側面に露出した第4接続電極33bの端部は、第4外部端子23に電気的に接続されている。

【0063】

第4電極33を構成する電極材料としては、第1電極30〜第3電極32を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子51も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第4電極33は第3電極32をz方向の軸を中心として180度回転させた形状とされている。このため、第4電極33を誘電体シート状に形成する場合には、第3電極32とは同一のマスクを用いて形成することができる。

【0064】

図13に、本実施形態例の可変容量素子の等価回路を示す。本実施形態例の可変容量素子51では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。そして、第1電極30〜第4電極33は、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。したがって本実施形態例の可変容量素子51では、第1コンデンサC1〜第3コンデンサC3が電極の積層方向に直列接続された構成とされている。

【0065】

本実施形態例の可変容量素子51においても、第1電極本体30a〜第4電極本体33aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0066】

〈3.第3の実施形態〉

次に、本開示の第3の実施形態に係る可変容量素子について説明する。図14Aは、本実施形態例の可変容量素子61の斜視図であり、図14Bは、本実施形態例の可変容量素子61の断面構成図である。本実施形態例の可変容量素子61は、第2の実施形態に係る可変容量素子51の第4電極33上部に、さらに第5電極34を備える構成とされている。

図14A及び図14Bにおいて、図10A及び図10Bに対応する部分には同一符号を付し重複説明を省略する。

【0067】

図14Aに示すように、本実施形態例の可変容量素子61は、直方体部材で構成された可変容量素子本体62と第1外部端子20〜第5外部端子24の4つの外部端子で構成されている。

第5外部端子24は、可変容量素子本体62のxz面で構成される長辺方向の一方の側面に形成され、第1外部端子20及び第3外部端子22と離間した置に形成されている。第5外部端子24のx方向の幅は、後述する第5接続電極34bの幅と同等の幅に形成されている。また、第5外部端子24は、第1外部端子20〜第4外部端子23と同様、z方向において可変容量素子本体62の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0068】

図15は、可変容量素子本体62を長辺方向の一方の側面から見たときの分解図である。また、図16Aは第5電極34を上面から見たときの平面構成図であり、図16Bは、第5電極34を一方の側面から見たときの構成図である。図15及び図16は、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0069】

可変容量素子本体62は、第1電極30〜第5電極34が誘電体層を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第5電極34の上層に上部誘電体層5が積層された構成とされている。

【0070】

第5電極34は、図16A及び図16Bに示すように、第5電極本体34aと、第5接続電極34bとで構成されている。第5電極本体34aは第1電極本体30a〜第4電極本体33aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0071】

第5接続電極34bは、第5電極本体34aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体62の側面に露出するように形成されている。また、第5接続電極34bは、可変容量素子61の焼結時において第5接続電極34b周辺に発生する残留応力が、第5電極本体34a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第5接続電極34bの面積は第5電極本体34aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第5接続電極34bのx方向の幅を第5電極本体34aのx方向の幅よりも十分に小さく形成している。

【0072】

また、本実施形態例では、第5接続電極34bは第1接続電極30b及び第3接続電極32bと可変容量素子本体62の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体62の側面に露出した第5接続電極34bの端部は、第5外部端子24に電気的に接続されている。

【0073】

第5電極34を構成する電極材料としては、第1電極30〜第4電極33を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子61も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0074】

図17に、本実施形態例の可変容量素子61の等価回路を示す。本実施形態例の可変容量素子61では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。そして、第1電極30〜第5電極34は、それぞれ異なる外部端子(第1外部端子20〜第5外部端子24)に接続されている。したがって本実施形態例の可変容量素子61では、第1コンデンサC1〜第4コンデンサC4が電極の積層方向に直列接続された構成とされている。

【0075】

本実施形態例の可変容量素子61においても、第1電極本体30a〜第5電極本体34aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0076】

〈4.第4の実施形態〉

次に、本開示の第4の実施形態に係る可変容量素子について説明する。図18Aは、本実施形態例の可変容量素子71の斜視図であり、図18Bは、本実施形態例の可変容量素子71の断面構成図である。本実施形態例の可変容量素子71は、第3の実施形態に係る可変容量素子61の第5電極34上部に、さらに第6電極を備える構成とされている。

図18A及び図18Bにおいて、図14A及び図14Bに対応する部分には同一符号を付し重複説明を省略する。

【0077】

図18Aに示すように、本実施形態例の可変容量素子71は、直方体部材で構成された可変容量素子本体72と第1外部端子20〜第6外部端子25の6つの外部端子で構成されている。

第6外部端子25は、可変容量素子本体72のxz面で構成される長辺方向の他方の側面に形成され、第2外部端子21及び第4外部端子23と離間した位置に形成されている。第6外部端子25のx方向の幅は、後述する第6接続電極35bの幅と同等の幅に形成されている。また、第6外部端子25は、第1外部端子20〜第5外部端子24と同様、z方向において可変容量素子本体72の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0078】

図19は、可変容量素子本体72を長辺方向の一方の側面から見たときの分解図である。また、図20Aは第6電極35を上面から見たときの平面構成図であり、図20Bは、第6電極35を一方の側面から見たときの構成図である。図19及び図20では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0079】

可変容量素子本体72は、第1電極30〜第6電極35が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第6電極35の上層に上部誘電体層5が積層された構成とされている。

【0080】

第6電極35は、図20A及び図20Bに示すように、第6電極本体35aと、第6接続電極35bとで構成されている。第6電極本体35aは第1電極本体30a〜第5電極本体34aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0081】

第6接続電極35bは、第6電極本体35aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体72の側面に露出するように形成されている。また、第6接続電極35bは、可変容量素子本体72の焼結時において第6接続電極35b周辺に発生する残留応力が、第6電極本体35a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第6接続電極35bの面積は第6電極本体35aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第6接続電極35bのx方向の幅を、第6電極本体35aのx方向の幅よりも十分に小さく形成している。

【0082】

また、本実施形態例では、第6電極35は第5電極34をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第6接続電極35bは第5接続電極34bの対角上に位置する。また、第6接続電極35b、第4接続電極33b、及び第2接続電極31bは可変容量素子本体の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体72の側面に露出した第6接続電極35bの端部は、第6外部端子25に電気的に接続されている。

【0083】

第6電極35を構成する電極材料としては、第1電極30〜第5電極34を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子71も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第6電極35は第5電極34をz方向の軸を中心として180度回転させた形状とされているため、第6電極35を誘電体シート状に形成する場合には、第5電極34を形成するためのマスクと同一のマスクを用いて形成することができる。

【0084】

図21に、本実施形態例の可変容量素子71の等価回路を示す。本実施形態例の可変容量素子71では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。そして、第1電極30〜第6電極35は、それぞれ異なる外部端子(第1外部端子20〜第6外部端子25)に接続されている。したがって本実施形態例の可変容量素子71では、第1コンデンサC1〜第5コンデンサC5が電極の積層方向に直列接続された構成とされている。

【0085】

本実施形態例の可変容量素子71においても、第1電極本体30a〜第6電極本体35aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0086】

〈5.第5の実施形態〉

次に、本開示の第5の実施形態に係る可変容量素子について説明する。図22Aは、本実施形態例の可変容量素子81の斜視図であり、図22Bは、本実施形態例の可変容量素子の断面構成図である。本実施形態例の可変容量素子は、第4の実施形態に係る可変容量素子71の第6電極35上部に、さらに第7電極36を備える構成とされている。

図22A及び図22Bにおいて、図18A及び図18Bに対応する部分には同一符号を付し重複説明を省略する。

【0087】

図22Aに示すように、本実施形態例の可変容量素子81は、直方体部材で構成された可変容量素子本体82と第1外部端子20〜第7外部端子26の7つの外部端子で構成されている。

第7外部端子26は、可変容量素子本体82のxz面で構成される長辺方向の一方の側面に形成され、第1外部端子20、第3外部端子22、及び第5外部端子24と離間した位置に形成されている。第7外部端子26のx方向の幅は、後述する第7接続電極36bの幅と同等の幅に形成されている。また、第7外部端子26は、第1外部端子20〜第6外部端子25と同様、z方向において可変容量素子本体82の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0088】

図23は、可変容量素子本体82を長辺方向の一方の側面から見たときの分解図である。また、図24Aは第7電極36を上面から見たときの平面構成図であり、図24Bは、第7電極36を一方の側面から見たときの構成図である。図23及び図24では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0089】

可変容量素子本体82は、第1電極30〜第7電極36が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第7電極36の上層に上部誘電体層5が積層された構成とされている。

【0090】

第7電極36は、図24A及び図24Bに示すように、第7電極本体36aと、第7接続電極36bとで構成されている。第7電極本体36aは第1電極本体30a〜第7電極本体36aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0091】

第7接続電極36bは、第7電極本体36aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体82の側面に露出するように形成されている。また、第7接続電極36bは、可変容量素子81の焼結時において第7接続電極36b周辺に発生する残留応力が、第7電極本体36a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第7接続電極36bの面積は第7電極本体36aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第7接続電極36bのx方向の幅を、第7電極本体36aのx方向の幅よりも十分に小さく形成している。

【0092】

また、本実施形態例では、第7接続電極36bは、第1接続電極30b、第3接続電極32b、及び第5接続電極34bと、可変容量素子本体82の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体82の側面に露出した第7接続電極36bの端部は、第7外部端子26に電気的に接続されている。

【0093】

第7電極36を構成する電極材料としては、第1電極30〜第7電極36を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子81も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0094】

図25に、本実施形態例の可変容量素子81の等価回路を示す。本実施形態例の可変容量素子81では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。また、z方向に積層される第6電極本体35a及び第7電極本体36aにより第6コンデンサC6が形成される。そして、第1電極30〜第7電極36は、それぞれ異なる外部端子(第1外部端子20〜第7外部端子26)に接続されている。したがって本実施形態例の可変容量素子81では、第1コンデンサC1〜第7コンデンサC7が電極の積層方向に直列接続された構成とされている。

【0095】

本実施形態例の可変容量素子81においても、第1電極本体30a〜第7電極本体36aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0096】

〈6.第6の実施形態〉

次に、本開示の第6の実施形態に係る可変容量素子について説明する。図26Aは、本実施形態例の可変容量素子91の斜視図であり、図26Bは、本実施形態例の可変容量素子91の断面構成図である。本実施形態例の可変容量素子91は、第5の実施形態に係る可変容量素子81の第7電極36上部に、さらに第8電極37を備える構成とされている。

図26A及び図26Bにおいて、図22A及び図22Bに対応する部分には同一符号を付し重複説明を省略する。

【0097】

図26Aに示すように、本実施形態例の可変容量素子91は、直方体部材で構成された可変容量素子本体92と第1外部端子20〜第8外部端子27の8つの外部端子で構成されている。

第8外部端子27は、可変容量素子本体92のxz面で構成される長辺方向の他方の側面に形成され、第2外部端子21、第4外部端子23、及び第6外部端子25と離間した位置に形成されている。第8外部端子27のx方向の幅は、後述する第8接続電極37bの幅と同等の幅に形成されている。また、第8外部端子27は、第1外部端子20〜第7外部端子26と同様、z方向において可変容量素子本体92の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0098】

図27は、可変容量素子本体92を長辺方向の一方の側面から見たときの分解図である。また、図28Aは第8電極37を上面から見たときの平面構成図であり、図28Bは、第8電極37を一方の側面から見たときの構成図である。図27及び図28では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0099】

可変容量素子本体92は、第1電極30〜第8電極37が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第8電極37の上層に上部誘電体層5が積層された構成とされている。

【0100】

第8電極37は、図28A及び図28Bに示すように、第8電極本体37aと、第8接続電極37bとで構成されている。第8電極本体38aは第1電極本体30a〜第8電極本体37aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0101】

第8接続電極37bは、第8電極本体37aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体92の側面に露出するように形成されている。また、第8接続電極37bは、可変容量素子本体92の焼結時において第8接続電極37b周辺に発生する残留応力が、第8電極本体37a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第8接続電極37bの面積は第8電極本体37aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第8接続電極37bのx方向の幅を、第8電極本体37aのx方向の幅よりも十分に小さく形成している。

【0102】

また、本実施形態例では、第8電極37は第7電極36をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第8接続電極38bは第7接続電極36bの対角上に位置している。そして、第8接続電極37bは、第6接続電極35b、第4接続電極33b、及び第2接続電極31bが形成された可変容量素子本体92の側面と同一の側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体92の側面に露出した第8接続電極37bの端部は、第8外部端子27に電気的に接続されている。

【0103】

第8電極37を構成する電極材料としては、第1電極30〜第8電極37を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子91も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第8電極37は第7電極36をz方向の軸を中心として180度回転させた形状とされているため、第8電極37を誘電体シート状に形成する場合には、第7電極36を形成するためのマスクと同一のマスクを用いて形成することができる。

【0104】

図29に、本実施形態例の可変容量素子91の等価回路を示す。本実施形態例の可変容量素子91では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。また、z方向に積層される第6電極本体35a及び第7電極本体36aにより第6コンデンサC6が形成される。また、z方向に積層される第7電極本体36a及び第8電極本体37aにより第7コンデンサC7が形成される。そして、第1電極30〜第8電極37は、それぞれ異なる外部端子(第1外部端子20〜第8外部端子27)に接続されている。したがって本実施形態例の可変容量素子91では、第1コンデンサC1〜第7コンデンサC7が電極の積層方向に直列接続された構成とされている。

【0105】

本実施形態例の可変容量素子91においても、第1電極本体30a〜第8電極本体37aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0106】

〈7.第7の実施形態〉

次に、本開示の第7の実施形態に係る可変容量素子について説明する。図30Aは、本実施形態例の可変容量素子101の斜視図であり、図30Bは、本実施形態例の可変容量素子101の断面構成図である。本実施形態例の可変容量素子101は、第1電極30〜第4電極33からなる積層体を2層積層した構成を有する例である。図30A及び図30Bにおいて、図10A及び図10Bに対応する部分には同一符号を付し、重複説明を省略する。

【0107】

図30Aに示すように、本実施形態例の可変容量素子101は、直方体部材で構成された可変容量素子本体102と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体102は、第1積層体6と、第2積層体7と、下部誘電体層4と、上部誘電体層5とで構成されている。

【0108】

図31は、可変容量素子本体102を長辺方向の一方の側面から見たときの分解図である。図31では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。図31に示すように、第1積層体6は、第1電極30、第2電極31、第3電極32、及び第4電極33が誘電体層3を介して下面側からこの順に積層された構成とされている。また、第2積層体7は、第1積層体6のz方向の上部に積層され、第4電極33、第3電極32、第2電極31、及び第1電極30が誘電体層3を介して下面側から順に積層された構成とされている。すなわち、第1積層体6と第2積層体7とでは、下面側から上面側に向けて積層される第1電極30〜第4電極33の積層の順番が逆になるように構成されている。また、第1積層体6の下層には、下部誘電体層4が形成され、第2積層体7の上層には、上部誘電体層5が積層されている。

【0109】

第1積層体6及び第2積層体7に形成された2つの第1電極30は第1外部端子20に接続され、第1積層体6及び第2積層体7に形成された2つの第2電極31は、第2外部端子21に接続される。また、第1積層体6及び第2積層体7に形成された2つの第3電極32は第3外部端子22に接続され、第1積層体6及び第2積層体7に形成された2つの第4電極33は第4外部端子23に接続される。

本実施形態例の可変容量素子101も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0110】

図32Aに、本実施形態例の可変容量素子101の内部の回路構成を示し、図32Bに本実施形態例の可変容量素子101の等価回路を示す。本実施形態例の可変容量素子101では、第1積層体6において、第1コンデンサC1、第2コンデンサC2、第3コンデンサC3が下面側から上面側に向かって順に形成される。一方、第2積層体7においては、第3コンデンサC3、第2コンデンサC2、第1コンデンサC1が下面側から上面側に向かって順に形成される。このとき、第1積層体6と第2積層体7との境界部分に形成された隣接する2つの第4電極33は同一の外部端子(第4外部端子23)に接続され、同電位とされるため、この2つの第4電極33間にはコンデンサは形成されない。

【0111】

そして、第1積層体6に形成される第1電極30〜第4電極33は、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。また、第2積層体7に形成される第1電極30〜第4電極33も、同様に、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。したがって、図32Aに示すように、第1積層体6、及び第2積層体7では、それぞれ、第1コンデンサC1〜第3コンデンサC3が電極の積層方向に直列接続された構成とされている。

【0112】

一方、第1積層体6に形成される第1電極30と第2積層体7に形成される第1電極30は、それぞれ共通の第1外部端子20に接続されている。また、第1積層体6に形成される第2電極31と第2積層体7に形成される第2電極31は、それぞれ共通の第2外部端子21に接続されている。また、第1積層体6に形成される第3電極32と第2積層体7に形成される第3電極32は、それぞれ共通の第3外部端子22に接続されている。また、第1積層体6に形成される第4電極33と第2積層体7に形成される第4電極33は、それぞれ共通の第4外部端子23に接続されている。したがって、第1積層体6に形成される第1コンデンサC1と第2積層体7に形成される第1コンデンサC2は並列接続されている。同様に、第1積層体6に形成される第2コンデンサC2と第2積層体7に形成される第2コンデンサC2は並列接続され、第1積層体6に形成される第3コンデンサC3と第2積層体7に形成される第3コンデンサC3は並列接続されている。

【0113】

したがって、この可変容量素子101を等価回路で表すと、図32Bに示すように、2つの第1コンデンサC1からなるコンデンサC1’と、2つの第2コンデンサC2からなるコンデンサC2’と、2つの第3コンデンサC3からなるコンデンサC3’が直列接続された回路となる。

【0114】

本実施形態例の可変容量素子101においても、第1積層体6及び第2積層体7において第1電極本体30a〜第4電極本体33aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。また、異なる外部端子に接続される複数の電極が誘電体層3を介して積層された積層体を複数積層し、かつ、それらの積層体を電気的に並列接続することにより、各コンデンサの容量を大きくすることができる。

【0115】

〈8.第8の実施形態〉

次に、本開示の第8の実施形態に係る可変容量素子について説明する。図33Aは、本実施形態例の可変容量素子111の斜視図であり、図33Bは、本実施形態例の可変容量素子111の断面構成図である。また、図34は、可変容量素子本体112を長辺方向の一方の側面から見たときの分解図である。本実施形態例の可変容量素子111は、第1電極30〜第4電極33からなる積層体を2層積層した構成を有する例である。図33及び図34において、図30及び図31に対応する部分には同一符号を付し、重複説明を省略する。

【0116】

図33Aに示すように、本実施形態例の可変容量素子111は、直方体部材で構成された可変容量素子本体112と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体112は、第1積層体6と、第2積層体7と、下部誘電体層4と、上部誘電体層5とで構成されている。また、本実施形態例では、第1積層体6の最上層に形成される第4電極33が、第2積層体7の最下層に形成される第4電極33を兼ねる構成とされている。本実施形態例の可変容量素子111も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0117】

本実施形態例の可変容量素子111の回路構成は、図32A及び図32Bに示した第7の実施形態と同様の回路構成となる。本実施形態例の可変容量素子111では、第1積層体6の最上層に形成される第4電極33が第2積層体7の最下層に形成される第4電極33を兼ねる構成とすることで、第7の実施形態に比較して可変容量素子111の低背化が図られ、小型化が可能となる。その他、第1の実施形態と同様の効果を得ることができる。

【0118】

〈9.第9の実施形態〉

次に、本開示の第9の実施形態に係る可変容量素子について説明する。図35Aは、本実施形態例の可変容量素子121の斜視図であり、図35Bは、本実施形態例の可変容量素子121の断面構成図である。本実施形態例の可変容量素子121は、電極の積層方向に応力制御部を設ける例である。図35A及び図35Bにおいて、図33A及び図33Bに対応する部分には同一符号を付し、重複説明を省略する。

【0119】

図35Aに示すように、本実施形態例の可変容量素子121は、直方体部材で構成された可変容量素子本体122と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体122は、第1積層体6と、第1応力制御部8と、第2応力制御部9と、下部誘電体層4と、上部誘電体層5とで構成されている。

【0120】

第1応力制御部8は、第1積層体6の下層側に形成され、誘電体層3を介して複数積層された第1電極30で構成されている。第1応力制御部8を構成する第1電極30は、第1積層体6の第1電極30と同様、第1外部端子20に接続されている。したがって、第1積層体6の最下層に形成される第1電極30と第1応力制御部8を構成する第1電極30とは同電位とされるため、この電極間にコンデンサは形成されない。さらに、第1応力制御部8に形成される複数の第1電極30も同電位とされるため、第1応力制御部8ではコンデンサが形成されない。

【0121】

第2応力制御部9は、第1積層体6の上層側に形成され、誘電体層3を介して複数積層された第4電極33で構成されている。第2応力制御部9を構成する第4電極33は、第1積層体6を構成する第4電極33と同様、第4外部端子23に接続されている。したがって、第1積層体6の最上層に形成される第4電極33と、第2応力制御部9を構成する第4電極33とは同電位とされるため、この電極間にコンデンサは形成されない。さらに、第2応力制御部9に形成される複数の第4電極33も同電位とされるため、第2応力制御部9ではコンデンサが形成されない。

【0122】

そして、本実施形態例の可変容量素子121では、第1応力制御部8、第1積層体6、及び第2応力制御部9に形成される内部電極は、その電極本体の形状が同一とされ、各辺、及び中心がz方向に重なるように積層されている。本実施形態例の可変容量素子121も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0123】

本実施形態例の可変容量素子121の等価回路は図13に示した等価回路と同様の構成となる。すなわち、本実施形態例では、第1積層体6に形成された第1電極30〜第4電極33でのみコンデンサが形成される。したがって、本実施形態例の可変容量素子121においても、図13と同様、第1コンデンサC1、第2コンデンサC2、第3コンデンサC3がこの順に直列接続された回路となる。

【0124】

本実施形態例の可変容量素子121では、第1応力制御部8及び第2応力制御部9においても、電極材料と誘電体材料の焼成時の収縮率の違いにより、残留応力が発生している。したがって、第1応力制御部8及び第2応力制御部9に発生した残留応力が第1積層体6に形成される第1コンデンサC1〜第3コンデンサC3に影響し、応力制御部を形成しない場合に比較して、容量値の増加、及び容量可変率の増加を図ることができる。

【0125】

また、本実施形態例においては、第1応力制御部8、第2応力制御部9、及び第1積層体6に形成される内部電極の電極本体の形状が同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0126】

ところで、第1〜第9の実施形態例では、第1電極30〜第4電極33のそれぞれにおいて、接続電極のx方向の幅を電極本体のx方向の幅よりも十分に小さく形成したが適宜変更可能である。例えば、DC電圧のみが印加される電極については、接続電極における電気抵抗が高くても良いため、電極本体に対する接続電極の幅を小さく形成しても良いが、AC電流が流れる電極については、電気抵抗の観点から接続電極の幅を大きく形成した方が好ましい。また、残留応力が、応力制御部や多層に積層された電極で支配される場合には、最外側の電極の接続電極の幅は広くしてもよい。また、接続電極の電極抵抗を下げる方法としては、電極幅を広くするほか、長さを短くしたり、厚さを厚くしたりするなどの方法が挙げられるが、これらを組み合わせてより好ましい形態を採ることができる。

【0127】

上述した第1〜第9の実施形態では、容量素子として印加する電圧に応じて容量が変化する可変容量素子を例に挙げて説明したが、本開示はこれに限定されない。上記第1〜第9の実施形態で説明した構成は、入力信号の種類及びその信号レベルに関係なく容量がほとんど変化しない容量素子(以下、定容量素子という)に対しても同様に適用可能である。

【0128】

ただし、この場合には、誘電体層は比誘電率の低い常誘電体材料で形成される。常誘電体材料としては、例えば、紙、ポリエチレンテレフタレート、ポリプロピレン、ポリフェニレンサルファイド、ポリスチレン、TiO2、MgTiO2、MgTiO3、SrMgTiO2、Ai2O3、Ta2O5等を用いることができる。このような定容量素子においても、上記第1の実施形態の可変容量素子と同様にして作製することができる。

【0129】

また、上述の実施形態では、各内部電極の中心が積層方向の直線上に配置される構成としたが、製造時の合わせずれ程度のずれも本開示に含むものとする。さらに、本実施形態例では、各内部電極の中心を誘電体層の中心に合わせる構成としたが、製造時の合わせずれ程度のずれも本開示に含むものとする。

【0130】

また、上述の第1〜第9の実施形態では、内部電極の形状を長方形状としたが、これに限られるものではなく、その他多角形状や、円形状、楕円形状とすることもできる。さらに、本開示の容量素子としては、上述の第1〜第9の実施形態を組み合わせて構成してもよく、趣旨を逸脱しない範囲ないでの種々の変形が可能である。

【0131】

なお、本開示に好適な静電容量素子の容量C(F)は、使用する周波数f(Hz)にも依存する。本開示はインピーダンスZ(オーム)(Z=1/2πfc)が2オーム以上、好ましくは15オーム以上、更に好ましくは、100オーム以上となる容量C(F)である容量素子に好適である。

【0132】

〈10.第10の実施形態:共振回路〉

次に、本発明の第10の実施形態に係る共振回路について説明する。本実施形態例は本発明の容量素子を共振回路に適用した例であり、特に、第1の実施形態における可変容量素子1を適用した例を示す。また、本実施形態例では、共振回路を非接触ICカードに用いた例を示す。

【0133】

図36は、本実施形態例の共振回路を用いた非接触ICカード130の受信系回路部のブロック構成図である。なお、本実施形態例では、説明を簡略化するために、信号の送信系(変調系)回路部は省略している。送信系回路部の構成は、従来の非接触ICカード等と同様の構成である。

【0134】

非接触ICカードは、図36に示すように、受信部131(アンテナ)と、整流部132と、信号処理部133とを備える。

【0135】

受信部131は、共振コイル134及び共振コンデンサ135からなる共振回路で構成され、非接触ICカード130のR/W(不図示)から送信される信号をこの共振回路で受信する。なお、図36では、共振コイル134をそのインダクタンス成分134a(L)と抵抗成分134b(r:数オーム程度)とに分けて図示している。

【0136】

共振コンデンサ135は、容量Coのコンデンサ135aと、受信信号の電圧値(受信電圧値)に応じて容量Cvが変化する可変容量素子1とが並列に接続されている。すなわち、本実施形態では、従来のアンテナ(共振コイル134とコンデンサ135aとからなる共振回路)に可変容量素子1を並列接続した構成となる。また、本実施形態例では、可変容量素子1として図1に示す可変容量素子を用いる例とする。

【0137】

コンデンサ135aは、従来のアンテナと同様に、常誘電体材料で形成されたコンデンサを用いる。常誘電体材料で形成されたコンデンサ135aは、比誘電率が低く、入力電圧の種類(交流または直流)及びその電圧値に関係なくその容量はほとんど変化しない。それゆえ、コンデンサ135aは、入力信号に対して非常に安定した特性を有する。従来のアンテナでは、アンテナの共振周波数がずれないようにするために、このような入力信号に対して安定性の高い常誘電体材料で形成されたコンデンサを用いる。

【0138】

なお、実際の回路上では、共振コイル134のインダクタンス成分Lのばらつきや信号処理部133内の集積回路の入力端子の寄生容量などによる受信部131の容量変動(数pF程度)が存在し、その変動量は非接触ICカード130毎に異なる。それゆえ、本実施形態では、これらの影響を抑制(補正)するために、コンデンサ135aの電極パターンをトリミングして容量Coを適宜調整している。

【0139】

整流部132は、整流用ダイオード136と整流用コンデンサ137とからなる半波整流回路で構成され、受信部131で受信した交流電圧を直流電圧に整流して出力する。

【0140】

信号処理部133は、主に半導体素子の集積回路(LSI:Large Scale Integration)で構成され、受信部131で受信した交流信号を復調する。信号処理部133内のLSIは整流部132から供給される直流電圧により駆動される。なお、LSIとしては、従来の非接触ICカードと同様のものを用いることができる。

【0141】

本実施形態例では、受信部に用いる可変容量素子1は積層される内部電極の中心(重心)が積層方向の直線上に配置されるため、より大きな残留応力が得られる。これにより、電気的特性が向上し、より低い電圧で大きな可変幅が得られる。また可変幅が大きくなる分共振コンデンサへの変化負担を減らせるため共振コンデンサの誘電体を厚くすれば耐圧が向上し、より大きなAC電圧を扱うことが可能となる。

【0142】

本実施形態例では、共振回路の可変容量素子として、第1の実施形態の可変容量素子1を用いる例としたが、第2〜第9の実施形態の可変容量素子を用いる例としてもよい。

【0143】

また、本開示は、以下の構成をとることができる。

【0144】

(1)

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子。

【0145】

(2)

前記内部電極の中心は、前記容量素子本体の重心を通る直線上に配置されている

(1)に記載の静電容量素子。

【0146】

(3)

前記内部電極は、前記電極本体と、前記電極本体と前記外部端子とを電気的に接続するための接続電極とで構成され、積層される複数の電極本体は同一形状に形成されている

(1)又は(2)に記載の静電容量素子。

【0147】

(4)

前記容量素子本体は、積層方向に直列接続されたコンデンサを構成する複数の内部電極を備える積層体を積層方向に複数個備え、異なる積層体に形成されたコンデンサ同士が並列接続されている

(1)〜(3)のいずれかに記載の静電容量素子。

【0148】

(5)

隣接する2つの積層体間において、一方の積層体の最上層に形成される内部電極が、他方の積層体の最下層に形成される内部電極を兼ねる

(4)に記載の静電容量素子。

【0149】

(6)

前記直列接続されたコンデンサの上層及び/又は下層には、誘電体層を介して積層され、コンデンサを形成しない電極本体が積層方向の直線上に配置された複数の内部電極からなる応力制御部を備え、

前記応力制御部に形成されるコンデンサを形成しない電極本体の重心と前記コンデンサを構成する電極本体の中心が直線上に配置されている

(1)〜(5)のいずれかに記載の静電容量素子。

【0150】

(7)

前記応力制御部の内部電極は、コンデンサを形成する内部電極のうち最隣接の内部電極と同電位とされている

(6)に記載の静電容量素子。

【0151】

(8)

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【符号の説明】

【0152】

1,51,61,71,81,91,10,111,121・・・可変容量素子、2,52,62,72,82,92,102,112・・・可変容量素子本体、3・・・誘電体層、4・・・下部誘電体層、5・・・上部誘電体層、6・・・第1積層体、7・・・第2積層体、8・・・第1応力制御部、9・・・第2応力制御部、20・・・第1外部端子、21・・・第2外部端子、22・・・第3外部端子、23・・・第4外部端子、24・・・第5外部端子、25・・・第6外部端子、26・・・第7外部端子、27・・・第8外部端子、30・・・第1電極、30a・・・第1電極本体、30b・・・第1接続電極、31・・・第2電極、31a・・・第2電極本体、31b・・・第2接続電極、32・・・第3電極、32a・・・第3電極本体、32b・・・第3接続電極、33・・・第4電極、33a・・・第4電極本体、33b・・・第4接続電極、34・・・第5電極、34a・・・第5電極本体、34b・・・第5接続電極、35・・・第6電極、35a・・・第6電極本体、35b・・・第6接続電極、36・・・第7電極、36a・・・第7電極本体、36b・・・第7接続電極、37・・・第8電極、37a・・・第8電極本体、37b・・・第8接続電極、38a・・・第8電極本体、38b・・・第8接続電極、130・・・非接触ICカード、131・・・受信部、132・・・整流部、133・・・信号処理部、134・・・共振コイル、134a・・・インダクタンス成分、134b・・・抵抗成分、135・・・共振コンデンサ、135a・・・コンデンサ、136・・・整流用ダイオード

【技術分野】

【0001】

本発明は、静電容量素子に関し、特に、電極の積層方向に直列接続して配置された複数のコンデンサを備える静電容量素子に関する。また、その静電容量素子を備える共振回路に関する。

【背景技術】

【0002】

従来、本願発明者らは、内部電極の積層方向に直列接続された複数の可変容量コンデンサからなる可変容量デバイスを提案した(特許文献1)。特許文献1に記載の技術では、誘電体層を介して各可変容量コンデンサを構成する内部電極を積層する構成とすることにより、一層当たりの内部電極の数を減らすことができ、電極や容量値などの設計自由度を広げることが可能となる。

【0003】

一方、本願発明者らは、複数の内部電極を積層して形成した容量素子において、応力制御部として、静電容量を形成する容量素子本体には無関係な内部電極を設け、焼成時に生じる残留応力によって電気的特性を向上させる技術を提案している(特許文献2)。特許文献2に記載の技術では、容量素子本体の上下に内部電極を積層させて形成した応力制御部を設けることで、容量素子の焼成時における誘電体層の収縮に起因した内部応力を容量素子本体の誘電体層に発生させることができる。この結果、容量素子本体の誘電体層の比誘電率を高めることができる。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2011−119482号公報

【特許文献2】WO2011/013658号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献1に記載された可変容量デバイスにおいても焼結時における誘電体層の収縮により内部応力は発生する。しかしながら、各層における内部電極の形状は、静電容量によって適宜設定されるものであり、内部応力を考慮した形状とはされていない。また、特許文献1では、直列接続された各可変容量コンデンサを構成する内部電極の面積積を変えることで、直列接続される各可変容量コンデンサ間にコンデンサを形成しない電極部分が形成され、この電極部分による電極抵抗が余分に増える問題がある。

【0006】

上述の点に鑑み、本開示は、電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、電気的特性を向上させることを目的とする。また、その静電容量素子を用いることにより、信頼性に優れた共振回路を提供することを目的する。

【課題を解決するための手段】

【0007】

本開示の静電容量素子は、容量素子本体と、外部端子とを備える。容量素子本体は、誘電体層と、誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とを備える。そして、容量素子本体では、これらの内部電極により2つ以上のコンデンサが形成され、該2つ以上のコンデンサが内部電極の積層方向に直列接続されている。また、外部端子は、容量素子本体の側面に形成され、静電容量をなす電極本体に電気的に接続されている。

【0008】

本開示の静電容量素子では、静電容量をなす電極本体の重心が積層方向の直線上に配置されるため、容量素子本体の焼成時における電極材料や誘電体材料の収縮方向が、その重心が配置された直線に向かうように発生する。これにより、内部に形成されるコンデンサの中心に残留応力が集中する。

【0009】

本開示の共振回路は、上述した静電容量素子を含む共振コンデンサと、共振コンデンサに接続された共振コイルを備える。

【発明の効果】

【0010】

本開示によれば、電極の積層方向に直列接続された複数のコンデンサを備える静電容量素子において、製造時における焼成処理において発生する残留応力を増大させることができるため電気的特性の向上が図られる。

【図面の簡単な説明】

【0011】

【図1】図1Aは、本開示の第1の実施形態に係る可変容量素子の概略斜視図であり、図1Bは、可変容量素子の断面構成図である。

【図2】本開示の第1の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図3】図3Aは第1電極を上面から見たときの平面構成図であり、図3Bは、第1電極を一方の側面から見たときの構成図である。

【図4】図4Aは第2電極を上面から見たときの平面構成図であり、図4Bは第2電極を一方の側面から見たときの構成図である

【図5】図5Aは、第3電極を上面から見たときの平面構成図であり、図5Bは第3電極を一方の側面から見たときの構成図である。

【図6】本開示の第1の実施形態に係る可変容量素子の等価回路図である。

【図7】図7Aは、比較例に係る可変容量素子の外観斜視図であり、図7Bは、比較例に係る可変容量素子の断面構成である。

【図8】図8Aは、比較例の可変容量素子における第1電極を上面から見たときの平面構成図であり、図8Bは、比較例の可変容量素子における第2電極を上面から見たときの平面構成図であり、図8Cは、比較例の可変容量素子における第3電極を上面から見たときの平面構成図である。

【図9】比較例に係る可変容量素子の等価回路図である。

【図10】図10Aは、本開示の第2の実施形態に係る可変容量素子の斜視図であり、図10Bは、本開示の第2の実施形態に係る可変容量素子の断面構成図である。

【図11】本開示の第2の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図12】図12Aは第4電極を上面から見たときの平面構成図であり、図12Bは第1電極を一方の側面から見たときの構成図である。

【図13】本開示の第2の実施形態に係る可変容量素子の等価回路図である。

【図14】図14Aは、本開示の第3の実施形態に係る可変容量素子の斜視図であり、図14Bは、本開示の第3の実施形態に係る可変容量素子の断面構成図である。

【図15】本開示の第3の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図16】図16Aは第5電極を上面から見たときの平面構成図であり、図16Bは第5電極を一方の側面から見たときの構成図である。

【図17】本開示の第3の実施形態に係る可変容量素子の等価回路図である。

【図18】図18Aは、本開示の第4の実施形態に係る可変容量素子の斜視図であり、図18Bは本開示の第4の実施形態に係る可変容量素子の断面構成図である。

【図19】本開示の第4の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図20】図20Aは第6電極を上面から見たときの平面構成図であり、図20Bは第1電極を一方の側面から見たときの構成図である。

【図21】本開示の第4の実施形態に係る可変容量素子の等価回路図である。

【図22】図22Aは、本開示の第5の実施形態に係る可変容量素子の斜視図であり、図22Bは、本開示の第5の実施形態に係る可変容量素子の断面構成図である。

【図23】本開示の第5の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図24】図24Aは第7電極を上面から見たときの平面構成図であり、図24Bは、第7電極を一方の側面から見たときの構成図である。

【図25】本開示の第5の実施形態に係る可変容量素子の等価回路図である。

【図26】図26Aは、本開示の第6の実施形態に係る可変容量素子の斜視図であり、図26Bは、本開示の第6の実施形態に係る可変容量素子の断面構成図である。

【図27】本開示の第6の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図28】図28Aは第8電極を上面から見たときの平面構成図であり、図28Bは第8電極を一方の側面から見たときの構成図である。

【図29】本開示の第6の実施形態に係る可変容量素子の等価回路図である。

【図30】図30Aは、本開示の第7の実施形態に係る可変容量素子の斜視図であり、図30Bは、本開示の第7の実施形態に係る可変容量素子の断面構成図である。

【図31】本開示の第7の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図32】図32Aは本開示の第7の実施形態に係る可変容量素子の内部の回路構成図であり、図32Bは本開示の第7の実施形態に係る可変容量素子の等価回路図である。

【図33】図33Aは、本開示の第8の実施形態に係る可変容量素子の斜視図であり、図33Bは、本開示の第8の実施形態に係る可変容量素子の断面構成図である。

【図34】本開示の第8の実施形態に係る可変容量素子本体を長辺方向の一方の側面から見たときの分解図である。

【図35】図35Aは、本開示の第9の実施形態に係る可変容量素子の斜視図であり、図35Bは、本開示の第9の実施形態に係る可変容量素子の断面構成図である。

【図36】本開示の第10の実施形態に係る共振回路を用いた非接触ICカードの受信系回路部のブロック構成図である

【発明を実施するための形態】

【0012】

以下に、本開示の実施形態に係る静電容量素子及びそれを備える共振回路の一例を、図面を参照しながら説明する。本開示の実施形態は以下の順で説明する。また、以下に説明する実施形態では、印加電圧によって容量値が変化する可変容量素子を例として説明する。なお、本開示は以下の例に限定されるものではない。

1.第1の実施形態:直列接続した2つのコンデンサを備える可変容量素子の一例

1−1 可変容量素子の構成

1−2 製造方法

1−3 回路構成

2.第2の実施形態:直列接続した3つのコンデンサを備える可変容量素子の一例

3.第3の実施形態:直列接続した4つのコンデンサを備える可変容量素子の一例

4.第4の実施形態:直列接続した5つのコンデンサを備える可変容量素子の一例

5.第5の実施形態:直列接続した6つのコンデンサを備える可変容量素子の一例

6.第6の実施形態:直列接続した7つのコンデンサを備える可変容量素子の一例

7.第7の実施形態:並列接続及び直列接続したコンデンサを備える可変容量素子の一例

8.第8の実施形態:並列接続及び直列接続したコンデンサを備える可変容量素子の一例

9.第9の実施形態:応力制御部を備える可変容量素子の一例

10.第10の実施形態:本開示の可変容量素子を適用した共振回路の一例

【0013】

〈1.第1の実施形態〉

[1−1 可変容量素子の構成]

図1Aは、本開示の第1の実施形態に係る可変容量素子1の概略斜視図であり、図1Bは、可変容量素子1の断面構成図である。以下では、後述する内部電極の積層方向をz方向、積層方向に直交する可変容量素子1の長辺方向をx方向、積層方向に直交する可変容量素子1の短辺方向をy方向として説明する。また、可変容量素子1のxy面で構成される一方の面を「上面」、xy面で構成される他方の面を「下面」として説明する。また、可変容量素子1の上面及び下面に垂直な面を「側面」として説明する。

【0014】

図1Aに示すように、本実施形態例の可変容量素子1は、xy面が長方形とされた直方体部材で構成された可変容量素子本体2と6つの外部端子(以下、それぞれ第1外部端子20〜第3外部端子22という)とで構成されている。

【0015】

第1外部端子20及び第3外部端子22は、可変容量素子本体2のxz面で構成される長辺方向の一方の側面に互いに離間して形成されている。また、第2外部端子21は、可変容量素子本体2のxz面で構成される長辺方向の他方の側面に形成され、第1外部端子20に対向する位置に形成されている。第1外部端子20〜第3外部端子22のx方向の幅は、それぞれ、後述する第1接続電極30b〜第3接続電極32bの幅と同等の幅に形成されている。また、第1外部端子20〜第3外部端子22は、それぞれz方向において可変容量素子本体2の側面を被覆すると共に、可変容量素子本体2の上面及び下面に張り出すように形成されている。

【0016】

可変容量素子本体2は、図1Bに示すように、誘電体層3と、誘電体層3を介して積層された3つの内部電極とで構成されている。以下の説明では、便宜上、3つの内部電極をそれぞれ第1電極30〜第3電極32と称する。本実施形態例の可変容量素子本体2は、第1電極30、第2電極31、第3電極32がこの順に積層された構成とされており、第1電極30の下層に下部誘電体層4が積層され、第3電極32の上層に上部誘電体層5が積層された構成とされている。

【0017】

図2は、可変容量素子本体2を長辺方向の一方の側面から見たときの分解図である。また、図3Aは第1電極30を上面から見たときの平面構成図であり、図3Bは、第1電極30を一方の側面から見たときの構成図である。また、図4Aは第2電極31を上面から見たときの平面構成図であり、図4Bは第2電極31を一方の側面から見たときの構成図である。また、図5Aは、第3電極32を上面から見たときの平面構成図であり、図5Bは第3電極32を一方の側面から見たときの構成図である。図2〜図5では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0018】

図2に示すように、可変容量素子本体2は、一方の面に電極が形成されたシート状の誘電体層3が積層された構造とされており、本実施形態例では、第1電極30、第2電極31、第3電極32が下面側から上面側にかけてこの順に積層された構成とされている。シート状に形成された各誘電体層3は、平面形状が長方形とされ、長方形を為す平面上に各電極が形成された構成とされている。

【0019】

また、本実施形態例では、第1電極30の下層、及び第3電極32の上層には、電極が形成されていない誘電体層3が複数層ずつ設けられており、この誘電体層3が下部誘電体層4と上部誘電体層5を構成している。この複数層の誘電体層3で構成された下部誘電体層4及び上部誘電体層5により、可変容量素子本体2の上面及び下面に電極が露出することを防ぐことができる。

【0020】

本実施形態例では、印加電圧に応じて容量が変化する可変容量素子1を構成するため、誘電体層3は強誘電体材料で構成されている。そのような強誘電体材料としては、具体的には、イオン分極を生じる誘電体材料を用いることができる。イオン分極を生じる強誘電体材料は、イオン結晶材料からなり、プラスのイオンとマイナスのイオンの原子が変位することで電気的に分極する強誘電体材料である。このイオン分極を生じる強誘電体材料は、一般に、所定の2つの元素をA及びBとすると、化学式ABO3(Oは酸素元素)で表され、ペロブスカイト構造を有する。このような強誘電体材料としては、例えば、チタン酸バリウム(BaTiO3)、ニオブ酸カリウム(KNbO3)、チタン酸鉛(PbTiO3)等があげられる。また、誘電体層3の形成材料として、チタン酸鉛(PbTiO3)にジルコン酸鉛(PbZrO3)を混ぜ合わせたPZT(チタン酸ジルコン酸鉛)を用いてもよい。

【0021】

また、強誘電体材料として、電子分極を生じる強誘電体材料を用いてもよい。この強誘電体材料では、プラスの電荷に偏った部分と、マイナスの電荷に偏った部分とに分かれて電気双極子モーメントが生じ、分極が生じる。そのような材料として、従来、Fe2+の電荷面と、Fe3+の電荷面の形成により、分極を形成して強誘電体的特性を示す希土類鉄酸化物が報告されている。この系においては、希土類元素をREとし、鉄族元素をTMとしたときに、分子式(RE)・(TM)2・O4(O:酸素元素)で表される材料が高誘電率を有することが報告されている。なお、希土類元素としては、例えば、Y、Er、Yb、Lu(特にYと重希土類元素)が挙げられ、鉄族元素としては、例えば、Fe、Co、Ni(特にFe)が挙げられる。また、(RE)・(TM)2・O4としては、例えば、ErFe2O4、LuFe2O4、YFe2O4が挙げられる。

【0022】

第1電極30は、図3A及び図3Bに示すように、第1電極本体30aと第1接続電極30bとで構成されている。第1電極本体30aは平面形状が長方形とされ、シート状に形成された誘電体層3の面積、すなわち、可変容量素子本体2のxy面の面積よりも小さく、可変容量素子本体2の側面に露出しないように形成されている。また、第1電極本体30aは、その中心が、誘電体層3の中心に一致するように形成されている。

【0023】

第1接続電極30bは、第1電極本体30aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第1接続電極30bは、可変容量素子本体2の焼結時において第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。

【0024】

ところで、ここでいう残留応力は、可変容量素子本体2の製造時における焼成処理での電極材料と誘電体材料の収縮率の違いで発生する。したがって、第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさないためには、第1接続電極30bの面積は第1電極本体30aの面積よりも十分に小さく形成されるのが好ましい。本実施形態例では、第1接続電極30bのx方向の幅を、第1電極本体30aのx方向の幅よりも十分に小さく形成している。

そして、可変容量素子本体2の側面に露出した第1接続電極30bの端部は、第1外部端子20に電気的に接続されている。

【0025】

ここで、第1接続電極30b周辺に発生する残留応力が、第1電極本体30a部分に発生する残留応力に影響を及ぼさない程度とするため、第1接続電極30aのx方向の幅は第1電極本体30aのx方向の幅の4分の1以下に設定するのが好ましい。

【0026】

第2電極31は、図4A及び図4Bに示すように、第2電極本体31aと、第2接続電極31bとで構成されている。第2電極本体31aは第1電極30を構成する第1電極本体30aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0027】

第2接続電極31bは、第2電極本体31aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第2接続電極31bは、可変容量素子本体2の焼成時において第2接続電極31b周辺に発生する残留応力が、第2電極本体31a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第2接続電極31bの面積は第2電極本体31aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第2接続電極31bのx方向の幅を、第2電極本体31aのx方向の幅よりも十分に小さく形成している。

【0028】

また、本実施形態例では、第2電極31は第1電極30をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第2接続電極31bは第1接続電極30bの対角上に位置するように形成される。そして、可変容量素子本体2の側面に露出した第2接続電極31bの端部は、第2外部端子21に電気的に接続されている。

【0029】

第3電極32は、図5A及び図5Bに示すように、第3電極本体32aと、第3接続電極32bとで構成されている。第3電極本体32aは第1電極本体30a、及び第2電極本体31aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0030】

第3接続電極32bは、第3電極本体32aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体2の側面に露出するように形成されている。また、第3接続電極32bは、可変容量素子本体2の焼結時において第3接続電極32b周辺に発生する残留応力が、第3電極本体32a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第3接続電極32bの面積は第3電極本体32aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第3接続電極32bのx方向の幅を、第3電極本体32aのx方向の幅よりも十分に小さく形成している。

【0031】

また、本実施形態例では、第3電極32は第1電極30をy方向の軸を中心に180度回転させた構成とされている。すなわち、第3接続電極32bと第1接続電極30bは、可変容量素子本体2の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体2の側面に露出した第3接続電極32bの端部は、第3外部端子22に電気的に接続されている。

【0032】

第1電極30〜第3電極32は、例えば金属微粉末(Pd、Pd/Ag、Ni等)を含む導電ペーストを用いて形成することができる。なお、本実施形態例では、第1電極30〜第3電極32は同じ材料で形成する。ただし、本開示はこれに限定されず、例えば用途等に応じて、第1電極30〜第3電極32を互いに異なる材料で形成してもよい。

【0033】

以上の構成により、第1電極30〜第3電極32は、図2に示すように、同一形状の第1電極本体30a〜第3電極本体32aの各辺、及び中心がz方向に重なるように積層されている。これにより、第1電極本体30a〜第3電極本体32aの中心(重心)がz方向の延びる直線上に配置される。また、本実施形態例では、第1電極本体30a〜第3電極本体32aは、その中心が誘電体層3の中心となるように形成されている。このため、第1電極本体30a〜第3電極本体32aの中心(重心)が、可変容量素子本体2の重心を通るz方向の軸上に配置される。

【0034】

[1−2 製造方法]

以上の構成を有する可変容量素子1の製造方法の一例を説明する。まず、所望の誘電体材料からなる誘電体シートを用意する。誘電体シートは、可変容量素子本体2において各誘電体層3を構成するものであり、例えば厚さ約2.5μmとされている。これらの誘電体シートは、ペースト状にした誘電体材料をPET(ポリエチレンテレフタレート)フィルム上に所望の厚さに塗布して形成することができる。また、図3〜図5に示した第1電極30〜第3電極32の形成領域に対応する領域が開口されたマスクを用意する。

【0035】

次に、例えば、Pt、Pd、Pd/Ag、Ni、Ni合金等の金属微粉末をペースト化した導電ペーストを調整する。そして、その導電ペーストを、前段で用意したそれぞれのマスクを介して誘電体シートの一方の表面に塗布(シルク印刷)する。これにより、一方の表面に第1電極30〜第3電極32が形成された誘電体シートを作成する。このとき、各電極の電極本体の中心が誘電体シートの中心に一致するように形成する。

【0036】

そして、第1電極30〜第3電極32が形成されたそれぞれの誘電体シートを、各電極が印刷された面の向きを揃えて、所望の順番に積層する。このとき、第1電極本体30a〜第3電極本体32aの各辺、及び中心がz方向に重なるように積層する。さらに、この積層体の上下に、電極が印刷されていない誘電体シートを積層させて圧着する。

【0037】

そして、圧着した部材を還元性の雰囲気中で高温焼成して、誘電体シートと導電ペーストで形成された各電極とを一体化する。これにより、可変容量素子本体2が作製される。その後、可変容量素子本体2の側面の所定位置に、第1外部端子20〜第3外部端子22を取り付ける。本実施形態例では、このようにして可変容量素子1を作製する。

【0038】

[1−3 回路構成]

図6に、本実施形態例の可変容量素子1の等価回路を示す。本実施形態例の可変容量素子1では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。そして、第1電極30〜第3電極32は、それぞれ異なる外部端子(第1外部端子20〜第3外部端子22)に接続されている。したがって本実施形態例の可変容量素子1では、第1コンデンサC1及び第2コンデンサC2が電極の積層方向に直列接続された構成とされている。

このような構成の可変容量素子1では、第1外部端子20〜第3外部端子22に所望のDC電圧を印加することにより、第1コンデンサC1〜第3コンデンサC3の容量が可変される。

【0039】

ところで、本実施形態例の可変容量素子1では、誘電体材料と電極材料の焼結時の収縮率の違いにより残留応力が発生する。この残留応力は、各層において電極材料及び誘電体材料が収縮する方向に発生する。一方、本実施形態例の可変容量素子1では、第1コンデンサC1、及び第2コンデンサC2を構成する第1電極本体30a〜第3電極本体32aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。さらに、第1電極本体30a〜第3電極本体32aは、その中心が誘電体層3の中心に一致するように形成されている。このため、本実施形態例の可変容量素子1では、焼成時に、各電極及び誘電体層は可変容量素子本体2の重心を通るz方向の軸方向に収縮する。これにより、焼結時において発生する残留応力を、第1コンデンサC1及び第2コンデンサC2の中心に集中して発生させることができる。

【0040】

[1−3 比較例]

図7Aは、比較例に係る可変容量素子200の外観斜視図であり、図7Bは、比較例に係る可変容量素子200の断面構成である。比較例に係る可変容量素子200は、内部電極の積層方向に直列接続されたコンデンサを備える可変容量素子であり、用途や必要とする容量などに応じて各内部電極の面積を自由に変化させる構成を採用した可変容量素子である。図7A、図7Bにおいても、後述する内部電極の積層方向をz方向、積層方向に直交する可変容量素子200の長辺方向をx方向、積層方向に直交する可変容量素子200の短辺方向をy方向として説明する。

【0041】

比較例に係る可変容量素子200は、直方体部材で構成された可変容量素子本体201と3つの外部端子(以下、それぞれ第1外部端子202〜第3外部端子204という)とで構成されている。

【0042】

第1外部端子202及び第3外部端子204は、可変容量素子本体201のxz面で構成される長辺方向の一方の側面に互いに離間して形成されている。また、第2外部端子203は、可変容量素子本体201のxz面で構成される長辺方向の他方の側面に形成され、第1外部端子202に対向する位置に形成されている。

【0043】

可変容量素子本体201は、誘電体層3を介して積層された3つの内部電極(以下、第1電極206〜第3電極208という)で構成されている。比較例に係る可変容量素子本体201においても、第1電極206、第2電極207、第3電極208がこの順に積層された構成とされている。

【0044】

図8Aは、第1電極206を上面から見たときの平面構成図であり、図8Bは、第2電極207を上面から見たときの平面構成図であり、図8Cは、第3電極208を上面から見たときの平面構成図である。

【0045】

第1電極206は、図8Aに示すように矩形状に形成され、一方の端部が可変容量素子本体201のx方向の一方の側面に露出するように形成されている。そして、第1電極206は、第1外部端子202に電気的に接続されている。

【0046】

第2電極207は、図8Bに示すように、第1電極206よりも大きい面積を有する矩形状に形成され、z方向において、第1電極206と一部重なるように形成されている。また、第2電極207の一方の端部は、可変容量素子本体201のx方向の他方の側面に露出するように形成されている。そして、第2電極207は第2外部端子203に電気的に接続されている。

【0047】

第3電極208は、図8Cに示すように矩形状に形成され、一方の端部が可変容量素子本体201のx方向の一方の側面に露出するように形成されている。また、このとき、第3電極208は、第1電極206とz方向に重ならない位置であって、第2電極207の一部に重なる領域に形成されている。そして、第3電極208は、第3外部端子204に電気的に接続されている。

【0048】

比較例に係る可変容量素子200においても、第1電極206〜第3電極208や誘電体層205を、本実施形態例の可変容量素子1における電極材料及び誘電体材料で構成する。そして、比較例に係る可変容量素子1においても、z方向に積層される第1電極206〜第3電極208は、それぞれ異なる外部端子(第1外部端子202〜第3外部端子204)に接続される。このため、内部電極の積層方向に直列接続されたコンデンサが形成される。

【0049】

図9は、比較例に係る可変容量素子200の等価回路図である。図9に示すように、比較例では、第1電極206と第2電極207とにより第1コンデンサCaが形成され、第2電極207と第3電極208とにより第2コンデンサCbが形成される。そして、比較例に係る可変容量素子200では、第1電極206〜第3電極208の面積を用途や必要とする容量に応じて適宜変えることで所望の容量を得る構成とされている。

【0050】

一方、比較例に係る可変容量素子200では、第1電極206及び第3電極208が第2電極207よりも小さい面積とされ、それぞれ第2電極207の一部にのみ重なるように形成されている。したがって、このような構成の可変容量素子200では、等価回路において、図7Bのx1で示す部分の電極抵抗が余分に増えてしまう。

【0051】

さらに、比較例に係る可変容量素子200では、第1電極206〜第3電極208が異なる面積に形成され、かつ、各電極の中心位置が積層方向の異なる軸上に配置されている。したがって、焼結時の電極材料及び誘電体材料の収縮に起因して発生する残留応力は、可変容量素子本体201内部で様々な方向に向くように発生する。このため、残留応力に起因する静電容量の増大などの効果が得られない。

【0052】

これに比較して、本実施形態例の可変容量素子1では、第1コンデンサC1及び第2コンデンサC2を構成する第1電極本体30a〜第3電極本体32aは全て同一形状とされ、かつ、各辺及び中心位置が積層方向に重なるように積層されている。したがって、各コンデンサ間の抵抗は、各電極層の厚さ方向に発生する抵抗のみとなり、隣接するコンデンサ間の抵抗値を最小に抑えることができる。

【0053】

また、本実施形態例では、第1電極本体30a〜第3電極本体32aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、本実施形態例の可変容量素子1では、焼結時において発生する残留応力を、第1コンデンサC1及び第2コンデンサC2の中心に集中して発生させることができる。この結果、残留応力により静電容量の増大や、容量可変率の増加など、電気的特性の向上が図られる。

【0054】

本実施形態例の可変容量素子1では、第1電極本体30a〜第3電極本体32aの中心が誘電体層3の中心に一致するように形成されている。これにより、第1電極本体30a〜第3電極本体32aの中心は、誘電体層205と内部電極との積層体である可変容量素子本体201の重心を通る直線上にくる。このように、第1電極本体30a〜第3電極本体32aの重心を可変容量素子本体201の重心を通る直線上となるように設計することで、より大きな残留応力を発生させることができる。

【0055】

〈2.第2の実施形態〉

次に、本開示の第2の実施形態に係る可変容量素子について説明する。図10Aは、本実施形態例の可変容量素子51の斜視図であり、図10Bは、本実施形態例の可変容量素子51の断面構成図である。本実施形態例の可変容量素子51は、第1の実施形態に係る可変容量素子1の第3電極32上部に、さらに第4電極を備える構成とされている。

図10A及び図10Bにおいて、図1A及び図1Bに対応する部分には同一符号を付し重複説明を省略する。

【0056】

図10Aに示すように、本実施形態例の可変容量素子51は、直方体部材で構成された可変容量素子本体52と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

【0057】

第4外部端子23は、可変容量素子本体52のxz面で構成される長辺方向の他方の側面に形成され、xy面でみたときに、第1外部端子20に対向する位置に形成されている。第4外部端子23のx方向の幅は、後述する第4接続電極33bの幅と同等の幅に形成されている。また、第4外部端子23は、第1外部端子20〜第3外部端子22と同様、z方向において可変容量素子本体52の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0058】

図11は、可変容量素子本体52を長辺方向の一方の側面から見たときの分解図である。また、図12Aは第4電極33を上面から見たときの平面構成図であり、図12Bは、第1電極30を一方の側面から見たときの構成図である。図11及び図12では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0059】

可変容量素子本体52は、第1電極30〜第4電極33が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第4電極33の上層に上部誘電体層5が積層された構成とされている。

【0060】

第4電極33は、図12A及び図12Bに示すように、第4電極本体33aと、第4接続電極33bとで構成されている。第4電極本体33aは第1電極本体30a〜第3電極本体32aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0061】

第4接続電極33bは、第4電極本体33aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体52の側面に露出するように形成されている。また、第4接続電極33bは、可変容量素子本体52の焼結時において第4接続電極33b周辺に発生する残留応力が、第4電極本体33a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第4接続電極33bの面積は第4電極本体33aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第4接続電極33bのx方向の幅を、第4電極本体33aのx方向の幅よりも十分に小さく形成している。

【0062】

また、本実施形態例では、第4電極33は第3電極32をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第4接続電極33bは第3接続電極32bの対角上に位置し、また、第4接続電極33bと第2接続電極31bは可変容量素子本体52の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体52の側面に露出した第4接続電極33bの端部は、第4外部端子23に電気的に接続されている。

【0063】

第4電極33を構成する電極材料としては、第1電極30〜第3電極32を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子51も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第4電極33は第3電極32をz方向の軸を中心として180度回転させた形状とされている。このため、第4電極33を誘電体シート状に形成する場合には、第3電極32とは同一のマスクを用いて形成することができる。

【0064】

図13に、本実施形態例の可変容量素子の等価回路を示す。本実施形態例の可変容量素子51では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。そして、第1電極30〜第4電極33は、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。したがって本実施形態例の可変容量素子51では、第1コンデンサC1〜第3コンデンサC3が電極の積層方向に直列接続された構成とされている。

【0065】

本実施形態例の可変容量素子51においても、第1電極本体30a〜第4電極本体33aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0066】

〈3.第3の実施形態〉

次に、本開示の第3の実施形態に係る可変容量素子について説明する。図14Aは、本実施形態例の可変容量素子61の斜視図であり、図14Bは、本実施形態例の可変容量素子61の断面構成図である。本実施形態例の可変容量素子61は、第2の実施形態に係る可変容量素子51の第4電極33上部に、さらに第5電極34を備える構成とされている。

図14A及び図14Bにおいて、図10A及び図10Bに対応する部分には同一符号を付し重複説明を省略する。

【0067】

図14Aに示すように、本実施形態例の可変容量素子61は、直方体部材で構成された可変容量素子本体62と第1外部端子20〜第5外部端子24の4つの外部端子で構成されている。

第5外部端子24は、可変容量素子本体62のxz面で構成される長辺方向の一方の側面に形成され、第1外部端子20及び第3外部端子22と離間した置に形成されている。第5外部端子24のx方向の幅は、後述する第5接続電極34bの幅と同等の幅に形成されている。また、第5外部端子24は、第1外部端子20〜第4外部端子23と同様、z方向において可変容量素子本体62の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0068】

図15は、可変容量素子本体62を長辺方向の一方の側面から見たときの分解図である。また、図16Aは第5電極34を上面から見たときの平面構成図であり、図16Bは、第5電極34を一方の側面から見たときの構成図である。図15及び図16は、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0069】

可変容量素子本体62は、第1電極30〜第5電極34が誘電体層を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第5電極34の上層に上部誘電体層5が積層された構成とされている。

【0070】

第5電極34は、図16A及び図16Bに示すように、第5電極本体34aと、第5接続電極34bとで構成されている。第5電極本体34aは第1電極本体30a〜第4電極本体33aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0071】

第5接続電極34bは、第5電極本体34aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体62の側面に露出するように形成されている。また、第5接続電極34bは、可変容量素子61の焼結時において第5接続電極34b周辺に発生する残留応力が、第5電極本体34a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第5接続電極34bの面積は第5電極本体34aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第5接続電極34bのx方向の幅を第5電極本体34aのx方向の幅よりも十分に小さく形成している。

【0072】

また、本実施形態例では、第5接続電極34bは第1接続電極30b及び第3接続電極32bと可変容量素子本体62の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体62の側面に露出した第5接続電極34bの端部は、第5外部端子24に電気的に接続されている。

【0073】

第5電極34を構成する電極材料としては、第1電極30〜第4電極33を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子61も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0074】

図17に、本実施形態例の可変容量素子61の等価回路を示す。本実施形態例の可変容量素子61では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。そして、第1電極30〜第5電極34は、それぞれ異なる外部端子(第1外部端子20〜第5外部端子24)に接続されている。したがって本実施形態例の可変容量素子61では、第1コンデンサC1〜第4コンデンサC4が電極の積層方向に直列接続された構成とされている。

【0075】

本実施形態例の可変容量素子61においても、第1電極本体30a〜第5電極本体34aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0076】

〈4.第4の実施形態〉

次に、本開示の第4の実施形態に係る可変容量素子について説明する。図18Aは、本実施形態例の可変容量素子71の斜視図であり、図18Bは、本実施形態例の可変容量素子71の断面構成図である。本実施形態例の可変容量素子71は、第3の実施形態に係る可変容量素子61の第5電極34上部に、さらに第6電極を備える構成とされている。

図18A及び図18Bにおいて、図14A及び図14Bに対応する部分には同一符号を付し重複説明を省略する。

【0077】

図18Aに示すように、本実施形態例の可変容量素子71は、直方体部材で構成された可変容量素子本体72と第1外部端子20〜第6外部端子25の6つの外部端子で構成されている。

第6外部端子25は、可変容量素子本体72のxz面で構成される長辺方向の他方の側面に形成され、第2外部端子21及び第4外部端子23と離間した位置に形成されている。第6外部端子25のx方向の幅は、後述する第6接続電極35bの幅と同等の幅に形成されている。また、第6外部端子25は、第1外部端子20〜第5外部端子24と同様、z方向において可変容量素子本体72の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0078】

図19は、可変容量素子本体72を長辺方向の一方の側面から見たときの分解図である。また、図20Aは第6電極35を上面から見たときの平面構成図であり、図20Bは、第6電極35を一方の側面から見たときの構成図である。図19及び図20では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0079】

可変容量素子本体72は、第1電極30〜第6電極35が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第6電極35の上層に上部誘電体層5が積層された構成とされている。

【0080】

第6電極35は、図20A及び図20Bに示すように、第6電極本体35aと、第6接続電極35bとで構成されている。第6電極本体35aは第1電極本体30a〜第5電極本体34aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0081】

第6接続電極35bは、第6電極本体35aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体72の側面に露出するように形成されている。また、第6接続電極35bは、可変容量素子本体72の焼結時において第6接続電極35b周辺に発生する残留応力が、第6電極本体35a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第6接続電極35bの面積は第6電極本体35aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第6接続電極35bのx方向の幅を、第6電極本体35aのx方向の幅よりも十分に小さく形成している。

【0082】

また、本実施形態例では、第6電極35は第5電極34をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第6接続電極35bは第5接続電極34bの対角上に位置する。また、第6接続電極35b、第4接続電極33b、及び第2接続電極31bは可変容量素子本体の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体72の側面に露出した第6接続電極35bの端部は、第6外部端子25に電気的に接続されている。

【0083】

第6電極35を構成する電極材料としては、第1電極30〜第5電極34を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子71も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第6電極35は第5電極34をz方向の軸を中心として180度回転させた形状とされているため、第6電極35を誘電体シート状に形成する場合には、第5電極34を形成するためのマスクと同一のマスクを用いて形成することができる。

【0084】

図21に、本実施形態例の可変容量素子71の等価回路を示す。本実施形態例の可変容量素子71では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。そして、第1電極30〜第6電極35は、それぞれ異なる外部端子(第1外部端子20〜第6外部端子25)に接続されている。したがって本実施形態例の可変容量素子71では、第1コンデンサC1〜第5コンデンサC5が電極の積層方向に直列接続された構成とされている。

【0085】

本実施形態例の可変容量素子71においても、第1電極本体30a〜第6電極本体35aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0086】

〈5.第5の実施形態〉

次に、本開示の第5の実施形態に係る可変容量素子について説明する。図22Aは、本実施形態例の可変容量素子81の斜視図であり、図22Bは、本実施形態例の可変容量素子の断面構成図である。本実施形態例の可変容量素子は、第4の実施形態に係る可変容量素子71の第6電極35上部に、さらに第7電極36を備える構成とされている。

図22A及び図22Bにおいて、図18A及び図18Bに対応する部分には同一符号を付し重複説明を省略する。

【0087】

図22Aに示すように、本実施形態例の可変容量素子81は、直方体部材で構成された可変容量素子本体82と第1外部端子20〜第7外部端子26の7つの外部端子で構成されている。

第7外部端子26は、可変容量素子本体82のxz面で構成される長辺方向の一方の側面に形成され、第1外部端子20、第3外部端子22、及び第5外部端子24と離間した位置に形成されている。第7外部端子26のx方向の幅は、後述する第7接続電極36bの幅と同等の幅に形成されている。また、第7外部端子26は、第1外部端子20〜第6外部端子25と同様、z方向において可変容量素子本体82の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0088】

図23は、可変容量素子本体82を長辺方向の一方の側面から見たときの分解図である。また、図24Aは第7電極36を上面から見たときの平面構成図であり、図24Bは、第7電極36を一方の側面から見たときの構成図である。図23及び図24では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0089】

可変容量素子本体82は、第1電極30〜第7電極36が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第7電極36の上層に上部誘電体層5が積層された構成とされている。

【0090】

第7電極36は、図24A及び図24Bに示すように、第7電極本体36aと、第7接続電極36bとで構成されている。第7電極本体36aは第1電極本体30a〜第7電極本体36aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0091】

第7接続電極36bは、第7電極本体36aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体82の側面に露出するように形成されている。また、第7接続電極36bは、可変容量素子81の焼結時において第7接続電極36b周辺に発生する残留応力が、第7電極本体36a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第7接続電極36bの面積は第7電極本体36aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第7接続電極36bのx方向の幅を、第7電極本体36aのx方向の幅よりも十分に小さく形成している。

【0092】

また、本実施形態例では、第7接続電極36bは、第1接続電極30b、第3接続電極32b、及び第5接続電極34bと、可変容量素子本体82の同一側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体82の側面に露出した第7接続電極36bの端部は、第7外部端子26に電気的に接続されている。

【0093】

第7電極36を構成する電極材料としては、第1電極30〜第7電極36を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子81も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0094】

図25に、本実施形態例の可変容量素子81の等価回路を示す。本実施形態例の可変容量素子81では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。また、z方向に積層される第6電極本体35a及び第7電極本体36aにより第6コンデンサC6が形成される。そして、第1電極30〜第7電極36は、それぞれ異なる外部端子(第1外部端子20〜第7外部端子26)に接続されている。したがって本実施形態例の可変容量素子81では、第1コンデンサC1〜第7コンデンサC7が電極の積層方向に直列接続された構成とされている。

【0095】

本実施形態例の可変容量素子81においても、第1電極本体30a〜第7電極本体36aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0096】

〈6.第6の実施形態〉

次に、本開示の第6の実施形態に係る可変容量素子について説明する。図26Aは、本実施形態例の可変容量素子91の斜視図であり、図26Bは、本実施形態例の可変容量素子91の断面構成図である。本実施形態例の可変容量素子91は、第5の実施形態に係る可変容量素子81の第7電極36上部に、さらに第8電極37を備える構成とされている。

図26A及び図26Bにおいて、図22A及び図22Bに対応する部分には同一符号を付し重複説明を省略する。

【0097】

図26Aに示すように、本実施形態例の可変容量素子91は、直方体部材で構成された可変容量素子本体92と第1外部端子20〜第8外部端子27の8つの外部端子で構成されている。

第8外部端子27は、可変容量素子本体92のxz面で構成される長辺方向の他方の側面に形成され、第2外部端子21、第4外部端子23、及び第6外部端子25と離間した位置に形成されている。第8外部端子27のx方向の幅は、後述する第8接続電極37bの幅と同等の幅に形成されている。また、第8外部端子27は、第1外部端子20〜第7外部端子26と同様、z方向において可変容量素子本体92の側面を被覆すると共に、上面及び下面に張り出すように形成されている。

【0098】

図27は、可変容量素子本体92を長辺方向の一方の側面から見たときの分解図である。また、図28Aは第8電極37を上面から見たときの平面構成図であり、図28Bは、第8電極37を一方の側面から見たときの構成図である。図27及び図28では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。

【0099】

可変容量素子本体92は、第1電極30〜第8電極37が誘電体層3を介してこの順に積層された構成とされ、第1電極30の下層に下部誘電体層4が積層され、第8電極37の上層に上部誘電体層5が積層された構成とされている。

【0100】

第8電極37は、図28A及び図28Bに示すように、第8電極本体37aと、第8接続電極37bとで構成されている。第8電極本体38aは第1電極本体30a〜第8電極本体37aと同一形状とされ、その中心が誘電体層3の中心に一致するように形成されている。

【0101】

第8接続電極37bは、第8電極本体37aのx方向に延びる辺に接続するように形成されると共に、可変容量素子本体92の側面に露出するように形成されている。また、第8接続電極37bは、可変容量素子本体92の焼結時において第8接続電極37b周辺に発生する残留応力が、第8電極本体37a部分に発生する残留応力に影響を及ぼさない程度の大きさに形成されることが好ましい。したがって、第8接続電極37bの面積は第8電極本体37aの面積よりも十分に小さく形成されるのが好ましく、本実施形態例では、第8接続電極37bのx方向の幅を、第8電極本体37aのx方向の幅よりも十分に小さく形成している。

【0102】

また、本実施形態例では、第8電極37は第7電極36をz方向の軸を中心に180度回転させた構成とされている。すなわち、xy面でみると、第8接続電極38bは第7接続電極36bの対角上に位置している。そして、第8接続電極37bは、第6接続電極35b、第4接続電極33b、及び第2接続電極31bが形成された可変容量素子本体92の側面と同一の側面に形成され、x方向において互いに離間した位置となるように形成される。そして、可変容量素子本体92の側面に露出した第8接続電極37bの端部は、第8外部端子27に電気的に接続されている。

【0103】

第8電極37を構成する電極材料としては、第1電極30〜第8電極37を構成する電極材料と同様の材料を用いることができる。また、本実施形態例の可変容量素子91も、第1の実施形態と同様の製造方法を用いて作製することができる。また、本実施形態例では、第8電極37は第7電極36をz方向の軸を中心として180度回転させた形状とされているため、第8電極37を誘電体シート状に形成する場合には、第7電極36を形成するためのマスクと同一のマスクを用いて形成することができる。

【0104】

図29に、本実施形態例の可変容量素子91の等価回路を示す。本実施形態例の可変容量素子91では、z方向に積層される第1電極本体30a及び第2電極本体31aにより第1コンデンサC1が形成される。また、z方向に積層される第2電極本体31a及び第3電極本体32aにより第2コンデンサC2が形成される。また、z方向に積層される第3電極本体32a及び第4電極本体33aにより第3コンデンサC3が形成される。また、z方向に積層される第4電極本体33a及び第5電極本体34aにより第4コンデンサC4が形成される。また、z方向に積層される第5電極本体34a及び第6電極本体35aにより第5コンデンサC5が形成される。また、z方向に積層される第6電極本体35a及び第7電極本体36aにより第6コンデンサC6が形成される。また、z方向に積層される第7電極本体36a及び第8電極本体37aにより第7コンデンサC7が形成される。そして、第1電極30〜第8電極37は、それぞれ異なる外部端子(第1外部端子20〜第8外部端子27)に接続されている。したがって本実施形態例の可変容量素子91では、第1コンデンサC1〜第7コンデンサC7が電極の積層方向に直列接続された構成とされている。

【0105】

本実施形態例の可変容量素子91においても、第1電極本体30a〜第8電極本体37aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0106】

〈7.第7の実施形態〉

次に、本開示の第7の実施形態に係る可変容量素子について説明する。図30Aは、本実施形態例の可変容量素子101の斜視図であり、図30Bは、本実施形態例の可変容量素子101の断面構成図である。本実施形態例の可変容量素子101は、第1電極30〜第4電極33からなる積層体を2層積層した構成を有する例である。図30A及び図30Bにおいて、図10A及び図10Bに対応する部分には同一符号を付し、重複説明を省略する。

【0107】

図30Aに示すように、本実施形態例の可変容量素子101は、直方体部材で構成された可変容量素子本体102と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体102は、第1積層体6と、第2積層体7と、下部誘電体層4と、上部誘電体層5とで構成されている。

【0108】

図31は、可変容量素子本体102を長辺方向の一方の側面から見たときの分解図である。図31では、誘電体層3及び各内部電極の中心(重心)を通る線を破線で示している。図31に示すように、第1積層体6は、第1電極30、第2電極31、第3電極32、及び第4電極33が誘電体層3を介して下面側からこの順に積層された構成とされている。また、第2積層体7は、第1積層体6のz方向の上部に積層され、第4電極33、第3電極32、第2電極31、及び第1電極30が誘電体層3を介して下面側から順に積層された構成とされている。すなわち、第1積層体6と第2積層体7とでは、下面側から上面側に向けて積層される第1電極30〜第4電極33の積層の順番が逆になるように構成されている。また、第1積層体6の下層には、下部誘電体層4が形成され、第2積層体7の上層には、上部誘電体層5が積層されている。

【0109】

第1積層体6及び第2積層体7に形成された2つの第1電極30は第1外部端子20に接続され、第1積層体6及び第2積層体7に形成された2つの第2電極31は、第2外部端子21に接続される。また、第1積層体6及び第2積層体7に形成された2つの第3電極32は第3外部端子22に接続され、第1積層体6及び第2積層体7に形成された2つの第4電極33は第4外部端子23に接続される。

本実施形態例の可変容量素子101も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0110】

図32Aに、本実施形態例の可変容量素子101の内部の回路構成を示し、図32Bに本実施形態例の可変容量素子101の等価回路を示す。本実施形態例の可変容量素子101では、第1積層体6において、第1コンデンサC1、第2コンデンサC2、第3コンデンサC3が下面側から上面側に向かって順に形成される。一方、第2積層体7においては、第3コンデンサC3、第2コンデンサC2、第1コンデンサC1が下面側から上面側に向かって順に形成される。このとき、第1積層体6と第2積層体7との境界部分に形成された隣接する2つの第4電極33は同一の外部端子(第4外部端子23)に接続され、同電位とされるため、この2つの第4電極33間にはコンデンサは形成されない。

【0111】

そして、第1積層体6に形成される第1電極30〜第4電極33は、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。また、第2積層体7に形成される第1電極30〜第4電極33も、同様に、それぞれ異なる外部端子(第1外部端子20〜第4外部端子23)に接続されている。したがって、図32Aに示すように、第1積層体6、及び第2積層体7では、それぞれ、第1コンデンサC1〜第3コンデンサC3が電極の積層方向に直列接続された構成とされている。

【0112】

一方、第1積層体6に形成される第1電極30と第2積層体7に形成される第1電極30は、それぞれ共通の第1外部端子20に接続されている。また、第1積層体6に形成される第2電極31と第2積層体7に形成される第2電極31は、それぞれ共通の第2外部端子21に接続されている。また、第1積層体6に形成される第3電極32と第2積層体7に形成される第3電極32は、それぞれ共通の第3外部端子22に接続されている。また、第1積層体6に形成される第4電極33と第2積層体7に形成される第4電極33は、それぞれ共通の第4外部端子23に接続されている。したがって、第1積層体6に形成される第1コンデンサC1と第2積層体7に形成される第1コンデンサC2は並列接続されている。同様に、第1積層体6に形成される第2コンデンサC2と第2積層体7に形成される第2コンデンサC2は並列接続され、第1積層体6に形成される第3コンデンサC3と第2積層体7に形成される第3コンデンサC3は並列接続されている。

【0113】

したがって、この可変容量素子101を等価回路で表すと、図32Bに示すように、2つの第1コンデンサC1からなるコンデンサC1’と、2つの第2コンデンサC2からなるコンデンサC2’と、2つの第3コンデンサC3からなるコンデンサC3’が直列接続された回路となる。

【0114】

本実施形態例の可変容量素子101においても、第1積層体6及び第2積層体7において第1電極本体30a〜第4電極本体33aが同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。また、異なる外部端子に接続される複数の電極が誘電体層3を介して積層された積層体を複数積層し、かつ、それらの積層体を電気的に並列接続することにより、各コンデンサの容量を大きくすることができる。

【0115】

〈8.第8の実施形態〉

次に、本開示の第8の実施形態に係る可変容量素子について説明する。図33Aは、本実施形態例の可変容量素子111の斜視図であり、図33Bは、本実施形態例の可変容量素子111の断面構成図である。また、図34は、可変容量素子本体112を長辺方向の一方の側面から見たときの分解図である。本実施形態例の可変容量素子111は、第1電極30〜第4電極33からなる積層体を2層積層した構成を有する例である。図33及び図34において、図30及び図31に対応する部分には同一符号を付し、重複説明を省略する。

【0116】

図33Aに示すように、本実施形態例の可変容量素子111は、直方体部材で構成された可変容量素子本体112と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体112は、第1積層体6と、第2積層体7と、下部誘電体層4と、上部誘電体層5とで構成されている。また、本実施形態例では、第1積層体6の最上層に形成される第4電極33が、第2積層体7の最下層に形成される第4電極33を兼ねる構成とされている。本実施形態例の可変容量素子111も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0117】

本実施形態例の可変容量素子111の回路構成は、図32A及び図32Bに示した第7の実施形態と同様の回路構成となる。本実施形態例の可変容量素子111では、第1積層体6の最上層に形成される第4電極33が第2積層体7の最下層に形成される第4電極33を兼ねる構成とすることで、第7の実施形態に比較して可変容量素子111の低背化が図られ、小型化が可能となる。その他、第1の実施形態と同様の効果を得ることができる。

【0118】

〈9.第9の実施形態〉

次に、本開示の第9の実施形態に係る可変容量素子について説明する。図35Aは、本実施形態例の可変容量素子121の斜視図であり、図35Bは、本実施形態例の可変容量素子121の断面構成図である。本実施形態例の可変容量素子121は、電極の積層方向に応力制御部を設ける例である。図35A及び図35Bにおいて、図33A及び図33Bに対応する部分には同一符号を付し、重複説明を省略する。

【0119】

図35Aに示すように、本実施形態例の可変容量素子121は、直方体部材で構成された可変容量素子本体122と第1外部端子20〜第4外部端子23の4つの外部端子で構成されている。

可変容量素子本体122は、第1積層体6と、第1応力制御部8と、第2応力制御部9と、下部誘電体層4と、上部誘電体層5とで構成されている。

【0120】

第1応力制御部8は、第1積層体6の下層側に形成され、誘電体層3を介して複数積層された第1電極30で構成されている。第1応力制御部8を構成する第1電極30は、第1積層体6の第1電極30と同様、第1外部端子20に接続されている。したがって、第1積層体6の最下層に形成される第1電極30と第1応力制御部8を構成する第1電極30とは同電位とされるため、この電極間にコンデンサは形成されない。さらに、第1応力制御部8に形成される複数の第1電極30も同電位とされるため、第1応力制御部8ではコンデンサが形成されない。

【0121】

第2応力制御部9は、第1積層体6の上層側に形成され、誘電体層3を介して複数積層された第4電極33で構成されている。第2応力制御部9を構成する第4電極33は、第1積層体6を構成する第4電極33と同様、第4外部端子23に接続されている。したがって、第1積層体6の最上層に形成される第4電極33と、第2応力制御部9を構成する第4電極33とは同電位とされるため、この電極間にコンデンサは形成されない。さらに、第2応力制御部9に形成される複数の第4電極33も同電位とされるため、第2応力制御部9ではコンデンサが形成されない。

【0122】

そして、本実施形態例の可変容量素子121では、第1応力制御部8、第1積層体6、及び第2応力制御部9に形成される内部電極は、その電極本体の形状が同一とされ、各辺、及び中心がz方向に重なるように積層されている。本実施形態例の可変容量素子121も、第1の実施形態と同様の製造方法を用いて作製することができる。

【0123】

本実施形態例の可変容量素子121の等価回路は図13に示した等価回路と同様の構成となる。すなわち、本実施形態例では、第1積層体6に形成された第1電極30〜第4電極33でのみコンデンサが形成される。したがって、本実施形態例の可変容量素子121においても、図13と同様、第1コンデンサC1、第2コンデンサC2、第3コンデンサC3がこの順に直列接続された回路となる。

【0124】

本実施形態例の可変容量素子121では、第1応力制御部8及び第2応力制御部9においても、電極材料と誘電体材料の焼成時の収縮率の違いにより、残留応力が発生している。したがって、第1応力制御部8及び第2応力制御部9に発生した残留応力が第1積層体6に形成される第1コンデンサC1〜第3コンデンサC3に影響し、応力制御部を形成しない場合に比較して、容量値の増加、及び容量可変率の増加を図ることができる。

【0125】

また、本実施形態例においては、第1応力制御部8、第2応力制御部9、及び第1積層体6に形成される内部電極の電極本体の形状が同一形状とされ、各辺、及び中心がz方向に重なるように積層されている。このため、第1の実施形態と同様の効果を得ることができる。

【0126】

ところで、第1〜第9の実施形態例では、第1電極30〜第4電極33のそれぞれにおいて、接続電極のx方向の幅を電極本体のx方向の幅よりも十分に小さく形成したが適宜変更可能である。例えば、DC電圧のみが印加される電極については、接続電極における電気抵抗が高くても良いため、電極本体に対する接続電極の幅を小さく形成しても良いが、AC電流が流れる電極については、電気抵抗の観点から接続電極の幅を大きく形成した方が好ましい。また、残留応力が、応力制御部や多層に積層された電極で支配される場合には、最外側の電極の接続電極の幅は広くしてもよい。また、接続電極の電極抵抗を下げる方法としては、電極幅を広くするほか、長さを短くしたり、厚さを厚くしたりするなどの方法が挙げられるが、これらを組み合わせてより好ましい形態を採ることができる。

【0127】

上述した第1〜第9の実施形態では、容量素子として印加する電圧に応じて容量が変化する可変容量素子を例に挙げて説明したが、本開示はこれに限定されない。上記第1〜第9の実施形態で説明した構成は、入力信号の種類及びその信号レベルに関係なく容量がほとんど変化しない容量素子(以下、定容量素子という)に対しても同様に適用可能である。

【0128】

ただし、この場合には、誘電体層は比誘電率の低い常誘電体材料で形成される。常誘電体材料としては、例えば、紙、ポリエチレンテレフタレート、ポリプロピレン、ポリフェニレンサルファイド、ポリスチレン、TiO2、MgTiO2、MgTiO3、SrMgTiO2、Ai2O3、Ta2O5等を用いることができる。このような定容量素子においても、上記第1の実施形態の可変容量素子と同様にして作製することができる。

【0129】

また、上述の実施形態では、各内部電極の中心が積層方向の直線上に配置される構成としたが、製造時の合わせずれ程度のずれも本開示に含むものとする。さらに、本実施形態例では、各内部電極の中心を誘電体層の中心に合わせる構成としたが、製造時の合わせずれ程度のずれも本開示に含むものとする。

【0130】

また、上述の第1〜第9の実施形態では、内部電極の形状を長方形状としたが、これに限られるものではなく、その他多角形状や、円形状、楕円形状とすることもできる。さらに、本開示の容量素子としては、上述の第1〜第9の実施形態を組み合わせて構成してもよく、趣旨を逸脱しない範囲ないでの種々の変形が可能である。

【0131】

なお、本開示に好適な静電容量素子の容量C(F)は、使用する周波数f(Hz)にも依存する。本開示はインピーダンスZ(オーム)(Z=1/2πfc)が2オーム以上、好ましくは15オーム以上、更に好ましくは、100オーム以上となる容量C(F)である容量素子に好適である。

【0132】

〈10.第10の実施形態:共振回路〉

次に、本発明の第10の実施形態に係る共振回路について説明する。本実施形態例は本発明の容量素子を共振回路に適用した例であり、特に、第1の実施形態における可変容量素子1を適用した例を示す。また、本実施形態例では、共振回路を非接触ICカードに用いた例を示す。

【0133】

図36は、本実施形態例の共振回路を用いた非接触ICカード130の受信系回路部のブロック構成図である。なお、本実施形態例では、説明を簡略化するために、信号の送信系(変調系)回路部は省略している。送信系回路部の構成は、従来の非接触ICカード等と同様の構成である。

【0134】

非接触ICカードは、図36に示すように、受信部131(アンテナ)と、整流部132と、信号処理部133とを備える。

【0135】

受信部131は、共振コイル134及び共振コンデンサ135からなる共振回路で構成され、非接触ICカード130のR/W(不図示)から送信される信号をこの共振回路で受信する。なお、図36では、共振コイル134をそのインダクタンス成分134a(L)と抵抗成分134b(r:数オーム程度)とに分けて図示している。

【0136】

共振コンデンサ135は、容量Coのコンデンサ135aと、受信信号の電圧値(受信電圧値)に応じて容量Cvが変化する可変容量素子1とが並列に接続されている。すなわち、本実施形態では、従来のアンテナ(共振コイル134とコンデンサ135aとからなる共振回路)に可変容量素子1を並列接続した構成となる。また、本実施形態例では、可変容量素子1として図1に示す可変容量素子を用いる例とする。

【0137】

コンデンサ135aは、従来のアンテナと同様に、常誘電体材料で形成されたコンデンサを用いる。常誘電体材料で形成されたコンデンサ135aは、比誘電率が低く、入力電圧の種類(交流または直流)及びその電圧値に関係なくその容量はほとんど変化しない。それゆえ、コンデンサ135aは、入力信号に対して非常に安定した特性を有する。従来のアンテナでは、アンテナの共振周波数がずれないようにするために、このような入力信号に対して安定性の高い常誘電体材料で形成されたコンデンサを用いる。

【0138】

なお、実際の回路上では、共振コイル134のインダクタンス成分Lのばらつきや信号処理部133内の集積回路の入力端子の寄生容量などによる受信部131の容量変動(数pF程度)が存在し、その変動量は非接触ICカード130毎に異なる。それゆえ、本実施形態では、これらの影響を抑制(補正)するために、コンデンサ135aの電極パターンをトリミングして容量Coを適宜調整している。

【0139】

整流部132は、整流用ダイオード136と整流用コンデンサ137とからなる半波整流回路で構成され、受信部131で受信した交流電圧を直流電圧に整流して出力する。

【0140】

信号処理部133は、主に半導体素子の集積回路(LSI:Large Scale Integration)で構成され、受信部131で受信した交流信号を復調する。信号処理部133内のLSIは整流部132から供給される直流電圧により駆動される。なお、LSIとしては、従来の非接触ICカードと同様のものを用いることができる。

【0141】

本実施形態例では、受信部に用いる可変容量素子1は積層される内部電極の中心(重心)が積層方向の直線上に配置されるため、より大きな残留応力が得られる。これにより、電気的特性が向上し、より低い電圧で大きな可変幅が得られる。また可変幅が大きくなる分共振コンデンサへの変化負担を減らせるため共振コンデンサの誘電体を厚くすれば耐圧が向上し、より大きなAC電圧を扱うことが可能となる。

【0142】

本実施形態例では、共振回路の可変容量素子として、第1の実施形態の可変容量素子1を用いる例としたが、第2〜第9の実施形態の可変容量素子を用いる例としてもよい。

【0143】

また、本開示は、以下の構成をとることができる。

【0144】

(1)

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子。

【0145】

(2)

前記内部電極の中心は、前記容量素子本体の重心を通る直線上に配置されている

(1)に記載の静電容量素子。

【0146】

(3)

前記内部電極は、前記電極本体と、前記電極本体と前記外部端子とを電気的に接続するための接続電極とで構成され、積層される複数の電極本体は同一形状に形成されている

(1)又は(2)に記載の静電容量素子。

【0147】

(4)

前記容量素子本体は、積層方向に直列接続されたコンデンサを構成する複数の内部電極を備える積層体を積層方向に複数個備え、異なる積層体に形成されたコンデンサ同士が並列接続されている

(1)〜(3)のいずれかに記載の静電容量素子。

【0148】

(5)

隣接する2つの積層体間において、一方の積層体の最上層に形成される内部電極が、他方の積層体の最下層に形成される内部電極を兼ねる

(4)に記載の静電容量素子。

【0149】

(6)

前記直列接続されたコンデンサの上層及び/又は下層には、誘電体層を介して積層され、コンデンサを形成しない電極本体が積層方向の直線上に配置された複数の内部電極からなる応力制御部を備え、

前記応力制御部に形成されるコンデンサを形成しない電極本体の重心と前記コンデンサを構成する電極本体の中心が直線上に配置されている

(1)〜(5)のいずれかに記載の静電容量素子。

【0150】

(7)

前記応力制御部の内部電極は、コンデンサを形成する内部電極のうち最隣接の内部電極と同電位とされている

(6)に記載の静電容量素子。

【0151】

(8)

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【符号の説明】

【0152】

1,51,61,71,81,91,10,111,121・・・可変容量素子、2,52,62,72,82,92,102,112・・・可変容量素子本体、3・・・誘電体層、4・・・下部誘電体層、5・・・上部誘電体層、6・・・第1積層体、7・・・第2積層体、8・・・第1応力制御部、9・・・第2応力制御部、20・・・第1外部端子、21・・・第2外部端子、22・・・第3外部端子、23・・・第4外部端子、24・・・第5外部端子、25・・・第6外部端子、26・・・第7外部端子、27・・・第8外部端子、30・・・第1電極、30a・・・第1電極本体、30b・・・第1接続電極、31・・・第2電極、31a・・・第2電極本体、31b・・・第2接続電極、32・・・第3電極、32a・・・第3電極本体、32b・・・第3接続電極、33・・・第4電極、33a・・・第4電極本体、33b・・・第4接続電極、34・・・第5電極、34a・・・第5電極本体、34b・・・第5接続電極、35・・・第6電極、35a・・・第6電極本体、35b・・・第6接続電極、36・・・第7電極、36a・・・第7電極本体、36b・・・第7接続電極、37・・・第8電極、37a・・・第8電極本体、37b・・・第8接続電極、38a・・・第8電極本体、38b・・・第8接続電極、130・・・非接触ICカード、131・・・受信部、132・・・整流部、133・・・信号処理部、134・・・共振コイル、134a・・・インダクタンス成分、134b・・・抵抗成分、135・・・共振コンデンサ、135a・・・コンデンサ、136・・・整流用ダイオード

【特許請求の範囲】

【請求項1】

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子。

【請求項2】

前記内部電極の重心は、前記容量素子本体の重心を通る直線上に配置されている

請求項1に記載の静電容量素子。

【請求項3】

前記内部電極は、前記電極本体と、前記電極本体と前記外部端子とを電気的に接続するための接続電極とで構成され、積層される複数の電極本体は同一形状に形成されている

請求項2に記載の静電容量素子。

【請求項4】

前記容量素子本体は、積層方向に直列接続されたコンデンサを構成する複数の内部電極を備える積層体を積層方向に複数個備え、異なる積層体に形成されたコンデンサ同士が並列接続されている

請求項1に記載の静電容量素子。

【請求項5】

隣接する2つの積層体間において、一方の積層体の最上層に形成される内部電極が、他方の積層体の最下層に形成される内部電極を兼ねる

請求項4に記載の静電容量素子。

【請求項6】

前記直列接続されたコンデンサの上層及び/又は下層には、誘電体層を介して積層され、コンデンサを形成しない電極本体が積層方向の直線上に配置された複数の内部電極からなる応力制御部を備え、

前記応力制御部に形成されるコンデンサを形成しない電極本体の重心と前記コンデンサを構成する電極本体の中心が直線上に配置されている

請求項1に記載の静電容量素子。

【請求項7】

前記応力制御部の内部電極は、コンデンサを形成する内部電極のうち最隣接の内部電極と同電位とされている

請求項6に記載の静電容量素子。

【請求項8】

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【請求項1】

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子。

【請求項2】

前記内部電極の重心は、前記容量素子本体の重心を通る直線上に配置されている

請求項1に記載の静電容量素子。

【請求項3】

前記内部電極は、前記電極本体と、前記電極本体と前記外部端子とを電気的に接続するための接続電極とで構成され、積層される複数の電極本体は同一形状に形成されている

請求項2に記載の静電容量素子。

【請求項4】

前記容量素子本体は、積層方向に直列接続されたコンデンサを構成する複数の内部電極を備える積層体を積層方向に複数個備え、異なる積層体に形成されたコンデンサ同士が並列接続されている

請求項1に記載の静電容量素子。

【請求項5】

隣接する2つの積層体間において、一方の積層体の最上層に形成される内部電極が、他方の積層体の最下層に形成される内部電極を兼ねる

請求項4に記載の静電容量素子。

【請求項6】

前記直列接続されたコンデンサの上層及び/又は下層には、誘電体層を介して積層され、コンデンサを形成しない電極本体が積層方向の直線上に配置された複数の内部電極からなる応力制御部を備え、

前記応力制御部に形成されるコンデンサを形成しない電極本体の重心と前記コンデンサを構成する電極本体の中心が直線上に配置されている

請求項1に記載の静電容量素子。

【請求項7】

前記応力制御部の内部電極は、コンデンサを形成する内部電極のうち最隣接の内部電極と同電位とされている

請求項6に記載の静電容量素子。

【請求項8】

誘電体層と、前記誘電体層を介して積層され、静電容量をなす電極本体の重心が積層方向の直線上に配置されるように配置された少なくとも3以上の内部電極とにより2つ以上のコンデンサが形成され、該2つ以上のコンデンサが前記内部電極の積層方向に直列接続された容量素子本体と、

前記容量素子本体の側面に形成され、静電容量をなす前記電極本体に電気的に接続された外部端子と、

を備える静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図19】

【図20】

【図22】

【図23】

【図24】

【図26】

【図27】

【図28】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図6】

【図17】

【図21】

【図25】

【図29】

【図2】

【図3】

【図4】

【図5】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図18】

【図19】

【図20】

【図22】

【図23】

【図24】

【図26】

【図27】

【図28】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図6】

【図17】

【図21】

【図25】

【図29】

【公開番号】特開2013−93363(P2013−93363A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−232897(P2011−232897)

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000108410)デクセリアルズ株式会社 (595)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月24日(2011.10.24)

【出願人】(000108410)デクセリアルズ株式会社 (595)

【Fターム(参考)】

[ Back to top ]