静電容量素子、静電容量素子の製造方法、及び共振回路

【課題】電極の形状、及び電極の積層数を変えること無く、異なる容量を有する静電容量素子を安定して製造する。

【解決手段】誘電体層12と、誘電体層12を狭むように誘電体層12の一方の面上に形成された一方の電極15と誘電体層12の他方の面上に形成された他方の電18極とからなる一対、又は複数対の電極を有した静電容量素子を構成する。一方の電極15と他方の電極18は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極15、又は/及び他方の電極18が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極15を他方の電極18に対して相対的に移動して形成した場合に誘電体層12を挟んで誘電体層12の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【解決手段】誘電体層12と、誘電体層12を狭むように誘電体層12の一方の面上に形成された一方の電極15と誘電体層12の他方の面上に形成された他方の電18極とからなる一対、又は複数対の電極を有した静電容量素子を構成する。一方の電極15と他方の電極18は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極15、又は/及び他方の電極18が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極15を他方の電極18に対して相対的に移動して形成した場合に誘電体層12を挟んで誘電体層12の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、静電容量素子及びそれを備える共振回路に関し、より具体的には、例えばpFオーダーの小さな容量を有する静電容量素子とその製造方法、及びその静電容量素子を備える共振回路に関する。

【背景技術】

【0002】

従来、外部からバイアス信号を印加することにより、容量を変化させて入力信号の周波数や時間などを制御する可変容量素子が活用されている。そのような可変容量素子としては、例えば、可変容量ダイオード(バリキャップ)やMEMS(Micro Electro Mechanical Systems)などが商品化されている。

【0003】

また、従来、上述のような可変容量素子を、非接触IC(Integrated Circuit)カードにおける保護回路として利用する技術が提案されている(例えば、特許文献1参照)。特許文献1に記載の技術では、非接触ICカードをそのリーダライターに近づけた際に、過大な受信信号により耐電圧性の低い半導体素子からなる制御回路が破壊されないようにするために、保護回路として可変容量素子を用いる。

【0004】

図19に、特許文献1で提案されている非接触ICカードのブロック構成図を示す。特許文献1では、可変容量素子として可変容量ダイオード303dを用いる。そして、バイアス除去用コンデンサ303c及び可変容量ダイオード303dの直列回路をコイル303a及びコンデンサ303bからなる共振回路に並列に接続する。

【0005】

特許文献1では、受信信号を検波回路313で検波して得た直流電圧Voutを抵抗314a及び314bで抵抗分割する。そして、抵抗分割された直流電圧(抵抗314bに掛かる直流電圧)を、その直流電圧の変動を除去するために設けられたコイル315を介して可変容量ダイオード303dに印加して、可変容量ダイオード303dの容量を調整する。すなわち、抵抗分割された直流電圧を可変容量ダイオード303dの制御電圧として用いる。

【0006】

特許文献1では、受信信号が過大な場合は、制御電圧により可変容量ダイオード303dの容量が小さくなり、これにより受信アンテナ303の共振周波数が高くなる。この結果、容量が変化する前の受信アンテナ303の共振周波数f0における受信信号のレスポンスは容量低下前より低くなり、受信信号レベルを抑制することができる。特許文献1で提案されている技術では、このようにして可変容量素子により信号処理部320(制御回路)を保護する。

【0007】

また、本発明者らは、従来、可変容量素子として強誘電体材料を用いた素子を提案している(例えば、特許文献2参照)。特許文献2では、信頼性及び生産性の向上を図るために、図20A及び図20Bに示すような電極構造を有する可変容量素子400を提案している。図20Aは、可変容量素子400の概略斜視図であり、図20Bは、可変容量素子400の断面構成図である。特許文献2の可変容量素子400では、直方体形状の誘電体層404の4つの面に、それぞれ端子が設けられる。4つの端子のうち、一方の対向する2つの端子が信号電源403に接続される信号端子403a及び403bであり、他方の対向する2つの端子が制御電源402に接続される制御端子402a及び402bである。

【0008】

可変容量素子400の内部は、図20Bに示すように、複数の制御電極402c〜402g及び複数の信号電極403c〜403fが、誘電体層404を介して交互に積層された構造になっている。具体的には、最下層から、制御電極402g、信号電極403f、制御電極402f、信号電極403e、制御電極402e、信号電極403d、制御電極402d、信号電極403c及び制御電極402cがこの順で誘電体層404を介して積層される。そして、図20Bの例では、制御電極402g、制御電極402e及び制御電極402cが一方の制御端子402aに接続され、制御電極402f及び制御電極402dが他方の制御端子402bに接続される。また、信号電極403f及び信号電極403dは一方の信号端子403aに接続され、信号電極403e及び信号電極403cは他方の信号端子403bに接続される。

【0009】

特許文献2の可変容量素子400では、制御端子及び信号端子に個別に電圧を印加することができるとともに、内部に信号電極及び制御電極を複数積層させるので、低コストで容量を増大することができるという利点がある。また、特許文献2のような構造の可変容量素子400は、製造が容易であり、低コストである。さらに、特許文献2の可変容量素子400では、バイアス除去用コンデンサは不要になる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平08−7059号公報

【特許文献2】特開2007−287996号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

比誘電率の大きい強誘電体材料を用いて、小さい容量の可変容量素子を作製する際には、誘電体層を厚くして電極間距離を大きくする、または、対向する電極面積を小さくする必要がある。しかしながら、誘電体層を厚くすると誘電体層に印加される電界強度が小さくなるので、可変容量素子の容量を変化させるための制御電圧が高くなる。したがって、低電圧で動作する可変容量素子を構成するためには誘電体層の厚さを薄くする必要がある

【0012】

しかしながら、誘電体層の厚さが薄いと容量が大きくなり、対向する電極面積を小さくする必要があるが製造上の制約のため100um以下のように小さな面積にはできないため一層あたりの容量を1pF以下といった小さい容量にできないという問題がある。このため、小さい容量で、かつ、制御電圧が小さい可変容量素子を作成する場合、電極の積層数を変えて異なる容量値の可変容量素子を作製するのが困難となり、容量値の異なる可変容量素子の品揃えを増やすのが困難となる。電極形状を変えることで異なる容量値の可変容量素子を形成することができるが、この場合、電極を形成するためのマスクを容量値の異なる可変容量素子毎に作製する必要がありコストがかかる。

【0013】

また、薄膜キャパシタのように、誘電体層とその誘電体層を狭持する一対の電極のみで構成されるコンデンサにおいては、電極の積層数で容量を変えることができない。このため、誘電体層の厚みが同じ場合は電極形状を変更することで違った容量のコンデンサを作製する。この場合も、電極を形成するためのマスクを容量値の異なるコンデンサ毎に作製する必要がありコストがかかる。

【0014】

本発明は、上記問題を解決するためになされたものであり、本発明の目的は、電極の形状、及び電極の積層数を変えること無く、異なる容量を有する静電容量素子を安定して製造することである。

【課題を解決するための手段】

【0015】

上記課題を解決し、本発明の目的を達成するため、本発明の静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【0016】

本発明の静電容量素子では、一方の電極を他方の電極に対して相対的に移動して形成した場合、誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、変更することができる。このため、同一の電極形状で、異なる容量の可変容量素子を形成することができる。

【0017】

本発明の静電容量素子の製造方法は、誘電体層上面の所望の位置に配置されたマスクを介して、一方の電極、及び他方の電極をパターン形成する。そして、一方の電極又は/及び他方の電極の形成は、一方の電極と他方の電極の誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように誘電体層上に配置するマスクの位置を調整しながら形成する。そして、本発明で形成される静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【0018】

本発明の静電容量素子の製造方法では、一方の電極又は/及び他方の電極の形成は、一方の電極と他方の電極の誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように誘電体層上に配置するマスクの位置を調整しながら形成する。マスク位置を変更することで、一方の電極及び他方の電極との重なり領域で形成される容量部の容量値が所定の容量値となるように調整できる。

【0019】

本発明の共振回路は、静電容量素子を含む共振コンデンサと、共振コンデンサに接続された共振コイルとを備える。静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【発明の効果】

【0020】

本発明によれば、誘電体層を挟んで配置される一対の電極の相対的な電極位置を製造時において調整することにより、完成される静電容量素子の容量値を変更することができる。これにより、電極の形状、及び電極の積層数を変えることなく、異なる容量を有する静電容量素子を安定して製造することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の第1の実施形態に係る可変容量素子の外観を示す斜視図である。

【図2】本発明の第1の実施形態に係る可変容量素子の回路構成例を示す図である。

【図3】第1の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図4】第1の実施形態における第1電極が形成された層の構成を示す図である。

【図5】第1の実施形態における第2電極が形成された層の構成を示す図である。

【図6】A、B 図3のA−A線上に沿う断面を示す図と、図3のB−B線上に沿う断面を示す図である。

【図7】第1の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図8】A、B 図7のA−A線上に沿う断面を示す図と、図7のB−B線上に沿う断面を示す図である。

【図9】A〜D 第1の実施形態における可変容量素子の製造方法を示す製造工程図である。

【図10】比較例に係る可変容量素子をz方向から透過してみたときの構成図である。

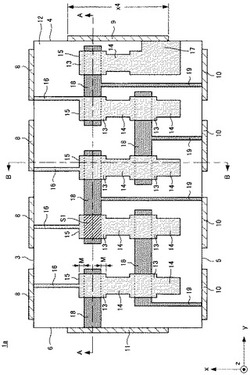

【図11】第1の実施形態の第3の構成例に係る可変容量素子の断面図である。

【図12】第2の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図13】第2の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図14】第3の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図15】第3の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図16】実際の回路上における可変容量素子周辺の回路構成例を示す図である。

【図17】可変容量素子と、バイアス除去用コンデンサとを一体化した可変容量素子の構成例を示した図である。

【図18】本発明の第4の実施形態の非接触ICカードの受信系(復調系)回路部のブロック構成を示す図である。

【図19】従来の非接触ICカードのブロック構成図である。

【図20】A,B 従来の可変容量素子の概略斜視図と、その断面構成図である

【発明を実施するための形態】

【0022】

以下に、本発明の実施形態に係る静電容量素子の一例を、図面を参照しながら、以下の順で説明する。なお、以下に示す例では、静電容量素子として可変容量素子を例に挙げ説明するが、本発明はこれに限定されるものではない。

1.第1の実施形態:可変容量素子

1−1 第1の構成例

1−2 第2の構成例

1−3 第3の構成例

2.第2の実施形態:可変容量素子

2−1 第1の構成例

2−2 第2の構成例

3.第3の実施形態:可変容量素子

3−1 第1の構成例

3−2 第2の構成例

4.第4の実施形態:共振回路

【0023】

〈1.第1の実施形態:可変容量素子〉

第1の実施形態では、容量の変化を制御する制御端子と、信号端子を設けた可変容量素子の一例を説明する。また、本実施形態例の可変容量素子は、pFオーダーの容量を有するものである。

【0024】

図1は本実施形態例の可変容量素子1の外観を示す斜視図であり、以下に説明する各構成例、及び、各実施形態例の可変容量素子に共通の構成である。また、図2に、本実施形態例の可変容量素子1の回路構成図を示す。

【0025】

本実施形態例の可変容量素子1は、後述する強誘電体層12、後述する第1電極15、及び第2電極18とで構成された積層体2と、第1電極15に接続された第1外部端子8、9と、第2電極18に接続された第2外部端子10、11とで構成されている。

【0026】

積層体2はほぼ直方体状に形成されている。第1外部端子8は、積層体2の第1の側面3に複数(図1では4つ)形成され、第1外部端子9は、第1の側面3に隣り合う第2の側面4に形成されている。また、第2外部端子10は、積層体2の第3の側面5に複数(図1では4つ)形成され、第1外部端子11は、第3の側面5に隣り合う第4の側面6に形成されている。また、これらの第1外部端子8、9及び第2外部端子10、11は、積層体2の上面及び下面において、面内に一部張り出すように形成されている。

【0027】

そして、第1外部端子8、9及び第2外部端子10、11には図2に示すように電源からバイアス抵抗Rを介して制御電圧V及び信号電圧が供給される。本実施形態例では、第1外部端子8及び第2外部端子10が制御(DC)端子で、第1外部端子9及び第2外部端子11が信号(AC)端子である。ここで、第1外部端子9及び第2外部端子11は、信号端子と制御端子を兼ねる構成とされている。そして、第1電極15及び第2電極18により複数の容量部が形成され、それらの容量部が直列に接続されている。

以下の説明では、積層体2における各層の積層方向をz方向とし、積層方向に垂直な面における短軸方向をx方向、長軸方向をy方向とする。

【0028】

本実施形態例の可変容量素子1は、容量部を構成する第1電極15及び第2電極18の電極形状を変えることなく、その形成位置を異ならせることによって容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例、第3の構成例について順に説明する。

【0029】

[1−1 第1の構成例]

図3は、本実施形態例の第1の構成例に係る可変容量素子1aをz方向から透過してみたときの構成図である。また、図4は、可変容量素子1aの第1電極をz方向から透過してみたときの構成図であり、図5は、可変容量素子1bの第2電極をz方向から透過してみたときの構成図である。また、図6Aは、図3のA−A線上に沿う断面を示す図であり、図6Bは、図3のB−B線上に沿う断面を示す図である。

【0030】

本実施形態例の可変容量素子1aでは、同一平面に形成された複数の第1電極15と、同一平面に形成された複数の第2電極18が、強誘電体層12を狭持するように配置されている。そして、その第1電極15の上側、及び第2電極18の下側にさらに1層ずつ強誘電体層12が積層された構成とされている。

【0031】

強誘電体層12(誘電体層)は、外部から印加される制御信号に応じて容量が変化する誘電体材料で形成される。例えば、第1電極15と第2電極18とで挟まれる1層分の強誘電体層12は、比誘電率が1000を超えるような強誘電体材料で形成されたシート状部材(厚さは、例えば2μm程度)で構成することができる。なお、強誘電体層12の電極が形成される面及びそれとは反対側の面の形状は長方形であり、その長辺と短辺の比は、例えば、2:1にすることができる。

【0032】

強誘電体層12の形成材料としては、イオン分極を生じる強誘電体材料を用いることができる。イオン分極を生じる強誘電体材料は、イオン結晶材料からなり、プラスのイオンとマイナスのイオンの原子が変位することで電気的に分極する強誘電体材料である。このイオン分極を生じる強誘電体材料は、一般に、所定の2つの元素をA及びBとすると、化学式ABO3(Oは酸素元素)で表され、ペロブスカイト構造を有する。このような強誘電体材料としては、例えば、チタン酸バリウム(BaTiO3)、ニオブ酸カリウム(KNbO3)、チタン酸鉛(PbTiO3)等が挙げられる。また、強誘電体層12の形成材料として、例えば、チタン酸鉛(PbTiO3)にジルコン酸鉛(PbZrO3)を混ぜ合わせたPZT(チタン酸ジルコン酸鉛)を用いてもよい。

【0033】

また、強誘電体層12の形成材料として、電子分極を生じる強誘電体材料を用いてもよい。この強誘電体材料では、プラスの電荷に偏った部分と、マイナスの電荷に偏った部分とに分かれて電気双極子モーメントが生じ、分極が生じる。そのような材料として、従来、Fe2+の電荷面と、Fe3+の電荷面の形成により、分極を形成して強誘電体的特性を示す希土類鉄酸化物が報告されている。この系においては、希土類元素をREとし、鉄族元素をTMとしたときに、分子式(RE)・(TM)2・O4(Oは酸素元素)で表される材料が高誘電率を有することが報告されている。なお、希土類元素としては、例えば、Y、Er、Yb、Lu(特にYと重希土類元素)が挙げられ、鉄族元素としては、例えば、Fe、Co、Ni(特にFe)が挙げられる。また、(RE)・(TM)2・O4としては、例えば、ErFe2O4、LuFe2O4、YFe2O4が挙げられる。また、強誘電体層12の形成材料として、異方性を有する強誘電体材料を用いてもよい。

【0034】

第1電極15は、図6A、図6Bに示すように、積層体2の真ん中に積層された強誘電体層12の上面に複数(図3では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。図4に示すように、各第1電極15は、y方向の電極幅がy1、x方向の電極幅がx1とされた長方形状の第1電極部13と、y方向の電極幅がy2(<y1)、x方向の電極幅がx1とされた長方形状の第2電極部14とがx方向に交互に接続された構成とされている。そして、積層体2の第4の側面6側から順に形成された4つの第1電極15は、第1電極部13と第2電極部14とが交互に2つずつ接続された構成とされている。一方、第2の側面4側に最隣接する第1電極15は、第1電極部13と第2電極部14が1つずつ接続された構成とされている。

【0035】

以上のように、第1電極15がy方向の電極幅が異なる第1電極部13と第2電極部14とによって構成されることにより、それぞれの第1電極15はx方向に2つの電極幅を有する構成とされる。そして、第1電極15の各第1電極部13の位置はy方向に水平とされ、各第2電極部14の位置はy方向に水平とされている。

【0036】

そして、積層体2の第4の側面6側から順に形成された4つの第1電極15のそれぞれは、積層体2のy方向の第1の側面3に露出するように第1電極15と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極15は、積層体2のx方向の第2の側面4に露出するように強誘電体層12の上面に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0037】

第2電極18は、図6A、図6Bに示すように、積層体2の真ん中に積層された強誘電体層12の下面に複数(図3では5つ)形成されている。図5に示すように、第2電極18は、y方向の電極幅がy3(>y1)とされ、x方向の電極幅がx2(<x1、<y3)とされた長方形状をなし、y方向に延在して形成されている。そして、各第2電極18は、x方向及びy方向に離間して設けられており、その長軸方向が、第1電極15の長軸方向と直交するように設けられている。また、第2電極18は、1つの第1電極15に交差するか、若しくは、y方向に隣接する2つの第1電極15に跨って配置され、第1電極15の第1電極部13と第2電極18が、z方向に重なるように配置されている。

【0038】

積層体2の第2の側面4側から順に形成された4つの第2電極18は、積層体2の第1の側面3に対向する第3の側面5に露出するように第2電極18と同層に形成されたそれぞれの内部端子19に接続されている。そして、この内部端子19は、積層体2の第3の側面5に形成された第2外部端子10に接続されている。また、積層体2の第4の側面6に最隣接する第2電極18は、第4の側面6に露出するように形成されている。そして、この第2電極18は、積層体2の第4の側面6に形成された第2外部端子11に接続されている。

【0039】

ここで、図3に示すように、積層体2の第4の側面6側から奇数番目の第2電極18を第1の側面3側に位置する第1電極部13の下層に配置し、偶数番目の第2電極18を第3の側面5側に位置する第1電極部13の下層に配置する。さらに、奇数番目の第2電極18と偶数番目の第2電極18とをx方向に重ならないように配置する。このような電極レイアウトとすることにより、第2電極18に接続されるそれぞれの内部端子19の引き回しを容易にすることができる。図3では、奇数番目の第2電極18を積層体2の第1の側面3側に配置し、偶数番目の第2電極18を第3の側面5側に配置する例としたが、逆の配置であってもよい。

【0040】

そして、第1の構成例に係る可変容量素子1aでは、図6A、及び図6Bに示すように、第1電極15の各第1電極部13と、その第1電極部13に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部20が形成される。容量部20では、第1電極15における第1電極部13と第1電極部13に対向する第2電極18との間で容量値C1が得られる。そして、第1の構成例に係る可変容量素子1aでは、第1電極15の第1電極部13と第2電極18がz方向に重なるような構成とされることにより、各容量部20を構成する電極面積は第1電極15と第2電極18の重なり面積S1(=x2×y1)とされる。

【0041】

また、第1の構成例における可変容量素子1aでは、同層に複数の第1電極15と複数の第2電極18とが構成され、さらに、一つの第1電極15に対して一つ、又は二つの第2電極18がz方向に重なるように構成される。これにより、同一面内において複数個の容量部20が形成される。

【0042】

[1−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子1bについて説明する。図7は、本実施形態例の第2の構成例に係る可変容量素子1bをz方向から透過してみたときの構成図である。また、図8Aは、図7のA−A線上に沿う断面構成であり、図8Bは、図7のB−B線上に沿う断面構成である。図7、図8A、及び図8Bにおいて、図3、図6A、及び図6Bに対応する部分には同一符号を付し重複説明を省略する。

【0043】

第2の構成例の可変容量素子1bでは、第1の構成例の可変容量素子1aに比較し、第1電極15が距離x1だけx方向の第1の側面側にシフトして形成されている。このため、第2電極18は、強誘電体層12を挟んで、第1電極15を構成する第2電極部14とz方向に重なるように配置されている。

【0044】

そして、第2の構成例に係る可変容量素子1bでは、図8A、図8Bに示すように、第1電極15の各第2電極部14と、その第2電極部14に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部21が形成される。容量部21では、第1電極15における第2電極部14と第2電極部14に対向する第2電極18との間で容量値C2が得られる。そして、第2の構成例に係る可変容量素子1bでは、第1電極15の第2電極部14と第2電極18がz方向に重なるような構成とされることにより、各容量部21を構成する電極面積は第1電極15と第2電極18の重なり面積S2(=x2×y2)とされる。

【0045】

第1電極15における第2電極部14のy方向の幅は、第1電極部13のy方向の幅よりも小さい。このため、第2の構成例における可変容量素子1bでは、各容量部21を構成する電極面積(S2)は、第1の構成例における可変容量素子1aの各容量部20を構成する電極面積(S1)よりも小さい。これにより、第2の構成例における可変容量素子1b全体の容量は、第1の構成例における可変容量素子1a全体の容量よりも小さくなる。

【0046】

このように、本実施形態例の可変容量素子1では、第1電極15、及び第2電極18の形状は同じであっても、第2電極18に対して相対的に移動することによって、容量値の異なる2種類の可変容量素子を構成することができる。

【0047】

本実施形態例の第1の構成例及び第2の構成例で形成される可変容量素子1a、1bは、図2に示すように、誘電体層12の内部に形成された第1電極15及び第2電極18により容量部が形成され、それらの容量部は直列接続される。そして、それらの容量部に、バイアス抵抗Rを介してGNDと制御電圧+Vを印加することで、それぞれの容量部に+Vの制御電圧が加わる。一方、信号電圧(AC電圧)は、9個直列された容量部を経由するため、全体の容量は1/9になるが、制御電圧は、それぞれの容量部に個別に加わるため、小さい値でもよい。すなわち、本実施形態例の可変容量素子1では、容量値を小さくして、制御電圧を高くしない回路的な工夫がされている。なお、バイアス抵抗Rは、一般的に500KΩ〜1MΩ程度である。

【0048】

[可変容量素子の製造方法]

次に、本実施形態例の第1の構成例、及び第2の構成例に係る可変容量素子1a、1bの製造方法について説明する。図9A〜図9Dは、本実施形態例に係る第1の構成例及び第2の構成例に係る可変容量素子1a、1bの製造工程図である。

【0049】

まず、図9Aに示すように、上述した強誘電体材料からなるシート部材(図9Aでは2枚)を用意する。なお、このシート部材が上述した強誘電体層12となり、一方は、上面に第1電極15が形成される強誘電体層12で、他方が、上面に第2電極18が形成される強誘電体層12である。

【0050】

次に、例えばPd、Pd/Ag、Ni等の金属微粉末をペースト化した導電ペーストを調整する。また、第1電極15の形状が開口された第1のマスク37と、第2電極18の形状が開口された第2のマスク38を準備する。そして、図9Bに示すように、第1のマスク37を一方のシート部材(強誘電体層12)上面の所定の位置に位置あわせして配置し、第2のマスク38を他方のシート部材(強誘電体層12)上面の所定の位置に位置あわせして配置する。

【0051】

その後、図9Cに示すように、第1のマスク37を介して一方のシート部材上部に導電ペーストを塗布(シルク印刷)し、第2のマスク38を介して他方のシート部材上部に導電ペーストを塗布する。これにより、それぞれのマスクの開口部分においてシート部材上部に導電ペーストが塗布されるので、一方のシート部材上部には第1電極15がパターン形成され、他方のシート部材上部に第2電極18がパターン形成される。

【0052】

そして、図9Dに示すように、第1のマスク37、及び第2のマスク38をそれぞれのシート部材上部から外すことにより、第1電極15が形成された強誘電体層12と、第2電極18が形成された強誘電体層12が形成される。

【0053】

この製造方法において、第1の構成例における可変容量素子1aを形成する場合には、シート部材を重ねたときに、第1電極15の第1電極部13の下層に第2電極18が重なるように、第1のマスク37及び第2のマスク38をそれぞれのシート部材に位置あわせする。

【0054】

一方、第2の構成例における可変容量素子1bを形成する場合には、シート部材を重ねたときに、第1電極15の第2電極部14の下層に第2電極18が重なるように、第1のマスク37と第2のマスク38をそれぞれのシート部材に位置あわせする。すなわち、第2の構成例における可変容量素子1bを形成する場合には、第1電極15の形成において、第1の構成例における可変容量素子1aを形成する場合に比較し、第1のマスク37をx方向の内部端子16が形成された側に距離x1だけずらしてシート部材上に配置する。

【0055】

ここで、第1の構成例の可変容量素子1aと第2の構成例の可変容量素子1bでは、それぞれの第1電極15の内部端子16はその長さが異なっている。このため、本実施形態例の製造方法では、マスクの位置を所定の距離だけ動かした場合にも、積層体2の側面に露出する内部端子16が形成されるようにマスクの内部端子16に対応する部分の開口が形成されている。

【0056】

その後、第2電極18(電極ペースト層)が塗布されたシート部材と、第1電極15(電極ペースト層)が塗布されたシート部材とを、シート部材と電極ペースト層が交互になるように下から積層する。そして、必要に応じて、最上層の第1電極15上部に電極ペースト層が形成されないシート部材を積層し、シート部材と導電ペースト層からなる積層体2を形成する。

【0057】

次いで、その積層体2を加熱圧着する。加熱圧着した部材を還元雰囲気中で高温焼成してシート部材と導電ペースト層(第1電極15、第2電極18)を一体化させる。その後、積層体2の第1の側面3〜第4の側面6に第1外部端子8、9、及び第2外部端子10、11を形成することにより、第1の構成例、又は第2の構成例に係る可変容量素子1a、1bが完成される。

このように、本実施形態例の可変容量素子1では、電極製造時のマスク位置を異ならせることで、第1の構成例、及び第2の構成例で示した通り、容量の異なる可変容量素子を形成することができる。

【0058】

本実施形態例の可変容量素子の製造方法は、上述のものに限られるものではない。例えば、薄膜キャパシタでは、電極はPtなどをSiなどの基板上にスパッタ法を用いて作成し不要な部分をエッチングにより除去し形成するが、不要な部分をエッチングするためのマスクの位置を下部電極と上部電極で相対的にシフトさせることで電極位置をシフトさせることが可能になる

【0059】

[電極形状の設計概要]

本実施形態例では、同じ電極形状であっても、その形成位置を調整することで容量値の異なる可変容量素子1a、1bを構成できるようにするため、第1電極15及び第2電極18の寸法をある程度考慮する必要がある。以下に、本実施形態例の可変容量素子1の第1電極15、第2電極18の形状及び寸法の設計概要を説明する。

【0060】

第1電極15における第1電極部13及び第2電極部14のx方向の電極幅x1は、第1電極15と第2電極18との製造時における意図しない位置ずれを考慮して、第2電極18のx方向の電極幅x2よりも所定の幅だけ広い構成とされるのが好ましい。これにより、図3でみると、第1電極15のx方向の中心位置と、第2電極18のx方向の中心位置を一致させた場合、重なり面積S1のx方向の両端にマージンM((x1−x2)/2)(第2電極18と重ならない領域)が形成される。このマージンMは、第1電極15と第2電極18との間の合わせずれを吸収できる幅であることが好ましく、例えば、10μm以上であることが好ましい。そして、製造上の制約も含めば、電極幅x1は、50μm以上であることが好ましく、より好適には、100μm以上であることが好ましい。

【0061】

このように、マージンMが形成されることにより、例えば、第1電極15が第2電極18に対して所定の位置からx方向にずれてしまった場合、そのずれ量がマージンMの幅よりも小さければ、第1電極15と第2電極18との重なり面積は変わらない。このため、一方向に電極位置をシフトさせるのみで所望の容量値を有する可変容量素子を形成することができるため、異なる容量値を有する可変容量素子の形成が容易となる。また、第1の構成例と第2の構成例とでは、第1電極15の位置が、第1電極部13及び第2電極部14のx方向の電極幅x1だけ異なる。この電極幅x1は、マージンMに比較して十分大きく、意図的にマスク位置を異ならせることでずらすことができる幅である。したがって、本実施形態例の可変容量素子1では、微少な合わせずれ程度では第1電極15と第2電極18の重なり面積は変わらず、意図した電極位置の移動によってのみ、第1電極15と第2電極18の重なる面積を変えることができる。

【0062】

また、本実施形態例では、第1電極15を構成する第1電極部13と第2電極部14のy方向の幅の違いにより第1の構成例における可変容量素子1aと第2の構成例における可変容量素子1bの容量値を変えることができる。したがって、電極幅y1と電極幅y2とを、例えば、y1:y2=1:0.8の関係となるような電極幅とすることにより、第1の構成例の可変容量素子1aの容量値と、第2の構成例の可変容量素子1bの容量値との比を1:0.8に設定することができる。ただし、電極幅y1と電極幅y2は異なる幅であればよく、種々の設定が可能である。

【0063】

また、第2電極18のy方向の電極幅y3は、第1電極15のy方向の最大の電極幅、すなわち、第1電極部13のy方向の電極幅y1よりも大きければよい。本実施形態例では、積層体2の第4の側面6に最隣接する第2電極18は、第4の側面6の第2外部端子11に接続されるため、積層体2の側面に露出する長さに形成される必要がある。また、その他の第2電極18は、それぞれ、2つの第1電極15に跨って形成されるため、y方向の電極幅y3は隣接する2つの第1電極を含むy方向の幅よりも大きく形成される必要がある。

【0064】

そして、本実施形態例では、第2電極18が長方形状とされ、その長軸方向(y方向)が第1電極15の長軸方向(x方向)に直交するように配置されている。このため、合わせずれにより、第2電極18と第1電極15とが所定の位置からy方向にずれてしまった場合にも、第2電極18と第1電極15との重なり面積は変化しない。これにより、y方向の位置ずれによって容量値が変化しない。

【0065】

また、本実施形態例では、第1の構成例に係る可変容量素子1aと第2の構成例に係る可変容量素子1bとで、第1電極15の形成位置をx方向に所定の量だけシフトする必要がある。このシフト量は、デバイスのx方向の長さと、デバイスサイズで制約される外部端子の長さによる制約を受ける。例えば、シフト量を積層体2の第2の側面4に形成される第1外部端子9のx方向の長さx4よりも大きくすると、第2の側面4に最隣接する第1電極15において、その内部端子17と第1外部端子9とを接続できなくなってしまうことがある。このため、本実施形態例の可変容量素子1では、第1電極15のシフト量を積層体2の第2の側面4に形成される第1外部端子9のx方向の長さx4よりも小さくしなければならない制約がある。第2の側面4に最隣接する第1電極15の内部端子17のx方向の幅x3を第1外部端子9のx方向の長さx4よりも大きくすることで、この制約を無くすことも可能である。しかしながら、電極作製の容易性、マスクシフトの容易性から、第1電極15のシフト量は第1外部端子9のx方向の長さx4よりも小さくすることが好ましい。なお、積層体2のy方向の幅が1.0mmで、x方向の幅が0.5mの小型サイズの可変容量素子の場合を考えると、第2の側面4に形成される第1外部端子9のx方向の長さx4は200〜300mmである。このため、第1電極15のシフト量は100〜200mmの範囲とするのが好ましい。

【0066】

[比較例]

次に、比較例に係る可変容量素子を示す。図10は、比較例に係る可変容量素子100をz方向から透過してみたときの構成図である。比較例に係る可変容量素子100の外観は、図1に示した本実施形態例の可変容量素子1と同様とし、図示を省略する。図10において、図3に対応する部分には同一符号を付し、重複説明を省略する。

【0067】

比較例に係る可変容量素子100は、第1電極101の形状が本実施形態例の可変容量素子1と異なる例である。

図10に示すように、比較例に係る可変容量素子100では、複数(図10では5つ)の第1電極101が積層体2の真ん中に積層された強誘電体層12の上面に形成されており、y方向の一方の側から他方の側にかけて、所定の距離ずつ離間して形成されている。第1電極101のそれぞれは、y方向の電極幅がy4、x方向の電極幅がx5(>x2)の長方形状に形成されている。

【0068】

そして、5つの第1電極101のうち、積層体2の第2の側面4に最隣接する第1電極101は、内部端子17を介して第2の側面4に形成された第1外部端子9に接続さる。残りの第1電極101は、内部端子16を介して積層体2の第1の側面3に形成されたそれぞれの第1外部端子8に接続される。

【0069】

比較例に係る可変容量素子100では、第2電極18は、1つの第1電極101に交差するか、若しくは、隣接する2つの第1電極101に跨るように交差して配置されている。そして、第1電極101と第2電極18とがz方向に重なる領域において容量部が形成される。容量部を構成する第1電極101及び第2電極18の電極面積は、第1電極101と第2電極18とのz方向の重なり面積S3(=x2×y4)とされる。

【0070】

比較例における可変容量素子100では、図10の波線で示すように、例えば第1電極101がΔxだけx方向に移動した場合にも、第2電極18と第1電極101との重なり面積S4は変わらない。このため、z方向に重なる第1電極101と第2電極18とその間に形成される強誘電体層12で形成される容量部の容量値は変化しない。比較例の可変容量素子100において、その容量値を変化させたい場合には、積層される電極の積層数を変化させたり電極形状を変えたりする必要がある。電極形状を変化させるには、異なるマスクを用いて電極を形成する必要がありコストがかかり、また、一層当たりの容量が大きい場合には、積層数を大きくして容量値を変える場合、容量値を大きく変化させることができても小さくすることはできない。

【0071】

一方、本実施形態例の可変容量素子1(1a、1b)では、第1電極15が、2つ以上の電極幅を有して構成されている。このため、強誘電体層12表面に第1電極15を形成するときのマスク位置を一方向(この場合x方向)に所定の量だけ移動させることで、第2電極18と第1電極15の重なり面積を容易に変えることができる。これにより、積層数が同じでありながら、違った容量の可変容量素子1(1a、1b)を得ることができる。そして、この場合、電極を形成するためのマスクを変更する必要がなく、製造プロセスの大きな変更も不要なため、高品質で低価格な可変容量素子1(1a、1b)を得ることができる。

【0072】

本実施形態例では、第1電極15の位置をx方向に移動して形成することで、容量値の異なる可変容量素子1(1a、1b)を構成する例とした。しかしながら、本発明は、これに限られるものではなく、第2電極18の位置をx方向に移動して形成することによっても、容量値の異なる可変容量素子を形成することができる。すなわち、第1電極15と第2電極18とが相対的に所定の量だけシフトするように第1電極15及び第2電極18を形成すれば容量値の異なる可変容量素子を形成できる。また、本実施形態例では、一方の電極を一方向に所定の量だけずらして形成することで容量を変えることができるため、位置決めが容易である。このような構成は、特に、pFオーダーの容量値を有する可変容量素子において容量値を微小変化させるのに有効である。

【0073】

また、本実施形態例では、強誘電体層12を挟んで複数対の第1電極15と第2電極18がz方向に重なるように構成することによって、同層で複数の容量部を構成する例としたが、1対の第1電極15と第2電極18とにより容量部を構成する例としてもよい。さらに、本実施形態例では、第1電極15と第2電極18とを強誘電体層12を挟んで複数層積層する構成としてもよい。例えば、3層の第1電極15と3層の第2電極18を交互に積層させることによって、5層の容量部を形成することができる。第1の構成例に係る可変容量素子1aにおいて1層分の容量値C1が9pFである場合は、5層の容量部で構成される容量値は45pFとなる。また、第2の構成例に係る可変容量素子1bにおいて1層分の容量値C2が8pFである場合は、5層の容量部で構成される容量値は40pFとなる。

【0074】

[1−3 第3の構成例]

以下に、第3の構成例として、第1の構成例に係る可変容量素子1aと第2の構成例に係る可変容量素子1bとを複数層ずつ積層して形成した可変容量素子を示す。図11は、第3の構成例に係る可変容量素子1cの断面構成を示す図である。図11において、図6A、図6B、図8A、及び図8Bに対応する部分には同一符号を付し、重複説明を省略する。

【0075】

図11では、簡単のため、同一層内に形成される第1電極15、及び第2電極18をそれぞれ一つずつ図示する。

図11に示すように、第3の構成例に係る可変容量素子1cは、3層の第2電極18と3層の第1電極15とが交互に積層された構成とされている。そして、3層の第1電極15のうち、下層の第1電極15と、上層の第1電極15は、対向する第2電極18に対して、第1の構成例に係る可変容量素子1aの第1電極15の位置と同様になるように形成されている。一方、3層の第1電極15のうち、真ん中の第1電極15は、対向する第2電極18に対して第2の構成例に係る可変容量素子1bの第1電極15の位置と同様になるように形成されている。

【0076】

すなわち、第3の構成例に係る可変容量素子1cでは、真ん中の第1電極15が、他の2つの第1電極15に比較してx方向に電極幅x1分だけずらして形成されている。これにより、下層の第1電極15とそれに対向する第2電極18とで第1の構成例に示した可変容量素子1aが2層形成される。また、真ん中の第1電極15とそれに対向する第2電極18とで第2の構成例に示した可変容量素子1bが2層形成される。また、上層の第1電極15とそれに対向する第2電極18とで第1の構成に示した可変容量素子1bが2層形成される。

【0077】

以上の構成では、例えば、第1の構成例に係る可変容量素子1aの容量値C1を9pF、第2の構成例に係る可変容量素子1bの容量値C2を8pFとすると、全体の容量値が、3×9+8×2=43pFとなる。このように、第2電極18と第1電極15とを交互に複数層形成した可変容量素子1cにおいて、形成位置を異ならせた複数の第1電極15を用いることによって層毎に容量値を異ならせることができる。そして、積層数や、第1の構成例に係る可変容量素子1aを構成する層の数や、第2の構成例に係る可変容量素子1bを構成する層の数を自由に設計することができるため、種々の容量値を有する可変容量素子を構成することができる。

【0078】

〈2.第2の実施形態:可変容量素子〉

次に、本発明の第2の実施形態について説明する。本実施形態例の可変容量素子の外観は、図1と同様であるから図示を省略する。本実施形態例の可変容量素子は、容量部を構成する電極形状を変えることなく、その形成位置を異ならせることによって、容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例について順に説明する。

【0079】

[2−1 第1の構成例]

図12は、本実施形態例の第1の構成例に係る可変容量素子22aをz方向から透過してみたときの構成図である。図12において、図3に対応する部分には同一符号を付し重複説明を省略する。

【0080】

第1電極23は、積層体2の真ん中に積層された強誘電体層12の上面に複数(図12では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。各第1電極23は、積層体2の第1の側面3を構成するy方向の辺から時計回りに約45°回転した第1方向に延在して形成されている。また、各第1電極23は、第1電極部25と、第2電極部24とが第1方向に交互に接続された構成とされている。第1電極部25は、第1方向の電極幅がw1、第1方向に直行する第2方向の電極幅がw2とされた長方形状とされ、第2電極部24は、第1方向の電極幅がw1、第2方向の電極幅がw3とされた長方形状とされている。図12では、積層体2の第4の側面6側から順に形成された4つの第1電極23は、第1電極部25と第2電極部24とが交互に4つ接続された構成とされている。また、第2の側面4側に最隣接する第1電極15は、第1電極部25と第2電極部24が接続された構成とされている。

【0081】

以上のように、第1電極23が第2方向の電極幅が異なる第1電極部25と第2電極部24とによって構成されることにより、それぞれの第1電極23は第1方向に2つの電極幅を有する構成とされる。また、本実施形態例では、第1電極23の各第1電極部25の位置はy方向に水平とされ、各第2電極部24の位置はy方向に水平とされている。

【0082】

積層体2の第4の側面6側から順に形成された4つの第1電極23のそれぞれは、積層体2の第1の側面3に露出するように第1電極23と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極23は、積層体2の第2の側面4に露出するように第1電極23と同層に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0083】

第2電極26は、積層体2の真ん中に積層された強誘電体層12の下面に複数(図12では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。第2電極26は、第1方向の電極幅がw4(<w1)とされ、第2方向の電極幅がw5(>w2)とされた長方形状とされ、第2方向に延在して形成されている。

【0084】

そして、第2電極26は、1つの第1電極23に直交するか、若しくはy方向に隣接する2つの第1電極23に跨って交差するように形成されており、第1電極23の第1電極部25と第2電極26がz方向に重なるように配置されている。

積層体2の第2の側面4に近い側の4つの第2電極26は、積層体2の第1の側面3に対向する第3の側面5に露出するように第2電極26と同層に形成されたそれぞれの内部端子19に接続されている。そして、この内部端子19は、積層体2の第3の側面5に形成された第2外部端子10に接続されている。また、積層体2の第4の側面6に最隣接する第2電極26は、第4の側面6に露出するように形成されている。そして、この第2電極26は、積層体2の第4の側面6に形成された第2外部端子11に接続されている。

【0085】

以上により、第1の構成例に係る可変容量素子22aでは、図12に示すように、第1電極23の各第1電極部25と、その第1電極部25に強誘電体層12を挟んで積層された第2電極26がz方向に重なる領域において容量部が形成される。また、図12の可変容量素子22aでは、複数の第1電極23と複数の第2電極26とが構成され、さらに、一つの第1電極23に対して一つ、又は二つの第2電極26がz方向に重なるように構成される。これにより、同一面内において複数個の容量部が形成される。そして、第1の構成例に係る可変容量素子22aでは、第1電極23の第1電極部25と第2電極26がz方向に重なるような構成とされることにより、各容量部を構成する電極面積は第1電極23と第2電極26の重なり面積S4(=w2×w4)とされる。

【0086】

[2−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子について説明する。図13は、本実施形態例の第2の構成例に係る可変容量素子22bをz方向から透過してみたときの構成図である。図13において、図12に対応する部分には同一符号を付し重複説明を省略する。

【0087】

第2の構成例の可変容量素子22bでは、第1の構成例の可変容量素子22aに比較し、第1電極23が図13に示すように距離x6だけx方向の第3の側面側にシフトして形成されている。距離x6は、第1電極23の第2電極部24と第2電極26がz方向に重なる配置となる距離である。このため、第2電極26は、強誘電体層12を挟んで、第1電極23を構成する第2電極部24とz方向に重なるように配置されている。

【0088】

以上により、第2の構成例に係る可変容量素子22bでは、強誘電体層12を挟んでz方向に対向する第1電極23の各第2電極部24と、第2電極26とで容量部が形成される。そして、第2の構成例に係る可変容量素子22bでは、第1電極23の第2電極部24と第2電極26がz方向に重なるような構成とされることにより、各容量部を構成する電極面積は第1電極23と第2電極26の重なり面積S5(=w3×w4)とされる。

【0089】

第1電極23における第2電極部24の第2方向の電極幅w3は、第1電極部25の第2方向の電極幅w2よりも小さい。このため、第2の構成例における可変容量素子22bでは、各容量部を構成する電極面積は、第1の構成例における可変容量素子22aの各容量部を構成する電極面積よりも小さい。これにより、第2の構成例における可変容量素子22a全体の容量は、第1の構成例における可変容量素子22b全体の容量よりも小さくなる。

【0090】

このように、本実施形態例では、第1電極23、及び第2電極26の形状は同じであっても、第1電極23の形成位置をずらすことによって、容量値の異なる2種類の可変容量素子22a、22bを構成することができる。

【0091】

本実施形態例の可変容量素子22a、22bも、第1の実施形態と同様にして形成することができる。したがって、本実施形態例においても、電極形成時に用いるマスクを第1の構成例における可変容量素子22aを形成する場合と、第2の構成例における可変容量素子22bを形成する場合とで変える必要がない。第1の構成例の可変容量素子22aを形成する場合には、z方向に第2電極26と第1電極23の第1電極部25が積層するような位置関係となるように、各電極を強誘電体層12上にパターン形成すればよい。また、第2の構成例の可変容量素子22bを形成する場合には、z方向に第2電極26と第2電極部24が積層するような位置関係となるように、各電極を強誘電体層12上にパターン形成すればよい。

【0092】

また、本実施形態例においても、同じ電極形状であってもその形成位置を調整することで容量値の異なる可変容量素子22a、22bを形成できるようにするため、第1電極23及び第2電極26の寸法をある程度考慮する必要がある。以下に、本実施形態例の可変容量素子22a、22bの第1電極23、第2電極26の形状及び寸法の設計概要を説明する。

【0093】

第1電極23の第1電極部25及び第2電極26の第1方向の電極幅w1は、第1電極23と第2電極26との製造時における意図しない位置ずれを考慮して、第2電極26の第1方向の電極幅w4よりも所定の幅だけ広い構成とされるのが好ましい。これにより、図12でみると、第1電極部25の第1方向の中心位置と、第2電極26の第1方向の中心位置を一致させた場合、重なり面積S4の第1方向の両端にマージンM((w1−w2)/2)(第2電極26と重ならない領域)が形成される。このマージンMは、第1電極23と第2電極26との間の合わせずれを吸収できる幅であることが好ましく、例えば、10μm以上であることが好ましい。そして、製造上の制約も含めば、電極幅w1は、50μm以上であることが好ましく、より好適には、100μm以上であることが好ましい。

【0094】

このように、マージンMが形成されることにより、例えば、第1電極23が第2電極26に対して所定の位置から第1方向にずれてしまった場合、そのずれ量がマージンMの幅よりも小さければ、第1電極23と第2電極26との重なり面積は変わらない。このため、所望の容量値を有する可変容量素子を形成することが容易となる。また、第1の構成例と第2の構成例とでは、図13に示すように、第1電極23の位置が、第1電極部25及び第2電極部24のx方向の電極幅x6だけ異なる。この電極幅x6は、マージンMに比較して十分大きく、意図的にマスク位置を異ならせることでずらすことができる幅である。したがって、本実施形態例では、微少な合わせずれ程度では第1電極23と第2電極26の重なり面積は変わらず、意図した電極位置の移動によってのみ、第1電極23と第2電極26の重なる面積を変えることができる。

【0095】

また、第1電極23の第1電極部25の第1方向の電極幅と、第2電極部24の第2方向の電極幅の違いによって、第1の構成例の可変容量素子22aと、第2の構成例の可変容量素子22bとで容量値を異ならせることができる。したがって、電極幅w2と電極幅w3とを、例えば、w2:w3=1:0.8の関係となるような電極幅とすることにより、第1の構成例の可変容量素子22aの容量値と、第2の構成例の可変容量素子22bの容量値との比を1:0.8に設定することができる。ただし、電極幅w2と電極幅w3は異なる幅であればよく、種々の設定が可能である。

【0096】

また、第2電極26の第2方向の電極幅w5は、第1電極23の第1方向の最大の電極幅w2、すなわち、第1電極部25の第1方向の電極幅w2よりも大きければよい。本実施形態例では、積層体2の第4の側面6に最隣接する第2電極26は、第4の側面6の第2外部端子11に接続されるため、積層体2の第4の側面6に露出する長さに形成される必要がある。また、その他の第2電極26は、それぞれ、2つの第1電極23に跨って形成されるため、第2方向の電極幅w5は隣接する2つの第1電極23を含む第2方向の幅よりも大きく形成される必要がある。

【0097】

そして、本実施形態例では、第2電極26が長方形状とされ、その長軸方向(第2方向)が第1電極23の長軸方向(第1方向)に直交するように配置されている。このため、合わせずれにより、第2電極26と第1電極23とが所定の位置から相対的に第2方向にずれてしまった場合にも、第2電極26と第1電極23との重なり面積は変化しない。これにより、第2方向の位置ずれによって容量値が変化しない。

その他、第1の実施形態に係る可変容量素子1(1a、1b)の電極構成と同様にして各電極の寸法を設計すればよい。

【0098】

本実施形態例では、第1電極23を強誘電体層12上面に斜め配置し、第2電極26を第1電極23に直交するように強誘電体層12下面に斜め配置する。これにより、第1の実施形態に係る可変容量素子1(1a、1b)に比較し、第2電極26の内部端子19を短く構成することができる。これにより、電極抵抗を低くすることができる。また、本実施形態例においても、第1の実施形態例に係る第3の構成例のような構成とすることもできる。

その他、第1の実施形態と同様の効果を得ることができる。

【0099】

ところで、第1及び第2の実施形態では、第1電極を長軸方向に2つの電極幅を有するように形成し、その幅方向に交差する第2電極を配置することで、第1電極と第2電極の重なり面積を変更可能な構成としている。本発明はこれに限られるものではなく、例えば、第1電極をその長軸方向に2つ以上の電極幅を有するように形成する例としてもよい。この場合には、同じ電極形状で、容量値の異なる2種類以上の可変容量素子を形成することが可能となる。

【0100】

また、第2電極についても、複数の電極幅を有する形状としてもよく、この場合は、第1電極及び第2電極の形成位置を、x方向、y方向に相対的に移動することで種々の構成が可能となる。また、第1電極の複数の電極幅と、第2電極の複数の電極幅を全て違う幅とすることで、容量値の異なる可変容量素子を、第1電極の電極幅の数と第2電極の電極幅の数を掛け合わせた数だけ形成することができる。

【0101】

〈3.第3の実施形態:可変容量素子〉

次に、本発明の第3の実施形態に係る可変容量素子について説明する。本実施形態例の可変容量素子の外観は、図1と同様であるから図示を省略する。本実施形態例の可変容量素子は、容量部を構成する電極形状を変えることなく、その形成位置を異ならせることによって、容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例について順に説明する。

【0102】

[3−1 第1の構成例]

図14は、本実施形態例の第1の構成例に係る可変容量素子30aをz方向から透過してみたときの構成図である。図14において、図3に対応する部分には同一符号を付し重複説明を省略する。

【0103】

第1電極31は、積層体2の真ん中に積層された強誘電体層12の上面に複数(図14では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。各第1電極31は、積層体2の第1の側面3側に幅広の底辺を有し、第3の側面5側に幅狭の上辺を有し、x方向の幅がx6の(>x2)台形形状の電極部32で構成されている。すなわち、第1電極31を構成する電極部32では、積層体2の第1の側面3側から第3の側面5側に向けて連続的に幅狭になっている。積層体2の第4の側面6側から4つの第1電極31は、2つの電極部32がx方向に接続して形成された構成とされており、第2の側面4に最隣接する第1電極31は、1つの電極部32のみで構成されている。

【0104】

積層体2の第4の側面6側から順に形成された4つの第1電極31のそれぞれは、積層体2の第1の側面3に露出するように第1電極31と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極31は、積層体2の第2の側面4に露出するように第1電極と同層に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0105】

第2電極18は、第1の実施形態における第2電極18と同形状とされ、1つの第1電極31に直交するか、若しくは、y方向に隣接する2つの第1電極31に跨って直交するように形成されている。また、第1の構成例に係る可変容量素子30aでは、第1電極31と第2電極18は、第1電極31の幅広側の領域に第2電極18がz方向に重なるように配置されている。

【0106】

以上により、第1の構成例に係る可変容量素子30aでは、図14に示すように、第1電極31と、その第1電極31に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部が形成される。また、図14の可変容量素子30aでは、複数の第1電極31と複数の第2電極18とが構成され、さらに、一つの第1電極31に対して一つ、又は二つの第2電極18がz方向に重なるように構成される。これにより、同一面内において複数個の容量部が形成される。そして、第1の構成例に係る可変容量素子30aでは、第1電極31の電極部32の幅広側において第1電極31と第2電極18がz方向に重なるような構成とされ、各容量部を構成する電極面積は第1電極31と第2電極18の重なり面積S6とされる。

【0107】

[3−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子について説明する。図15は、本実施形態例の第2の構成例に係る可変容量素子30bをz方向から透過してみたときの構成図である。図15において、図14に対応する部分には同一符号を付し重複説明を省略する。

【0108】

第2の構成例の可変容量素子30bでは、第1の構成例の可変容量素子30aに比較し、第1電極31が距離Δx(<x2)だけx方向の第3の側面5側にシフトして形成されている。このため、第2電極18は、強誘電体層12を挟んで、第1電極31の幅狭側とz方向に重なるように配置されている。ところで、距離Δxは、第1電極31を構成する電極部32と第2電極18とがz方向に重なる範囲内とする。すなわち、Δxは少なくともとも電極部32のx方向の長さx6から第2電極18のx方向の長さx2を差し引いた長さよりも小さい値とされる。

【0109】

以上により、第2の構成例に係る可変容量素子30bでは、強誘電体層12を挟んでz方向に対向する第1電極31における電極部32の幅狭側と、第2電極18とで容量部が形成される。そして、第2の構成例に係る可変容量素子30bでは、第1電極31の電極部32の幅狭側において第1電極31と第2電極18がz方向に重なるような構成とされ、各容量部を構成する電極面積は第1電極31と第2電極18の重なり面積S7とされる。

【0110】

第2の構成例では、第1電極31の電極部32の幅狭側において、第1電極31と第2電極18とが重なる構成とされる。このため、第2の構成例における可変容量素子30bでは、各容量部を構成する電極面積は、第1の構成例における可変容量素子30aの各容量部を構成する電極面積よりも小さい。これにより、第2の構成例における可変容量素子30b全体の容量は、第1の構成例における可変容量素子30a全体の容量よりも小さくなる。

【0111】

このように、本実施形態例では、第1電極31、及び第2電極18の形状は同じであっても、第1電極31の形成位置をずらすことによって、容量値の異なる2種類の可変容量素子30a、30bを構成することができる。

【0112】

本実施形態例の可変容量素子30a、30bは、第1の実施形態と同様にして形成することができる。したがって、本実施形態例においても、電極形成時に用いるマスクを第1の構成例における可変容量素子30aを形成する場合と、第2の構成例における可変容量素子30bを形成する場合とで変える必要がない。第1の構成例の可変容量素子30aを形成する場合には、z方向に第2電極18と第1電極31の電極部32の幅広側が積層するような位置関係となるように、各電極をシート上に形成すればよい。また、第2の構成例の可変容量素子30bを形成する場合には、z方向に第2電極18と第1電極31の電極部32の幅狭部が積層するような位置関係となるように、各電極をシート上に形成すればよい。

【0113】

本実施形態例では、第1電極31を台形形状(テーパー形状)とし、第1電極31の電極幅が変化する方向に第1電極31と第2電極18との重なり位置をシフトすることにより、重なり面積は連続的に変化する。これにより、電極形状を変えることなく、重なり位置を変えることにより、容量値が微少に異なる可変容量素子を形成することができる。

【0114】

また、本実施形態例でも、第1電極31の長軸方向と第2電極18の長軸方向とが交差する。このため、第1電極31と第2電極18とがy方向に相対的に位置ずれした場合には、容量値の変化はなく、第1電極31と第2電極18とをx方向に相対的にシフトした場合にのみ容量値が変化する。これにより、x方向における第1電極31と第2電極18との相対的な位置関係を変更することでのみ容量値の異なる可変容量素子30a、30bを形成することができ、設計が容易となる。

その他、第1の実施形態と同様の効果を得ることができる。

【0115】

上記第1の実施形態〜第3の実施形態では、静電容量素子として可変容量素子を例に挙げ説明したが、本発明はこれに限定されない。上記第1の実施形態〜第3の実施形態で説明した第1電極及び第2電極の構成は、入力信号の種類及びその信号レベルに関係なく容量がほとんど変化しない静電容量素子(以下、定容量素子という)に対しても同様に適用可能である。

【0116】

ただし、この場合、誘電体層は、比誘電率の低い常誘電体材料で形成される。常誘電体材料としては、例えば、紙、ポリエチレンテレフタレート、ポリプロピレン、ポリフェニレンサルファイド、ポリスチレン、ポリスチレン、TiO2、MgTiO2、MgTiO3、SrMgTiO2、Al2O3、Ta2O5等を用いることができる。なお、このような定容量素子は、上記第1の実施形態の可変容量素子と同様にして作製することができる。上述した可変容量素子では、全ての外部端子をDC端子として用いたが、定容量素子を構成する場合にはDC端子が不要であることが明らかであり、AC端子のみの2端子品とすることもできる。

【0117】

図16に、実際の回路上における可変容量素子周辺の回路構成例を示す。

実際の回路上では、可変容量素子1の一方の端子を、バイアス除去用コンデンサ61を介して交流信号の一方の入出力端子63に接続するとともに、電流制限抵抗62を介して制御電圧の入力端子64に接続する。また、可変容量素子50の他方の端子を、交流信号の他方の入出力端子65に接続するとともに、制御電圧の出力端子66に接続する。

【0118】

このような可変容量素子1の回路構成では、信号電流(交流信号)は、バイアス除去用コンデンサ61及び可変容量素子1を流れ、制御電流(直流バイアス電流)は、電流制限抵抗62を介して可変容量素子1のみを流れる。この際、制御電圧を変化させることにより、可変容量素子1の容量Cvが変化し、その結果、信号電流も変化する。

【0119】

[可変容量素子の構成]

そこで、次に、可変容量素子1と、バイアス除去用コンデンサ61とを一体化した例を説明する。図17に、可変容量素子1と、バイアス除去用コンデンサ61とを一体化した素子の構成例を示す。なお、図17において、第1の実施形態(図3)と同様の構成には同じ符号を付して示す。

【0120】

可変容量素子1は、強誘電体層12と、強誘電体層12を挟み込むように対向して形成された可変容量素子1用の第1電極15及び第2電極18とを備える。さらに、可変容量素子1は、強誘電体層12を挟み込むように対向して形成されたバイアス除去用コンデンサ61の第1電極53及び第2電極54を備える。

【0121】

可変容量素子1用の第1電極15及びバイアス除去用コンデンサ61の第1電極53は、強誘電体層12の上面51aに、所定間隔離れて形成される。また、可変容量素子1用の第2電極18及びバイアス除去用コンデンサ61の第2電極54は、強誘電体層51の下面51bに、所定間隔離れて形成される。すなわち、本実施形態では、可変容量素子1及びバイアス除去用コンデンサ61の誘電体層を共通にする。

【0122】

また、可変容量素子1用の第1電極15とバイアス除去用コンデンサ61の第1電極53とはリード線55等で接続される。なお、可変容量素子1用の第1電極15とバイアス除去用コンデンサ61の第1電極53とを接続するための所定の電線パターンを強誘電体層12の上面51aに形成して両者を接続してもよい。

【0123】

可変容量素子1用の第1電極15及びバイアス除去用コンデンサ61の第1電極53は、リード線56により、電流制限抵抗62を介して制御電圧の入力端子64に接続される(図16及び17参照)。可変容量素子1用の第2電極18は、リード線57により、交流信号の他方の入出力端子65及び制御電圧の出力端子66に接続される。そして、バイアス除去用コンデンサ61の第2電極54は、リード線58により、交流信号の一方の入出力端子63に接続される。このように接続することにより、図16の回路構成と同様に、信号電流(交流信号)がバイアス除去用コンデンサ61及び可変容量素子1を流れ、制御電流(直流バイアス電流)は、電流制限抵抗62を介して可変容量素子1のみを流れる。

【0124】

なお、可変容量素子1用の第1電極15及び第2電極18は、上記第2及び第3の実施形態の可変容量素子で用いた第1電極及び第2電極と同様の形状でも構成することができる。一方、バイアス除去用コンデンサ61の第1電極53及び第2電極54は、従来のコンデンサと同様の形状で形成することができる。

【0125】

このように、可変容量素子1と、バイアス除去用コンデンサ61とを一体化することにより、本発明の可変容量素子を適用する装置の寸法を小さくすることができる。また、部品点数を減らすことができるので、装置のコストを低減することができる。

【0126】

〈4.第4の実施形態:共振回路〉

第4の実施形態では、上述した本発明の静電容量素子を備える非接触受信装置の構成例を説明する。

【0127】

[非接触受信装置の構成]

本実施形態では、非接触受信装置として、非接触ICカードを例に挙げ説明する。図18に、本実施形態の非接触ICカードの受信系(復調系)回路部のブロック構成を示す。なお、図18では、説明を簡略するために、信号の送信系(変調系)回路部は省略し

ている。送信系回路部の構成は、従来の非接触ICカード等と同様に構成することができる。

【0128】

非接触ICカード260は、受信部261(アンテナ)と、整流部262と、信号処理部263とを備える。

【0129】

受信部261は、共振コイル264及び共振コンデンサ265からなる共振回路を備え、非接触ICカード260のリーダライター(不図示)から送信される信号をこの共振回路で受信する。なお、図18では、共振コイル264をそのインダクタンス成分264a(L)と抵抗成分264b(r:数オーム程度)とに分けて図示している。また、受信部261は、共振コンデンサ265内の後述する可変容量素子267の制御電源270と、可変容量素子267及び制御電源270間に設けられた2つの電流制限抵抗271及び272とを備える。

【0130】

共振コンデンサ265は、容量Coの定容量コンデンサ266と、可変容量素子267と、可変容量素子267の両端子にそれぞれ接続された2つのバイアス除去用コンデンサ268及び269とで構成される。そして、定容量コンデンサ266と、可変容量素子267並びに2つのバイアス除去用コンデンサ268及び269からなる直列回路とは、共振コイル264に並列接続される。

【0131】

定容量コンデンサ266は、上述した種々の実施形態及び種々の変形例で説明した電極及び外部端子の構成を有する2端子タイプの定容量コンデンサ(定容量素子)のいずれかで構成される。定容量コンデンサ266を構成する誘電体層は、第1の実施形態で説明した比誘電率の低い誘電体材料(常誘電体材料)で形成されており、入力信号の種類(交流または直流)及びその信号レベルに関係なく、その容量はほとんど変化しない。

【0132】

なお、実際の回路上では、共振コイル264のインダクタンス成分Lのばらつきや信号処理部263内の集積回路の入力端子の寄生容量などによる受信部261の容量変動(数pF程度)が存在し、その変動量は非接触ICカード260毎に異なる。それゆえ、本実施形態では、これらの影響を抑制(補正)するために、定容量コンデンサ266内の内部電極の電極パターンをトリミングして容量Coを適宜調整する。

【0133】

可変容量素子267もまた、上述した種々の実施形態で説明した2端子タイプの可変容量素子のいずれかで構成される。なお、可変容量素子267を構成する誘電体層は、第1の実施形態で説明した比誘電率の大きな強誘電体材料で形成される。なお、本発明はこれに限定されず、可変容量素子267を4端子タイプの可変容量素子で構成してもよい。

【0134】

また、可変容量素子267は、電流制限抵抗271及び272を介して制御電源270に接続される。そして、可変容量素子267の容量Cvは、制御電源270から印加される制御電圧に応じて変化する。

【0135】

なお、バイアス除去用コンデンサ268及び269、並びに、電流制限抵抗271及び272は、制御電源から流れる直流バイアス電流(制御電流)と、受信信号電流との干渉による影響を抑制するために設けられる。具体的には、バイアス除去用コンデンサ268及び269は、信号回路の保護及び/又は分離のために設けられ、電流制限抵抗271及び272は、制御回路の保護及び/又は分離のために設けられる。

【0136】

整流部262は、整流用ダイオード273と整流用コンデンサ274とからなる半波整流回路で構成され、受信部261で受信した交流電圧を直流電圧に整流して出力する。

【0137】

信号処理部263は、主に半導体素子の集積回路(LSI:Large Scale Integration

)で構成され、受信部261で受信した交流信号を復調する。信号処理部263内のLSIは整流部262から供給される直流電圧により駆動される。なお、LSIとしては、従来の非接触ICカードと同様のものを用いることができる。

【0138】

本実施形態の非接触ICカード260において、可変容量素子267は、過大な受信信号により耐電圧性の低い半導体素子からなる制御回路が破壊されないようにするために用いられる。具体的には、受信信号が過大な場合に、制御電圧により可変容量素子267の容量Cvを小さくする。これにより、可変容量素子267の容量低下分に対応した周波数Δfだけ、受信部261の共振周波数が高域にシフトする。これにより、容量可変前の共振周波数f0における受信信号のレスポンスは、容量可変前より低くなり、受信信号のレベルが抑制される。その結果、制御回路に過大な電流信号が流れないようにすることができ、制御回路の破壊を防止することができる。

【0139】

本実施形態の非接触ICカード260では、定容量コンデンサ266及び可変容量素子267に、本発明の電極構成を有する静電容量素子を用いているので、より高性能の非接触ICカードを提供することができる。また、可変容量素子267に、本発明の電極構成を有する静電容量素子を用いているので、より低い駆動電圧で非接触ICカードを駆動することができる。

【0140】

なお、本実施形態では、定容量コンデンサ266及び可変容量素子267の両方を本発明の電極構成を有する静電容量素子で構成する例を説明したが、本発明はこれに限定されず、いずれか一方を本発明の静電容量素子で構成してもよい。また、本実施形態では、定容量コンデンサ266を備えない構成としてもよい。

【0141】

また、本実施形態の非接触ICカード260では、可変容量素子267の制御電源270を設ける例を説明したが、本発明はこれに限定されない。例えば、特許文献1等と同様に、整流部262から出力された直流電圧から、例えば抵抗分割等の手法により所望の制御電圧を抽出するような構成にしてもよい。

【0142】

さらに、本実施形態では、非接触受信装置の一例として、非接触ICカードを例にとり説明したが、本発明はこれに限定されない。本発明は、共振コイル及び共振コンデンサからなる共振回路を用いて非接触で情報及び/または電力を受信する任意の装置に適用可能であり、同様の効果が得られる。例えば、携帯電話等や、ワイアレス電力伝送装置にも適用可能である。なお、ワイアレス電力伝送装置では、電力を非接触で伝送する装置であるので、非接触ICカードのように受信信号を復調する信号処理部を備えなくてもよい。

【符号の説明】

【0143】

1、1a、1b、1c・・・可変容量素子、2・・・積層体、3・・・第1の側面、4・・・第2の側面、5・・・第3の側面、6・・・第4の側面、8・・・第1外部端子、9・・・第1外部端子、10・・・第2外部端子、11・・・第2外部端子、12・・・強誘電体層、13・・・第1電極部、14・・・第2電極部、15・・・第1電極、16、17・・・内部端子、18・・・第2電極、19・・・内部端子、20、21・・・容量部、22a、22b・・・可変容量素子、23・・・第1電極、24・・・第2電極部、25・・・第1電極部、26・・・第2電極、30a、30b・・・可変容量素子、31・・・第1電極、32・・・電極部

【技術分野】

【0001】

本発明は、静電容量素子及びそれを備える共振回路に関し、より具体的には、例えばpFオーダーの小さな容量を有する静電容量素子とその製造方法、及びその静電容量素子を備える共振回路に関する。

【背景技術】

【0002】

従来、外部からバイアス信号を印加することにより、容量を変化させて入力信号の周波数や時間などを制御する可変容量素子が活用されている。そのような可変容量素子としては、例えば、可変容量ダイオード(バリキャップ)やMEMS(Micro Electro Mechanical Systems)などが商品化されている。

【0003】

また、従来、上述のような可変容量素子を、非接触IC(Integrated Circuit)カードにおける保護回路として利用する技術が提案されている(例えば、特許文献1参照)。特許文献1に記載の技術では、非接触ICカードをそのリーダライターに近づけた際に、過大な受信信号により耐電圧性の低い半導体素子からなる制御回路が破壊されないようにするために、保護回路として可変容量素子を用いる。

【0004】

図19に、特許文献1で提案されている非接触ICカードのブロック構成図を示す。特許文献1では、可変容量素子として可変容量ダイオード303dを用いる。そして、バイアス除去用コンデンサ303c及び可変容量ダイオード303dの直列回路をコイル303a及びコンデンサ303bからなる共振回路に並列に接続する。

【0005】

特許文献1では、受信信号を検波回路313で検波して得た直流電圧Voutを抵抗314a及び314bで抵抗分割する。そして、抵抗分割された直流電圧(抵抗314bに掛かる直流電圧)を、その直流電圧の変動を除去するために設けられたコイル315を介して可変容量ダイオード303dに印加して、可変容量ダイオード303dの容量を調整する。すなわち、抵抗分割された直流電圧を可変容量ダイオード303dの制御電圧として用いる。

【0006】

特許文献1では、受信信号が過大な場合は、制御電圧により可変容量ダイオード303dの容量が小さくなり、これにより受信アンテナ303の共振周波数が高くなる。この結果、容量が変化する前の受信アンテナ303の共振周波数f0における受信信号のレスポンスは容量低下前より低くなり、受信信号レベルを抑制することができる。特許文献1で提案されている技術では、このようにして可変容量素子により信号処理部320(制御回路)を保護する。

【0007】

また、本発明者らは、従来、可変容量素子として強誘電体材料を用いた素子を提案している(例えば、特許文献2参照)。特許文献2では、信頼性及び生産性の向上を図るために、図20A及び図20Bに示すような電極構造を有する可変容量素子400を提案している。図20Aは、可変容量素子400の概略斜視図であり、図20Bは、可変容量素子400の断面構成図である。特許文献2の可変容量素子400では、直方体形状の誘電体層404の4つの面に、それぞれ端子が設けられる。4つの端子のうち、一方の対向する2つの端子が信号電源403に接続される信号端子403a及び403bであり、他方の対向する2つの端子が制御電源402に接続される制御端子402a及び402bである。

【0008】

可変容量素子400の内部は、図20Bに示すように、複数の制御電極402c〜402g及び複数の信号電極403c〜403fが、誘電体層404を介して交互に積層された構造になっている。具体的には、最下層から、制御電極402g、信号電極403f、制御電極402f、信号電極403e、制御電極402e、信号電極403d、制御電極402d、信号電極403c及び制御電極402cがこの順で誘電体層404を介して積層される。そして、図20Bの例では、制御電極402g、制御電極402e及び制御電極402cが一方の制御端子402aに接続され、制御電極402f及び制御電極402dが他方の制御端子402bに接続される。また、信号電極403f及び信号電極403dは一方の信号端子403aに接続され、信号電極403e及び信号電極403cは他方の信号端子403bに接続される。

【0009】

特許文献2の可変容量素子400では、制御端子及び信号端子に個別に電圧を印加することができるとともに、内部に信号電極及び制御電極を複数積層させるので、低コストで容量を増大することができるという利点がある。また、特許文献2のような構造の可変容量素子400は、製造が容易であり、低コストである。さらに、特許文献2の可変容量素子400では、バイアス除去用コンデンサは不要になる。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平08−7059号公報

【特許文献2】特開2007−287996号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

比誘電率の大きい強誘電体材料を用いて、小さい容量の可変容量素子を作製する際には、誘電体層を厚くして電極間距離を大きくする、または、対向する電極面積を小さくする必要がある。しかしながら、誘電体層を厚くすると誘電体層に印加される電界強度が小さくなるので、可変容量素子の容量を変化させるための制御電圧が高くなる。したがって、低電圧で動作する可変容量素子を構成するためには誘電体層の厚さを薄くする必要がある

【0012】

しかしながら、誘電体層の厚さが薄いと容量が大きくなり、対向する電極面積を小さくする必要があるが製造上の制約のため100um以下のように小さな面積にはできないため一層あたりの容量を1pF以下といった小さい容量にできないという問題がある。このため、小さい容量で、かつ、制御電圧が小さい可変容量素子を作成する場合、電極の積層数を変えて異なる容量値の可変容量素子を作製するのが困難となり、容量値の異なる可変容量素子の品揃えを増やすのが困難となる。電極形状を変えることで異なる容量値の可変容量素子を形成することができるが、この場合、電極を形成するためのマスクを容量値の異なる可変容量素子毎に作製する必要がありコストがかかる。

【0013】

また、薄膜キャパシタのように、誘電体層とその誘電体層を狭持する一対の電極のみで構成されるコンデンサにおいては、電極の積層数で容量を変えることができない。このため、誘電体層の厚みが同じ場合は電極形状を変更することで違った容量のコンデンサを作製する。この場合も、電極を形成するためのマスクを容量値の異なるコンデンサ毎に作製する必要がありコストがかかる。

【0014】

本発明は、上記問題を解決するためになされたものであり、本発明の目的は、電極の形状、及び電極の積層数を変えること無く、異なる容量を有する静電容量素子を安定して製造することである。

【課題を解決するための手段】

【0015】

上記課題を解決し、本発明の目的を達成するため、本発明の静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【0016】

本発明の静電容量素子では、一方の電極を他方の電極に対して相対的に移動して形成した場合、誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、変更することができる。このため、同一の電極形状で、異なる容量の可変容量素子を形成することができる。

【0017】

本発明の静電容量素子の製造方法は、誘電体層上面の所望の位置に配置されたマスクを介して、一方の電極、及び他方の電極をパターン形成する。そして、一方の電極又は/及び他方の電極の形成は、一方の電極と他方の電極の誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように誘電体層上に配置するマスクの位置を調整しながら形成する。そして、本発明で形成される静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【0018】

本発明の静電容量素子の製造方法では、一方の電極又は/及び他方の電極の形成は、一方の電極と他方の電極の誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように誘電体層上に配置するマスクの位置を調整しながら形成する。マスク位置を変更することで、一方の電極及び他方の電極との重なり領域で形成される容量部の容量値が所定の容量値となるように調整できる。

【0019】

本発明の共振回路は、静電容量素子を含む共振コンデンサと、共振コンデンサに接続された共振コイルとを備える。静電容量素子は、誘電体層と、誘電体層を狭むように誘電体層の一方の面上に形成された一方の電極と誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極を有する。一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置されている。また、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有する。そして、一対、又は複数対の電極は、一方の電極を他方の電極に対して相対的に移動して形成した場合に誘電体層を挟んで誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能とされている。

【発明の効果】

【0020】

本発明によれば、誘電体層を挟んで配置される一対の電極の相対的な電極位置を製造時において調整することにより、完成される静電容量素子の容量値を変更することができる。これにより、電極の形状、及び電極の積層数を変えることなく、異なる容量を有する静電容量素子を安定して製造することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の第1の実施形態に係る可変容量素子の外観を示す斜視図である。

【図2】本発明の第1の実施形態に係る可変容量素子の回路構成例を示す図である。

【図3】第1の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図4】第1の実施形態における第1電極が形成された層の構成を示す図である。

【図5】第1の実施形態における第2電極が形成された層の構成を示す図である。

【図6】A、B 図3のA−A線上に沿う断面を示す図と、図3のB−B線上に沿う断面を示す図である。

【図7】第1の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図8】A、B 図7のA−A線上に沿う断面を示す図と、図7のB−B線上に沿う断面を示す図である。

【図9】A〜D 第1の実施形態における可変容量素子の製造方法を示す製造工程図である。

【図10】比較例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図11】第1の実施形態の第3の構成例に係る可変容量素子の断面図である。

【図12】第2の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図13】第2の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図14】第3の実施形態の第1の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図15】第3の実施形態の第2の構成例に係る可変容量素子をz方向から透過してみたときの構成図である。

【図16】実際の回路上における可変容量素子周辺の回路構成例を示す図である。

【図17】可変容量素子と、バイアス除去用コンデンサとを一体化した可変容量素子の構成例を示した図である。

【図18】本発明の第4の実施形態の非接触ICカードの受信系(復調系)回路部のブロック構成を示す図である。

【図19】従来の非接触ICカードのブロック構成図である。

【図20】A,B 従来の可変容量素子の概略斜視図と、その断面構成図である

【発明を実施するための形態】

【0022】

以下に、本発明の実施形態に係る静電容量素子の一例を、図面を参照しながら、以下の順で説明する。なお、以下に示す例では、静電容量素子として可変容量素子を例に挙げ説明するが、本発明はこれに限定されるものではない。

1.第1の実施形態:可変容量素子

1−1 第1の構成例

1−2 第2の構成例

1−3 第3の構成例

2.第2の実施形態:可変容量素子

2−1 第1の構成例

2−2 第2の構成例

3.第3の実施形態:可変容量素子

3−1 第1の構成例

3−2 第2の構成例

4.第4の実施形態:共振回路

【0023】

〈1.第1の実施形態:可変容量素子〉

第1の実施形態では、容量の変化を制御する制御端子と、信号端子を設けた可変容量素子の一例を説明する。また、本実施形態例の可変容量素子は、pFオーダーの容量を有するものである。

【0024】

図1は本実施形態例の可変容量素子1の外観を示す斜視図であり、以下に説明する各構成例、及び、各実施形態例の可変容量素子に共通の構成である。また、図2に、本実施形態例の可変容量素子1の回路構成図を示す。

【0025】

本実施形態例の可変容量素子1は、後述する強誘電体層12、後述する第1電極15、及び第2電極18とで構成された積層体2と、第1電極15に接続された第1外部端子8、9と、第2電極18に接続された第2外部端子10、11とで構成されている。

【0026】

積層体2はほぼ直方体状に形成されている。第1外部端子8は、積層体2の第1の側面3に複数(図1では4つ)形成され、第1外部端子9は、第1の側面3に隣り合う第2の側面4に形成されている。また、第2外部端子10は、積層体2の第3の側面5に複数(図1では4つ)形成され、第1外部端子11は、第3の側面5に隣り合う第4の側面6に形成されている。また、これらの第1外部端子8、9及び第2外部端子10、11は、積層体2の上面及び下面において、面内に一部張り出すように形成されている。

【0027】

そして、第1外部端子8、9及び第2外部端子10、11には図2に示すように電源からバイアス抵抗Rを介して制御電圧V及び信号電圧が供給される。本実施形態例では、第1外部端子8及び第2外部端子10が制御(DC)端子で、第1外部端子9及び第2外部端子11が信号(AC)端子である。ここで、第1外部端子9及び第2外部端子11は、信号端子と制御端子を兼ねる構成とされている。そして、第1電極15及び第2電極18により複数の容量部が形成され、それらの容量部が直列に接続されている。

以下の説明では、積層体2における各層の積層方向をz方向とし、積層方向に垂直な面における短軸方向をx方向、長軸方向をy方向とする。

【0028】

本実施形態例の可変容量素子1は、容量部を構成する第1電極15及び第2電極18の電極形状を変えることなく、その形成位置を異ならせることによって容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例、第3の構成例について順に説明する。

【0029】

[1−1 第1の構成例]

図3は、本実施形態例の第1の構成例に係る可変容量素子1aをz方向から透過してみたときの構成図である。また、図4は、可変容量素子1aの第1電極をz方向から透過してみたときの構成図であり、図5は、可変容量素子1bの第2電極をz方向から透過してみたときの構成図である。また、図6Aは、図3のA−A線上に沿う断面を示す図であり、図6Bは、図3のB−B線上に沿う断面を示す図である。

【0030】

本実施形態例の可変容量素子1aでは、同一平面に形成された複数の第1電極15と、同一平面に形成された複数の第2電極18が、強誘電体層12を狭持するように配置されている。そして、その第1電極15の上側、及び第2電極18の下側にさらに1層ずつ強誘電体層12が積層された構成とされている。

【0031】

強誘電体層12(誘電体層)は、外部から印加される制御信号に応じて容量が変化する誘電体材料で形成される。例えば、第1電極15と第2電極18とで挟まれる1層分の強誘電体層12は、比誘電率が1000を超えるような強誘電体材料で形成されたシート状部材(厚さは、例えば2μm程度)で構成することができる。なお、強誘電体層12の電極が形成される面及びそれとは反対側の面の形状は長方形であり、その長辺と短辺の比は、例えば、2:1にすることができる。

【0032】

強誘電体層12の形成材料としては、イオン分極を生じる強誘電体材料を用いることができる。イオン分極を生じる強誘電体材料は、イオン結晶材料からなり、プラスのイオンとマイナスのイオンの原子が変位することで電気的に分極する強誘電体材料である。このイオン分極を生じる強誘電体材料は、一般に、所定の2つの元素をA及びBとすると、化学式ABO3(Oは酸素元素)で表され、ペロブスカイト構造を有する。このような強誘電体材料としては、例えば、チタン酸バリウム(BaTiO3)、ニオブ酸カリウム(KNbO3)、チタン酸鉛(PbTiO3)等が挙げられる。また、強誘電体層12の形成材料として、例えば、チタン酸鉛(PbTiO3)にジルコン酸鉛(PbZrO3)を混ぜ合わせたPZT(チタン酸ジルコン酸鉛)を用いてもよい。

【0033】

また、強誘電体層12の形成材料として、電子分極を生じる強誘電体材料を用いてもよい。この強誘電体材料では、プラスの電荷に偏った部分と、マイナスの電荷に偏った部分とに分かれて電気双極子モーメントが生じ、分極が生じる。そのような材料として、従来、Fe2+の電荷面と、Fe3+の電荷面の形成により、分極を形成して強誘電体的特性を示す希土類鉄酸化物が報告されている。この系においては、希土類元素をREとし、鉄族元素をTMとしたときに、分子式(RE)・(TM)2・O4(Oは酸素元素)で表される材料が高誘電率を有することが報告されている。なお、希土類元素としては、例えば、Y、Er、Yb、Lu(特にYと重希土類元素)が挙げられ、鉄族元素としては、例えば、Fe、Co、Ni(特にFe)が挙げられる。また、(RE)・(TM)2・O4としては、例えば、ErFe2O4、LuFe2O4、YFe2O4が挙げられる。また、強誘電体層12の形成材料として、異方性を有する強誘電体材料を用いてもよい。

【0034】

第1電極15は、図6A、図6Bに示すように、積層体2の真ん中に積層された強誘電体層12の上面に複数(図3では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。図4に示すように、各第1電極15は、y方向の電極幅がy1、x方向の電極幅がx1とされた長方形状の第1電極部13と、y方向の電極幅がy2(<y1)、x方向の電極幅がx1とされた長方形状の第2電極部14とがx方向に交互に接続された構成とされている。そして、積層体2の第4の側面6側から順に形成された4つの第1電極15は、第1電極部13と第2電極部14とが交互に2つずつ接続された構成とされている。一方、第2の側面4側に最隣接する第1電極15は、第1電極部13と第2電極部14が1つずつ接続された構成とされている。

【0035】

以上のように、第1電極15がy方向の電極幅が異なる第1電極部13と第2電極部14とによって構成されることにより、それぞれの第1電極15はx方向に2つの電極幅を有する構成とされる。そして、第1電極15の各第1電極部13の位置はy方向に水平とされ、各第2電極部14の位置はy方向に水平とされている。

【0036】

そして、積層体2の第4の側面6側から順に形成された4つの第1電極15のそれぞれは、積層体2のy方向の第1の側面3に露出するように第1電極15と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極15は、積層体2のx方向の第2の側面4に露出するように強誘電体層12の上面に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0037】

第2電極18は、図6A、図6Bに示すように、積層体2の真ん中に積層された強誘電体層12の下面に複数(図3では5つ)形成されている。図5に示すように、第2電極18は、y方向の電極幅がy3(>y1)とされ、x方向の電極幅がx2(<x1、<y3)とされた長方形状をなし、y方向に延在して形成されている。そして、各第2電極18は、x方向及びy方向に離間して設けられており、その長軸方向が、第1電極15の長軸方向と直交するように設けられている。また、第2電極18は、1つの第1電極15に交差するか、若しくは、y方向に隣接する2つの第1電極15に跨って配置され、第1電極15の第1電極部13と第2電極18が、z方向に重なるように配置されている。

【0038】

積層体2の第2の側面4側から順に形成された4つの第2電極18は、積層体2の第1の側面3に対向する第3の側面5に露出するように第2電極18と同層に形成されたそれぞれの内部端子19に接続されている。そして、この内部端子19は、積層体2の第3の側面5に形成された第2外部端子10に接続されている。また、積層体2の第4の側面6に最隣接する第2電極18は、第4の側面6に露出するように形成されている。そして、この第2電極18は、積層体2の第4の側面6に形成された第2外部端子11に接続されている。

【0039】

ここで、図3に示すように、積層体2の第4の側面6側から奇数番目の第2電極18を第1の側面3側に位置する第1電極部13の下層に配置し、偶数番目の第2電極18を第3の側面5側に位置する第1電極部13の下層に配置する。さらに、奇数番目の第2電極18と偶数番目の第2電極18とをx方向に重ならないように配置する。このような電極レイアウトとすることにより、第2電極18に接続されるそれぞれの内部端子19の引き回しを容易にすることができる。図3では、奇数番目の第2電極18を積層体2の第1の側面3側に配置し、偶数番目の第2電極18を第3の側面5側に配置する例としたが、逆の配置であってもよい。

【0040】

そして、第1の構成例に係る可変容量素子1aでは、図6A、及び図6Bに示すように、第1電極15の各第1電極部13と、その第1電極部13に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部20が形成される。容量部20では、第1電極15における第1電極部13と第1電極部13に対向する第2電極18との間で容量値C1が得られる。そして、第1の構成例に係る可変容量素子1aでは、第1電極15の第1電極部13と第2電極18がz方向に重なるような構成とされることにより、各容量部20を構成する電極面積は第1電極15と第2電極18の重なり面積S1(=x2×y1)とされる。

【0041】

また、第1の構成例における可変容量素子1aでは、同層に複数の第1電極15と複数の第2電極18とが構成され、さらに、一つの第1電極15に対して一つ、又は二つの第2電極18がz方向に重なるように構成される。これにより、同一面内において複数個の容量部20が形成される。

【0042】

[1−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子1bについて説明する。図7は、本実施形態例の第2の構成例に係る可変容量素子1bをz方向から透過してみたときの構成図である。また、図8Aは、図7のA−A線上に沿う断面構成であり、図8Bは、図7のB−B線上に沿う断面構成である。図7、図8A、及び図8Bにおいて、図3、図6A、及び図6Bに対応する部分には同一符号を付し重複説明を省略する。

【0043】

第2の構成例の可変容量素子1bでは、第1の構成例の可変容量素子1aに比較し、第1電極15が距離x1だけx方向の第1の側面側にシフトして形成されている。このため、第2電極18は、強誘電体層12を挟んで、第1電極15を構成する第2電極部14とz方向に重なるように配置されている。

【0044】

そして、第2の構成例に係る可変容量素子1bでは、図8A、図8Bに示すように、第1電極15の各第2電極部14と、その第2電極部14に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部21が形成される。容量部21では、第1電極15における第2電極部14と第2電極部14に対向する第2電極18との間で容量値C2が得られる。そして、第2の構成例に係る可変容量素子1bでは、第1電極15の第2電極部14と第2電極18がz方向に重なるような構成とされることにより、各容量部21を構成する電極面積は第1電極15と第2電極18の重なり面積S2(=x2×y2)とされる。

【0045】

第1電極15における第2電極部14のy方向の幅は、第1電極部13のy方向の幅よりも小さい。このため、第2の構成例における可変容量素子1bでは、各容量部21を構成する電極面積(S2)は、第1の構成例における可変容量素子1aの各容量部20を構成する電極面積(S1)よりも小さい。これにより、第2の構成例における可変容量素子1b全体の容量は、第1の構成例における可変容量素子1a全体の容量よりも小さくなる。

【0046】

このように、本実施形態例の可変容量素子1では、第1電極15、及び第2電極18の形状は同じであっても、第2電極18に対して相対的に移動することによって、容量値の異なる2種類の可変容量素子を構成することができる。

【0047】

本実施形態例の第1の構成例及び第2の構成例で形成される可変容量素子1a、1bは、図2に示すように、誘電体層12の内部に形成された第1電極15及び第2電極18により容量部が形成され、それらの容量部は直列接続される。そして、それらの容量部に、バイアス抵抗Rを介してGNDと制御電圧+Vを印加することで、それぞれの容量部に+Vの制御電圧が加わる。一方、信号電圧(AC電圧)は、9個直列された容量部を経由するため、全体の容量は1/9になるが、制御電圧は、それぞれの容量部に個別に加わるため、小さい値でもよい。すなわち、本実施形態例の可変容量素子1では、容量値を小さくして、制御電圧を高くしない回路的な工夫がされている。なお、バイアス抵抗Rは、一般的に500KΩ〜1MΩ程度である。

【0048】

[可変容量素子の製造方法]

次に、本実施形態例の第1の構成例、及び第2の構成例に係る可変容量素子1a、1bの製造方法について説明する。図9A〜図9Dは、本実施形態例に係る第1の構成例及び第2の構成例に係る可変容量素子1a、1bの製造工程図である。

【0049】

まず、図9Aに示すように、上述した強誘電体材料からなるシート部材(図9Aでは2枚)を用意する。なお、このシート部材が上述した強誘電体層12となり、一方は、上面に第1電極15が形成される強誘電体層12で、他方が、上面に第2電極18が形成される強誘電体層12である。

【0050】

次に、例えばPd、Pd/Ag、Ni等の金属微粉末をペースト化した導電ペーストを調整する。また、第1電極15の形状が開口された第1のマスク37と、第2電極18の形状が開口された第2のマスク38を準備する。そして、図9Bに示すように、第1のマスク37を一方のシート部材(強誘電体層12)上面の所定の位置に位置あわせして配置し、第2のマスク38を他方のシート部材(強誘電体層12)上面の所定の位置に位置あわせして配置する。

【0051】

その後、図9Cに示すように、第1のマスク37を介して一方のシート部材上部に導電ペーストを塗布(シルク印刷)し、第2のマスク38を介して他方のシート部材上部に導電ペーストを塗布する。これにより、それぞれのマスクの開口部分においてシート部材上部に導電ペーストが塗布されるので、一方のシート部材上部には第1電極15がパターン形成され、他方のシート部材上部に第2電極18がパターン形成される。

【0052】

そして、図9Dに示すように、第1のマスク37、及び第2のマスク38をそれぞれのシート部材上部から外すことにより、第1電極15が形成された強誘電体層12と、第2電極18が形成された強誘電体層12が形成される。

【0053】

この製造方法において、第1の構成例における可変容量素子1aを形成する場合には、シート部材を重ねたときに、第1電極15の第1電極部13の下層に第2電極18が重なるように、第1のマスク37及び第2のマスク38をそれぞれのシート部材に位置あわせする。

【0054】

一方、第2の構成例における可変容量素子1bを形成する場合には、シート部材を重ねたときに、第1電極15の第2電極部14の下層に第2電極18が重なるように、第1のマスク37と第2のマスク38をそれぞれのシート部材に位置あわせする。すなわち、第2の構成例における可変容量素子1bを形成する場合には、第1電極15の形成において、第1の構成例における可変容量素子1aを形成する場合に比較し、第1のマスク37をx方向の内部端子16が形成された側に距離x1だけずらしてシート部材上に配置する。

【0055】

ここで、第1の構成例の可変容量素子1aと第2の構成例の可変容量素子1bでは、それぞれの第1電極15の内部端子16はその長さが異なっている。このため、本実施形態例の製造方法では、マスクの位置を所定の距離だけ動かした場合にも、積層体2の側面に露出する内部端子16が形成されるようにマスクの内部端子16に対応する部分の開口が形成されている。

【0056】

その後、第2電極18(電極ペースト層)が塗布されたシート部材と、第1電極15(電極ペースト層)が塗布されたシート部材とを、シート部材と電極ペースト層が交互になるように下から積層する。そして、必要に応じて、最上層の第1電極15上部に電極ペースト層が形成されないシート部材を積層し、シート部材と導電ペースト層からなる積層体2を形成する。

【0057】

次いで、その積層体2を加熱圧着する。加熱圧着した部材を還元雰囲気中で高温焼成してシート部材と導電ペースト層(第1電極15、第2電極18)を一体化させる。その後、積層体2の第1の側面3〜第4の側面6に第1外部端子8、9、及び第2外部端子10、11を形成することにより、第1の構成例、又は第2の構成例に係る可変容量素子1a、1bが完成される。

このように、本実施形態例の可変容量素子1では、電極製造時のマスク位置を異ならせることで、第1の構成例、及び第2の構成例で示した通り、容量の異なる可変容量素子を形成することができる。

【0058】

本実施形態例の可変容量素子の製造方法は、上述のものに限られるものではない。例えば、薄膜キャパシタでは、電極はPtなどをSiなどの基板上にスパッタ法を用いて作成し不要な部分をエッチングにより除去し形成するが、不要な部分をエッチングするためのマスクの位置を下部電極と上部電極で相対的にシフトさせることで電極位置をシフトさせることが可能になる

【0059】

[電極形状の設計概要]

本実施形態例では、同じ電極形状であっても、その形成位置を調整することで容量値の異なる可変容量素子1a、1bを構成できるようにするため、第1電極15及び第2電極18の寸法をある程度考慮する必要がある。以下に、本実施形態例の可変容量素子1の第1電極15、第2電極18の形状及び寸法の設計概要を説明する。

【0060】

第1電極15における第1電極部13及び第2電極部14のx方向の電極幅x1は、第1電極15と第2電極18との製造時における意図しない位置ずれを考慮して、第2電極18のx方向の電極幅x2よりも所定の幅だけ広い構成とされるのが好ましい。これにより、図3でみると、第1電極15のx方向の中心位置と、第2電極18のx方向の中心位置を一致させた場合、重なり面積S1のx方向の両端にマージンM((x1−x2)/2)(第2電極18と重ならない領域)が形成される。このマージンMは、第1電極15と第2電極18との間の合わせずれを吸収できる幅であることが好ましく、例えば、10μm以上であることが好ましい。そして、製造上の制約も含めば、電極幅x1は、50μm以上であることが好ましく、より好適には、100μm以上であることが好ましい。

【0061】

このように、マージンMが形成されることにより、例えば、第1電極15が第2電極18に対して所定の位置からx方向にずれてしまった場合、そのずれ量がマージンMの幅よりも小さければ、第1電極15と第2電極18との重なり面積は変わらない。このため、一方向に電極位置をシフトさせるのみで所望の容量値を有する可変容量素子を形成することができるため、異なる容量値を有する可変容量素子の形成が容易となる。また、第1の構成例と第2の構成例とでは、第1電極15の位置が、第1電極部13及び第2電極部14のx方向の電極幅x1だけ異なる。この電極幅x1は、マージンMに比較して十分大きく、意図的にマスク位置を異ならせることでずらすことができる幅である。したがって、本実施形態例の可変容量素子1では、微少な合わせずれ程度では第1電極15と第2電極18の重なり面積は変わらず、意図した電極位置の移動によってのみ、第1電極15と第2電極18の重なる面積を変えることができる。

【0062】

また、本実施形態例では、第1電極15を構成する第1電極部13と第2電極部14のy方向の幅の違いにより第1の構成例における可変容量素子1aと第2の構成例における可変容量素子1bの容量値を変えることができる。したがって、電極幅y1と電極幅y2とを、例えば、y1:y2=1:0.8の関係となるような電極幅とすることにより、第1の構成例の可変容量素子1aの容量値と、第2の構成例の可変容量素子1bの容量値との比を1:0.8に設定することができる。ただし、電極幅y1と電極幅y2は異なる幅であればよく、種々の設定が可能である。

【0063】

また、第2電極18のy方向の電極幅y3は、第1電極15のy方向の最大の電極幅、すなわち、第1電極部13のy方向の電極幅y1よりも大きければよい。本実施形態例では、積層体2の第4の側面6に最隣接する第2電極18は、第4の側面6の第2外部端子11に接続されるため、積層体2の側面に露出する長さに形成される必要がある。また、その他の第2電極18は、それぞれ、2つの第1電極15に跨って形成されるため、y方向の電極幅y3は隣接する2つの第1電極を含むy方向の幅よりも大きく形成される必要がある。

【0064】

そして、本実施形態例では、第2電極18が長方形状とされ、その長軸方向(y方向)が第1電極15の長軸方向(x方向)に直交するように配置されている。このため、合わせずれにより、第2電極18と第1電極15とが所定の位置からy方向にずれてしまった場合にも、第2電極18と第1電極15との重なり面積は変化しない。これにより、y方向の位置ずれによって容量値が変化しない。

【0065】

また、本実施形態例では、第1の構成例に係る可変容量素子1aと第2の構成例に係る可変容量素子1bとで、第1電極15の形成位置をx方向に所定の量だけシフトする必要がある。このシフト量は、デバイスのx方向の長さと、デバイスサイズで制約される外部端子の長さによる制約を受ける。例えば、シフト量を積層体2の第2の側面4に形成される第1外部端子9のx方向の長さx4よりも大きくすると、第2の側面4に最隣接する第1電極15において、その内部端子17と第1外部端子9とを接続できなくなってしまうことがある。このため、本実施形態例の可変容量素子1では、第1電極15のシフト量を積層体2の第2の側面4に形成される第1外部端子9のx方向の長さx4よりも小さくしなければならない制約がある。第2の側面4に最隣接する第1電極15の内部端子17のx方向の幅x3を第1外部端子9のx方向の長さx4よりも大きくすることで、この制約を無くすことも可能である。しかしながら、電極作製の容易性、マスクシフトの容易性から、第1電極15のシフト量は第1外部端子9のx方向の長さx4よりも小さくすることが好ましい。なお、積層体2のy方向の幅が1.0mmで、x方向の幅が0.5mの小型サイズの可変容量素子の場合を考えると、第2の側面4に形成される第1外部端子9のx方向の長さx4は200〜300mmである。このため、第1電極15のシフト量は100〜200mmの範囲とするのが好ましい。

【0066】

[比較例]

次に、比較例に係る可変容量素子を示す。図10は、比較例に係る可変容量素子100をz方向から透過してみたときの構成図である。比較例に係る可変容量素子100の外観は、図1に示した本実施形態例の可変容量素子1と同様とし、図示を省略する。図10において、図3に対応する部分には同一符号を付し、重複説明を省略する。

【0067】

比較例に係る可変容量素子100は、第1電極101の形状が本実施形態例の可変容量素子1と異なる例である。

図10に示すように、比較例に係る可変容量素子100では、複数(図10では5つ)の第1電極101が積層体2の真ん中に積層された強誘電体層12の上面に形成されており、y方向の一方の側から他方の側にかけて、所定の距離ずつ離間して形成されている。第1電極101のそれぞれは、y方向の電極幅がy4、x方向の電極幅がx5(>x2)の長方形状に形成されている。

【0068】

そして、5つの第1電極101のうち、積層体2の第2の側面4に最隣接する第1電極101は、内部端子17を介して第2の側面4に形成された第1外部端子9に接続さる。残りの第1電極101は、内部端子16を介して積層体2の第1の側面3に形成されたそれぞれの第1外部端子8に接続される。

【0069】

比較例に係る可変容量素子100では、第2電極18は、1つの第1電極101に交差するか、若しくは、隣接する2つの第1電極101に跨るように交差して配置されている。そして、第1電極101と第2電極18とがz方向に重なる領域において容量部が形成される。容量部を構成する第1電極101及び第2電極18の電極面積は、第1電極101と第2電極18とのz方向の重なり面積S3(=x2×y4)とされる。

【0070】

比較例における可変容量素子100では、図10の波線で示すように、例えば第1電極101がΔxだけx方向に移動した場合にも、第2電極18と第1電極101との重なり面積S4は変わらない。このため、z方向に重なる第1電極101と第2電極18とその間に形成される強誘電体層12で形成される容量部の容量値は変化しない。比較例の可変容量素子100において、その容量値を変化させたい場合には、積層される電極の積層数を変化させたり電極形状を変えたりする必要がある。電極形状を変化させるには、異なるマスクを用いて電極を形成する必要がありコストがかかり、また、一層当たりの容量が大きい場合には、積層数を大きくして容量値を変える場合、容量値を大きく変化させることができても小さくすることはできない。

【0071】

一方、本実施形態例の可変容量素子1(1a、1b)では、第1電極15が、2つ以上の電極幅を有して構成されている。このため、強誘電体層12表面に第1電極15を形成するときのマスク位置を一方向(この場合x方向)に所定の量だけ移動させることで、第2電極18と第1電極15の重なり面積を容易に変えることができる。これにより、積層数が同じでありながら、違った容量の可変容量素子1(1a、1b)を得ることができる。そして、この場合、電極を形成するためのマスクを変更する必要がなく、製造プロセスの大きな変更も不要なため、高品質で低価格な可変容量素子1(1a、1b)を得ることができる。

【0072】

本実施形態例では、第1電極15の位置をx方向に移動して形成することで、容量値の異なる可変容量素子1(1a、1b)を構成する例とした。しかしながら、本発明は、これに限られるものではなく、第2電極18の位置をx方向に移動して形成することによっても、容量値の異なる可変容量素子を形成することができる。すなわち、第1電極15と第2電極18とが相対的に所定の量だけシフトするように第1電極15及び第2電極18を形成すれば容量値の異なる可変容量素子を形成できる。また、本実施形態例では、一方の電極を一方向に所定の量だけずらして形成することで容量を変えることができるため、位置決めが容易である。このような構成は、特に、pFオーダーの容量値を有する可変容量素子において容量値を微小変化させるのに有効である。

【0073】

また、本実施形態例では、強誘電体層12を挟んで複数対の第1電極15と第2電極18がz方向に重なるように構成することによって、同層で複数の容量部を構成する例としたが、1対の第1電極15と第2電極18とにより容量部を構成する例としてもよい。さらに、本実施形態例では、第1電極15と第2電極18とを強誘電体層12を挟んで複数層積層する構成としてもよい。例えば、3層の第1電極15と3層の第2電極18を交互に積層させることによって、5層の容量部を形成することができる。第1の構成例に係る可変容量素子1aにおいて1層分の容量値C1が9pFである場合は、5層の容量部で構成される容量値は45pFとなる。また、第2の構成例に係る可変容量素子1bにおいて1層分の容量値C2が8pFである場合は、5層の容量部で構成される容量値は40pFとなる。

【0074】

[1−3 第3の構成例]

以下に、第3の構成例として、第1の構成例に係る可変容量素子1aと第2の構成例に係る可変容量素子1bとを複数層ずつ積層して形成した可変容量素子を示す。図11は、第3の構成例に係る可変容量素子1cの断面構成を示す図である。図11において、図6A、図6B、図8A、及び図8Bに対応する部分には同一符号を付し、重複説明を省略する。

【0075】

図11では、簡単のため、同一層内に形成される第1電極15、及び第2電極18をそれぞれ一つずつ図示する。

図11に示すように、第3の構成例に係る可変容量素子1cは、3層の第2電極18と3層の第1電極15とが交互に積層された構成とされている。そして、3層の第1電極15のうち、下層の第1電極15と、上層の第1電極15は、対向する第2電極18に対して、第1の構成例に係る可変容量素子1aの第1電極15の位置と同様になるように形成されている。一方、3層の第1電極15のうち、真ん中の第1電極15は、対向する第2電極18に対して第2の構成例に係る可変容量素子1bの第1電極15の位置と同様になるように形成されている。

【0076】

すなわち、第3の構成例に係る可変容量素子1cでは、真ん中の第1電極15が、他の2つの第1電極15に比較してx方向に電極幅x1分だけずらして形成されている。これにより、下層の第1電極15とそれに対向する第2電極18とで第1の構成例に示した可変容量素子1aが2層形成される。また、真ん中の第1電極15とそれに対向する第2電極18とで第2の構成例に示した可変容量素子1bが2層形成される。また、上層の第1電極15とそれに対向する第2電極18とで第1の構成に示した可変容量素子1bが2層形成される。

【0077】

以上の構成では、例えば、第1の構成例に係る可変容量素子1aの容量値C1を9pF、第2の構成例に係る可変容量素子1bの容量値C2を8pFとすると、全体の容量値が、3×9+8×2=43pFとなる。このように、第2電極18と第1電極15とを交互に複数層形成した可変容量素子1cにおいて、形成位置を異ならせた複数の第1電極15を用いることによって層毎に容量値を異ならせることができる。そして、積層数や、第1の構成例に係る可変容量素子1aを構成する層の数や、第2の構成例に係る可変容量素子1bを構成する層の数を自由に設計することができるため、種々の容量値を有する可変容量素子を構成することができる。

【0078】

〈2.第2の実施形態:可変容量素子〉

次に、本発明の第2の実施形態について説明する。本実施形態例の可変容量素子の外観は、図1と同様であるから図示を省略する。本実施形態例の可変容量素子は、容量部を構成する電極形状を変えることなく、その形成位置を異ならせることによって、容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例について順に説明する。

【0079】

[2−1 第1の構成例]

図12は、本実施形態例の第1の構成例に係る可変容量素子22aをz方向から透過してみたときの構成図である。図12において、図3に対応する部分には同一符号を付し重複説明を省略する。

【0080】

第1電極23は、積層体2の真ん中に積層された強誘電体層12の上面に複数(図12では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。各第1電極23は、積層体2の第1の側面3を構成するy方向の辺から時計回りに約45°回転した第1方向に延在して形成されている。また、各第1電極23は、第1電極部25と、第2電極部24とが第1方向に交互に接続された構成とされている。第1電極部25は、第1方向の電極幅がw1、第1方向に直行する第2方向の電極幅がw2とされた長方形状とされ、第2電極部24は、第1方向の電極幅がw1、第2方向の電極幅がw3とされた長方形状とされている。図12では、積層体2の第4の側面6側から順に形成された4つの第1電極23は、第1電極部25と第2電極部24とが交互に4つ接続された構成とされている。また、第2の側面4側に最隣接する第1電極15は、第1電極部25と第2電極部24が接続された構成とされている。

【0081】

以上のように、第1電極23が第2方向の電極幅が異なる第1電極部25と第2電極部24とによって構成されることにより、それぞれの第1電極23は第1方向に2つの電極幅を有する構成とされる。また、本実施形態例では、第1電極23の各第1電極部25の位置はy方向に水平とされ、各第2電極部24の位置はy方向に水平とされている。

【0082】

積層体2の第4の側面6側から順に形成された4つの第1電極23のそれぞれは、積層体2の第1の側面3に露出するように第1電極23と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極23は、積層体2の第2の側面4に露出するように第1電極23と同層に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0083】

第2電極26は、積層体2の真ん中に積層された強誘電体層12の下面に複数(図12では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。第2電極26は、第1方向の電極幅がw4(<w1)とされ、第2方向の電極幅がw5(>w2)とされた長方形状とされ、第2方向に延在して形成されている。

【0084】

そして、第2電極26は、1つの第1電極23に直交するか、若しくはy方向に隣接する2つの第1電極23に跨って交差するように形成されており、第1電極23の第1電極部25と第2電極26がz方向に重なるように配置されている。

積層体2の第2の側面4に近い側の4つの第2電極26は、積層体2の第1の側面3に対向する第3の側面5に露出するように第2電極26と同層に形成されたそれぞれの内部端子19に接続されている。そして、この内部端子19は、積層体2の第3の側面5に形成された第2外部端子10に接続されている。また、積層体2の第4の側面6に最隣接する第2電極26は、第4の側面6に露出するように形成されている。そして、この第2電極26は、積層体2の第4の側面6に形成された第2外部端子11に接続されている。

【0085】

以上により、第1の構成例に係る可変容量素子22aでは、図12に示すように、第1電極23の各第1電極部25と、その第1電極部25に強誘電体層12を挟んで積層された第2電極26がz方向に重なる領域において容量部が形成される。また、図12の可変容量素子22aでは、複数の第1電極23と複数の第2電極26とが構成され、さらに、一つの第1電極23に対して一つ、又は二つの第2電極26がz方向に重なるように構成される。これにより、同一面内において複数個の容量部が形成される。そして、第1の構成例に係る可変容量素子22aでは、第1電極23の第1電極部25と第2電極26がz方向に重なるような構成とされることにより、各容量部を構成する電極面積は第1電極23と第2電極26の重なり面積S4(=w2×w4)とされる。

【0086】

[2−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子について説明する。図13は、本実施形態例の第2の構成例に係る可変容量素子22bをz方向から透過してみたときの構成図である。図13において、図12に対応する部分には同一符号を付し重複説明を省略する。

【0087】

第2の構成例の可変容量素子22bでは、第1の構成例の可変容量素子22aに比較し、第1電極23が図13に示すように距離x6だけx方向の第3の側面側にシフトして形成されている。距離x6は、第1電極23の第2電極部24と第2電極26がz方向に重なる配置となる距離である。このため、第2電極26は、強誘電体層12を挟んで、第1電極23を構成する第2電極部24とz方向に重なるように配置されている。

【0088】

以上により、第2の構成例に係る可変容量素子22bでは、強誘電体層12を挟んでz方向に対向する第1電極23の各第2電極部24と、第2電極26とで容量部が形成される。そして、第2の構成例に係る可変容量素子22bでは、第1電極23の第2電極部24と第2電極26がz方向に重なるような構成とされることにより、各容量部を構成する電極面積は第1電極23と第2電極26の重なり面積S5(=w3×w4)とされる。

【0089】

第1電極23における第2電極部24の第2方向の電極幅w3は、第1電極部25の第2方向の電極幅w2よりも小さい。このため、第2の構成例における可変容量素子22bでは、各容量部を構成する電極面積は、第1の構成例における可変容量素子22aの各容量部を構成する電極面積よりも小さい。これにより、第2の構成例における可変容量素子22a全体の容量は、第1の構成例における可変容量素子22b全体の容量よりも小さくなる。

【0090】

このように、本実施形態例では、第1電極23、及び第2電極26の形状は同じであっても、第1電極23の形成位置をずらすことによって、容量値の異なる2種類の可変容量素子22a、22bを構成することができる。

【0091】

本実施形態例の可変容量素子22a、22bも、第1の実施形態と同様にして形成することができる。したがって、本実施形態例においても、電極形成時に用いるマスクを第1の構成例における可変容量素子22aを形成する場合と、第2の構成例における可変容量素子22bを形成する場合とで変える必要がない。第1の構成例の可変容量素子22aを形成する場合には、z方向に第2電極26と第1電極23の第1電極部25が積層するような位置関係となるように、各電極を強誘電体層12上にパターン形成すればよい。また、第2の構成例の可変容量素子22bを形成する場合には、z方向に第2電極26と第2電極部24が積層するような位置関係となるように、各電極を強誘電体層12上にパターン形成すればよい。

【0092】

また、本実施形態例においても、同じ電極形状であってもその形成位置を調整することで容量値の異なる可変容量素子22a、22bを形成できるようにするため、第1電極23及び第2電極26の寸法をある程度考慮する必要がある。以下に、本実施形態例の可変容量素子22a、22bの第1電極23、第2電極26の形状及び寸法の設計概要を説明する。

【0093】

第1電極23の第1電極部25及び第2電極26の第1方向の電極幅w1は、第1電極23と第2電極26との製造時における意図しない位置ずれを考慮して、第2電極26の第1方向の電極幅w4よりも所定の幅だけ広い構成とされるのが好ましい。これにより、図12でみると、第1電極部25の第1方向の中心位置と、第2電極26の第1方向の中心位置を一致させた場合、重なり面積S4の第1方向の両端にマージンM((w1−w2)/2)(第2電極26と重ならない領域)が形成される。このマージンMは、第1電極23と第2電極26との間の合わせずれを吸収できる幅であることが好ましく、例えば、10μm以上であることが好ましい。そして、製造上の制約も含めば、電極幅w1は、50μm以上であることが好ましく、より好適には、100μm以上であることが好ましい。

【0094】

このように、マージンMが形成されることにより、例えば、第1電極23が第2電極26に対して所定の位置から第1方向にずれてしまった場合、そのずれ量がマージンMの幅よりも小さければ、第1電極23と第2電極26との重なり面積は変わらない。このため、所望の容量値を有する可変容量素子を形成することが容易となる。また、第1の構成例と第2の構成例とでは、図13に示すように、第1電極23の位置が、第1電極部25及び第2電極部24のx方向の電極幅x6だけ異なる。この電極幅x6は、マージンMに比較して十分大きく、意図的にマスク位置を異ならせることでずらすことができる幅である。したがって、本実施形態例では、微少な合わせずれ程度では第1電極23と第2電極26の重なり面積は変わらず、意図した電極位置の移動によってのみ、第1電極23と第2電極26の重なる面積を変えることができる。

【0095】

また、第1電極23の第1電極部25の第1方向の電極幅と、第2電極部24の第2方向の電極幅の違いによって、第1の構成例の可変容量素子22aと、第2の構成例の可変容量素子22bとで容量値を異ならせることができる。したがって、電極幅w2と電極幅w3とを、例えば、w2:w3=1:0.8の関係となるような電極幅とすることにより、第1の構成例の可変容量素子22aの容量値と、第2の構成例の可変容量素子22bの容量値との比を1:0.8に設定することができる。ただし、電極幅w2と電極幅w3は異なる幅であればよく、種々の設定が可能である。

【0096】

また、第2電極26の第2方向の電極幅w5は、第1電極23の第1方向の最大の電極幅w2、すなわち、第1電極部25の第1方向の電極幅w2よりも大きければよい。本実施形態例では、積層体2の第4の側面6に最隣接する第2電極26は、第4の側面6の第2外部端子11に接続されるため、積層体2の第4の側面6に露出する長さに形成される必要がある。また、その他の第2電極26は、それぞれ、2つの第1電極23に跨って形成されるため、第2方向の電極幅w5は隣接する2つの第1電極23を含む第2方向の幅よりも大きく形成される必要がある。

【0097】

そして、本実施形態例では、第2電極26が長方形状とされ、その長軸方向(第2方向)が第1電極23の長軸方向(第1方向)に直交するように配置されている。このため、合わせずれにより、第2電極26と第1電極23とが所定の位置から相対的に第2方向にずれてしまった場合にも、第2電極26と第1電極23との重なり面積は変化しない。これにより、第2方向の位置ずれによって容量値が変化しない。

その他、第1の実施形態に係る可変容量素子1(1a、1b)の電極構成と同様にして各電極の寸法を設計すればよい。

【0098】

本実施形態例では、第1電極23を強誘電体層12上面に斜め配置し、第2電極26を第1電極23に直交するように強誘電体層12下面に斜め配置する。これにより、第1の実施形態に係る可変容量素子1(1a、1b)に比較し、第2電極26の内部端子19を短く構成することができる。これにより、電極抵抗を低くすることができる。また、本実施形態例においても、第1の実施形態例に係る第3の構成例のような構成とすることもできる。

その他、第1の実施形態と同様の効果を得ることができる。

【0099】

ところで、第1及び第2の実施形態では、第1電極を長軸方向に2つの電極幅を有するように形成し、その幅方向に交差する第2電極を配置することで、第1電極と第2電極の重なり面積を変更可能な構成としている。本発明はこれに限られるものではなく、例えば、第1電極をその長軸方向に2つ以上の電極幅を有するように形成する例としてもよい。この場合には、同じ電極形状で、容量値の異なる2種類以上の可変容量素子を形成することが可能となる。

【0100】

また、第2電極についても、複数の電極幅を有する形状としてもよく、この場合は、第1電極及び第2電極の形成位置を、x方向、y方向に相対的に移動することで種々の構成が可能となる。また、第1電極の複数の電極幅と、第2電極の複数の電極幅を全て違う幅とすることで、容量値の異なる可変容量素子を、第1電極の電極幅の数と第2電極の電極幅の数を掛け合わせた数だけ形成することができる。

【0101】

〈3.第3の実施形態:可変容量素子〉

次に、本発明の第3の実施形態に係る可変容量素子について説明する。本実施形態例の可変容量素子の外観は、図1と同様であるから図示を省略する。本実施形態例の可変容量素子は、容量部を構成する電極形状を変えることなく、その形成位置を異ならせることによって、容量値の異なる複数の構成を取り得る。以下に、第1の構成例、第2の構成例について順に説明する。

【0102】

[3−1 第1の構成例]

図14は、本実施形態例の第1の構成例に係る可変容量素子30aをz方向から透過してみたときの構成図である。図14において、図3に対応する部分には同一符号を付し重複説明を省略する。

【0103】

第1電極31は、積層体2の真ん中に積層された強誘電体層12の上面に複数(図14では5つ)形成されており、y方向の一方の側から他方の側に所定の距離ずつ離間して形成されている。各第1電極31は、積層体2の第1の側面3側に幅広の底辺を有し、第3の側面5側に幅狭の上辺を有し、x方向の幅がx6の(>x2)台形形状の電極部32で構成されている。すなわち、第1電極31を構成する電極部32では、積層体2の第1の側面3側から第3の側面5側に向けて連続的に幅狭になっている。積層体2の第4の側面6側から4つの第1電極31は、2つの電極部32がx方向に接続して形成された構成とされており、第2の側面4に最隣接する第1電極31は、1つの電極部32のみで構成されている。

【0104】

積層体2の第4の側面6側から順に形成された4つの第1電極31のそれぞれは、積層体2の第1の側面3に露出するように第1電極31と同層に形成された内部端子16に接続されている。そして、この内部端子16は、第1の側面3に形成されたそれぞれの第1外部端子8に接続されている。また、積層体2の第2の側面4に最隣接する第1電極31は、積層体2の第2の側面4に露出するように第1電極と同層に形成された内部端子17に接続されている。そして、この内部端子17は、積層体2の第2の側面4に形成された第1外部端子9に接続されている。

【0105】

第2電極18は、第1の実施形態における第2電極18と同形状とされ、1つの第1電極31に直交するか、若しくは、y方向に隣接する2つの第1電極31に跨って直交するように形成されている。また、第1の構成例に係る可変容量素子30aでは、第1電極31と第2電極18は、第1電極31の幅広側の領域に第2電極18がz方向に重なるように配置されている。

【0106】

以上により、第1の構成例に係る可変容量素子30aでは、図14に示すように、第1電極31と、その第1電極31に強誘電体層12を挟んで積層された第2電極18がz方向に重なる領域において容量部が形成される。また、図14の可変容量素子30aでは、複数の第1電極31と複数の第2電極18とが構成され、さらに、一つの第1電極31に対して一つ、又は二つの第2電極18がz方向に重なるように構成される。これにより、同一面内において複数個の容量部が形成される。そして、第1の構成例に係る可変容量素子30aでは、第1電極31の電極部32の幅広側において第1電極31と第2電極18がz方向に重なるような構成とされ、各容量部を構成する電極面積は第1電極31と第2電極18の重なり面積S6とされる。

【0107】

[3−2 第2の構成例]

次に、本実施形態例の第2の構成例に係る可変容量素子について説明する。図15は、本実施形態例の第2の構成例に係る可変容量素子30bをz方向から透過してみたときの構成図である。図15において、図14に対応する部分には同一符号を付し重複説明を省略する。

【0108】

第2の構成例の可変容量素子30bでは、第1の構成例の可変容量素子30aに比較し、第1電極31が距離Δx(<x2)だけx方向の第3の側面5側にシフトして形成されている。このため、第2電極18は、強誘電体層12を挟んで、第1電極31の幅狭側とz方向に重なるように配置されている。ところで、距離Δxは、第1電極31を構成する電極部32と第2電極18とがz方向に重なる範囲内とする。すなわち、Δxは少なくともとも電極部32のx方向の長さx6から第2電極18のx方向の長さx2を差し引いた長さよりも小さい値とされる。

【0109】

以上により、第2の構成例に係る可変容量素子30bでは、強誘電体層12を挟んでz方向に対向する第1電極31における電極部32の幅狭側と、第2電極18とで容量部が形成される。そして、第2の構成例に係る可変容量素子30bでは、第1電極31の電極部32の幅狭側において第1電極31と第2電極18がz方向に重なるような構成とされ、各容量部を構成する電極面積は第1電極31と第2電極18の重なり面積S7とされる。

【0110】

第2の構成例では、第1電極31の電極部32の幅狭側において、第1電極31と第2電極18とが重なる構成とされる。このため、第2の構成例における可変容量素子30bでは、各容量部を構成する電極面積は、第1の構成例における可変容量素子30aの各容量部を構成する電極面積よりも小さい。これにより、第2の構成例における可変容量素子30b全体の容量は、第1の構成例における可変容量素子30a全体の容量よりも小さくなる。

【0111】

このように、本実施形態例では、第1電極31、及び第2電極18の形状は同じであっても、第1電極31の形成位置をずらすことによって、容量値の異なる2種類の可変容量素子30a、30bを構成することができる。

【0112】

本実施形態例の可変容量素子30a、30bは、第1の実施形態と同様にして形成することができる。したがって、本実施形態例においても、電極形成時に用いるマスクを第1の構成例における可変容量素子30aを形成する場合と、第2の構成例における可変容量素子30bを形成する場合とで変える必要がない。第1の構成例の可変容量素子30aを形成する場合には、z方向に第2電極18と第1電極31の電極部32の幅広側が積層するような位置関係となるように、各電極をシート上に形成すればよい。また、第2の構成例の可変容量素子30bを形成する場合には、z方向に第2電極18と第1電極31の電極部32の幅狭部が積層するような位置関係となるように、各電極をシート上に形成すればよい。

【0113】

本実施形態例では、第1電極31を台形形状(テーパー形状)とし、第1電極31の電極幅が変化する方向に第1電極31と第2電極18との重なり位置をシフトすることにより、重なり面積は連続的に変化する。これにより、電極形状を変えることなく、重なり位置を変えることにより、容量値が微少に異なる可変容量素子を形成することができる。

【0114】

また、本実施形態例でも、第1電極31の長軸方向と第2電極18の長軸方向とが交差する。このため、第1電極31と第2電極18とがy方向に相対的に位置ずれした場合には、容量値の変化はなく、第1電極31と第2電極18とをx方向に相対的にシフトした場合にのみ容量値が変化する。これにより、x方向における第1電極31と第2電極18との相対的な位置関係を変更することでのみ容量値の異なる可変容量素子30a、30bを形成することができ、設計が容易となる。

その他、第1の実施形態と同様の効果を得ることができる。

【0115】

上記第1の実施形態〜第3の実施形態では、静電容量素子として可変容量素子を例に挙げ説明したが、本発明はこれに限定されない。上記第1の実施形態〜第3の実施形態で説明した第1電極及び第2電極の構成は、入力信号の種類及びその信号レベルに関係なく容量がほとんど変化しない静電容量素子(以下、定容量素子という)に対しても同様に適用可能である。

【0116】

ただし、この場合、誘電体層は、比誘電率の低い常誘電体材料で形成される。常誘電体材料としては、例えば、紙、ポリエチレンテレフタレート、ポリプロピレン、ポリフェニレンサルファイド、ポリスチレン、ポリスチレン、TiO2、MgTiO2、MgTiO3、SrMgTiO2、Al2O3、Ta2O5等を用いることができる。なお、このような定容量素子は、上記第1の実施形態の可変容量素子と同様にして作製することができる。上述した可変容量素子では、全ての外部端子をDC端子として用いたが、定容量素子を構成する場合にはDC端子が不要であることが明らかであり、AC端子のみの2端子品とすることもできる。

【0117】

図16に、実際の回路上における可変容量素子周辺の回路構成例を示す。

実際の回路上では、可変容量素子1の一方の端子を、バイアス除去用コンデンサ61を介して交流信号の一方の入出力端子63に接続するとともに、電流制限抵抗62を介して制御電圧の入力端子64に接続する。また、可変容量素子50の他方の端子を、交流信号の他方の入出力端子65に接続するとともに、制御電圧の出力端子66に接続する。

【0118】

このような可変容量素子1の回路構成では、信号電流(交流信号)は、バイアス除去用コンデンサ61及び可変容量素子1を流れ、制御電流(直流バイアス電流)は、電流制限抵抗62を介して可変容量素子1のみを流れる。この際、制御電圧を変化させることにより、可変容量素子1の容量Cvが変化し、その結果、信号電流も変化する。

【0119】

[可変容量素子の構成]

そこで、次に、可変容量素子1と、バイアス除去用コンデンサ61とを一体化した例を説明する。図17に、可変容量素子1と、バイアス除去用コンデンサ61とを一体化した素子の構成例を示す。なお、図17において、第1の実施形態(図3)と同様の構成には同じ符号を付して示す。

【0120】

可変容量素子1は、強誘電体層12と、強誘電体層12を挟み込むように対向して形成された可変容量素子1用の第1電極15及び第2電極18とを備える。さらに、可変容量素子1は、強誘電体層12を挟み込むように対向して形成されたバイアス除去用コンデンサ61の第1電極53及び第2電極54を備える。

【0121】

可変容量素子1用の第1電極15及びバイアス除去用コンデンサ61の第1電極53は、強誘電体層12の上面51aに、所定間隔離れて形成される。また、可変容量素子1用の第2電極18及びバイアス除去用コンデンサ61の第2電極54は、強誘電体層51の下面51bに、所定間隔離れて形成される。すなわち、本実施形態では、可変容量素子1及びバイアス除去用コンデンサ61の誘電体層を共通にする。

【0122】

また、可変容量素子1用の第1電極15とバイアス除去用コンデンサ61の第1電極53とはリード線55等で接続される。なお、可変容量素子1用の第1電極15とバイアス除去用コンデンサ61の第1電極53とを接続するための所定の電線パターンを強誘電体層12の上面51aに形成して両者を接続してもよい。

【0123】

可変容量素子1用の第1電極15及びバイアス除去用コンデンサ61の第1電極53は、リード線56により、電流制限抵抗62を介して制御電圧の入力端子64に接続される(図16及び17参照)。可変容量素子1用の第2電極18は、リード線57により、交流信号の他方の入出力端子65及び制御電圧の出力端子66に接続される。そして、バイアス除去用コンデンサ61の第2電極54は、リード線58により、交流信号の一方の入出力端子63に接続される。このように接続することにより、図16の回路構成と同様に、信号電流(交流信号)がバイアス除去用コンデンサ61及び可変容量素子1を流れ、制御電流(直流バイアス電流)は、電流制限抵抗62を介して可変容量素子1のみを流れる。

【0124】

なお、可変容量素子1用の第1電極15及び第2電極18は、上記第2及び第3の実施形態の可変容量素子で用いた第1電極及び第2電極と同様の形状でも構成することができる。一方、バイアス除去用コンデンサ61の第1電極53及び第2電極54は、従来のコンデンサと同様の形状で形成することができる。

【0125】

このように、可変容量素子1と、バイアス除去用コンデンサ61とを一体化することにより、本発明の可変容量素子を適用する装置の寸法を小さくすることができる。また、部品点数を減らすことができるので、装置のコストを低減することができる。

【0126】

〈4.第4の実施形態:共振回路〉

第4の実施形態では、上述した本発明の静電容量素子を備える非接触受信装置の構成例を説明する。

【0127】

[非接触受信装置の構成]

本実施形態では、非接触受信装置として、非接触ICカードを例に挙げ説明する。図18に、本実施形態の非接触ICカードの受信系(復調系)回路部のブロック構成を示す。なお、図18では、説明を簡略するために、信号の送信系(変調系)回路部は省略し

ている。送信系回路部の構成は、従来の非接触ICカード等と同様に構成することができる。

【0128】

非接触ICカード260は、受信部261(アンテナ)と、整流部262と、信号処理部263とを備える。

【0129】

受信部261は、共振コイル264及び共振コンデンサ265からなる共振回路を備え、非接触ICカード260のリーダライター(不図示)から送信される信号をこの共振回路で受信する。なお、図18では、共振コイル264をそのインダクタンス成分264a(L)と抵抗成分264b(r:数オーム程度)とに分けて図示している。また、受信部261は、共振コンデンサ265内の後述する可変容量素子267の制御電源270と、可変容量素子267及び制御電源270間に設けられた2つの電流制限抵抗271及び272とを備える。

【0130】

共振コンデンサ265は、容量Coの定容量コンデンサ266と、可変容量素子267と、可変容量素子267の両端子にそれぞれ接続された2つのバイアス除去用コンデンサ268及び269とで構成される。そして、定容量コンデンサ266と、可変容量素子267並びに2つのバイアス除去用コンデンサ268及び269からなる直列回路とは、共振コイル264に並列接続される。

【0131】

定容量コンデンサ266は、上述した種々の実施形態及び種々の変形例で説明した電極及び外部端子の構成を有する2端子タイプの定容量コンデンサ(定容量素子)のいずれかで構成される。定容量コンデンサ266を構成する誘電体層は、第1の実施形態で説明した比誘電率の低い誘電体材料(常誘電体材料)で形成されており、入力信号の種類(交流または直流)及びその信号レベルに関係なく、その容量はほとんど変化しない。

【0132】

なお、実際の回路上では、共振コイル264のインダクタンス成分Lのばらつきや信号処理部263内の集積回路の入力端子の寄生容量などによる受信部261の容量変動(数pF程度)が存在し、その変動量は非接触ICカード260毎に異なる。それゆえ、本実施形態では、これらの影響を抑制(補正)するために、定容量コンデンサ266内の内部電極の電極パターンをトリミングして容量Coを適宜調整する。

【0133】

可変容量素子267もまた、上述した種々の実施形態で説明した2端子タイプの可変容量素子のいずれかで構成される。なお、可変容量素子267を構成する誘電体層は、第1の実施形態で説明した比誘電率の大きな強誘電体材料で形成される。なお、本発明はこれに限定されず、可変容量素子267を4端子タイプの可変容量素子で構成してもよい。

【0134】

また、可変容量素子267は、電流制限抵抗271及び272を介して制御電源270に接続される。そして、可変容量素子267の容量Cvは、制御電源270から印加される制御電圧に応じて変化する。

【0135】

なお、バイアス除去用コンデンサ268及び269、並びに、電流制限抵抗271及び272は、制御電源から流れる直流バイアス電流(制御電流)と、受信信号電流との干渉による影響を抑制するために設けられる。具体的には、バイアス除去用コンデンサ268及び269は、信号回路の保護及び/又は分離のために設けられ、電流制限抵抗271及び272は、制御回路の保護及び/又は分離のために設けられる。

【0136】

整流部262は、整流用ダイオード273と整流用コンデンサ274とからなる半波整流回路で構成され、受信部261で受信した交流電圧を直流電圧に整流して出力する。

【0137】

信号処理部263は、主に半導体素子の集積回路(LSI:Large Scale Integration

)で構成され、受信部261で受信した交流信号を復調する。信号処理部263内のLSIは整流部262から供給される直流電圧により駆動される。なお、LSIとしては、従来の非接触ICカードと同様のものを用いることができる。

【0138】

本実施形態の非接触ICカード260において、可変容量素子267は、過大な受信信号により耐電圧性の低い半導体素子からなる制御回路が破壊されないようにするために用いられる。具体的には、受信信号が過大な場合に、制御電圧により可変容量素子267の容量Cvを小さくする。これにより、可変容量素子267の容量低下分に対応した周波数Δfだけ、受信部261の共振周波数が高域にシフトする。これにより、容量可変前の共振周波数f0における受信信号のレスポンスは、容量可変前より低くなり、受信信号のレベルが抑制される。その結果、制御回路に過大な電流信号が流れないようにすることができ、制御回路の破壊を防止することができる。

【0139】

本実施形態の非接触ICカード260では、定容量コンデンサ266及び可変容量素子267に、本発明の電極構成を有する静電容量素子を用いているので、より高性能の非接触ICカードを提供することができる。また、可変容量素子267に、本発明の電極構成を有する静電容量素子を用いているので、より低い駆動電圧で非接触ICカードを駆動することができる。

【0140】

なお、本実施形態では、定容量コンデンサ266及び可変容量素子267の両方を本発明の電極構成を有する静電容量素子で構成する例を説明したが、本発明はこれに限定されず、いずれか一方を本発明の静電容量素子で構成してもよい。また、本実施形態では、定容量コンデンサ266を備えない構成としてもよい。

【0141】

また、本実施形態の非接触ICカード260では、可変容量素子267の制御電源270を設ける例を説明したが、本発明はこれに限定されない。例えば、特許文献1等と同様に、整流部262から出力された直流電圧から、例えば抵抗分割等の手法により所望の制御電圧を抽出するような構成にしてもよい。

【0142】

さらに、本実施形態では、非接触受信装置の一例として、非接触ICカードを例にとり説明したが、本発明はこれに限定されない。本発明は、共振コイル及び共振コンデンサからなる共振回路を用いて非接触で情報及び/または電力を受信する任意の装置に適用可能であり、同様の効果が得られる。例えば、携帯電話等や、ワイアレス電力伝送装置にも適用可能である。なお、ワイアレス電力伝送装置では、電力を非接触で伝送する装置であるので、非接触ICカードのように受信信号を復調する信号処理部を備えなくてもよい。

【符号の説明】

【0143】

1、1a、1b、1c・・・可変容量素子、2・・・積層体、3・・・第1の側面、4・・・第2の側面、5・・・第3の側面、6・・・第4の側面、8・・・第1外部端子、9・・・第1外部端子、10・・・第2外部端子、11・・・第2外部端子、12・・・強誘電体層、13・・・第1電極部、14・・・第2電極部、15・・・第1電極、16、17・・・内部端子、18・・・第2電極、19・・・内部端子、20、21・・・容量部、22a、22b・・・可変容量素子、23・・・第1電極、24・・・第2電極部、25・・・第1電極部、26・・・第2電極、30a、30b・・・可変容量素子、31・・・第1電極、32・・・電極部

【特許請求の範囲】

【請求項1】

誘電体層と、

前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極と

を備える静電容量素子。

【請求項2】

前記誘電体層を挟んで重なる電極の面積は、前記一方の電極を一定量だけ移動したときにのみ段階的に変えることができる

請求項1に記載の静電容量素子。

【請求項3】

前記一方の電極と前記他方の電極は、互いの電極の長軸方向が直交するように配置されている

請求項1又は2に記載の静電容量素子。

【請求項4】

前記一対の電極又は複数対の電極は、誘電体層の厚さ方向に複数層積層されている

請求項1〜3のいずれかに記載の静電容量素子。

【請求項5】

前記誘電体層が強誘電体材料で形成され、外部から印加される制御信号に応じて容量が変化する

請求項1〜4のいずれかに記載の静電容量素子。

【請求項6】

誘電体層と、前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極とを備える静電容量素子の製造方法であって、

前記一方の電極及び他方の電極は、前記誘電体層上面の所定の位置に位置あわせしたマスクを用いてパターン形成し、

前記一方の電極又は/及び他方の電極の形成は、前記一方の電極と前記他方の電極の前記誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように前記誘電体層上面に配置するマスクの位置を調整しながら形成する

静電容量素子の製造方法。

【請求項7】

前記一方の電極、又は/及び他方の電極は、前記誘電体層を挟んで重なる電極の面積が、前記一方の電極を一定量だけ移動したときにのみ段階的に変えることができる形状とする

請求項6に記載の静電容量素子の製造方法。

【請求項8】

前記一方の電極と前記他方の電極は、互いの電極の長軸方向が直交するように形成する

請求項6又は7に記載の静電容量素子の製造方法。

【請求項9】

前記一対の電極又は複数対の電極を、誘電体層の厚さ方向に複数層積層する

請求項6〜8のいずれかに記載の静電容量素子の製造方法。

【請求項10】

前記誘電体層を、外部から印加される制御信号に応じて容量が変化する強誘電体材料で形成する

請求項6〜9のいずれかに記載の静電容量素子の製造方法。

【請求項11】

誘電体層と、前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極とを有する静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【請求項1】

誘電体層と、

前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極と

を備える静電容量素子。

【請求項2】

前記誘電体層を挟んで重なる電極の面積は、前記一方の電極を一定量だけ移動したときにのみ段階的に変えることができる

請求項1に記載の静電容量素子。

【請求項3】

前記一方の電極と前記他方の電極は、互いの電極の長軸方向が直交するように配置されている

請求項1又は2に記載の静電容量素子。

【請求項4】

前記一対の電極又は複数対の電極は、誘電体層の厚さ方向に複数層積層されている

請求項1〜3のいずれかに記載の静電容量素子。

【請求項5】

前記誘電体層が強誘電体材料で形成され、外部から印加される制御信号に応じて容量が変化する

請求項1〜4のいずれかに記載の静電容量素子。

【請求項6】

誘電体層と、前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極とを備える静電容量素子の製造方法であって、

前記一方の電極及び他方の電極は、前記誘電体層上面の所定の位置に位置あわせしたマスクを用いてパターン形成し、

前記一方の電極又は/及び他方の電極の形成は、前記一方の電極と前記他方の電極の前記誘電体層の厚み方向に重なる電極の面積が所定の面積を有するように前記誘電体層上面に配置するマスクの位置を調整しながら形成する

静電容量素子の製造方法。

【請求項7】

前記一方の電極、又は/及び他方の電極は、前記誘電体層を挟んで重なる電極の面積が、前記一方の電極を一定量だけ移動したときにのみ段階的に変えることができる形状とする

請求項6に記載の静電容量素子の製造方法。

【請求項8】

前記一方の電極と前記他方の電極は、互いの電極の長軸方向が直交するように形成する

請求項6又は7に記載の静電容量素子の製造方法。

【請求項9】

前記一対の電極又は複数対の電極を、誘電体層の厚さ方向に複数層積層する

請求項6〜8のいずれかに記載の静電容量素子の製造方法。

【請求項10】

前記誘電体層を、外部から印加される制御信号に応じて容量が変化する強誘電体材料で形成する

請求項6〜9のいずれかに記載の静電容量素子の製造方法。

【請求項11】

誘電体層と、前記誘電体層を狭むように前記誘電体層の一方の面上に形成された一方の電極と前記誘電体層の他方の面上に形成された他方の電極とからなる一対、又は複数対の電極であって、一方の電極と他方の電極は、互いの電極の長軸方向が交差するように配置され、一方の電極、又は/及び他方の電極が少なくとも2つ以上の電極幅を有し、一方の電極を他方の電極に対して相対的に移動して形成した場合に前記誘電体層を挟んで前記誘電体層の厚み方向に重なる電極の面積を、連続的、又は段階的に変更可能な一対、又は複数対の電極とを有する静電容量素子を含む共振コンデンサと、

前記共振コンデンサに接続された共振コイルと

を備える共振回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2012−60030(P2012−60030A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−203580(P2010−203580)

【出願日】平成22年9月10日(2010.9.10)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月10日(2010.9.10)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]