非接触電子装置

【課題】キャリア蓄積を用いたトランジスタによって構成された非接触電子装置を、通信距離及び通信状況によらず安定して動作させ、かつ当該非接触電子装置の通信可能距離を増大させることを目的とする。

【解決手段】キャリア蓄積を利用したトランジスタによって構成された非接触電子装置であって、アンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、アンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、第一の直流電源電圧が第一の平滑化コンデンサによって平滑化された電圧を用いて動作する論理回路と、論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、第一の直流電源電圧が第一の平滑化コンデンサによって平滑化された電圧を第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする。

【解決手段】キャリア蓄積を利用したトランジスタによって構成された非接触電子装置であって、アンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、アンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、第一の直流電源電圧が第一の平滑化コンデンサによって平滑化された電圧を用いて動作する論理回路と、論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、第一の直流電源電圧が第一の平滑化コンデンサによって平滑化された電圧を第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタによって構成された非接触電子装置に関し、特にキャリア蓄積を用いたトランジスタによって構成された非接触電子装置に関する。

【背景技術】

【0002】

アンテナ及び半導体集積回路装置を搭載した非接触電子装置(所謂ICタグ)は、無線通信による個体識別を可能とし、識別対象物の生産・管理等に利用されている。

【0003】

ICタグの機能について説明する。

【0004】

ICタグは、リーダ・ライタ装置との間で情報を交換するものであって、自身が保持しているデータをリーダ・ライタ装置に送信する機能、及び、リーダ・ライタ装置から送信されたデータを保持する機能等を備える。

【0005】

具体的には、ICタグは、リーダ・ライタ装置から供給されたキャリア信号をアンテナを介して受信し、受信したキャリア信号から直流電源電圧を生成し、生成した直流電源電圧をICタグに搭載された半導体集積回路装置に供給する。また、ICタグは、半導体集積回路装置内でキャリア信号に重畳したデータをリーダ・ライタ装置に送信する。

【0006】

ICタグが、データをリーダ・ライタ装置に送信する場合、半導体集積回路装置内に搭載された負荷変調回路を用いる。

【0007】

負荷変調回路は、半導体集積回路装置の消費電力を変動させる回路である。負荷変調回路によって、アンテナを構成するアンテナ端子の間の電圧が変動し、この変動が電磁場を介しリーダ・ライタ装置に伝送されることによって、リーダ・ライタ装置はデータを検出する。

【0008】

ICタグに搭載される半導体集積回路装置は、シリコンを用いたトランジスタ(MOSFET(Metal Oxide Semiconductor Field Effect Transistor))を主に用いて製造される。これによって、ICタグの大量生産によるコスト低減を実現でき、ICタグの普及の一助となっている。

【0009】

近年、従来のシリコンを用いたトランジスタでは達成困難なICタグの新規機能を実現するため、トランジスタに用いる半導体材料及びトランジスタ構造が提案されている。

【0010】

新規な半導体材料によって構成されたトランジスタ又は新規な構造のトランジスタを搭載したICタグであっても、既存のICタグと同じ通信形態及び通信範囲が求められる。

【0011】

近年、ICタグに用いられるようになったキャリア蓄積を用いたトランジスタについて、図16を用いて説明する。

【0012】

図16は、キャリア蓄積を用いたトランジスタを説明するための断面図である。

【0013】

キャリア蓄積を用いたトランジスタは、半導体層(チャネル層CL1)が酸化物半導体である薄膜トランジスタ(TFT)であり、具体的には、第一金属層ML1、チャネル層CL1、絶縁体層IL1、第二金属層ML2、及び基板層SL1から構成される。

【0014】

第一金属層ML1は、モリブデンで構成され、ドレイン電極及びソース電極を形成する。チャネル層CL1は、金属酸化物を主に含む半導体(酸化物)で構成される。酸化物半導体は、アモルファスインジウム亜鉛酸化物(a−IGZO)及び亜鉛スズ酸化物(ZTO)等である。絶縁体層IL1は、シリカ(SiO2)で構成される。第二金属層ML2は、第一金属層ML1と同じく、モリブデンで構成される。また、第二金属層ML2は、ゲート電極を形成する。基板層SL1は石英で構成される。

【0015】

キャリア蓄積を用いたトランジスタの動作について簡単に説明する。

【0016】

ゲート電極とソース電極との間に電圧が印加された場合、ゲート電極とソース電極との間の静電容量によってチャネル層CL1にキャリアが蓄積する。この状態で、ドレイン電極とソース電極との間に電圧が印加された場合、キャリア層CL1に蓄積されるキャリアが増大することによってドレイン電極とソース電極との間の導電率が増大する。これによって、ドレイン電極からソース電極へ電流が流れる。

【0017】

なお、通常のトランジスタ(例えば、MOSFET)は、ドレイン電極とソース電極との間の導電率を増大させるために、反転層を用いる。キャリア蓄積を用いたトランジスタは、上述したように、ドレイン電極とソース電極との間の導電率を増大させるために、チャネル層CL1(蓄積層)を用いる。このため、通常のトランジスタのゲート電極とソース電極との間の静電容量は数フェムトファラッド以下であるのに対して、キャリア蓄積を用いたトランジスタのゲート電極とソース電極との間の静電容量は数十〜数百フェムトファラッド程度となり、キャリア蓄積を用いたトランジスタのゲート電極とソース電極との間の静電容量は、通常のトランジスタのゲート電極とソース電極との間の静電容量よりも大きくなる。

【0018】

図17は、ICタグに搭載される従来の半導体集積回路装置の第1の回路構成の説明図である。

【0019】

半導体集積回路装置は、アンテナ端子LA及びLB、整流回路T1、負荷変調回路T2、並びに論理回路L1を備える。

【0020】

アンテナ端子LA及びLBは、ICタグに搭載されるアンテナに接続される。

【0021】

整流回路T1は、アンテナを介して受信した電力を直流電力に変換する。整流回路T1は、平滑化コンデンサC1に接続される。平滑化コンデンサC1は、整流回路T1によって変換された直流電力を平滑化する。

【0022】

論理回路L1は、整流回路T1が出力する直流電力で動作し、各種処理を実行する。

【0023】

負荷変調回路T2は、論理回路L1からの変調信号をアンテナから出力するために、半導体集積回路装置の消費電力を変動させることによって、アンテナ端子LA及びLB間の電圧を変動させる。具体的には、負荷変調回路T2は、半導体集積回路装置の消費電力を増大させることによって、アンテナ端子LA及びLB間の電圧を低下させ、半導体集積回路装置の消費電力を低下させるころによって、アンテナ端子LA及びLB間の電圧を増大させる。

【0024】

図18は、図17に示す半導体集積回路装置における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0025】

図17で説明したように、負荷変調回路T2は、半導体集積回路装置における消費電力を増大させることによって、アンテナ端子LA及びLB間の電圧(LA−LB)を低下させることができる。しかし、これによって、整流回路T1が出力する直流電力の電圧(VDD1)も低下してしまう。

【0026】

整流回路T1が出力する直流電力の電圧が低下すると、直流電力で動作する論理回路L1は、不具合が発生する。この不具合は、例えば、初期化していないにもかかわらず初期化信号を発行してしまう不具合、動作速度が不安定になる不具合、クロック信号が不安定になる不具合等がある。

【0027】

このため、負荷変調回路T2による直流電力の電圧(VDD1)の低下をできるだけ防止することが望まれる。

【0028】

しかしながら、ICタグとリーダ・ライタ装置との間の距離が長ければ長いほど、アンテナ端子間電圧の振幅を大きくしなければならず、負荷変調回路T2は、半導体集積回路装置における消費電力の変動を増大させなければならない。このため、負荷変調回路T2が直流電力の電圧(VDD1)を低下させてしまうことを妨げることができない。

【0029】

以上より、図17に示す半導体集積回路装置は、負荷変調回路T2が直流電力の電圧(VDD1)の変動を増大させると、論理回路L1の動作電圧も変動させてしまう点が欠点である。

【0030】

そこで、負荷変調回路T2をアンテナ端子LA及びLBに直接接続する図19に示すような半導体集積回路装置が用いられる。

【0031】

図19は、ICタグに搭載される従来の半導体集積回路装置の第2の回路構成の説明図である。

【0032】

上述したように、図19に示す半導体集積回路装置の負荷変調回路T2がアンテナ端子LA及びLBに直接接続される。

【0033】

ここで、負荷変調回路T2が図16に示すキャリア蓄積を用いたトランジスタである場合、キャリア蓄積を用いたトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量を介して、アンテナ端子が受信した高周波信号が論理回路L1に伝達されてしまう場合がある。これは、図16で説明したように、キャリア蓄積を用いたトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量が、通常のトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量よりも例えば10倍〜100倍以上大きいことに起因する。

【0034】

図20は、図19に示す半導体集積回路装置における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0035】

図19に示す半導体集積回路装置では、図20に示すように、論理回路L1が出力する変調信号電圧(MOD1)に高周波信号が伝搬してしまう。

【0036】

高周波信号が論理回路L1に伝達すると、論理回路L1の動作が不安定となる問題がある。

【0037】

特許文献1及び2には、アンテナが受信した電力から論理回路L1用の電源電圧を生成する整流回路と、アンテナが受信した電力から負荷変調回路用の電源電圧を生成する整流回路とを備える半導体集積回路装置、つまり、図19に示す半導体集積回路装置に類似する半導体集積回路装置が開示されている。

【0038】

また、特許文献3には、アンテナ端子間に接続されるコンデンサの静電容量が高周波信号の伝達を抑制することが開示されている。

【先行技術文献】

【特許文献】

【0039】

【特許文献1】国際公開第2004/064346

【特許文献2】特開平10−322250号公報

【特許文献3】特開2005−267643号公報

【発明の概要】

【発明が解決しようとする課題】

【0040】

特許文献1及び2には開示された技術では、送受信回路と電源回路を分離することで、送受信特性を向上させる技術が開示されていたが、図19及び図20で説明したように、論理回路に高周波信号が伝達することを防ぐための技術ではなく、特許文献3に示されているように十分な変調度が得られない場合がある。

【0041】

また、特許文献3に開示された開示された技術では、論理回路への高周波信号の伝達を防止することはできない。

【0042】

本発明は、キャリア蓄積を用いたトランジスタによって構成された非接触電子装置を、通信距離及び通信状況によらず安定して動作させ、かつ当該非接触電子装置の通信可能距離を増大させることを目的とする。

【課題を解決するための手段】

【0043】

本発明の代表的な一例を示せば、キャリア蓄積を利用したトランジスタによって構成される非接触電子装置であって、第一の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第一のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、第二の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第二のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、前記第一の平滑化コンデンサによって前記第一の直流電源電圧が平滑化された電圧を用いて動作する論理回路と、前記論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記変調信号増幅回路が出力する第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする。

【発明の効果】

【0044】

本願において開示される発明のうち代表的なものによって得られる効果を簡潔に説明すれば、下記の通りである。すなわち、キャリア蓄積を用いたトランジスタによって構成された非接触電子装置を、通信距離及び通信状況によらず安定して動作させ、かつ、当該非接触電子装置の通信可能距離を増大させることができる。

【図面の簡単な説明】

【0045】

【図1】本発明の第1実施形態のICタグシステムの説明図である。

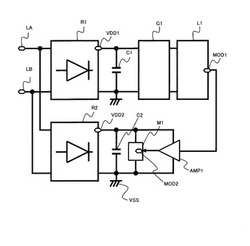

【図2】本発明の第1実施形態のICチップの回路構成の説明図である。

【図3】本発明の第1実施形態の整流回路に適用可能な整流回路の説明図である。

【図4】本発明の第1実施形態の整流回路に適用可能な整流回路の説明図である。

【図5】本発明の第1実施形態のレギュレータ回路に適用可能な回路の説明図である。

【図6】本発明の第1実施形態のレギュレータ回路に適用可能な回路の説明図である。

【図7】本発明の第1実施形態の負荷変調回路に適用可能な回路の説明図である。

【図8】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図9】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図10】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図11】本発明の第1実施形態のICチップにおける直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【図12】本発明の第2実施形態のICチップの回路構成の説明図である。

【図13】本発明の第3実施形態のICチップの回路構成の説明図である。

【図14】本発明の第3実施形態の比較回路に適用可能な回路の説明図である。

【図15】本発明の第4実施形態のICチップの回路構成の説明図である。

【図16】キャリア蓄積を用いたトランジスタを説明するための断面図である。

【図17】ICタグに搭載される従来の半導体集積回路装置の第1の回路構成の説明図である。

【図18】第1の回路構成の半導体集積回路装置における直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【図19】ICタグに搭載される従来の半導体集積回路装置の第2の回路構成の説明図である。

【図20】第2の回路構成半導体集積回路装置における直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【発明を実施するための形態】

【0046】

(第1実施形態)

以下、本発明の第1実施形態を図1〜図11を用いて説明する。

【0047】

図1は、本発明の第1実施形態のICタグシステムの説明図である。

【0048】

ICタグシステムは、リーダ・ライタ装置RW1及びICタグTG1を備える。

【0049】

ICタグTG1は、リーダ・ライタ装置RW1からデータを受信し、自身に格納されたデータをリーダ・ライタ装置RW1に送信する。

【0050】

リーダ・ライタ装置RW1は、ICタグTG1からデータを受信し(データの読み出し)、また、ICタグTG1にデータを送信する(データの書き込み)。なお、本実施形態では、リーダ・ライタ装置RW1は、データの読み込み機能及びデータの書き込み機能を備えるものとして説明するが、データの書き込み機能は必須の構成ではない。

【0051】

ICタグTG1は、アンテナコイルA1、共振コンデンサC4、及びICチップIC1を備える。

【0052】

リーダ・ライタ装置RW1は、アンテナコイルA2を備え、アンテナコイルA2を介して高周波信号を放射する。リーダ・ライタ装置RW1とICタグTG1とは磁界結合しているため、アンテナコイルA1から放射された高周波信号は、アンテナコイルA1及び共振コンデンサC4を介してICチップIC1に入力される。なお、磁界結合とはアンテナコイルA1及びA2が発生させる磁界によって、アンテナコイルA1及びA2が結合している状態である。

【0053】

ICタグTG1への高周波信号の入力について説明する。

【0054】

リーダ・ライタ装置RW1は、アンテナコイルA2に印加される電圧を変動させることによって、アンテナコイルA2が発生させる磁界を変動させる。また、磁界の変動によってICタグTG1のアンテナコイルA1の電圧として観測される高周波信号が発生するため、ICタグTG1は送信信号を検出できる。このようにして、高周波信号がアンテナコイルA1からアンテナコイルA2に入力される。

【0055】

ICチップIC1は、入力された高周波信号から自身を起動させるための電源電圧を生成し、必要な場合には入力された高周波信号から命令を抽出する。また、ICチップIC1は、リーダ・ライタ装置RW1からの命令に対する応答信号を生成し、生成した応答信号をアンテナコイルA2を介してリーダ・ライタ装置RW1に送信する。

【0056】

ICチップIC1の応答信号をリーダ・ライタ装置RW1に送信する機能について説明する。

【0057】

ICチップIC1は、応答信号をリーダ・ライタ装置RW1に送信する場合、自身の消費電力を変動させることによって、アンテナコイルA1の端子間(LA―LB)の電圧を変動させる。上述したように、アンテナコイルA1及びA2が磁界結合しているため、アンテナコイルA1の端子間の電圧の変動は、アンテナコイルA2の端子間の電圧の変動としてリーダ・ライタ装置RW1によって検出される。このようにして、ICチップIC1は、応答信号をリーダ・ライタ装置RW1に送信できる。

【0058】

なお、図1では、リーダ・ライタ装置RW1とICタグTG1との間の磁界結合を利用して、ICチップIC1の電源電圧を生成し、リーダ・ライタ装置RW1とICタグTG1との間でデータを通信する磁界結合方式を用いたが、マイクロ波方式を用いてもよい。

【0059】

マイクロ波方式は、リーダ・ライタ装置RW1が電波を放射し、アンテナによって当該高周波信号を受信することでICチップIC1が電源電圧を生成し、電波を利用してリーダ・ライタ装置RW1とICタグTG1との間でデータを通信する方式である。

【0060】

磁界結合方式又はマイクロ波方式を用いるかは、リーダ・ライタ装置RW1とICタグTC1との無線通信周波数に依存し、一般に無線通信周波数が125kHz〜135kHz、及び13.56MHzである場合には磁界結合方式を用い、無線通信周波数が2.45GHzである場合にはマイクロ波方式を用いる。

【0061】

図2は、本発明の第1実施形態のICチップIC1の回路構成の説明図である。

【0062】

ICチップIC1は、アンテナ端子LA及びLB、整流回路R1、平滑化コンデンサC1、レギュレータ回路G1、論理回路L1、送信用増幅回路(変調信号(MOD1)増幅回路)AMP1、負荷変調回路MOD2、平滑化コンデンサC2、及び整流回路R2を備える。

【0063】

アンテナ端子LA及びLBには、図1に示すアンテナコイルA1及び共振コンデンサC4が接続される。また、アンテナ端子LA及びLBには、整流回路R1及びR2が接続される。

【0064】

整流回路R1及びR2は、リーダ・ライタ装置R1からアンテナコイルA1が受信した高周波信号によってアンテナ端子LA及びLA間の電圧(交流電圧)を直流電源電圧に変換する回路であり、整流回路R1及びR2の詳細は、図3及び図4で詳細を説明する。

【0065】

本発明は、アンテナ端子LA及びLBに接続される整流回路R1及びR2は、図16に示すキャリア蓄積を用いるトランジスタによって構成されることを前提とする。なお、本発明のICチップIC1に搭載されるすべてのトランジスタが図16に示すキャリア蓄積を用いるトランジスタによって構成されてもよい。

【0066】

整流回路R1から直流電源電圧に変換された直流電源電圧VDD1が出力され、整流回路R2から直流電源電圧に変換された直流電源電圧VDD2が出力される。なお、基準電圧は電圧VSSとする。直流電源電圧VDD1は論理回路L1の動作に用いられ、直流電源電圧VDD2は送信用増幅回路AMP1及び負荷変調回路M1の動作に用いられる。

【0067】

整流回路R1の直流電源電圧VDD1の出力先には、平滑化コンデンサC1、レギュレータ回路G1、及び論理回路L1が接続される。

【0068】

平滑化コンデンサC1は、直流電源電圧VDD1を平滑化し、直流電源電圧VDD1の高周波ノイズを除去する。

【0069】

レギュレータ回路G1は、論理回路L1に過大な電圧及び電流が印加されることを防止する。また、レギュレータ回路G1は、高周波信号の振幅が大きい場合(例えば、1μW〜10μW)であっても、安定した電圧を生成することによって、論理回路L1の動作を安定させる。なお、レギュレータ回路G1の詳細は、図5及び図6で詳細を説明する。

【0070】

論理回路L1は、直流電源電圧VDD1によって動作し、高周波信号に重畳された命令に対応する処理を実行する。また、論理回路L1は、IDデータ等を保持し、当該IDデータ等に基づく演算処理を実行する。さらに、論理回路L1は、リーダ・ライタ装置RW1に送信する送信信号等を生成する。

【0071】

整流回路R2の直流電源電圧回路VDD2の出力先には、平滑化コンデンサC2、負荷変調回路M1、及び送信用増幅回路AMP1が接続される。

【0072】

平滑化コンデンサC2は、平滑化コンデンサC1と同じく、直流電源電圧VDD2を平滑化し、直流電源電圧VDD2の高周波ノイズを除去する。

【0073】

負荷変調回路M1は、変調信号MOD2に応じて、自身の消費電力を変動させることによって、ICチップIC1の消費電力を変動させ、アンテナ端子LA及びLB間の電圧を変動させ、変調信号MOD2をリーダ・ライタ装置RW1に送信する。換言すれば、負荷変調回路M1は、変調信号MOD2に応じて、自身の消費電力を変動させ、整流回路R2が出力する直流電源電圧VDD2を変動させることによって、アンテナ端子LA及びLB間の電圧を変動させる。なお、負荷変調回路M1の詳細は、図7で説明する。

【0074】

送信用増幅回路AMP1は、論理回路L1から出力された送信信号である変調信号MOD1を増幅した変調信号MOD2を負荷変調回路M1に入力する。なお、送信用増幅回路AMP1の詳細は、図8〜図10で説明する。

【0075】

以上のように、本実施形態のICチップIC1は、整流回路R1によって論理回路L1を動作させるための直流電源電圧VDD1を生成し、さらに、整流回路R2によって、負荷変調回路M1が変動させる直流電源電圧VDD2を生成する。このため、負荷変調回路M1が直流電源電圧VDD2を低減させても、直流電源電圧VDD1には影響ないので、論理回路L1への電源電圧を安定させつつ、変調信号MOD2の振幅を大きくすることができる。また、整流回路R1及びR2のトランジスタに図16に示すキャリア蓄積を用いたトランジスタである薄膜トランジスタを採用しても、整流回路R1及びR2に接続される平滑化コンデンサC1及びC2によって高周波が論理回路L1に入力することを防止できる。

【0076】

また、論理回路L1から出力される変調信号MOD1の最大電圧は、論理回路L1及びレギュレーション回路G1によって直流電源電圧VDD1よりも低下する。このため、総信用増幅回路AMP1によって、この変調信号MOD1の電圧を直流電源電圧VDD2まで増幅させる。これによって、変調信号MOD2の振幅を増幅させることができ、ICタグTG1の通信可能距離を大きくすることができる。

【0077】

図3は、本発明の第1実施形態の整流回路R1及びR2に適用可能な整流回路の説明図である。

【0078】

図3に示す整流回路は、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合の電圧のみを出力する半波整流回路である。

【0079】

図3に示す整流回路はトランジスタT1を備える。トランジスタT1のゲート電極及びドレイン端子はアンテナ端子LAに接続され、ソース電極は直流電源電圧VDD4の出力先となる。アンテナ端子LBはトランジスタT1には接続されず、アンテナ端子LBに印加される電圧は基準電圧VSSとなる。

【0080】

トランジスタT1は、ドレイン端子からソース電極へ電流が流れる電圧(アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合の電圧)のみを出力する。

【0081】

図3に示す半波整流回路を用いた場合、図4に示す全波整流回路を用いた場合よりも整流回路に使用するトランジスタ数を低減できるので、ICチップIC1の製造コストを低減できる。

【0082】

なお、図3に示す半波整流回路を整流回路R1及びR2に適用する場合、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性よりも、大きな電流が流れるように設計することが好適である。しかし、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性と、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性とを同じにしてもよいし、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性よりも、小さな電流が流れるように設計されてもよい。

【0083】

図4は、本発明の第1実施形態の整流回路R1及びR2に適用可能な整流回路の説明図である。

【0084】

図4に示す整流回路は、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合には、アンテナ端子LAがトランジスタT5を介してVDD4端子と接続され、アンテナ端子LBがトランジスタT4を介して基準電圧VSS端子と接続され、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも小さい場合には、アンテナ端子LAがトランジスタT3を介して基準電圧VSS端子と接続され、アンテナ端子LBがトランジスタT6を介して電圧VDD4端子と接続される。これによって、図4に示す整流回路は、すべてのサイクルの電圧を直流電源電圧として出力する全波整流回路である。

【0085】

図4に示す整流回路は、トランジスタT3、T4、T5、及びT6を備える。

【0086】

トランジスタT3のドレイン端子はアンテナ端子LAに接続され、ゲート端子はアンテナ端子LBに接続され、ソース端子からは基準電圧VSSが出力される。

【0087】

トランジスタT4のドレイン端子はアンテナ端子LBに接続され、ゲート端子はアンテナ端子LAに接続され、ソース端子からは基準電圧VSSが出力される。

【0088】

トランジスタT5のドレイン端子及びゲート端子はアンテナ端子LAに接続され、ソース端子からは直流電源電圧VDD4が出力される。

【0089】

トランジスタT6のドレイン端子及びゲート端子はアンテナ端子LBに接続され、ソース端子からは直流電源電圧VDD4が出力される。

【0090】

アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧より高い場合、トランジスタT3及びT6は、ドレイン端子からソース端子へはほとんど電流が流れないオフ状態となる。また、この場合、トランジスタT4及びT5は、ドレイン端子からソース端子へ電流が流れるオン状態となる。

【0091】

したがって、直流電源電圧VDD4はアンテナ端子LAに印加される電圧と近い電圧となり、基準電圧VSSはアンテナ端子LBに印加される電圧と近い電圧となる。

【0092】

一方、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧より低い場合、トランジスタT4及びT5は、ドレイン端子からソース端子へはほとんど電流が流れないオフ状態となる。また、この場合、トランジスタT3及びT6は、ドレイン端子からソース端子へ電流が流れるオン状態となる。

【0093】

したがって、直流電源電圧VDD4はアンテナ端子LBに印加される電圧と近い電圧となり、基準電圧VSSはアンテナ端子LAに印加される電圧と近い電圧となる。

【0094】

このようにして、図4に示す整流回路は、アンテナ端子LA及びLBに印加される電圧の大小に関係なく、すべてのサイクルの電圧を直流電源電圧VDD4として出力できる。これによって、図4に示す全波整流回路を整流回路に適用した場合、図3に示す半波整流回路を整流回路に適用した場合よりも、使用するトランジスタ数は増大するが、電力変換効率が高くなる。

【0095】

なお、図4に示す全波整流回路を整流回路R1及びR2に適用する場合、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性よりも、大きな電流が流れるように設計することが好適である。しかし、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性と、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性とを同じにしてもよいし、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性よりも、小さな電流が流れるように設計されてもよい。

【0096】

また、整流回路R1及びR2の一方に図4に示す全波整流回路を適用し、他方に図3に半波整流回路を適用してもよいし、整流回路R1及びR2の両方に図3に示す半波整流回路又は図4に示す全波整流回路を適用してもよい。

【0097】

図5は、本発明の第1実施形態のレギュレータ回路G1に適用可能な回路の説明図である。

【0098】

図5に示すレギュレータ回路G1は、所謂、シャントレギュレータと呼ばれる構成である。

【0099】

図5に示すレギュレータ回路では、直流電源電圧VDD1と基準電圧VSSとの間にトランジスタT7及び電源モニタ回路MON1が接続される。

【0100】

電源モニタ回路MON1には直流電源電圧VDD1が入力され、電源モニタ回路MON1は、直流電源電圧VDD1の増大に即して増大するREG信号をトランジスタT7のゲート端子に入力する。

【0101】

トランジスタは、ゲート端子に流れる電流が増大すると、ドレイン端子からソース端子に流れる電流も増大させるため、トランジスタT7は、REG信号の増大に伴って直流電源電圧VDD1と基準電圧VSSとの間に流れる電流を増大させ、ICチップIC1の消費電流を増大させる。これによって、トランジスタT7は、REG信号の増大に伴って、直流電源電圧VDD1と基準電圧VSSとの間の電圧を降下させることができる。

【0102】

このようにして、図5に示すレギュレータ回路G1は、直流電源電圧VDD1が過大となった場合には、当該過大な直流電源電圧VDD1を論理回路L1に入力することを防止できる。

【0103】

なお、電源モニタ回路MON1の詳細な説明は省略するが、電源モニタ回路MON1は、例えばトランジスタを用いて構成できる。

【0104】

図6は、本発明の第1実施形態のレギュレータ回路G1に適用可能な回路の説明図である。

【0105】

図6に示すレギュレータ回路G1は、所謂、クランプ回路である。

【0106】

図6に示すレギュレータ回路G1は、直流電源電圧VDD1と基準電圧VSSとの間にショットキーバリアダイオードD1を備える。ショットキーバリアダイオードD1のカソードに直流電源電圧VDD1が入力され、アノードに基準電圧VSSが入力される。

【0107】

ここで、ショットキーバリアダイオードD1は、降伏電圧がPN接合ダイオードよりも低く、カソードに印加される直流電源電圧VDD1が降伏電圧以上である場合、自身に流れる電流を増大させる。

【0108】

これによって、図6に示すレギュレータ回路G1は、直流電源電圧VDD1が降伏電圧以上である場合、直流電源電圧VDD1を降下させることができるので、過大な直流電源電圧VDD1を論理回路L1に入力することを防止できる。

【0109】

なお、図6に示すレギュレータ回路は、ショットキーバリアダイオードD1を用いたが、ショットキーバリアダイオードD1の代わりに定電圧ダイオードを用いてもよい。

【0110】

図7は、本発明の第1実施形態の負荷変調回路M1に適用可能な回路の説明図である。

【0111】

図7に示す負荷変調回路M1は、インピーダンス素子Z1、及びトランジスタT2を備える。

【0112】

具体的には、直流電源電圧VDDと基準電圧VSSとの間に、インピーダンス素子Z1を介してトランジスタT2が接続される。

【0113】

トランジスタT2のゲート端子には変調信号MOD2が入力され、トランジスタT2のドレイン端子には直流電源電圧VDDからインピーダンス素子Z1に印加される電圧を減じた電圧が入力され、トランジスタT2のソース端子には基準電圧VSSが入力される。

【0114】

トランジスタT2は、ゲート端子に入力される変調信号MOD2の電圧の増減に伴って、ドレイン端子からソース端子に流れる電流を増減させる。これによって、トランジスタT2は、ICチップIC1の消費電力を増減させ、変調信号MOD2の電圧の増減に伴ってアンテナ端子LAとLBとの間の電圧を変動させることができる。

【0115】

なお、インピーダンス素子Z1は、インピーダンスを有する素子であればよく、例えば、抵抗及びコンデンサであればよい。また、インピーダンス素子Z1はインピーダンスが「0」であってもよい。すなわち、トランジスタT2のドレイン端子に直流電源電圧VDDが直接入力されてもよい。

【0116】

また、負荷変調回路M1の消費電力は、ICチップIC1の消費電力を鑑みて、トランジスタT2のドレイン端子とソース端子との間電流特性及びインピーダンス素子Z1のインピーダンスを調整することによって調整できる。

【0117】

図8は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0118】

図8に示す送信用増幅回路AMP1は、トランジスタT8及びT9を備える。

【0119】

トランジスタT8のドレイン端子及びゲート端子には直流電源電圧VDD2が入力され、ソース端子にはトランジスタT9のドレイン端子が接続される。なお、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線から変調信号MOD2が出力される。

【0120】

また、トランジスタT9のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧が入力される。

【0121】

変調信号MOD1の電圧が、トランジスタT9の閾値電圧(トランジスタT9がオン状態となるための電圧)より低く、かつ、基準電圧VSS付近の電圧である場合(変調信号MOD1の電圧が低電位状態である場合)、トランジスタT9はオフ状態であり、トランジスタT8のゲート端子に直流電源電圧VDD2が入力されるため、トランジスタT8はオン状態である。

【0122】

この場合、トランジスタT8のドレイン端子とソース端子との間は、トランジスタT9のドレイン端子とソース端子との間よりも電流が流れやすい。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0123】

一方、変調信号MOD1の電圧がトランジスタT9の閾値電圧以上である場合、トランジスタT9はオン状態となる。閾値電圧は直流電源電圧VDD2よりも低い電圧である。ここで、変調信号MOD1の電圧が直流電源電圧VDD2とほぼ同じ電圧となる高電位状態となれば、トランジスタT9のドレイン端子とソース端子との間は、トランジスタT8のドレイン端子とソース端子との間よりも電流が流れやすい。このため、変調信号MOD1の電圧が高電位状態となれば、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0124】

変調信号MOD1の電圧が低電位状態である場合、変調信号MOD2は直流電源電圧VDD2に近い電圧となり、変調信号MOD1の電圧が高電位状態である場合、変調信号MOD2は基準電圧VSSに近い電圧となる。これによって、図8に示す送信用増幅回路AMP1は、変調信号MOD1の電圧を増幅させ、広い電圧範囲(基準電圧VSSから直流電源電圧VDDの範囲)で変調信号MOD2を出力できる。

【0125】

図8に示す送信用増幅回路AMP1をICチップIC1に搭載した場合、変調信号MOD1の電圧が高電位状態となれば、基準電圧VSS付近の電圧の変調信号MOD2が出力され、変調信号MOD1が低電位状態であれば、直流電源電圧VDD2付近の電圧の変調信号MOD2が出力される。このように、図8に示す送信用増幅回路AMP1から出力される変調信号MOD2は、入力信号である変調信号MOD1の反転信号となる。

【0126】

図9は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0127】

図9に示す送信用増幅回路AMP1は、トランジスタT8、T9、T10、及びT11を備える。なお、トランジスタT8及びT9の動作は、図8に示す送信用増幅回路AMP1のトランジスタT8及びT9の動作と同じである。

【0128】

トランジスタT8のドレイン端子及びゲート端子には直流電源電圧VDD2が入力され、ソース端子はトランジスタT9のドレイン端子に接続される。また、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線は、トランジスタT10のゲート端子に接続される。

【0129】

トランジスタT9のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧VSSが入力される。トランジスタT10のドレイン端子には直流電源電圧VDD2が入力され、ソース端子はトランジスタT11のドレイン端子に接続される。トランジスタT10のソース端子とトランジスタT11のドレイン端子との接続線から変調信号MOD2が出力される。トランジスタT11のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧VSSが入力される。

【0130】

トランジスタT8及びT9の詳細な動作は図8と同じであるので説明を省略する。変調信号MOD1が低電位状態である場合、トランジスタT10のゲート端子には直流電源電圧VDD2とほぼ同じ電圧が入力され、変調信号MOD1が高電位状態である場合、トランジスタT10のゲート端子には基準電圧VSSとほぼ同じ電圧が入力される。

【0131】

変調信号MOD1が低電位状態である場合のトランジスタT10及びT11の動作について説明する。

【0132】

この場合、トランジスタT11のゲート端子には低電位状態である変調信号MOD1が入力されるため、トランジスタT11はオフ状態となる。トランジスタT10のドレイン端子とソース端子との間は、トランジスタT11のドレイン端子とソース端子との間より電流が流れやすくなる。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0133】

次に、変調信号MOD1が高電位状態である場合のトランジスタT10及びT11の動作について説明する。

【0134】

この場合、トランジスタT11のゲート端子には高電位状態である変調信号MOD1が入力されるため、トランジスタT11はオン状態となる。一方、トランジスタT10のゲート端子には基準電圧VSSとほぼ同じ電圧が入力されるため、トランジスタT10はオフ状態となるか、又は、トランジスタT10のドレイン端子とソース端子との間は、トランジスタT11のドレイン端子とソース端子との間よりも電流が流れにくい状態となる。このため、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0135】

なお、図9に示す送信用増幅回路AMP1は、図8に示す送信用増幅回路AMP1と同じく、変調信号MOD1に対して反転信号となる変調信号MOD2を出力する。具体的には、図9に示す送信用増幅回路AMP1は、変調信号MOD1の電圧が高電位状態となれば、基準電圧VSS付近の電圧の変調信号MOD2が出力され、変調信号MOD1が低電位状態であれば、直流電源電圧VDD2付近の電圧の変調信号MOD2が出力される。

【0136】

しかし、図9に示す送信用増幅回路AMP1は、トランジスタT8及びT9によって増幅した電圧をトランジスタT10のゲート端子に入力し、トランジスタT10及びT11によって当該電圧を増幅しているので、図8に示す送信用増幅回路AMP1よりも、変調信号MOD2の電圧の最大電圧を直流電源電圧VDD2に近づけることができ、変調信号MOD2の電圧の最小電圧を基準電圧VSSに近づけることができる。

【0137】

図10は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0138】

図10に示す送信用増幅回路AMP1は、トランジスタT8、T9、T12、及びT13を備える。なお、トランジスタT8及びT9は、図8及び図9に示す送信用増幅回路AMP1のトランジスタT8及びT9と同じである。

【0139】

図10に示す送信用増幅回路AMP1は、トランジスタT12のゲート端子に直流電源電圧VDD2が入力される点、及び、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線がトランジスタT13のゲート端子に接続される点で、図9に示す送信用増幅回路AMP1と異なる。

【0140】

これによって、図10に示す送信用増幅回路AMP1は、変調信号MOD1と同相の変調信号MOD2を出力できる。

【0141】

具体的には、変調信号MOD1が低電位状態である場合、トランジスタT13のゲート端子には直流電源電圧VDD2とほぼ同じ電圧が入力されるため、トランジスタT13はオン状態となる。一方、トランジスタT12のゲート端子には直流電源電圧VDD2が入力される。このため、トランジスタT12のドレイン端子とソース端子との間は、トランジスタT13のドレイン端子とソース端子との間よりも電流が流れにくくなる。したがって、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0142】

また、変調信号MOD1が高電位状態である場合、トランジスタT13のゲート端子には基準電圧VSSとほぼ同じ電圧が入力されるため、トランジスタT13はオフ状態となる。トランジスタT12のドレイン端子とソース端子との間は、トランジスタT13のドレイン端子とソース端子との間より電流が流れやすくなる。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0143】

このようにすると、変調信号MOD1は、トランジスタT8及びT9によって一度反転増幅された後、トランジスタT12及びT13によって再度反転増幅されるので、変調信号MOD2は変調信号MOD1と同相となる。

【0144】

また、図10に示す送信用増幅回路AMP1が出力する変調信号MOD2の振幅は、図9に示す送信用増幅回路AMP1が出力する変調信号MOD2の振幅以上となる。

【0145】

図11は、本発明の第1実施形態のICチップIC1における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0146】

図11に示す直流電源電圧(VDD1)の振幅の変動を、図18及び図20に示す直流電源電圧(VDD1)の振幅の変動よりも低減でき、かつ、アンテナ端子間電圧(LA−LB)の振幅の変動を、図18及び図20に示すアンテナ端子間電圧(LA−LB)の振幅の変動よりも増大させることができる。

【0147】

これは、実施形態のICチップIC1は、整流回路R1によって論理回路L1を動作させるための直流電源電圧VDD1を生成し、さらに、整流回路R2によって、負荷変調回路M1が変動させる直流電源電圧VDD2を生成することによる。

【0148】

また、整流回路R1及びR2に接続される平滑化コンデンサC1及びC2によって高周波を除去しているので、図11に示すように、変調信号電圧(MOD1)に高周波信号が伝搬していない。

【0149】

これによって、論理回路L1の動作するための電圧となる直流電源電圧(VDD1)の振幅の低減を防止しつつ、アンテナ端子間電圧(LA−LB)の振幅を増大させることができるので、通信可能距離を低減させずにICチップIC1の動作を安定させることができる。また、論理回路L1の動作するための電圧となる直流電源電圧(VDD1)に高周波信号が伝搬しないので、ICチップIC1の動作を安定させることができる。

【0150】

(第2実施形態)

次に、本発明の第2実施形態を図12を用いて説明する。

【0151】

図12は、本発明の第2実施形態のICチップIC1の回路構成の説明図である。

【0152】

図12に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0153】

リーダ・ライタ装置RW1から送信された信号を復調した復調信号を論理回路L1に入力するために、直流電源電圧VDD2が論理回路L1に入力される点で、図12に示すICチップIC1は第1実施形態のICチップIC1と異なる。

【0154】

リーダ・ライタ装置RW1から送信された信号は、整流回路R2及び平滑化コンデンサC2によって復調される。この復調された電圧(VDD2)が復調信号として論理回路L1に入力される。

【0155】

論理回路L1に復調信号が入力された場合、論理回路L1は、入力された復調信号が示す命令を検出し、検出した命令に対応する処理を実行する。

【0156】

ここで、第1実施形態の図2に示すICチップIC1の回路構成では、論理回路L1に復調信号を入力しようとすると、論理回路L1は、直流電源電圧VDD1から当該復調信号を検出する構成にせざるを得ない。

【0157】

論理回路L1に入力される直流電源電圧VDD1は、レギュレータ回路G1によって、所定値以上の電圧が除去された電圧である。このため、論理回路L1は、復調信号が示す命令を正確に検出できない。

【0158】

このため、本発明の第2実施形態では、論理回路L1を起動させるための直流電源電圧VDD1とは別に、論理回路L1に復調信号を入力するための直流電源電圧VDD2を論理回路L1に入力するようにした。

【0159】

直流電源電圧VDD2はレギュレータ回路G1による影響を受けないので、論理回路L1は、復調信号が示す命令を正確に検出できる。

【0160】

なお、整流回路R2及び平滑化容量C2がリーダ・ライタ装置RW1から送信された信号を復調する動作は負荷変調回路M1の動作に影響を与えず、また、負荷変調回路M1の動作は、整流回路R2及び平滑化容量C2の復調動作に影響を与えない。

【0161】

(第3実施形態)

次に、本発明の第3実施形態を図13及び図14を用いて説明する。

【0162】

図13は、本発明の第3実施形態のICチップIC1の回路構成の説明図である。

【0163】

図13に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0164】

図13に示すICチップIC1は、図2に示す第1実施形態のICチップIC1の構成に加えて、論理回路L1から出力された変調信号MOD1と送信用増幅回路AMP1から出力された変調信号MOD2とを比較し、電圧の大きい方の変調信号を変調信号MOD3として負荷変調回路M1に入力する比較回路CMP1を備える。比較回路CMP1の詳細は、図14で詳細を説明する。なお、変調信号MOD2は、変調信号MOD1を送信用増幅回路AMP1が増幅した信号であり、変調信号MOD1と変調信号MOD2とは同相信号である。このため、本実施形態では、送信用増幅回路AMP1は、図10に示す送信用増幅回路AMP1が採用される。

【0165】

負荷変調回路M1は、比較回路CMP1から出力された変調信号MOD3に応じて、自身の消費電力を変動させることによって、ICチップIC1の消費電力を変動させ、アンテナ端子LA及びLB間の電圧を変動させる。

【0166】

負荷変調回路M1に変調信号M1及び変調信号M2のうち電圧が大きい方の変調信号が入力されるので、負荷変調回路M1に入力される変調信号MOD3の電圧が直流電源電圧VDD1以下となることを防止する。これによって、アンテナ端子間電圧(LA−LB)の振幅の変動が低下することを防止できる。

【0167】

本実施形態の効果について具体的に説明する。

【0168】

図2に示す第1実施形態のICチップIC1では、負荷変調回路M1に変調信号MOD2が入力される。図7に示す負荷変調回路M1に入力される変調信号MOD2が高電位状態である場合、トランジスタT2のドレイン端子とソース端子との間は電流が流れやすい状態となるため、負荷変調回路M1は、直流電源電圧VDD2を低下させる。このため、増幅用増進回路AMP1の増幅率が低下し、送信用増幅回路AMP1によって増幅される変調信号MOD2の電圧も、直流電源電圧VDD2の低下に伴って、低下してしまう。これによって、十分な変調信号MOD2の振幅を得られなくなる場合がある。

【0169】

これに対して、本実施形態のICチップIC1では、比較回路CMP1によって変調信号MOD1及び変調信号MOD2のうち電圧が大きい方の変調信号が負荷変調回路M1に入力されるので、直流電源電圧VDD2の低下に伴い送信用増幅回路AMP1から出力される変調信号MOD2が低下しても、負荷変調回路M1に入力される変調信号MOD1の電圧が変調信号MOD1の電圧以下になることを防止できる。これによって、送信用増幅回路M1に入力される変調信号MOD3の振幅を変調信号MOD1の振幅に担保することができ、変調信号MOD1の振幅以下の変調信号が送信用増幅回路M1に入力されることを防止でき、ICタグTG1の通信可能距離が低減することを防止できる。

【0170】

図14は、本発明の第3実施形態の比較回路CMP1に適用可能な回路の説明図である。

【0171】

比較回路CMP1は、トランジスタT14及びT15を備える。

【0172】

トランジスタT14のゲート端子及びドレイン端子には変調信号MOD1が入力され、トランジスタT15のゲート端子及びドレイン端子には変調信号MOD2が入力される。また、トランジスタT14のソース端子とトランジスタT15のソース端子とが接続される。トランジスタT14のソース端子とトランジスタT15のソース端子との接続線から変調信号MOD3が出力される。

【0173】

変調信号MOD1の電圧が変調信号MOD2の電圧よりも高い場合、トランジスタT14はオン状態となり、トランジスタT15はオフ状態となる。このため、トランジスタT14のドレイン端子とソース端子との間は、トランジスタT15のドレイン端子とソース端子との間より、電流が流れやすくなるので、変調信号MOD3には、変更信号MOD1に近い電圧が出力される。

【0174】

また、変調信号MOD2の電圧が変調信号MOD1の電圧よりも高い場合、トランジスタT15はオン状態となり、トランジスタT14はオフ状態となる。このため、トランジスタT15のドレイン端子とソース端子との間は、トランジスタT14のドレイン端子とソース端子との間より、電流が流れやすくなるので、変調信号MOD3には、変更信号MOD2に近い電圧が出力される。

【0175】

(第4実施形態)

本発明の第4実施形態を図15を用いて説明する。

【0176】

図15は、本発明の第4実施形態のICチップIC1の回路構成の説明図である。

【0177】

図15に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0178】

図15に示すICチップIC1は、整流回路R3及び平滑化コンデンサC3を備える点、並びに、送信用増幅回路AMP1に直流電源電圧VDD3が入力される点で、図2に示す第1実施形態のICチップIC1と異なる。

【0179】

アンテナ端子LA及びLBには、整流回路R1、R2及びR3が接続される。

【0180】

整流回路R3は、リーダ・ライタ装置R1からアンテナコイルA1が受信した高周波信号によってアンテナ端子LA及びLA間の電圧(交流電圧)を直流電源電圧VDD3に変換する回路である。整流回路R3は、整流回路R1及びR2と同じく、図3又は図4に示す整流回路を適用すればよい。

【0181】

なお、整流回路R3を構成するトランジスタは、図16に示すキャリア蓄積を用いたトランジスタである。

【0182】

送信用増幅回路VDD3は、整流回路R3から出力される直流電源電圧VDD3を用いて動作し、負荷直流回路M1に入力される直流電源電圧VDD2を共用しない。

【0183】

これによって、図7に示す負荷変調回路M1に入力される変調信号MOD2が高電位状態である場合に負荷変調回路M1が直流電源電圧VDD2を低下させても、送信用増幅回路AMP1は、変調信号MOD1を直流電源電圧VDD3から基準電圧VSSの範囲で増幅できる。これによって、送信用増幅回路AMP1は、振幅の大きい変調信号MOD2を負荷変調回路M1に入力できる。

【0184】

したがって、本実施形態によれば、アンテナ端子間電圧(LA−LB)の振幅の変動が低下することを防止でき、ICタグTG1の通信可能距離を大きくすることができる。

【0185】

以上、本発明者によりなされた発明を実施形態に基づき具体的に説明したが、本発明は上述した実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0186】

本願発明は、非接触電子装置、所謂、ICタグ等に適用可能である。

【符号の説明】

【0187】

A1及びA2…コイルアンテナ

AMP1…送信用増幅回路

C1〜4…平滑化コンデンサ

CL1…チャネル層

IL1…絶縁体層

ML1及びML2…金属層

MOD1〜MOD3…変調信号

LA及びLB…アンテナ端子

R1〜R3…整流回路

RW1…リーダ・ライタ装置

SL1…基板層

T1〜15…トランジスタ

TG1…ICタグ

【技術分野】

【0001】

本発明は、トランジスタによって構成された非接触電子装置に関し、特にキャリア蓄積を用いたトランジスタによって構成された非接触電子装置に関する。

【背景技術】

【0002】

アンテナ及び半導体集積回路装置を搭載した非接触電子装置(所謂ICタグ)は、無線通信による個体識別を可能とし、識別対象物の生産・管理等に利用されている。

【0003】

ICタグの機能について説明する。

【0004】

ICタグは、リーダ・ライタ装置との間で情報を交換するものであって、自身が保持しているデータをリーダ・ライタ装置に送信する機能、及び、リーダ・ライタ装置から送信されたデータを保持する機能等を備える。

【0005】

具体的には、ICタグは、リーダ・ライタ装置から供給されたキャリア信号をアンテナを介して受信し、受信したキャリア信号から直流電源電圧を生成し、生成した直流電源電圧をICタグに搭載された半導体集積回路装置に供給する。また、ICタグは、半導体集積回路装置内でキャリア信号に重畳したデータをリーダ・ライタ装置に送信する。

【0006】

ICタグが、データをリーダ・ライタ装置に送信する場合、半導体集積回路装置内に搭載された負荷変調回路を用いる。

【0007】

負荷変調回路は、半導体集積回路装置の消費電力を変動させる回路である。負荷変調回路によって、アンテナを構成するアンテナ端子の間の電圧が変動し、この変動が電磁場を介しリーダ・ライタ装置に伝送されることによって、リーダ・ライタ装置はデータを検出する。

【0008】

ICタグに搭載される半導体集積回路装置は、シリコンを用いたトランジスタ(MOSFET(Metal Oxide Semiconductor Field Effect Transistor))を主に用いて製造される。これによって、ICタグの大量生産によるコスト低減を実現でき、ICタグの普及の一助となっている。

【0009】

近年、従来のシリコンを用いたトランジスタでは達成困難なICタグの新規機能を実現するため、トランジスタに用いる半導体材料及びトランジスタ構造が提案されている。

【0010】

新規な半導体材料によって構成されたトランジスタ又は新規な構造のトランジスタを搭載したICタグであっても、既存のICタグと同じ通信形態及び通信範囲が求められる。

【0011】

近年、ICタグに用いられるようになったキャリア蓄積を用いたトランジスタについて、図16を用いて説明する。

【0012】

図16は、キャリア蓄積を用いたトランジスタを説明するための断面図である。

【0013】

キャリア蓄積を用いたトランジスタは、半導体層(チャネル層CL1)が酸化物半導体である薄膜トランジスタ(TFT)であり、具体的には、第一金属層ML1、チャネル層CL1、絶縁体層IL1、第二金属層ML2、及び基板層SL1から構成される。

【0014】

第一金属層ML1は、モリブデンで構成され、ドレイン電極及びソース電極を形成する。チャネル層CL1は、金属酸化物を主に含む半導体(酸化物)で構成される。酸化物半導体は、アモルファスインジウム亜鉛酸化物(a−IGZO)及び亜鉛スズ酸化物(ZTO)等である。絶縁体層IL1は、シリカ(SiO2)で構成される。第二金属層ML2は、第一金属層ML1と同じく、モリブデンで構成される。また、第二金属層ML2は、ゲート電極を形成する。基板層SL1は石英で構成される。

【0015】

キャリア蓄積を用いたトランジスタの動作について簡単に説明する。

【0016】

ゲート電極とソース電極との間に電圧が印加された場合、ゲート電極とソース電極との間の静電容量によってチャネル層CL1にキャリアが蓄積する。この状態で、ドレイン電極とソース電極との間に電圧が印加された場合、キャリア層CL1に蓄積されるキャリアが増大することによってドレイン電極とソース電極との間の導電率が増大する。これによって、ドレイン電極からソース電極へ電流が流れる。

【0017】

なお、通常のトランジスタ(例えば、MOSFET)は、ドレイン電極とソース電極との間の導電率を増大させるために、反転層を用いる。キャリア蓄積を用いたトランジスタは、上述したように、ドレイン電極とソース電極との間の導電率を増大させるために、チャネル層CL1(蓄積層)を用いる。このため、通常のトランジスタのゲート電極とソース電極との間の静電容量は数フェムトファラッド以下であるのに対して、キャリア蓄積を用いたトランジスタのゲート電極とソース電極との間の静電容量は数十〜数百フェムトファラッド程度となり、キャリア蓄積を用いたトランジスタのゲート電極とソース電極との間の静電容量は、通常のトランジスタのゲート電極とソース電極との間の静電容量よりも大きくなる。

【0018】

図17は、ICタグに搭載される従来の半導体集積回路装置の第1の回路構成の説明図である。

【0019】

半導体集積回路装置は、アンテナ端子LA及びLB、整流回路T1、負荷変調回路T2、並びに論理回路L1を備える。

【0020】

アンテナ端子LA及びLBは、ICタグに搭載されるアンテナに接続される。

【0021】

整流回路T1は、アンテナを介して受信した電力を直流電力に変換する。整流回路T1は、平滑化コンデンサC1に接続される。平滑化コンデンサC1は、整流回路T1によって変換された直流電力を平滑化する。

【0022】

論理回路L1は、整流回路T1が出力する直流電力で動作し、各種処理を実行する。

【0023】

負荷変調回路T2は、論理回路L1からの変調信号をアンテナから出力するために、半導体集積回路装置の消費電力を変動させることによって、アンテナ端子LA及びLB間の電圧を変動させる。具体的には、負荷変調回路T2は、半導体集積回路装置の消費電力を増大させることによって、アンテナ端子LA及びLB間の電圧を低下させ、半導体集積回路装置の消費電力を低下させるころによって、アンテナ端子LA及びLB間の電圧を増大させる。

【0024】

図18は、図17に示す半導体集積回路装置における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0025】

図17で説明したように、負荷変調回路T2は、半導体集積回路装置における消費電力を増大させることによって、アンテナ端子LA及びLB間の電圧(LA−LB)を低下させることができる。しかし、これによって、整流回路T1が出力する直流電力の電圧(VDD1)も低下してしまう。

【0026】

整流回路T1が出力する直流電力の電圧が低下すると、直流電力で動作する論理回路L1は、不具合が発生する。この不具合は、例えば、初期化していないにもかかわらず初期化信号を発行してしまう不具合、動作速度が不安定になる不具合、クロック信号が不安定になる不具合等がある。

【0027】

このため、負荷変調回路T2による直流電力の電圧(VDD1)の低下をできるだけ防止することが望まれる。

【0028】

しかしながら、ICタグとリーダ・ライタ装置との間の距離が長ければ長いほど、アンテナ端子間電圧の振幅を大きくしなければならず、負荷変調回路T2は、半導体集積回路装置における消費電力の変動を増大させなければならない。このため、負荷変調回路T2が直流電力の電圧(VDD1)を低下させてしまうことを妨げることができない。

【0029】

以上より、図17に示す半導体集積回路装置は、負荷変調回路T2が直流電力の電圧(VDD1)の変動を増大させると、論理回路L1の動作電圧も変動させてしまう点が欠点である。

【0030】

そこで、負荷変調回路T2をアンテナ端子LA及びLBに直接接続する図19に示すような半導体集積回路装置が用いられる。

【0031】

図19は、ICタグに搭載される従来の半導体集積回路装置の第2の回路構成の説明図である。

【0032】

上述したように、図19に示す半導体集積回路装置の負荷変調回路T2がアンテナ端子LA及びLBに直接接続される。

【0033】

ここで、負荷変調回路T2が図16に示すキャリア蓄積を用いたトランジスタである場合、キャリア蓄積を用いたトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量を介して、アンテナ端子が受信した高周波信号が論理回路L1に伝達されてしまう場合がある。これは、図16で説明したように、キャリア蓄積を用いたトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量が、通常のトランジスタのドレイン電極とゲート電極との間の静電容量、及びソース電極とゲート電極との間の静電容量よりも例えば10倍〜100倍以上大きいことに起因する。

【0034】

図20は、図19に示す半導体集積回路装置における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0035】

図19に示す半導体集積回路装置では、図20に示すように、論理回路L1が出力する変調信号電圧(MOD1)に高周波信号が伝搬してしまう。

【0036】

高周波信号が論理回路L1に伝達すると、論理回路L1の動作が不安定となる問題がある。

【0037】

特許文献1及び2には、アンテナが受信した電力から論理回路L1用の電源電圧を生成する整流回路と、アンテナが受信した電力から負荷変調回路用の電源電圧を生成する整流回路とを備える半導体集積回路装置、つまり、図19に示す半導体集積回路装置に類似する半導体集積回路装置が開示されている。

【0038】

また、特許文献3には、アンテナ端子間に接続されるコンデンサの静電容量が高周波信号の伝達を抑制することが開示されている。

【先行技術文献】

【特許文献】

【0039】

【特許文献1】国際公開第2004/064346

【特許文献2】特開平10−322250号公報

【特許文献3】特開2005−267643号公報

【発明の概要】

【発明が解決しようとする課題】

【0040】

特許文献1及び2には開示された技術では、送受信回路と電源回路を分離することで、送受信特性を向上させる技術が開示されていたが、図19及び図20で説明したように、論理回路に高周波信号が伝達することを防ぐための技術ではなく、特許文献3に示されているように十分な変調度が得られない場合がある。

【0041】

また、特許文献3に開示された開示された技術では、論理回路への高周波信号の伝達を防止することはできない。

【0042】

本発明は、キャリア蓄積を用いたトランジスタによって構成された非接触電子装置を、通信距離及び通信状況によらず安定して動作させ、かつ当該非接触電子装置の通信可能距離を増大させることを目的とする。

【課題を解決するための手段】

【0043】

本発明の代表的な一例を示せば、キャリア蓄積を利用したトランジスタによって構成される非接触電子装置であって、第一の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第一のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、第二の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第二のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、前記第一の平滑化コンデンサによって前記第一の直流電源電圧が平滑化された電圧を用いて動作する論理回路と、前記論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記変調信号増幅回路が出力する第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする。

【発明の効果】

【0044】

本願において開示される発明のうち代表的なものによって得られる効果を簡潔に説明すれば、下記の通りである。すなわち、キャリア蓄積を用いたトランジスタによって構成された非接触電子装置を、通信距離及び通信状況によらず安定して動作させ、かつ、当該非接触電子装置の通信可能距離を増大させることができる。

【図面の簡単な説明】

【0045】

【図1】本発明の第1実施形態のICタグシステムの説明図である。

【図2】本発明の第1実施形態のICチップの回路構成の説明図である。

【図3】本発明の第1実施形態の整流回路に適用可能な整流回路の説明図である。

【図4】本発明の第1実施形態の整流回路に適用可能な整流回路の説明図である。

【図5】本発明の第1実施形態のレギュレータ回路に適用可能な回路の説明図である。

【図6】本発明の第1実施形態のレギュレータ回路に適用可能な回路の説明図である。

【図7】本発明の第1実施形態の負荷変調回路に適用可能な回路の説明図である。

【図8】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図9】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図10】本発明の第1実施形態の送信用増幅回路に適用可能な回路の説明図である。

【図11】本発明の第1実施形態のICチップにおける直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【図12】本発明の第2実施形態のICチップの回路構成の説明図である。

【図13】本発明の第3実施形態のICチップの回路構成の説明図である。

【図14】本発明の第3実施形態の比較回路に適用可能な回路の説明図である。

【図15】本発明の第4実施形態のICチップの回路構成の説明図である。

【図16】キャリア蓄積を用いたトランジスタを説明するための断面図である。

【図17】ICタグに搭載される従来の半導体集積回路装置の第1の回路構成の説明図である。

【図18】第1の回路構成の半導体集積回路装置における直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【図19】ICタグに搭載される従来の半導体集積回路装置の第2の回路構成の説明図である。

【図20】第2の回路構成半導体集積回路装置における直流電源電圧、変調信号電圧及びアンテナ端子間電圧の数値解析結果の説明図である。

【発明を実施するための形態】

【0046】

(第1実施形態)

以下、本発明の第1実施形態を図1〜図11を用いて説明する。

【0047】

図1は、本発明の第1実施形態のICタグシステムの説明図である。

【0048】

ICタグシステムは、リーダ・ライタ装置RW1及びICタグTG1を備える。

【0049】

ICタグTG1は、リーダ・ライタ装置RW1からデータを受信し、自身に格納されたデータをリーダ・ライタ装置RW1に送信する。

【0050】

リーダ・ライタ装置RW1は、ICタグTG1からデータを受信し(データの読み出し)、また、ICタグTG1にデータを送信する(データの書き込み)。なお、本実施形態では、リーダ・ライタ装置RW1は、データの読み込み機能及びデータの書き込み機能を備えるものとして説明するが、データの書き込み機能は必須の構成ではない。

【0051】

ICタグTG1は、アンテナコイルA1、共振コンデンサC4、及びICチップIC1を備える。

【0052】

リーダ・ライタ装置RW1は、アンテナコイルA2を備え、アンテナコイルA2を介して高周波信号を放射する。リーダ・ライタ装置RW1とICタグTG1とは磁界結合しているため、アンテナコイルA1から放射された高周波信号は、アンテナコイルA1及び共振コンデンサC4を介してICチップIC1に入力される。なお、磁界結合とはアンテナコイルA1及びA2が発生させる磁界によって、アンテナコイルA1及びA2が結合している状態である。

【0053】

ICタグTG1への高周波信号の入力について説明する。

【0054】

リーダ・ライタ装置RW1は、アンテナコイルA2に印加される電圧を変動させることによって、アンテナコイルA2が発生させる磁界を変動させる。また、磁界の変動によってICタグTG1のアンテナコイルA1の電圧として観測される高周波信号が発生するため、ICタグTG1は送信信号を検出できる。このようにして、高周波信号がアンテナコイルA1からアンテナコイルA2に入力される。

【0055】

ICチップIC1は、入力された高周波信号から自身を起動させるための電源電圧を生成し、必要な場合には入力された高周波信号から命令を抽出する。また、ICチップIC1は、リーダ・ライタ装置RW1からの命令に対する応答信号を生成し、生成した応答信号をアンテナコイルA2を介してリーダ・ライタ装置RW1に送信する。

【0056】

ICチップIC1の応答信号をリーダ・ライタ装置RW1に送信する機能について説明する。

【0057】

ICチップIC1は、応答信号をリーダ・ライタ装置RW1に送信する場合、自身の消費電力を変動させることによって、アンテナコイルA1の端子間(LA―LB)の電圧を変動させる。上述したように、アンテナコイルA1及びA2が磁界結合しているため、アンテナコイルA1の端子間の電圧の変動は、アンテナコイルA2の端子間の電圧の変動としてリーダ・ライタ装置RW1によって検出される。このようにして、ICチップIC1は、応答信号をリーダ・ライタ装置RW1に送信できる。

【0058】

なお、図1では、リーダ・ライタ装置RW1とICタグTG1との間の磁界結合を利用して、ICチップIC1の電源電圧を生成し、リーダ・ライタ装置RW1とICタグTG1との間でデータを通信する磁界結合方式を用いたが、マイクロ波方式を用いてもよい。

【0059】

マイクロ波方式は、リーダ・ライタ装置RW1が電波を放射し、アンテナによって当該高周波信号を受信することでICチップIC1が電源電圧を生成し、電波を利用してリーダ・ライタ装置RW1とICタグTG1との間でデータを通信する方式である。

【0060】

磁界結合方式又はマイクロ波方式を用いるかは、リーダ・ライタ装置RW1とICタグTC1との無線通信周波数に依存し、一般に無線通信周波数が125kHz〜135kHz、及び13.56MHzである場合には磁界結合方式を用い、無線通信周波数が2.45GHzである場合にはマイクロ波方式を用いる。

【0061】

図2は、本発明の第1実施形態のICチップIC1の回路構成の説明図である。

【0062】

ICチップIC1は、アンテナ端子LA及びLB、整流回路R1、平滑化コンデンサC1、レギュレータ回路G1、論理回路L1、送信用増幅回路(変調信号(MOD1)増幅回路)AMP1、負荷変調回路MOD2、平滑化コンデンサC2、及び整流回路R2を備える。

【0063】

アンテナ端子LA及びLBには、図1に示すアンテナコイルA1及び共振コンデンサC4が接続される。また、アンテナ端子LA及びLBには、整流回路R1及びR2が接続される。

【0064】

整流回路R1及びR2は、リーダ・ライタ装置R1からアンテナコイルA1が受信した高周波信号によってアンテナ端子LA及びLA間の電圧(交流電圧)を直流電源電圧に変換する回路であり、整流回路R1及びR2の詳細は、図3及び図4で詳細を説明する。

【0065】

本発明は、アンテナ端子LA及びLBに接続される整流回路R1及びR2は、図16に示すキャリア蓄積を用いるトランジスタによって構成されることを前提とする。なお、本発明のICチップIC1に搭載されるすべてのトランジスタが図16に示すキャリア蓄積を用いるトランジスタによって構成されてもよい。

【0066】

整流回路R1から直流電源電圧に変換された直流電源電圧VDD1が出力され、整流回路R2から直流電源電圧に変換された直流電源電圧VDD2が出力される。なお、基準電圧は電圧VSSとする。直流電源電圧VDD1は論理回路L1の動作に用いられ、直流電源電圧VDD2は送信用増幅回路AMP1及び負荷変調回路M1の動作に用いられる。

【0067】

整流回路R1の直流電源電圧VDD1の出力先には、平滑化コンデンサC1、レギュレータ回路G1、及び論理回路L1が接続される。

【0068】

平滑化コンデンサC1は、直流電源電圧VDD1を平滑化し、直流電源電圧VDD1の高周波ノイズを除去する。

【0069】

レギュレータ回路G1は、論理回路L1に過大な電圧及び電流が印加されることを防止する。また、レギュレータ回路G1は、高周波信号の振幅が大きい場合(例えば、1μW〜10μW)であっても、安定した電圧を生成することによって、論理回路L1の動作を安定させる。なお、レギュレータ回路G1の詳細は、図5及び図6で詳細を説明する。

【0070】

論理回路L1は、直流電源電圧VDD1によって動作し、高周波信号に重畳された命令に対応する処理を実行する。また、論理回路L1は、IDデータ等を保持し、当該IDデータ等に基づく演算処理を実行する。さらに、論理回路L1は、リーダ・ライタ装置RW1に送信する送信信号等を生成する。

【0071】

整流回路R2の直流電源電圧回路VDD2の出力先には、平滑化コンデンサC2、負荷変調回路M1、及び送信用増幅回路AMP1が接続される。

【0072】

平滑化コンデンサC2は、平滑化コンデンサC1と同じく、直流電源電圧VDD2を平滑化し、直流電源電圧VDD2の高周波ノイズを除去する。

【0073】

負荷変調回路M1は、変調信号MOD2に応じて、自身の消費電力を変動させることによって、ICチップIC1の消費電力を変動させ、アンテナ端子LA及びLB間の電圧を変動させ、変調信号MOD2をリーダ・ライタ装置RW1に送信する。換言すれば、負荷変調回路M1は、変調信号MOD2に応じて、自身の消費電力を変動させ、整流回路R2が出力する直流電源電圧VDD2を変動させることによって、アンテナ端子LA及びLB間の電圧を変動させる。なお、負荷変調回路M1の詳細は、図7で説明する。

【0074】

送信用増幅回路AMP1は、論理回路L1から出力された送信信号である変調信号MOD1を増幅した変調信号MOD2を負荷変調回路M1に入力する。なお、送信用増幅回路AMP1の詳細は、図8〜図10で説明する。

【0075】

以上のように、本実施形態のICチップIC1は、整流回路R1によって論理回路L1を動作させるための直流電源電圧VDD1を生成し、さらに、整流回路R2によって、負荷変調回路M1が変動させる直流電源電圧VDD2を生成する。このため、負荷変調回路M1が直流電源電圧VDD2を低減させても、直流電源電圧VDD1には影響ないので、論理回路L1への電源電圧を安定させつつ、変調信号MOD2の振幅を大きくすることができる。また、整流回路R1及びR2のトランジスタに図16に示すキャリア蓄積を用いたトランジスタである薄膜トランジスタを採用しても、整流回路R1及びR2に接続される平滑化コンデンサC1及びC2によって高周波が論理回路L1に入力することを防止できる。

【0076】

また、論理回路L1から出力される変調信号MOD1の最大電圧は、論理回路L1及びレギュレーション回路G1によって直流電源電圧VDD1よりも低下する。このため、総信用増幅回路AMP1によって、この変調信号MOD1の電圧を直流電源電圧VDD2まで増幅させる。これによって、変調信号MOD2の振幅を増幅させることができ、ICタグTG1の通信可能距離を大きくすることができる。

【0077】

図3は、本発明の第1実施形態の整流回路R1及びR2に適用可能な整流回路の説明図である。

【0078】

図3に示す整流回路は、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合の電圧のみを出力する半波整流回路である。

【0079】

図3に示す整流回路はトランジスタT1を備える。トランジスタT1のゲート電極及びドレイン端子はアンテナ端子LAに接続され、ソース電極は直流電源電圧VDD4の出力先となる。アンテナ端子LBはトランジスタT1には接続されず、アンテナ端子LBに印加される電圧は基準電圧VSSとなる。

【0080】

トランジスタT1は、ドレイン端子からソース電極へ電流が流れる電圧(アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合の電圧)のみを出力する。

【0081】

図3に示す半波整流回路を用いた場合、図4に示す全波整流回路を用いた場合よりも整流回路に使用するトランジスタ数を低減できるので、ICチップIC1の製造コストを低減できる。

【0082】

なお、図3に示す半波整流回路を整流回路R1及びR2に適用する場合、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性よりも、大きな電流が流れるように設計することが好適である。しかし、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性と、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性とを同じにしてもよいし、整流回路R1に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタT1のドレイン端子とソース端子との間の電流特性よりも、小さな電流が流れるように設計されてもよい。

【0083】

図4は、本発明の第1実施形態の整流回路R1及びR2に適用可能な整流回路の説明図である。

【0084】

図4に示す整流回路は、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも大きい場合には、アンテナ端子LAがトランジスタT5を介してVDD4端子と接続され、アンテナ端子LBがトランジスタT4を介して基準電圧VSS端子と接続され、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧よりも小さい場合には、アンテナ端子LAがトランジスタT3を介して基準電圧VSS端子と接続され、アンテナ端子LBがトランジスタT6を介して電圧VDD4端子と接続される。これによって、図4に示す整流回路は、すべてのサイクルの電圧を直流電源電圧として出力する全波整流回路である。

【0085】

図4に示す整流回路は、トランジスタT3、T4、T5、及びT6を備える。

【0086】

トランジスタT3のドレイン端子はアンテナ端子LAに接続され、ゲート端子はアンテナ端子LBに接続され、ソース端子からは基準電圧VSSが出力される。

【0087】

トランジスタT4のドレイン端子はアンテナ端子LBに接続され、ゲート端子はアンテナ端子LAに接続され、ソース端子からは基準電圧VSSが出力される。

【0088】

トランジスタT5のドレイン端子及びゲート端子はアンテナ端子LAに接続され、ソース端子からは直流電源電圧VDD4が出力される。

【0089】

トランジスタT6のドレイン端子及びゲート端子はアンテナ端子LBに接続され、ソース端子からは直流電源電圧VDD4が出力される。

【0090】

アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧より高い場合、トランジスタT3及びT6は、ドレイン端子からソース端子へはほとんど電流が流れないオフ状態となる。また、この場合、トランジスタT4及びT5は、ドレイン端子からソース端子へ電流が流れるオン状態となる。

【0091】

したがって、直流電源電圧VDD4はアンテナ端子LAに印加される電圧と近い電圧となり、基準電圧VSSはアンテナ端子LBに印加される電圧と近い電圧となる。

【0092】

一方、アンテナ端子LAに印加される電圧がアンテナ端子LBに印加される電圧より低い場合、トランジスタT4及びT5は、ドレイン端子からソース端子へはほとんど電流が流れないオフ状態となる。また、この場合、トランジスタT3及びT6は、ドレイン端子からソース端子へ電流が流れるオン状態となる。

【0093】

したがって、直流電源電圧VDD4はアンテナ端子LBに印加される電圧と近い電圧となり、基準電圧VSSはアンテナ端子LAに印加される電圧と近い電圧となる。

【0094】

このようにして、図4に示す整流回路は、アンテナ端子LA及びLBに印加される電圧の大小に関係なく、すべてのサイクルの電圧を直流電源電圧VDD4として出力できる。これによって、図4に示す全波整流回路を整流回路に適用した場合、図3に示す半波整流回路を整流回路に適用した場合よりも、使用するトランジスタ数は増大するが、電力変換効率が高くなる。

【0095】

なお、図4に示す全波整流回路を整流回路R1及びR2に適用する場合、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性よりも、大きな電流が流れるように設計することが好適である。しかし、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性と、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性とを同じにしてもよいし、整流回路R1に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性は、整流回路R2に搭載されるトランジスタのドレイン端子とソース端子との間の電流特性よりも、小さな電流が流れるように設計されてもよい。

【0096】

また、整流回路R1及びR2の一方に図4に示す全波整流回路を適用し、他方に図3に半波整流回路を適用してもよいし、整流回路R1及びR2の両方に図3に示す半波整流回路又は図4に示す全波整流回路を適用してもよい。

【0097】

図5は、本発明の第1実施形態のレギュレータ回路G1に適用可能な回路の説明図である。

【0098】

図5に示すレギュレータ回路G1は、所謂、シャントレギュレータと呼ばれる構成である。

【0099】

図5に示すレギュレータ回路では、直流電源電圧VDD1と基準電圧VSSとの間にトランジスタT7及び電源モニタ回路MON1が接続される。

【0100】

電源モニタ回路MON1には直流電源電圧VDD1が入力され、電源モニタ回路MON1は、直流電源電圧VDD1の増大に即して増大するREG信号をトランジスタT7のゲート端子に入力する。

【0101】

トランジスタは、ゲート端子に流れる電流が増大すると、ドレイン端子からソース端子に流れる電流も増大させるため、トランジスタT7は、REG信号の増大に伴って直流電源電圧VDD1と基準電圧VSSとの間に流れる電流を増大させ、ICチップIC1の消費電流を増大させる。これによって、トランジスタT7は、REG信号の増大に伴って、直流電源電圧VDD1と基準電圧VSSとの間の電圧を降下させることができる。

【0102】

このようにして、図5に示すレギュレータ回路G1は、直流電源電圧VDD1が過大となった場合には、当該過大な直流電源電圧VDD1を論理回路L1に入力することを防止できる。

【0103】

なお、電源モニタ回路MON1の詳細な説明は省略するが、電源モニタ回路MON1は、例えばトランジスタを用いて構成できる。

【0104】

図6は、本発明の第1実施形態のレギュレータ回路G1に適用可能な回路の説明図である。

【0105】

図6に示すレギュレータ回路G1は、所謂、クランプ回路である。

【0106】

図6に示すレギュレータ回路G1は、直流電源電圧VDD1と基準電圧VSSとの間にショットキーバリアダイオードD1を備える。ショットキーバリアダイオードD1のカソードに直流電源電圧VDD1が入力され、アノードに基準電圧VSSが入力される。

【0107】

ここで、ショットキーバリアダイオードD1は、降伏電圧がPN接合ダイオードよりも低く、カソードに印加される直流電源電圧VDD1が降伏電圧以上である場合、自身に流れる電流を増大させる。

【0108】

これによって、図6に示すレギュレータ回路G1は、直流電源電圧VDD1が降伏電圧以上である場合、直流電源電圧VDD1を降下させることができるので、過大な直流電源電圧VDD1を論理回路L1に入力することを防止できる。

【0109】

なお、図6に示すレギュレータ回路は、ショットキーバリアダイオードD1を用いたが、ショットキーバリアダイオードD1の代わりに定電圧ダイオードを用いてもよい。

【0110】

図7は、本発明の第1実施形態の負荷変調回路M1に適用可能な回路の説明図である。

【0111】

図7に示す負荷変調回路M1は、インピーダンス素子Z1、及びトランジスタT2を備える。

【0112】

具体的には、直流電源電圧VDDと基準電圧VSSとの間に、インピーダンス素子Z1を介してトランジスタT2が接続される。

【0113】

トランジスタT2のゲート端子には変調信号MOD2が入力され、トランジスタT2のドレイン端子には直流電源電圧VDDからインピーダンス素子Z1に印加される電圧を減じた電圧が入力され、トランジスタT2のソース端子には基準電圧VSSが入力される。

【0114】

トランジスタT2は、ゲート端子に入力される変調信号MOD2の電圧の増減に伴って、ドレイン端子からソース端子に流れる電流を増減させる。これによって、トランジスタT2は、ICチップIC1の消費電力を増減させ、変調信号MOD2の電圧の増減に伴ってアンテナ端子LAとLBとの間の電圧を変動させることができる。

【0115】

なお、インピーダンス素子Z1は、インピーダンスを有する素子であればよく、例えば、抵抗及びコンデンサであればよい。また、インピーダンス素子Z1はインピーダンスが「0」であってもよい。すなわち、トランジスタT2のドレイン端子に直流電源電圧VDDが直接入力されてもよい。

【0116】

また、負荷変調回路M1の消費電力は、ICチップIC1の消費電力を鑑みて、トランジスタT2のドレイン端子とソース端子との間電流特性及びインピーダンス素子Z1のインピーダンスを調整することによって調整できる。

【0117】

図8は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0118】

図8に示す送信用増幅回路AMP1は、トランジスタT8及びT9を備える。

【0119】

トランジスタT8のドレイン端子及びゲート端子には直流電源電圧VDD2が入力され、ソース端子にはトランジスタT9のドレイン端子が接続される。なお、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線から変調信号MOD2が出力される。

【0120】

また、トランジスタT9のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧が入力される。

【0121】

変調信号MOD1の電圧が、トランジスタT9の閾値電圧(トランジスタT9がオン状態となるための電圧)より低く、かつ、基準電圧VSS付近の電圧である場合(変調信号MOD1の電圧が低電位状態である場合)、トランジスタT9はオフ状態であり、トランジスタT8のゲート端子に直流電源電圧VDD2が入力されるため、トランジスタT8はオン状態である。

【0122】

この場合、トランジスタT8のドレイン端子とソース端子との間は、トランジスタT9のドレイン端子とソース端子との間よりも電流が流れやすい。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0123】

一方、変調信号MOD1の電圧がトランジスタT9の閾値電圧以上である場合、トランジスタT9はオン状態となる。閾値電圧は直流電源電圧VDD2よりも低い電圧である。ここで、変調信号MOD1の電圧が直流電源電圧VDD2とほぼ同じ電圧となる高電位状態となれば、トランジスタT9のドレイン端子とソース端子との間は、トランジスタT8のドレイン端子とソース端子との間よりも電流が流れやすい。このため、変調信号MOD1の電圧が高電位状態となれば、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0124】

変調信号MOD1の電圧が低電位状態である場合、変調信号MOD2は直流電源電圧VDD2に近い電圧となり、変調信号MOD1の電圧が高電位状態である場合、変調信号MOD2は基準電圧VSSに近い電圧となる。これによって、図8に示す送信用増幅回路AMP1は、変調信号MOD1の電圧を増幅させ、広い電圧範囲(基準電圧VSSから直流電源電圧VDDの範囲)で変調信号MOD2を出力できる。

【0125】

図8に示す送信用増幅回路AMP1をICチップIC1に搭載した場合、変調信号MOD1の電圧が高電位状態となれば、基準電圧VSS付近の電圧の変調信号MOD2が出力され、変調信号MOD1が低電位状態であれば、直流電源電圧VDD2付近の電圧の変調信号MOD2が出力される。このように、図8に示す送信用増幅回路AMP1から出力される変調信号MOD2は、入力信号である変調信号MOD1の反転信号となる。

【0126】

図9は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0127】

図9に示す送信用増幅回路AMP1は、トランジスタT8、T9、T10、及びT11を備える。なお、トランジスタT8及びT9の動作は、図8に示す送信用増幅回路AMP1のトランジスタT8及びT9の動作と同じである。

【0128】

トランジスタT8のドレイン端子及びゲート端子には直流電源電圧VDD2が入力され、ソース端子はトランジスタT9のドレイン端子に接続される。また、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線は、トランジスタT10のゲート端子に接続される。

【0129】

トランジスタT9のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧VSSが入力される。トランジスタT10のドレイン端子には直流電源電圧VDD2が入力され、ソース端子はトランジスタT11のドレイン端子に接続される。トランジスタT10のソース端子とトランジスタT11のドレイン端子との接続線から変調信号MOD2が出力される。トランジスタT11のゲート端子には変調信号MOD1が入力され、ソース端子には基準電圧VSSが入力される。

【0130】

トランジスタT8及びT9の詳細な動作は図8と同じであるので説明を省略する。変調信号MOD1が低電位状態である場合、トランジスタT10のゲート端子には直流電源電圧VDD2とほぼ同じ電圧が入力され、変調信号MOD1が高電位状態である場合、トランジスタT10のゲート端子には基準電圧VSSとほぼ同じ電圧が入力される。

【0131】

変調信号MOD1が低電位状態である場合のトランジスタT10及びT11の動作について説明する。

【0132】

この場合、トランジスタT11のゲート端子には低電位状態である変調信号MOD1が入力されるため、トランジスタT11はオフ状態となる。トランジスタT10のドレイン端子とソース端子との間は、トランジスタT11のドレイン端子とソース端子との間より電流が流れやすくなる。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0133】

次に、変調信号MOD1が高電位状態である場合のトランジスタT10及びT11の動作について説明する。

【0134】

この場合、トランジスタT11のゲート端子には高電位状態である変調信号MOD1が入力されるため、トランジスタT11はオン状態となる。一方、トランジスタT10のゲート端子には基準電圧VSSとほぼ同じ電圧が入力されるため、トランジスタT10はオフ状態となるか、又は、トランジスタT10のドレイン端子とソース端子との間は、トランジスタT11のドレイン端子とソース端子との間よりも電流が流れにくい状態となる。このため、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0135】

なお、図9に示す送信用増幅回路AMP1は、図8に示す送信用増幅回路AMP1と同じく、変調信号MOD1に対して反転信号となる変調信号MOD2を出力する。具体的には、図9に示す送信用増幅回路AMP1は、変調信号MOD1の電圧が高電位状態となれば、基準電圧VSS付近の電圧の変調信号MOD2が出力され、変調信号MOD1が低電位状態であれば、直流電源電圧VDD2付近の電圧の変調信号MOD2が出力される。

【0136】

しかし、図9に示す送信用増幅回路AMP1は、トランジスタT8及びT9によって増幅した電圧をトランジスタT10のゲート端子に入力し、トランジスタT10及びT11によって当該電圧を増幅しているので、図8に示す送信用増幅回路AMP1よりも、変調信号MOD2の電圧の最大電圧を直流電源電圧VDD2に近づけることができ、変調信号MOD2の電圧の最小電圧を基準電圧VSSに近づけることができる。

【0137】

図10は、本発明の第1実施形態の送信用増幅回路AMP1に適用可能な回路の説明図である。

【0138】

図10に示す送信用増幅回路AMP1は、トランジスタT8、T9、T12、及びT13を備える。なお、トランジスタT8及びT9は、図8及び図9に示す送信用増幅回路AMP1のトランジスタT8及びT9と同じである。

【0139】

図10に示す送信用増幅回路AMP1は、トランジスタT12のゲート端子に直流電源電圧VDD2が入力される点、及び、トランジスタT8のソース端子とトランジスタT9のドレイン端子との接続線がトランジスタT13のゲート端子に接続される点で、図9に示す送信用増幅回路AMP1と異なる。

【0140】

これによって、図10に示す送信用増幅回路AMP1は、変調信号MOD1と同相の変調信号MOD2を出力できる。

【0141】

具体的には、変調信号MOD1が低電位状態である場合、トランジスタT13のゲート端子には直流電源電圧VDD2とほぼ同じ電圧が入力されるため、トランジスタT13はオン状態となる。一方、トランジスタT12のゲート端子には直流電源電圧VDD2が入力される。このため、トランジスタT12のドレイン端子とソース端子との間は、トランジスタT13のドレイン端子とソース端子との間よりも電流が流れにくくなる。したがって、変調信号MOD2は、基準電圧VSSとほぼ同じ電圧が出力される。

【0142】

また、変調信号MOD1が高電位状態である場合、トランジスタT13のゲート端子には基準電圧VSSとほぼ同じ電圧が入力されるため、トランジスタT13はオフ状態となる。トランジスタT12のドレイン端子とソース端子との間は、トランジスタT13のドレイン端子とソース端子との間より電流が流れやすくなる。このため、変調信号MOD2は、直流電源電圧VDD2とほぼ同じ電圧が出力される。

【0143】

このようにすると、変調信号MOD1は、トランジスタT8及びT9によって一度反転増幅された後、トランジスタT12及びT13によって再度反転増幅されるので、変調信号MOD2は変調信号MOD1と同相となる。

【0144】

また、図10に示す送信用増幅回路AMP1が出力する変調信号MOD2の振幅は、図9に示す送信用増幅回路AMP1が出力する変調信号MOD2の振幅以上となる。

【0145】

図11は、本発明の第1実施形態のICチップIC1における直流電源電圧(VDD1)、変調信号電圧(MOD1)及びアンテナ端子間電圧(LA−LB)の数値解析結果の説明図である。

【0146】

図11に示す直流電源電圧(VDD1)の振幅の変動を、図18及び図20に示す直流電源電圧(VDD1)の振幅の変動よりも低減でき、かつ、アンテナ端子間電圧(LA−LB)の振幅の変動を、図18及び図20に示すアンテナ端子間電圧(LA−LB)の振幅の変動よりも増大させることができる。

【0147】

これは、実施形態のICチップIC1は、整流回路R1によって論理回路L1を動作させるための直流電源電圧VDD1を生成し、さらに、整流回路R2によって、負荷変調回路M1が変動させる直流電源電圧VDD2を生成することによる。

【0148】

また、整流回路R1及びR2に接続される平滑化コンデンサC1及びC2によって高周波を除去しているので、図11に示すように、変調信号電圧(MOD1)に高周波信号が伝搬していない。

【0149】

これによって、論理回路L1の動作するための電圧となる直流電源電圧(VDD1)の振幅の低減を防止しつつ、アンテナ端子間電圧(LA−LB)の振幅を増大させることができるので、通信可能距離を低減させずにICチップIC1の動作を安定させることができる。また、論理回路L1の動作するための電圧となる直流電源電圧(VDD1)に高周波信号が伝搬しないので、ICチップIC1の動作を安定させることができる。

【0150】

(第2実施形態)

次に、本発明の第2実施形態を図12を用いて説明する。

【0151】

図12は、本発明の第2実施形態のICチップIC1の回路構成の説明図である。

【0152】

図12に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0153】

リーダ・ライタ装置RW1から送信された信号を復調した復調信号を論理回路L1に入力するために、直流電源電圧VDD2が論理回路L1に入力される点で、図12に示すICチップIC1は第1実施形態のICチップIC1と異なる。

【0154】

リーダ・ライタ装置RW1から送信された信号は、整流回路R2及び平滑化コンデンサC2によって復調される。この復調された電圧(VDD2)が復調信号として論理回路L1に入力される。

【0155】

論理回路L1に復調信号が入力された場合、論理回路L1は、入力された復調信号が示す命令を検出し、検出した命令に対応する処理を実行する。

【0156】

ここで、第1実施形態の図2に示すICチップIC1の回路構成では、論理回路L1に復調信号を入力しようとすると、論理回路L1は、直流電源電圧VDD1から当該復調信号を検出する構成にせざるを得ない。

【0157】

論理回路L1に入力される直流電源電圧VDD1は、レギュレータ回路G1によって、所定値以上の電圧が除去された電圧である。このため、論理回路L1は、復調信号が示す命令を正確に検出できない。

【0158】

このため、本発明の第2実施形態では、論理回路L1を起動させるための直流電源電圧VDD1とは別に、論理回路L1に復調信号を入力するための直流電源電圧VDD2を論理回路L1に入力するようにした。

【0159】

直流電源電圧VDD2はレギュレータ回路G1による影響を受けないので、論理回路L1は、復調信号が示す命令を正確に検出できる。

【0160】

なお、整流回路R2及び平滑化容量C2がリーダ・ライタ装置RW1から送信された信号を復調する動作は負荷変調回路M1の動作に影響を与えず、また、負荷変調回路M1の動作は、整流回路R2及び平滑化容量C2の復調動作に影響を与えない。

【0161】

(第3実施形態)

次に、本発明の第3実施形態を図13及び図14を用いて説明する。

【0162】

図13は、本発明の第3実施形態のICチップIC1の回路構成の説明図である。

【0163】

図13に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0164】

図13に示すICチップIC1は、図2に示す第1実施形態のICチップIC1の構成に加えて、論理回路L1から出力された変調信号MOD1と送信用増幅回路AMP1から出力された変調信号MOD2とを比較し、電圧の大きい方の変調信号を変調信号MOD3として負荷変調回路M1に入力する比較回路CMP1を備える。比較回路CMP1の詳細は、図14で詳細を説明する。なお、変調信号MOD2は、変調信号MOD1を送信用増幅回路AMP1が増幅した信号であり、変調信号MOD1と変調信号MOD2とは同相信号である。このため、本実施形態では、送信用増幅回路AMP1は、図10に示す送信用増幅回路AMP1が採用される。

【0165】

負荷変調回路M1は、比較回路CMP1から出力された変調信号MOD3に応じて、自身の消費電力を変動させることによって、ICチップIC1の消費電力を変動させ、アンテナ端子LA及びLB間の電圧を変動させる。

【0166】

負荷変調回路M1に変調信号M1及び変調信号M2のうち電圧が大きい方の変調信号が入力されるので、負荷変調回路M1に入力される変調信号MOD3の電圧が直流電源電圧VDD1以下となることを防止する。これによって、アンテナ端子間電圧(LA−LB)の振幅の変動が低下することを防止できる。

【0167】

本実施形態の効果について具体的に説明する。

【0168】

図2に示す第1実施形態のICチップIC1では、負荷変調回路M1に変調信号MOD2が入力される。図7に示す負荷変調回路M1に入力される変調信号MOD2が高電位状態である場合、トランジスタT2のドレイン端子とソース端子との間は電流が流れやすい状態となるため、負荷変調回路M1は、直流電源電圧VDD2を低下させる。このため、増幅用増進回路AMP1の増幅率が低下し、送信用増幅回路AMP1によって増幅される変調信号MOD2の電圧も、直流電源電圧VDD2の低下に伴って、低下してしまう。これによって、十分な変調信号MOD2の振幅を得られなくなる場合がある。

【0169】

これに対して、本実施形態のICチップIC1では、比較回路CMP1によって変調信号MOD1及び変調信号MOD2のうち電圧が大きい方の変調信号が負荷変調回路M1に入力されるので、直流電源電圧VDD2の低下に伴い送信用増幅回路AMP1から出力される変調信号MOD2が低下しても、負荷変調回路M1に入力される変調信号MOD1の電圧が変調信号MOD1の電圧以下になることを防止できる。これによって、送信用増幅回路M1に入力される変調信号MOD3の振幅を変調信号MOD1の振幅に担保することができ、変調信号MOD1の振幅以下の変調信号が送信用増幅回路M1に入力されることを防止でき、ICタグTG1の通信可能距離が低減することを防止できる。

【0170】

図14は、本発明の第3実施形態の比較回路CMP1に適用可能な回路の説明図である。

【0171】

比較回路CMP1は、トランジスタT14及びT15を備える。

【0172】

トランジスタT14のゲート端子及びドレイン端子には変調信号MOD1が入力され、トランジスタT15のゲート端子及びドレイン端子には変調信号MOD2が入力される。また、トランジスタT14のソース端子とトランジスタT15のソース端子とが接続される。トランジスタT14のソース端子とトランジスタT15のソース端子との接続線から変調信号MOD3が出力される。

【0173】

変調信号MOD1の電圧が変調信号MOD2の電圧よりも高い場合、トランジスタT14はオン状態となり、トランジスタT15はオフ状態となる。このため、トランジスタT14のドレイン端子とソース端子との間は、トランジスタT15のドレイン端子とソース端子との間より、電流が流れやすくなるので、変調信号MOD3には、変更信号MOD1に近い電圧が出力される。

【0174】

また、変調信号MOD2の電圧が変調信号MOD1の電圧よりも高い場合、トランジスタT15はオン状態となり、トランジスタT14はオフ状態となる。このため、トランジスタT15のドレイン端子とソース端子との間は、トランジスタT14のドレイン端子とソース端子との間より、電流が流れやすくなるので、変調信号MOD3には、変更信号MOD2に近い電圧が出力される。

【0175】

(第4実施形態)

本発明の第4実施形態を図15を用いて説明する。

【0176】

図15は、本発明の第4実施形態のICチップIC1の回路構成の説明図である。

【0177】

図15に示すICチップIC1の構成のうち、図2に示す第1実施形態のICチップIC1の構成と同じ構成は、同じ符号を付与し、説明を省略する。

【0178】

図15に示すICチップIC1は、整流回路R3及び平滑化コンデンサC3を備える点、並びに、送信用増幅回路AMP1に直流電源電圧VDD3が入力される点で、図2に示す第1実施形態のICチップIC1と異なる。

【0179】

アンテナ端子LA及びLBには、整流回路R1、R2及びR3が接続される。

【0180】

整流回路R3は、リーダ・ライタ装置R1からアンテナコイルA1が受信した高周波信号によってアンテナ端子LA及びLA間の電圧(交流電圧)を直流電源電圧VDD3に変換する回路である。整流回路R3は、整流回路R1及びR2と同じく、図3又は図4に示す整流回路を適用すればよい。

【0181】

なお、整流回路R3を構成するトランジスタは、図16に示すキャリア蓄積を用いたトランジスタである。

【0182】

送信用増幅回路VDD3は、整流回路R3から出力される直流電源電圧VDD3を用いて動作し、負荷直流回路M1に入力される直流電源電圧VDD2を共用しない。

【0183】

これによって、図7に示す負荷変調回路M1に入力される変調信号MOD2が高電位状態である場合に負荷変調回路M1が直流電源電圧VDD2を低下させても、送信用増幅回路AMP1は、変調信号MOD1を直流電源電圧VDD3から基準電圧VSSの範囲で増幅できる。これによって、送信用増幅回路AMP1は、振幅の大きい変調信号MOD2を負荷変調回路M1に入力できる。

【0184】

したがって、本実施形態によれば、アンテナ端子間電圧(LA−LB)の振幅の変動が低下することを防止でき、ICタグTG1の通信可能距離を大きくすることができる。

【0185】

以上、本発明者によりなされた発明を実施形態に基づき具体的に説明したが、本発明は上述した実施形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

【産業上の利用可能性】

【0186】

本願発明は、非接触電子装置、所謂、ICタグ等に適用可能である。

【符号の説明】

【0187】

A1及びA2…コイルアンテナ

AMP1…送信用増幅回路

C1〜4…平滑化コンデンサ

CL1…チャネル層

IL1…絶縁体層

ML1及びML2…金属層

MOD1〜MOD3…変調信号

LA及びLB…アンテナ端子

R1〜R3…整流回路

RW1…リーダ・ライタ装置

SL1…基板層

T1〜15…トランジスタ

TG1…ICタグ

【特許請求の範囲】

【請求項1】

キャリア蓄積層を利用したトランジスタによって構成される非接触電子装置であって、

第一の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第一のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、

第二の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第二のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、

前記第一の平滑化コンデンサによって前記第一の直流電源電圧が平滑化された電圧を用いて動作する論理回路と、

前記論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、

前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記変調信号増幅回路が出力する第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする非接触電子装置。

【請求項2】

前記変調信号増幅回路は、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を用いて動作し、前記第一の変調信号の電圧を前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を超えない増幅が可能であることを特徴とする請求項1に記載の非接触電子装置。

【請求項3】

前記第一の変調信号の電圧と前記第二の変調信号の電圧とを比較し、電圧が大きい方の変調信号を変調信号として出力する比較回路を備え、

前記負荷変調回路は、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記比較回路が出力する変調信号に基づいて変動させることを特徴とする請求項1に記載の非接触電子装置。

【請求項4】

第三の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第三のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第三の直流電源電圧に変換する第三の整流回路を備え、

前記変調信号増幅回路は、前記第三の平滑化コンデンサによって第三の直流電源電圧が平滑化された電圧を用いて動作し、前記第一の変調信号の電圧を前記第三の平滑化コンデンサによって第三の直流電源電圧が平滑化された電圧まで増幅可能であることを特徴とする請求項1に記載の非接触電子装置。

【請求項5】

前記トランジスタは、薄膜トランジスタであることを特徴とする請求項1から請求項4のいずれか一つに記載の非接触電子装置。

【請求項6】

前記トランジスタの半導体層が金属酸化物を主体とした半導体であることを特徴とする請求項1から請求項5のいずれか一つに記載の非接触電子装置。

【請求項1】

キャリア蓄積層を利用したトランジスタによって構成される非接触電子装置であって、

第一の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第一のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第一の直流電源電圧に変換する第一の整流回路と、

第二の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第二のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第二の直流電源電圧に変換する第二の整流回路と、

前記第一の平滑化コンデンサによって前記第一の直流電源電圧が平滑化された電圧を用いて動作する論理回路と、

前記論理回路が出力する第一の変調信号を増幅した第二の変調信号を出力する変調信号増幅回路と、

前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記変調信号増幅回路が出力する第二の変調信号に基づいて変動させる負荷変調回路と、を備えることを特徴とする非接触電子装置。

【請求項2】

前記変調信号増幅回路は、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を用いて動作し、前記第一の変調信号の電圧を前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を超えない増幅が可能であることを特徴とする請求項1に記載の非接触電子装置。

【請求項3】

前記第一の変調信号の電圧と前記第二の変調信号の電圧とを比較し、電圧が大きい方の変調信号を変調信号として出力する比較回路を備え、

前記負荷変調回路は、前記第二の平滑化コンデンサによって前記第二の直流電源電圧が平滑化された電圧を、前記比較回路が出力する変調信号に基づいて変動させることを特徴とする請求項1に記載の非接触電子装置。

【請求項4】

第三の平滑化コンデンサに接続され、前記キャリア蓄積を利用した第三のトランジスタによって構成され、前記非接触電子装置に接続されるアンテナが受信した信号を第三の直流電源電圧に変換する第三の整流回路を備え、

前記変調信号増幅回路は、前記第三の平滑化コンデンサによって第三の直流電源電圧が平滑化された電圧を用いて動作し、前記第一の変調信号の電圧を前記第三の平滑化コンデンサによって第三の直流電源電圧が平滑化された電圧まで増幅可能であることを特徴とする請求項1に記載の非接触電子装置。

【請求項5】

前記トランジスタは、薄膜トランジスタであることを特徴とする請求項1から請求項4のいずれか一つに記載の非接触電子装置。

【請求項6】

前記トランジスタの半導体層が金属酸化物を主体とした半導体であることを特徴とする請求項1から請求項5のいずれか一つに記載の非接触電子装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−33335(P2013−33335A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2011−168352(P2011−168352)

【出願日】平成23年8月1日(2011.8.1)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成23年8月1日(2011.8.1)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]