非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、非晶質酸化物を利用した半導体デバイス、電気素子、及び回路に関する。特に、非晶質酸化物を利用した半導体デバイスに関する。

【背景技術】

【0002】

近年、液晶やエレクトロルミネッセンス(ElectroLuminescence:EL)技術等の進歩により、平面薄型画像表示装置(Flat Panel Display:FPD)が実用化されている。

【0003】

これらFPDは、ガラス基板上に設けた非晶質シリコン薄膜や多結晶シリコン薄膜を活性層に用いる電界効果型薄膜トランジスタ(Thin Film Transistor:TFT)のアクティブマトリクス回路により駆動されている。

【0004】

一方、これらFPDのより一層の薄型化、軽量化、耐破損性の向上を求めて、ガラス基板の替わりに軽量で可撓性のある樹脂基板を用いる試みも行われている。

【0005】

しかし、上述のシリコン薄膜を用いるトランジスタの製造は、比較的高温の熱工程を要し、一般的に耐熱性の低い樹脂基板上に直接形成することは困難である。

【0006】

そこで、低温での成膜が可能な、たとえばZnOを材料とした酸化物半導体薄膜を用いるTFTの開発が活発に行われている(特許文献1)。

【0007】

このように、新規な半導体デバイスが期待されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−298062号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

そこで、本発明は、非晶質酸化物を利用した様々な半導体デバイスや、それを用いた回路等を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の集積回路は、電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする。

【0011】

ところで、本発明者が酸化物半導体を検討したところ、ZnOは、一般に安定なアモルファス相を形成することができないことが判った。そして、殆どのZnOは多結晶相を呈するために、多結晶粒子間の界面でキャリアは散乱され、結果として電子移動度を大きくすることができないようである。

【0012】

また、ZnOには、酸素欠陥が入りやすく、キャリア電子が多数発生してしまうため、電気伝導度を小さくすることが難しい。このために、トランジスタのゲート電圧が無印加時でも、ソース端子とドレイン端子間に大きな電流が流れてしまい、TFTのノーマリーオフ動作を実現できないことが判った。また、トランジスタのオン・オフ比を大きくすることも難しいようである。

【0013】

また、本発明者は、特開2000−044236号公報に記載されている非晶質酸化物膜ZnxMyInzO(x+3y/2+3z/2)(式中、MはAl及びGaのうち少なくとも一つの元素である。)について検討した。この材料は、電子キャリア濃度が、1018/cm3以上であり、単なる透明電極としては好適な材料である。

【0014】

しかし、電子キャリア濃度が1018/cm3以上の酸化物をTFTのチャネル層に用いた場合、オン・オフ比が十分にとれず、ノーマリーオフ型のTFTにはふさわしくないことが分かった。

【0015】

つまり、従来の非晶質酸化物膜では、電子キャリア濃度が1018/cm3未満の膜を得ることはできていなかった。

【0016】

そこで、本発明者は、電界効果型トランジスタの活性層として、電子キャリア濃度が1018/cm3未満の非晶質酸化物を用いているTFTを作製したところ、所望の特性のTFTが得られることを発見したのである。

【0017】

しかも、このような非晶質酸化物は、TFT以外の半導体デバイスにも好適に用いることができることも判明した。

【0018】

本発明者らは、InGaO3(ZnO)m、及びこの材料の成膜条件に関する研究開発を精力的に進めた結果、成膜時の酸素雰囲気の条件を制御することで、電子キャリア濃度を1018/cm3未満にできることを見出した。

【0019】

しかも、このような非晶質酸化物は、TFT以外の半導体デバイスにも好適に用いることができることも判明した。

【0020】

即ち、本発明は、室温での電子キャリア濃度が、1018/cm3未満のアモルファス酸化物を電子伝導体材料として用いていることを特徴とする半導体デバイスである。更にまた、別の本発明は、電子キャリア濃度が増加すると共に、電子移動度が増加することを特徴とするアモルファス酸化物を電子伝導体材料として用いていることを特徴とする半導体デバイスである。

【発明の効果】

【0021】

本発明によれば、非晶質酸化物を利用した新規な集積回路を提供できる。

【図面の簡単な説明】

【0022】

【図1】パルスレーザー蒸着法で成膜したIn−Ga−Zn−O系アモルファス膜の電子キャリア濃度と成膜中の酸素分圧の関係を示すグラフである。

【図2】パルスレーザー蒸着法で成膜したIn−Ga−Zn−O系アモルファス膜の電子キャリアの数と電子移動度の関係を示すグラフである。

【図3】In−Ga−Zn−O系アモルファス膜の電気伝導度と成膜中の酸素分圧の関係を示すグラフである。

【図4】酸素分圧0.8Paの雰囲気でパルスレーザー蒸着法で成膜したInGaO3(Zn1−xMgxO)のxの値に対する電気伝導度、キャリア濃度、電子移動度の変化を示すグラフである。

【図5】実施例1で作製したトップゲート型MISFET素子構造を示す模式図である。

【図6】実施例1で作製したトップゲート型MISFET素子の電流−電圧特性を示すグラフである。

【図7】SIT素子の実施例1を示す図である。

【図8】SIT素子の実施例2を示す図である。

【図9】SIT素子の実施例3を示す図である。

【図10】SIT素子の実施例4を示す図である。

【図11】SBT素子の実施例を示す図である。

【図12】PN−T素子の実施例を示す図である。

【図13】SBD素子の実施例を示す図である。

【図14】PN−D素子の実施例を示す図である。

【図15】抵抗素子の実施例1を示す図である。

【図16】抵抗素子の実施例2を示す図である。

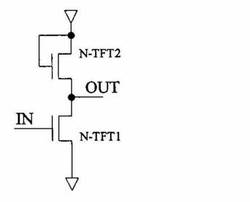

【図17】実施例1のインバータ回路1を示す図である。

【図18】実施例1のインバータ回路2を示す図である。

【図19】実施例1のインバータ回路3を示す図である。

【図20】実施例1のインバータ回路4を示す図である。

【図21】実施例1のインバータ回路5を示す図である。

【図22】実施例1のインバータ回路6を示す図である。

【図23】実施例2のNAND回路1を示す図である。

【図24】実施例2のNAND回路2を示す図である。

【図25】実施例2のNAND回路3を示す図である。

【図26】実施例2のNOR回路1を示す図である。

【図27】実施例2のNOR回路2を示す図である。

【図28】実施例2のNOR回路3を示す図である。

【図29】実施例3のクロックドインバータ回路1を示す図である。

【図30】実施例3のクロックドインバータ回路2を示す図である。

【図31】実施例3のクロックドインバータ回路3を示す図である。

【図32】実施例3のD−フリップフロップを示す図である。

【図33】実施例3のシフトレジスタを示す図である。

【図34】実施例4の1ビットSRAMセル回路1を示す図である。

【図35】実施例4の1ビットSRAMセル回路2を示す図である。

【図36】実施例4の1ビットSRAMセル回路3を示す図である。

【図37】実施例5のNOR型ROM回路1を示す図である。

【図38】実施例5のNOR型ROM回路2の作製の第一段階を示す図である。

【図39】実施例5のNOR型ROM回路2の作製の第二段階を示す図である。

【図40】実施例5のNOR型ROM回路2を示す図である。

【図41】実施例6のNAND型ROM回路1を示す図である。

【図42】実施例6のNAND型ROM回路2を示す図である。

【図43】実施例7の差動増幅回路1を示す図である。

【図44】実施例7の差動増幅回路2を示す図である。

【図45】実施例8のN−TFTを示す図である。

【図46】実施例9のアクティブマトリックスバックプレーンを示す図である。

【図47】実施例1のインバータ回路7を示す図である。

【図48】PLD法を行う際に用いられる装置の模式図である。

【図49】PLD法を行う際に用いられる装置の模式図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

【0024】

まず、第1の実施形態として、本発明に係る半導体デバイスを、そして、第2の実施形態として、集積回路について説明し、その後、本発明に用いられる非晶質酸化物について詳述している。

【0025】

(第1の実施形態:半導体デバイス)

まず、P型領域とN型領域とを有する半導体デバイスについて説明する。ここでいう、半導体デバイスは、PN接合型トランジスタやヘテロ接合デバイスが含まれる。

【0026】

本発明では、N型領域を構成する非晶質酸化物として、電子キャリア濃度が1018/cm3未満である酸化物や、電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す酸化物を用いることに特徴がある。この非晶質酸化物については後述する。

【0027】

なお、基板上で、前記P型領域内に前記N型領域が設けられているか、あるいは前記N型領域内に前記P型領域が設けられていることも好ましい形態である。

【0028】

また、前記P型領域と前記N型領域とが、基板上の同一層に形成されていることも好ましい形態である。

【0029】

また、P型領域及びN型領域を非晶質酸化物を異なる材料で構成することも好ましい形態である。

【0030】

更にまた、本発明は、上記透明酸化物半導体膜をN型半導体として用いたSIT素子に関する。

【0031】

例として図7を用いて説明する。

【0032】

具体的には、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物半導体とオーミックコンタクトを形成できるITOにより電極11−1を形成し、続いて、上記電極上に上記透明酸化物半導体膜13を形成する。さらに、上記酸化物膜中に、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptにより電極12を複数形成し、さらに上記酸化物膜を積層する。その後、電極11−2を電極11−1と同じ材料で形成することで、SIT素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも、高い電流能力を有する素子を実現する、という効果が得られる。

【0033】

又、上記電極12のPtを薄くする、あるいは、上記電極12として、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きいP型の透明酸化膜半導体を用いる事で、透明なSIT素子を作製できる。

【0034】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたSBT素子に関する。

【0035】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1、11−2を形成する。そして、電極11−1、11−2間に、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptによりゲート電極12を形成することで、SBT素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも簡単な構成で、ゲート電極に印加する電圧で電極11−1、11−2間の電流を制御できるトランジスタ素子を実現する、という効果が得られる。特に、上記電極11−2の下の上記酸化物膜を薄くすることで、よりゲート電圧により変調できる電流の大きさが大きくなる。

【0036】

又、上記電極12のPtを薄くする事で、透明なSBT素子を作製できる。

【0037】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたPN−T素子に関する。

【0038】

具体的には、図12に示すように、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物N型半導体膜13を形成する。

【0039】

続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1、11−2を形成する。そして、電極11−1、11−2間に、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体材料14を積層する。さらに、上記P型半導体材料上に、上記P型半導体材料とオーミックコンタクトを形成できる材料、例えば、Ptによりゲート電極12を形成することで、PN−T素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも簡単な構成で、ゲート電極に印加する電圧で電極11−1、11−2間の電流を制御できるトランジスタ素子を実現する、という効果が得られる。特に、上記電極12の下の上記酸化物膜を薄くすることで、よりゲート電圧により変調できる電流の大きさが大きくなる。

【0040】

又、上記電極12のPtを薄くし、上記P型半導体に透明酸化物P型半導体を用いれば、透明なPN−T素子を作製できる。

【0041】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたBPT素子に関する。

【0042】

具体的には、ガラス、プラスチックなどの絶縁基板上に、透明酸化物N型半導体膜1、透明酸化物N型半導体でキャリア密度・伝導度が異なる半導体膜1’、フェルミ準位の絶対値が上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体膜を形成する。続いて、上記酸化物膜1、1’上に、オーミックコンタクトを形成できるITOにより、電極1−1、1−2を形成する。さらに、上記P型半導体膜上にオーミックコンタクトを形成できる材料、例えば、Ptにより、ベース電極2を形成することで、BPT素子を作製することができる。

【0043】

又、上記電極2のPtを薄くし、上記P型半導体に透明酸化物P型半導体を用いれば、透明なBPT素子を作製できる。

【0044】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたSBD素子に関する。

【0045】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極1と、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptにより電極2を形成することで、SBD素子を作製することができる。

【0046】

又、上記電極2のPtを薄くする事で、透明なSBD素子を作製できる。

【0047】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたPN−D素子に関する(図14)。

【0048】

具体的には、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物N型半導体膜13を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11と、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体材料14をそれぞれ積層する。さらに、上記P型半導体とオーミックコンタクトを形成できる材料、例えば、Ptにより電極12を形成することで、PN−D素子を作製することができる。

【0049】

又、上記P型半導体材料として、透明酸化膜P型半導体を用い、上記電極2のPtを薄くする事で、透明なPN−D素子を作製できる。

【0050】

本発明は、上記透明酸化物半導体膜を抵抗材料として用いた抵抗素子に関する。

【0051】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1と11−2を形成することで、透明な抵抗素子を作製することができる。

【0052】

上記半導体膜1と上記電極11−1、11−2の間に、上記半導体膜1とキャリア密度と伝導度が異なる上記透明酸化物N型半導体膜を備えても良い。ただし、上記酸化物の層が共に、キャリア濃度が1018/cm3未満、かつ、伝導度が10S/cm以下である必要はない。

【0053】

上記透明酸化物N型半導体とオーミックコンタクトを形成する材料として、例えば、上記ITOやカルシウム(Ca)などの、仕事関数が上記半導体膜のフェルミ準位の絶対値と同程度、又は、やや小さいことを特徴とする金属・合金等が挙げられる。

【0054】

上記SIT、SBTのゲート電極、並びに、上記SDのショットキー障壁を形成する電極として用いる大きな仕事関数を持つ高導電性材料として、例えば、白金(Pt)やNi、金(Au)などの金属がある。

【0055】

さらに、上記金属を非常に薄く形成することで、透明又は半透明な金属膜が形成でき、上記酸化物と組み合わせることで、透明なSIT、SBT、並びにSDを作製することが可能である。

【0056】

上記SIT、PN−Tのゲート電極用のP型半導体、並びに、上記PN−DのP型半導体として、例えば、アクセプターをドープしたSi等の無機半導体、ペンタセン等の低分子有機半導体、ポリチオフェン、ポリフェニレンビニレン等の高分子有機半導体、Cu2O等の酸化物半導体を用いる事ができる。ただし、PN接合障壁を形成する為には、上記P型半導体のフェルミ準位の絶対値は、上記酸化物N型半導体のフェルミ準位の絶対値よりも、大きい値を持つものとする。

【0057】

さらに、上記酸化物P型半導体と、ITO等の透明な電極を用いる事で、透明なSIT、PN−T、並びにPN−Dを作製することが可能である。

【0058】

また、上述したSiなどの半導体材料の多くは、電子キャリア濃度が1018/cm3未満である非晶質透明酸化物や、電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質透明酸化物とバンドギャップが異なる。よって、この非晶質透明酸化物半導体からなる領域とヘテロ接合を形成する。こうして、ヘテロ接合を有する半導体デバイスが構成される。

【0059】

(第2の実施形態:集積回路)

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いた論理回路に関する。

【0060】

具体的には、上記透明膜を電子伝導体とした抵抗と、上記透明膜を用いたN−TFTを電源−接地電位(GND)間に直列に接続し、上記N−TFTのゲートを信号入力とし、上記TFTのソースを出力とする。

【0061】

これにより、半導体層として上記透明膜のみを用いたインバータ回路を構成できる。

【0062】

さらに、上記抵抗に代わり、P型半導体を活性層として用いたP型TFT(以下、P−TFT)を用い、P−TFTのゲートをN−TFTのゲートと共通の入力とすることで、相補型TFT回路を構成することができる。

【0063】

これにより、インバータの動作時における貫通電流を抑制し、低消費電力である回路を構成できる、という効果が得られる。

【0064】

上記P型半導体の材料として、例えば、ドープしたSi等の無機半導体、ペンタセン等の低分子有機半導体、ポリチオフェン、ポリフェニレンビニレン等の高分子有機半導体、Cu2O等の酸化物半導体を用いる事が好ましい。特に、上記酸化物半導体をP型半導体として用いる場合には、半導体層が透明な回路を構成できる。

【0065】

上記インバータ回路と同様に、クロックドインバータ回路、NAND回路、NOR回路、フリップフロップ、シフトレジスタ等の論理回路を構成することができる。

【0066】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いたSRAM回路に関する。

【0067】

具体的には、2つの上記透明膜を用いたN−TFTを備えたインバータ回路について、入力と出力を接続し、上記インバータの各入力と2本のビット線(BL、BLバー)の間にN−TFTを各々備える。そして、上記N−TFTのゲートは共にワード線(WL)に接続されている。これにより、N型半導体層として上記透明膜を用いた1ビットSRAMセル回路を構成できる。

【0068】

さらに、上記N−TFTと上記透明膜を抵抗で構成されるインバータを用いる場合には、少なくともTFTと抵抗が透明であるSRAMを作製することができる。

【0069】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いたROM回路に関する。

【0070】

具体的には、複数のワード線(WL1〜WLn)と、複数のビット線(BL1〜BLn)を備える。そして、上記ビット線の各々には、ワード線がゲートに接続され、ソースがGNDに接続された、ドレインが並列に接続された上記透明膜を半導体膜とするN−TFTを複数備える。ただし、1本のビット線に対し、全ての上記ワード線に相当するN−TFTを備えておらず、いくつかのワード線に相当するN−TFTを省かれている。これにより、N型半導体層として上記透明膜を用いたNOR型ROM回路を構成できる。

【0071】

さらに、上記透明膜を用いることで、上記ROM回路のTFT部を透明にできる。

【0072】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いた差動増幅回路に関する。

【0073】

具体的には、ソースがGNDに接地され、ゲートにバイアス電圧として一定電圧が印加されるN−TFTと、ゲートを入力とし、ソースが上記N−TFTのドレインと接続されている2つのN−TFTとを備える。そして、2つの上記N−TFTの各々のドレインと電源間に抵抗を備え、上記N−TFTのドレインと抵抗間を出力とすることで差動増幅回路を構成できる。

【0074】

さらに、上記抵抗に上記透明膜を用いることで、少なくとも上記N−TFTと抵抗部分を透明にできる。

【0075】

また、本発明は、上記透明膜を半導体とするTFTを、N−TFTとして用いた回路によって構成されるICタグ又はIDタグに関する。

【0076】

具体的には、上記ICタグ又はIDタグは、上記論理回路、上記メモリ回路、上記差動増幅回路を用いたアナログ回路、上記N−TFTのゲート−ドレイン間をショートすることでダイオードの特性を実現する素子を用いた整流回路をすべて、あるいは、少なくともいずれかを含んで構成されている。

【0077】

上記IDタグは、上記透明膜を用いることで、少なくとも上記N−TFTと抵抗部分を透明にできる。

【0078】

また、本発明は、上記透明膜を半導体とするTFTを、N−TFTとして用いたアクティブマトリックス基板に関する。

【0079】

具体的には、上記N−TFTを、各セル回路のスイッチング素子として用いた、LCD(LiquidCrystalDisplay、液晶ディスプレイ)、有機EL(Electro−Luminescence)ディスプレイ、光センサ等のアクティブマトリックス基板を作製できる。

【0080】

上記アクティブマトリックス基板は、上記透明膜を半導体とするN−TFTを用いることで、開口率を増やすことができる、という効果が得られる。

【0081】

なお、上述の回路は、必ずしも、全ての要素をTFTで構成する必要はない。適宜PNトランジスタやSIT,SB−T,BP−Tを用いて回路を構成することもできる。

【0082】

(非晶質酸化物について)

本発明に係る非晶質酸化物の電子キャリア濃度は、室温で測定する場合の値である。室温とは、例えば25℃であり、具体的には0℃から40℃程度の範囲から適宜選択されるある温度である。なお、本発明に係るアモルファス酸化物の電子キャリア濃度は、0℃から40℃の範囲全てにおいて、1018/cm3未満を充足する必要はない。例えば、25℃において、キャリア電子密度1018/cm3未満が実現されていればよい。また、電子キャリア濃度を更に下げ、1017/cm3以下、より好ましくは1016/cm3以下にするとノーマリーオフのTFTが歩留まり良く得られる。

【0083】

なお、1018/cm3未満とは、好ましくは1×1018/cm3未満であり、より好適には、1.0×1018/cm3未満である。

【0084】

電子キャリア濃度の測定は、ホール効果測定により求めることが出来る。

【0085】

なお、本発明において、アモルファス酸化物とは、X線回折スペクトルにおいて、ハローパターンが観測され、特定の回折線を示さない酸化物をいう。

【0086】

本発明のアモルファス酸化物における、電子キャリア濃度の下限値は、TFTのチャネル層として適用できれば特に限定されるものではない。下限値は、例えば、1012/cm3である。

【0087】

従って、本発明においては、後述する各実施例のようにアモルファス酸化物の材料、組成比、製造条件などを制御して、例えば、電子キャリア濃度を、1012/cm3以上1018/cm3未満とする。より好ましくは1013/cm3以上1017/cm3以下、更には1015/cm3以上1016/cm3以下の範囲にすることが好ましいものである。前記非晶質酸化物としては、InZnGa酸化物のほかにも、In酸化物、InxZn1−x酸化物(0.2≦x≦1)、InxSn1−x酸化物(0.8≦x≦1)、あるいはInx(Zn、Sn)1−x酸化物(0.15≦x≦1)から適宜選択できる。

【0088】

なお、Inx(Zn、Sn)1−x酸化物は、Inx(ZnySn1−y)1−x酸化物と記載することができ、yの範囲は1から0である。

【0089】

なお、ZnとSnを含まないIn酸化物の場合は、Inの一部をGaに置換することもできる。即ち、InxGa1−x酸化物(0≦x≦1)の場合である。

【0090】

以下に、本発明者らが作製することに成功した電子キャリア濃度が1018/cm3未満の非晶質酸化物について詳述する。

【0091】

上記酸化物とは、In−Ga−Zn−Oを含み構成され、結晶状態における組成がInGaO3(ZnO)m(mは6未満の自然数)で表され、電子キャリア濃度が1018/cm3未満であることを特徴とする。

【0092】

また上記酸化物は、In−Ga−Zn−Mg−Oを含み構成され、結晶状態の組成がInGaO3(Zn1−xMgxO)m(mは6未満の自然数、0<x≦1)で表され、電子キャリア濃度が1018/cm3未満であることを特徴とする。

【0093】

なお、これらの酸化物で構成される膜において、電子移動度が1cm2/(V・秒)超になるように設計することも好ましい。

【0094】

上記膜をチャネル層に用いれば、トランジスターオフ時のゲート電流が0.1マイクロアンペヤ未満のノーマリーオフで、オン・オフ比が103超のトランジスタ特性を実現できる。そして、可視光に対して、透明あるいは透光性を有し、フレキシブルなTFTが実現される。

【0095】

なお、上記膜は、伝導電子数の増加と共に、電子移動度が大きくなることを特徴とする。透明膜を形成する基板としては、ガラス基板、樹脂製プラスチック基板又はプラスチックフィルムなどを用いることができる。

【0096】

上記非晶質酸化物膜をチャネル層に利用する際には、Al2O3,Y2O3、又はHfO2の1種、又はそれらの化合物を少なくとも二種以上含む混晶化合物をゲート絶縁膜に利用できる。

【0097】

また、非晶質酸化物中に、電気抵抗を高めるための不純物イオンを意図的に添加せず、酸素ガスを含む雰囲気中で、成膜することも好ましい形態である。

【0098】

本発明者らは、この半絶縁性酸化物アモルファス薄膜は、伝導電子数の増加と共に、電子移動度が大きくなるという特異な特性を見出した。そして、その膜を用いてTFTを作成し、オン・オフ比、ピンチオフ状態での飽和電流、スイッチ速度などのトランジスタ特性が更に向上することを見出した。即ち、非晶質酸化物を利用して、ノーマリーオフ型のTFTを実現できることを見出した。

【0099】

非晶質酸化物薄膜を膜トランジスタのチャネル層として用いると、電子移動度が1cm2/(V・秒)超、好ましくは5cm2/(V・秒)超にすることができる。

【0100】

電子キャリア濃度が、1018/cm3未満、好ましくは、1016/cm3未満のときは、オフ時(ゲート電圧無印加時)のドレイン・ソース端子間の電流を、10マイクロアンペヤ未満、好ましくは0.1マイクロアンペア未満にすることができる。

【0101】

また、該膜を用いれば、電子移動度が1cm2/(V・秒)超、好ましくは5cm2/(V・秒)超の時は、ピンチオフ後の飽和電流を10マイクロアンペア超にでき、オン・オフ比を103超とすることができる。

【0102】

TFTでは、ピンチオフ状態では、ゲート端子に高電圧が印加され、チャネル中には高密度の電子が存在している。

【0103】

したがって、本発明によれば、電子移動度が増加した分だけ、より飽和電流値を大きくすることができる。この結果、オン・オフ比の増大、飽和電流の増大、スイッチング速度の増大など、トランジスタ特性の向上が期待できる。

【0104】

なお、通常の化合物中では、電子数が増大すると、電子間の衝突により、電子移動度は減少する。

【0105】

なお、上記TFTの構造としては、半導体チャネル層の上にゲート絶縁膜とゲート端子を順に形成するスタガ(トップゲート)構造や、ゲート端子の上にゲート絶縁膜と半導体チャネル層を順に形成する逆スタガ(ボトムゲート)構造を用いることができる。

【0106】

(第1の成膜法:PLD法)

結晶状態における組成がInGaO3(ZnO)m(mは6未満の自然数)で表される非晶質酸化物薄膜は、mの値が6未満の場合は、800℃以上の高温まで、非晶質状態が安定に保たれるが、mの値が大きくなるにつれ、結晶化しやすくなる。すなわち、InGaO3に対するZnOの比が増大して、ZnO組成に近づくにつれ、結晶化しやすくなる。

【0107】

したがって、非晶質TFTのチャネル層としては、mの値が6未満であることが好ましい。

【0108】

成膜方法は、InGaO3(ZnO)m組成を有する多結晶焼結体をターゲットとして、気相成膜法を用いるのが良い。気相成膜法の中でも、スッパタ法、パルスレーザー蒸着法が適している。さらに、量産性の観点から、スパッタ法が最も適している。

【0109】

しかしながら、通常の条件で該非晶質膜を作成すると、主として酸素欠損が生じ、これまで、電子キャリア濃度を1018/cm3未満、電気伝導度にして、10S/cm以下にすることができなかった。そうした膜を用いた場合、ノーマリーオフのトランジスタを構成することができない。

【0110】

本発明者らは、図9で示される装置により、パルスレーザー蒸着法で作製したIn−Ga−Zn−Oを作製した。

【0111】

図48に示すようなPLD成膜装置を用いて、成膜を行った。

【0112】

同図において、701はRP(ロータリーポンプ)、702はTMP(ターボ分子ポンプ)、703は準備室、704はRHEED用電子銃、705は基板を回転、上下移動するための基板保持手段、706はレーザー入射窓である。また、707は基板、708はターゲット、709はラジカル源、710はガス導入口、711はターゲットを回転、上下移動するためのターゲット保持手段、712はバイパスライン、713はメインライン、714はTMP(ターボ分子ポンプ)である。また、715はRP(ロータリーポンプ)、716はチタンゲッターポンプ、717はシャッターである。また、図中718はIG(イオン真空計)、719はPG(ピラニ真空計)、720はBG(バラトロン真空計)、721は成長室(チャンバー)である。

【0113】

KrFエキシマレーザーを用いたパルスレーザー蒸着法により、SiO2ガラス基板(コーニング社製1737)上にIn−Ga−Zn−O系アモルファス酸化物半導体薄膜を堆積させた。堆積前の処理として、基板の超音波による脱脂洗浄を、アセトン,エタノール,超純水を用いて、各5分間行った後、空気中100℃で乾燥させた。

【0114】

前記多結晶ターゲットには、InGaO3(ZnO)4焼結体ターゲット(サイズ20mmΦ5mmt)を用いた。これは、出発原料として、In2O3:Ga2O3:ZnO(各4N試薬)を湿式混合した後(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て得られるものである。こうして作製したターゲットの電気伝導度は、90(S/cm)であった。成長室の到達真空を2×10−6(Pa)にして、成長中の酸素分圧を6.5(Pa)に制御して成膜を行った。

【0115】

チャンバー721内酸素分圧は6.5Pa、基板温度は25℃である。

【0116】

なお、ターゲット708と被成膜基板707間の距離は、30(mm)であり、入射窓716から入射されるKrFエキシマレーザーのパワーは、1.5−3(mJ/cm2/pulse)の範囲である。また、パルス幅は、20(nsec)、繰り返し周波数は10(Hz)、そして照射スポット径は、1×1(mm角)とした。

【0117】

こうして、成膜レート7(nm/min)で成膜を行った。

【0118】

得られた薄膜について、薄膜のすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは認められなかったことから、作製したIn−Ga−Zn−O系薄膜はアモルファスであるといえる。

【0119】

さらに、X線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。蛍光X線(XRF)分析の結果、薄膜の金属組成比はIn:Ga:Zn=0.98:1.02:4であった。

【0120】

電気伝導度は、約10−2S/cm未満であった。電子キャリア濃度は約1016/cm3以下、電子移動度は約5cm2/(V・秒)と推定される。

【0121】

光吸収スペクトルの解析から、作製したアモルファス薄膜の禁制帯エネルギー幅は、約3eVと求まった。以上のことから、作製したIn−Ga−Zn−O系薄膜は、結晶のInGaO3(ZnO)4の組成に近いアモルファス相を呈しており、酸素欠損が少なく、電気伝導度が小さな透明な平坦薄膜であることが分かった。

【0122】

具体的に図1を用いて説明する。同図は、In−Ga−Zn−Oから構成され、結晶状態を仮定した時の組成がInGaO3(ZnO)m(mは6未満の数)で表される透明アモルファス酸化物薄膜を本実施例と同じ条件下で作成する場合を示した特性図である。この特性図は、酸素分圧を変化させた場合に、成膜された酸化物の電子キャリア濃度の変化を示したものである。

【0123】

本実施例と同じ条件下で酸素分圧を4.5Pa超の高い雰囲気中で、成膜することにより、図1に示すように、電子キャリア濃度を1018/cm3未満に低下させることができた。この場合、基板の温度は意図的に加温しない状態で、ほぼ室温に維持されている。フレキシブルなプラスチックフィルムを基板として使用するには、基板温度は100℃未満に保つことが好ましい。

【0124】

酸素分圧をさらに大きくすると、電子キャリア濃度をさらに低下させることができる。例えば、図1に示す様に、基板温度25℃、酸素分圧5Paで成膜したInGaO3(ZnO)4薄膜では、さらに、電子キャリア数を1016/cm3に低下させることができた。

【0125】

得られた薄膜は、図2に示す様に、電子移動度が1cm2/(V・秒)超であった。しかし、本実施例のパルスレーザー蒸着法では、酸素分圧を6.5Pa以上にすると、堆積した膜の表面が凸凹となり、TFTのチャネル層として用いることが困難となる。

【0126】

従って、酸素分圧4.5Pa超、望ましくは5Pa超、6.5Pa未満の雰囲気で、パルスレーザー蒸着法で、結晶状態における組成InGaO3(ZnO)m(mは6未満の数)で表される透明アモルファス酸化物薄膜を作製する。この透明アモルファス酸化物薄膜を用いれば、ノーマリーオフのトランジスタを構成することができる。

【0127】

また、該薄膜の電子移動度は、1cm2/V・秒超が得られ、オン・オフ比を103超に大きくすることができた。

【0128】

以上、説明したように、本実施例に示した条件下でPLD法によりInGaZn酸化物の成膜を行う場合は、酸素分圧を4.5Pa以上6.5Pa未満になるように制御することが望ましい。

【0129】

なお、電子キャリア濃度を1018/cm3未満を実現するためには、酸素分圧の条件、成膜装置の構成や、成膜する材料や組成などに依存する。

【0130】

次に、上記装置における酸素分圧6.5Paの条件で、アモルファス酸化物を作製し、図5に示すトップゲート型MISFET素子を作製した。具体的には、まず、ガラス基板(1)上に上記のアモルファスIn−Ga−Zn−O薄膜の作製法により、チャンネル層(2)として用いる厚さ120nmの半絶縁性アモルファスInGaO3(ZnO)4膜を形成した。

【0131】

さらにその上に、チャンバー内酸素分圧を1Pa未満にして、パルスレーザー堆積法により電気伝導度の大きなInGaO3(ZnO)4及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜し(厚み:90nm、比誘電率:約15、リーク電流密度:0.5MV/cm印加時に10−3A/cm2)、その上に金を成膜した。そして、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。

【0132】

MISFET素子の特性評価

図6に、室温下で測定したMISFET素子の電流−電圧特性を示す。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型半導体であることが分かる。これは、アモルファスIn−Ga−Zn−O系半導体がn型であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的な半導体トランジスタの挙動を示した。利得特性を調べたところ、VDS=4V印加時におけるゲート電圧VGSの閾値は約−0.5Vであった。また、VG=10V時には、IDS=1.0×10−5Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Ga−Zn−O系アモルファス半導体薄膜内にキャリアを誘起できたことに対応する。

【0133】

トランジスタのオン・オフ比は、103超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約7cm2(Vs)−1の電界効果移動度が得られた。作製した素子に可視光を照射して同様の測定を行なったが、トランジスタ特性の変化は認められなかった。

【0134】

本実施例によれば、電子キャリア濃度が小さく、したがって、電気抵抗が高く、かつ電子移動度が大きいチャネル層を有する薄膜トランジスタを実現できる。

【0135】

なお、上記したアモルファス酸化物は、電子キャリア濃度の増加と共に、電子移動度が増加し、さらに縮退伝導を示すという優れた特性を備えていた。

【0136】

本実施例では、ガラス基板上に薄膜トランジスタを作製したが、成膜自体が室温で行えるので、プラスチック板やフィルムなどの基板が使用可能である。

【0137】

また、本実施例で得られたアモルファス酸化物は、可視光の光吸収が殆どなく、透明なフレキシブルTFTを実現できる。

【0138】

(第2の成膜法:スパッタ法(SP法))

雰囲気ガスとしてアルゴンガスを用いた高周波SP法により、成膜する場合について説明する。

【0139】

SP法は、図49に示す装置を用いて行った。同図において、807は被成膜基板、808はターゲット、805は冷却機構付き基板保持手段、814は、ターボ分子ポンプ、815はロータリーポンプ、817はシャッターである。また、818はイオン真空計、819はピラニ真空計、821は成長室(チャンバー)、830はゲートバルブである。

【0140】

被成膜基板807としては、SiO2ガラス基板(コーニング社製1737)を用意した。成膜前処理として、この基板の超音波脱脂洗浄を、アセトン、エタノール、超純水により各5分ずつ行った後、空気中100℃で乾燥させた。

【0141】

ターゲット材料としては、InGaO3(ZnO)4組成を有する多結晶焼結体(サイズ20mmΦ5mmt)を用いた。

【0142】

この焼結体は、出発原料として、In2O3:Ga2O3:ZnO(各4N試薬)を湿式混合(溶媒:エタノール)し、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て作製した。このターゲット808の電気伝導度は90(S/cm)であり、半絶縁体状態であった。

【0143】

成長室821内の到達真空は、1×10−4(Pa)であり、成長中の酸素ガスとアルゴンガスの全圧は、4〜0.1×10−1(Pa)の範囲での一定の値とした。そして、アルゴンガスと酸素との分圧比を変えて、酸素分圧を10−3〜2×10−1(Pa)の範囲で変化させた。

【0144】

また、基板温度は、室温とし、ターゲット808と被成膜基板807間の距離は、30(mm)であった。

【0145】

投入電力は、RF180Wであり、成膜レートは、10(nm/min)で行った。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−Zn−Ga−O系膜はアモルファス膜であることが示された。

【0146】

さらに、X線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。蛍光X線(XRF)分析の結果、薄膜の金属組成比はIn:Ga:Zn=0.98:1.02:4であった。

【0147】

成膜時の雰囲気の酸素分圧を変化させ、得られたアモルファス酸化物膜の電気伝導度を測定した。その結果を図3に示す。

【0148】

図3に示すように、酸素分圧を3×10−2Pa超の高い雰囲気中で、成膜することにより、電気伝導度を10S/cm未満に低下させることができた。

【0149】

酸素分圧をさらに大きくすることにより、電子キャリア数を低下させることができた。例えば、図3に示す様に、基板温度25℃、酸素分圧10−1Paで成膜したInGaO3(ZnO)4薄膜では、さらに、電気伝導度を約10−10S/cmに低下させることができた。また、酸素分圧10−1Pa超で成膜したInGaO3(ZnO)4薄膜は、電気抵抗が高すぎて電気伝導度は測定できなかった。この場合、電子移動度は測定できなかったが、電子キャリア濃度が大きな膜での値から外挿して、電子移動度は、約1cm2/V・秒と推定された。

【0150】

すなわち、酸素分圧3×10−2Pa超、望ましくは5×10−1Pa超のアルゴンガス雰囲気下でスパッタ蒸着法で成膜を行った。この成膜により、In−Ga−Zn−Oから構成され、結晶状態における組成InGaO3(ZnO)m(mは6未満の自然数)で表される透明アモルファス酸化物薄膜を作製した。この透明アモルファス酸化物薄膜を用い、ノーマリーオフで、かつオン・オフ比を103超のトランジスタを構成することができた。

【0151】

本実施例で示した装置、材料を用いる場合は、スパッタによる成膜の際の酸素分圧としては、例えば、3×10−2Pa以上、5×10−1Pa以下の範囲である。なお、パルスレーザー蒸着法およびスパッタ法で作成された薄膜では、図2に示す様に、伝導電子数の増加と共に、電子移動度が増加する。

【0152】

上記のとおり、酸素分圧を制御することにより、酸素欠陥を低減でき、その結果、電子キャリア濃度を減少できる。また、アモルファス状態では、多結晶状態とは異なり、本質的に粒子界面が存在しないために、高電子移動度のアモルファス薄膜を得ることができる。

【0153】

なお、ガラス基板の代わりに厚さ200μmのポリエチレン・テレフタレート(PET)フィルムを用いた場合にも、得られたInGaO3(ZnO)4アモルファス酸化物膜は、同様の特性を示した。

【0154】

なお、ターゲットとして、多結晶InGaO3(Zn1−xMgxO)m(mは6未満の自然数、0<x≦1)を用いれば、1Pa未満の酸素分圧下でも、高抵抗非晶質InGaO3(Zn1−xMgxO)m膜を得ることができる。

【0155】

例えば、Znを80at%のMgで置換したターゲットを使用した場合、酸素分圧0.8Paの雰囲気で、パルスレーザー堆積法で得られた膜の電子キャリア濃度を1016/cm3未満とすることができる(電気抵抗値は、約10−2S/cmである。)。

【0156】

こうした膜の電子移動度は、Mg無添加膜に比べて低下するが、その程度は少なく、室温での電子移動度は約5cm2/(V・秒)で、アモルファスシリコンに比べて、1桁程度大きな値を示す。同じ条件で成膜した場合、Mg含有量の増加に対して、電気伝導度と電子移動度は、共に低下するので、Mgの含有量は、好ましくは、20%超、85%未満(xにして、0.2<x<0.85)である。

【0157】

上記した非晶質酸化物膜を用いた薄膜トランジスタにおいて、Al2O3,Y2O3、HfO2、又はそれらの化合物を少なくとも二つ以上含む混晶化合物をゲート絶縁膜とすることが好ましい。

【0158】

ゲート絶縁薄膜とチャネル層薄膜との界面に欠陥が存在すると、電子移動度の低下及びトランジスタ特性にヒステリシスが生じる。また、ゲート絶縁膜の種類により、リーク電流が大きく異なる。このために、チャネル層に適合したゲート絶縁膜を選定する必要がある。Al2O3膜を用いれば、リーク電流を低減できる。また、Y2O3膜を用いればヒステリシスを小さくできる。さらに、高誘電率のHfO2膜を用いれば、電子移動度を大きくすることができる。また、これらの膜の混晶を用いて、リーク電流、ヒステリシスが小さく、電子移動度の大きなTFTを形成できる。また、ゲート絶縁膜形成プロセス及びチャネル層形成プロセスは、室温で行うことができるので、TFT構造として、スタガ構造及び逆スタガ構造いずれをも形成することができる。

【0159】

このように形成したTFTは、ゲート端子、ソース端子、及び、ドレイン端子を備えた3端子素子である。このTFTは、セラミックス、ガラス、又はプラスチックなどの絶縁基板上に成膜した半導体薄膜を、電子又はホールが移動するチャネル層として用いるものである。そして、このTFTはゲート端子に電圧を印加して、チャンネル層に流れる電流を制御し、ソース端子とドレイン端子間の電流をスイッチングする機能を有するアクテイブ素子である。

【0160】

なお、酸素欠損量を制御して所望の電子キャリア濃度を達成できていることが本発明においては重要である。

【0161】

上記記載においては、非晶質酸化物膜の酸素量(酸素欠損量)の制御を、成膜時に酸素を所定濃度含む雰囲気中で行うことで制御している。しかし、成膜後、当該酸化物膜を酸素を含む雰囲気中で後処理して酸素欠損量を制御(低減あるいは増加)することも好ましいものである。

【0162】

効果的に酸素欠損量を制御するには、酸素を含む雰囲気中の温度を0℃以上300℃以下、好ましくは、25℃以上、250℃以下、更に好ましくは100℃以上200℃以下で行うのがよい。

【0163】

勿論、成膜時にも酸素を含む雰囲気中で行い、且つ成膜後の後処理でも酸素を含む雰囲気中で後処理してもよい。また、所定の電子キャリア濃度(1018/cm3未満)を得られるのであれば、成膜時には、酸素分圧制御は行わないで、成膜後の後処理を酸素を含む雰囲気中で行ってもよい。

【0164】

なお、本発明における電子キャリア濃度の下限としては、得られる酸化物膜をどのような素子や回路あるいは装置に用いるかにもよるが、例えば1014/cm3以上である。

【0165】

(材料系の拡大)

さらに、組成系を拡大して研究を進めた結果、Zn,In及びSnのうち、少なくとも1種類の元素の酸化物からなるアモルファス酸化物で、電子キャリア濃度が小さく、かつ電子移動度が大きいアモルファス酸化物膜を作製できることを見出した。

【0166】

また、このアモルファス酸化物膜は、伝導電子数の増加と共に、電子移動度が大きくなるという特異な特性を有することを見出した。

【0167】

その膜を用いてTFTを作成し、オン・オフ比、ピンチオフ状態での飽和電流、スイッチ速度などのトランジスタ特性に優れたノーマリーオフ型のTFTを作成できる。

【0168】

本発明には、以下(a)から(h)の特徴を有する酸化物を用いることができる。

(a) 室温での電子キャリア濃度が、1018/cm3未満のアモルファス酸化物。

(b) 電子キャリア濃度が増加すると共に、電子移動度が増加することを特徴とするアモルファス酸化物。

【0169】

なおここで、室温とは0℃から40℃程度の温度をいう。アモルファスとは、X線回折スペクトルにおいて、ハローパターンのみが観測され、特定の回折線を示さない化合物をいう。また、ここでの電子移動度は、ホール効果測定で得られる電子移動度をいう。

(c) 室温での電子移動度が、0.1cm2/V・秒超であることを特徴とする上記(a)又は(b)に記載されるアモルファス酸化物。

(d) 縮退伝導を示す上記(b)から(c)のいずれかに記載されるアモルファス酸化物である。なお、ここでの縮退伝導とは、電気抵抗の温度依存性における熱活性化エネルギーが、30meV以下の状態をいう。

(e) Zn,In及びSnのうち、少なくとも1種類の元素を構成成分として含む上記(a)から(d)のいずれかに記載されるアモルファス酸化物。

(f) 上記(e)に記載のアモルファス酸化物に、Znより原子番号の小さい2族元素M2(M2は、Mg,Ca)、Inより原子番号の小さい3属元素M3(M3は、B,Al、Ga、Y),Snより小さい原子番号の小さい4属元素M4(M4は、Si,Ge,Zr)、5属元素M5(M5は、V,Nb,Ta)およびLu、Wのうち、少なくとも1種類の元素を含むアモルファス酸化物膜。

(g) 結晶状態における組成がIn1−xM3xO3(Zn1−yM2yO)m(0≦x、y≦1、mは0又は6未満の自然数)である化合物単体又はmの異なる化合物の混合体である(a)から(f)のいずれかに記載のアモルファス酸化物膜。M3は例えば、Gaであり、M2は例えば、Mgである。

(h) ガラス基板、金属基板、プラスチック基板又はプラスチックフィルム上に設けた上記(a)から(g)記載のアモルファス酸化物膜。

【0170】

また、本発明は、(10)上記記載のアモルファス酸化物、又はアモルファス酸化物膜をチャネル層に用いた電界効果型トランジスタである。

【0171】

なお、電子キャリア濃度が1018/cm3未満、1015/cm3超のアモルファス酸化物膜をチャネル層に用い、ソース端子、ドレイン端子及びゲート絶縁膜を介してゲート端子を配した電界効果型トランジスタを構成する。ソース・ドレイン端子間に5V程度の電圧を印加したとき、ゲート電圧を印加しないときのソース・ドレイン端子間の電流を約10−7アンペヤにすることができる。

【0172】

酸化物結晶の電子移動度は、金属イオンのs軌道の重なりが大きくなるほど、大きくなり、原子番号の大きなZn,In,Snの酸化物結晶は、0.1から200cm2/(V・秒)の大きな電子移動度を持つ。

【0173】

さらに、酸化物では、酸素と金属イオンとがイオン結合している。

【0174】

そのため、化学結合の方向性がなく、構造がランダムで、結合の方向が不均一なアモルファス状態でも、電子移動度は、結晶状態の電子移動度に比較して、同程度の大きさを有することが可能となる。

【0175】

一方で、Zn,In,Snを原子番号の小さな元素で置換することにより、電子移動度は小さくなる、こうした結果により、本発明のよるアモルファス酸化物の電子移動度は、約0.01cm2/(V・秒)から20cm2/(V・秒)である。

【0176】

上記酸化物を用いてトランジスタのチャネル層を作製する場合、トランジスタにおいて、Al2O3,Y2O3、HfO2、又はそれらの化合物を少なくとも二つ以上含む混晶化合物をゲート絶縁膜とすることが好ましい。

【0177】

ゲート絶縁薄膜とチャネル層薄膜との界面に欠陥が存在すると、電子移動度の低下及びトランジスタ特性にヒステリシスが生じる。また、ゲート絶縁膜の種類により、リーク電流が大きく異なる。このために、チャネル層に適合したゲート絶縁膜を選定する必要がある。Al2O3膜を用いれば、リーク電流を低減できる。また、Y2O3膜を用いればヒステリシスを小さくできる。さらに、高誘電率のHfO2膜を用いれば、電界効果移動度を大きくすることができる。また、これらの化合物の混晶からなる膜を用いて、リーク電流、ヒステリシスが小さく、電界効果移動度の大きなTFTを形成できる。また、ゲート絶縁膜形成プロセス及びチャネル層形成プロセスは、室温で行うことができるので、TFT構造として、スタガ構造及び逆スタガ構造いずれをも形成することができる。

【0178】

In2O3酸化物膜は、気相法により成膜でき、成膜中の雰囲気に水分を、0.1Pa程度添加することにより、アモルファス膜が得られる。

【0179】

また、ZnO及びSnO2は、アモルファス膜を得ることは難しいが、In2O3を、ZnOの場合には20原子量%程度、SnO2の場合には、90原子量%程度添加することによりアモルファス膜を得ることができる。特に、Sn−In―O系アモルファス膜を得るためには、雰囲気中に窒素ガスを0.1Pa程度導入すればよい。

【0180】

上記のアモルファス膜に、Znより原子番号の小さい2族元素M2(M2は、Mg,Ca)、Inより原子番号の小さい3属元素M3(M3は、B,Al、Ga、Y),Snより小さい原子番号の小さい4属元素M4(M4は、Si,Ge,Zr)、5属元素M5(M5は、V,Nb,Ta)およびLu、Wのうち、少なくとも1種類の複合酸化物を構成する元素を添加できる。

【0181】

それにより、室温での、アモルファス膜をより安定化させることができる。また、アモルファス膜が得られる組成範囲を広げることができる。

【0182】

特に、共有結合性の強い、B,Si,Geの添加は、アモルファス相安定化に有効であるし、イオン半径の差の大きいイオンから構成される複合酸化物は、アモルファス相が安定化する。

【0183】

たとえば、In−Zn−O系では、Inが約20原子%超の組成範囲でないと、室温で安定なアモルファス膜は得難いが、MgをInと当量添加することにより、Inが約15原子量%超の組成範囲で、安定なアモルファス膜を得ることができる。

【0184】

気相法による成膜において、雰囲気を制御することにより、電子キャリア濃度が、1018/cm3未満、1015/cm3超のアモルファス酸化膜を得ることができる。

【0185】

アモルファス酸化物の成膜方法としては、パルスレーザー蒸着法(PLD法)、スパッタ法(SP法)及び電子ビーム蒸着法などの気相法を用いるのがよい。気相法の中でも、材料系の組成を制御しやすい点では、PLD法が、量産性の点からは、SP法が適している。しかし、成膜法は、これらの方法に限られるのものではない。

【0186】

(PLD法によるIn−Zn−Ga−O系アモルファス酸化膜の成膜)

KrFエキシマレーザーを用いたPLD法により、ガラス基板(コーニング社製1737)上にIn−Zn―Ga―O系アモルファス酸化物膜を堆積させた。このとき、InGaO3(ZnO)及びInGaO3(ZnO)4組成を有する多結晶焼結体をそれぞれターゲットとした。

【0187】

成膜装置は、既述の図48に記載されている装置を用い、成膜条件は、当該装置を用いた場合と同様とした。

【0188】

基板温度は25℃である。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、2種類のターゲットから作製したIn−Zn−Ga−O系膜は、いずれもアモルファス膜であることが示された。

【0189】

さらに、ガラス基板上のIn−Zn―Ga―O系アモルファス酸化物膜のX線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。

【0190】

蛍光X線(XRF)分析の結果、InGaO3(ZnO)組成を有する多結晶焼結体をターゲットとして得られた膜の金属組成比はIn:Ga:Zn=1.1:1.1:0.9であった。また、InGaO(ZnO)4組成を有する多結晶焼結体をターゲットとして得られた膜の金属組成比は、In:Ga:Zn=0.98:1.02:4であった。

【0191】

成膜時の雰囲気の酸素分圧を変化させ、InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜の電子キャリア濃度を測定した。その結果を図1に示す。酸素分圧が4.2Pa超の雰囲気中で成膜することにより、電子キャリア濃度を1018/cm3未満に低下させることができた。この場合、基板の温度は意図的に加温しない状態でほぼ室温に維持されている。また、酸素分圧が6.5Pa未満の時は、得られたアモルファス酸化物膜の表面は平坦であった。

【0192】

酸素分圧が5Paの時、InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜の電子キャリア濃度は1016/cm3、電気伝導度は、10−2S/cmであった。また、電子移動度は、約5cm2/V・秒と推測された。光吸収スペクトルの解析から、作製したアモルファス酸化物膜の禁制帯エネルギー幅は、約3eVと求まった。

【0193】

酸素分圧をさらに大きくすると、電子キャリア濃度をさらに低下させることができた。図1に示す様に、基板温度25℃、酸素分圧6Paで成膜したIn−Zn−Ga−O系アモルファス酸化物膜では、電子キャリア濃度を8×1015/cm3(電気伝導:約8×10−3S/cm)に低下させることができた。得られた膜は、電子移動度が1cm2/(V・秒)超と推測された。しかし、PLD法では、酸素分圧を6.5Pa以上にすると、堆積した膜の表面が凸凹となり、TFTのチャネル層として用いることが困難となった。

【0194】

InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとし、異なる酸素分圧で成膜したIn−Zn−Ga−O系アモルファス酸化物膜に関して、電子キャリア濃度と電子移動度の関係を調べた。その結果を図2に示す。電子キャリア濃度が、1016/cm3から1020/cm3に増加すると、電子移動度は、約3cm2/(V・秒)から約11cm2/(V・秒)に増加することが示された。また、InGaO3(ZnO)組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜に関しても、同様の傾向が見られた。

【0195】

ガラス基板の代わりに厚さ200μmのポリエチレン・テレフタレート(PET)フィルムを用いた場合にも、得られたIn−Zn−Ga−O系アモルファス酸化物膜は、同様の特性を示した。

(PLD法によるIn−Zn−Ga−Mg−O系アモルファス酸化物膜の成膜)

ターゲットとして多結晶InGaO3(Zn1−xMgxO)4(0<x≦1)を用い、PLD法により、ガラス基板上にInGaO3(Zn1−xMgxO)4(0<x≦1)膜を成膜した。

【0196】

成膜装置は、図48に記載の装置を用いた。

【0197】

被成膜基板としては、SiO2ガラス基板(コーニング社製1737)を用意した。その基板に前処理として、超音波脱脂洗浄を、アセトン、エタノール、超純水により各5分間ずつ行った後、空気中100℃で.乾燥させた。ターゲットとしては、InGa(Zn1−xMgxO)4(x=1−0)焼結体(サイズ20mmΦ5mmt)を用いた。

【0198】

ターゲットは、出発原料In2O3:Ga2O3:ZnO:MgO(各4N試薬)を、湿式混合(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て作製した。

【0199】

成長室到達真空は、2×10−6(Pa)であり、成長中の酸素分圧は、0.8(Pa)とした。基板温度は、室温(25℃)で行い、ターゲットと被成膜基板間の距離は、30(mm)であった。

【0200】

なお、KrFエキシマレーザーのパワーは、1.5(mJ/cm2/pulse)、パルス幅は、20(nsec)、繰り返し周波数は、10(Hz)、照射スポット径は、1×1(mm角)とした。成膜レートは、7(nm/min)であった。

【0201】

雰囲気は酸素分圧0.8Paで、基板温度は25℃である。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−Zn−Ga−Mg−O系膜はアモルファス膜であることが示された。得られた膜の表面は平坦であった。

【0202】

異なるx値のターゲットを用いて、酸素分圧0.8Paの雰囲気中で成膜したIn−Zn−Ga−Mg−O系アモルファス酸化物膜の電気伝導度、電子キャリア濃度及び電子移動度のx値依存性を調べた。

【0203】

その結果を、図4に示す。x値が0.4超のとき、酸素分圧0.8Paの雰囲気中で、PLD法により成膜したアモルファス酸化物膜では、電子キャリア濃度を1018/cm3未満にできることが示された。また、x値が0.4超のアモルファス酸化物膜では、電子移動度は、1cm2/V・秒超であった。

【0204】

図4に示すように、Znを80原子%のMgで置換したターゲットを使用した場合、酸素分圧0.8Paの雰囲気で、パルスレーザー堆積法で得られた膜の電子キャリア濃度を1016/cm3未満とすることができる(電気抵抗値は、約10−2S/cmである。)。こうした膜の電子移動度は、Mg無添加膜に比べて低下するが、その程度は少なく、室温での電子移動度は約5cm2/(V・秒)で、アモルファスシリコンに比べて、1桁程度大きな値を示す。同じ条件で成膜した場合、Mg含有量の増加に対して、電気伝導度と電子移動度は、共に低下するので、Mgの含有量は、好ましくは、20原子%超、85原子%未満(xにして、0.2<x<0.85)、より好適には0.5<x<0.85である。

【0205】

ガラス基板の代わりに厚さ200μmのポリエチレン・テレフタレート(PET)フィルムを用いた場合にも、得られたInGaO3(Zn1−xMgxO)4(0<x≦1)アモルファス酸化物膜は、同様の特性を示した。

【0206】

(PLD法によるIn2O3アモルファス酸化物膜の成膜)

KrFエキシマレーザーを用いたPLD法により、In2O3多結晶焼結体をターゲットとして、厚さ200μmのPETフィルム上にIn2O3膜を成膜した。

【0207】

装置は、図48に示した装置を用いた。被成膜基板として、SiO2ガラス基板(コーニング社製1737)を用意した。

【0208】

この基板の前処理として、超音波脱脂洗浄を、アセトン、エタノール、超純水で各5分間ずつ行った後、空気中100℃で乾燥させた。

【0209】

ターゲットとしては、In2O3焼結体(サイズ20mmΦ5mmt)を用いた。これは、出発原料In2O3(4N試薬)を仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て準備した。

【0210】

成長室到達真空は、2×10−6(Pa)、成長中の酸素分圧は、5(Pa)、基板温度は室温とした。

【0211】

酸素分圧は5Pa、水蒸気分圧は0.1Paとし、さらに、酸素ラジカル発生装置に200Wを印加して、酸素ラジカルを発生させた。

【0212】

ターゲットと被成膜基板間の距離は、40(mm)、KrFエキシマレーザーのパワーは0.5(mJ/cm2/pulse)、パルス幅は、20(nsec)、繰り返し周波数は、10(Hz)、照射スポット径は1×1(mm角)であった。成膜レートは、3(nm/min)であった。

【0213】

得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−O系膜はアモルファス膜であることが示された。膜厚は、80nmであった。

【0214】

得られたIn−O系アモルファス酸化物膜の電子キャリア濃度は5×1017/cm3で、電子移動度は、約7cm2/V・秒であった。

【0215】

(PLD法によるIn−Sn−O系アモルファス酸化物膜の成膜)

KrFエキシマレーザーを用いたPLD法により、(In0.9Sn0.1)O3.1多結晶焼結体をターゲットとして、厚さ200μmのPETフィルム上にIn−Sn−O系酸化物膜を成膜した。

【0216】

具体的には、被成膜基板として、SiO2ガラス基板(コーニング社製1737)を用意した。

【0217】

基板前処理として、超音波脱脂洗浄をアセトン、エタノール、超純水を用いて各5分間ずつ行った。その後、空気中100℃で乾燥させた。

【0218】

ターゲットは、In2O3−SnO2焼結体(サイズ20mmΦ5mmt)を準備した。これは、出発原料として、In2O3−SnO2(4N試薬)を湿式混合(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て得られる。

【0219】

基板温度は室温である。酸素分圧は5(Pa)、窒素分圧は、0.1(Pa)とし、さらに、酸素ラジカル発生装置に200Wを印加して、酸素ラジカルを発生させた。

【0220】

ターゲットと被成膜基板間の距離は、30(mm)とし、KrFエキシマレーザーのパワーは、1.5(mJ/cm2/pulse)、パルス幅は、20(nsec)であった、また、繰り返し周波数は、10(Hz)、照射スポット径は、1×1(mm角)であった。成膜レートは、6(nm/min)であった。

【0221】

得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−Sn−O系膜はアモルファス膜であることが示された。

【0222】

得られたIn−Sn−Oアモルファス酸化物膜の電子キャリア濃度は、8×1017/cm3で、電子移動度は、約5cm2/V・秒であった。膜厚は、100nmであった。

【0223】

(PLD法によるIn−Ga−O系アモルファス酸化物膜の成膜)

被成膜基板として、SiO2ガラス基板(コーニング社製1737)を用意した。

【0224】

基板の前処理として、超音波脱脂洗浄をアセトン、エタノール、超純水を用いて、各5分間行った後、空気中100℃で.乾燥させた。

【0225】

ターゲットとして、(In2O3)1−x−(Ga2O3)x(X=0−1)焼結体(サイズ20mmΦ5mmt)を用意した。なお、例えばx=0.1の場合は、ターゲットは、(In0.9Ga0.1)2O3多結晶焼結体ということになる。

【0226】

これは、出発原料:In2O3−Ga2O2(4N試薬)を、湿式混合(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て得られる。

【0227】

成長室到達真空は、2×10−6(Pa)であり、成長中の酸素分圧は、1(Pa)とした。

【0228】

基板温度は、室温で行い、ターゲットと被成膜基板間の距離は、30(mm)、KrFエキシマレーザーのパワーは、1.5(mJ/cm2/pulse)であった。また、パルス幅は、20(nsec)、繰り返し周波数は、10(Hz)、照射スポット径は、1×1(mm角)であった。成膜レートは、6(nm/min)であった。

【0229】

基板温度は25℃である。酸素分圧は1Paであった。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−Ga−O系膜はアモルファス膜であることが示された。膜厚は、120nmであった。

【0230】

得られたIn−Ga−Oアモルファス酸化物膜の電子キャリア濃度は、8×1016/cm3で、電子移動度は、約1cm2/V・秒であった。

(In−Zn−Ga−O系アモルファス酸化物膜を用いたTFT素子の作製(ガラス基板))

【0231】

TFT素子の作製

図5に示すトップゲート型TFT素子を作製した。

【0232】

まず、ガラス基板(1)上に、InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとし、酸素分圧5Paの条件で、前述したPLD装置を用いて、In−Ga−Zn−O系アモルファス酸化物膜を作製した。チャンネル層(2)として用いる厚さ120nmのIn−Ga−Zn−O系アモルファス膜を形成した。

【0233】

さらにその上に、チャンバー内の酸素分圧を1Pa未満にして、PLD法により電気伝導度の大きなIn−Ga−Zn−O系アモルファス膜及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。

【0234】

最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜した(厚み:90nm、比誘電率:約15、リーク電流密度:0.5MV/cm印加時に10−3A/cm2)。その上に金を成膜し、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。チャネル長は、50μmで、チャネル幅は、200μmであった。

【0235】

TFT素子の特性評価

図6に、室温下で測定したTFT素子の電流−電圧特性を示す。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型伝導であることが分かる。

【0236】

これは、アモルファスIn−Ga−Zn−O系アモルファス酸化物膜がn型伝導体であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的な半導体トランジスタの挙動を示した。利得特性を調べたところ、VDS=4V印加時におけるゲート電圧VGSの閾値は約−0.5Vであった。

【0237】

また、VG=10V時には、IDS=1.0×10−5Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Ga−Zn−O系アモルファス酸化物膜内にキャリアを誘起できたことに対応する。

【0238】

トランジスタのオン・オフ比は、103超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約7cm2(Vs)−1の電界効果移動度が得られた。作製した素子に可視光を照射して同様の測定を行なったが、トランジスタ特性の変化は認められなかった。

【0239】

なお、アモルファス酸化物の電子キャリア濃度を1018/cm3未満にすることでTFTのチャネル層として適用できる。この電子キャリア濃度としては、1017/cm3以下がより好ましく、1016/cm3以下にすると更に好ましかった。

【0240】

(In−Zn−Ga−O系アモルファス酸化物膜を用いたTFT素子の作製(アモルファス基板))

図5に示すトップゲート型TFT素子を作製した。まず、ポリエチレン・テレフタレート(PET)フィルム(1)上に、PLD法により、チャンネル層(2)として用いる厚さ120nmのIn−Zn−Ga−O系アモルファス酸化物膜を形成した。このとき、InGaO3(ZnO)組成を有する多結晶焼結体をターゲットとし、酸素分圧5Paの雰囲気で成膜を行った。

【0241】

さらにその上に、チャンバー内酸素分圧を1Pa未満にして、PLD法により電気伝導度の大きなIn−Zn−Ga−O系アモルファス酸化物膜及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)を電子ビーム蒸着法により成膜して、その上に金を成膜した。そして、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。チャネル長は、50μmで、チャネル幅は、200μmであった。ゲート絶縁膜として、Y2O3(厚さ:140nm),Al2O3(厚さ:130μm)及びHfO2(厚さ:140μm)を用いた3種類の上記の構造を有するTFTを作成した。

【0242】

TFT素子の特性評価

PETフィルム上に形成したTFTの室温下で測定した電流−電圧特性は、図6と同様であった。すなわち、ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことから、チャネルがn型伝導であることが分かる。これは、アモルファスIn−Ga−Zn−O系アモルファス酸化物膜がn型伝導体であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的なトランジスタの挙動を示した。また、Vg=0のときには、Ids=10−8A,Vg=10V時には、IDS=2.0×10−5Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Ga−Zn−O系アモルファス酸化物膜内に電子キャリアを誘起できたことに対応する。

【0243】

トランジスタのオン・オフ比は、103超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約7cm2(Vs)−1の電界効果移動度が得られた。

【0244】

PETフィルム上に作成した素子を、曲率半径30mmで屈曲させ、同様のトランジスタ特性の測定を行ったが、トランジスタ特性に変化は認められなかった。また、可視光を照射して同様の測定を行なったが、トランジスタ特性の変化は認められなかった。

【0245】

ゲート絶縁膜としてAl2O3膜を用いたTFTでも、図6に示したものと類似のトランジスタ特性を示したが、Vg=0のときには、Ids=10−8A,Vg=10V時には、IDS=5.0×10−6Aの電流が流れた。トランジスタのオン・オフ比は、102超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約2cm2(Vs)−1の電界効果移動度が得られた。

【0246】

ゲート絶縁膜としてHfO2膜を用いたTFTでも、図6に示したものと類似のトランジスタ特性を示したが、Vg=0のときには、Ids=10−8A,Vg=10V時には、IDS=1.0×10−6Aの電流が流れた。トランジスタのオン・オフ比は、102超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約10cm2(Vs)−1の電界効果移動度が得られた。

【0247】

(PLD法によるIn2O3アモルファス酸化物膜を用いたTFT素子の作成)

図5に示すトップゲート型TFT素子を作製した。まず、ポリエチレン・テレフタレート(PET)フィルム(1)上に、PLD法により、チャンネル層(2)として用いる厚さ80nmのIn2O3アモルファス酸化物膜を形成した。

【0248】

さらにその上に、チャンバー内酸素分圧を1Pa未満にして、さらに酸素ラジカル発生装置への印加電圧をゼロにして、PLD法により、電気伝導度の大きなIn2O3アモルファス酸化物膜及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜して、その上に金を成膜した。そして、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。

【0249】

TFT素子の特性評価

PETフィルム上に形成したTFTの室温下で測定した電流−電圧特性を測定した。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型半導体であることが分かる。これは、In−O系アモルファス酸化物膜がn型伝導体であるという事実と矛盾しない。IDSはVDS=5V程度で飽和(ピンチオフ)する典型的なトランジスタの挙動を示した。また、Vg=0V時には、2×10−8A、VG=10V時には、IDS=2.0×10−6Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−O系アモルファス酸化物膜内に電子キャリアを誘起できたことに対応する。

【0250】

トランジスタのオン・オフ比は、約102であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約10cm2(Vs)−1の電界効果移動度が得られた。ガラス基板上に作成したTFT素子も同様の特性を示した。

【0251】

PETフィルム上に作成した素子を、曲率半径30mmで曲げ、同様のトランジスタ特性の測定を行ったが、トランジスタ特性に変化は認められなかった。

【0252】

(PLD法によるIn−Sn−O系アモルファス酸化物膜を用いたTFT素子の作成)

図5に示すトップゲート型TFT素子を作製した。まず、ポリエチレン・テレフタレート(PET)フィルム(1)上に、PLD法により、チャンネル層(2)として用いる厚さ100nmのIn−Sn−O系アモルファス酸化物膜を形成した。さらにその上に、チャンバー内酸素分圧を1Pa未満にして、さらに酸素ラジカル発生装置への印加電圧をゼロにして、PLD法により、電気伝導度の大きなIn−Sn−O系アモルファス酸化物膜及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜し、その上に金を成膜して、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。

【0253】

TFT素子の特性評価

PETフィルム上に形成したTFTの室温下で測定した電流−電圧特性を測定した。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型半導体であることが分かる。これは、In−Sn−O系アモルファス酸化物膜がn型伝導体であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的なトランジスタの挙動を示した。また、Vg=0V時には、5×10−8A、VG=10V時には、IDS=5.0×10−5Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Sn−O系アモルファス酸化物膜内に電子キャリアを誘起できたことに対応する。

【0254】

トランジスタのオン・オフ比は、約103であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約5cm2(Vs)−1の電界効果移動度が得られた。ガラス基板上に作成したTFT素子も同様の特性を示した。

【0255】

PETフィルム上に作成した素子を、曲率半径30mmで曲げ、同様のトランジスタ特性の測定を行ったが、トランジスタ特性に変化は認められなかった。

【0256】

(PLD法によるIn−Ga−O系アモルファス酸化物膜を用いたTFT素子の作成)

図5に示すトップゲート型TFT素子を作製した。まず、ポリエチレン・テレフタレート(PET)フィルム(1)上に、実施例6に示した成膜法により、チャンネル層(2)として用いる厚さ120nmのIn−Ga−O系アモルファス酸化物膜を形成した。さらにその上に、チャンバー内の酸素分圧を1Pa未満にして、さらに酸素ラジカル発生装置への印加電圧をゼロにして、PLD法により、電気伝導度の大きなIn−Ga−O系アモルファス酸化物膜及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜し、その上に金を成膜して、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。

【0257】

TFT素子の特性評価

PETフィルム上に形成したTFTの室温下で測定した電流−電圧特性を測定した。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型半導体であることが分かる。これは、In−Ga−O系アモルファス酸化物膜がn型伝導体であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的なトランジスタの挙動を示した。また、Vg=0V時には、1×10−8A、VG=10V時には、IDS=1.0×10−6Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Ga−O系アモルファス酸化物膜内に電子キャリアを誘起できたことに対応する。

【0258】

トランジスタのオン・オフ比は、約102であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約0.8cm2(Vs)−1の電界効果移動度が得られた。ガラス基板上に作成したTFT素子も同様の特性を示した。

【0259】

PETフィルム上に作成した素子を、曲率半径30mmで曲げ、同様のトランジスタ特性の測定を行ったが、トランジスタ特性に変化は認められなかった。

【0260】

なお、アモルファス酸化物の電子キャリア濃度を1018/cm3未満にすることでTFTのチャネル層として適用できる。この電子キャリア濃度としては、1017/cm3以下がより好ましく、1016/cm3以下にすると更に好ましかった。

【0261】

(実施例1:上記透明膜を用いたSIT素子)

図7に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法によりITO薄膜を30nm形成し、フォトリソグラフィー法とリフトオフ法により、ドレイン電極11−1をパターニングする。続いて、上記方法によりIn−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成した。そして、フォトリソグラフィー法とリフトオフ法により、上記電極11−1上に上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。その後、電極12として、パルスレーザー堆積法により、Pt薄膜を30nm形成し、上記半導体膜上で、くし歯状になるように、フォトリソグラフィー法とリフトオフ法でパターニングする。さらに、上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法にて30nm形成した。そして、上記ゲート電極12を覆うように、フォトリソグラフィー法とリフトオフ法により、上記In−Ga−Zn−O系アモルファスN型半導体膜をパターニングする。但し、上記半導体膜は、上記ドレイン電極上に形成した半導体膜よりも、キャリア密度と伝導度が高いものが好ましく、キャリア密度が1018/cm3以上のものでも良い。最後に、上記In−Ga−Zn−O系アモルファスN型半導体上にITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングすることでソース電極11−2を形成する。上記手段により、SIT素子が作製できる(図7)。

【0262】

上記SIT素子のドレイン電極−ソース電極間に流れる電流は、上記ゲート電極12に印加される電圧に従って形成されるポテンシャル障壁を、上記ドレイン電極−ソース電極間に印加される電圧によりどれだけ下げられるかによって決まる。又、上記SIT素子は、キャリアを電子とする多数キャリアデバイスであり、また、上記ドレイン−ソース間も狭いため、TFTに比べ大きな電流を流す事ができる。

【0263】

上記SIT素子において、上記ゲート電極12を形成するPtに代わり、フェルミ準位の絶対値が、In−Ga−Zn−O系アモルファスN型半導体のフェルミ準位の絶対値よりも大きなP型半導体14を用いて、同様なSIT素子の作製が可能である(図8)。

【0264】

又、同じ機能のSIT素子でも図9、図10に示したような構成も可能である。

【0265】

(実施例2:上記透明膜を用いたSBT素子)

図11に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法により上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成した。そして、フォトリソグラフィー法とリフトオフ法により、パターニングされた上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。続いて、上記半導体膜上に、上記In−Ga−Zn−O系アモルファスN型半導体13を30nmさらに形成した。そして、フォトリソグラフィー法とリフトオフ法で、ゲート電極に相当する所が凹形状になるようにパターニングする。その後、上記ゲート電極12として、パルスレーザー堆積法により、Pt薄膜を30nm形成し、上記半導体膜の凹部に、フォトリソグラフィー法とリフトオフ法でパターニングする。さらに、上記In−Ga−Zn−O系アモルファスN型半導体の凸部に、ITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングすることで、ドレイン電極11−1、ソース電極11−2を形成する。上記手段により、SBT素子が作製できる(図11)。

【0266】

ここで、上記ゲート、ドレインとソース電極の作製順を入れ替えても良い。

【0267】

上記SBT素子のドレイン電極−ソース電極間に流れる電流は、上記ゲート電極2に印加される電圧に従って形成される空乏領域の大きさが変わるため、上記ドレイン電極−ソース電極間の電流経路のサイズが増減することにより決まる。上記SBT素子は、TFTと異なり、絶縁層が必要ないため、簡単な素子構造で形成できる利点がある。

【0268】

(実施例3:上記透明膜を用いたPN−T素子の作製)

図12に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法により上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成した。そして、フォトリソグラフィー法とリフトオフ法により、パターニングされた上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。続いて、上記半導体膜上に、上記In−Ga−Zn−O系アモルファスN型半導体13を30nmさらに形成し、フォトリソグラフィー法とリフトオフ法で、ゲート電極に相当する所が凹形状になるようにパターニングする。その後、半導体膜の凹部に、フェルミ準位の絶対値が、上記In−Ga−Zn−O系アモルファスN型半導体のフェルミ準位の絶対値よりも大きなP型半導体膜14をパルスレーザー堆積法、フォトリソグラフィー法、リフトオフ法にて30nm形成する。さらに、上記ゲート電極12として、パルスレーザー堆積法によりPt薄膜を30nm形成し、上記P型半導体膜上にフォトリソグラフィー法とリフトオフ法でパターニングする。最後に、上記In−Ga−Zn−O系アモルファスN型半導体の凸部に、ITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングすることで、ドレイン電極11−1、ソース電極11−2を形成する。上記手段により、PN−T素子が作製できる(図12)。

【0269】

ここで、上記ゲート、ドレインとソース電極の作製順を入れ替えても良い。

【0270】

上記PN−T素子のドレイン電極−ソース電極間に流れる電流は、上記ゲート電極2に印加される電圧に従って、上記N型半導体内に形成される空乏領域の大きさが変わるため、上記ドレイン電極−ソース電極間の電流経路のサイズが増減することにより決まる。上記PN−T素子は、TFTと異なり、絶縁層が必要ないという利点がある。

【0271】

(実施例4:上記透明膜を用いたSD素子)

図13に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法により上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成する。そして、フォトリソグラフィー法とリフトオフ法により、パターニングされた上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。続いて、上記半導体上に、電極12として、パルスレーザー堆積法により、Pt薄膜を30nm形成し、フォトリソグラフィー法とリフトオフ法でパターニングする。さらに、上記半導体上に、電極11として、パルスレーザー法でITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングする。上記手段により、SD素子が作製できる(図13)。

【0272】

ここで、上記電極11と電極12の作製順を入れ替えても良い。

【0273】

上記SD素子は、上記電極12と上記半導体膜13の間でショットキー障壁が形成されることで、整流性を持つようになる。

【0274】

(実施例5:上記透明膜を用いたPN−D素子)

図14に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法により上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成する。そして、フォトリソグラフィー法とリフトオフ法により、パターニングされた上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。続いて、上記半導体上に、フェルミ準位の絶対値が、上記In−Ga−Zn−O系アモルファスN型半導体のフェルミ準位の絶対値よりも大きなP型半導体膜14を、パルスレーザー堆積法により30nm形成する。そして、フォトリソグラフィー法とリフトオフ法でパターニングする。さらに、上記P型半導体上に、電極12として、パルスレーザー法でPtを30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングする。最後に、上記N型半導体上に、電極11として、パルスレーザー法でITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングする。上記手段により、PN−D素子が作製できる(図14)。

【0275】

ここで、上記電極11と電極12の作製順を入れ替えても良い。

【0276】

上記PN−D素子は、上記半導体膜13と上記半導体膜14の間でPN接合が形成されることで、整流性を持つようになる。

【0277】

(実施例6:上記透明膜を用いた抵抗素子)

図15に示すように、ガラス、プラスチックなどの絶縁基板10上に、パルスレーザー堆積法により上記In−Ga−Zn−O系アモルファスN型半導体13をパルスレーザー堆積法により30nm形成した。フォトリソグラフィー法とリフトオフ法により、パターニングされた上記In−Ga−Zn−O系アモルファスN型半導体膜を形成する。続いて、上記N型半導体上に、電極11−1、11−2として、パルスレーザー法でITO膜を30nm形成し、フォトリソグラフィー法とリフトオフ法によりパターニングする。上記手段により、透明な抵抗素子が作製できる(図15)。

【0278】

又、上記抵抗素子は、上記電極11−1、11−2と上記半導体膜13の間に上記半導体膜と異なるキャリア密度、伝導度であるIn−Ga−Zn−O系アモルファスN型半導体13’を備えても良い(図16)。

【0279】

以下では、特に断りの無い限り、N−TFTとする場合、上記透明膜を用いたノーマリーオフ(エンハンスメント形)のMISFETである。

【0280】

(実施例7:上記透明膜を活性層とするTFTを使用したインバータ回路)

N型半導体である上記透明膜を活性層とするN−TFT1,2を電源−GND間に直列に接続する。そして、ドレインが電源に接続しているN−TFT2のゲートを電源と接続し、ソースがGNDに接地しているN−TFT1のゲートを入力、ドレインを出力とすることでインバータ回路が実現する(図17)。

【0281】

また、上記N−TFT2に代わり、上記透明膜を抵抗として用いてもインバータ回路を構成することが可能である(図18)。

【0282】

また、上記インバータよりも、出力立ち上がり能力を上げる方法として、N−TFT2の代わりに、ゲート−ソース間をショートしたN型のデプレッション形トランジスタ(以下、N−DTFT)N−DTFT1を用いることができる(図19)。

【0283】

上記のインバータ回路では、入力がハイレベルの場合の出力はローレベルとなるが、その電圧は、上記N−TFT1とN−TFT2(又は、抵抗、N−DTFT1)との分圧で決まる。そのため、ローレベルを出力するには、N−TFT1に比べ、N−TFT2の電流能力を下げる。その結果、出力の充電能力が低くなる。出力の充電能力を高めるには図20、21に示すインバータ回路を用いる。この回路は、上記インバータの出力をゲートとし、電源をドレインとするN−TFT4と、上記N−TFT4のソースとGND間に有り、インバータの入力がゲートであるN−TFT3を備える。そして、この回路は上記N−TFT3のドレインを出力とする2段型のインバータ回路(図20、21)である。この2段型のインバータ回路の場合、上記N−TFT4は、ソースフォロワ構成であり、出力の充電能力を高めることができる。

【0284】

また、2段型インバータ回路例として図47という構成も可能である。

【0285】

さらに、上記インバータ回路において、上記N−TFT2、抵抗、N−DTFT1に代わり、P型半導体を活性層とするP型TFT(P−TFT1)を用いることで、静的な貫通電流が無く、駆動能力が高い相補的インバータ回路が構成できる(図22)。

【0286】

P型半導体としては、Si等の無機半導体、ペンタセン・ポリチオフェン等の有機半導体、酸化物半導体が考えられる。しかし、TFTとしてボトムゲート構造が可能ならば、プロセスの簡易性からは、マスク蒸着やインクジェットで可能な有機半導体を用いることで、簡便に上記相補的インバータの構成が可能である。一方、P型の酸化物半導体で、上記相補的インバータを作製した場合、半導体部が透明な回路を作製できる利点がある。

【0287】

(実施例8:上記透明膜を活性層とするTFTを使用したNAND、NOR回路)

N型半導体である上記透明膜を活性層とするN−TFT1,2を用いたインバータのN−TFT1のソースとGND間にN−TFT3を挿入する。そして、N−TFT1のゲートを第一の入力(IN1)、N−TFT3のゲートを第二の入力(IN2)とする。こうして、NAND回路を構成することができる(図23)。

【0288】

また、上記インバータと同様にN−TFT2に代わり、ゲート−ソース間をショートしたN−DTFT1(図24)、あるいは抵抗を用いてもNAND回路の構成が可能である。

【0289】

さらに、P型半導体を活性層とするP型TFTを用いた場合、N−TFT2に代わり、2つのP型TFT、P−TFT1とP−TFT2を電源と出力間に並列に接続し、それぞれのゲートをIN1、IN2とすることで、NAND回路を構成できる(図25)。

【0290】

一方、N型半導体である上記透明膜を活性層とするN−TFT1,2を用いたインバータのN−TFT1に並列に、N−TFT3を挿入し、N−TFT1のゲートを第一の入力(IN1)、N−TFT3のゲートを第二の入力(IN2)とすることで、NOR回路を構成することができる(図26)。

【0291】

また、上記インバータと同様にN−TFT2に代わり、ゲート−ソース間をショートしたN−DTFT1(図27)、あるいは抵抗を用いてもNOR回路の構成が可能である。

【0292】

さらに、P型半導体を活性層とするP型TFTを用いた場合には、N−TFT2に代わり、2つのP型TFT、P−TFT1とP−TFT2を電源と出力間に直列に接続し、それぞれのゲートを上記IN1、IN2とすることで、NOR回路を構成できる(図28)。

【0293】

(実施例9:上記透明膜を活性層とするTFTを使用したクロックドインバータ、フリップフロップ、シフトレジスタ回路)

N型半導体である上記透明膜を活性層とするN−TFT1,2を用いたインバータの出力に、N−TFT3を挿入する。そして、ゲートをクロック信号(CP)で制御することで、クロック信号によって、インバータ信号を出力するか、高抵抗とするかを制御するクロックドインバータ回路が構成できる(図29)。

【0294】

上記クロックドインバータのN−TFT2は、ゲート−ソース間をショートしたN−DTFT1、あるいは抵抗を用いても回路の構成が可能である。

【0295】

さらに、P型半導体を活性層とするP型TFTを用いた場合には、N−TFT2に代わりに、ゲートを入力と接続したP−TFT1を用いることで構成できる。また、上記N−TFT3に並列にP−TFT2を挿入し、ゲートをクロックの反転信号(CPバー)で制御することで、出力電圧の振幅を大きくできる(図30)。

【0296】

また、P型TFTを用いた場合、上記構成以外に、上記P型TFTを用いたインバータ(図22)に対し、P−TFT2をPTFT−1と出力間に直列に接続し、N−TFT4をN−TFT1と出力間に直列に接続する。そして、P−TFT2のゲートをCPバー、N−TFT4のゲートをCPで制御することで、クロックドインバータを構成できる(図31)。

【0297】

上記インバータとクロックドインバータを用いることで、フリップフロップを構成することが可能となる。

【0298】

例えば、D−フリップフロップおいて、その入力INは、CPバーにより制御されるクロックドインバータ(C−INV1)にされ、上記C−INV1の出力は、インバータ(INV1)の入力に接続される。上記INV1の出力は、CPにより制御され、上記INV1の入力と出力が接続されたクロックドインバータ(C−INV2)の入力と、同じくCPにより制御されるクロックドインバータ(C−INV3)の入力に接続される。上記C−INV3の出力は、インバータ(INV2)の入力に接続される。上記INV2の出力は、CPバーにより制御され、上記INV1の入力と出力が接続されたクロックドインバータ(C−INV2)の入力に接続されると共に、D−フリップフロップの出力Qとなる(図32)。

【0299】

上記フリップフロップを用いることで、シフトレジスタが構成可能となる(図33)。

【0300】

(実施例10:上記透明膜を活性層とするTFTを使用した1ビットSRAMセル回路)

N型半導体である上記透明膜を活性層とするN−TFT、並びに、上記インバータ回路を用いて1ビットSRAMセル回路を構成できる。

【0301】

上記SRAMセル回路は、2つのインバータINV1、INV2を備える。上記2つのインバータにおいて、INV1の出力とINV2の入力、並びに、INV2の出力とINV1の入力を接続し、ゲートがワード線WLに接続される。そして、INV2の出力とビット線BLとの間に設けたN−TFT1と、ゲートが上記WLに接続され、上記INV1の出力と反転ビット線BLバーとの間に設けたN−TFT2とを備える(図34)。

【0302】

上記SRAMセル回路中のインバータには、上記実施例1に示したインバータを用いることができる。図35に上記N−TFTと抵抗を用いたインバータを採用した場合の構成、図36に上記N−TFTとP−TFTを用いたインバータを採用した場合の構成を示す。

【0303】

(実施例11:上記透明膜を活性層とするTFTを使用したNOR型ROM回路)

本実施例のNOR型ROM回路は、複数のワード線(WL1〜WL3)と、複数のビット線(BL1〜BL2)を備える。そして、上記ビット線の各々には、ワード線がゲートに接続され、ソースがGNDに接続された、ドレインが並列に接続された上記透明膜を用いたN−TFTを複数備える。ただし、上記ビット線BL1に対し、ワード線WL1に相当するN−TFTを備えておらず、また、上記ビット線BL2に対し、ワード線WL2に相当するN−TFTを備えていない(図37)。

【0304】

上記ROM回路は、まずハイレベルにプリチャージされた後、各々のワード線にハイレベル、又は、ローレベルの電圧を印加することで、特定のビット線のみがローレベル(GNDレベル)の電圧とすることができる。例えば、WL1がハイ、WL2、WL3がローの場合、BL1はハイのままであるが、BL2はローとなる。このようにワード線に相当するN−TFTの有無により、ビット線の信号レベルが決定されるという、メモリ動作が実現される。

【0305】

上記ROM回路は、上記ワード線、ビット線、N−TFTを増やすことで、より多ビットのメモリ動作が可能である。

【0306】

さらに、上記ROM回路は、各ビット線が1つのN−TFTにより放電されるNOR型であるため高速動作が可能である一方、コンタクトが数多く必要なため面積が大きい。上記NOR型ROM回路は、N−TFTを形成するか否かにより、データを記憶しているが、基板作製後、データを光(UV光)により書き込む事ができるNOR型ROM回路も実現できる。

【0307】

上記N−TFTは、上記透明膜中の酸素欠損によりキャリアを形成している。酸素を含む雰囲気中で熱アニール、例えば摂氏150℃で2時間ほど熱アニールすることで、上記透明膜中の酸素欠損を埋め、上記透明膜の伝導度が下げられ、上記N−TFTは、オンしなくなる、つまり、TFT動作しなくなる。その後、裏面より光(UV光)を当てると、上記透明膜中に酸素欠損が再生成され、上記N−TFTは、ON、つまり、TFT動作ができるようになる。

【0308】

従って、まず、全てのワード線に相当するN−TFTを形成(図38)した後、熱アニールすることで全ての上記N−TFTがONできなくなる(図39)。続いて、動作可能にしたい上記N−TFTの個所のみ光を通すマスクを準備し、上記マスク経由にて光(UV光)を裏面より照射する。それにより、上記N−TFTの内、光が照射されたN−TFTのみが動作する(図40)。これにより、NOR型ROM回路が構成できる。

【0309】

上記光によりデータ書き込みができるROM回路は、同一の基板上で、マスクを変えるだけで異なるデータを書き込むことができ、また、一度書き込んだデータも再度熱アニールすることで、消去・再書き込みが可能となる。

【0310】

(実施例12:上記透明膜を活性層とするTFTを使用したNAND型ROM回路)

本実施例のNAND型ROM回路は、複数のワード線(WL1〜WL3)と、複数のビット線(BL1〜BL2)を備える。またNAND型ROM回路は、WL2がゲートに接続され、BL1にドレインが接続された上記透明膜を用いたN−TFTと、それと直列に、WL3がゲートに接続され、ソースがGNDに接続された透明膜を用いたN−TFTとを備える。また、WL1がゲートに接続され、BL2にドレインに接続された上記透明膜を用いたN−TFTと、それと直列に、WL3がゲートに接続され、ソースがGNDに接続された上記透明膜を用いたN−TFTにより構成される(図41)。

【0311】

上記ROM回路は、まずハイレベルにプリチャージされた後、各々のワード線にハイレベル、又は、ローレベルの電圧を印加することで、特定のビット線のみがローレベル(GNDレベル)の電圧とすることができる。例えば、WL1がロー、WL2、WL3がハイの場合、BL1はローとなり、BL2はハイのままとなる。このようにワード線に相当するN−TFTの有無により、ビット線の信号レベルが決定されるという、メモリ動作が実現される。

【0312】

上記ROM回路は、上記ワード線、ビット線、N−TFTを増やすことで、より多ビットのメモリ動作が可能である。

【0313】

さらに、上記ROM回路は、各ビット線が複数の直列接続されたN−TFTにより放電されるNAND型であるため動作が遅くなる一方、コンタクトが少ないため面積を小さくすることができる。

【0314】

また、上記ROM回路は、同一の機能を、上記N−TFTとデプレッション形TFTを用いて構成することも可能である(図42)。

(実施例13:上記透明膜を活性層とするTFTを使用した差動増幅回路)

N型半導体である上記透明膜を活性層とするN−TFT、並びに、抵抗を用いて差動増幅回路を構成できる。

【0315】

差動増幅回路は、ソースがGNDに接地され、ゲートには一定電圧VBが印加されている上記透明膜を用いたN−TFT3と、ソースが上記N−TFT3に接続され、ゲートを入力IN+、IN−とするN−TFT1、N−TFT2とを有する。また差動増幅回路は、一端が電源に接続され、他の一端がN−TFT1のドレインに接続されている抵抗1と、一端が電源に接続され、他の一端がN−TFT2のドレインに接続されている抵抗2とを備え、N−TFT2のドレインを出力とする(図43)。

【0316】

上記差動増幅回路は、SRAMのセンスアンプにも使用でき、アナログ回路の基本構成要素である。

【0317】

さらに、以下の構成の出力段を追加して新たな差動増幅回路を構成することができる。出力段は、上記差動増幅回路から、ソースが接地され、ゲートには一定電圧VBが印加されているN−TFT4を有する。また出力段は、ソースが上記N−TFT4のドレインと接続され、ドレインが電源と接続され、ゲートが上記差動増幅回路の出力と接続されているN−TFT5で構成されるレベルシフト段を有する。さらに、ソースが接地され、ゲートが前記レベルシフト段のN−TFT4のドレインと接続されているN−TFT6を有する。また、ソースが上記N−TFT6のドレインと接続され、ドレインが電源と接続され、ゲートが上記差動増幅回路の出力と接続されているN−TFT7を有する。このように出力段を追加し、全体の出力を上記N−TFT6のドレインとする新たな差動増幅回路を構成する(図44)ことで、負荷を駆動する能力を上げることができる。

【0318】

(実施例14:上記透明膜を活性層とするTFTを使用したIDタグ)

N型半導体である上記透明膜を活性層とするN−TFT、並びに、上記論理回路、メモリ回路、差動増幅回路を用いて、ICカードやIDタグに必要な、数MHz以下の低速で動作する回路を構成することが可能である。

【0319】

図45に、例として、RF−IDタグのブロック図を示す。上記IDタグは、アンテナ部、電源部、メモリ部、制御回路、クロック回路から構成される。上記電源部は、AC信号を正側のみに整流する整流回路と、回路に適当な電圧を供給する電圧供給回路から構成され、上記メモリ部は、デコーダ回路、ROM回路、レジスタ回路から構成される。

【0320】

上記整流回路には、ダイオードが必要であるが、上記透明膜を用いるN−TFTのゲート−ドレイン間を接続した素子で代用できる可能性がある。また、上記電圧供給回路は、上記実施例7で示した差動増幅器を用いて、レギュレータにより構成できる。

【0321】

一方、上記デコーダ回路は、上記実施例で示したインバータ、NAND、NOR等の論理回路により構成でき、また、レジスタ回路は、上記実施例で示したフリップフロップで構成できる。

【0322】

(実施例15:上記透明膜を活性層とするTFTを使用したディスプレイのバックプレーン)

N型半導体である上記透明膜を活性層とするN−TFTをアクティブマトリックスとして用いることで、上記TFTが透明なディスプレイのバックプレーンが形成できる(図46)。基板に透明な材料を用いた場合には、上記バックプレーンのTFT部は、透明となり、LCDや有機ELディスプレイの開口率を高めることや、基板側からも光を出すことが可能となる。

【産業上の利用可能性】

【0323】

本発明に係る透明酸化物膜、並びに当該膜を用いた半導体素子や回路は、LCDや有機ELディスプレイのスイッチング素子として利用できる。また、プラスチックフィルムをはじめとするフレキシブル素材を基板とするフレキシブル・ディスプレイをはじめ、ICカードやIDタグなどの構成要素として幅広く応用できる。

【符号の説明】

【0324】

1 基板

2 チャンネル層

3 ゲート絶縁膜

4 ゲート端子

5 ドレイン端子

6 ソース端子

10 絶縁基板

11−1、11−2 電極

12 ゲート電極

13 透明酸化物N型半導体膜

14 P型半導体材料

【技術分野】

【0001】

本発明は、非晶質酸化物を利用した半導体デバイス、電気素子、及び回路に関する。特に、非晶質酸化物を利用した半導体デバイスに関する。

【背景技術】

【0002】

近年、液晶やエレクトロルミネッセンス(ElectroLuminescence:EL)技術等の進歩により、平面薄型画像表示装置(Flat Panel Display:FPD)が実用化されている。

【0003】

これらFPDは、ガラス基板上に設けた非晶質シリコン薄膜や多結晶シリコン薄膜を活性層に用いる電界効果型薄膜トランジスタ(Thin Film Transistor:TFT)のアクティブマトリクス回路により駆動されている。

【0004】

一方、これらFPDのより一層の薄型化、軽量化、耐破損性の向上を求めて、ガラス基板の替わりに軽量で可撓性のある樹脂基板を用いる試みも行われている。

【0005】

しかし、上述のシリコン薄膜を用いるトランジスタの製造は、比較的高温の熱工程を要し、一般的に耐熱性の低い樹脂基板上に直接形成することは困難である。

【0006】

そこで、低温での成膜が可能な、たとえばZnOを材料とした酸化物半導体薄膜を用いるTFTの開発が活発に行われている(特許文献1)。

【0007】

このように、新規な半導体デバイスが期待されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2003−298062号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

そこで、本発明は、非晶質酸化物を利用した様々な半導体デバイスや、それを用いた回路等を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の集積回路は、電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする。

【0011】

ところで、本発明者が酸化物半導体を検討したところ、ZnOは、一般に安定なアモルファス相を形成することができないことが判った。そして、殆どのZnOは多結晶相を呈するために、多結晶粒子間の界面でキャリアは散乱され、結果として電子移動度を大きくすることができないようである。

【0012】

また、ZnOには、酸素欠陥が入りやすく、キャリア電子が多数発生してしまうため、電気伝導度を小さくすることが難しい。このために、トランジスタのゲート電圧が無印加時でも、ソース端子とドレイン端子間に大きな電流が流れてしまい、TFTのノーマリーオフ動作を実現できないことが判った。また、トランジスタのオン・オフ比を大きくすることも難しいようである。

【0013】

また、本発明者は、特開2000−044236号公報に記載されている非晶質酸化物膜ZnxMyInzO(x+3y/2+3z/2)(式中、MはAl及びGaのうち少なくとも一つの元素である。)について検討した。この材料は、電子キャリア濃度が、1018/cm3以上であり、単なる透明電極としては好適な材料である。

【0014】

しかし、電子キャリア濃度が1018/cm3以上の酸化物をTFTのチャネル層に用いた場合、オン・オフ比が十分にとれず、ノーマリーオフ型のTFTにはふさわしくないことが分かった。

【0015】

つまり、従来の非晶質酸化物膜では、電子キャリア濃度が1018/cm3未満の膜を得ることはできていなかった。

【0016】

そこで、本発明者は、電界効果型トランジスタの活性層として、電子キャリア濃度が1018/cm3未満の非晶質酸化物を用いているTFTを作製したところ、所望の特性のTFTが得られることを発見したのである。

【0017】

しかも、このような非晶質酸化物は、TFT以外の半導体デバイスにも好適に用いることができることも判明した。

【0018】

本発明者らは、InGaO3(ZnO)m、及びこの材料の成膜条件に関する研究開発を精力的に進めた結果、成膜時の酸素雰囲気の条件を制御することで、電子キャリア濃度を1018/cm3未満にできることを見出した。

【0019】

しかも、このような非晶質酸化物は、TFT以外の半導体デバイスにも好適に用いることができることも判明した。

【0020】

即ち、本発明は、室温での電子キャリア濃度が、1018/cm3未満のアモルファス酸化物を電子伝導体材料として用いていることを特徴とする半導体デバイスである。更にまた、別の本発明は、電子キャリア濃度が増加すると共に、電子移動度が増加することを特徴とするアモルファス酸化物を電子伝導体材料として用いていることを特徴とする半導体デバイスである。

【発明の効果】

【0021】

本発明によれば、非晶質酸化物を利用した新規な集積回路を提供できる。

【図面の簡単な説明】

【0022】

【図1】パルスレーザー蒸着法で成膜したIn−Ga−Zn−O系アモルファス膜の電子キャリア濃度と成膜中の酸素分圧の関係を示すグラフである。

【図2】パルスレーザー蒸着法で成膜したIn−Ga−Zn−O系アモルファス膜の電子キャリアの数と電子移動度の関係を示すグラフである。

【図3】In−Ga−Zn−O系アモルファス膜の電気伝導度と成膜中の酸素分圧の関係を示すグラフである。

【図4】酸素分圧0.8Paの雰囲気でパルスレーザー蒸着法で成膜したInGaO3(Zn1−xMgxO)のxの値に対する電気伝導度、キャリア濃度、電子移動度の変化を示すグラフである。

【図5】実施例1で作製したトップゲート型MISFET素子構造を示す模式図である。

【図6】実施例1で作製したトップゲート型MISFET素子の電流−電圧特性を示すグラフである。

【図7】SIT素子の実施例1を示す図である。

【図8】SIT素子の実施例2を示す図である。

【図9】SIT素子の実施例3を示す図である。

【図10】SIT素子の実施例4を示す図である。

【図11】SBT素子の実施例を示す図である。

【図12】PN−T素子の実施例を示す図である。

【図13】SBD素子の実施例を示す図である。

【図14】PN−D素子の実施例を示す図である。

【図15】抵抗素子の実施例1を示す図である。

【図16】抵抗素子の実施例2を示す図である。

【図17】実施例1のインバータ回路1を示す図である。

【図18】実施例1のインバータ回路2を示す図である。

【図19】実施例1のインバータ回路3を示す図である。

【図20】実施例1のインバータ回路4を示す図である。

【図21】実施例1のインバータ回路5を示す図である。

【図22】実施例1のインバータ回路6を示す図である。

【図23】実施例2のNAND回路1を示す図である。

【図24】実施例2のNAND回路2を示す図である。

【図25】実施例2のNAND回路3を示す図である。

【図26】実施例2のNOR回路1を示す図である。

【図27】実施例2のNOR回路2を示す図である。

【図28】実施例2のNOR回路3を示す図である。

【図29】実施例3のクロックドインバータ回路1を示す図である。

【図30】実施例3のクロックドインバータ回路2を示す図である。

【図31】実施例3のクロックドインバータ回路3を示す図である。

【図32】実施例3のD−フリップフロップを示す図である。

【図33】実施例3のシフトレジスタを示す図である。

【図34】実施例4の1ビットSRAMセル回路1を示す図である。

【図35】実施例4の1ビットSRAMセル回路2を示す図である。

【図36】実施例4の1ビットSRAMセル回路3を示す図である。

【図37】実施例5のNOR型ROM回路1を示す図である。

【図38】実施例5のNOR型ROM回路2の作製の第一段階を示す図である。

【図39】実施例5のNOR型ROM回路2の作製の第二段階を示す図である。

【図40】実施例5のNOR型ROM回路2を示す図である。

【図41】実施例6のNAND型ROM回路1を示す図である。

【図42】実施例6のNAND型ROM回路2を示す図である。

【図43】実施例7の差動増幅回路1を示す図である。

【図44】実施例7の差動増幅回路2を示す図である。

【図45】実施例8のN−TFTを示す図である。

【図46】実施例9のアクティブマトリックスバックプレーンを示す図である。

【図47】実施例1のインバータ回路7を示す図である。

【図48】PLD法を行う際に用いられる装置の模式図である。

【図49】PLD法を行う際に用いられる装置の模式図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態について図面を用いて詳細に説明する。

【0024】

まず、第1の実施形態として、本発明に係る半導体デバイスを、そして、第2の実施形態として、集積回路について説明し、その後、本発明に用いられる非晶質酸化物について詳述している。

【0025】

(第1の実施形態:半導体デバイス)

まず、P型領域とN型領域とを有する半導体デバイスについて説明する。ここでいう、半導体デバイスは、PN接合型トランジスタやヘテロ接合デバイスが含まれる。

【0026】

本発明では、N型領域を構成する非晶質酸化物として、電子キャリア濃度が1018/cm3未満である酸化物や、電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す酸化物を用いることに特徴がある。この非晶質酸化物については後述する。

【0027】

なお、基板上で、前記P型領域内に前記N型領域が設けられているか、あるいは前記N型領域内に前記P型領域が設けられていることも好ましい形態である。

【0028】

また、前記P型領域と前記N型領域とが、基板上の同一層に形成されていることも好ましい形態である。

【0029】

また、P型領域及びN型領域を非晶質酸化物を異なる材料で構成することも好ましい形態である。

【0030】

更にまた、本発明は、上記透明酸化物半導体膜をN型半導体として用いたSIT素子に関する。

【0031】

例として図7を用いて説明する。

【0032】

具体的には、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物半導体とオーミックコンタクトを形成できるITOにより電極11−1を形成し、続いて、上記電極上に上記透明酸化物半導体膜13を形成する。さらに、上記酸化物膜中に、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptにより電極12を複数形成し、さらに上記酸化物膜を積層する。その後、電極11−2を電極11−1と同じ材料で形成することで、SIT素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも、高い電流能力を有する素子を実現する、という効果が得られる。

【0033】

又、上記電極12のPtを薄くする、あるいは、上記電極12として、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きいP型の透明酸化膜半導体を用いる事で、透明なSIT素子を作製できる。

【0034】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたSBT素子に関する。

【0035】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1、11−2を形成する。そして、電極11−1、11−2間に、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptによりゲート電極12を形成することで、SBT素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも簡単な構成で、ゲート電極に印加する電圧で電極11−1、11−2間の電流を制御できるトランジスタ素子を実現する、という効果が得られる。特に、上記電極11−2の下の上記酸化物膜を薄くすることで、よりゲート電圧により変調できる電流の大きさが大きくなる。

【0036】

又、上記電極12のPtを薄くする事で、透明なSBT素子を作製できる。

【0037】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたPN−T素子に関する。

【0038】

具体的には、図12に示すように、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物N型半導体膜13を形成する。

【0039】

続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1、11−2を形成する。そして、電極11−1、11−2間に、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体材料14を積層する。さらに、上記P型半導体材料上に、上記P型半導体材料とオーミックコンタクトを形成できる材料、例えば、Ptによりゲート電極12を形成することで、PN−T素子を作製することができる。従って、上記透明酸化物半導体膜を用いたTFTよりも簡単な構成で、ゲート電極に印加する電圧で電極11−1、11−2間の電流を制御できるトランジスタ素子を実現する、という効果が得られる。特に、上記電極12の下の上記酸化物膜を薄くすることで、よりゲート電圧により変調できる電流の大きさが大きくなる。

【0040】

又、上記電極12のPtを薄くし、上記P型半導体に透明酸化物P型半導体を用いれば、透明なPN−T素子を作製できる。

【0041】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたBPT素子に関する。

【0042】

具体的には、ガラス、プラスチックなどの絶縁基板上に、透明酸化物N型半導体膜1、透明酸化物N型半導体でキャリア密度・伝導度が異なる半導体膜1’、フェルミ準位の絶対値が上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体膜を形成する。続いて、上記酸化物膜1、1’上に、オーミックコンタクトを形成できるITOにより、電極1−1、1−2を形成する。さらに、上記P型半導体膜上にオーミックコンタクトを形成できる材料、例えば、Ptにより、ベース電極2を形成することで、BPT素子を作製することができる。

【0043】

又、上記電極2のPtを薄くし、上記P型半導体に透明酸化物P型半導体を用いれば、透明なBPT素子を作製できる。

【0044】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたSBD素子に関する。

【0045】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極1と、上記半導体膜のフェルミ準位の絶対値よりも大きな仕事関数を持つ材料、例えば、Ptにより電極2を形成することで、SBD素子を作製することができる。

【0046】

又、上記電極2のPtを薄くする事で、透明なSBD素子を作製できる。

【0047】

本発明は、上記透明酸化物半導体膜をN型半導体として用いたPN−D素子に関する(図14)。

【0048】

具体的には、ガラス、プラスチックなどの絶縁基板10上に、上記透明酸化物N型半導体膜13を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11と、フェルミ準位の絶対値が、上記半導体膜のフェルミ準位の絶対値よりも大きなP型半導体材料14をそれぞれ積層する。さらに、上記P型半導体とオーミックコンタクトを形成できる材料、例えば、Ptにより電極12を形成することで、PN−D素子を作製することができる。

【0049】

又、上記P型半導体材料として、透明酸化膜P型半導体を用い、上記電極2のPtを薄くする事で、透明なPN−D素子を作製できる。

【0050】

本発明は、上記透明酸化物半導体膜を抵抗材料として用いた抵抗素子に関する。

【0051】

具体的には、ガラス、プラスチックなどの絶縁基板上に、上記透明酸化物N型半導体膜1を形成する。続いて、上記酸化物膜上に、オーミックコンタクトを形成できるITOにより、電極11−1と11−2を形成することで、透明な抵抗素子を作製することができる。

【0052】

上記半導体膜1と上記電極11−1、11−2の間に、上記半導体膜1とキャリア密度と伝導度が異なる上記透明酸化物N型半導体膜を備えても良い。ただし、上記酸化物の層が共に、キャリア濃度が1018/cm3未満、かつ、伝導度が10S/cm以下である必要はない。

【0053】

上記透明酸化物N型半導体とオーミックコンタクトを形成する材料として、例えば、上記ITOやカルシウム(Ca)などの、仕事関数が上記半導体膜のフェルミ準位の絶対値と同程度、又は、やや小さいことを特徴とする金属・合金等が挙げられる。

【0054】

上記SIT、SBTのゲート電極、並びに、上記SDのショットキー障壁を形成する電極として用いる大きな仕事関数を持つ高導電性材料として、例えば、白金(Pt)やNi、金(Au)などの金属がある。

【0055】

さらに、上記金属を非常に薄く形成することで、透明又は半透明な金属膜が形成でき、上記酸化物と組み合わせることで、透明なSIT、SBT、並びにSDを作製することが可能である。

【0056】

上記SIT、PN−Tのゲート電極用のP型半導体、並びに、上記PN−DのP型半導体として、例えば、アクセプターをドープしたSi等の無機半導体、ペンタセン等の低分子有機半導体、ポリチオフェン、ポリフェニレンビニレン等の高分子有機半導体、Cu2O等の酸化物半導体を用いる事ができる。ただし、PN接合障壁を形成する為には、上記P型半導体のフェルミ準位の絶対値は、上記酸化物N型半導体のフェルミ準位の絶対値よりも、大きい値を持つものとする。

【0057】

さらに、上記酸化物P型半導体と、ITO等の透明な電極を用いる事で、透明なSIT、PN−T、並びにPN−Dを作製することが可能である。

【0058】

また、上述したSiなどの半導体材料の多くは、電子キャリア濃度が1018/cm3未満である非晶質透明酸化物や、電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質透明酸化物とバンドギャップが異なる。よって、この非晶質透明酸化物半導体からなる領域とヘテロ接合を形成する。こうして、ヘテロ接合を有する半導体デバイスが構成される。

【0059】

(第2の実施形態:集積回路)

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いた論理回路に関する。

【0060】

具体的には、上記透明膜を電子伝導体とした抵抗と、上記透明膜を用いたN−TFTを電源−接地電位(GND)間に直列に接続し、上記N−TFTのゲートを信号入力とし、上記TFTのソースを出力とする。

【0061】

これにより、半導体層として上記透明膜のみを用いたインバータ回路を構成できる。

【0062】

さらに、上記抵抗に代わり、P型半導体を活性層として用いたP型TFT(以下、P−TFT)を用い、P−TFTのゲートをN−TFTのゲートと共通の入力とすることで、相補型TFT回路を構成することができる。

【0063】

これにより、インバータの動作時における貫通電流を抑制し、低消費電力である回路を構成できる、という効果が得られる。

【0064】

上記P型半導体の材料として、例えば、ドープしたSi等の無機半導体、ペンタセン等の低分子有機半導体、ポリチオフェン、ポリフェニレンビニレン等の高分子有機半導体、Cu2O等の酸化物半導体を用いる事が好ましい。特に、上記酸化物半導体をP型半導体として用いる場合には、半導体層が透明な回路を構成できる。

【0065】

上記インバータ回路と同様に、クロックドインバータ回路、NAND回路、NOR回路、フリップフロップ、シフトレジスタ等の論理回路を構成することができる。

【0066】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いたSRAM回路に関する。

【0067】

具体的には、2つの上記透明膜を用いたN−TFTを備えたインバータ回路について、入力と出力を接続し、上記インバータの各入力と2本のビット線(BL、BLバー)の間にN−TFTを各々備える。そして、上記N−TFTのゲートは共にワード線(WL)に接続されている。これにより、N型半導体層として上記透明膜を用いた1ビットSRAMセル回路を構成できる。

【0068】

さらに、上記N−TFTと上記透明膜を抵抗で構成されるインバータを用いる場合には、少なくともTFTと抵抗が透明であるSRAMを作製することができる。

【0069】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いたROM回路に関する。

【0070】

具体的には、複数のワード線(WL1〜WLn)と、複数のビット線(BL1〜BLn)を備える。そして、上記ビット線の各々には、ワード線がゲートに接続され、ソースがGNDに接続された、ドレインが並列に接続された上記透明膜を半導体膜とするN−TFTを複数備える。ただし、1本のビット線に対し、全ての上記ワード線に相当するN−TFTを備えておらず、いくつかのワード線に相当するN−TFTを省かれている。これにより、N型半導体層として上記透明膜を用いたNOR型ROM回路を構成できる。

【0071】

さらに、上記透明膜を用いることで、上記ROM回路のTFT部を透明にできる。

【0072】

また、本発明は、上記透明膜を半導体膜とするTFTを、N−TFTとして用いた差動増幅回路に関する。

【0073】

具体的には、ソースがGNDに接地され、ゲートにバイアス電圧として一定電圧が印加されるN−TFTと、ゲートを入力とし、ソースが上記N−TFTのドレインと接続されている2つのN−TFTとを備える。そして、2つの上記N−TFTの各々のドレインと電源間に抵抗を備え、上記N−TFTのドレインと抵抗間を出力とすることで差動増幅回路を構成できる。

【0074】

さらに、上記抵抗に上記透明膜を用いることで、少なくとも上記N−TFTと抵抗部分を透明にできる。

【0075】

また、本発明は、上記透明膜を半導体とするTFTを、N−TFTとして用いた回路によって構成されるICタグ又はIDタグに関する。

【0076】

具体的には、上記ICタグ又はIDタグは、上記論理回路、上記メモリ回路、上記差動増幅回路を用いたアナログ回路、上記N−TFTのゲート−ドレイン間をショートすることでダイオードの特性を実現する素子を用いた整流回路をすべて、あるいは、少なくともいずれかを含んで構成されている。

【0077】

上記IDタグは、上記透明膜を用いることで、少なくとも上記N−TFTと抵抗部分を透明にできる。

【0078】

また、本発明は、上記透明膜を半導体とするTFTを、N−TFTとして用いたアクティブマトリックス基板に関する。

【0079】

具体的には、上記N−TFTを、各セル回路のスイッチング素子として用いた、LCD(LiquidCrystalDisplay、液晶ディスプレイ)、有機EL(Electro−Luminescence)ディスプレイ、光センサ等のアクティブマトリックス基板を作製できる。

【0080】

上記アクティブマトリックス基板は、上記透明膜を半導体とするN−TFTを用いることで、開口率を増やすことができる、という効果が得られる。

【0081】

なお、上述の回路は、必ずしも、全ての要素をTFTで構成する必要はない。適宜PNトランジスタやSIT,SB−T,BP−Tを用いて回路を構成することもできる。

【0082】

(非晶質酸化物について)

本発明に係る非晶質酸化物の電子キャリア濃度は、室温で測定する場合の値である。室温とは、例えば25℃であり、具体的には0℃から40℃程度の範囲から適宜選択されるある温度である。なお、本発明に係るアモルファス酸化物の電子キャリア濃度は、0℃から40℃の範囲全てにおいて、1018/cm3未満を充足する必要はない。例えば、25℃において、キャリア電子密度1018/cm3未満が実現されていればよい。また、電子キャリア濃度を更に下げ、1017/cm3以下、より好ましくは1016/cm3以下にするとノーマリーオフのTFTが歩留まり良く得られる。

【0083】

なお、1018/cm3未満とは、好ましくは1×1018/cm3未満であり、より好適には、1.0×1018/cm3未満である。

【0084】

電子キャリア濃度の測定は、ホール効果測定により求めることが出来る。

【0085】

なお、本発明において、アモルファス酸化物とは、X線回折スペクトルにおいて、ハローパターンが観測され、特定の回折線を示さない酸化物をいう。

【0086】

本発明のアモルファス酸化物における、電子キャリア濃度の下限値は、TFTのチャネル層として適用できれば特に限定されるものではない。下限値は、例えば、1012/cm3である。

【0087】

従って、本発明においては、後述する各実施例のようにアモルファス酸化物の材料、組成比、製造条件などを制御して、例えば、電子キャリア濃度を、1012/cm3以上1018/cm3未満とする。より好ましくは1013/cm3以上1017/cm3以下、更には1015/cm3以上1016/cm3以下の範囲にすることが好ましいものである。前記非晶質酸化物としては、InZnGa酸化物のほかにも、In酸化物、InxZn1−x酸化物(0.2≦x≦1)、InxSn1−x酸化物(0.8≦x≦1)、あるいはInx(Zn、Sn)1−x酸化物(0.15≦x≦1)から適宜選択できる。

【0088】

なお、Inx(Zn、Sn)1−x酸化物は、Inx(ZnySn1−y)1−x酸化物と記載することができ、yの範囲は1から0である。

【0089】

なお、ZnとSnを含まないIn酸化物の場合は、Inの一部をGaに置換することもできる。即ち、InxGa1−x酸化物(0≦x≦1)の場合である。

【0090】

以下に、本発明者らが作製することに成功した電子キャリア濃度が1018/cm3未満の非晶質酸化物について詳述する。

【0091】

上記酸化物とは、In−Ga−Zn−Oを含み構成され、結晶状態における組成がInGaO3(ZnO)m(mは6未満の自然数)で表され、電子キャリア濃度が1018/cm3未満であることを特徴とする。

【0092】

また上記酸化物は、In−Ga−Zn−Mg−Oを含み構成され、結晶状態の組成がInGaO3(Zn1−xMgxO)m(mは6未満の自然数、0<x≦1)で表され、電子キャリア濃度が1018/cm3未満であることを特徴とする。

【0093】

なお、これらの酸化物で構成される膜において、電子移動度が1cm2/(V・秒)超になるように設計することも好ましい。

【0094】

上記膜をチャネル層に用いれば、トランジスターオフ時のゲート電流が0.1マイクロアンペヤ未満のノーマリーオフで、オン・オフ比が103超のトランジスタ特性を実現できる。そして、可視光に対して、透明あるいは透光性を有し、フレキシブルなTFTが実現される。

【0095】

なお、上記膜は、伝導電子数の増加と共に、電子移動度が大きくなることを特徴とする。透明膜を形成する基板としては、ガラス基板、樹脂製プラスチック基板又はプラスチックフィルムなどを用いることができる。

【0096】

上記非晶質酸化物膜をチャネル層に利用する際には、Al2O3,Y2O3、又はHfO2の1種、又はそれらの化合物を少なくとも二種以上含む混晶化合物をゲート絶縁膜に利用できる。

【0097】

また、非晶質酸化物中に、電気抵抗を高めるための不純物イオンを意図的に添加せず、酸素ガスを含む雰囲気中で、成膜することも好ましい形態である。

【0098】

本発明者らは、この半絶縁性酸化物アモルファス薄膜は、伝導電子数の増加と共に、電子移動度が大きくなるという特異な特性を見出した。そして、その膜を用いてTFTを作成し、オン・オフ比、ピンチオフ状態での飽和電流、スイッチ速度などのトランジスタ特性が更に向上することを見出した。即ち、非晶質酸化物を利用して、ノーマリーオフ型のTFTを実現できることを見出した。

【0099】

非晶質酸化物薄膜を膜トランジスタのチャネル層として用いると、電子移動度が1cm2/(V・秒)超、好ましくは5cm2/(V・秒)超にすることができる。

【0100】

電子キャリア濃度が、1018/cm3未満、好ましくは、1016/cm3未満のときは、オフ時(ゲート電圧無印加時)のドレイン・ソース端子間の電流を、10マイクロアンペヤ未満、好ましくは0.1マイクロアンペア未満にすることができる。

【0101】

また、該膜を用いれば、電子移動度が1cm2/(V・秒)超、好ましくは5cm2/(V・秒)超の時は、ピンチオフ後の飽和電流を10マイクロアンペア超にでき、オン・オフ比を103超とすることができる。

【0102】

TFTでは、ピンチオフ状態では、ゲート端子に高電圧が印加され、チャネル中には高密度の電子が存在している。

【0103】

したがって、本発明によれば、電子移動度が増加した分だけ、より飽和電流値を大きくすることができる。この結果、オン・オフ比の増大、飽和電流の増大、スイッチング速度の増大など、トランジスタ特性の向上が期待できる。

【0104】

なお、通常の化合物中では、電子数が増大すると、電子間の衝突により、電子移動度は減少する。

【0105】

なお、上記TFTの構造としては、半導体チャネル層の上にゲート絶縁膜とゲート端子を順に形成するスタガ(トップゲート)構造や、ゲート端子の上にゲート絶縁膜と半導体チャネル層を順に形成する逆スタガ(ボトムゲート)構造を用いることができる。

【0106】

(第1の成膜法:PLD法)

結晶状態における組成がInGaO3(ZnO)m(mは6未満の自然数)で表される非晶質酸化物薄膜は、mの値が6未満の場合は、800℃以上の高温まで、非晶質状態が安定に保たれるが、mの値が大きくなるにつれ、結晶化しやすくなる。すなわち、InGaO3に対するZnOの比が増大して、ZnO組成に近づくにつれ、結晶化しやすくなる。

【0107】

したがって、非晶質TFTのチャネル層としては、mの値が6未満であることが好ましい。

【0108】

成膜方法は、InGaO3(ZnO)m組成を有する多結晶焼結体をターゲットとして、気相成膜法を用いるのが良い。気相成膜法の中でも、スッパタ法、パルスレーザー蒸着法が適している。さらに、量産性の観点から、スパッタ法が最も適している。

【0109】

しかしながら、通常の条件で該非晶質膜を作成すると、主として酸素欠損が生じ、これまで、電子キャリア濃度を1018/cm3未満、電気伝導度にして、10S/cm以下にすることができなかった。そうした膜を用いた場合、ノーマリーオフのトランジスタを構成することができない。

【0110】

本発明者らは、図9で示される装置により、パルスレーザー蒸着法で作製したIn−Ga−Zn−Oを作製した。

【0111】

図48に示すようなPLD成膜装置を用いて、成膜を行った。

【0112】

同図において、701はRP(ロータリーポンプ)、702はTMP(ターボ分子ポンプ)、703は準備室、704はRHEED用電子銃、705は基板を回転、上下移動するための基板保持手段、706はレーザー入射窓である。また、707は基板、708はターゲット、709はラジカル源、710はガス導入口、711はターゲットを回転、上下移動するためのターゲット保持手段、712はバイパスライン、713はメインライン、714はTMP(ターボ分子ポンプ)である。また、715はRP(ロータリーポンプ)、716はチタンゲッターポンプ、717はシャッターである。また、図中718はIG(イオン真空計)、719はPG(ピラニ真空計)、720はBG(バラトロン真空計)、721は成長室(チャンバー)である。

【0113】

KrFエキシマレーザーを用いたパルスレーザー蒸着法により、SiO2ガラス基板(コーニング社製1737)上にIn−Ga−Zn−O系アモルファス酸化物半導体薄膜を堆積させた。堆積前の処理として、基板の超音波による脱脂洗浄を、アセトン,エタノール,超純水を用いて、各5分間行った後、空気中100℃で乾燥させた。

【0114】

前記多結晶ターゲットには、InGaO3(ZnO)4焼結体ターゲット(サイズ20mmΦ5mmt)を用いた。これは、出発原料として、In2O3:Ga2O3:ZnO(各4N試薬)を湿式混合した後(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て得られるものである。こうして作製したターゲットの電気伝導度は、90(S/cm)であった。成長室の到達真空を2×10−6(Pa)にして、成長中の酸素分圧を6.5(Pa)に制御して成膜を行った。

【0115】

チャンバー721内酸素分圧は6.5Pa、基板温度は25℃である。

【0116】

なお、ターゲット708と被成膜基板707間の距離は、30(mm)であり、入射窓716から入射されるKrFエキシマレーザーのパワーは、1.5−3(mJ/cm2/pulse)の範囲である。また、パルス幅は、20(nsec)、繰り返し周波数は10(Hz)、そして照射スポット径は、1×1(mm角)とした。

【0117】

こうして、成膜レート7(nm/min)で成膜を行った。

【0118】

得られた薄膜について、薄膜のすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは認められなかったことから、作製したIn−Ga−Zn−O系薄膜はアモルファスであるといえる。

【0119】

さらに、X線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。蛍光X線(XRF)分析の結果、薄膜の金属組成比はIn:Ga:Zn=0.98:1.02:4であった。

【0120】

電気伝導度は、約10−2S/cm未満であった。電子キャリア濃度は約1016/cm3以下、電子移動度は約5cm2/(V・秒)と推定される。

【0121】

光吸収スペクトルの解析から、作製したアモルファス薄膜の禁制帯エネルギー幅は、約3eVと求まった。以上のことから、作製したIn−Ga−Zn−O系薄膜は、結晶のInGaO3(ZnO)4の組成に近いアモルファス相を呈しており、酸素欠損が少なく、電気伝導度が小さな透明な平坦薄膜であることが分かった。

【0122】

具体的に図1を用いて説明する。同図は、In−Ga−Zn−Oから構成され、結晶状態を仮定した時の組成がInGaO3(ZnO)m(mは6未満の数)で表される透明アモルファス酸化物薄膜を本実施例と同じ条件下で作成する場合を示した特性図である。この特性図は、酸素分圧を変化させた場合に、成膜された酸化物の電子キャリア濃度の変化を示したものである。

【0123】

本実施例と同じ条件下で酸素分圧を4.5Pa超の高い雰囲気中で、成膜することにより、図1に示すように、電子キャリア濃度を1018/cm3未満に低下させることができた。この場合、基板の温度は意図的に加温しない状態で、ほぼ室温に維持されている。フレキシブルなプラスチックフィルムを基板として使用するには、基板温度は100℃未満に保つことが好ましい。

【0124】

酸素分圧をさらに大きくすると、電子キャリア濃度をさらに低下させることができる。例えば、図1に示す様に、基板温度25℃、酸素分圧5Paで成膜したInGaO3(ZnO)4薄膜では、さらに、電子キャリア数を1016/cm3に低下させることができた。

【0125】

得られた薄膜は、図2に示す様に、電子移動度が1cm2/(V・秒)超であった。しかし、本実施例のパルスレーザー蒸着法では、酸素分圧を6.5Pa以上にすると、堆積した膜の表面が凸凹となり、TFTのチャネル層として用いることが困難となる。

【0126】

従って、酸素分圧4.5Pa超、望ましくは5Pa超、6.5Pa未満の雰囲気で、パルスレーザー蒸着法で、結晶状態における組成InGaO3(ZnO)m(mは6未満の数)で表される透明アモルファス酸化物薄膜を作製する。この透明アモルファス酸化物薄膜を用いれば、ノーマリーオフのトランジスタを構成することができる。

【0127】

また、該薄膜の電子移動度は、1cm2/V・秒超が得られ、オン・オフ比を103超に大きくすることができた。

【0128】

以上、説明したように、本実施例に示した条件下でPLD法によりInGaZn酸化物の成膜を行う場合は、酸素分圧を4.5Pa以上6.5Pa未満になるように制御することが望ましい。

【0129】

なお、電子キャリア濃度を1018/cm3未満を実現するためには、酸素分圧の条件、成膜装置の構成や、成膜する材料や組成などに依存する。

【0130】

次に、上記装置における酸素分圧6.5Paの条件で、アモルファス酸化物を作製し、図5に示すトップゲート型MISFET素子を作製した。具体的には、まず、ガラス基板(1)上に上記のアモルファスIn−Ga−Zn−O薄膜の作製法により、チャンネル層(2)として用いる厚さ120nmの半絶縁性アモルファスInGaO3(ZnO)4膜を形成した。

【0131】

さらにその上に、チャンバー内酸素分圧を1Pa未満にして、パルスレーザー堆積法により電気伝導度の大きなInGaO3(ZnO)4及び金膜をそれぞれ30nm積層した。そして、フォトリソグラフィー法とリフトオフ法により、ドレイン端子(5)及びソース端子(6)を形成した。最後にゲート絶縁膜(3)として用いるY2O3膜を電子ビーム蒸着法により成膜し(厚み:90nm、比誘電率:約15、リーク電流密度:0.5MV/cm印加時に10−3A/cm2)、その上に金を成膜した。そして、フォトリソグラフィー法とリフトオフ法により、ゲート端子(4)を形成した。

【0132】

MISFET素子の特性評価

図6に、室温下で測定したMISFET素子の電流−電圧特性を示す。ドレイン電圧VDSの増加に伴い、ドレイン電流IDSが増加したことからチャネルがn型半導体であることが分かる。これは、アモルファスIn−Ga−Zn−O系半導体がn型であるという事実と矛盾しない。IDSはVDS=6V程度で飽和(ピンチオフ)する典型的な半導体トランジスタの挙動を示した。利得特性を調べたところ、VDS=4V印加時におけるゲート電圧VGSの閾値は約−0.5Vであった。また、VG=10V時には、IDS=1.0×10−5Aの電流が流れた。これはゲートバイアスにより絶縁体のIn−Ga−Zn−O系アモルファス半導体薄膜内にキャリアを誘起できたことに対応する。

【0133】

トランジスタのオン・オフ比は、103超であった。また、出力特性から電界効果移動度を算出したところ、飽和領域において約7cm2(Vs)−1の電界効果移動度が得られた。作製した素子に可視光を照射して同様の測定を行なったが、トランジスタ特性の変化は認められなかった。

【0134】

本実施例によれば、電子キャリア濃度が小さく、したがって、電気抵抗が高く、かつ電子移動度が大きいチャネル層を有する薄膜トランジスタを実現できる。

【0135】

なお、上記したアモルファス酸化物は、電子キャリア濃度の増加と共に、電子移動度が増加し、さらに縮退伝導を示すという優れた特性を備えていた。

【0136】

本実施例では、ガラス基板上に薄膜トランジスタを作製したが、成膜自体が室温で行えるので、プラスチック板やフィルムなどの基板が使用可能である。

【0137】

また、本実施例で得られたアモルファス酸化物は、可視光の光吸収が殆どなく、透明なフレキシブルTFTを実現できる。

【0138】

(第2の成膜法:スパッタ法(SP法))

雰囲気ガスとしてアルゴンガスを用いた高周波SP法により、成膜する場合について説明する。

【0139】

SP法は、図49に示す装置を用いて行った。同図において、807は被成膜基板、808はターゲット、805は冷却機構付き基板保持手段、814は、ターボ分子ポンプ、815はロータリーポンプ、817はシャッターである。また、818はイオン真空計、819はピラニ真空計、821は成長室(チャンバー)、830はゲートバルブである。

【0140】

被成膜基板807としては、SiO2ガラス基板(コーニング社製1737)を用意した。成膜前処理として、この基板の超音波脱脂洗浄を、アセトン、エタノール、超純水により各5分ずつ行った後、空気中100℃で乾燥させた。

【0141】

ターゲット材料としては、InGaO3(ZnO)4組成を有する多結晶焼結体(サイズ20mmΦ5mmt)を用いた。

【0142】

この焼結体は、出発原料として、In2O3:Ga2O3:ZnO(各4N試薬)を湿式混合(溶媒:エタノール)し、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て作製した。このターゲット808の電気伝導度は90(S/cm)であり、半絶縁体状態であった。

【0143】

成長室821内の到達真空は、1×10−4(Pa)であり、成長中の酸素ガスとアルゴンガスの全圧は、4〜0.1×10−1(Pa)の範囲での一定の値とした。そして、アルゴンガスと酸素との分圧比を変えて、酸素分圧を10−3〜2×10−1(Pa)の範囲で変化させた。

【0144】

また、基板温度は、室温とし、ターゲット808と被成膜基板807間の距離は、30(mm)であった。

【0145】

投入電力は、RF180Wであり、成膜レートは、10(nm/min)で行った。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、作製したIn−Zn−Ga−O系膜はアモルファス膜であることが示された。

【0146】

さらに、X線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。蛍光X線(XRF)分析の結果、薄膜の金属組成比はIn:Ga:Zn=0.98:1.02:4であった。

【0147】

成膜時の雰囲気の酸素分圧を変化させ、得られたアモルファス酸化物膜の電気伝導度を測定した。その結果を図3に示す。

【0148】

図3に示すように、酸素分圧を3×10−2Pa超の高い雰囲気中で、成膜することにより、電気伝導度を10S/cm未満に低下させることができた。

【0149】

酸素分圧をさらに大きくすることにより、電子キャリア数を低下させることができた。例えば、図3に示す様に、基板温度25℃、酸素分圧10−1Paで成膜したInGaO3(ZnO)4薄膜では、さらに、電気伝導度を約10−10S/cmに低下させることができた。また、酸素分圧10−1Pa超で成膜したInGaO3(ZnO)4薄膜は、電気抵抗が高すぎて電気伝導度は測定できなかった。この場合、電子移動度は測定できなかったが、電子キャリア濃度が大きな膜での値から外挿して、電子移動度は、約1cm2/V・秒と推定された。

【0150】

すなわち、酸素分圧3×10−2Pa超、望ましくは5×10−1Pa超のアルゴンガス雰囲気下でスパッタ蒸着法で成膜を行った。この成膜により、In−Ga−Zn−Oから構成され、結晶状態における組成InGaO3(ZnO)m(mは6未満の自然数)で表される透明アモルファス酸化物薄膜を作製した。この透明アモルファス酸化物薄膜を用い、ノーマリーオフで、かつオン・オフ比を103超のトランジスタを構成することができた。

【0151】

本実施例で示した装置、材料を用いる場合は、スパッタによる成膜の際の酸素分圧としては、例えば、3×10−2Pa以上、5×10−1Pa以下の範囲である。なお、パルスレーザー蒸着法およびスパッタ法で作成された薄膜では、図2に示す様に、伝導電子数の増加と共に、電子移動度が増加する。

【0152】

上記のとおり、酸素分圧を制御することにより、酸素欠陥を低減でき、その結果、電子キャリア濃度を減少できる。また、アモルファス状態では、多結晶状態とは異なり、本質的に粒子界面が存在しないために、高電子移動度のアモルファス薄膜を得ることができる。

【0153】

なお、ガラス基板の代わりに厚さ200μmのポリエチレン・テレフタレート(PET)フィルムを用いた場合にも、得られたInGaO3(ZnO)4アモルファス酸化物膜は、同様の特性を示した。

【0154】

なお、ターゲットとして、多結晶InGaO3(Zn1−xMgxO)m(mは6未満の自然数、0<x≦1)を用いれば、1Pa未満の酸素分圧下でも、高抵抗非晶質InGaO3(Zn1−xMgxO)m膜を得ることができる。

【0155】

例えば、Znを80at%のMgで置換したターゲットを使用した場合、酸素分圧0.8Paの雰囲気で、パルスレーザー堆積法で得られた膜の電子キャリア濃度を1016/cm3未満とすることができる(電気抵抗値は、約10−2S/cmである。)。

【0156】

こうした膜の電子移動度は、Mg無添加膜に比べて低下するが、その程度は少なく、室温での電子移動度は約5cm2/(V・秒)で、アモルファスシリコンに比べて、1桁程度大きな値を示す。同じ条件で成膜した場合、Mg含有量の増加に対して、電気伝導度と電子移動度は、共に低下するので、Mgの含有量は、好ましくは、20%超、85%未満(xにして、0.2<x<0.85)である。

【0157】

上記した非晶質酸化物膜を用いた薄膜トランジスタにおいて、Al2O3,Y2O3、HfO2、又はそれらの化合物を少なくとも二つ以上含む混晶化合物をゲート絶縁膜とすることが好ましい。

【0158】

ゲート絶縁薄膜とチャネル層薄膜との界面に欠陥が存在すると、電子移動度の低下及びトランジスタ特性にヒステリシスが生じる。また、ゲート絶縁膜の種類により、リーク電流が大きく異なる。このために、チャネル層に適合したゲート絶縁膜を選定する必要がある。Al2O3膜を用いれば、リーク電流を低減できる。また、Y2O3膜を用いればヒステリシスを小さくできる。さらに、高誘電率のHfO2膜を用いれば、電子移動度を大きくすることができる。また、これらの膜の混晶を用いて、リーク電流、ヒステリシスが小さく、電子移動度の大きなTFTを形成できる。また、ゲート絶縁膜形成プロセス及びチャネル層形成プロセスは、室温で行うことができるので、TFT構造として、スタガ構造及び逆スタガ構造いずれをも形成することができる。

【0159】

このように形成したTFTは、ゲート端子、ソース端子、及び、ドレイン端子を備えた3端子素子である。このTFTは、セラミックス、ガラス、又はプラスチックなどの絶縁基板上に成膜した半導体薄膜を、電子又はホールが移動するチャネル層として用いるものである。そして、このTFTはゲート端子に電圧を印加して、チャンネル層に流れる電流を制御し、ソース端子とドレイン端子間の電流をスイッチングする機能を有するアクテイブ素子である。

【0160】

なお、酸素欠損量を制御して所望の電子キャリア濃度を達成できていることが本発明においては重要である。

【0161】

上記記載においては、非晶質酸化物膜の酸素量(酸素欠損量)の制御を、成膜時に酸素を所定濃度含む雰囲気中で行うことで制御している。しかし、成膜後、当該酸化物膜を酸素を含む雰囲気中で後処理して酸素欠損量を制御(低減あるいは増加)することも好ましいものである。

【0162】

効果的に酸素欠損量を制御するには、酸素を含む雰囲気中の温度を0℃以上300℃以下、好ましくは、25℃以上、250℃以下、更に好ましくは100℃以上200℃以下で行うのがよい。

【0163】

勿論、成膜時にも酸素を含む雰囲気中で行い、且つ成膜後の後処理でも酸素を含む雰囲気中で後処理してもよい。また、所定の電子キャリア濃度(1018/cm3未満)を得られるのであれば、成膜時には、酸素分圧制御は行わないで、成膜後の後処理を酸素を含む雰囲気中で行ってもよい。

【0164】

なお、本発明における電子キャリア濃度の下限としては、得られる酸化物膜をどのような素子や回路あるいは装置に用いるかにもよるが、例えば1014/cm3以上である。

【0165】

(材料系の拡大)

さらに、組成系を拡大して研究を進めた結果、Zn,In及びSnのうち、少なくとも1種類の元素の酸化物からなるアモルファス酸化物で、電子キャリア濃度が小さく、かつ電子移動度が大きいアモルファス酸化物膜を作製できることを見出した。

【0166】

また、このアモルファス酸化物膜は、伝導電子数の増加と共に、電子移動度が大きくなるという特異な特性を有することを見出した。

【0167】

その膜を用いてTFTを作成し、オン・オフ比、ピンチオフ状態での飽和電流、スイッチ速度などのトランジスタ特性に優れたノーマリーオフ型のTFTを作成できる。

【0168】

本発明には、以下(a)から(h)の特徴を有する酸化物を用いることができる。

(a) 室温での電子キャリア濃度が、1018/cm3未満のアモルファス酸化物。

(b) 電子キャリア濃度が増加すると共に、電子移動度が増加することを特徴とするアモルファス酸化物。

【0169】

なおここで、室温とは0℃から40℃程度の温度をいう。アモルファスとは、X線回折スペクトルにおいて、ハローパターンのみが観測され、特定の回折線を示さない化合物をいう。また、ここでの電子移動度は、ホール効果測定で得られる電子移動度をいう。

(c) 室温での電子移動度が、0.1cm2/V・秒超であることを特徴とする上記(a)又は(b)に記載されるアモルファス酸化物。

(d) 縮退伝導を示す上記(b)から(c)のいずれかに記載されるアモルファス酸化物である。なお、ここでの縮退伝導とは、電気抵抗の温度依存性における熱活性化エネルギーが、30meV以下の状態をいう。

(e) Zn,In及びSnのうち、少なくとも1種類の元素を構成成分として含む上記(a)から(d)のいずれかに記載されるアモルファス酸化物。

(f) 上記(e)に記載のアモルファス酸化物に、Znより原子番号の小さい2族元素M2(M2は、Mg,Ca)、Inより原子番号の小さい3属元素M3(M3は、B,Al、Ga、Y),Snより小さい原子番号の小さい4属元素M4(M4は、Si,Ge,Zr)、5属元素M5(M5は、V,Nb,Ta)およびLu、Wのうち、少なくとも1種類の元素を含むアモルファス酸化物膜。

(g) 結晶状態における組成がIn1−xM3xO3(Zn1−yM2yO)m(0≦x、y≦1、mは0又は6未満の自然数)である化合物単体又はmの異なる化合物の混合体である(a)から(f)のいずれかに記載のアモルファス酸化物膜。M3は例えば、Gaであり、M2は例えば、Mgである。

(h) ガラス基板、金属基板、プラスチック基板又はプラスチックフィルム上に設けた上記(a)から(g)記載のアモルファス酸化物膜。

【0170】

また、本発明は、(10)上記記載のアモルファス酸化物、又はアモルファス酸化物膜をチャネル層に用いた電界効果型トランジスタである。

【0171】

なお、電子キャリア濃度が1018/cm3未満、1015/cm3超のアモルファス酸化物膜をチャネル層に用い、ソース端子、ドレイン端子及びゲート絶縁膜を介してゲート端子を配した電界効果型トランジスタを構成する。ソース・ドレイン端子間に5V程度の電圧を印加したとき、ゲート電圧を印加しないときのソース・ドレイン端子間の電流を約10−7アンペヤにすることができる。

【0172】

酸化物結晶の電子移動度は、金属イオンのs軌道の重なりが大きくなるほど、大きくなり、原子番号の大きなZn,In,Snの酸化物結晶は、0.1から200cm2/(V・秒)の大きな電子移動度を持つ。

【0173】

さらに、酸化物では、酸素と金属イオンとがイオン結合している。

【0174】

そのため、化学結合の方向性がなく、構造がランダムで、結合の方向が不均一なアモルファス状態でも、電子移動度は、結晶状態の電子移動度に比較して、同程度の大きさを有することが可能となる。

【0175】

一方で、Zn,In,Snを原子番号の小さな元素で置換することにより、電子移動度は小さくなる、こうした結果により、本発明のよるアモルファス酸化物の電子移動度は、約0.01cm2/(V・秒)から20cm2/(V・秒)である。

【0176】

上記酸化物を用いてトランジスタのチャネル層を作製する場合、トランジスタにおいて、Al2O3,Y2O3、HfO2、又はそれらの化合物を少なくとも二つ以上含む混晶化合物をゲート絶縁膜とすることが好ましい。

【0177】

ゲート絶縁薄膜とチャネル層薄膜との界面に欠陥が存在すると、電子移動度の低下及びトランジスタ特性にヒステリシスが生じる。また、ゲート絶縁膜の種類により、リーク電流が大きく異なる。このために、チャネル層に適合したゲート絶縁膜を選定する必要がある。Al2O3膜を用いれば、リーク電流を低減できる。また、Y2O3膜を用いればヒステリシスを小さくできる。さらに、高誘電率のHfO2膜を用いれば、電界効果移動度を大きくすることができる。また、これらの化合物の混晶からなる膜を用いて、リーク電流、ヒステリシスが小さく、電界効果移動度の大きなTFTを形成できる。また、ゲート絶縁膜形成プロセス及びチャネル層形成プロセスは、室温で行うことができるので、TFT構造として、スタガ構造及び逆スタガ構造いずれをも形成することができる。

【0178】

In2O3酸化物膜は、気相法により成膜でき、成膜中の雰囲気に水分を、0.1Pa程度添加することにより、アモルファス膜が得られる。

【0179】

また、ZnO及びSnO2は、アモルファス膜を得ることは難しいが、In2O3を、ZnOの場合には20原子量%程度、SnO2の場合には、90原子量%程度添加することによりアモルファス膜を得ることができる。特に、Sn−In―O系アモルファス膜を得るためには、雰囲気中に窒素ガスを0.1Pa程度導入すればよい。

【0180】

上記のアモルファス膜に、Znより原子番号の小さい2族元素M2(M2は、Mg,Ca)、Inより原子番号の小さい3属元素M3(M3は、B,Al、Ga、Y),Snより小さい原子番号の小さい4属元素M4(M4は、Si,Ge,Zr)、5属元素M5(M5は、V,Nb,Ta)およびLu、Wのうち、少なくとも1種類の複合酸化物を構成する元素を添加できる。

【0181】

それにより、室温での、アモルファス膜をより安定化させることができる。また、アモルファス膜が得られる組成範囲を広げることができる。

【0182】

特に、共有結合性の強い、B,Si,Geの添加は、アモルファス相安定化に有効であるし、イオン半径の差の大きいイオンから構成される複合酸化物は、アモルファス相が安定化する。

【0183】

たとえば、In−Zn−O系では、Inが約20原子%超の組成範囲でないと、室温で安定なアモルファス膜は得難いが、MgをInと当量添加することにより、Inが約15原子量%超の組成範囲で、安定なアモルファス膜を得ることができる。

【0184】

気相法による成膜において、雰囲気を制御することにより、電子キャリア濃度が、1018/cm3未満、1015/cm3超のアモルファス酸化膜を得ることができる。

【0185】

アモルファス酸化物の成膜方法としては、パルスレーザー蒸着法(PLD法)、スパッタ法(SP法)及び電子ビーム蒸着法などの気相法を用いるのがよい。気相法の中でも、材料系の組成を制御しやすい点では、PLD法が、量産性の点からは、SP法が適している。しかし、成膜法は、これらの方法に限られるのものではない。

【0186】

(PLD法によるIn−Zn−Ga−O系アモルファス酸化膜の成膜)

KrFエキシマレーザーを用いたPLD法により、ガラス基板(コーニング社製1737)上にIn−Zn―Ga―O系アモルファス酸化物膜を堆積させた。このとき、InGaO3(ZnO)及びInGaO3(ZnO)4組成を有する多結晶焼結体をそれぞれターゲットとした。

【0187】

成膜装置は、既述の図48に記載されている装置を用い、成膜条件は、当該装置を用いた場合と同様とした。

【0188】

基板温度は25℃である。得られた膜に関し、膜面にすれすれ入射X線回折(薄膜法、入射角0.5度)を行ったところ、明瞭な回折ピークは検出されず、2種類のターゲットから作製したIn−Zn−Ga−O系膜は、いずれもアモルファス膜であることが示された。

【0189】

さらに、ガラス基板上のIn−Zn―Ga―O系アモルファス酸化物膜のX線反射率測定を行い、パターンの解析を行った結果、薄膜の平均二乗粗さ(Rrms)は約0.5nmであり、膜厚は約120nmであることが分かった。

【0190】

蛍光X線(XRF)分析の結果、InGaO3(ZnO)組成を有する多結晶焼結体をターゲットとして得られた膜の金属組成比はIn:Ga:Zn=1.1:1.1:0.9であった。また、InGaO(ZnO)4組成を有する多結晶焼結体をターゲットとして得られた膜の金属組成比は、In:Ga:Zn=0.98:1.02:4であった。

【0191】

成膜時の雰囲気の酸素分圧を変化させ、InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜の電子キャリア濃度を測定した。その結果を図1に示す。酸素分圧が4.2Pa超の雰囲気中で成膜することにより、電子キャリア濃度を1018/cm3未満に低下させることができた。この場合、基板の温度は意図的に加温しない状態でほぼ室温に維持されている。また、酸素分圧が6.5Pa未満の時は、得られたアモルファス酸化物膜の表面は平坦であった。

【0192】

酸素分圧が5Paの時、InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜の電子キャリア濃度は1016/cm3、電気伝導度は、10−2S/cmであった。また、電子移動度は、約5cm2/V・秒と推測された。光吸収スペクトルの解析から、作製したアモルファス酸化物膜の禁制帯エネルギー幅は、約3eVと求まった。

【0193】

酸素分圧をさらに大きくすると、電子キャリア濃度をさらに低下させることができた。図1に示す様に、基板温度25℃、酸素分圧6Paで成膜したIn−Zn−Ga−O系アモルファス酸化物膜では、電子キャリア濃度を8×1015/cm3(電気伝導:約8×10−3S/cm)に低下させることができた。得られた膜は、電子移動度が1cm2/(V・秒)超と推測された。しかし、PLD法では、酸素分圧を6.5Pa以上にすると、堆積した膜の表面が凸凹となり、TFTのチャネル層として用いることが困難となった。

【0194】

InGaO3(ZnO)4組成を有する多結晶焼結体をターゲットとし、異なる酸素分圧で成膜したIn−Zn−Ga−O系アモルファス酸化物膜に関して、電子キャリア濃度と電子移動度の関係を調べた。その結果を図2に示す。電子キャリア濃度が、1016/cm3から1020/cm3に増加すると、電子移動度は、約3cm2/(V・秒)から約11cm2/(V・秒)に増加することが示された。また、InGaO3(ZnO)組成を有する多結晶焼結体をターゲットとして得られたアモルファス酸化膜に関しても、同様の傾向が見られた。

【0195】

ガラス基板の代わりに厚さ200μmのポリエチレン・テレフタレート(PET)フィルムを用いた場合にも、得られたIn−Zn−Ga−O系アモルファス酸化物膜は、同様の特性を示した。

(PLD法によるIn−Zn−Ga−Mg−O系アモルファス酸化物膜の成膜)

ターゲットとして多結晶InGaO3(Zn1−xMgxO)4(0<x≦1)を用い、PLD法により、ガラス基板上にInGaO3(Zn1−xMgxO)4(0<x≦1)膜を成膜した。

【0196】

成膜装置は、図48に記載の装置を用いた。

【0197】

被成膜基板としては、SiO2ガラス基板(コーニング社製1737)を用意した。その基板に前処理として、超音波脱脂洗浄を、アセトン、エタノール、超純水により各5分間ずつ行った後、空気中100℃で.乾燥させた。ターゲットとしては、InGa(Zn1−xMgxO)4(x=1−0)焼結体(サイズ20mmΦ5mmt)を用いた。

【0198】

ターゲットは、出発原料In2O3:Ga2O3:ZnO:MgO(各4N試薬)を、湿式混合(溶媒:エタノール)、仮焼(1000℃:2h)、乾式粉砕、本焼結(1550℃:2h)を経て作製した。

【0199】

成長室到達真空は、2×10−6(Pa)であり、成長中の酸素分圧は、0.8(Pa)とした。基板温度は、室温(25℃)で行い、ターゲットと被成膜基板間の距離は、30(mm)であった。

【0200】

なお、KrFエキシマレーザーのパワーは、1.5(mJ/cm2/pulse)、パルス幅は、20(nsec)、繰り返し周波数は、10(Hz)、照射スポット径は、1×1(mm角)とした。成膜レートは、7(nm/min)であった。