音源装置

【目的】本発明は、波形メモリから波形データを読み出して楽音信号を発生する音源装置に関し、安価であるにも拘わらずボイス数を多く確保することのできる音源装置を提供することを目的とする。

【構成】本発明の音源装置は、波形データを記憶した波形メモリ24と、制御プログラムを記憶したプログラムメモリ21と、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路23(230)を備えて構成される。

【構成】本発明の音源装置は、波形データを記憶した波形メモリ24と、制御プログラムを記憶したプログラムメモリ21と、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路23(230)を備えて構成される。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、波形メモリから波形データを読み出して楽音信号を発生する音源装置に関する。

【0002】

【従来の技術】近年、パーソナルコンピュータは高機能化・高性能化の傾向にある。このような高機能化の1つとして、近年のパーソナルコンピュータには「楽音発生機能」が備えられるのが一般的になっている。この楽音発生機能は、いわゆる音源ボードと呼ばれるハードウエアで構成された音源装置と、これを制御するためにパーソナルコンピュータに組み込まれたソフトウエアとにより実現されている。

【0003】上記音源装置には波形メモリが搭載されており、この波形メモリから波形データが順次読み出されて楽音信号が生成される。そして、この楽音信号に基づいて楽音が発生される。かかる音源装置では、波形データの読出アドレス計算、波形データの補間、エンベロープの付加等の膨大な信号処理が行われる。かかる信号処理を例えばプロセッサに行わせると膨大な時間がかかる。従って、リアルタイムで楽音信号を生成するために、従来の音源装置は、プロセッサを用いることなくハードウエアで構成されるのが一般的であった。

【0004】しかし、音源装置をハードウエアで構成すると処理の高速化は実現できるが、音源装置の開発に時間がかかり、また、仕様の変更等に柔軟に対応できないという問題があった。

【0005】ところで、近年は、高速動作可能なデジタルシグナルプロセッサ(以下、「DSP」と略する。)が開発され、各種分野に応用可能になってきた。そこで、かかるDSPを使用して音源装置を構成する試みがなされている。

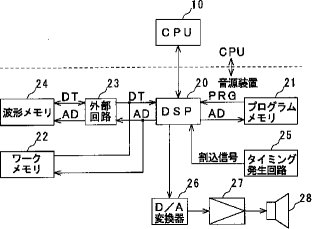

【0006】このようなDSPが使用された音源装置の一例を図10に示す。図10において、10は、例えばパーソナルコンピュータのような中央処理装置(以下、「CPU」という。)である。音源装置は、このCPU10から与えられるデータに応じて動作する。音源装置は、DSP20、プログラムメモリ21、ワークメモリ22、波形メモリ24、タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28で構成されている。

【0007】DSP20は、プログラムメモリ21に記憶された制御プログラムに従って各種処理を行う。DSP20は、プログラムメモリ21にアドレスADを送出し、このアドレスADに応じてプログラムメモリ21から読み出されたプログラムPRGを解釈・実行することにより各種処理を行う。このDSP20が行う処理の詳細については後述する。

【0008】プログラムメモリ21は、DSP20を動作させるための制御プログラムを記憶している。このプログラムメモリ21としては、例えばリードオンリメモリ(以下、「ROM」と略する。)又はランダムアクセスメモリ(以下、RAM」と略する。)が使用されている。なお、プログラムメモリ21がRAMで構成される場合は、音源装置を動作させるに先だって、DSP20の制御の下に、制御プログラムがCPU10からプログラムメモリ21にロードされる(以下、「イニシャルプログラムロード」という)。

【0009】ワークメモリ22は、DSP20が使用する各種データを一時記憶するために使用される。このワークメモリ22はRAMで構成されている。DSP20は、ワークメモリ22にアドレスADを送出してデータDTの書き込み又は読み出しを行う。

【0010】波形メモリ24は、複数の音色(例えば楽器音)に対応する複数の波形データを記憶している。DSP20は、波形メモリ24に所定のアドレスADを送出して波形データDTを読み出す。この波形メモリ24は、例えばROM又はRAMで構成されている。なお、波形メモリ24がRAMで構成される場合は、音源装置を動作させるに先だって、DSP20の制御の下に、波形データがCPU10から波形メモリ24にロードされる(以下、「イニシャル波形データロード」という)。

【0011】タイミング発生回路25は、その時点で設定されているテンポに応じた時間間隔で割込信号を発生してDSP20に供給する。DSP20は、この割込信号を受信したタイミングで全ボイスに対する発音処理を行う。これにより、DSP20は、テンポに応じた時間間隔でデジタル楽音信号を発生する。

【0012】D/A変換器26は、DSP20で生成されたデジタル楽音信号をアナログ楽音信号(オーディオ信号)に変換する。このD/A変換器26から出力されるアナログ楽音信号は、増幅器27で増幅されてスピーカ28に供給される。これにより、スピーカ28から楽音が放音される。

【0013】図11は、DSP20が行う処理を機能的に分類して示したものである。即ち、DSP20の処理部は、メイン部500、CPUインタフェース部501、デジタル制御増幅部(以下、「DCA」部という。)503、累算部504、デジタル制御オシレータ部(以下、「DCO部」という。)530及び補間部531とで構成されている。

【0014】メイン部500は、CPUインタフェース部501、DCA部503、累算部504、DCO部530及び補間部531の間の処理の流れを制御する。CPUインタフェース部501は、CPU10とメイン部500との間のデータ送受を制御する。即ち、CPUインタフェース部501は、CPU10から送られてくるデータを受信してメイン部500に渡し、逆に、メイン部500から送られてきたデータをCPU10に渡す。

【0015】DCO部530は、メイン部500からの指示に応じて、波形メモリ24に与える読出アドレスADを生成する。このDCO部530は、ボイス数に対応する数の読出アドレス生成部で構成されている。各読出アドレス生成部は、例えば1つの音色に対応する一連の波形データを順次読み出すための読出アドレスを生成する。各読出アドレス生成部によって読み出される波形データ(音色)の先頭アドレス、及び、順次読み出す際の読出アドレスの増分値は、それぞれCPU10から与えられるパラメータによって決定される。各読出アドレス生成部は、上記先頭アドレスから上記増分値を順次累算して出力する。

【0016】このDCO部530の各読出アドレス生成部から出力される読出アドレスADが時分割で波形メモリ24に与えられることにより波形データが読み出される。波形メモリ24から読み出された波形データは、DSP20の補間部531に供給される。

【0017】補間部531は、波形メモリ24から読み出された波形データの補間をとって出力する。この補間部531は、ボイス数に対応する数の補間値生成部で構成されている。各補間値生成部は、例えば1つの音色に対応する各波形データを順次補間する。補間は、読出アドレスの前後の整数アドレスに格納されている2つの波形データを、その読出アドレスの小数部の値に応じて案分して新たな波形データを作成することにより行われる。この補間部531の各補間値生成部で時分割で生成された波形データはDCA部503に送られる。

【0018】DCA部503は、補間部531で作成された波形データの振幅を制御することよりエンベロープを付加する処理を行う。このDCA部503は、ボイス数に対応する数の振幅制御部で構成されている。エンベロープの形状は、CPU10からDSP20を介して送られてくるパラメータに従って決定される。このDCA部503の各振幅制御部で時分割でエンベロープが付加された波形データは累算部504に送られる。

【0019】累算部504は、出力系列(例えば左チャンネルと右チャンネル)毎に、DCA部503から時分割で送られてくる波形データに重み付けし、それを累算する。この累算部504で累算された出力系列毎の波形データがデジタル楽音信号としてD/A変換器26に供給される。

【0020】

【発明が解決しようとする課題】従来のDSPを使用した音源装置は、上記のように構成されているので、当該音源装置で確保できるボイス数は、DSPの処理性能(速度)に依存して決定される。DCO部530の読出アドレス生成処理、補間部531の補間処理及びDCA部503の振幅制御処理は、各ボイス毎に、しかもリアルタイム性を損なうことなくデジタル楽音信号を生成するためには一定時間内に行う必要がある。従って、DSPが処理可能なボイス数はDSPの処理性能によって自ずと決定される。

【0021】高性能のDSPを用いればボイス数を多く確保することができるが高性能のDSPは高価格であり音源装置が高価になってしまう。一方、音源装置の価格を抑えようとすれば、低価格・低性能のDSPを使用せざるを得ないが、ボイス数が少なくなる。ボイス数が少ないと、発生する楽音が貧弱になったり、場合によっては所望の楽音が得られないという事態が発生する。

【0022】本発明は、安価であるにも拘わらずボイス数を多く確保することのできる音源装置を提供することを目的とする。

【0023】

【課題を解決するための手段】上記目的を達成するために、本発明の音源装置は、波形データを記憶した波形メモリと、制御プログラムを記憶したプログラムメモリと、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路と、該アドレス生成回路で生成された読出アドレスによって前記波形メモリから読み出された波形データを、該読出アドレスの一部に基づいて補間して前記処理装置に供給する補間回路とを備えている。

【0024】

【作用】従来の音源装置において、例えばDSPやCPUといった処理装置でアドレス生成処理を行っていた。これに対して、本発明の音源装置においては、かかるアドレス生成処理を、処理装置の外部に設けられたアドレス生成回路で行う。また、上記アドレス生成回路で生成された読出アドレスに基づいて波形メモリから読み出された波形データを補間する処理を、処理装置の外部に設けられた補間回路で行う。これにより、更に処理装置の負荷(処理時間)が軽減される。

【0025】

【実施例】以下、本発明の音源装置の実施例につき、図面を参照しながら詳細に説明する。なお、以下の実施例では、PCM変調(Pulse Code Modulation)された波形データを波形メモリに記憶しておき、この波形データを読み出して補間しながら楽音信号を発生するPCM音源装置について説明するが、本発明はPCM音源装置に限定されるものではなく、例えばADPCM変調(Adaptive DifferentialPulse Code Modulation )方式やDPCM変調(Differential Pulse Code Modulation)方式の音源装置のように、予め作成された波形データを波形メモリに記憶しておき、これを読み出して補間しつつ楽音信号を発生するあらゆる音源装置に適用できる。

【0026】なお、以下の説明においては、「従来の技術」の項で説明したものと同一又は相当部分には同一符号を付し、説明を省略し又は簡単化する。

【0027】図1は本発明の音源装置の実施例の構成を示すブロック図である。本実施例は外部回路23を有し、DSP20は外部回路23を介して波形メモリ24にアクセスする点で、従来の音源装置と相違する。

【0028】図1において、10はCPUである。音源装置は、このCPU10から与えられるデータに応じて動作する。CPU10から音源装置に送られるデータには、例えば、波形データ、制御プログラム、音源制御用パラメータ(詳細は後述する)等が含まれる。上記波形データは波形メモリ24に、制御プログラムはプログラムメモリ21にそれぞれロードされる。また、音源制御用パラメータは、一旦ワークメモリ22にロードされ、必要に応じて取り出されて各種処理に使用される。

【0029】音源装置は、DSP20、プログラムメモリ21、ワークメモリ22、外部回路23、波形メモリ24、タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28で構成されている。

【0030】DSP20としては、例えば汎用のDSPを用いることができる。DSP20は本音源装置の中核をなすものであり、既に説明したように、プログラムメモリ21に記憶された制御プログラムに従って各種処理を行う。このDSP20が行う処理の一部は、「従来の技術」の欄で説明したものとは異なる(詳細は後述する)。

【0031】プログラムメモリ21は例えばROMで構成され、既に説明したように、制御プログラムを記憶する。このプログラムメモリ21はRAMで構成することもできる。この場合は、本音源装置を動作させるに先立って、イニシャルプログラムロードが行われる。

【0032】ワークメモリ22は「従来の技術」の欄で説明したものと同じである。本音源装置が備えているRAMの一部は、ワークメモリ22及び外部回路バッファ212に割り当てられている。ワークメモリ22には、例えば図4に示されるように、音源制御用パラメータが記憶されている。音源制御用パラメータは、各ボイスに対応してnセット(ボイス0〜ボイスn−1)設けられており、各音源制御用パラメータは、アドレス生成用パラメータ、振幅制御用パラメータ及び必要に応じてパンポットデータで構成されている。

【0033】アドレス生成用パラメータには、スタートアドレスSA、ループトップアドレスLT、ループエンドアドレスLE及び角周波数データωが含まれている。ここに、スタートアドレスSAは、各音色に対応する各波形データ群が格納されている領域の先頭アドレスである。ループトップアドレスLTは、上記波形データ群のうち、繰り返し読み出しの対象となる領域の先頭アドレスである。ループエンドアドレスLEは、上記波形データ群のうち、繰り返し読み出しの対象となる領域の最終アドレスである。角周波数データωは音高を規定するために使用される。具体的には、角周波数データωは、波形メモリ24から波形データをシーケンシャルに読み出す際の現読出アドレスCAの増分値である。この角周波数データωは小数点以下の有効数字を有する。現読出アドレスCAは整数部(整数アドレスCAI)と小数部(小数アドレスCAF)とで構成される。

【0034】本音源装置では、スタートアドレスSAを現読出アドレスCAとして波形データの読み出しが開始され、以後は、この現読出アドレスCAに角周波数データωを順次累算した値を新しい現読出アドレスCAとして波形データの読み出しが行われる。そして、現読出アドレスCAがループエンドアドレスLEに至ったらループトップアドレスLTに戻って波形データの読み出しが継続され、以下同様の動作が繰り返される。

【0035】振幅制御用パラメータは、レベルデータとスピードデータとで構成されている。更に詳しくは、アタック用のレベルデータとスピードデータ、ディケイ用のレベルデータとスピードデータ、及びリリース用スピードデータとで構成されている。これら各データは、何れも波形データにエンベロープを付加するために使用される。

【0036】パンポットデータは、音源装置で、例えば2系列(左右両チャンネル)用の楽音信号に基づいて形成される音像定位を定めるために使用される。例えば図3R>3に示されるように、0000H〜FFFFH(末桁の「H」は16進数であることを示す。以下においても同じ。)のパンポットデータに対し、図示する特性をもって各チャンネルの音量が制御される。図示例の特性では、パンポットデータが0000Hに近づく程音像は左に偏り、FFFFHに近づく程音像は右に偏る。

【0037】外部回路バッファ212は、外部回路インタフェース部202内に設けられるバッファであり、外部回路23内のDCO部230と、DSP20内のメイン部200とのデータの送受を行うために使用される。この外部回路バッファ212には、現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE、角周波数データω、次読出アドレスCAN、補間済み波形データを記憶する領域が定義されている。

【0038】メイン部200が外部回路23にアドレス生成用パラメータを渡すときは、アドレス生成用パラメータ(現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE、角周波数データω)を、この外部回路バッファ212にセットする。また、外部回路23からは、次読出アドレスCAN及び補間済み波形データWDがこの外部回路バッファ212に入力される。この外部回路バッファ212の詳細については後述する。

【0039】波形メモリ24は例えばROMで構成され、既に説明したように、複数の音色を発生するための複数の波形データを記憶している。この波形メモリ24はRAMで構成することができる。この場合は、CPU10から波形メモリ24にデータをロードするためのロードパスが新たに設けられる。そして、本音源装置を動作させるに先だって、イニシャル波形データロードが行われる。

【0040】外部回路23は、波形メモリ24に対する読出アドレスを生成するDCO部230と、波形メモリ24から読み出された波形データの補間をとる補間部240とから構成されている(図2参照)。DCO部230はアドレス生成回路に対応するものであり、従来の音源装置において、DSP20のソフトウエア機能により実現されていたアドレス生成処理をハードウエア化したものである。同様に、補間部240は補間回路に対応するものであり、従来の音源装置において、DSP20のソフトウエア機能により実現されていた補間処理をハードウエア化したものである。これらの詳細については後述する。

【0041】タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28は、「従来の技術」の欄で説明したものと同じである。但し、D/A変換器26、増幅器27及びスピーカ28は、図1及び図2においては1個しか記載されていないが、左右両チャンネル用として2個が用意されている。

【0042】図2は、DSP20が行う処理を機能的に分類して示したものである。即ち、DSP20の処理部は、メイン部200、CPUインタフェース部201、外部回路インタフェース部202、DCA部203及び累算部204とで構成されている。

【0043】メイン部200は、CPUインタフェース部201、外部回路インタフェース部202、DCA部203及び累算部204の間の処理の流れを制御する。CPUインタフェース部201の機能は、従来の技術の欄で説明したCPUインタフェース部501の機能と同じである。

【0044】外部回路インタフェース部202は、外部回路23とDSP20との間のデータ送受を制御する。例えば、外部インタフェース部202では、メイン部200から送られてくるデータを外部回路23に渡し、外部回路23から送られてくるデータをDCA部203に渡す処理が行われる。更に詳しくは、外部回路インタフェース部202は、メイン部200から送られてきたアドレス生成用パラメータをDCO部230に渡すと共に、DCO部230で算出された現読出アドレスCAを記憶する。また、外部回路インタフェース部202は、現読出アドレスCAの小数アドレスCAFを補間部240に渡すと共に、補間部240から送られてくる補間済み波形データをDCA部203に渡す。

【0045】DCA部203及び累算部204は、それぞれ、従来の技術の欄で説明したDCA部503及び累算部504と同じ機能を有する。

【0046】次に、外部回路23に含まれるDCO部230及び補間部240のそれぞれの詳細につき、図5及び図6を参照しながら説明する。

【0047】図5は、DCO部230の回路構成を示す。DCO部230には、図示されるように、メイン部200から外部回路インタフェース部202を経由してアドレス生成用パラメータが与えられる。アドレス生成用パラメータは、現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE及び角周波数データωで成る。なお、初期状態においては、現読出アドレスCAはスタートアドレスSAである。DCO部230は、これら各データに基づき、波形メモリ24に与える整数アドレスCAI及びCAI+1、並びに次読出アドレスCANを生成する。なお、波形メモリ24の容量が大きい場合は、バンクアドレスBAを用いるように構成することもできる。このバンクアドレスBAは波形メモリ24に形成されたバンクを指定するために使用される。以下においては、バンクアドレスBAは存在しないものとして説明する。

【0048】DCO部230は、加算器231、233、236、237、インバータ232、234、セレクタ235及び遅延回路238で構成されている。各加算器231、233、236、237のAは被加数の入力端子、Bは加数の入力端子、CIはキャリーの入力端子、COはキャリーの出力端子であり、以下においても同じである。

【0049】バンクアドレスBAを有する音源装置においては、そのまま出力されて波形メモリ24に供給される。また、現読出アドレスCAのうちの整数アドレスCAIは、そのまま出力されて波形メモリ24に供給される。また、現読出アドレスCA(整数アドレス及び小数アドレス)は加算器231及び237の各A入力端子に供給される。加算器231は、DCO部230からB入力端子に供給されている角周波数データωと現読出アドレスCAとを加算し、仮の次読出アドレスCA1として出力する。この仮の次読出アドレスCA1はインバータ232で反転されて加算器233のA入力端子に供給される。

【0050】加算器233は、DCO部230からB入力端子に供給されているループエンドアドレスLEとインバータ232の出力とを、キャリー入力を「1」として加算する。これにより、ループエンドアドレスLEと仮の次読出アドレスCA1の2の補数とが加算される。換言すれば、ループエンドアドレスLEから仮の次読出アドレスCA1が減算される。

【0051】この加算器233による加算の結果、キャリーが発生すれば「仮の次読出アドレスCA1≦ループエンドアドレスLE」であり、仮の次読出アドレスCA1がループエンドアドレスLEを越えていないことが判断される。一方、キャリーが発生しなければ「仮の次読出アドレスCA1>ループエンドアドレスLE」であり、仮の次読出アドレスCA1がループエンドアドレスLEを越えたことが判断される。

【0052】この加算器233のキャリー出力はセレクタ235のセレクト端子Sに供給される。加算器233の出力は、ループエンドアドレスLEと仮の次読出アドレスCA1との差Δであり、仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は正の値、仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は負の値として得られる。加算器233の出力Δは、インバータ234で反転されて加算器236のA入力端子に供給される。

【0053】セレクタ235は、加算器233からのキャリーに応じてループエンドアドレスLE又はループトップアドレスLTの何れかを選択して出力する。即ち、セレクタ235は、加算器233でキャリーが発生した場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は、ループエンドアドレスLEを出力し、加算器233でキャリーが発生しない場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は、ループトップアドレスLTを出力する。このセレクタ235の出力は、加算器236のB入力端子に供給される。

【0054】加算器236は、セレクタ235の出力とインバータ232の出力とを、キャリー入力を「1」として加算する。これにより、セレクタ235の出力と差Δの2の補数とが加算される。換言すれば、セレクタ235の出力から差Δが減算される。これは、加算器233からキャリーが発生したかどうかにより、次のように動作する。

【0055】即ち、キャリーが発生した場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は、ループエンドアドレスLEから差Δ(正の値)が減算される。これにより、上記仮の次読出アドレスCA1が次読出アドレスCANとして加算器236から出力される。一方、キャリーが発生していない場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は、ループトップアドレスLTから差Δ(負の値)を減算する。これにより、次読出アドレスCANがループトップアドレスLTにラウンドする機能が実現されている。この加算器236から出力される次読出アドレスCANは、DSP20に送られ、次回の現読出アドレスCAの生成のために保存される。

【0056】また、加算器237は、現読出アドレスCAのうちの整数アドレスCAIを「+1」して出力する。この加算器237の出力は遅延回路238に供給される。遅延回路238は、加算器237の出力を一定時間遅延させて次の整数アドレスCAI+1として出力する。この整数アドレスCAI+1は、波形メモリ24に供給される。ここに一定時間とは、波形メモリ24が整数アドレスCAIを受け取ってから波形データの読み出しを完了するまでの時間である。従って、波形メモリ24からは、整数アドレスCAIに対応する波形データと整数アドレスCAI+1に対応する波形データとが一定時間間隔をおいて連続して読み出される。

【0057】図6は、補間部240の回路構成を示す。補間部240には、図示されるように、メイン部200から外部インタフェース部202を経由してアドレス生成用パラメータのうちの読出アドレスの小数アドレスCAFが与えられる。なお、初期状態においては、現読出アドレスCAはスタートアドレスSAであり、その小数アドレスCAFはゼロである。

【0058】補間部240は、ラッチ241、インバータ242、加算器243、乗算器244及び加算器245とにより構成されている。

【0059】波形メモリ24から読み出された整数アドレスCAIに対応する波形データWD0は、ラッチ241に一旦ラッチされる。このラッチ241の出力は、インバータ242で反転されて加算器243のA入力端子に供給されると共に、加算器245のA入力端子に供給される。

【0060】上記波形データWD0が読み出されてから上記一定時間経過後に波形データWD1が読み出されて加算器243のB入力端子に供給される。加算器243は、インバータ242の出力とB入力端子に供給された波形データWD1とを、キャリー入力を「1」として加算する。これにより、波形データWD1に波形データWD0の2の補数が加算される、換言すれば、波形データWD1から波形データWD0が減算される。この加算器243の出力は、乗算器244のB入力端子に供給される。一方、乗算器244のA入力端子には現読出アドレスCAの小数部(小数アドレスCAF)が供給されている。従って、この乗算器244からは、上記波形データWD1と波形データWD0との差が小数アドレスCAFの値に応じて案分された値が出力される。この乗算器244の出力は、加算器245のB入力端子に供給される。

【0061】加算器245のA入力端子には波形データWD0が供給されている。従って、この加算器245からは、波形データWD0に上記案分された値が加算された波形データ、つまり補間がとられた波形データWDが出力される。この波形データWDは、DSP20の外部回路インタフェース部202を介してDCA部203に供給される。

【0062】なお、上記補間部240として、直線補間をする場合の回路構成例を示したが、これに限定されるものではない。例えば最小二乗法、その他のいかなる補間方法をも用いることができる。

【0063】次に、上記の構成において、本音源装置の動作について、図7〜図9のフローチャートを参照しながら説明する。なお、各フローチャートに示された処理は、DSP20によって行われる。

【0064】図7は、本音源装置のメインルーチンを示すフローチャートであり、主としてDSP20のメイン部200によって行われる処理である。このメインルーチンは、電源投入により起動される。即ち、電源が投入されると、先ず、初期化処理が行われる(ステップS10)。

【0065】この初期化処理では、DSP20の内部状態が初期状態に設定されると共に、図示しないRAMに定義されているレジスタ、カウンタ或いはフラグ等に初期値が設定される。この初期化処理が終了すると、次いで、パラメータ転送の有無が調べられる(ステップS11)。即ち、CPU10から音源制御用パラメータが送られてきたかどうかが調べられる。これは、例えばメイン部200がCPUインタフェース部201に設けられている受信バッファ(図示しない)を調べることにより行われる。そして、パラメータ転送があることが判断されると、受信されたパラメータがワークメモリ22に転送される(ステップS12)。ステップS11でパラメータ転送がないことが判断されると、このステップS12はスキップされる。

【0066】次いで、発音タイミングであるかどうかが調べられる(ステップS13)。これは発音フラグを参照することにより行われる。ここに、発音フラグとは、図示しないRAMに設けられるフラグであり、各ボイスの発音処理を実行すべきタイミングであるかどうかを記憶するために使用される。この発音フラグは、後述する割込処理ルーチンにおいてセットされる。

【0067】ここで発音タイミングでないことが判断されるとステップS11に戻り、上述した処理を繰り返す。即ち、DSP20のメイン部200は、通常は、ステップS11〜S13を繰り返し実行しながらCPU10からパラメータが転送されてくるのを待って待機している。そして、CPU10からパラメータが転送されてくるとこれをワークメモリ22に転送する。このステップS11〜S13の繰り返しの中で、ステップS13において発音タイミングであることが判断されると、ステップS14以下の発音処理に移る。

【0068】発音処理では、先ず、DSP20は割込禁止モードにされる(ステップS14)。これにより、後述するステップS21で割込禁止モードが解除されるまでは、割込処理ルーチンがコールされることはない。従って、発音フラグがオンにされることもない。次いで、各ボイスに付された番号nが「0」にクリアされる(ステップS15)。

【0069】次いで、ボイスnに対する発音処理が行われる(ステップS16)。この処理では、ボイスnの波形データを出力系列毎に累算する処理が行われる(詳細については後述する)。次いで、上記番号nがインクリメントされ(ステップS17)、その番号nが本音源装置の総ボイス数に等しくなったかどうかが調べられる(ステップS18)。そして、等しくなければステップS16に戻って次のボイスに対する発音処理が行われる。

【0070】上記繰り返しにおいて、番号nが本音源装置の総ボイス数に等しくなったことが判断されると、次いで、上記ステップS16で生成された系列毎の波形データの累算値が出力される(ステップS19)。この波形データの累算値は、系列毎にD/A変換器26に送られる。その後、系列毎の波形データの累算値はクリアされ、次の発音処理に備えられる。

【0071】次いで、発音フラグがオフにされる(ステップS20)。そして、割込禁止モードが解除され(ステップS21)、その後、ステップS11に戻って以下同様の処理が行われる。

【0072】次に、上記ステップS16で行われるボイスnの発音処理の詳細について、図8を参照しながら説明する。この発音処理は、DSP20のメイン部200及びDCA部203で行われる処理に対応する。先ず、ボイスnに対応するアドレス生成用パラメータがワークメモリ22から読み出される(ステップS30)。この読み出されたアドレス生成用パラメータは、外部回路23に送られる(ステップS31)。これにより、外部回路23のDCO部230及び補間部240は、上述した動作により、次読出アドレスCANを算出すると共に、現読出アドレスCAの中の整数アドレスCAI及びCAI+1から波形データWD0及びWD1を読み出して補間を行う。この外部回路23で算出された次読出アドレスCAN及び補間済み波形データWDは外部回路インタフェース部202の外部回路バッファ212に格納される(図4参照)。

【0073】この外部回路23の動作と並行して、ワークメモリ22から振幅制御用パラメータが読み出され(ステップS32)、この読み出された振幅制御用パラメータから現在の発音タイミングにおけるエンベロープデータが計算される(ステップS33)。このステップS33の処理は、DCA部203で行われる処理に対応する。次いで、外部回路インタフェース部202の外部回路バッファ212から次読出アドレスCAN及び補間済み波形データWDが取り出され(ステップS34)、次読出アドレスCANは、ワークメモリ22の現読出アドレスCAの格納領域に転送される(ステップS35)。

【0074】次いで、外部回路バッファ212に格納されている補間済み波形データWDと上記ステップS33で算出されたエンベロープデータとが乗算される(ステップS36)。このステップS36の処理は、DCA部203で行われる処理に対応する。そして、この乗算結果がパンポットデータに応じて出力系列毎(例えばLチャンネル及びRチャンネル毎)に重み付けされ累算される(ステップS37)。重み付けは、音源制御用パラメータに含まれるパンポットデータに従って、例えば図3に示される音量特性となるように、上記乗算結果に演算又はテーブル変換を施すことにより実現できる。このステップS37の処理は、累算部204の処理に対応する。なお、パンポットデータによる音量特性は、図3に示される特性に限定されず、任意の特性を使用することができる。その後、この発音処理ルーチンからリターンしてメインルーチンに戻る。

【0075】図9には、割込処理ルーチンが示されている。この割込処理ルーチンは、タイミング発生回路25から割込信号が発生される度にコールされる。この割込処理ルーチンでは、発音フラグをオンにする処理が行われる(ステップS40)。この発音フラグがオンにされることにより、メインルーチンのステップS13で発音タイミングが到来したことが判断される。

【0076】以上説明したように、本実施例によれば、従来の音源装置において、例えばDSPやCPUといった処理装置でアドレス生成処理及び補間処理を行っていた。これに対して、本発明の音源装置においては、かかるアドレス生成処理及び補間処理を、処理装置の外部に設けられた外部回路に搭載されたアドレス生成回路及び補間回路で行うようにした。これにより、処理装置の負荷(処理時間)が軽減される。

【0077】なお、本発明では、ハードウエア化する部分については上記実施例に示したものに限定されず、DSP20の処理によって実現されているデジタル制御増幅部(DCA部203)の機能の全部又は一部をハードウエア化して外部回路23とすることも可能である。更に、上記実施例では、DSP20が行う処理として、音源装置で一般的に行われる代表的な機能に対する処理のみについて説明したが、DSP20ではその他の各種処理、例えばフィルタ演算処理によるグロウル効果の他、ディレイ、コーラス、リバーブ、3D等の音響効果を付加する処理等を行っても良く、本発明では、かかる各種処理を実現する機能をハードウエア化して外部回路とすることも可能である。

【0078】また、上記実施例では、ステレオ出力を可能にする2系列(L及びR)の出力を有する音源装置について説明したが、これに限定されるものではない。即ち、本発明は、モノラル出力の音源装置についても同様に適用できる。この場合、パンポットデータは不要であり、また、図8に示した発音処理のステップS37では、出力系列毎に重み付けして加算するのではなく、全ての乗算結果を単純に加算するように構成すれば良い。

【0079】更に、本発明は、3系列以上の出力を有する音源装置にも適用できる。この場合、多チャンネルによる音像定位を制御するパンポットデータを用意し、図8R>8に示した発音処理のステップS37は、3以上の出力系列毎に重み付けして加算するように構成すれば良い。

【0080】

【発明の効果】以上詳述したように、本発明の音源装置によれば、安価であるにも拘わらずボイス数を多く確保することのできる音源装置を提供できる。

【0081】即ち、本音源装置においては、アドレス生成処理を、処理装置の外部に設けられたアドレス生成回路で行うようにしているので、処理装置の負荷が軽減され、この軽減された負荷に対応する時間で更に他のボイスの処理を行うことができる。これにより、ボイス数を増やすことができるので、発生すべき楽音が貧弱になったり、所望の楽音が得られないという事態の発生を防止できる。また、高価な処理装置を使用する必要もないので、安価な音源装置を実現できる。

【0082】また、本音源装置においては、アドレス生成回路に加え、補間処理を外部に設けられた補間回路という簡単な回路で行うようにしているので、処理装置の負荷が更に軽減され、この軽減された負荷に対応する時間で更に他のボイスの処理を行うことができる。これにより、更にボイス数を増やすことができるので、発生すべき楽音が貧弱になったり、所望の楽音が得られないという事態の発生を防止できる。

【0083】また、上記軽減された処理時間を用いて音響効果の付加、例えばフィルタ演算による音色変化を行わせれば、より表情豊かな楽音を発生させることも可能となる。

【図面の簡単な説明】

【図1】本発明の実施例の音源装置の構成を示すブロック図である。

【図2】本発明の実施例におけるDSPが行う処理を機能的に分類して示した図である。

【図3】本発明の実施例におけるパンポットデータの一例を示す図である。

【図4】本発明の実施例で使用されるRAMの割り当ての一例を示す図である。

【図5】本発明の実施例における外部回路のDCO部の回路構成を示す図である。

【図6】本発明の実施例における外部回路の補間部の回路構成を示す図である。

【図7】本発明の実施例の音源装置のメインルーチンを示すフローチャートである。

【図8】本発明の実施例の音源装置の発音処理を示すフローチャートである。

【図9】本発明の実施例の音源装置の割込処理を示すフローチャートである。

【図10】従来の音源装置の構成を示すブロック図である。

【図11】従来の音源装置におけるDSPが行う処理を機能的に分類して示した図である。

【符号の説明】

10 CPU

20 DSP

21 プログラムメモリ

22 ワークメモリ

23 外部回路

24 波形メモリ

25 タイミング発生回路

26 D/A変換器

27 増幅器

28 スピーカ

200、500 メイン部

201、501 CPUインタフェース部

202 外部回路インタフェース部

203、503 DCA部

204、504 累算部

230、530 DCO部

240、531 補間部

【0001】

【産業上の利用分野】本発明は、波形メモリから波形データを読み出して楽音信号を発生する音源装置に関する。

【0002】

【従来の技術】近年、パーソナルコンピュータは高機能化・高性能化の傾向にある。このような高機能化の1つとして、近年のパーソナルコンピュータには「楽音発生機能」が備えられるのが一般的になっている。この楽音発生機能は、いわゆる音源ボードと呼ばれるハードウエアで構成された音源装置と、これを制御するためにパーソナルコンピュータに組み込まれたソフトウエアとにより実現されている。

【0003】上記音源装置には波形メモリが搭載されており、この波形メモリから波形データが順次読み出されて楽音信号が生成される。そして、この楽音信号に基づいて楽音が発生される。かかる音源装置では、波形データの読出アドレス計算、波形データの補間、エンベロープの付加等の膨大な信号処理が行われる。かかる信号処理を例えばプロセッサに行わせると膨大な時間がかかる。従って、リアルタイムで楽音信号を生成するために、従来の音源装置は、プロセッサを用いることなくハードウエアで構成されるのが一般的であった。

【0004】しかし、音源装置をハードウエアで構成すると処理の高速化は実現できるが、音源装置の開発に時間がかかり、また、仕様の変更等に柔軟に対応できないという問題があった。

【0005】ところで、近年は、高速動作可能なデジタルシグナルプロセッサ(以下、「DSP」と略する。)が開発され、各種分野に応用可能になってきた。そこで、かかるDSPを使用して音源装置を構成する試みがなされている。

【0006】このようなDSPが使用された音源装置の一例を図10に示す。図10において、10は、例えばパーソナルコンピュータのような中央処理装置(以下、「CPU」という。)である。音源装置は、このCPU10から与えられるデータに応じて動作する。音源装置は、DSP20、プログラムメモリ21、ワークメモリ22、波形メモリ24、タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28で構成されている。

【0007】DSP20は、プログラムメモリ21に記憶された制御プログラムに従って各種処理を行う。DSP20は、プログラムメモリ21にアドレスADを送出し、このアドレスADに応じてプログラムメモリ21から読み出されたプログラムPRGを解釈・実行することにより各種処理を行う。このDSP20が行う処理の詳細については後述する。

【0008】プログラムメモリ21は、DSP20を動作させるための制御プログラムを記憶している。このプログラムメモリ21としては、例えばリードオンリメモリ(以下、「ROM」と略する。)又はランダムアクセスメモリ(以下、RAM」と略する。)が使用されている。なお、プログラムメモリ21がRAMで構成される場合は、音源装置を動作させるに先だって、DSP20の制御の下に、制御プログラムがCPU10からプログラムメモリ21にロードされる(以下、「イニシャルプログラムロード」という)。

【0009】ワークメモリ22は、DSP20が使用する各種データを一時記憶するために使用される。このワークメモリ22はRAMで構成されている。DSP20は、ワークメモリ22にアドレスADを送出してデータDTの書き込み又は読み出しを行う。

【0010】波形メモリ24は、複数の音色(例えば楽器音)に対応する複数の波形データを記憶している。DSP20は、波形メモリ24に所定のアドレスADを送出して波形データDTを読み出す。この波形メモリ24は、例えばROM又はRAMで構成されている。なお、波形メモリ24がRAMで構成される場合は、音源装置を動作させるに先だって、DSP20の制御の下に、波形データがCPU10から波形メモリ24にロードされる(以下、「イニシャル波形データロード」という)。

【0011】タイミング発生回路25は、その時点で設定されているテンポに応じた時間間隔で割込信号を発生してDSP20に供給する。DSP20は、この割込信号を受信したタイミングで全ボイスに対する発音処理を行う。これにより、DSP20は、テンポに応じた時間間隔でデジタル楽音信号を発生する。

【0012】D/A変換器26は、DSP20で生成されたデジタル楽音信号をアナログ楽音信号(オーディオ信号)に変換する。このD/A変換器26から出力されるアナログ楽音信号は、増幅器27で増幅されてスピーカ28に供給される。これにより、スピーカ28から楽音が放音される。

【0013】図11は、DSP20が行う処理を機能的に分類して示したものである。即ち、DSP20の処理部は、メイン部500、CPUインタフェース部501、デジタル制御増幅部(以下、「DCA」部という。)503、累算部504、デジタル制御オシレータ部(以下、「DCO部」という。)530及び補間部531とで構成されている。

【0014】メイン部500は、CPUインタフェース部501、DCA部503、累算部504、DCO部530及び補間部531の間の処理の流れを制御する。CPUインタフェース部501は、CPU10とメイン部500との間のデータ送受を制御する。即ち、CPUインタフェース部501は、CPU10から送られてくるデータを受信してメイン部500に渡し、逆に、メイン部500から送られてきたデータをCPU10に渡す。

【0015】DCO部530は、メイン部500からの指示に応じて、波形メモリ24に与える読出アドレスADを生成する。このDCO部530は、ボイス数に対応する数の読出アドレス生成部で構成されている。各読出アドレス生成部は、例えば1つの音色に対応する一連の波形データを順次読み出すための読出アドレスを生成する。各読出アドレス生成部によって読み出される波形データ(音色)の先頭アドレス、及び、順次読み出す際の読出アドレスの増分値は、それぞれCPU10から与えられるパラメータによって決定される。各読出アドレス生成部は、上記先頭アドレスから上記増分値を順次累算して出力する。

【0016】このDCO部530の各読出アドレス生成部から出力される読出アドレスADが時分割で波形メモリ24に与えられることにより波形データが読み出される。波形メモリ24から読み出された波形データは、DSP20の補間部531に供給される。

【0017】補間部531は、波形メモリ24から読み出された波形データの補間をとって出力する。この補間部531は、ボイス数に対応する数の補間値生成部で構成されている。各補間値生成部は、例えば1つの音色に対応する各波形データを順次補間する。補間は、読出アドレスの前後の整数アドレスに格納されている2つの波形データを、その読出アドレスの小数部の値に応じて案分して新たな波形データを作成することにより行われる。この補間部531の各補間値生成部で時分割で生成された波形データはDCA部503に送られる。

【0018】DCA部503は、補間部531で作成された波形データの振幅を制御することよりエンベロープを付加する処理を行う。このDCA部503は、ボイス数に対応する数の振幅制御部で構成されている。エンベロープの形状は、CPU10からDSP20を介して送られてくるパラメータに従って決定される。このDCA部503の各振幅制御部で時分割でエンベロープが付加された波形データは累算部504に送られる。

【0019】累算部504は、出力系列(例えば左チャンネルと右チャンネル)毎に、DCA部503から時分割で送られてくる波形データに重み付けし、それを累算する。この累算部504で累算された出力系列毎の波形データがデジタル楽音信号としてD/A変換器26に供給される。

【0020】

【発明が解決しようとする課題】従来のDSPを使用した音源装置は、上記のように構成されているので、当該音源装置で確保できるボイス数は、DSPの処理性能(速度)に依存して決定される。DCO部530の読出アドレス生成処理、補間部531の補間処理及びDCA部503の振幅制御処理は、各ボイス毎に、しかもリアルタイム性を損なうことなくデジタル楽音信号を生成するためには一定時間内に行う必要がある。従って、DSPが処理可能なボイス数はDSPの処理性能によって自ずと決定される。

【0021】高性能のDSPを用いればボイス数を多く確保することができるが高性能のDSPは高価格であり音源装置が高価になってしまう。一方、音源装置の価格を抑えようとすれば、低価格・低性能のDSPを使用せざるを得ないが、ボイス数が少なくなる。ボイス数が少ないと、発生する楽音が貧弱になったり、場合によっては所望の楽音が得られないという事態が発生する。

【0022】本発明は、安価であるにも拘わらずボイス数を多く確保することのできる音源装置を提供することを目的とする。

【0023】

【課題を解決するための手段】上記目的を達成するために、本発明の音源装置は、波形データを記憶した波形メモリと、制御プログラムを記憶したプログラムメモリと、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路と、該アドレス生成回路で生成された読出アドレスによって前記波形メモリから読み出された波形データを、該読出アドレスの一部に基づいて補間して前記処理装置に供給する補間回路とを備えている。

【0024】

【作用】従来の音源装置において、例えばDSPやCPUといった処理装置でアドレス生成処理を行っていた。これに対して、本発明の音源装置においては、かかるアドレス生成処理を、処理装置の外部に設けられたアドレス生成回路で行う。また、上記アドレス生成回路で生成された読出アドレスに基づいて波形メモリから読み出された波形データを補間する処理を、処理装置の外部に設けられた補間回路で行う。これにより、更に処理装置の負荷(処理時間)が軽減される。

【0025】

【実施例】以下、本発明の音源装置の実施例につき、図面を参照しながら詳細に説明する。なお、以下の実施例では、PCM変調(Pulse Code Modulation)された波形データを波形メモリに記憶しておき、この波形データを読み出して補間しながら楽音信号を発生するPCM音源装置について説明するが、本発明はPCM音源装置に限定されるものではなく、例えばADPCM変調(Adaptive DifferentialPulse Code Modulation )方式やDPCM変調(Differential Pulse Code Modulation)方式の音源装置のように、予め作成された波形データを波形メモリに記憶しておき、これを読み出して補間しつつ楽音信号を発生するあらゆる音源装置に適用できる。

【0026】なお、以下の説明においては、「従来の技術」の項で説明したものと同一又は相当部分には同一符号を付し、説明を省略し又は簡単化する。

【0027】図1は本発明の音源装置の実施例の構成を示すブロック図である。本実施例は外部回路23を有し、DSP20は外部回路23を介して波形メモリ24にアクセスする点で、従来の音源装置と相違する。

【0028】図1において、10はCPUである。音源装置は、このCPU10から与えられるデータに応じて動作する。CPU10から音源装置に送られるデータには、例えば、波形データ、制御プログラム、音源制御用パラメータ(詳細は後述する)等が含まれる。上記波形データは波形メモリ24に、制御プログラムはプログラムメモリ21にそれぞれロードされる。また、音源制御用パラメータは、一旦ワークメモリ22にロードされ、必要に応じて取り出されて各種処理に使用される。

【0029】音源装置は、DSP20、プログラムメモリ21、ワークメモリ22、外部回路23、波形メモリ24、タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28で構成されている。

【0030】DSP20としては、例えば汎用のDSPを用いることができる。DSP20は本音源装置の中核をなすものであり、既に説明したように、プログラムメモリ21に記憶された制御プログラムに従って各種処理を行う。このDSP20が行う処理の一部は、「従来の技術」の欄で説明したものとは異なる(詳細は後述する)。

【0031】プログラムメモリ21は例えばROMで構成され、既に説明したように、制御プログラムを記憶する。このプログラムメモリ21はRAMで構成することもできる。この場合は、本音源装置を動作させるに先立って、イニシャルプログラムロードが行われる。

【0032】ワークメモリ22は「従来の技術」の欄で説明したものと同じである。本音源装置が備えているRAMの一部は、ワークメモリ22及び外部回路バッファ212に割り当てられている。ワークメモリ22には、例えば図4に示されるように、音源制御用パラメータが記憶されている。音源制御用パラメータは、各ボイスに対応してnセット(ボイス0〜ボイスn−1)設けられており、各音源制御用パラメータは、アドレス生成用パラメータ、振幅制御用パラメータ及び必要に応じてパンポットデータで構成されている。

【0033】アドレス生成用パラメータには、スタートアドレスSA、ループトップアドレスLT、ループエンドアドレスLE及び角周波数データωが含まれている。ここに、スタートアドレスSAは、各音色に対応する各波形データ群が格納されている領域の先頭アドレスである。ループトップアドレスLTは、上記波形データ群のうち、繰り返し読み出しの対象となる領域の先頭アドレスである。ループエンドアドレスLEは、上記波形データ群のうち、繰り返し読み出しの対象となる領域の最終アドレスである。角周波数データωは音高を規定するために使用される。具体的には、角周波数データωは、波形メモリ24から波形データをシーケンシャルに読み出す際の現読出アドレスCAの増分値である。この角周波数データωは小数点以下の有効数字を有する。現読出アドレスCAは整数部(整数アドレスCAI)と小数部(小数アドレスCAF)とで構成される。

【0034】本音源装置では、スタートアドレスSAを現読出アドレスCAとして波形データの読み出しが開始され、以後は、この現読出アドレスCAに角周波数データωを順次累算した値を新しい現読出アドレスCAとして波形データの読み出しが行われる。そして、現読出アドレスCAがループエンドアドレスLEに至ったらループトップアドレスLTに戻って波形データの読み出しが継続され、以下同様の動作が繰り返される。

【0035】振幅制御用パラメータは、レベルデータとスピードデータとで構成されている。更に詳しくは、アタック用のレベルデータとスピードデータ、ディケイ用のレベルデータとスピードデータ、及びリリース用スピードデータとで構成されている。これら各データは、何れも波形データにエンベロープを付加するために使用される。

【0036】パンポットデータは、音源装置で、例えば2系列(左右両チャンネル)用の楽音信号に基づいて形成される音像定位を定めるために使用される。例えば図3R>3に示されるように、0000H〜FFFFH(末桁の「H」は16進数であることを示す。以下においても同じ。)のパンポットデータに対し、図示する特性をもって各チャンネルの音量が制御される。図示例の特性では、パンポットデータが0000Hに近づく程音像は左に偏り、FFFFHに近づく程音像は右に偏る。

【0037】外部回路バッファ212は、外部回路インタフェース部202内に設けられるバッファであり、外部回路23内のDCO部230と、DSP20内のメイン部200とのデータの送受を行うために使用される。この外部回路バッファ212には、現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE、角周波数データω、次読出アドレスCAN、補間済み波形データを記憶する領域が定義されている。

【0038】メイン部200が外部回路23にアドレス生成用パラメータを渡すときは、アドレス生成用パラメータ(現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE、角周波数データω)を、この外部回路バッファ212にセットする。また、外部回路23からは、次読出アドレスCAN及び補間済み波形データWDがこの外部回路バッファ212に入力される。この外部回路バッファ212の詳細については後述する。

【0039】波形メモリ24は例えばROMで構成され、既に説明したように、複数の音色を発生するための複数の波形データを記憶している。この波形メモリ24はRAMで構成することができる。この場合は、CPU10から波形メモリ24にデータをロードするためのロードパスが新たに設けられる。そして、本音源装置を動作させるに先だって、イニシャル波形データロードが行われる。

【0040】外部回路23は、波形メモリ24に対する読出アドレスを生成するDCO部230と、波形メモリ24から読み出された波形データの補間をとる補間部240とから構成されている(図2参照)。DCO部230はアドレス生成回路に対応するものであり、従来の音源装置において、DSP20のソフトウエア機能により実現されていたアドレス生成処理をハードウエア化したものである。同様に、補間部240は補間回路に対応するものであり、従来の音源装置において、DSP20のソフトウエア機能により実現されていた補間処理をハードウエア化したものである。これらの詳細については後述する。

【0041】タイミング発生回路25、D/A変換器26、増幅器27及びスピーカ28は、「従来の技術」の欄で説明したものと同じである。但し、D/A変換器26、増幅器27及びスピーカ28は、図1及び図2においては1個しか記載されていないが、左右両チャンネル用として2個が用意されている。

【0042】図2は、DSP20が行う処理を機能的に分類して示したものである。即ち、DSP20の処理部は、メイン部200、CPUインタフェース部201、外部回路インタフェース部202、DCA部203及び累算部204とで構成されている。

【0043】メイン部200は、CPUインタフェース部201、外部回路インタフェース部202、DCA部203及び累算部204の間の処理の流れを制御する。CPUインタフェース部201の機能は、従来の技術の欄で説明したCPUインタフェース部501の機能と同じである。

【0044】外部回路インタフェース部202は、外部回路23とDSP20との間のデータ送受を制御する。例えば、外部インタフェース部202では、メイン部200から送られてくるデータを外部回路23に渡し、外部回路23から送られてくるデータをDCA部203に渡す処理が行われる。更に詳しくは、外部回路インタフェース部202は、メイン部200から送られてきたアドレス生成用パラメータをDCO部230に渡すと共に、DCO部230で算出された現読出アドレスCAを記憶する。また、外部回路インタフェース部202は、現読出アドレスCAの小数アドレスCAFを補間部240に渡すと共に、補間部240から送られてくる補間済み波形データをDCA部203に渡す。

【0045】DCA部203及び累算部204は、それぞれ、従来の技術の欄で説明したDCA部503及び累算部504と同じ機能を有する。

【0046】次に、外部回路23に含まれるDCO部230及び補間部240のそれぞれの詳細につき、図5及び図6を参照しながら説明する。

【0047】図5は、DCO部230の回路構成を示す。DCO部230には、図示されるように、メイン部200から外部回路インタフェース部202を経由してアドレス生成用パラメータが与えられる。アドレス生成用パラメータは、現読出アドレスCA、ループトップアドレスLT、ループエンドアドレスLE及び角周波数データωで成る。なお、初期状態においては、現読出アドレスCAはスタートアドレスSAである。DCO部230は、これら各データに基づき、波形メモリ24に与える整数アドレスCAI及びCAI+1、並びに次読出アドレスCANを生成する。なお、波形メモリ24の容量が大きい場合は、バンクアドレスBAを用いるように構成することもできる。このバンクアドレスBAは波形メモリ24に形成されたバンクを指定するために使用される。以下においては、バンクアドレスBAは存在しないものとして説明する。

【0048】DCO部230は、加算器231、233、236、237、インバータ232、234、セレクタ235及び遅延回路238で構成されている。各加算器231、233、236、237のAは被加数の入力端子、Bは加数の入力端子、CIはキャリーの入力端子、COはキャリーの出力端子であり、以下においても同じである。

【0049】バンクアドレスBAを有する音源装置においては、そのまま出力されて波形メモリ24に供給される。また、現読出アドレスCAのうちの整数アドレスCAIは、そのまま出力されて波形メモリ24に供給される。また、現読出アドレスCA(整数アドレス及び小数アドレス)は加算器231及び237の各A入力端子に供給される。加算器231は、DCO部230からB入力端子に供給されている角周波数データωと現読出アドレスCAとを加算し、仮の次読出アドレスCA1として出力する。この仮の次読出アドレスCA1はインバータ232で反転されて加算器233のA入力端子に供給される。

【0050】加算器233は、DCO部230からB入力端子に供給されているループエンドアドレスLEとインバータ232の出力とを、キャリー入力を「1」として加算する。これにより、ループエンドアドレスLEと仮の次読出アドレスCA1の2の補数とが加算される。換言すれば、ループエンドアドレスLEから仮の次読出アドレスCA1が減算される。

【0051】この加算器233による加算の結果、キャリーが発生すれば「仮の次読出アドレスCA1≦ループエンドアドレスLE」であり、仮の次読出アドレスCA1がループエンドアドレスLEを越えていないことが判断される。一方、キャリーが発生しなければ「仮の次読出アドレスCA1>ループエンドアドレスLE」であり、仮の次読出アドレスCA1がループエンドアドレスLEを越えたことが判断される。

【0052】この加算器233のキャリー出力はセレクタ235のセレクト端子Sに供給される。加算器233の出力は、ループエンドアドレスLEと仮の次読出アドレスCA1との差Δであり、仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は正の値、仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は負の値として得られる。加算器233の出力Δは、インバータ234で反転されて加算器236のA入力端子に供給される。

【0053】セレクタ235は、加算器233からのキャリーに応じてループエンドアドレスLE又はループトップアドレスLTの何れかを選択して出力する。即ち、セレクタ235は、加算器233でキャリーが発生した場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は、ループエンドアドレスLEを出力し、加算器233でキャリーが発生しない場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は、ループトップアドレスLTを出力する。このセレクタ235の出力は、加算器236のB入力端子に供給される。

【0054】加算器236は、セレクタ235の出力とインバータ232の出力とを、キャリー入力を「1」として加算する。これにより、セレクタ235の出力と差Δの2の補数とが加算される。換言すれば、セレクタ235の出力から差Δが減算される。これは、加算器233からキャリーが発生したかどうかにより、次のように動作する。

【0055】即ち、キャリーが発生した場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えていない場合は、ループエンドアドレスLEから差Δ(正の値)が減算される。これにより、上記仮の次読出アドレスCA1が次読出アドレスCANとして加算器236から出力される。一方、キャリーが発生していない場合、つまり仮の次読出アドレスCA1がループエンドアドレスLEを越えた場合は、ループトップアドレスLTから差Δ(負の値)を減算する。これにより、次読出アドレスCANがループトップアドレスLTにラウンドする機能が実現されている。この加算器236から出力される次読出アドレスCANは、DSP20に送られ、次回の現読出アドレスCAの生成のために保存される。

【0056】また、加算器237は、現読出アドレスCAのうちの整数アドレスCAIを「+1」して出力する。この加算器237の出力は遅延回路238に供給される。遅延回路238は、加算器237の出力を一定時間遅延させて次の整数アドレスCAI+1として出力する。この整数アドレスCAI+1は、波形メモリ24に供給される。ここに一定時間とは、波形メモリ24が整数アドレスCAIを受け取ってから波形データの読み出しを完了するまでの時間である。従って、波形メモリ24からは、整数アドレスCAIに対応する波形データと整数アドレスCAI+1に対応する波形データとが一定時間間隔をおいて連続して読み出される。

【0057】図6は、補間部240の回路構成を示す。補間部240には、図示されるように、メイン部200から外部インタフェース部202を経由してアドレス生成用パラメータのうちの読出アドレスの小数アドレスCAFが与えられる。なお、初期状態においては、現読出アドレスCAはスタートアドレスSAであり、その小数アドレスCAFはゼロである。

【0058】補間部240は、ラッチ241、インバータ242、加算器243、乗算器244及び加算器245とにより構成されている。

【0059】波形メモリ24から読み出された整数アドレスCAIに対応する波形データWD0は、ラッチ241に一旦ラッチされる。このラッチ241の出力は、インバータ242で反転されて加算器243のA入力端子に供給されると共に、加算器245のA入力端子に供給される。

【0060】上記波形データWD0が読み出されてから上記一定時間経過後に波形データWD1が読み出されて加算器243のB入力端子に供給される。加算器243は、インバータ242の出力とB入力端子に供給された波形データWD1とを、キャリー入力を「1」として加算する。これにより、波形データWD1に波形データWD0の2の補数が加算される、換言すれば、波形データWD1から波形データWD0が減算される。この加算器243の出力は、乗算器244のB入力端子に供給される。一方、乗算器244のA入力端子には現読出アドレスCAの小数部(小数アドレスCAF)が供給されている。従って、この乗算器244からは、上記波形データWD1と波形データWD0との差が小数アドレスCAFの値に応じて案分された値が出力される。この乗算器244の出力は、加算器245のB入力端子に供給される。

【0061】加算器245のA入力端子には波形データWD0が供給されている。従って、この加算器245からは、波形データWD0に上記案分された値が加算された波形データ、つまり補間がとられた波形データWDが出力される。この波形データWDは、DSP20の外部回路インタフェース部202を介してDCA部203に供給される。

【0062】なお、上記補間部240として、直線補間をする場合の回路構成例を示したが、これに限定されるものではない。例えば最小二乗法、その他のいかなる補間方法をも用いることができる。

【0063】次に、上記の構成において、本音源装置の動作について、図7〜図9のフローチャートを参照しながら説明する。なお、各フローチャートに示された処理は、DSP20によって行われる。

【0064】図7は、本音源装置のメインルーチンを示すフローチャートであり、主としてDSP20のメイン部200によって行われる処理である。このメインルーチンは、電源投入により起動される。即ち、電源が投入されると、先ず、初期化処理が行われる(ステップS10)。

【0065】この初期化処理では、DSP20の内部状態が初期状態に設定されると共に、図示しないRAMに定義されているレジスタ、カウンタ或いはフラグ等に初期値が設定される。この初期化処理が終了すると、次いで、パラメータ転送の有無が調べられる(ステップS11)。即ち、CPU10から音源制御用パラメータが送られてきたかどうかが調べられる。これは、例えばメイン部200がCPUインタフェース部201に設けられている受信バッファ(図示しない)を調べることにより行われる。そして、パラメータ転送があることが判断されると、受信されたパラメータがワークメモリ22に転送される(ステップS12)。ステップS11でパラメータ転送がないことが判断されると、このステップS12はスキップされる。

【0066】次いで、発音タイミングであるかどうかが調べられる(ステップS13)。これは発音フラグを参照することにより行われる。ここに、発音フラグとは、図示しないRAMに設けられるフラグであり、各ボイスの発音処理を実行すべきタイミングであるかどうかを記憶するために使用される。この発音フラグは、後述する割込処理ルーチンにおいてセットされる。

【0067】ここで発音タイミングでないことが判断されるとステップS11に戻り、上述した処理を繰り返す。即ち、DSP20のメイン部200は、通常は、ステップS11〜S13を繰り返し実行しながらCPU10からパラメータが転送されてくるのを待って待機している。そして、CPU10からパラメータが転送されてくるとこれをワークメモリ22に転送する。このステップS11〜S13の繰り返しの中で、ステップS13において発音タイミングであることが判断されると、ステップS14以下の発音処理に移る。

【0068】発音処理では、先ず、DSP20は割込禁止モードにされる(ステップS14)。これにより、後述するステップS21で割込禁止モードが解除されるまでは、割込処理ルーチンがコールされることはない。従って、発音フラグがオンにされることもない。次いで、各ボイスに付された番号nが「0」にクリアされる(ステップS15)。

【0069】次いで、ボイスnに対する発音処理が行われる(ステップS16)。この処理では、ボイスnの波形データを出力系列毎に累算する処理が行われる(詳細については後述する)。次いで、上記番号nがインクリメントされ(ステップS17)、その番号nが本音源装置の総ボイス数に等しくなったかどうかが調べられる(ステップS18)。そして、等しくなければステップS16に戻って次のボイスに対する発音処理が行われる。

【0070】上記繰り返しにおいて、番号nが本音源装置の総ボイス数に等しくなったことが判断されると、次いで、上記ステップS16で生成された系列毎の波形データの累算値が出力される(ステップS19)。この波形データの累算値は、系列毎にD/A変換器26に送られる。その後、系列毎の波形データの累算値はクリアされ、次の発音処理に備えられる。

【0071】次いで、発音フラグがオフにされる(ステップS20)。そして、割込禁止モードが解除され(ステップS21)、その後、ステップS11に戻って以下同様の処理が行われる。

【0072】次に、上記ステップS16で行われるボイスnの発音処理の詳細について、図8を参照しながら説明する。この発音処理は、DSP20のメイン部200及びDCA部203で行われる処理に対応する。先ず、ボイスnに対応するアドレス生成用パラメータがワークメモリ22から読み出される(ステップS30)。この読み出されたアドレス生成用パラメータは、外部回路23に送られる(ステップS31)。これにより、外部回路23のDCO部230及び補間部240は、上述した動作により、次読出アドレスCANを算出すると共に、現読出アドレスCAの中の整数アドレスCAI及びCAI+1から波形データWD0及びWD1を読み出して補間を行う。この外部回路23で算出された次読出アドレスCAN及び補間済み波形データWDは外部回路インタフェース部202の外部回路バッファ212に格納される(図4参照)。

【0073】この外部回路23の動作と並行して、ワークメモリ22から振幅制御用パラメータが読み出され(ステップS32)、この読み出された振幅制御用パラメータから現在の発音タイミングにおけるエンベロープデータが計算される(ステップS33)。このステップS33の処理は、DCA部203で行われる処理に対応する。次いで、外部回路インタフェース部202の外部回路バッファ212から次読出アドレスCAN及び補間済み波形データWDが取り出され(ステップS34)、次読出アドレスCANは、ワークメモリ22の現読出アドレスCAの格納領域に転送される(ステップS35)。

【0074】次いで、外部回路バッファ212に格納されている補間済み波形データWDと上記ステップS33で算出されたエンベロープデータとが乗算される(ステップS36)。このステップS36の処理は、DCA部203で行われる処理に対応する。そして、この乗算結果がパンポットデータに応じて出力系列毎(例えばLチャンネル及びRチャンネル毎)に重み付けされ累算される(ステップS37)。重み付けは、音源制御用パラメータに含まれるパンポットデータに従って、例えば図3に示される音量特性となるように、上記乗算結果に演算又はテーブル変換を施すことにより実現できる。このステップS37の処理は、累算部204の処理に対応する。なお、パンポットデータによる音量特性は、図3に示される特性に限定されず、任意の特性を使用することができる。その後、この発音処理ルーチンからリターンしてメインルーチンに戻る。

【0075】図9には、割込処理ルーチンが示されている。この割込処理ルーチンは、タイミング発生回路25から割込信号が発生される度にコールされる。この割込処理ルーチンでは、発音フラグをオンにする処理が行われる(ステップS40)。この発音フラグがオンにされることにより、メインルーチンのステップS13で発音タイミングが到来したことが判断される。

【0076】以上説明したように、本実施例によれば、従来の音源装置において、例えばDSPやCPUといった処理装置でアドレス生成処理及び補間処理を行っていた。これに対して、本発明の音源装置においては、かかるアドレス生成処理及び補間処理を、処理装置の外部に設けられた外部回路に搭載されたアドレス生成回路及び補間回路で行うようにした。これにより、処理装置の負荷(処理時間)が軽減される。

【0077】なお、本発明では、ハードウエア化する部分については上記実施例に示したものに限定されず、DSP20の処理によって実現されているデジタル制御増幅部(DCA部203)の機能の全部又は一部をハードウエア化して外部回路23とすることも可能である。更に、上記実施例では、DSP20が行う処理として、音源装置で一般的に行われる代表的な機能に対する処理のみについて説明したが、DSP20ではその他の各種処理、例えばフィルタ演算処理によるグロウル効果の他、ディレイ、コーラス、リバーブ、3D等の音響効果を付加する処理等を行っても良く、本発明では、かかる各種処理を実現する機能をハードウエア化して外部回路とすることも可能である。

【0078】また、上記実施例では、ステレオ出力を可能にする2系列(L及びR)の出力を有する音源装置について説明したが、これに限定されるものではない。即ち、本発明は、モノラル出力の音源装置についても同様に適用できる。この場合、パンポットデータは不要であり、また、図8に示した発音処理のステップS37では、出力系列毎に重み付けして加算するのではなく、全ての乗算結果を単純に加算するように構成すれば良い。

【0079】更に、本発明は、3系列以上の出力を有する音源装置にも適用できる。この場合、多チャンネルによる音像定位を制御するパンポットデータを用意し、図8R>8に示した発音処理のステップS37は、3以上の出力系列毎に重み付けして加算するように構成すれば良い。

【0080】

【発明の効果】以上詳述したように、本発明の音源装置によれば、安価であるにも拘わらずボイス数を多く確保することのできる音源装置を提供できる。

【0081】即ち、本音源装置においては、アドレス生成処理を、処理装置の外部に設けられたアドレス生成回路で行うようにしているので、処理装置の負荷が軽減され、この軽減された負荷に対応する時間で更に他のボイスの処理を行うことができる。これにより、ボイス数を増やすことができるので、発生すべき楽音が貧弱になったり、所望の楽音が得られないという事態の発生を防止できる。また、高価な処理装置を使用する必要もないので、安価な音源装置を実現できる。

【0082】また、本音源装置においては、アドレス生成回路に加え、補間処理を外部に設けられた補間回路という簡単な回路で行うようにしているので、処理装置の負荷が更に軽減され、この軽減された負荷に対応する時間で更に他のボイスの処理を行うことができる。これにより、更にボイス数を増やすことができるので、発生すべき楽音が貧弱になったり、所望の楽音が得られないという事態の発生を防止できる。

【0083】また、上記軽減された処理時間を用いて音響効果の付加、例えばフィルタ演算による音色変化を行わせれば、より表情豊かな楽音を発生させることも可能となる。

【図面の簡単な説明】

【図1】本発明の実施例の音源装置の構成を示すブロック図である。

【図2】本発明の実施例におけるDSPが行う処理を機能的に分類して示した図である。

【図3】本発明の実施例におけるパンポットデータの一例を示す図である。

【図4】本発明の実施例で使用されるRAMの割り当ての一例を示す図である。

【図5】本発明の実施例における外部回路のDCO部の回路構成を示す図である。

【図6】本発明の実施例における外部回路の補間部の回路構成を示す図である。

【図7】本発明の実施例の音源装置のメインルーチンを示すフローチャートである。

【図8】本発明の実施例の音源装置の発音処理を示すフローチャートである。

【図9】本発明の実施例の音源装置の割込処理を示すフローチャートである。

【図10】従来の音源装置の構成を示すブロック図である。

【図11】従来の音源装置におけるDSPが行う処理を機能的に分類して示した図である。

【符号の説明】

10 CPU

20 DSP

21 プログラムメモリ

22 ワークメモリ

23 外部回路

24 波形メモリ

25 タイミング発生回路

26 D/A変換器

27 増幅器

28 スピーカ

200、500 メイン部

201、501 CPUインタフェース部

202 外部回路インタフェース部

203、503 DCA部

204、504 累算部

230、530 DCO部

240、531 補間部

【特許請求の範囲】

【請求項1】 波形データを記憶した波形メモリと、制御プログラムを記憶したプログラムメモリと、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路と、該アドレス生成回路で生成された読出アドレスによって前記波形メモリから読み出された波形データを、該読出アドレスの一部に基づいて補間して前記処理装置に供給する補間回路、と備えたことを特徴とする音源装置。

【請求項1】 波形データを記憶した波形メモリと、制御プログラムを記憶したプログラムメモリと、該プログラムメモリに記憶された制御プログラムに従って、外部から与えられたパラメータに応じた処理を行うことにより楽音信号を生成する処理装置を備えた音源装置であって、前記処理装置からの制御信号に応じて前記波形メモリから波形データを読み出すための読出アドレスを生成するアドレス生成回路と、該アドレス生成回路で生成された読出アドレスによって前記波形メモリから読み出された波形データを、該読出アドレスの一部に基づいて補間して前記処理装置に供給する補間回路、と備えたことを特徴とする音源装置。

【図1】

【図2】

【図3】

【図9】

【図4】

【図5】

【図6】

【図10】

【図7】

【図8】

【図11】

【図2】

【図3】

【図9】

【図4】

【図5】

【図6】

【図10】

【図7】

【図8】

【図11】

【公開番号】特開平8−146962

【公開日】平成8年(1996)6月7日

【国際特許分類】

【出願番号】特願平6−312780

【出願日】平成6年(1994)11月22日

【出願人】(000001410)株式会社河合楽器製作所 (563)

【公開日】平成8年(1996)6月7日

【国際特許分類】

【出願日】平成6年(1994)11月22日

【出願人】(000001410)株式会社河合楽器製作所 (563)

[ Back to top ]