領域記述子グローバル化制御を有するメモリ管理ユニットおよび動作方法

【課題】メモリ保護ユニット(MPU)(60)と、メモリ保護ユニットに関連する複数の領域記述子62を含むコンピュータ処理システムと方法の実施形態が提供される。

【解決手段】領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値を含む。制御論理は、翻訳識別子制御インジケータが第1状態にあるか否か判定し、翻訳識別子制御インジケータが第1状態にある場合には、制御論理は、処理システムによって実行されている第1プロセスが処理システムによって実行されている第2プロセスに割当てられたメモリ領域にアクセスできるようにする。

【解決手段】領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値を含む。制御論理は、翻訳識別子制御インジケータが第1状態にあるか否か判定し、翻訳識別子制御インジケータが第1状態にある場合には、制御論理は、処理システムによって実行されている第1プロセスが処理システムによって実行されている第2プロセスに割当てられたメモリ領域にアクセスできるようにする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的にデータ処理システム、より具体的には領域記述子グローバル化制御を有するメモリ管理ユニット(MMU)に関する。

【背景技術】

【0002】

幾つかの内蔵プロセッサが、多数の可変長メモリ領域に対して保護情報を提供する内部メモリ保護ユニット(MPU)を実施する。アクセス保護は、命令フェッチとデータ読込/書出アクセスに基づき、これらのアクセスアドレスをメモリ保護ユニットMPUの各エントリに比較して一致を判定(決定)することによって実行される。アクセスに対する記述子の一致は、アクセスアドレスが領域記述子によって定義されたアドレスレンジ内にあり、現在のプロセス識別子(PID)が領域記述子によって定義されたプログラム済み領域識別子に一致し、そして当該領域記述子に関連した許可がこのアクセスタイプを許すときに起こる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第6810471号

【発明の概要】

【発明が解決しようとする課題】

【0004】

メモリ保護ユニットMPUの或る実施において、すべて0値にプログラムされた領域識別子は、どんなプロセスによっても一致でき、通常スーパーバイザ専用領域のために使用される「グローバルな」領域記述子を示す。しかし、スーパーバイザのユーザ領域へのアクセスも必要とされるため、この実施は典型的に多重冗長領域記述子を要求するか、または現在のプロセス識別子PID値を修正してプログラムされた領域識別子に一致させるためにスーパーバイザコードを要求する。しかし、これらの解決は、リソース使用または性能オーバーヘッドの点で不利益をもたらす。さらに他のマッピング制約のために、スーパーバイザモードにおいて現在のプロセス識別子PID値を変更してユーザ領域のプロセス識別子PID値に一致させることは可能ではないであろう。

【課題を解決するための手段】

【0005】

メモリ管理ユニット(MPU)の領域記述子の動的グローバル化は、種々の制御機構を使用することによって可能となろう。たとえば一実施形態において、メモリ保護ユニットMPU内のすべてのまたは選択された領域記述子エントリの有効な領域IDをマスキングするグローバル化論理は実施できよう。一例において、このマスキングは、一時的に領域記述子エントリの有効な領域IDをすべて0値(または他の幾つかの所定の値)に強制して、領域記述子エントリの「グローバル化」を生じさせることができる。代替として、マスキングの結果、現在のプロセスIDは、領域記述子中にプログラムされた領域IDよりもグローバルなIDに一致することを必要とすることになろう。それゆえプロセッサの適切な状態における現在のプロセス動作(たとえばスーパーバイザモードにおける動作または特定のプロセス識別子値を有する動作)は、領域記述子エントリの特定の領域IDに一致する必要なく、領域記述子エントリによって定義された領域にアクセスできる。このようにして現在のプロセスは、メモリ領域に対応する領域記述子エントリによって異なるプロセスに割当てられたメモリ領域にアクセスできる。

【図面の簡単な説明】

【0006】

以下に本発明を図示によって説明するが、本発明は添付部の図面に限られるものではなく、同じ参照番号は類似の要素を指している。図中の要素は簡素かつ明瞭を旨として図示されており、必ずしも縮尺通りに描かれていない。

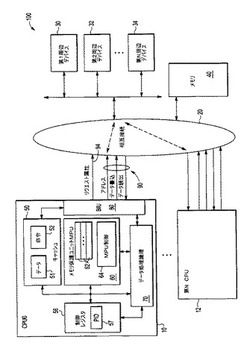

【図1】本発明の一実施形態に従いデータ処理システムをブロック図の形式で示す。

【図2】本発明の一実施形態に従い、図1のデータ処理システム内のメモリ保護ユニット(MPU)をブロック図の形式で示す。

【図3】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUにおける領域記述子を表の形式で示す。

【図4】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUで使用可能なメモリ保護ユニットMPU制御とステータスレジスタを線図の形式で示す。

【図5】本発明の一実施形態に従い、図4のメモリ保護ユニットMPU制御とステータスレジスタの種々のフィールドに対する記述を表の形式で示す。

【図6】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図7】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUで使用可能なメモリ保護ユニットMPU制御とステータスレジスタを線図の形式で示す。

【図8】本発明の一実施形態に従い、図7のメモリ保護ユニットMPU制御とステータスレジスタの種々のフィールドに対する記述を表の形式で示す。

【図9】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図10】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図11】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの動作方法をフローチャートの形式で示す。

【発明を実施するための形態】

【0007】

本明細書中で使用される「バス」という言葉は、データ、アドレス、制御またはステータスなど1種類以上のタイプの情報を伝送するために使用できる複数の信号または導体の意味で用いる。本明細書中で論じられる導体は、単一導体、複数導体、一方向導体または双方向導体として図示または記述されよう。しかし、異なる実施形態において導体は別様であってよい。たとえば双方向導体よりも別個の一方向導体が使用されることもあれば、その逆のこともある。複数導体も多数の信号を連続的にまたは時分割多重化方式で伝送する単一導体に置き換えられてよい。同様に、多数の信号を運ぶ単一導体は、これらの信号のサブセットを運ぶ種々の異なる導体に分けることもできる。それゆえ信号の伝送については多くの選択肢が存在する。

【0008】

「アサートする」または「セットする」と、「ネゲートする」(または「デアサートする」もしくは「クリアする」)という言葉は、本明細書中では信号、ステータスビットまたは類似の装置をそれぞれ論理的に真の状態または論理的に偽の状態に翻訳することに関連して用いる。論理的に真の状態が論理レベル1であるならば、論理的に偽の状態は論理レベル0である。そして論理的に真の状態が論理レベル0であるならば、論理的に偽の状態は論理レベル1である。

【0009】

図1は、本発明の実施形態に従うデータ処理システム100を図示するブロック図である。データ処理システム100は、CPU0として表す第1プロセッサ10、第NのCPU(CPUN)として表す第2プロセッサコア12、インタコネクト20、メモリデバイス40、および周辺デバイス30、32、34を有する。プロセッサ10はさらに、データキャッシュ51と命令キャッシュ52を含むキャッシュ50;さらに領域記述子62とメモリ保護ユニットMPU制御モジュール64を含むメモリ保護ユニットMPU60;データ処理論理モジュール70;さらに現在のプロセス識別子(PID)を記憶する記憶回路57を含む制御レジスタ56;バスインタフェースユニット(BIU)80を有する。プロセッサ12は、類似のサブコンポーネント(図示せず)を有しており、各々のプロセッサは、追加のモジュール(見やすくするために図示せず)を含むことができる。

【0010】

メモリアクセス保護ポリシーは、データ処理システム100に含まれている1つ以上のメモリ保護ユニット(MPU)60で実施できる。データ処理システム100の動作中、プロセッサ10および12におけるデータ処理論理モジュール70は、メモリ40内の位置にアクセスするリクエストを出すことができる。たとえばデータ処理論理モジュール70は、メモリ40からプログラム命令またはデータ情報を取出し、またはデータ情報をメモリ40に記憶するリクエストを出すことができる。メモリアクセス保護ポリシーは、リクエストされたアクセスを許可または拒否するか判定(決定)する。メモリ保護ユニット内の2つの領域記述子がメモリ内のエリアで互いに重なるアドレスレンジを持ち、相反するアクセスポリシーを有するならば、デフォルトアクセスポリシーが実施されてよい。

【0011】

図1に示す実施形態においてデータ処理システム100は、携帯電子デバイス、コンピュータデバイス、自動車用デバイス、通信デバイスなどを含む多数の電子システムに組み込むことができる汎用データ処理デバイスである。プロセッサ10および12は、ソフトウエアを実行するように構成された回路であり、これによって所望されたタスクを実行する。

【0012】

メモリアクセスリクエストは、典型的にメモリ40内の特定の位置から情報を取出すロード命令の実行、またはメモリ40内の特定の位置に情報を書込む記憶命令の実行に関連している。アクセスしようとするメモリ内の位置を識別するために、メモリアクセスリクエストにはアドレスが付随する。ロード命令または記憶命令は、ソフトウエアプログラムに含めることができ、ソフトウエアプログラムは、スーパーバイザモードまたはユーザモードで実行できる。ソフトウエアプログラムの実行は、プロセスとも呼ばれ、読込アクセスリクエストまたは書出アクセスリクエストは、実行されている特定のプロセスに割当てられた現在のプロセス識別子値(PID)に関連させることができる。このプロセス識別子PIDは、制御レジスタ56内の記憶回路57に記憶できる。

【0013】

メモリ読込動作中にアクセスされる情報は、命令を含むか、またはデータ情報を含むことができ、メモリ書出動作に関連した情報は、一般的にデータ情報である。したがってメモリアクセスリクエストは、1つ以上のリクエスト属性の値に基づき特徴付けることができる。リクエスト属性の例は、アクセスしようとする位置のアドレスを示すためのアドレス属性;リクエストが読込リクエストであるか否かを示すための読込属性;リクエストが書出リクエストであるか否かを示すための書出属性;リクエストがスーパーバイザモードで出されたか否かを示すためのスーパーバイザ属性;リクエストがユーザモードで出されたか否かを示すためのユーザ属性、リクエストに関連したプロセスを識別するためのプロセス識別(PID)属性;リクエストされた情報が命令であるか否かを識別するための命令属性などを含む。任意の数のリクエスト属性を領域記述子62に含めて、メモリアクセスリクエストに関連させることができる。

【0014】

本明細書中で使用されているメモリ位置は、固有のシステムアドレスを有するすべてのデータ記憶位置を指すことが意図されている。そのような位置は、メモリデバイス40、周辺デバイス30、32、34などを含めて、システムアドレススペース内に含めることができる。同様に、フレーズメモリアクセスリクエストは、本明細書中では固有のシステムアドレスに基づく記憶位置にアクセスするすべてのリクエストを指すために用いられている。簡素にするために、本明細書中に記載されているメモリマッピングされた記憶位置および対応するアクセスリクエストは、それぞれメモリおよびメモリアクセスリクエストと呼ぶ。

【0015】

プロセッサ10および12は、インタコネクト20を介して、メモリ40および周辺デバイス30−34と通信できる。特に、インタコネクト20は、信号を伝送してリクエスト情報(REQUEST INFORMATION)90とリクエスト属性(REQUEST ATTRIBUTES)94を提供することができる。リクエスト情報90は、メモリアドレス(ADDRESS)、書出データ(WDATA)および読込データ(RDATA)を含む。メモリデバイス40は、プロセッサ10またはプロセッサ12によって出されたメモリアクセスリクエストを介してアクセス可能な記憶位置を提供できる。メモリデバイス40は、動的ランダムアクセスメモリ(DRAM)、静的ランダムアクセスメモリ(SRAM)などを含め任意の種類のメモリタイプを有してよい。見やすくするために、図1は、データ処理システム100のその他の構成要素で、動作が当業者によく知られているもの、たとえば高度キャッシュメモリデバイス、外部インタフェースなどは省いてある。さらにデータ処理システム100が有するプロセッサの数は、これよりも多くても少なくてもよい。

【0016】

動作中、プロセッサ10および12は、メモリ40にアクセスして、命令を取得し、データ情報を取出し、またはデータ情報を記憶することできる。たとえばプロセッサ10内のデータ処理論理モジュール70は、メモリ40の特定のメモリアドレスでデータ情報を取出すためにメモリアクセスリクエストを出すことができる。メモリ保護ユニットMPU60は、メモリアクセスリクエストを外部のプロセッサ10に伝送する前に、リクエストするデバイス(またはリクエストの発生源のソフトウエアプロセス)がアクセスを許すのに適した許可を持っているか判定できる。さらにプロセッサ10は、所望のデータ情報がデータキャッシュ51内にあるか判定できる。メモリ保護ユニットMPU60が、リクエストは許可されたが、所望のデータ情報がデータキャッシュ51内に存在しない(キャッシュミス)と判定したら、メモリアクセスリクエストがバスインタフェースユニットBIU80に送られる。バスインタフェースユニットBIU80は、インタコネクト20を介してメモリアクセスリクエストをメモリ40または周辺デバイス30、32、34に転送するように構成されている。

【0017】

バスインタフェースユニットBIU80は、信号ADDRESS、読込命令信号(図示せず)、およびリクエストに関連した他の属性の値を識別するリクエスト属性94を介してメモリアドレスを伝送することによってメモリ読込アクセスリクエストを開始できる。これらの信号は、インタコネクト20を介してメモリ40に伝えられる。メモリデバイス40は、リクエストされたデータ情報をバスインタフェースユニットBIU80に戻し、次いで信号RDATAによってインタコネクト20を介してデータ処理論理モジュール70に戻すことができる。

【0018】

同様の仕方で、プロセッサ10におけるデータ処理論理モジュール70は、メモリ40の特定のメモリアドレスにデータ情報を記憶するためにメモリアクセスリクエストを出すことができる。メモリ保護ユニットMPU60は、メモリアクセスリクエストを外部のプロセッサ10に伝送する前に、リクエストに関連したリクエスト属性の値に基づきアクセスを許可または拒否するか判定できる。メモリ保護ユニットMPU60が、リクエストに付随する属性は、メモリ保護ユニットMPU60によって維持される属性の要件を満たすと判定したら、メモリアクセスリクエストがバスインタフェースユニットBIU80に提供される。

【0019】

バスインタフェースユニットBIU80は、信号ADDRESS、信号WDATAを介してメモリ40に記憶されるべきデータ情報、書出命令信号(図示せず)、およびリクエストに関連した特権を識別するリクエスト属性94を介してメモリアドレスを伝送することによってメモリ書出アクセスリクエストを開始できる。

【0020】

メモリ40から読込または書出すためのメモリアクセスリクエストは、アクセスリクエストに関連した種々のリクエスト属性を示すために信号リクエスト属性94を介してメモリ40に送信できる追加の情報を含んでよい。リクエスト属性94は、上述したようにリクエスト源を識別する情報およびリクエストのタイプを含むことができる。たとえばリクエスト属性94は、リクエストがスーパーバイザモードかユーザモードのいずれで実行されるプロセスに関連しているかの指示、リクエストが読込動作か書出動作のいずれを実行するかの指示などを含むことができる。リクエスト属性94は、関連したメモリアクセスリクエストをさらに特定の方法で特徴付けることができる他の情報を含むことができる。

【0021】

上述したように、メモリ保護ユニットMPUたとえばメモリ保護ユニットMPU60は、1つ以上のアドレス領域に関連するそれぞれの許可情報を維持できる。メモリ保護ユニットMPU60は、命令フェッチおよびデータ読込/書出に基づき、メモリアドレスおよびこのメモリアクセスリクエストに関連するプロセスID(PID)をメモリ保護ユニットMPU60内の各エントリ(領域記述子62内に記憶)に比較して一致を判定することによって保護を実行する。メモリ保護ユニットMPU60がメモリアドレスに対応して一致する領域記述子62を識別すると、当該領域記述子62に含まれている属性が評価され得る。属性は、共に保護ポリシーの状況を定義する任意の数のリクエスト属性に関するものであってよい。たとえば領域記述子は、特定のメモリアドレス領域内に含まれている位置が書出保護されることを指定でき、またどんな場合に情報を記憶するリクエスト、たとえば情報が領域内の所定の位置に記憶されるべきであることを示す属性を有するリクエストが拒否され、または情報を取出すリクエスト、たとえば情報が領域内の位置から読込まれるべきであることを示す属性を有するリクエストが許可されるかを指定できる。同様に、領域記述子62は、メモリアドレス領域内に含まれている位置は、アクセスリクエストがスーパーバイザモードで実行されるプロセスによって出されたことを示す属性に関連するアクセスリクエストにだけアクセス可能であることを指定できる。

【0022】

メモリ保護ユニットMPU60の動作は、図2および図3を参照すれば一層よく理解されよう。図2は、本発明の特定の実施形態に従うメモリ保護ユニットMPU60を図示するブロック図である。メモリ保護ユニットMPU60は、1組の命令領域記述子202、1組のデータ領域記述子204、および1組の共有(命令またはデータ)領域記述子206を含む。メモリ保護ユニットMPU60は、メモリ保護ユニットMPU制御モジュール64も含む。メモリ保護ユニットMPU制御モジュール64は、リクエストに関連したアドレスおよび特権属性に基づき、またはアクセスが命令フェッチアクセス、読込アクセスもしくは書出アクセスであるかに基づき、ならびに領域記述子202、204および206に含まれた1つ以上の領域記述子の内容に基づき、各々のリクエストされたメモリアクセスを選択的に許可または拒否するように動作する。上述したように、リクエスト属性94は、アクセスリクエストを開始するデバイスまたはソフトウエアプロセスがスーパーバイザ特権を持っているか、それともユーザ特権しか持っていないかの指示を含むことができ、およびその他の属性、たとえばバスマスタ識別番号なども含んでよい。メモリアクセスリクエストが拒否されたら、メモリ保護ユニットMPU制御モジュール64は、リクエストするデバイスにメモリアクセス例外が発生したことを示す終了エラー応答を返すことができる。

【0023】

図3は、本発明の特定の実施形態に従い、領域記述子202、204または206のいずれかに対応できる領域記述子300の実施形態を図示する表である。領域記述子300(領域記述子エントリとも呼ぶ)は、複数のフィールド320−331を含む。フィールド320は、有効属性Vに関係する。対応する有効なビットがアサートされなければ、領域記述子は、無効である。有効なビットがアサートされ、領域記述子に関連したアドレスレンジがアドレスに関連するリクエストを有し、そして領域記述子に関連した領域識別子がリクエストに関連したプロセス識別子PIDに一致するならば、領域記述子に含まれた許可情報は、メモリアクセスリクエストに応答したと見なすことができる。

【0024】

フィールド321UPPER BOUNDとフィールド322LOWER BOUNDは、それぞれ領域記述子の関連アドレスレンジを示すための上限アドレス属性と下限アドレス属性に関する。

【0025】

フィールド325は、命令属性INSTに関する。この属性は、領域記述子が命令アクセス、たとえば対応する命令リクエスト属性もアサートされるようなアクセスリクエストに対してのみ有効であることを識別するためにアサートされ得る。したがって対応する命令属性は、セット202(命令領域記述子)に含まれた領域記述子ではアサートされ、セット204(データ領域記述子)に含まれた領域記述子ではネゲートされる。

【0026】

フィールド326は、SX属性(スーパーバイザ実行)、SW属性(スーパーバイザ書出)、およびSR属性(スーパーバイザ読込)を含む複数のアクセス可能属性に関係する。これらの属性は、領域記述子によって指定されたアドレス領域内に含まれた位置に対して領域記述子によって許可されるスーパーバイザレベルのソフトウエアのタイプを識別するために個々にアサートされ得る。たとえばSW属性(スーパーバイザ書出)がアサートされたら、(リクエストに付随する相応のリクエスト属性をアサートすることによって)スーパーバイザアクセスと書出アクセスの両方として識別されたアクセスリクエストは、関連するメモリアドレス領域内の位置に情報を記憶することを記述子によって許可される。同様に、SR属性(スーパーバイザ読込)がアサートされたら、スーパーバイザアクセスと読込アクセスの両方として識別されたアクセスリクエストは、関連する領域内の位置を読込むことを記述子によって許可される。属性SX(スーパーバイザ実行)は、関連する領域内の位置が実行され得るか否か識別する。

【0027】

フィールド327は、UX属性(ユーザ実行)、UW属性(ユーザ書出)、およびUR属性(ユーザ読込)を含む複数のアクセス可能属性に関係し、これらの属性は、個々に記述子によって領域記述子に対応する位置に対して許可されたユーザレベル・アクセスリクエストのタイプを識別する。

【0028】

フィールド328は、キャッシュ禁止領域属性CIに関係する。キャッシュ禁止領域属性は、リクエストするデバイスに対して関連する領域内の位置から取出された情報をキャッシュデバイス、たとえば図1のデータキャッシュ51や命令キャッシュ52に記憶しないように命令するためにアサートされ得る。

【0029】

フィールド329は、保護された領域属性Gに関係する。保護された領域属性は、関連する領域内に含まれる位置が通常のメモリ素子またはレジスタとは別様に動作することを示すためにアサートされ得る。その一例は、FIFO、揮発性記憶素子などに続いてまたは応答して値が変化できるメモリマッピングされた位置である。したがって保護された位置に関連する情報は、典型的にキャッシュメモリデバイスには記憶されない。

【0030】

フィールド330の翻訳識別子TIDは、領域記述子に対する領域識別子に関係する(TIDは、翻訳識別子とも呼ばれることに留意されたい)。上述したように、領域記述子の有効なビットがアサートされ、受領されたリクエストに対応するアクセスアドレスが領域記述子の上限(UPPER_BOUND)および下限によって示されたアドレスレンジ内にあり、そして受領されたリクエストに対応するプロセス識別子PID値が翻訳識別子TIDに一致したら、受領されたリクエストは、領域記述子に一致する。以下に論じるように、翻訳識別子TIDを「グローバル化」して、或る状況においては一致を示すために受領されたリクエストに対応するプロセス識別子PID値が翻訳識別子TIDに一致する必要がないようにすることは、有用であろう。このようにすると、以下に詳細に説明するように、翻訳識別子TIDは、種々の条件下で1回以上の制御を用いてマスキングされよう。

【0031】

フィールド331の領域グローバル化制御RGCは、領域記述子に対する領域グローバル化制御に関係する。領域グローバル化制御RGCは、グローバル化に対するより精細な粒度を許容する。たとえばそれはどの領域記述子をグローバル化制御に適用すべきかを示すために用いられてよい。このようにして、領域グローバル化制御RGCが或る領域記述子に対してアサートされたら、グローバル化制御(すなわちマスキング制御)が適用されるが、領域グローバル化制御RGCがアサートされなければ、グローバル化制御は適用されず、一致が生じるか否かの判定に翻訳識別子TIDが使用される。このフィールドは、領域記述子内に存在することも存在しないこともある。

【0032】

メモリ保護ユニットMPU60の動作中、データ処理論理70によって生成されるメモリアクセスリクエストが評価されて、アクセスしようとする位置のアドレス、リクエストに関連したプロセス識別子PID(記憶回路57から取得できる)、リクエストされたプロセッサまたはプロセスアクセスリクエストはスーパーバイザ特権またはユーザ特権を有するか、リクエストは読込アクセスまたは書出アクセスであるか、そしてリクエストは命令アクセスまたはデータアクセスに対するものであるかを判定できる。領域記述子202、204および206は、他のリクエスト属性に対応する追加のフィールド、またはアクセスリクエストを所望の仕方で識別し、またはさらに適格にする追加のフィールドを含むことができる。メモリ保護ユニットMPU60は、適当な単数または複数のセクタの各々の有効な領域記述子を審査できる(たとえば命令領域記述子と命令アクセスリクエストに対する共有領域記述子、およびデータ領域記述子とデータアクセスリクエストに対する共有領域記述子)。メモリ保護ユニットMPU60が入ってくるアクセスリクエストに一致する領域記述子を識別したら、メモリ保護ユニットMPU60は、リクエスト属性に基づき、および一致する領域記述子によって指定された許可に基づきアクセスを許可または拒否する。たとえばアドレスXYZを書出すユーザモードリクエストが受領されたら、そして有効な領域記述子がアドレスXYZを含むアドレス領域を定義し、そしてメモリアクセスリクエストに関連するプロセス識別子PIDが有効な領域記述子の翻訳識別子TIDに一致する値を持つ場合、UW属性(ユーザ書出)がアサートされればリクエストされたアクセスは許可され、UW属性(ユーザ書出)がアサートされなければ拒否され得る。さらにメモリアクセスが許可されたら、メモリアクセスは、一致する領域記述子内のキャッシュ禁止領域属性CIフィールドと保護された領域属性Gフィールドの値に基づき、それぞれキャッシュ禁止アクセスまたは保護されたアクセスとして実行され得る。1つ以上の有効な領域記述子がリクエストされたアクセスアドレスおよび対応するプロセス識別子PIDに一致したら、どの領域記述子または領域記述子の部分がアクセスを統制するかを判定するために任意のポリシーが利用されてよい。たとえば多数の一致する領域記述子の最も制限の少ないアクセス許可が使用されてよい。

【0033】

上述したように、スーパーバイザレベルのソフトウエアには、現在進行中のプロセスに関わりなく(すなわちプロセス識別子PID値に関わりなく)、コードのそれ自身のセクション(たとえばメモリ内のスーパーバイザ専用領域)にアクセスできるようにすることが望ましいであろう。さらにメモリ内のこれらのスーパーバイザ専用領域にアクセスすることに加えて、スーパーバイザがユーザ領域にアクセスできるようにすることも望ましいであろう。しかし、メモリ保護ユニットMPU60によって定義された各々の特定のユーザ領域は、プロセス識別子PID値に結び付いている。それゆえ一実施形態においては、アドレスレンジがアクセスリクエストのアドレスを有する領域記述子の翻訳識別子TIDに、実際の記憶された翻訳識別子TID値に関わりなく、一時的に0値(または他の所定の値)を強制して一致を許可するグローバル化制御機構が含まれている。これが行なわれてよいのは、たとえばスーパーバイザモードの場合のみであり、ユーザモードでは行なわれない。それゆえ一実施形態において、メモリ保護ユニットMPU60は、スーパーバイザモードにあるときにエントリに対するアドレスレンジ比較のプロセス識別子PID/翻訳識別子TID部分を実行するときに、すべての領域記述子(または領域記述子のサブセット)内の翻訳識別子TIDビットをグローバルに0にマスキングする能力を提供する。これはメモリ保護ユニットMPU制御レジスタにおいて制御ビットをセットすることによって行うことができる。

【0034】

図4は、グローバルマスキング制御フィールド、翻訳識別子制御TIDCTL、およびメモリ保護ユニットイネーブルフィールドMPUENを含む多数のフィールドを有するメモリ保護ユニットMPU制御およびステータスレジスタ400の例を線図の形式で示す。(翻訳識別子制御TIDCTLフィールドは、翻訳識別子制御インジケータとも呼ばれ、メモリ保護ユニットMPU制御およびステータスレジスタ400は、MPU0CSR0とも呼ばれることに留意されたい。)図4の例で、翻訳識別子制御TIDCTLフィールドは、ビット29に位置する1ビットフィールドであり、メモリ保護ユニットイネーブルMPUENフィールドは、ビット31に位置する1ビットフィールドである。図4の32ビットレジスタ内の残りのビットは予備で、他の制御またはステータス情報のために使用できる。代替的な実施形態は、メモリ保護ユニットMPU制御およびステータスレジスタを別様に配置でき、図示されているよりも多いまたは少ないフィールドを含んでよい。一実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ400は、メモリ保護ユニットMPU制御64内に位置している。

【0035】

図5は、翻訳識別子制御TIDCTLフィールドとメモリ保護ユニットイネーブルMPUENフィールドに対する記述を表の形式で提供する。メモリ保護ユニットイネーブルMPUENフィールドに関して、メモリ保護ユニットイネーブルMPUENビットがアサートされたら(論理レベル1)、メモリ保護ユニットMPU60はイネーブルされ、逆にネゲートされたら(論理レベル0)、メモリ保護ユニットMPU60はディスエーブルされる。それゆえこのビットは、メモリ保護ユニットMPU60の動作をイネーブルする。イネーブルされると、アクセスアドレスは、メモリ保護ユニットMPU60内の各エントリに一致条件について比較される。一致条件が生じず、アクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、アクセスに対する例外条件が送信される。翻訳識別子制御TIDCTLフィールドに関して、翻訳識別子制御TIDCTLフィールドがネゲートされたら(論理レベル0)、翻訳識別子TID比較が普通に行なわれ、グローバル化マスキングは行なわれない。すなわちこの場合には、メモリ保護ユニットMPU60の有効な領域記述子によって生じるべき一致条件について、アクセスアドレスは、有効な領域記述子のアドレスレンジ内になければならず、アクセスのプロセス識別子PIDは、有効な領域記述子の翻訳識別子TIDに一致しなければならない。翻訳識別子制御TIDCTLフィールドがアサートされたら(論理レベル1)、スーパーバイザモードにあるときにグローバル化マスキングを用いて翻訳識別子TID比較が行われる。さらに多数のヒットに対して(すなわち多数の領域記述子が一致条件となる場合)、一致する記述子の最も制限の少ないアクセス許可が使用される。現在の実施形態において、翻訳識別子制御TIDCTLビットがアサートされると、(ユーザモードではなく)スーパーバイザモードにあるときにプロセス識別子PID/翻訳識別子TID比較を行うときにすべての領域記述子内の翻訳識別子TIDビットがマスキングされる。

【0036】

スーパーバイザモードにあるときにマスキングを用いて翻訳識別子TID比較が行なわれるように翻訳識別子制御TIDCTLビットをアサートすることによって、スーパーバイザコードは、ユーザタスクのために最初にロードされた領域記述子を、これらの記述子内のプログラムされた翻訳識別子TID値に関わりなく利用することが許される。この能力は、特定の状況においてアクティブであるために必要とされるスーパーバイザ領域記述子の数を最小化するために用いることができ、それによって効率を高めることができる。さらに領域記述子内の実際の内容は、変更されない。すなわち翻訳識別子TID値は、プログラムされた状態に留まり、比較論理で0または他の所定の値にマスキングされるのみである。

【0037】

図6は、アクセスアドレスに対する領域記述子一致論理600とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理600は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。一致論理600は、ANDゲート618、616、610および602、ORゲート604、ならびにコンパレータ612、614、606および608を含む。ANDゲート602の第1入力は、対応する領域記述子エントリからの有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート604の出力に結合され、第3入力はANDゲート610の出力に結合される。ANDゲート602の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままか、または低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート604の第1入力はコンパレータ606の出力に結合され、ORゲート604の第2入力はコンパレータ608の出力に結合される。コンパレータ606は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート618の出力に結合された第2入力とを有する。ANDゲート618は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート618の第2入力は、ANDゲート616の出力に結合された反転入力である。

【0038】

ANDゲート616の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ400から翻訳識別子制御TIDCTL値を受取るように結合されており、ANDゲート616の第2入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。コンパレータ608は、ANDゲート618の出力に結合された第1入力を有する。ANDゲート610は、コンパレータ612の出力に結合された第1入力と、コンパレータ614の出力に結合された第2入力とを有する。コンパレータ612は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力とを有する。コンパレータ614は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力とを有する。

【0039】

動作中、一致論理600は、受取ったメモリアクセスリクエストおよび対応する領域記述子エントリに関して一致が生じるか判定する。一致論理600は、有効なビットがアサートされ(MPU_エントリ[V]は論理レベル1である)、ゲート604とゲート610の各々の出力が論理レベル1である場合のみ出力一致信号(MPU_エントリ_一致)をアサートする。受取ったメモリアクセスリクエストのアクセスアドレスが、領域記述子エントリの上限と下限によって指示されたアドレスレンジ内にあるとき、ANDゲート610の出力は高い(論理レベル1)。すなわちコンパレータ612は、アクセスアドレスが上限よりも小さいかチェックして、もし小さければその出力を論理レベル1にアサートし、またコンパレータ614は、アクセスアドレスが下限よりも大きいかチェックし、もし大きければその出力を論理レベル1にアサートする。これら両比較が出力を論理レベル1にアサートした場合のみ、ゲート610の出力は論理レベル1である。

【0040】

プロセス識別子PID/翻訳識別子TID比較部分および選択的グローバル化マスキングは、ORゲート604およびORゲート604を駆動する論理によって実行される。翻訳識別子制御TIDCTLビットが論理レベル0であれば、つまり翻訳識別子TID比較が普通に行なわれるならば、ANDゲート616の出力は論理レベル0であり、翻訳識別子TID値は、コンパレータ606および608に対するANDゲート618のnビット出力に提供される。しかし、翻訳識別子制御TIDCTLビットが論理レベル1であれば、スーパーバイザモードにあるとき翻訳識別子TID比較は、マスキングされる。それゆえMSR[PR]が論理レベル1でユーザモードを示すならば、ANDゲート616の第2入力で反転するために、ANDゲート616の出力は論理レベル0である。この場合には翻訳識別子TIDの値は、マスキングされずにANDゲート618を通過してコンパレータ606および608に提供される。しかしMSR[PR]が論理レベル0で、スーパーバイザモードを示すならば(および翻訳識別子制御TIDCTLが論理レベル1であれば)、ANDゲート616の出力は論理レベル1であり、ANDゲート618の第2入力で反転するために、ANDゲート618の出力はすべて0に強制される。それゆえ翻訳識別子TID値よりすべて0の値がコンパレータ606および608に提供される。翻訳識別子TID値がANDゲート618を通されたら、コンパレータ606によってプロセス識別子PIDに比較されて一致が生じるか判定される。好都合な比較(すなわち一致)の結果としてコンパレータ606の出力は高くなり(論理レベル1)、不都合な比較の結果としてコンパレータ606の出力低くなる(論理レベル0)。それゆえプロセス識別子PIDが翻訳識別子TID値に一致するならば、コンパレータ608の出力に関わりなくORゲート604の出力は高くなり、プライベートアドレスレンジが示される。しかしANDゲート618によって翻訳識別子TID値がすべて0値に強制されると、コンパレータ606の出力は低くなって不都合な比較を示すが、コンパレータ608の出力は高くなって好都合な比較(すなわち一致)を示す。この場合には、翻訳識別子TIDのマスキングのために共有レンジが示される。コンパレータ606の出力が高くなるか、またはコンパレータ608の出力が高くなる限り、その結果として比較のプロセス識別子PID/翻訳識別子TID部分が一致する。

【0041】

図4と図5の例の説明において、翻訳識別子制御TIDCTLビットがアサートされると、スーパーバイザモード中にプロセス識別子PID/翻訳識別子TID比較を実行したときにすべての領域記述子内の翻訳識別子TIDビットがマスキングされることに留意されたい。しかし、代替的な実施形態において、各領域記述子は、(上に図3を参照して述べたように)領域グローバル化制御RGCフィールドを含むことができ、領域グローバル化制御RGCフィールドがアサートされた領域記述子(たとえば論理レベル1)内の翻訳識別子TIDビットは、プロセス識別子PID/翻訳識別子TID比較の実行中マスキングされ、領域グローバル化制御RGCフィールドがネゲートされた領域記述子(たとえば論理レベル0)内のおよび翻訳識別子TIDビットはマスキングされない。領域グローバル化制御RGCフィールドによって示されるように、翻訳識別子制御TIDCTLを選択された領域記述子に適用できるようにするために、一致論理600は適宜修正されてよい。

【0042】

図7は、グローバル化プロセス識別子PID値、グローバル化プロセス識別子G_PID、グローバルマスキング制御フィールド、翻訳識別子制御TIDCTL、領域グローバル化制御イネーブルフィールド、領域グローバル化制御イネーブルRGCENおよびMPUイネーブルフィールドメモリ保護ユニットイネーブルMPUENを含む多数のフィールドを有するメモリ保護ユニットMPU制御およびステータスレジスタ700の別の例を線図の形式で示す。(翻訳識別子制御TIDCTLフィールドは、翻訳識別子制御インジケータとも呼ばれ、メモリ保護ユニットMPU制御およびステータスレジスタ700は、MPU0CSR0とも呼ばれることに留意されたい。)図7の例で、グローバル化プロセス識別子G_PIDフィールドは、ビット0−15に位置する16ビットフィールドであり、翻訳識別子制御TIDCTLフィールドは、ビット28および29に位置する多ビットフィールド(この例では2ビット)であり、領域グローバル化制御イネーブルRGCENフィールドは、ビット30に位置する1ビットフィールドであり、およびメモリ保護ユニットイネーブルMPUENフィールドは、ビット31に位置する1ビットフィールドである。図7の32ビットレジスタ内の残りのビットは予備であり、他の制御またはステータス情報に使用できる。代替的な実施形態は、メモリ保護ユニットMPU制御およびステータスレジスタを別様に配置でき、図示されているよりも多いまたは少ないフィールドを含んでよい。一実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ700は、メモリ保護ユニットMPU制御64内に位置している。

【0043】

図8は、グローバル化プロセス識別子G_PIDフィールド、翻訳識別子制御TIDCTLフィールド、領域グローバル化制御イネーブルRGCENフィールド、およびメモリ保護ユニットイネーブルMPUENフィールドに対する記述を表の形式で提供する。メモリ保護ユニットイネーブルMPUENフィールドに関して、メモリ保護ユニットイネーブルMPUENビットがアサートされたら(つまり論理レベル1なら)メモリ保護ユニットMPU60はイネーブルされ、逆にネゲートされたら(つまり論理レベル0なら)メモリ保護ユニットMPU60はディスエーブルされる。それゆえこのビットは、メモリ保護ユニットMPU60の動作をイネーブルする。イネーブルされたときアクセスアドレスは、メモリ保護ユニットMPU60内の各エントリに一致条件について比較される。一致条件が生じず、アクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにイネーブルされなければ、アクセスに対する例外条件が送信される。翻訳識別子制御TIDCTLフィールドに関して、翻訳識別子制御TIDCTLフィールドが00であれば、翻訳識別子TID比較が普通に行なわれ、グローバル化マスキングは実行されない。すなわちこの場合には、メモリ保護ユニットMPU60の有効な領域記述子で生じるべき一致条件について、アクセスアドレスは、有効な領域記述子のアドレスレンジ内になければならず、アクセスのプロセス識別子PIDは、有効な領域記述子の翻訳識別子TIDに一致しなければならない。翻訳識別子制御TIDCTLフィールドが01であれば、スーパーバイザモードにあるときにグローバル化マスキングを用いて翻訳識別子TID比較が行われる。さらに多数のヒットに対して(すなわち多数の領域記述子が一致条件となる場合)、一致する記述子の最も制限の少ないアクセス許可が使用される。それゆえ翻訳識別子TIDが00または01のときメモリ保護ユニットMPU60は、上に図5と図6に関して翻訳識別子TIDがそれぞれ0または1である場合について記述されたように動作することに留意されたい。翻訳識別子制御TIDCTLフィールドが10であれば、現在のプロセス識別子PID値がメモリ保護ユニットMPUステータスおよび制御レジスタ700内に記憶されたグローバル化プロセス識別子G_PID値に一致するとき、グローバル化マスキングを用いて翻訳識別子TID比較が行なわれる。この場合も多数のヒットに対しては、一致する記述子の最も制限の少ないアクセス許可が使用される。

【0044】

引き続き図8を参照して、領域グローバル化制御イネーブルRGCENフィールドが0の値を有する場合には、グローバル化マスキングがイネーブルされたとき領域記述子内の領域グローバル化制御RGCフィールドは、無視される。このようにしてグローバル化マスキングがイネーブルされると、(たとえばスーパーバイザモードでプロセス識別子PID/翻訳識別子TID比較を実行するときに翻訳識別子TIDビットをマスキングすることによって、または現在のプロセス識別子PIDを特定の記述子の翻訳識別子TIDよりもグローバル化プロセス識別子G_PIDに比較することによって)メモリ保護ユニットMPU60のすべての領域記述子が適宜マスキングされる。領域グローバル化制御イネーブルRGCENフィールドが1の値を有する場合には、領域記述子内の領域グローバル化制御RGCフィールドは、グローバル化マスキングがイネーブルされたとき記述子のグローバル化を適格にするために使用される。すなわち一実施形態において、領域グローバル化制御RGCフィールドがアサートされた領域記述子(たとえば論理レベル1)のみがグローバル化マスキングによってマスキングされる一方、領域グローバル化制御RGCフィールドがネゲートされた領域記述子(論理レベル0)に対しては、現在のプロセス識別子PID記述子の翻訳識別子TIDとの比較が普通に行なわれるであろう。

【0045】

図9は、アクセスアドレスに対する領域記述子一致論理900とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理900は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。図9の例は、グローバル化イネーブルを制御するためにグローバル化プロセス識別子G_PIDフィールドの使用を含むが、領域グローバル化制御イネーブルRGCENの使用は含まない。一致論理900は、ANDゲート922、920、918および902、ORゲート916および904、ならびにコンパレータ924、912、914、906および908を含む。ANDゲート902の第1入力は、対応する領域記述子エントリから有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート904の出力に結合され、第3入力はANDゲート910の出力に結合される。ANDゲート902の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままかまたは低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート904の第1入力はコンパレータ906の出力に結合され、ORゲート904の第2入力は、コンパレータ908の出力に結合される。コンパレータ906は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート918の出力に結合された第2入力を有する。ANDゲート618は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート918の第2入力は、ORゲート916の出力に結合された反転入力である。ORゲート916の第1入力は、ANDゲート922の出力に結合されている。ANDゲート922の第1入力は、第1インジケータを受取るように結合されており、この第1インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値が「01」であることを示す。それゆえもし翻訳識別子制御TIDCTLフィールドの値が「01」でなければ、第1インジケータは論理レベル0である。ANDゲート922の第2入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。ORゲート916の第2入力はANDゲート920の出力に結合される。ANDゲート920の第1入力は、第2インジケータを受取るように結合され、この第2インジケータは論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値は「10」であることを示す。それゆえ翻訳識別子制御TIDCTLフィールドの値が「10」でなければ、第2インジケータは論理レベル0である。ANDゲート920の第2入力はコンパレータ924の出力に結合される。コンパレータ924は、(たとえば記憶回路57から)現在のプロセス識別子PIDを受取るように結合された第1入力と、メモリ保護ユニットMPU制御およびステータスレジスタ700からグローバル化プロセス識別子G_PID値を受取るように結合された第2入力を有する。コンパレータ608は、ANDゲート918の出力に結合された第1入力を有する。ANDゲート910は、コンパレータ912の出力に結合された第1入力と、コンパレータ914の出力に結合された第2入力を有する。コンパレータ912は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力を有する。コンパレータ914は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力を有する。

【0046】

動作中、一致論理900は、受取ったメモリアクセスリクエストおよび対応する領域記述子エントリに関して一致が生じるか判定する。一致論理900は、有効なビットがアサートされ(MPU_エントリ[V]は論理レベル1である)、ゲート904とゲート910の各々の出力が論理レベル1である場合のみ出力一致信号(MPU_エントリ_一致)をアサートする。受取ったメモリアクセスリクエストのアクセスアドレスが領域記述子エントリの上限と下限によって指示されたアドレスレンジ内にあるとき、ANDゲート910の出力は高い(論理レベル1)。すなわちコンパレータ912は、アクセスアドレスが上限よりも小さいかチェックして、そうであればその出力を論理レベル1にアサートし、またコンパレータ9614は、アクセスアドレスが下限よりも大きいかチェックして、そうであれば出力を論理レベル1にアサートする。これら両比較が出力を論理レベル1にアサートした場合のみ、ゲート910の出力は論理レベル1である。

【0047】

プロセス識別子PID/翻訳識別子TID比較部分は、選択的グローバル化マスキングと同様、ORゲート904およびORゲート904を駆動する論理によって実施される。翻訳識別子制御TIDCTLフィールドが00であれば、つまり翻訳識別子TID比較が普通に行なわれるならば、ORゲート916の出力は論理レベル0であり、翻訳識別子TID値は、コンパレータ906および908へのANDゲート918のnビット出力に提供される。すなわち翻訳識別子制御TIDCTLが00であり、したがって01でも10でもなければ、ORゲート916への入力は論理レベル0である。翻訳識別子制御TIDCTLフィールドが論理レベル1であれば、スーパーバイザモードにあるとき翻訳識別子TID比較は、マスキングされる。それゆえMSR[PR]が論理レベル1であり、ユーザモードを示すならば、ANDゲート922の第2入力で反転するために、ANDゲート922の出力は論理レベル0である。また、翻訳識別子制御TIDCTLフィールドが論理レベル01であれば、ANDゲート922への第1入力は0であり、ANDゲート922の出力は0である。それゆえORゲート916の出力は0であり、翻訳識別子TIDの値は、マスキングされずにANDゲート918を通ってコンパレータ606および608に提供される。しかしMSR[PR]が論理レベル0でスーパーバイザモードを示すならば(および翻訳識別子制御TIDCTLが01であれば)、ANDゲート922の出力は論理レベル1である。この場合にはORゲート916の出力も1であり、ANDゲート918の第2入力で反転するために、ANDゲート918の出力はすべて0に強制される。それゆえコンパレータ906および908には、翻訳識別子TID値よりもすべて0の値が提供される。この場合ORゲート916の第2入力も、0であることに留意されたい。しかし、翻訳識別子制御TIDCTLフィールドが10であるならば、グローバル化プロセス識別子G_PID値を用いてグローバル化マスキング実施される。この場合にはANDゲート920への第1入力は論理レベル1であり、コンパレータ924は、現在のプロセス識別子PID値をメモリ保護ユニットMPU制御およびステータスレジスタ700からのグローバル化プロセス識別子G_PID値に比較する。一致があれば、コンパレータ924の出力は論理レベル1となり、ANDゲート920の出力は論理レベル1となる。この場合ORゲート916への第1入力は、(翻訳識別子制御TIDCTLが10なので)論理レベル0であり、ORゲート916の第2入力は論理レベル1である。それゆえORゲート916の出力も1であり、そしてANDゲート918の第2入力で反転するために、ANDゲート918の出力はすべて0に強制される。ORゲート916は、翻訳識別子制御TIDCTLが01または10かに従いグローバル化マスキングが生じるための適当な条件が満たされているか検出する。グローバル化マスキングが生じるべきであるならば、翻訳識別子TID値はすべて0に強制され、そうでなければ翻訳識別子TID値は、マスキングされずにANDゲート918を通過する。

【0048】

翻訳識別子TID値がANDゲート918を通過すると、コンパレータ906によってプロセス識別子PIDに比較されて一致が生じるか判定する。好都合な比較(すなわち一致)の結果としてコンパレータ906の出力は高くなり(論理レベル1)、不都合な比較の結果としてコンパレータ906の出力は低くなる(論理レベル0)。それゆえプロセス識別子PIDが翻訳識別子TID値に一致すれば、コンパレータ908の出力に関わりなくORゲート904の出力が高くなり、プライベートアドレスレンジが示される。しかしANDゲート918によって翻訳識別子TID値がすべて0値に強制されると、コンパレータ906の出力は低くなって不都合な比較を示すが、コンパレータ908の出力は高くなって好都合な比較(すなわち一致)を示す。この場合には、翻訳識別子TIDのマスキングのために共有レンジが示される。コンパレータ906の出力が高くなるか、またはコンパレータ908の出力が高くなれば、比較のプロセス識別子PID/翻訳識別子TID部分は、一致する結果となる。

【0049】

図10は、アクセスアドレスに対する領域記述子一致論理1000とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理1000は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。図10の例は、図9に示したように、グローバル化イネーブルを制御するためにグローバル化プロセス識別子G_PIDフィールドの使用を有し、さらに領域グローバル化制御イネーブルRGCENの使用を含む。一致論理1000は、ANDゲート1022、1020、1018,1010,1002および1026、ORゲート1016および1004、ならびにコンパレータ1024、1012、1014、1006および1008を含む。ANDゲート1002の第1入力は、対応する領域記述子エントリからの有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート1004の出力に結合され、第3入力はANDゲート1010の出力に結合される。ANDゲート1002の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままかまたは低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート1004の第1入力はコンパレータ1006の出力に結合され、ORゲート1004の第2入力はコンパレータ1008の出力に結合される。コンパレータ1006は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート1018の出力に結合された第2入力を有する。ANDゲート1018は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート1018の第2入力は、ORゲート1016の出力に結合された反転入力である。ORゲート1016の第1入力は、ANDゲート1022の出力に結合されている。ANDゲート1022の第1入力は、ORゲート1028の出力に結合されている。ORゲート1028の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ700から、領域グローバル化制御イネーブルRGCENの値を受取るように結合された反転入力である。ORゲート1028の第2入力は、ANDゲート1026の出力に結合されている。

【0050】

ANDゲート1026の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ700から、領域グローバル化制御イネーブルRGCENの値を受取るように結合されており、ANDゲート1026の第2入力は、現在の記述子エントリの領域グローバル化制御RGCフィールドの値を受取るように結合されている。ANDゲート1022の第2入力は、第1インジケータを受取るように結合されている。この第1インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値が「01」であることを示す。それゆえもし翻訳識別子制御TIDCTLフィールドの値が「01」でなければ、第1インジケータは論理レベル0である。ANDゲート1022の第3入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。ORゲート1016の第2入力は、ANDゲート920の出力に結合される。ANDゲート1020の第1入力は、ORゲート1028の出力に結合されている。ANDゲート1020の第2入力は、第2インジケータを受取るように結合され、この第2インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値は「10」であることを示す。それゆえ翻訳識別子制御TIDCTLフィールドの値が「10」でなければ、第2インジケータは論理レベル0である。ANDゲート1020の第3入力は、コンパレータ1024の出力に結合される。コンパレータ1024は(たとえば記憶回路57から)現在のプロセス識別子PIDを受取るように結合された第1入力と、メモリ保護ユニットMPU制御およびステータスレジスタ700からグローバル化プロセス識別子G_PID値を受取るように結合された第2入力を有する。コンパレータ1008は、ANDゲート1018の出力に結合された第1入力を有する。ANDゲート1010は、コンパレータ1012の出力に結合された第1入力と、コンパレータ1014の出力に結合された第2入力を有する。コンパレータ1012は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力を有する。コンパレータ1014は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力を有する。

【0051】

動作中、上にゲート916、918、906、908、904、912、914、910および902に関して説明したことは、それぞれゲート1016、1018、1006、1008、1004、1012、1014、1010、1002に該当することに留意されたい。しかし、一致論理1000においてグローバル化マスキングは、領域グローバル化制御イネーブルRGCENがイネーブルされると(たとえば論理レベル1)、さらに各エントリの領域グローバル化制御RGCフィールドによって適格にされる。領域グローバル化制御イネーブルRGCENがイネーブルされないと(たとえば論理レベル0)、ORゲート1028の反転入力のために、(ANDゲート1026の出力における値に関わりなく)ORゲート1028の出力は論理レベル1である。このようにしてエントリに対して翻訳識別子制御TIDCTL値に従い、グローバル化マスキングが実施される。すなわちORゲート1028の出力は論理レベル1であるから、ORゲート1028の出力はゲート1022および1020の出力に影響せず、これらのゲートの出力は、他の2つの入力によって判定される(これについては上に図9の類似の回路を参照して説明した)。

【0052】

領域グローバル化制御イネーブルRGCENがイネーブルされると、特定の領域記述子に対するグローバル化マスキングが、領域記述子の対応する領域グローバル化制御RGCフィールドによって判定される。領域グローバル化制御イネーブルRGCENがイネーブルされると(論理レベル1)、ORゲート1028の第1入力は論理レベル0であり、ORゲート1028の出力は、ANDゲート1026の出力によって判定される。それゆえ領域グローバル化制御イネーブルRGCENはイネーブルされるが、対応する領域記述子(すなわちエントリ)の領域グローバル化制御RGCフィールドが論理レベル0であれば、領域記述子に対してグローバル化マスキングは実施されない。この場合にはANDゲート1026の出力は論理レベル0であり、したがってORゲート1028の出力も論理レベル0である。このことはANDゲート1022および1020の出力、したがってORゲート1016の出力が、論理レベル0であることを保証する。それゆえ翻訳識別子TIDの値は、マスキングされずにANDゲート1018を通過してコンパレータ1006および1008に達する。しかし、領域グローバル化制御イネーブルRGCENがイネーブルされ(論理レベル1)、対応する領域記述子の領域グローバル化制御RGCフィールドが1であれば、エントリに対して翻訳識別子制御TIDCTL値に従うグローバル化マスキングが実施される。この場合にはANDゲート1026の出力およびORゲート1028は論理レベル1であり、したがってゲート1022および1020の出力には影響せず、これらのゲートの出力は、他の2つの入力によって判定される(これについては上に図9の類似の回路を参照して説明した)。それゆえ領域グローバル化制御イネーブルRGCENがイネーブルされ、領域記述子の領域グローバル化制御RGCがアサートされたら、当該領域記述子に対してグローバル化マスキングがイネーブルされて、翻訳識別子制御TIDCTLフィールドの値に従いプロセス識別子PIDが、領域記述子の翻訳識別子TIDに一致しない他のプロセスによって利用され得る。

【0053】

図11は、本発明の一実施形態に従うメモリ保護ユニットMPU60の動作の方法1100をフローチャートで示す。図11に示す実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ(たとえばメモリ保護ユニットMPU制御およびステータスレジスタ700)のRCGENと、グローバル化プロセス識別子G_PIDフィールドおよび領域記述子の領域グローバル化制御RGCフィールドとが、メモリ保護ユニットMPU60に対して存在している。図示された実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ(たとえばメモリ保護ユニットMPU制御およびステータスレジスタ700)の翻訳識別子制御TIDCTLフィールドは、少なくとも3つの状態(たとえば00、01、10)を持てることが前提とされている。方法1100はブロック1102で開始し、ここで翻訳識別子制御TIDCTL、RCGEN、グローバル化プロセス識別子G_PID、およびメモリ保護ユニットイネーブルMPUENフィールドが適当に初期化される。たとえば或る適当な状態は、翻訳識別子制御TIDCTL(たとえば図8に関して説明した00、01、10)に記憶でき、適当なグローバルプロセス識別子PIDはグローバル化プロセス識別子G_PIDに記憶でき、RCGENはアサートまたはネゲートされて、それぞれ領域グローバル化制御RGCフィールドの使用をイネーブルまたはディスエーブルすることができる。メモリ保護ユニットMPU60の領域記述子内の各領域グローバル化制御RGCフィールドは、各領域記述子エントリが作成されるときに初期化され得る。

【0054】

方法1100は判定ダイヤモンド1104に進み、ここでRCGENがイネーブルされるか判定される。RCGENがイネーブルされなければ、方法は判定ダイヤモンド1108に進み、ここでメモリ保護ユニットMPU60内の各領域記述子について翻訳識別子制御TIDCTLフィールドの値に基づき、グローバル化マスキングが選択的にイネーブルされる。以下に説明するように判定ダイヤモンド1108、1110および1112は、領域記述子に対応する特定のメモリ領域についてグローバル化マスキングが行なわれるべきか判定する。判定ダイヤモンド1104で領域グローバル化制御イネーブルRGCENがイネーブルされたら、フローチャートは判定ダイヤモンド1106に進み、ここで各領域記述子について対応する領域グローバル化制御RGCが、イネーブルされるか判定される。次に方法1100は判定ダイヤモンド1108に進み、ここで(判定ダイヤモンド1108、1110および1112に対応して)翻訳識別子制御TIDCTL値に従いグローバル化マスキングを実施するか否かの判定は、領域グローバル化制御RGCフィールドがイネーブルされた領域記述子についてのみ行なわれる。領域グローバル化制御RGCがイネーブルされない他のすべての領域記述子については、翻訳識別子TID比較が普通に行なわれ、上述したように一致条件が生じるためには現在のプロセス識別子PIDは、領域記述子の翻訳識別子TIDに一致する必要がある。

【0055】

判定ダイヤモンド1108では、グローバル化がイネーブルされた領域記述子(RGCENがイネーブルされない場合にはすべての領域記述子、または領域グローバル化制御イネーブルRGCENがイネーブルされた場合にはイネーブルされた領域グローバル化制御RGCフィールドを持つ領域記述子のみ)について、翻訳識別子制御TIDCTLフィールドが状態0にあるか判定される。一実施形態において状態0は、図8を参照して述べられた「00」の値に対応することができる。対応する場合には方法1100はブロック1122に進み、ここでは翻訳識別子TIDのマスキングは生じない。このマスキングがない場合には、一致条件を判定するための翻訳識別子TID比較が普通に行なわれる。判定ダイヤモンド1108で翻訳識別子制御TIDCTLフィールドが状態0になければ、方法1100は判定ダイヤモンド1110に進み、ここで翻訳識別子制御TIDCTLフィールドが状態2にあるか判定される。一実施形態において状態2は、図8を参照して述べたように「10」の値に対応することができる。対応する場合には、方法1100は判定ダイヤモンド1114に進み、ここで現在のメモリアクセスリクエストに対応する現在のプロセス識別子PIDが、グローバル化プロセス識別子PID(メモリ保護ユニットMPU制御およびステータスレジスタのグローバル化プロセス識別子G_PID)に一致するか判定される。一致しない場合には、方法はブロック1122に進み、ここでは当該領域記述子に対して翻訳識別子TIDのマスキングは実施されない。一致する場合には、方法は判定ダイヤモンド1116に進み、ここで(領域記述子のUPPER_BOUNDフィールドとLOWER_BOUNDフィールドを用いて)現在のメモリアクセスリクエストのアドレスが、領域記述子に対応するメモリ領域に一致するか判定される。判定ダイヤモンド1116でアドレスの一致がなければ、方法1100はブロック1120に進み、ここでは当該エントリについて一致条件は生じない。或る場合には、アクセス例外が出される(たとえばメモリ保護ユニットMPU60のどの領域記述子とも一致が生じない場合)。判定ダイヤモンド1116でアドレスの一致があれば、方法1100はブロック1118に進み、ここで方法は翻訳識別子TIDの比較をマスキングして、現在のプロセスが、(メモリ保護ユニットMPU60の領域記述子によって)異なるプロセスに割当てられ得るメモリにアクセスできるようにする。

【0056】

判定ダイヤモンド1110で翻訳識別子制御TIDCTLフィールドが状態2になければ、方法1100は判定ダイヤモンド1112に進み、ここで翻訳識別子制御TIDCTLフィールドが状態1にあり(図8を参照して述べたように「10」の翻訳識別子制御TIDCTL値に対応することができる)、プロセッサは、スーパーバイザモードで動作しているか判定される。該当しない場合には、方法1100はポイントBを通ってブロック1122に進み、ここではマスキングが実施されない。該当する場合には、方法1100は判定ダイヤモンド1124に進み、ここで現在のメモリアクセスリクエストのアドレスが領域記述子に対応するメモリの領域に一致するか判定される。一致しない場合には、方法1100はポイントAを通ってブロック1120に進む。アドレスの一致が生じる場合には、方法1100はブロック1118に進み、ここで方法は、翻訳識別子TIDとプロセス識別子PIDの一致比較をマスキングして、現在のプロセスが異なるプロセスに割当てられ得るメモリにアクセスできるようにする。

【0057】

それゆえ以上によって、どのようにグローバル化マスキングが行なわれて、プロセッサ上のプロセス実行が、メモリ保護ユニットMPU領域記述子の方法によって異なるプロセスに割当てられたメモリ内の領域にアクセスできるようになるかが理解される。このようにしてグローバル化マスキングは、領域記述子の翻訳識別子TIDなど領域記述子の部分が、一致条件の判定において利用されないようにすることができる。たとえば翻訳識別子TIDに対してグローバル化マスキングが行なわれると、現在のプロセスのプロセス識別子は、アクセスされているメモリ領域に対応する領域記述子の翻訳識別子TIDに一致する必要がない。一実施形態においてグローバル化マスキングがイネーブルされると、領域記述子の翻訳識別子TIDが0に強制されて領域記述子比較から有効に除外されるので、現在のプロセスは、任意のプロセス識別子PID値を持つことができる。代替としてグローバル化マスキングがイネーブルされると、現在のプロセスは、アクセスされている領域に対応する翻訳識別子TIDよりも、グローバルプロセス識別子PIDに一致しなければならない。さらに領域記述子の領域グローバル化制御RGCフィールドなど追加の制御を用いることによって、メモリ保護ユニットMPU内の領域記述子のサブセットに対してグローバル化マスキングが実施され得る。このようにして処理時間またはメモリ保護ユニットMPU内のエントリの数を増すことなく、スーパーバイザコードなど特定のソフトウエアによって多くの制御を与えることができる。

【0058】

本発明を実施する装置は、大部分が当業者に公知の電子コンポーネントと電子回路からなるので、本発明の基礎をなすコンセプトを理解および評価し、また本発明の教示を不明瞭または散漫にしないために、回路の詳細については上述したように必要と見なされる程度を越えて説明しない。

【0059】

上記の実施形態の幾つかで該当するものは、多様な種類の情報処理システムを用いて実施できる。たとえば図1とこれに関する議論は、例示的な情報処理アーキテクチャを記述しているが、この例示的なアーキテクチャは、単に本発明の種々の側面を論じる際に有益な参照を提供するために提示されているに過ぎない。もちろん、アーキテクチャの記述は、議論の目的のために単純化されており、本発明に従って使用できる多様なタイプの適当なアーキテクチャの一つに過ぎない。当業者は、論理ブロックの境界が単に例示的なものであり、代替的な実施形態は、論理ブロックや回路要素を統合したり、別様に機能を分解して種々の論理ブロックや回路要素に課したりできることを認識するであろう。

【0060】

したがって本明細書中に示されたアーキテクチャは、単に例示的なものであり、実際には同じ機能を達成する他の多くのアーキテクチャも実施できることが理解されるべきである。抽象的ではあるが明確な意味において、同じ機能を達成するためのコンポーネントの任意の構成は、所望の機能が達成されるように有効に「関連している」。したがって本明細書中で特定の機能を達成するために組み合わされた2つのコンポーネントは、アーキテクチャであるか中間的なコンポーネントであるかに関わりなく、所望の機能が達成されるように互いに「関連している」。同様に、そのように関連している任意の2つのコンポーネントは、所望の機能を達成するために互いに「動作的に接続している」または「動作的に結合している」と見ることができる。

【0061】

またたとえば一実施形態において、システム100の図示された素子は、単一の集積回路上または同じデバイス内に配置された回路である。代替として、システム100は、任意の数の別個の集積回路または互いに相互接続された別個のデバイスを含むことができる。

【0062】

さらに当業者は、上記の動作の機能間の境界が単に例示的なものに過ぎないことを認識するであろう。多数の動作の機能は、単一の動作に組み合わされ、および/または単一の動作の機能は、追加の動作に配分されてよい。さらに代替的な実施形態は、特定の動作の多数のインスタンスを含んでよく、動作の順序は、他の種々の実施形態で変更されてよい。

【0063】

本明細書において本発明は、特定の実施形態を参照して説明されているが、以下の特許請求の範囲に記載された本発明の範囲から逸脱することなく種々の変容や変更を行うことができる。したがって詳細な説明と図面は、制限的な意味ではなく例示的な意味を持つものと見なされるべきであり、そのようなすべての変容は、本発明の範囲に含まれることが意図されている。本明細書で特定の実施形態に関して記載されているいかなる効果、利点または問題の解決も、一部または全部の請求項の枢要、不可欠または必須の特徴もしくは要素と解釈されることを意図していない。

【0064】

本明細書中で使用されている「結合」という言葉は、直接的結合または機械的結合に制限されることを意図していない。

さらに本明細書中で使用されている「a」または「an」の言葉は、1つまたは1つよりも多いものとして定義される。また、特許請求の範囲において「少なくとも1つの」や「1つ以上の」などの導入句を使用することは、不定冠詞「a」または「an」によって他の請求要素を導入することが、そのように導入された請求要素を含む特定の請求項を、そのような要素を1個のみ含む発明に制限することを含意するものと解釈されてはならない。これは、同じ請求項が「1つ以上の」または「少なくとも1つの」という導入句と、「a」または「an」などの不定冠詞を含む場合も同様である。

【0065】

別途記載のない限り、「第1」および「第2」という言葉は、そのような言葉で記述される要素を任意に区別するために用いられる。したがってこれらの言葉は、必ずしもそれらの要素の時間順や優先順を示すことが意図されていない。

【0066】

以下に、本発明の種々の実施形態を示す。

技術思想1に含まれるコンピュータ処理システムは、メモリ保護ユニット(MPU)と;メモリ保護ユニットに関連する複数の領域記述子とを有し、領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値とを有する。コンピュータ処理システムはさらに、翻訳識別子制御インジケータ(TIDCTL)と;制御論理とを有しており、制御論理は、翻訳識別子制御インジケータが第1状態にあるか否かを判定して、翻訳識別子制御インジケータが第1状態にある場合には、処理システムによって実行されている第1プロセスが、処理システムの第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である。技術思想2は技術思想1のシステムを有し、制御論理は、翻訳識別子制御インジケータが第1状態にある場合には、複数の領域記述子の第2プロセスに対応する1つ以上の部分をマスキングする。技術思想3は技術思想2のシステムを有し、領域記述子のマスキングされた部分は、翻訳識別子値(TID)である。技術思想4は技術思想1のシステムを有し、さらに領域グローバル化制御イネーブルインジケータ(RGCEN)と;プロセス識別子(PID)と;制御論理とを有し、制御論理は、領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定するように動作可能であり、領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、翻訳識別子制御TIDCTLインジケータが第1状態にあるか否かに応じて第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるようにする。技術思想5は技術思想4のシステムを有し、さらに領域記述子は、グローバル化インジケータが第1状態にあるときには、それぞれの領域記述子が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を含む。技術思想6は技術思想1のシステムを有し、さらに制御レジスタ内のグローバル化PID(G_PID)フィールドと;制御論理とを有し、翻訳識別子制御インジケータが第1状態にあり、かつ第1プロセスのプロセス識別子(PID)値がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、制御論理は、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である。技術思想7は技術思想1のシステムを有し、さらに翻訳識別子制御インジケータが第1状態にあり、第1プロセスがスーパーバイザモードにあるときには、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である制御論理を有する。技術思想8は技術思想1のシステムを有し、さらに制御レジスタ内のメモリ保護ユニットイネーブル(MPUEN)インジケータを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、第1プロセスのアクセスアドレスが複数の領域記述子の1つ以上におけるアドレスに比較されて一致が存在するか否かを判定する。技術思想9は技術思想8のシステムを有し、一致が検出されず、かつアクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる。

【0067】

技術思想10に含まれるコンピュータ処理システムは、メモリ保護ユニット(MPU)と;グローバル化プロセス識別子(G_PID)フィールドを含む制御レジスタと;メモリ保護ユニットMPUに関連する複数の領域記述子とを有し、少なくとも1つの領域記述子が第1プロセスに割当てられており;さらに制御論理を有する。制御論理は、第1プロセスに対するプロセス識別子(PID)がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、第1プロセスが、第2プロセスのために割当てられたメモリ領域にアクセスできるように動作可能である。技術思想11は技術思想10のシステムを有し、さらに翻訳識別子制御インジケータ(TIDCTL)と;制御論理とを有し、翻訳識別子制御(TIDCTL)インジケータが第1状態にあり、かつ第1プロセスがスーパーバイザモードにあるときには、制御論理が第1プロセスと第2プロセスとに対する複数の領域記述子の1つ以上における翻訳識別子値(TID)をマスキングするように動作可能である。技術思想12は技術思想10のシステムを有し、翻訳識別子制御インジケータ(TIDCTL)が第1状態にある場合には、制御論理は、領域記述子の第2プロセスに使用される部分をマスキングする。技術思想13は技術思想12のシステムを有し、領域記述子のマスキングされた部分は、翻訳識別子値(TID)である。技術思想14は技術思想12のシステムを有し、さらに複数の領域記述子の1つ以上は、それぞれの領域記述子において定義されたメモリ領域が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を含む。技術思想15は技術思想14のシステムを有し、さらに領域グローバル化制御イネーブルインジケータ(RGCEN)を含む制御レジスタと;制御論理とを有し、制御論理は、領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定して、領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、翻訳識別子制御TIDCTLインジケータが第1状態にあるか否かに応じて第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である。技術思想17は技術思想14のシステムを有し、さらに制御レジスタ内のメモリ保護ユニットイネーブル(MPUEN)インジケータを初期化することを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、アクセスアドレスを複数の領域記述子の1つ以上で指定されたアドレスレンジに比較して一致が存在するか否かを判定し;一致が検出されず、かつアクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる。

【0068】

技術思想18に含まれる方法は、コンピュータシステムにおけるメモリ保護ユニット(MPU)の制御レジスタ内の翻訳識別子制御(TIDCTL)インジケータを初期化することを有し;翻訳識別子制御TIDCTLインジケータが第1状態にあるときには、第1プロセスと第2プロセスとに対するメモリ保護ユニットMPUの複数の領域記述子の1つ以上において翻訳識別子比較をマスキングして、第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるようにする。技術思想19は技術思想18の方法を有し、さらに制御レジスタ内の領域グローバル化制御イネーブル(RGCEN)インジケータを初期化することを有し;領域グローバル化制御イネーブルRGCENと翻訳識別子制御TIDCTLインジケータとが両方とも指定された状態にあるときには、第2プロセスに対する領域記述子における領域グローバル化制御(RGC)インジケータが指定された状態にあるか否かに基づき、翻訳識別子のマスキングが実施されることを含む。技術思想20は技術思想18の方法を有し、さらに制御レジスタ内のグローバル化プロセス識別子(G_PID)を初期化して第2プロセスに対するプロセス識別子(PID)を指定し;制御レジスタ内の初期化メモリ保護ユニットイネーブル(MPUEN)インジケータを初期化することを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、アクセスアドレスを複数の領域記述子の1つ以上によって定義されたアドレスレンジに比較して、一致が存在するか否かを判定することを含む。

【技術分野】

【0001】

本発明は、一般的にデータ処理システム、より具体的には領域記述子グローバル化制御を有するメモリ管理ユニット(MMU)に関する。

【背景技術】

【0002】

幾つかの内蔵プロセッサが、多数の可変長メモリ領域に対して保護情報を提供する内部メモリ保護ユニット(MPU)を実施する。アクセス保護は、命令フェッチとデータ読込/書出アクセスに基づき、これらのアクセスアドレスをメモリ保護ユニットMPUの各エントリに比較して一致を判定(決定)することによって実行される。アクセスに対する記述子の一致は、アクセスアドレスが領域記述子によって定義されたアドレスレンジ内にあり、現在のプロセス識別子(PID)が領域記述子によって定義されたプログラム済み領域識別子に一致し、そして当該領域記述子に関連した許可がこのアクセスタイプを許すときに起こる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】米国特許第6810471号

【発明の概要】

【発明が解決しようとする課題】

【0004】

メモリ保護ユニットMPUの或る実施において、すべて0値にプログラムされた領域識別子は、どんなプロセスによっても一致でき、通常スーパーバイザ専用領域のために使用される「グローバルな」領域記述子を示す。しかし、スーパーバイザのユーザ領域へのアクセスも必要とされるため、この実施は典型的に多重冗長領域記述子を要求するか、または現在のプロセス識別子PID値を修正してプログラムされた領域識別子に一致させるためにスーパーバイザコードを要求する。しかし、これらの解決は、リソース使用または性能オーバーヘッドの点で不利益をもたらす。さらに他のマッピング制約のために、スーパーバイザモードにおいて現在のプロセス識別子PID値を変更してユーザ領域のプロセス識別子PID値に一致させることは可能ではないであろう。

【課題を解決するための手段】

【0005】

メモリ管理ユニット(MPU)の領域記述子の動的グローバル化は、種々の制御機構を使用することによって可能となろう。たとえば一実施形態において、メモリ保護ユニットMPU内のすべてのまたは選択された領域記述子エントリの有効な領域IDをマスキングするグローバル化論理は実施できよう。一例において、このマスキングは、一時的に領域記述子エントリの有効な領域IDをすべて0値(または他の幾つかの所定の値)に強制して、領域記述子エントリの「グローバル化」を生じさせることができる。代替として、マスキングの結果、現在のプロセスIDは、領域記述子中にプログラムされた領域IDよりもグローバルなIDに一致することを必要とすることになろう。それゆえプロセッサの適切な状態における現在のプロセス動作(たとえばスーパーバイザモードにおける動作または特定のプロセス識別子値を有する動作)は、領域記述子エントリの特定の領域IDに一致する必要なく、領域記述子エントリによって定義された領域にアクセスできる。このようにして現在のプロセスは、メモリ領域に対応する領域記述子エントリによって異なるプロセスに割当てられたメモリ領域にアクセスできる。

【図面の簡単な説明】

【0006】

以下に本発明を図示によって説明するが、本発明は添付部の図面に限られるものではなく、同じ参照番号は類似の要素を指している。図中の要素は簡素かつ明瞭を旨として図示されており、必ずしも縮尺通りに描かれていない。

【図1】本発明の一実施形態に従いデータ処理システムをブロック図の形式で示す。

【図2】本発明の一実施形態に従い、図1のデータ処理システム内のメモリ保護ユニット(MPU)をブロック図の形式で示す。

【図3】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUにおける領域記述子を表の形式で示す。

【図4】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUで使用可能なメモリ保護ユニットMPU制御とステータスレジスタを線図の形式で示す。

【図5】本発明の一実施形態に従い、図4のメモリ保護ユニットMPU制御とステータスレジスタの種々のフィールドに対する記述を表の形式で示す。

【図6】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図7】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUで使用可能なメモリ保護ユニットMPU制御とステータスレジスタを線図の形式で示す。

【図8】本発明の一実施形態に従い、図7のメモリ保護ユニットMPU制御とステータスレジスタの種々のフィールドに対する記述を表の形式で示す。

【図9】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図10】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの領域記述子エントリに対する領域記述子一致論理を示す。

【図11】本発明の一実施形態に従い、図2のメモリ保護ユニットMPUの動作方法をフローチャートの形式で示す。

【発明を実施するための形態】

【0007】

本明細書中で使用される「バス」という言葉は、データ、アドレス、制御またはステータスなど1種類以上のタイプの情報を伝送するために使用できる複数の信号または導体の意味で用いる。本明細書中で論じられる導体は、単一導体、複数導体、一方向導体または双方向導体として図示または記述されよう。しかし、異なる実施形態において導体は別様であってよい。たとえば双方向導体よりも別個の一方向導体が使用されることもあれば、その逆のこともある。複数導体も多数の信号を連続的にまたは時分割多重化方式で伝送する単一導体に置き換えられてよい。同様に、多数の信号を運ぶ単一導体は、これらの信号のサブセットを運ぶ種々の異なる導体に分けることもできる。それゆえ信号の伝送については多くの選択肢が存在する。

【0008】

「アサートする」または「セットする」と、「ネゲートする」(または「デアサートする」もしくは「クリアする」)という言葉は、本明細書中では信号、ステータスビットまたは類似の装置をそれぞれ論理的に真の状態または論理的に偽の状態に翻訳することに関連して用いる。論理的に真の状態が論理レベル1であるならば、論理的に偽の状態は論理レベル0である。そして論理的に真の状態が論理レベル0であるならば、論理的に偽の状態は論理レベル1である。

【0009】

図1は、本発明の実施形態に従うデータ処理システム100を図示するブロック図である。データ処理システム100は、CPU0として表す第1プロセッサ10、第NのCPU(CPUN)として表す第2プロセッサコア12、インタコネクト20、メモリデバイス40、および周辺デバイス30、32、34を有する。プロセッサ10はさらに、データキャッシュ51と命令キャッシュ52を含むキャッシュ50;さらに領域記述子62とメモリ保護ユニットMPU制御モジュール64を含むメモリ保護ユニットMPU60;データ処理論理モジュール70;さらに現在のプロセス識別子(PID)を記憶する記憶回路57を含む制御レジスタ56;バスインタフェースユニット(BIU)80を有する。プロセッサ12は、類似のサブコンポーネント(図示せず)を有しており、各々のプロセッサは、追加のモジュール(見やすくするために図示せず)を含むことができる。

【0010】

メモリアクセス保護ポリシーは、データ処理システム100に含まれている1つ以上のメモリ保護ユニット(MPU)60で実施できる。データ処理システム100の動作中、プロセッサ10および12におけるデータ処理論理モジュール70は、メモリ40内の位置にアクセスするリクエストを出すことができる。たとえばデータ処理論理モジュール70は、メモリ40からプログラム命令またはデータ情報を取出し、またはデータ情報をメモリ40に記憶するリクエストを出すことができる。メモリアクセス保護ポリシーは、リクエストされたアクセスを許可または拒否するか判定(決定)する。メモリ保護ユニット内の2つの領域記述子がメモリ内のエリアで互いに重なるアドレスレンジを持ち、相反するアクセスポリシーを有するならば、デフォルトアクセスポリシーが実施されてよい。

【0011】

図1に示す実施形態においてデータ処理システム100は、携帯電子デバイス、コンピュータデバイス、自動車用デバイス、通信デバイスなどを含む多数の電子システムに組み込むことができる汎用データ処理デバイスである。プロセッサ10および12は、ソフトウエアを実行するように構成された回路であり、これによって所望されたタスクを実行する。

【0012】

メモリアクセスリクエストは、典型的にメモリ40内の特定の位置から情報を取出すロード命令の実行、またはメモリ40内の特定の位置に情報を書込む記憶命令の実行に関連している。アクセスしようとするメモリ内の位置を識別するために、メモリアクセスリクエストにはアドレスが付随する。ロード命令または記憶命令は、ソフトウエアプログラムに含めることができ、ソフトウエアプログラムは、スーパーバイザモードまたはユーザモードで実行できる。ソフトウエアプログラムの実行は、プロセスとも呼ばれ、読込アクセスリクエストまたは書出アクセスリクエストは、実行されている特定のプロセスに割当てられた現在のプロセス識別子値(PID)に関連させることができる。このプロセス識別子PIDは、制御レジスタ56内の記憶回路57に記憶できる。

【0013】

メモリ読込動作中にアクセスされる情報は、命令を含むか、またはデータ情報を含むことができ、メモリ書出動作に関連した情報は、一般的にデータ情報である。したがってメモリアクセスリクエストは、1つ以上のリクエスト属性の値に基づき特徴付けることができる。リクエスト属性の例は、アクセスしようとする位置のアドレスを示すためのアドレス属性;リクエストが読込リクエストであるか否かを示すための読込属性;リクエストが書出リクエストであるか否かを示すための書出属性;リクエストがスーパーバイザモードで出されたか否かを示すためのスーパーバイザ属性;リクエストがユーザモードで出されたか否かを示すためのユーザ属性、リクエストに関連したプロセスを識別するためのプロセス識別(PID)属性;リクエストされた情報が命令であるか否かを識別するための命令属性などを含む。任意の数のリクエスト属性を領域記述子62に含めて、メモリアクセスリクエストに関連させることができる。

【0014】

本明細書中で使用されているメモリ位置は、固有のシステムアドレスを有するすべてのデータ記憶位置を指すことが意図されている。そのような位置は、メモリデバイス40、周辺デバイス30、32、34などを含めて、システムアドレススペース内に含めることができる。同様に、フレーズメモリアクセスリクエストは、本明細書中では固有のシステムアドレスに基づく記憶位置にアクセスするすべてのリクエストを指すために用いられている。簡素にするために、本明細書中に記載されているメモリマッピングされた記憶位置および対応するアクセスリクエストは、それぞれメモリおよびメモリアクセスリクエストと呼ぶ。

【0015】

プロセッサ10および12は、インタコネクト20を介して、メモリ40および周辺デバイス30−34と通信できる。特に、インタコネクト20は、信号を伝送してリクエスト情報(REQUEST INFORMATION)90とリクエスト属性(REQUEST ATTRIBUTES)94を提供することができる。リクエスト情報90は、メモリアドレス(ADDRESS)、書出データ(WDATA)および読込データ(RDATA)を含む。メモリデバイス40は、プロセッサ10またはプロセッサ12によって出されたメモリアクセスリクエストを介してアクセス可能な記憶位置を提供できる。メモリデバイス40は、動的ランダムアクセスメモリ(DRAM)、静的ランダムアクセスメモリ(SRAM)などを含め任意の種類のメモリタイプを有してよい。見やすくするために、図1は、データ処理システム100のその他の構成要素で、動作が当業者によく知られているもの、たとえば高度キャッシュメモリデバイス、外部インタフェースなどは省いてある。さらにデータ処理システム100が有するプロセッサの数は、これよりも多くても少なくてもよい。

【0016】

動作中、プロセッサ10および12は、メモリ40にアクセスして、命令を取得し、データ情報を取出し、またはデータ情報を記憶することできる。たとえばプロセッサ10内のデータ処理論理モジュール70は、メモリ40の特定のメモリアドレスでデータ情報を取出すためにメモリアクセスリクエストを出すことができる。メモリ保護ユニットMPU60は、メモリアクセスリクエストを外部のプロセッサ10に伝送する前に、リクエストするデバイス(またはリクエストの発生源のソフトウエアプロセス)がアクセスを許すのに適した許可を持っているか判定できる。さらにプロセッサ10は、所望のデータ情報がデータキャッシュ51内にあるか判定できる。メモリ保護ユニットMPU60が、リクエストは許可されたが、所望のデータ情報がデータキャッシュ51内に存在しない(キャッシュミス)と判定したら、メモリアクセスリクエストがバスインタフェースユニットBIU80に送られる。バスインタフェースユニットBIU80は、インタコネクト20を介してメモリアクセスリクエストをメモリ40または周辺デバイス30、32、34に転送するように構成されている。

【0017】

バスインタフェースユニットBIU80は、信号ADDRESS、読込命令信号(図示せず)、およびリクエストに関連した他の属性の値を識別するリクエスト属性94を介してメモリアドレスを伝送することによってメモリ読込アクセスリクエストを開始できる。これらの信号は、インタコネクト20を介してメモリ40に伝えられる。メモリデバイス40は、リクエストされたデータ情報をバスインタフェースユニットBIU80に戻し、次いで信号RDATAによってインタコネクト20を介してデータ処理論理モジュール70に戻すことができる。

【0018】

同様の仕方で、プロセッサ10におけるデータ処理論理モジュール70は、メモリ40の特定のメモリアドレスにデータ情報を記憶するためにメモリアクセスリクエストを出すことができる。メモリ保護ユニットMPU60は、メモリアクセスリクエストを外部のプロセッサ10に伝送する前に、リクエストに関連したリクエスト属性の値に基づきアクセスを許可または拒否するか判定できる。メモリ保護ユニットMPU60が、リクエストに付随する属性は、メモリ保護ユニットMPU60によって維持される属性の要件を満たすと判定したら、メモリアクセスリクエストがバスインタフェースユニットBIU80に提供される。

【0019】

バスインタフェースユニットBIU80は、信号ADDRESS、信号WDATAを介してメモリ40に記憶されるべきデータ情報、書出命令信号(図示せず)、およびリクエストに関連した特権を識別するリクエスト属性94を介してメモリアドレスを伝送することによってメモリ書出アクセスリクエストを開始できる。

【0020】

メモリ40から読込または書出すためのメモリアクセスリクエストは、アクセスリクエストに関連した種々のリクエスト属性を示すために信号リクエスト属性94を介してメモリ40に送信できる追加の情報を含んでよい。リクエスト属性94は、上述したようにリクエスト源を識別する情報およびリクエストのタイプを含むことができる。たとえばリクエスト属性94は、リクエストがスーパーバイザモードかユーザモードのいずれで実行されるプロセスに関連しているかの指示、リクエストが読込動作か書出動作のいずれを実行するかの指示などを含むことができる。リクエスト属性94は、関連したメモリアクセスリクエストをさらに特定の方法で特徴付けることができる他の情報を含むことができる。

【0021】

上述したように、メモリ保護ユニットMPUたとえばメモリ保護ユニットMPU60は、1つ以上のアドレス領域に関連するそれぞれの許可情報を維持できる。メモリ保護ユニットMPU60は、命令フェッチおよびデータ読込/書出に基づき、メモリアドレスおよびこのメモリアクセスリクエストに関連するプロセスID(PID)をメモリ保護ユニットMPU60内の各エントリ(領域記述子62内に記憶)に比較して一致を判定することによって保護を実行する。メモリ保護ユニットMPU60がメモリアドレスに対応して一致する領域記述子62を識別すると、当該領域記述子62に含まれている属性が評価され得る。属性は、共に保護ポリシーの状況を定義する任意の数のリクエスト属性に関するものであってよい。たとえば領域記述子は、特定のメモリアドレス領域内に含まれている位置が書出保護されることを指定でき、またどんな場合に情報を記憶するリクエスト、たとえば情報が領域内の所定の位置に記憶されるべきであることを示す属性を有するリクエストが拒否され、または情報を取出すリクエスト、たとえば情報が領域内の位置から読込まれるべきであることを示す属性を有するリクエストが許可されるかを指定できる。同様に、領域記述子62は、メモリアドレス領域内に含まれている位置は、アクセスリクエストがスーパーバイザモードで実行されるプロセスによって出されたことを示す属性に関連するアクセスリクエストにだけアクセス可能であることを指定できる。

【0022】

メモリ保護ユニットMPU60の動作は、図2および図3を参照すれば一層よく理解されよう。図2は、本発明の特定の実施形態に従うメモリ保護ユニットMPU60を図示するブロック図である。メモリ保護ユニットMPU60は、1組の命令領域記述子202、1組のデータ領域記述子204、および1組の共有(命令またはデータ)領域記述子206を含む。メモリ保護ユニットMPU60は、メモリ保護ユニットMPU制御モジュール64も含む。メモリ保護ユニットMPU制御モジュール64は、リクエストに関連したアドレスおよび特権属性に基づき、またはアクセスが命令フェッチアクセス、読込アクセスもしくは書出アクセスであるかに基づき、ならびに領域記述子202、204および206に含まれた1つ以上の領域記述子の内容に基づき、各々のリクエストされたメモリアクセスを選択的に許可または拒否するように動作する。上述したように、リクエスト属性94は、アクセスリクエストを開始するデバイスまたはソフトウエアプロセスがスーパーバイザ特権を持っているか、それともユーザ特権しか持っていないかの指示を含むことができ、およびその他の属性、たとえばバスマスタ識別番号なども含んでよい。メモリアクセスリクエストが拒否されたら、メモリ保護ユニットMPU制御モジュール64は、リクエストするデバイスにメモリアクセス例外が発生したことを示す終了エラー応答を返すことができる。

【0023】

図3は、本発明の特定の実施形態に従い、領域記述子202、204または206のいずれかに対応できる領域記述子300の実施形態を図示する表である。領域記述子300(領域記述子エントリとも呼ぶ)は、複数のフィールド320−331を含む。フィールド320は、有効属性Vに関係する。対応する有効なビットがアサートされなければ、領域記述子は、無効である。有効なビットがアサートされ、領域記述子に関連したアドレスレンジがアドレスに関連するリクエストを有し、そして領域記述子に関連した領域識別子がリクエストに関連したプロセス識別子PIDに一致するならば、領域記述子に含まれた許可情報は、メモリアクセスリクエストに応答したと見なすことができる。

【0024】

フィールド321UPPER BOUNDとフィールド322LOWER BOUNDは、それぞれ領域記述子の関連アドレスレンジを示すための上限アドレス属性と下限アドレス属性に関する。

【0025】

フィールド325は、命令属性INSTに関する。この属性は、領域記述子が命令アクセス、たとえば対応する命令リクエスト属性もアサートされるようなアクセスリクエストに対してのみ有効であることを識別するためにアサートされ得る。したがって対応する命令属性は、セット202(命令領域記述子)に含まれた領域記述子ではアサートされ、セット204(データ領域記述子)に含まれた領域記述子ではネゲートされる。

【0026】

フィールド326は、SX属性(スーパーバイザ実行)、SW属性(スーパーバイザ書出)、およびSR属性(スーパーバイザ読込)を含む複数のアクセス可能属性に関係する。これらの属性は、領域記述子によって指定されたアドレス領域内に含まれた位置に対して領域記述子によって許可されるスーパーバイザレベルのソフトウエアのタイプを識別するために個々にアサートされ得る。たとえばSW属性(スーパーバイザ書出)がアサートされたら、(リクエストに付随する相応のリクエスト属性をアサートすることによって)スーパーバイザアクセスと書出アクセスの両方として識別されたアクセスリクエストは、関連するメモリアドレス領域内の位置に情報を記憶することを記述子によって許可される。同様に、SR属性(スーパーバイザ読込)がアサートされたら、スーパーバイザアクセスと読込アクセスの両方として識別されたアクセスリクエストは、関連する領域内の位置を読込むことを記述子によって許可される。属性SX(スーパーバイザ実行)は、関連する領域内の位置が実行され得るか否か識別する。

【0027】

フィールド327は、UX属性(ユーザ実行)、UW属性(ユーザ書出)、およびUR属性(ユーザ読込)を含む複数のアクセス可能属性に関係し、これらの属性は、個々に記述子によって領域記述子に対応する位置に対して許可されたユーザレベル・アクセスリクエストのタイプを識別する。

【0028】

フィールド328は、キャッシュ禁止領域属性CIに関係する。キャッシュ禁止領域属性は、リクエストするデバイスに対して関連する領域内の位置から取出された情報をキャッシュデバイス、たとえば図1のデータキャッシュ51や命令キャッシュ52に記憶しないように命令するためにアサートされ得る。

【0029】

フィールド329は、保護された領域属性Gに関係する。保護された領域属性は、関連する領域内に含まれる位置が通常のメモリ素子またはレジスタとは別様に動作することを示すためにアサートされ得る。その一例は、FIFO、揮発性記憶素子などに続いてまたは応答して値が変化できるメモリマッピングされた位置である。したがって保護された位置に関連する情報は、典型的にキャッシュメモリデバイスには記憶されない。

【0030】

フィールド330の翻訳識別子TIDは、領域記述子に対する領域識別子に関係する(TIDは、翻訳識別子とも呼ばれることに留意されたい)。上述したように、領域記述子の有効なビットがアサートされ、受領されたリクエストに対応するアクセスアドレスが領域記述子の上限(UPPER_BOUND)および下限によって示されたアドレスレンジ内にあり、そして受領されたリクエストに対応するプロセス識別子PID値が翻訳識別子TIDに一致したら、受領されたリクエストは、領域記述子に一致する。以下に論じるように、翻訳識別子TIDを「グローバル化」して、或る状況においては一致を示すために受領されたリクエストに対応するプロセス識別子PID値が翻訳識別子TIDに一致する必要がないようにすることは、有用であろう。このようにすると、以下に詳細に説明するように、翻訳識別子TIDは、種々の条件下で1回以上の制御を用いてマスキングされよう。

【0031】

フィールド331の領域グローバル化制御RGCは、領域記述子に対する領域グローバル化制御に関係する。領域グローバル化制御RGCは、グローバル化に対するより精細な粒度を許容する。たとえばそれはどの領域記述子をグローバル化制御に適用すべきかを示すために用いられてよい。このようにして、領域グローバル化制御RGCが或る領域記述子に対してアサートされたら、グローバル化制御(すなわちマスキング制御)が適用されるが、領域グローバル化制御RGCがアサートされなければ、グローバル化制御は適用されず、一致が生じるか否かの判定に翻訳識別子TIDが使用される。このフィールドは、領域記述子内に存在することも存在しないこともある。

【0032】

メモリ保護ユニットMPU60の動作中、データ処理論理70によって生成されるメモリアクセスリクエストが評価されて、アクセスしようとする位置のアドレス、リクエストに関連したプロセス識別子PID(記憶回路57から取得できる)、リクエストされたプロセッサまたはプロセスアクセスリクエストはスーパーバイザ特権またはユーザ特権を有するか、リクエストは読込アクセスまたは書出アクセスであるか、そしてリクエストは命令アクセスまたはデータアクセスに対するものであるかを判定できる。領域記述子202、204および206は、他のリクエスト属性に対応する追加のフィールド、またはアクセスリクエストを所望の仕方で識別し、またはさらに適格にする追加のフィールドを含むことができる。メモリ保護ユニットMPU60は、適当な単数または複数のセクタの各々の有効な領域記述子を審査できる(たとえば命令領域記述子と命令アクセスリクエストに対する共有領域記述子、およびデータ領域記述子とデータアクセスリクエストに対する共有領域記述子)。メモリ保護ユニットMPU60が入ってくるアクセスリクエストに一致する領域記述子を識別したら、メモリ保護ユニットMPU60は、リクエスト属性に基づき、および一致する領域記述子によって指定された許可に基づきアクセスを許可または拒否する。たとえばアドレスXYZを書出すユーザモードリクエストが受領されたら、そして有効な領域記述子がアドレスXYZを含むアドレス領域を定義し、そしてメモリアクセスリクエストに関連するプロセス識別子PIDが有効な領域記述子の翻訳識別子TIDに一致する値を持つ場合、UW属性(ユーザ書出)がアサートされればリクエストされたアクセスは許可され、UW属性(ユーザ書出)がアサートされなければ拒否され得る。さらにメモリアクセスが許可されたら、メモリアクセスは、一致する領域記述子内のキャッシュ禁止領域属性CIフィールドと保護された領域属性Gフィールドの値に基づき、それぞれキャッシュ禁止アクセスまたは保護されたアクセスとして実行され得る。1つ以上の有効な領域記述子がリクエストされたアクセスアドレスおよび対応するプロセス識別子PIDに一致したら、どの領域記述子または領域記述子の部分がアクセスを統制するかを判定するために任意のポリシーが利用されてよい。たとえば多数の一致する領域記述子の最も制限の少ないアクセス許可が使用されてよい。

【0033】

上述したように、スーパーバイザレベルのソフトウエアには、現在進行中のプロセスに関わりなく(すなわちプロセス識別子PID値に関わりなく)、コードのそれ自身のセクション(たとえばメモリ内のスーパーバイザ専用領域)にアクセスできるようにすることが望ましいであろう。さらにメモリ内のこれらのスーパーバイザ専用領域にアクセスすることに加えて、スーパーバイザがユーザ領域にアクセスできるようにすることも望ましいであろう。しかし、メモリ保護ユニットMPU60によって定義された各々の特定のユーザ領域は、プロセス識別子PID値に結び付いている。それゆえ一実施形態においては、アドレスレンジがアクセスリクエストのアドレスを有する領域記述子の翻訳識別子TIDに、実際の記憶された翻訳識別子TID値に関わりなく、一時的に0値(または他の所定の値)を強制して一致を許可するグローバル化制御機構が含まれている。これが行なわれてよいのは、たとえばスーパーバイザモードの場合のみであり、ユーザモードでは行なわれない。それゆえ一実施形態において、メモリ保護ユニットMPU60は、スーパーバイザモードにあるときにエントリに対するアドレスレンジ比較のプロセス識別子PID/翻訳識別子TID部分を実行するときに、すべての領域記述子(または領域記述子のサブセット)内の翻訳識別子TIDビットをグローバルに0にマスキングする能力を提供する。これはメモリ保護ユニットMPU制御レジスタにおいて制御ビットをセットすることによって行うことができる。

【0034】

図4は、グローバルマスキング制御フィールド、翻訳識別子制御TIDCTL、およびメモリ保護ユニットイネーブルフィールドMPUENを含む多数のフィールドを有するメモリ保護ユニットMPU制御およびステータスレジスタ400の例を線図の形式で示す。(翻訳識別子制御TIDCTLフィールドは、翻訳識別子制御インジケータとも呼ばれ、メモリ保護ユニットMPU制御およびステータスレジスタ400は、MPU0CSR0とも呼ばれることに留意されたい。)図4の例で、翻訳識別子制御TIDCTLフィールドは、ビット29に位置する1ビットフィールドであり、メモリ保護ユニットイネーブルMPUENフィールドは、ビット31に位置する1ビットフィールドである。図4の32ビットレジスタ内の残りのビットは予備で、他の制御またはステータス情報のために使用できる。代替的な実施形態は、メモリ保護ユニットMPU制御およびステータスレジスタを別様に配置でき、図示されているよりも多いまたは少ないフィールドを含んでよい。一実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ400は、メモリ保護ユニットMPU制御64内に位置している。

【0035】

図5は、翻訳識別子制御TIDCTLフィールドとメモリ保護ユニットイネーブルMPUENフィールドに対する記述を表の形式で提供する。メモリ保護ユニットイネーブルMPUENフィールドに関して、メモリ保護ユニットイネーブルMPUENビットがアサートされたら(論理レベル1)、メモリ保護ユニットMPU60はイネーブルされ、逆にネゲートされたら(論理レベル0)、メモリ保護ユニットMPU60はディスエーブルされる。それゆえこのビットは、メモリ保護ユニットMPU60の動作をイネーブルする。イネーブルされると、アクセスアドレスは、メモリ保護ユニットMPU60内の各エントリに一致条件について比較される。一致条件が生じず、アクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、アクセスに対する例外条件が送信される。翻訳識別子制御TIDCTLフィールドに関して、翻訳識別子制御TIDCTLフィールドがネゲートされたら(論理レベル0)、翻訳識別子TID比較が普通に行なわれ、グローバル化マスキングは行なわれない。すなわちこの場合には、メモリ保護ユニットMPU60の有効な領域記述子によって生じるべき一致条件について、アクセスアドレスは、有効な領域記述子のアドレスレンジ内になければならず、アクセスのプロセス識別子PIDは、有効な領域記述子の翻訳識別子TIDに一致しなければならない。翻訳識別子制御TIDCTLフィールドがアサートされたら(論理レベル1)、スーパーバイザモードにあるときにグローバル化マスキングを用いて翻訳識別子TID比較が行われる。さらに多数のヒットに対して(すなわち多数の領域記述子が一致条件となる場合)、一致する記述子の最も制限の少ないアクセス許可が使用される。現在の実施形態において、翻訳識別子制御TIDCTLビットがアサートされると、(ユーザモードではなく)スーパーバイザモードにあるときにプロセス識別子PID/翻訳識別子TID比較を行うときにすべての領域記述子内の翻訳識別子TIDビットがマスキングされる。

【0036】

スーパーバイザモードにあるときにマスキングを用いて翻訳識別子TID比較が行なわれるように翻訳識別子制御TIDCTLビットをアサートすることによって、スーパーバイザコードは、ユーザタスクのために最初にロードされた領域記述子を、これらの記述子内のプログラムされた翻訳識別子TID値に関わりなく利用することが許される。この能力は、特定の状況においてアクティブであるために必要とされるスーパーバイザ領域記述子の数を最小化するために用いることができ、それによって効率を高めることができる。さらに領域記述子内の実際の内容は、変更されない。すなわち翻訳識別子TID値は、プログラムされた状態に留まり、比較論理で0または他の所定の値にマスキングされるのみである。

【0037】

図6は、アクセスアドレスに対する領域記述子一致論理600とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理600は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。一致論理600は、ANDゲート618、616、610および602、ORゲート604、ならびにコンパレータ612、614、606および608を含む。ANDゲート602の第1入力は、対応する領域記述子エントリからの有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート604の出力に結合され、第3入力はANDゲート610の出力に結合される。ANDゲート602の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままか、または低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート604の第1入力はコンパレータ606の出力に結合され、ORゲート604の第2入力はコンパレータ608の出力に結合される。コンパレータ606は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート618の出力に結合された第2入力とを有する。ANDゲート618は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート618の第2入力は、ANDゲート616の出力に結合された反転入力である。

【0038】

ANDゲート616の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ400から翻訳識別子制御TIDCTL値を受取るように結合されており、ANDゲート616の第2入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。コンパレータ608は、ANDゲート618の出力に結合された第1入力を有する。ANDゲート610は、コンパレータ612の出力に結合された第1入力と、コンパレータ614の出力に結合された第2入力とを有する。コンパレータ612は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力とを有する。コンパレータ614は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力とを有する。

【0039】

動作中、一致論理600は、受取ったメモリアクセスリクエストおよび対応する領域記述子エントリに関して一致が生じるか判定する。一致論理600は、有効なビットがアサートされ(MPU_エントリ[V]は論理レベル1である)、ゲート604とゲート610の各々の出力が論理レベル1である場合のみ出力一致信号(MPU_エントリ_一致)をアサートする。受取ったメモリアクセスリクエストのアクセスアドレスが、領域記述子エントリの上限と下限によって指示されたアドレスレンジ内にあるとき、ANDゲート610の出力は高い(論理レベル1)。すなわちコンパレータ612は、アクセスアドレスが上限よりも小さいかチェックして、もし小さければその出力を論理レベル1にアサートし、またコンパレータ614は、アクセスアドレスが下限よりも大きいかチェックし、もし大きければその出力を論理レベル1にアサートする。これら両比較が出力を論理レベル1にアサートした場合のみ、ゲート610の出力は論理レベル1である。

【0040】

プロセス識別子PID/翻訳識別子TID比較部分および選択的グローバル化マスキングは、ORゲート604およびORゲート604を駆動する論理によって実行される。翻訳識別子制御TIDCTLビットが論理レベル0であれば、つまり翻訳識別子TID比較が普通に行なわれるならば、ANDゲート616の出力は論理レベル0であり、翻訳識別子TID値は、コンパレータ606および608に対するANDゲート618のnビット出力に提供される。しかし、翻訳識別子制御TIDCTLビットが論理レベル1であれば、スーパーバイザモードにあるとき翻訳識別子TID比較は、マスキングされる。それゆえMSR[PR]が論理レベル1でユーザモードを示すならば、ANDゲート616の第2入力で反転するために、ANDゲート616の出力は論理レベル0である。この場合には翻訳識別子TIDの値は、マスキングされずにANDゲート618を通過してコンパレータ606および608に提供される。しかしMSR[PR]が論理レベル0で、スーパーバイザモードを示すならば(および翻訳識別子制御TIDCTLが論理レベル1であれば)、ANDゲート616の出力は論理レベル1であり、ANDゲート618の第2入力で反転するために、ANDゲート618の出力はすべて0に強制される。それゆえ翻訳識別子TID値よりすべて0の値がコンパレータ606および608に提供される。翻訳識別子TID値がANDゲート618を通されたら、コンパレータ606によってプロセス識別子PIDに比較されて一致が生じるか判定される。好都合な比較(すなわち一致)の結果としてコンパレータ606の出力は高くなり(論理レベル1)、不都合な比較の結果としてコンパレータ606の出力低くなる(論理レベル0)。それゆえプロセス識別子PIDが翻訳識別子TID値に一致するならば、コンパレータ608の出力に関わりなくORゲート604の出力は高くなり、プライベートアドレスレンジが示される。しかしANDゲート618によって翻訳識別子TID値がすべて0値に強制されると、コンパレータ606の出力は低くなって不都合な比較を示すが、コンパレータ608の出力は高くなって好都合な比較(すなわち一致)を示す。この場合には、翻訳識別子TIDのマスキングのために共有レンジが示される。コンパレータ606の出力が高くなるか、またはコンパレータ608の出力が高くなる限り、その結果として比較のプロセス識別子PID/翻訳識別子TID部分が一致する。

【0041】

図4と図5の例の説明において、翻訳識別子制御TIDCTLビットがアサートされると、スーパーバイザモード中にプロセス識別子PID/翻訳識別子TID比較を実行したときにすべての領域記述子内の翻訳識別子TIDビットがマスキングされることに留意されたい。しかし、代替的な実施形態において、各領域記述子は、(上に図3を参照して述べたように)領域グローバル化制御RGCフィールドを含むことができ、領域グローバル化制御RGCフィールドがアサートされた領域記述子(たとえば論理レベル1)内の翻訳識別子TIDビットは、プロセス識別子PID/翻訳識別子TID比較の実行中マスキングされ、領域グローバル化制御RGCフィールドがネゲートされた領域記述子(たとえば論理レベル0)内のおよび翻訳識別子TIDビットはマスキングされない。領域グローバル化制御RGCフィールドによって示されるように、翻訳識別子制御TIDCTLを選択された領域記述子に適用できるようにするために、一致論理600は適宜修正されてよい。

【0042】

図7は、グローバル化プロセス識別子PID値、グローバル化プロセス識別子G_PID、グローバルマスキング制御フィールド、翻訳識別子制御TIDCTL、領域グローバル化制御イネーブルフィールド、領域グローバル化制御イネーブルRGCENおよびMPUイネーブルフィールドメモリ保護ユニットイネーブルMPUENを含む多数のフィールドを有するメモリ保護ユニットMPU制御およびステータスレジスタ700の別の例を線図の形式で示す。(翻訳識別子制御TIDCTLフィールドは、翻訳識別子制御インジケータとも呼ばれ、メモリ保護ユニットMPU制御およびステータスレジスタ700は、MPU0CSR0とも呼ばれることに留意されたい。)図7の例で、グローバル化プロセス識別子G_PIDフィールドは、ビット0−15に位置する16ビットフィールドであり、翻訳識別子制御TIDCTLフィールドは、ビット28および29に位置する多ビットフィールド(この例では2ビット)であり、領域グローバル化制御イネーブルRGCENフィールドは、ビット30に位置する1ビットフィールドであり、およびメモリ保護ユニットイネーブルMPUENフィールドは、ビット31に位置する1ビットフィールドである。図7の32ビットレジスタ内の残りのビットは予備であり、他の制御またはステータス情報に使用できる。代替的な実施形態は、メモリ保護ユニットMPU制御およびステータスレジスタを別様に配置でき、図示されているよりも多いまたは少ないフィールドを含んでよい。一実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ700は、メモリ保護ユニットMPU制御64内に位置している。

【0043】

図8は、グローバル化プロセス識別子G_PIDフィールド、翻訳識別子制御TIDCTLフィールド、領域グローバル化制御イネーブルRGCENフィールド、およびメモリ保護ユニットイネーブルMPUENフィールドに対する記述を表の形式で提供する。メモリ保護ユニットイネーブルMPUENフィールドに関して、メモリ保護ユニットイネーブルMPUENビットがアサートされたら(つまり論理レベル1なら)メモリ保護ユニットMPU60はイネーブルされ、逆にネゲートされたら(つまり論理レベル0なら)メモリ保護ユニットMPU60はディスエーブルされる。それゆえこのビットは、メモリ保護ユニットMPU60の動作をイネーブルする。イネーブルされたときアクセスアドレスは、メモリ保護ユニットMPU60内の各エントリに一致条件について比較される。一致条件が生じず、アクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにイネーブルされなければ、アクセスに対する例外条件が送信される。翻訳識別子制御TIDCTLフィールドに関して、翻訳識別子制御TIDCTLフィールドが00であれば、翻訳識別子TID比較が普通に行なわれ、グローバル化マスキングは実行されない。すなわちこの場合には、メモリ保護ユニットMPU60の有効な領域記述子で生じるべき一致条件について、アクセスアドレスは、有効な領域記述子のアドレスレンジ内になければならず、アクセスのプロセス識別子PIDは、有効な領域記述子の翻訳識別子TIDに一致しなければならない。翻訳識別子制御TIDCTLフィールドが01であれば、スーパーバイザモードにあるときにグローバル化マスキングを用いて翻訳識別子TID比較が行われる。さらに多数のヒットに対して(すなわち多数の領域記述子が一致条件となる場合)、一致する記述子の最も制限の少ないアクセス許可が使用される。それゆえ翻訳識別子TIDが00または01のときメモリ保護ユニットMPU60は、上に図5と図6に関して翻訳識別子TIDがそれぞれ0または1である場合について記述されたように動作することに留意されたい。翻訳識別子制御TIDCTLフィールドが10であれば、現在のプロセス識別子PID値がメモリ保護ユニットMPUステータスおよび制御レジスタ700内に記憶されたグローバル化プロセス識別子G_PID値に一致するとき、グローバル化マスキングを用いて翻訳識別子TID比較が行なわれる。この場合も多数のヒットに対しては、一致する記述子の最も制限の少ないアクセス許可が使用される。

【0044】

引き続き図8を参照して、領域グローバル化制御イネーブルRGCENフィールドが0の値を有する場合には、グローバル化マスキングがイネーブルされたとき領域記述子内の領域グローバル化制御RGCフィールドは、無視される。このようにしてグローバル化マスキングがイネーブルされると、(たとえばスーパーバイザモードでプロセス識別子PID/翻訳識別子TID比較を実行するときに翻訳識別子TIDビットをマスキングすることによって、または現在のプロセス識別子PIDを特定の記述子の翻訳識別子TIDよりもグローバル化プロセス識別子G_PIDに比較することによって)メモリ保護ユニットMPU60のすべての領域記述子が適宜マスキングされる。領域グローバル化制御イネーブルRGCENフィールドが1の値を有する場合には、領域記述子内の領域グローバル化制御RGCフィールドは、グローバル化マスキングがイネーブルされたとき記述子のグローバル化を適格にするために使用される。すなわち一実施形態において、領域グローバル化制御RGCフィールドがアサートされた領域記述子(たとえば論理レベル1)のみがグローバル化マスキングによってマスキングされる一方、領域グローバル化制御RGCフィールドがネゲートされた領域記述子(論理レベル0)に対しては、現在のプロセス識別子PID記述子の翻訳識別子TIDとの比較が普通に行なわれるであろう。

【0045】

図9は、アクセスアドレスに対する領域記述子一致論理900とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理900は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。図9の例は、グローバル化イネーブルを制御するためにグローバル化プロセス識別子G_PIDフィールドの使用を含むが、領域グローバル化制御イネーブルRGCENの使用は含まない。一致論理900は、ANDゲート922、920、918および902、ORゲート916および904、ならびにコンパレータ924、912、914、906および908を含む。ANDゲート902の第1入力は、対応する領域記述子エントリから有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート904の出力に結合され、第3入力はANDゲート910の出力に結合される。ANDゲート902の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままかまたは低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート904の第1入力はコンパレータ906の出力に結合され、ORゲート904の第2入力は、コンパレータ908の出力に結合される。コンパレータ906は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート918の出力に結合された第2入力を有する。ANDゲート618は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート918の第2入力は、ORゲート916の出力に結合された反転入力である。ORゲート916の第1入力は、ANDゲート922の出力に結合されている。ANDゲート922の第1入力は、第1インジケータを受取るように結合されており、この第1インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値が「01」であることを示す。それゆえもし翻訳識別子制御TIDCTLフィールドの値が「01」でなければ、第1インジケータは論理レベル0である。ANDゲート922の第2入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。ORゲート916の第2入力はANDゲート920の出力に結合される。ANDゲート920の第1入力は、第2インジケータを受取るように結合され、この第2インジケータは論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値は「10」であることを示す。それゆえ翻訳識別子制御TIDCTLフィールドの値が「10」でなければ、第2インジケータは論理レベル0である。ANDゲート920の第2入力はコンパレータ924の出力に結合される。コンパレータ924は、(たとえば記憶回路57から)現在のプロセス識別子PIDを受取るように結合された第1入力と、メモリ保護ユニットMPU制御およびステータスレジスタ700からグローバル化プロセス識別子G_PID値を受取るように結合された第2入力を有する。コンパレータ608は、ANDゲート918の出力に結合された第1入力を有する。ANDゲート910は、コンパレータ912の出力に結合された第1入力と、コンパレータ914の出力に結合された第2入力を有する。コンパレータ912は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力を有する。コンパレータ914は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力を有する。

【0046】

動作中、一致論理900は、受取ったメモリアクセスリクエストおよび対応する領域記述子エントリに関して一致が生じるか判定する。一致論理900は、有効なビットがアサートされ(MPU_エントリ[V]は論理レベル1である)、ゲート904とゲート910の各々の出力が論理レベル1である場合のみ出力一致信号(MPU_エントリ_一致)をアサートする。受取ったメモリアクセスリクエストのアクセスアドレスが領域記述子エントリの上限と下限によって指示されたアドレスレンジ内にあるとき、ANDゲート910の出力は高い(論理レベル1)。すなわちコンパレータ912は、アクセスアドレスが上限よりも小さいかチェックして、そうであればその出力を論理レベル1にアサートし、またコンパレータ9614は、アクセスアドレスが下限よりも大きいかチェックして、そうであれば出力を論理レベル1にアサートする。これら両比較が出力を論理レベル1にアサートした場合のみ、ゲート910の出力は論理レベル1である。

【0047】

プロセス識別子PID/翻訳識別子TID比較部分は、選択的グローバル化マスキングと同様、ORゲート904およびORゲート904を駆動する論理によって実施される。翻訳識別子制御TIDCTLフィールドが00であれば、つまり翻訳識別子TID比較が普通に行なわれるならば、ORゲート916の出力は論理レベル0であり、翻訳識別子TID値は、コンパレータ906および908へのANDゲート918のnビット出力に提供される。すなわち翻訳識別子制御TIDCTLが00であり、したがって01でも10でもなければ、ORゲート916への入力は論理レベル0である。翻訳識別子制御TIDCTLフィールドが論理レベル1であれば、スーパーバイザモードにあるとき翻訳識別子TID比較は、マスキングされる。それゆえMSR[PR]が論理レベル1であり、ユーザモードを示すならば、ANDゲート922の第2入力で反転するために、ANDゲート922の出力は論理レベル0である。また、翻訳識別子制御TIDCTLフィールドが論理レベル01であれば、ANDゲート922への第1入力は0であり、ANDゲート922の出力は0である。それゆえORゲート916の出力は0であり、翻訳識別子TIDの値は、マスキングされずにANDゲート918を通ってコンパレータ606および608に提供される。しかしMSR[PR]が論理レベル0でスーパーバイザモードを示すならば(および翻訳識別子制御TIDCTLが01であれば)、ANDゲート922の出力は論理レベル1である。この場合にはORゲート916の出力も1であり、ANDゲート918の第2入力で反転するために、ANDゲート918の出力はすべて0に強制される。それゆえコンパレータ906および908には、翻訳識別子TID値よりもすべて0の値が提供される。この場合ORゲート916の第2入力も、0であることに留意されたい。しかし、翻訳識別子制御TIDCTLフィールドが10であるならば、グローバル化プロセス識別子G_PID値を用いてグローバル化マスキング実施される。この場合にはANDゲート920への第1入力は論理レベル1であり、コンパレータ924は、現在のプロセス識別子PID値をメモリ保護ユニットMPU制御およびステータスレジスタ700からのグローバル化プロセス識別子G_PID値に比較する。一致があれば、コンパレータ924の出力は論理レベル1となり、ANDゲート920の出力は論理レベル1となる。この場合ORゲート916への第1入力は、(翻訳識別子制御TIDCTLが10なので)論理レベル0であり、ORゲート916の第2入力は論理レベル1である。それゆえORゲート916の出力も1であり、そしてANDゲート918の第2入力で反転するために、ANDゲート918の出力はすべて0に強制される。ORゲート916は、翻訳識別子制御TIDCTLが01または10かに従いグローバル化マスキングが生じるための適当な条件が満たされているか検出する。グローバル化マスキングが生じるべきであるならば、翻訳識別子TID値はすべて0に強制され、そうでなければ翻訳識別子TID値は、マスキングされずにANDゲート918を通過する。

【0048】

翻訳識別子TID値がANDゲート918を通過すると、コンパレータ906によってプロセス識別子PIDに比較されて一致が生じるか判定する。好都合な比較(すなわち一致)の結果としてコンパレータ906の出力は高くなり(論理レベル1)、不都合な比較の結果としてコンパレータ906の出力は低くなる(論理レベル0)。それゆえプロセス識別子PIDが翻訳識別子TID値に一致すれば、コンパレータ908の出力に関わりなくORゲート904の出力が高くなり、プライベートアドレスレンジが示される。しかしANDゲート918によって翻訳識別子TID値がすべて0値に強制されると、コンパレータ906の出力は低くなって不都合な比較を示すが、コンパレータ908の出力は高くなって好都合な比較(すなわち一致)を示す。この場合には、翻訳識別子TIDのマスキングのために共有レンジが示される。コンパレータ906の出力が高くなるか、またはコンパレータ908の出力が高くなれば、比較のプロセス識別子PID/翻訳識別子TID部分は、一致する結果となる。

【0049】

図10は、アクセスアドレスに対する領域記述子一致論理1000とその属性、およびそれがどのようにメモリ保護ユニットMPUエントリ内の対応するフィールドに比較されるかを、一部は概略的に、一部はブロック図で示す。それゆえ領域記述子一致論理1000は、比較論理とも呼ばれ、メモリ保護ユニットMPU60内の各領域記述子エントリに対して繰り返される。図10の例は、図9に示したように、グローバル化イネーブルを制御するためにグローバル化プロセス識別子G_PIDフィールドの使用を有し、さらに領域グローバル化制御イネーブルRGCENの使用を含む。一致論理1000は、ANDゲート1022、1020、1018,1010,1002および1026、ORゲート1016および1004、ならびにコンパレータ1024、1012、1014、1006および1008を含む。ANDゲート1002の第1入力は、対応する領域記述子エントリからの有効なビット(MPU_エントリ[V])を受取るように結合され、第2入力はORゲート1004の出力に結合され、第3入力はANDゲート1010の出力に結合される。ANDゲート1002の出力は、一致条件が生じるか否かを示す一致信号MPU_エントリ_一致を提供する。たとえば一致信号が高くなれば(論理レベル1)、当該領域記述子エントリに対する一致が生じており、一致信号が低いままかまたは低くなれば(論理レベル0)、一致は生じなかったことになる。ORゲート1004の第1入力はコンパレータ1006の出力に結合され、ORゲート1004の第2入力はコンパレータ1008の出力に結合される。コンパレータ1006は、(たとえば記憶回路57によって提供され得る)現在のアクセスリクエストのプロセス識別子PIDを受取るように結合された第1入力と、ANDゲート1018の出力に結合された第2入力を有する。ANDゲート1018は、対応する領域記述子エントリから翻訳識別子TID値(MPU_エントリ[TID])を受取るように結合された第1nビット入力を有する。ANDゲート1018の第2入力は、ORゲート1016の出力に結合された反転入力である。ORゲート1016の第1入力は、ANDゲート1022の出力に結合されている。ANDゲート1022の第1入力は、ORゲート1028の出力に結合されている。ORゲート1028の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ700から、領域グローバル化制御イネーブルRGCENの値を受取るように結合された反転入力である。ORゲート1028の第2入力は、ANDゲート1026の出力に結合されている。

【0050】

ANDゲート1026の第1入力は、メモリ保護ユニットMPU制御およびステータスレジスタ700から、領域グローバル化制御イネーブルRGCENの値を受取るように結合されており、ANDゲート1026の第2入力は、現在の記述子エントリの領域グローバル化制御RGCフィールドの値を受取るように結合されている。ANDゲート1022の第2入力は、第1インジケータを受取るように結合されている。この第1インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値が「01」であることを示す。それゆえもし翻訳識別子制御TIDCTLフィールドの値が「01」でなければ、第1インジケータは論理レベル0である。ANDゲート1022の第3入力は、スーパーバイザ/ユーザモードインジケータ(MSR[PR])を受取るように結合された反転入力である。これはたとえば制御レジスタ56内に配置できる機械状態レジスタ(MSR)の問題状態(PR)に対応しよう。本明細書中に記載された実施形態において、MSR[PR]に対する0の値はスーパーバイザモードを示し、1の値はユーザモードを示す。ORゲート1016の第2入力は、ANDゲート920の出力に結合される。ANDゲート1020の第1入力は、ORゲート1028の出力に結合されている。ANDゲート1020の第2入力は、第2インジケータを受取るように結合され、この第2インジケータは、論理レベル1にアサートされたら、メモリ保護ユニットMPU制御およびステータスレジスタ700からの翻訳識別子制御TIDCTLフィールドの2ビット値は「10」であることを示す。それゆえ翻訳識別子制御TIDCTLフィールドの値が「10」でなければ、第2インジケータは論理レベル0である。ANDゲート1020の第3入力は、コンパレータ1024の出力に結合される。コンパレータ1024は(たとえば記憶回路57から)現在のプロセス識別子PIDを受取るように結合された第1入力と、メモリ保護ユニットMPU制御およびステータスレジスタ700からグローバル化プロセス識別子G_PID値を受取るように結合された第2入力を有する。コンパレータ1008は、ANDゲート1018の出力に結合された第1入力を有する。ANDゲート1010は、コンパレータ1012の出力に結合された第1入力と、コンパレータ1014の出力に結合された第2入力を有する。コンパレータ1012は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから上限値(MPU_エントリ[UPPER_BOUND])を受取るように結合された第2入力を有する。コンパレータ1014は、メモリアクセスリクエストのアクセスアドレスを受取るように結合された第1入力と、対応する領域記述子エントリから下限値(MPU_エントリ[LOWER_BOUND])を受取るように結合された第2入力を有する。

【0051】

動作中、上にゲート916、918、906、908、904、912、914、910および902に関して説明したことは、それぞれゲート1016、1018、1006、1008、1004、1012、1014、1010、1002に該当することに留意されたい。しかし、一致論理1000においてグローバル化マスキングは、領域グローバル化制御イネーブルRGCENがイネーブルされると(たとえば論理レベル1)、さらに各エントリの領域グローバル化制御RGCフィールドによって適格にされる。領域グローバル化制御イネーブルRGCENがイネーブルされないと(たとえば論理レベル0)、ORゲート1028の反転入力のために、(ANDゲート1026の出力における値に関わりなく)ORゲート1028の出力は論理レベル1である。このようにしてエントリに対して翻訳識別子制御TIDCTL値に従い、グローバル化マスキングが実施される。すなわちORゲート1028の出力は論理レベル1であるから、ORゲート1028の出力はゲート1022および1020の出力に影響せず、これらのゲートの出力は、他の2つの入力によって判定される(これについては上に図9の類似の回路を参照して説明した)。

【0052】

領域グローバル化制御イネーブルRGCENがイネーブルされると、特定の領域記述子に対するグローバル化マスキングが、領域記述子の対応する領域グローバル化制御RGCフィールドによって判定される。領域グローバル化制御イネーブルRGCENがイネーブルされると(論理レベル1)、ORゲート1028の第1入力は論理レベル0であり、ORゲート1028の出力は、ANDゲート1026の出力によって判定される。それゆえ領域グローバル化制御イネーブルRGCENはイネーブルされるが、対応する領域記述子(すなわちエントリ)の領域グローバル化制御RGCフィールドが論理レベル0であれば、領域記述子に対してグローバル化マスキングは実施されない。この場合にはANDゲート1026の出力は論理レベル0であり、したがってORゲート1028の出力も論理レベル0である。このことはANDゲート1022および1020の出力、したがってORゲート1016の出力が、論理レベル0であることを保証する。それゆえ翻訳識別子TIDの値は、マスキングされずにANDゲート1018を通過してコンパレータ1006および1008に達する。しかし、領域グローバル化制御イネーブルRGCENがイネーブルされ(論理レベル1)、対応する領域記述子の領域グローバル化制御RGCフィールドが1であれば、エントリに対して翻訳識別子制御TIDCTL値に従うグローバル化マスキングが実施される。この場合にはANDゲート1026の出力およびORゲート1028は論理レベル1であり、したがってゲート1022および1020の出力には影響せず、これらのゲートの出力は、他の2つの入力によって判定される(これについては上に図9の類似の回路を参照して説明した)。それゆえ領域グローバル化制御イネーブルRGCENがイネーブルされ、領域記述子の領域グローバル化制御RGCがアサートされたら、当該領域記述子に対してグローバル化マスキングがイネーブルされて、翻訳識別子制御TIDCTLフィールドの値に従いプロセス識別子PIDが、領域記述子の翻訳識別子TIDに一致しない他のプロセスによって利用され得る。

【0053】

図11は、本発明の一実施形態に従うメモリ保護ユニットMPU60の動作の方法1100をフローチャートで示す。図11に示す実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ(たとえばメモリ保護ユニットMPU制御およびステータスレジスタ700)のRCGENと、グローバル化プロセス識別子G_PIDフィールドおよび領域記述子の領域グローバル化制御RGCフィールドとが、メモリ保護ユニットMPU60に対して存在している。図示された実施形態において、メモリ保護ユニットMPU制御およびステータスレジスタ(たとえばメモリ保護ユニットMPU制御およびステータスレジスタ700)の翻訳識別子制御TIDCTLフィールドは、少なくとも3つの状態(たとえば00、01、10)を持てることが前提とされている。方法1100はブロック1102で開始し、ここで翻訳識別子制御TIDCTL、RCGEN、グローバル化プロセス識別子G_PID、およびメモリ保護ユニットイネーブルMPUENフィールドが適当に初期化される。たとえば或る適当な状態は、翻訳識別子制御TIDCTL(たとえば図8に関して説明した00、01、10)に記憶でき、適当なグローバルプロセス識別子PIDはグローバル化プロセス識別子G_PIDに記憶でき、RCGENはアサートまたはネゲートされて、それぞれ領域グローバル化制御RGCフィールドの使用をイネーブルまたはディスエーブルすることができる。メモリ保護ユニットMPU60の領域記述子内の各領域グローバル化制御RGCフィールドは、各領域記述子エントリが作成されるときに初期化され得る。

【0054】

方法1100は判定ダイヤモンド1104に進み、ここでRCGENがイネーブルされるか判定される。RCGENがイネーブルされなければ、方法は判定ダイヤモンド1108に進み、ここでメモリ保護ユニットMPU60内の各領域記述子について翻訳識別子制御TIDCTLフィールドの値に基づき、グローバル化マスキングが選択的にイネーブルされる。以下に説明するように判定ダイヤモンド1108、1110および1112は、領域記述子に対応する特定のメモリ領域についてグローバル化マスキングが行なわれるべきか判定する。判定ダイヤモンド1104で領域グローバル化制御イネーブルRGCENがイネーブルされたら、フローチャートは判定ダイヤモンド1106に進み、ここで各領域記述子について対応する領域グローバル化制御RGCが、イネーブルされるか判定される。次に方法1100は判定ダイヤモンド1108に進み、ここで(判定ダイヤモンド1108、1110および1112に対応して)翻訳識別子制御TIDCTL値に従いグローバル化マスキングを実施するか否かの判定は、領域グローバル化制御RGCフィールドがイネーブルされた領域記述子についてのみ行なわれる。領域グローバル化制御RGCがイネーブルされない他のすべての領域記述子については、翻訳識別子TID比較が普通に行なわれ、上述したように一致条件が生じるためには現在のプロセス識別子PIDは、領域記述子の翻訳識別子TIDに一致する必要がある。

【0055】

判定ダイヤモンド1108では、グローバル化がイネーブルされた領域記述子(RGCENがイネーブルされない場合にはすべての領域記述子、または領域グローバル化制御イネーブルRGCENがイネーブルされた場合にはイネーブルされた領域グローバル化制御RGCフィールドを持つ領域記述子のみ)について、翻訳識別子制御TIDCTLフィールドが状態0にあるか判定される。一実施形態において状態0は、図8を参照して述べられた「00」の値に対応することができる。対応する場合には方法1100はブロック1122に進み、ここでは翻訳識別子TIDのマスキングは生じない。このマスキングがない場合には、一致条件を判定するための翻訳識別子TID比較が普通に行なわれる。判定ダイヤモンド1108で翻訳識別子制御TIDCTLフィールドが状態0になければ、方法1100は判定ダイヤモンド1110に進み、ここで翻訳識別子制御TIDCTLフィールドが状態2にあるか判定される。一実施形態において状態2は、図8を参照して述べたように「10」の値に対応することができる。対応する場合には、方法1100は判定ダイヤモンド1114に進み、ここで現在のメモリアクセスリクエストに対応する現在のプロセス識別子PIDが、グローバル化プロセス識別子PID(メモリ保護ユニットMPU制御およびステータスレジスタのグローバル化プロセス識別子G_PID)に一致するか判定される。一致しない場合には、方法はブロック1122に進み、ここでは当該領域記述子に対して翻訳識別子TIDのマスキングは実施されない。一致する場合には、方法は判定ダイヤモンド1116に進み、ここで(領域記述子のUPPER_BOUNDフィールドとLOWER_BOUNDフィールドを用いて)現在のメモリアクセスリクエストのアドレスが、領域記述子に対応するメモリ領域に一致するか判定される。判定ダイヤモンド1116でアドレスの一致がなければ、方法1100はブロック1120に進み、ここでは当該エントリについて一致条件は生じない。或る場合には、アクセス例外が出される(たとえばメモリ保護ユニットMPU60のどの領域記述子とも一致が生じない場合)。判定ダイヤモンド1116でアドレスの一致があれば、方法1100はブロック1118に進み、ここで方法は翻訳識別子TIDの比較をマスキングして、現在のプロセスが、(メモリ保護ユニットMPU60の領域記述子によって)異なるプロセスに割当てられ得るメモリにアクセスできるようにする。

【0056】

判定ダイヤモンド1110で翻訳識別子制御TIDCTLフィールドが状態2になければ、方法1100は判定ダイヤモンド1112に進み、ここで翻訳識別子制御TIDCTLフィールドが状態1にあり(図8を参照して述べたように「10」の翻訳識別子制御TIDCTL値に対応することができる)、プロセッサは、スーパーバイザモードで動作しているか判定される。該当しない場合には、方法1100はポイントBを通ってブロック1122に進み、ここではマスキングが実施されない。該当する場合には、方法1100は判定ダイヤモンド1124に進み、ここで現在のメモリアクセスリクエストのアドレスが領域記述子に対応するメモリの領域に一致するか判定される。一致しない場合には、方法1100はポイントAを通ってブロック1120に進む。アドレスの一致が生じる場合には、方法1100はブロック1118に進み、ここで方法は、翻訳識別子TIDとプロセス識別子PIDの一致比較をマスキングして、現在のプロセスが異なるプロセスに割当てられ得るメモリにアクセスできるようにする。

【0057】

それゆえ以上によって、どのようにグローバル化マスキングが行なわれて、プロセッサ上のプロセス実行が、メモリ保護ユニットMPU領域記述子の方法によって異なるプロセスに割当てられたメモリ内の領域にアクセスできるようになるかが理解される。このようにしてグローバル化マスキングは、領域記述子の翻訳識別子TIDなど領域記述子の部分が、一致条件の判定において利用されないようにすることができる。たとえば翻訳識別子TIDに対してグローバル化マスキングが行なわれると、現在のプロセスのプロセス識別子は、アクセスされているメモリ領域に対応する領域記述子の翻訳識別子TIDに一致する必要がない。一実施形態においてグローバル化マスキングがイネーブルされると、領域記述子の翻訳識別子TIDが0に強制されて領域記述子比較から有効に除外されるので、現在のプロセスは、任意のプロセス識別子PID値を持つことができる。代替としてグローバル化マスキングがイネーブルされると、現在のプロセスは、アクセスされている領域に対応する翻訳識別子TIDよりも、グローバルプロセス識別子PIDに一致しなければならない。さらに領域記述子の領域グローバル化制御RGCフィールドなど追加の制御を用いることによって、メモリ保護ユニットMPU内の領域記述子のサブセットに対してグローバル化マスキングが実施され得る。このようにして処理時間またはメモリ保護ユニットMPU内のエントリの数を増すことなく、スーパーバイザコードなど特定のソフトウエアによって多くの制御を与えることができる。

【0058】

本発明を実施する装置は、大部分が当業者に公知の電子コンポーネントと電子回路からなるので、本発明の基礎をなすコンセプトを理解および評価し、また本発明の教示を不明瞭または散漫にしないために、回路の詳細については上述したように必要と見なされる程度を越えて説明しない。

【0059】

上記の実施形態の幾つかで該当するものは、多様な種類の情報処理システムを用いて実施できる。たとえば図1とこれに関する議論は、例示的な情報処理アーキテクチャを記述しているが、この例示的なアーキテクチャは、単に本発明の種々の側面を論じる際に有益な参照を提供するために提示されているに過ぎない。もちろん、アーキテクチャの記述は、議論の目的のために単純化されており、本発明に従って使用できる多様なタイプの適当なアーキテクチャの一つに過ぎない。当業者は、論理ブロックの境界が単に例示的なものであり、代替的な実施形態は、論理ブロックや回路要素を統合したり、別様に機能を分解して種々の論理ブロックや回路要素に課したりできることを認識するであろう。

【0060】

したがって本明細書中に示されたアーキテクチャは、単に例示的なものであり、実際には同じ機能を達成する他の多くのアーキテクチャも実施できることが理解されるべきである。抽象的ではあるが明確な意味において、同じ機能を達成するためのコンポーネントの任意の構成は、所望の機能が達成されるように有効に「関連している」。したがって本明細書中で特定の機能を達成するために組み合わされた2つのコンポーネントは、アーキテクチャであるか中間的なコンポーネントであるかに関わりなく、所望の機能が達成されるように互いに「関連している」。同様に、そのように関連している任意の2つのコンポーネントは、所望の機能を達成するために互いに「動作的に接続している」または「動作的に結合している」と見ることができる。

【0061】

またたとえば一実施形態において、システム100の図示された素子は、単一の集積回路上または同じデバイス内に配置された回路である。代替として、システム100は、任意の数の別個の集積回路または互いに相互接続された別個のデバイスを含むことができる。

【0062】

さらに当業者は、上記の動作の機能間の境界が単に例示的なものに過ぎないことを認識するであろう。多数の動作の機能は、単一の動作に組み合わされ、および/または単一の動作の機能は、追加の動作に配分されてよい。さらに代替的な実施形態は、特定の動作の多数のインスタンスを含んでよく、動作の順序は、他の種々の実施形態で変更されてよい。

【0063】

本明細書において本発明は、特定の実施形態を参照して説明されているが、以下の特許請求の範囲に記載された本発明の範囲から逸脱することなく種々の変容や変更を行うことができる。したがって詳細な説明と図面は、制限的な意味ではなく例示的な意味を持つものと見なされるべきであり、そのようなすべての変容は、本発明の範囲に含まれることが意図されている。本明細書で特定の実施形態に関して記載されているいかなる効果、利点または問題の解決も、一部または全部の請求項の枢要、不可欠または必須の特徴もしくは要素と解釈されることを意図していない。

【0064】

本明細書中で使用されている「結合」という言葉は、直接的結合または機械的結合に制限されることを意図していない。

さらに本明細書中で使用されている「a」または「an」の言葉は、1つまたは1つよりも多いものとして定義される。また、特許請求の範囲において「少なくとも1つの」や「1つ以上の」などの導入句を使用することは、不定冠詞「a」または「an」によって他の請求要素を導入することが、そのように導入された請求要素を含む特定の請求項を、そのような要素を1個のみ含む発明に制限することを含意するものと解釈されてはならない。これは、同じ請求項が「1つ以上の」または「少なくとも1つの」という導入句と、「a」または「an」などの不定冠詞を含む場合も同様である。

【0065】

別途記載のない限り、「第1」および「第2」という言葉は、そのような言葉で記述される要素を任意に区別するために用いられる。したがってこれらの言葉は、必ずしもそれらの要素の時間順や優先順を示すことが意図されていない。

【0066】

以下に、本発明の種々の実施形態を示す。

技術思想1に含まれるコンピュータ処理システムは、メモリ保護ユニット(MPU)と;メモリ保護ユニットに関連する複数の領域記述子とを有し、領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値とを有する。コンピュータ処理システムはさらに、翻訳識別子制御インジケータ(TIDCTL)と;制御論理とを有しており、制御論理は、翻訳識別子制御インジケータが第1状態にあるか否かを判定して、翻訳識別子制御インジケータが第1状態にある場合には、処理システムによって実行されている第1プロセスが、処理システムの第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である。技術思想2は技術思想1のシステムを有し、制御論理は、翻訳識別子制御インジケータが第1状態にある場合には、複数の領域記述子の第2プロセスに対応する1つ以上の部分をマスキングする。技術思想3は技術思想2のシステムを有し、領域記述子のマスキングされた部分は、翻訳識別子値(TID)である。技術思想4は技術思想1のシステムを有し、さらに領域グローバル化制御イネーブルインジケータ(RGCEN)と;プロセス識別子(PID)と;制御論理とを有し、制御論理は、領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定するように動作可能であり、領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、翻訳識別子制御TIDCTLインジケータが第1状態にあるか否かに応じて第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるようにする。技術思想5は技術思想4のシステムを有し、さらに領域記述子は、グローバル化インジケータが第1状態にあるときには、それぞれの領域記述子が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を含む。技術思想6は技術思想1のシステムを有し、さらに制御レジスタ内のグローバル化PID(G_PID)フィールドと;制御論理とを有し、翻訳識別子制御インジケータが第1状態にあり、かつ第1プロセスのプロセス識別子(PID)値がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、制御論理は、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である。技術思想7は技術思想1のシステムを有し、さらに翻訳識別子制御インジケータが第1状態にあり、第1プロセスがスーパーバイザモードにあるときには、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である制御論理を有する。技術思想8は技術思想1のシステムを有し、さらに制御レジスタ内のメモリ保護ユニットイネーブル(MPUEN)インジケータを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、第1プロセスのアクセスアドレスが複数の領域記述子の1つ以上におけるアドレスに比較されて一致が存在するか否かを判定する。技術思想9は技術思想8のシステムを有し、一致が検出されず、かつアクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる。

【0067】

技術思想10に含まれるコンピュータ処理システムは、メモリ保護ユニット(MPU)と;グローバル化プロセス識別子(G_PID)フィールドを含む制御レジスタと;メモリ保護ユニットMPUに関連する複数の領域記述子とを有し、少なくとも1つの領域記述子が第1プロセスに割当てられており;さらに制御論理を有する。制御論理は、第1プロセスに対するプロセス識別子(PID)がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、第1プロセスが、第2プロセスのために割当てられたメモリ領域にアクセスできるように動作可能である。技術思想11は技術思想10のシステムを有し、さらに翻訳識別子制御インジケータ(TIDCTL)と;制御論理とを有し、翻訳識別子制御(TIDCTL)インジケータが第1状態にあり、かつ第1プロセスがスーパーバイザモードにあるときには、制御論理が第1プロセスと第2プロセスとに対する複数の領域記述子の1つ以上における翻訳識別子値(TID)をマスキングするように動作可能である。技術思想12は技術思想10のシステムを有し、翻訳識別子制御インジケータ(TIDCTL)が第1状態にある場合には、制御論理は、領域記述子の第2プロセスに使用される部分をマスキングする。技術思想13は技術思想12のシステムを有し、領域記述子のマスキングされた部分は、翻訳識別子値(TID)である。技術思想14は技術思想12のシステムを有し、さらに複数の領域記述子の1つ以上は、それぞれの領域記述子において定義されたメモリ領域が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を含む。技術思想15は技術思想14のシステムを有し、さらに領域グローバル化制御イネーブルインジケータ(RGCEN)を含む制御レジスタと;制御論理とを有し、制御論理は、領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定して、領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、翻訳識別子制御TIDCTLインジケータが第1状態にあるか否かに応じて第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である。技術思想17は技術思想14のシステムを有し、さらに制御レジスタ内のメモリ保護ユニットイネーブル(MPUEN)インジケータを初期化することを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、アクセスアドレスを複数の領域記述子の1つ以上で指定されたアドレスレンジに比較して一致が存在するか否かを判定し;一致が検出されず、かつアクセスタイプがメモリ保護ユニットMPU保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる。

【0068】

技術思想18に含まれる方法は、コンピュータシステムにおけるメモリ保護ユニット(MPU)の制御レジスタ内の翻訳識別子制御(TIDCTL)インジケータを初期化することを有し;翻訳識別子制御TIDCTLインジケータが第1状態にあるときには、第1プロセスと第2プロセスとに対するメモリ保護ユニットMPUの複数の領域記述子の1つ以上において翻訳識別子比較をマスキングして、第1プロセスが、第2プロセスに割当てられたメモリ領域にアクセスできるようにする。技術思想19は技術思想18の方法を有し、さらに制御レジスタ内の領域グローバル化制御イネーブル(RGCEN)インジケータを初期化することを有し;領域グローバル化制御イネーブルRGCENと翻訳識別子制御TIDCTLインジケータとが両方とも指定された状態にあるときには、第2プロセスに対する領域記述子における領域グローバル化制御(RGC)インジケータが指定された状態にあるか否かに基づき、翻訳識別子のマスキングが実施されることを含む。技術思想20は技術思想18の方法を有し、さらに制御レジスタ内のグローバル化プロセス識別子(G_PID)を初期化して第2プロセスに対するプロセス識別子(PID)を指定し;制御レジスタ内の初期化メモリ保護ユニットイネーブル(MPUEN)インジケータを初期化することを有し、メモリ保護ユニットイネーブルMPUENインジケータが第1状態にあるときには、アクセスアドレスを複数の領域記述子の1つ以上によって定義されたアドレスレンジに比較して、一致が存在するか否かを判定することを含む。

【特許請求の範囲】

【請求項1】

メモリ保護ユニット(MPU)と;

前記メモリ保護ユニットに関連する複数の領域記述子であって、前記領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値とを有することと;

翻訳識別子制御インジケータ(TIDCTL)と;

第1制御論理と

を有するコンピュータ処理システムであって、

前記第1制御論理は、前記翻訳識別子制御インジケータが第1状態にあるか否かを判定し、前記翻訳識別子制御インジケータが第1状態にある場合には、前記コンピュータ処理システムによって実行されている第1プロセスが、前記コンピュータ処理システムの第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である

ことを特徴とする、コンピュータ処理システム。

【請求項2】

前記第1制御論理は、前記翻訳識別子制御インジケータが第1状態にある場合には、複数の前記領域記述子の第2プロセスに対応する1つ以上の部分をマスキングする、

請求項1記載のコンピュータ処理システム。

【請求項3】

前記領域記述子のマスキングされた前記部分は、翻訳識別子値(TID)である、

請求項2記載のコンピュータ処理システム。

【請求項4】

前記コンピュータ処理システムはさらに、

領域グローバル化制御イネーブルインジケータ(RGCEN)と;

プロセス識別子(PID)と;

第2制御論理とを有し、

前記第2制御論理は、前記領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定するように動作可能であり、前記領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、前記翻訳識別子制御インジケータ(TIDCTL)が前記第1状態にあるか否かに応じて前記第1プロセスが、前記第2プロセスに割当てられたメモリ領域にアクセスできるようにする、

請求項1記載のコンピュータ処理システム。

【請求項5】

前記領域記述子は、グローバル化インジケータが第1状態にあるときには、それぞれの領域記述子が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を有する、

請求項4記載のコンピュータ処理システム。

【請求項6】

前記コンピュータ処理システムはさらに、

制御レジスタ内のグローバル化PID(G_PID)フィールドと;

第3制御論理と

を有し、

前記第3制御論理は、前記翻訳識別子制御インジケータが第1状態にあり、かつ第1プロセスのプロセス識別子(PID)値がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である、

請求項1記載のコンピュータ処理システム。

【請求項7】

前記コンピュータ処理システムはさらに第4制御論理を有し、

前記第4制御論理は、前記翻訳識別子制御インジケータが第1状態にあり、かつ第1プロセスがスーパーバイザモードにあるときには、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である、

請求項1記載のコンピュータ処理システム。

【請求項8】

前記コンピュータ処理システムはさらに、制御レジスタ内のメモリ保護ユニットイネーブルインジケータ(MPUEN)を有し、

前記メモリ保護ユニットイネーブルインジケータが第1状態にあるときには、第1プロセスのアクセスアドレスが、複数の領域記述子の1つ以上におけるアドレスに比較されて一致が存在するか否かが判定される、

請求項1記載のコンピュータ処理システム。

【請求項9】

前記一致が検出されず、かつアクセスタイプがメモリ保護ユニット保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる、

請求項8記載のコンピュータ処理システム。

【請求項10】

メモリ保護ユニット(MPU)と;

グローバル化プロセス識別子(G_PID)フィールドを含む制御レジスタと;

メモリ保護ユニットに関連する複数の領域記述子であって、少なくとも1つの前記領域記述子が第1プロセスに割当てられていることと;

第1制御論理と

を有するコンピュータ処理システムであって、

前記第1制御論理は、前記第1プロセスに対するプロセス識別子(PID)がグローバル化プロセス識別子(G_PID)フィールド内の値に一致するときには、前記第1プロセスが、第2プロセスのために割当てられたメモリ領域にアクセスできるように動作可能である、

コンピュータ処理システム。

【請求項11】

前記コンピュータ処理システムはさらに、

翻訳識別子制御インジケータ(TIDCTL)と;

第2制御論理と

を有し、

前記第2制御論理は、前記翻訳識別子制御インジケータ(TIDCTL)が第1状態にあり、かつ第1プロセスがスーパーバイザモードにあるときには、前記第1プロセスと前記第2プロセスとに対する複数の領域記述子の、1つ以上における翻訳識別子値(TID)をマスキングするように動作可能である、

請求項10記載のコンピュータ処理システム。

【請求項12】

翻訳識別子制御インジケータ(TIDCTL)が第1状態にある場合には、前記第1制御論理は、領域記述子の第2プロセスに使用される部分をマスキングする、

請求項10記載のコンピュータ処理システム。

【請求項13】

前記領域記述子のマスキングされた部分は、翻訳識別子値(TID)である、

請求項12記載のコンピュータ処理システム。

【請求項14】

複数の領域記述子の1つ以上は、それぞれの領域記述子において定義されたメモリ領域が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を有する、

請求項12記載のコンピュータ処理システム。

【請求項15】

前記コンピュータ処理システムはさらに、

領域グローバル化制御イネーブルインジケータ(RGCEN)を含む制御レジスタと;

第3制御論理と

を有し、

前記第3制御論理は、前記領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定し、前記領域グローバル化制御イネーブルインジケータが前記第1状態にはない場合には、翻訳識別子制御インジケータ(TIDCTL)が第1状態にあるか否かに応じて、前記第1プロセスが、前記第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である、

請求項14記載のコンピュータ処理システム。

【請求項16】

前記第1制御論理はさらに、制御レジスタ内のメモリ保護ユニットイネーブルインジケータ(MPUEN)を初期化し、前記メモリ保護ユニットイネーブルインジケータ(MPUEN)が第1状態にあるときには、アクセスアドレスを、複数の領域記述子の1つ以上で指定されたアドレスレンジに比較して一致が存在するか否かを判定し;

一致が検出されず、かつアクセスタイプがメモリ保護ユニット保護をバイパスするようにはイネーブルされないときには、例外条件が送信されてアクセスを試みる、

請求項14記載のコンピュータ処理システム。

【請求項17】

コンピュータ処理システムにおけるメモリ保護ユニット(MPU)の制御レジスタ内の、翻訳識別子制御インジケータ(TIDCTL)を初期化することと;

前記翻訳識別子制御インジケータ(TIDCTL)が第1状態にあるときには、第1プロセスと第2プロセスとに対するメモリ保護ユニットの複数の領域記述子の1つ以上において翻訳識別子比較をマスキングすることで、前記第1プロセスが、前記第2プロセスに割当てられたメモリ領域にアクセスできるようにすることと

を有する方法。

【請求項18】

前記方法はさらに、制御レジスタ内の領域グローバル化制御イネーブルインジケータ(RGCEN)を初期化することと;

前記領域グローバル化制御イネーブルインジケータ(RGCEN)と前記翻訳識別子制御インジケータ(TIDCTL)とが両方とも指定された状態にあるときには、前記第2プロセスに対する領域記述子における領域グローバル化制御インジケータ(RGC)が指定された状態にあるか否かに基づき、翻訳識別子のマスキングを実施することと

を有する、請求項17記載の方法。

【請求項19】

前記方法はさらに、制御レジスタ内のグローバル化プロセス識別子(G_PID)を初期化することで、前記第2プロセスに対するプロセス識別子(PID)を指定することと;

制御レジスタ内の初期化メモリ保護ユニットイネーブルインジケータ(MPUEN)を初期化して、メモリ保護ユニットイネーブルインジケータが第1状態にあるときには、アクセスアドレスを複数の領域記述子の1つ以上によって定義されたアドレスレンジに比較して、一致が存在するか否かを判定することと

を有する、請求項17記載の方法。

【請求項1】

メモリ保護ユニット(MPU)と;

前記メモリ保護ユニットに関連する複数の領域記述子であって、前記領域記述子は、それぞれのメモリ領域に対するアドレスレンジと翻訳識別子値とを有することと;

翻訳識別子制御インジケータ(TIDCTL)と;

第1制御論理と

を有するコンピュータ処理システムであって、

前記第1制御論理は、前記翻訳識別子制御インジケータが第1状態にあるか否かを判定し、前記翻訳識別子制御インジケータが第1状態にある場合には、前記コンピュータ処理システムによって実行されている第1プロセスが、前記コンピュータ処理システムの第2プロセスに割当てられたメモリ領域にアクセスできるように動作可能である

ことを特徴とする、コンピュータ処理システム。

【請求項2】

前記第1制御論理は、前記翻訳識別子制御インジケータが第1状態にある場合には、複数の前記領域記述子の第2プロセスに対応する1つ以上の部分をマスキングする、

請求項1記載のコンピュータ処理システム。

【請求項3】

前記領域記述子のマスキングされた前記部分は、翻訳識別子値(TID)である、

請求項2記載のコンピュータ処理システム。

【請求項4】

前記コンピュータ処理システムはさらに、

領域グローバル化制御イネーブルインジケータ(RGCEN)と;

プロセス識別子(PID)と;

第2制御論理とを有し、

前記第2制御論理は、前記領域グローバル化制御イネーブルインジケータが第1状態にあるか否かを判定するように動作可能であり、前記領域グローバル化制御イネーブルインジケータが第1状態にはない場合には、前記翻訳識別子制御インジケータ(TIDCTL)が前記第1状態にあるか否かに応じて前記第1プロセスが、前記第2プロセスに割当てられたメモリ領域にアクセスできるようにする、

請求項1記載のコンピュータ処理システム。

【請求項5】

前記領域記述子は、グローバル化インジケータが第1状態にあるときには、それぞれの領域記述子が他のプロセスによって利用され得るか否かを示す領域グローバル化制御インジケータ(RGC)を有する、

請求項4記載のコンピュータ処理システム。

【請求項6】

前記コンピュータ処理システムはさらに、

制御レジスタ内のグローバル化PID(G_PID)フィールドと;

第3制御論理と

を有し、

前記第3制御論理は、前記翻訳識別子制御インジケータが第1状態にあり、かつ第1プロセスのプロセス識別子(PID)値がグローバル化プロセス識別子G_PIDフィールド内の値に一致するときには、翻訳識別子(TID)比較のためにグローバル化マスキングを使用するように動作可能である、

請求項1記載のコンピュータ処理システム。