駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

【解決手段】オフセット補償機能付き駆動回路190は、入力電位に応じたレベルの出力電位を出力するプッシュ型駆動回路160と、駆動回路160のオフセット電圧VOFを補償するオフセット補償回路とを備える。オフセット補償回路は、キャパシタ122およびスイッチS1〜S4を含む。スイッチS1,S2をオンしてキャパシタ122をオフセット電圧VOFに充電し、次にスイッチS3をオンしてVI+VOFを駆動回路160に与え、次いでスイッチS4をオンしてVO=VIとする。したがって、消費電流を低減し、オフセット電圧VOFを補償できる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は駆動回路に関し、特に、入力電位に応じた電位を出力ノードに出力する駆動回路に関する。

【背景技術】

【0002】

従来より、半導体集積回路装置には、駆動能力が小さな電位発生回路で生成された電位を負荷に伝達するための駆動回路が設けられている。図80は、そのような駆動回路300の構成を示す回路図である。図80において、この駆動回路300は、P型電界効果トランジスタ(以下、P型トランジスタと称す)301,302、N型電界効果トランジスタ(以下、N型トランジスタと称す)303,304および定電流源305を含む。

【0003】

P型トランジスタ301,302は、それぞれ電源電位VCCのノードとノードN301,N302との間に接続され、それらのゲートはともにノードN301に接続される。P型トランジスタ301,302は、カレントミラー回路を構成する。N型トランジスタ303は、ノードN301とN305の間に接続され、そのゲートは入力ノードN303に接続される。N型トランジスタ304は、ノードN302とN305の間に接続され、そのゲートは出力ノードN304およびノードN302に接続される。定電流源305は、ノードN305と接地電位GNDのノードとの間に接続され、一定の電流を流す。

【0004】

N型トランジスタ303には、入力ノードN303の電位VIに応じた値の電流が流れる。N型トランジスタ303とP型トランジスタ301は直列接続され、P型トランジスタ301と302はカレントミラー回路を構成しているので、トランジスタ301〜303には同じ値の電流が流れる。出力ノードN304の電位VOが入力電位VIよりも低い場合は、トランジスタ301〜303に流れる電流よりもN型トランジスタ304に流れる電流が小さくなり、出力電位VOが上昇する。出力ノードN304の電位VOが入力電位VIよりも高い場合は、トランジスタ301〜303に流れる電流よりもN型トランジスタ304に流れる電流が大きくなり、出力電位VOが低下する。したがって、出力電位VOは入力電位VIに等しくなる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の駆動回路300では、電源電位VCCのノードからトランジスタ301〜304および定電流源305を介して接地電位GNDのノードに一定の貫通電流が常時流れていたので、消費電流が大きいという問題があった。

【0006】

それゆえに、この発明の主たる目的は、消費電流が小さな駆動回路を提供することである。

【課題を解決するための手段】

【0007】

この発明に係る駆動回路は、入力電位に応じた電位を出力ノードに出力する駆動回路であって、入力電位を予め定められた第1の電圧だけある電位方向にレベルシフトさせた電位を出力する第1のレベルシフト回路と、第1のレベルシフト回路の出力電位をある電位方向と逆の電位方向に予め定められた第2の電圧だけレベルシフトさせた電位を出力ノードに出力する第2のレベルシフト回路と、第1および第2の電圧の差の電圧であるオフセット電圧を打消して出力ノードの電位を入力電位に一致させるオフセット補償回路とを備えたものである。第1のレベルシフト回路は、その一方電極が第1の電源電位を受ける第1の電流制限素子と、その第1の電極が第2の電源電位を受け、その入力電極が入力電位を受ける第1の導電形式の第1のトランジスタと、その第1の電極および入力電極が第1の電流制限素子の他方電極に接続され、その第2の電極が第1のトランジスタの第2の電極に接続された第2の導電形式の第2のトランジスタとを含む。第2のレベルシフト回路は、その第1の電極が第3の電源電位を受け、その入力電極が第1の電流制限素子の他方電極に接続された第2の導電形式の第3のトランジスタと、その第1の電極が第3のトランジスタの第2の電極に接続され、その第2の電極および入力電極が出力ノードに接続された第1の導電形式の第4のトランジスタとを含む。

【発明の効果】

【0008】

この発明に係る駆動回路では、入力電位を第1の電圧だけある電位方向にレベルシフトさせた電位を出力する第1のレベルシフト回路と、第1のレベルシフト回路の出力電位をある電位方向と逆の電位方向に第2の電圧だけレベルシフトさせた電位を出力ノードに出力する第2のレベルシフト回路と、第1および第2の電圧の差の電圧であるオフセット電圧を打消して出力ノードの電位を入力電位に一致させるオフセット補償回路とが設けられる。したがって、第1および第2のレベルシフト回路の貫通電流を小さく抑えることにより、消費電流が小さくてすむ。また、オフセット補償回路を設けたので、出力電位を入力電位に一致させることができる。

【図面の簡単な説明】

【0009】

【図1】この発明の実施の形態1によるカラー液晶表示装置の全体構成を示すブロック図である。

【図2】図1に示した各液晶セルに対応して設けられた液晶駆動回路の構成を示す回路図である。

【図3】図1に示した水平走査回路の要部を示す回路ブロック図である。

【図4】図3に示した駆動回路の構成を示す回路図である。

【図5】図4に示した駆動回路の動作を説明するための回路図である。

【図6】図4に示した駆動回路の動作を説明するためのタイムチャートである。

【図7】実施の形態1の変更例を示す回路図である。

【図8】実施の形態1の他の変更例を示す回路図である。

【図9】実施の形態1のさらに他の変更例を示す回路図である。

【図10】この発明の実施の形態2による駆動回路のレベルシフト回路の構成を示す回路図である。

【図11】この発明の実施の形態3による駆動回路のレベルシフトの構成を示す回路図である。

【図12】この発明の実施の形態4による駆動回路のレベルシフト回路の構成を示す回路図である。

【図13】この発明の実施の形態5による駆動回路のレベルシフト回路の構成を示す回路図である。

【図14】実施の形態1の問題点を説明するための図である。

【図15】実施の形態1の問題点を説明するための回路図である。

【図16】実施の形態6の原理を説明するための回路図である。

【図17】この発明の実施の形態6による駆動回路の構成を示す回路図である。

【図18】図17に示した駆動回路の構成をより詳細に示す回路図である。

【図19】実施の形態6の変更例を示す回路図である。

【図20】実施の形態6の他の変更例を示す回路図である。

【図21】実施の形態6のさらに他の変更例を示す回路図である。

【図22】この発明の実施の形態7による駆動回路の構成を示す回路図である。

【図23】図22に示した駆動回路の動作を示すタイムチャートである。

【図24】実施の形態7の変更例を示す回路図である。

【図25】この発明の実施の形態8による駆動回路の構成を示す回路図である。

【図26】実施の形態8の変更例を示す回路図である。

【図27】実施の形態8の他の変更例を示す回路図である。

【図28】実施の形態8のさらに他の変更例を示す回路図である。

【図29】実施の形態8のさらに他の変更例を示す回路図である。

【図30】実施の形態8のさらに他の変更例を示す回路図である。

【図31】この発明の実施の形態9による駆動回路の構成を示す回路図である。

【図32】図31に示した駆動回路の動作を示すタイムチャートである。

【図33】実施の形態9の変更例を示す回路図である。

【図34】この発明の実施の形態10による駆動回路の構成を示す回路図である。

【図35】実施の形態10の変更例を示す回路図である。

【図36】この発明の実施の形態11による駆動回路の構成を示す回路図である。

【図37】図36に示した駆動回路の構成を示す回路図である。

【図38】この発明の実施の形態12によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図39】図38に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図40】この発明の実施の形態13によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図41】図40に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図42】図40に示したオフセット補償機能付駆動回路の動作を示す他のタイムチャートである。

【図43】実施の形態13の変更例を示す回路図である。

【図44】実施の形態13の他の変更例を示す回路図である。

【図45】実施の形態13のさらに他の変更例を示す回路図である。

【図46】実施の形態13のさらに他の変更例を示す回路図である。

【図47】実施の形態13のさらに他の変更例を示す回路図である。

【図48】実施の形態13のさらに他の変更例を示す回路図である。

【図49】実施の形態13のさらに他の変更例を示す回路図である。

【図50】実施の形態13のさらに他の変更例を示す回路図である。

【図51】実施の形態13のさらに他の変更例を示す回路図である。

【図52】実施の形態13のさらに他の変更例を示す回路図である。

【図53】実施の形態13のさらに他の変更例を示す回路図である。

【図54】実施の形態13のさらに他の変更例を示す回路図である。

【図55】この発明の実施の形態14によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図56】図55に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図57】図55に示したオフセット補償機能付駆動回路の動作を示す他のタイムチャートである。

【図58】この発明の実施の形態15によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図59】図58に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図60】この発明の実施の形態16によるカラー液晶表示装置の要部を示す回路図である。

【図61】図60に示したカラー液晶表示装置に含まれるプッシュ型駆動回路の構成を示す回路図である。

【図62】図60に示したプッシュ型駆動回路の構成をより詳細に示す回路図である。

【図63】実施の形態16の変更例を示す回路図である。

【図64】実施の形態16の他の変更例を示す回路図である。

【図65】この発明の実施の形態17によるプル型駆動回路の構成を示す回路図である。

【図66】実施の形態17の変更例を示す回路図である。

【図67】この発明の実施の形態18による駆動回路の構成を示す回路ブロック図である。

【図68】実施の形態18の変更例を示す回路図である。

【図69】実施の形態18の他の変更例を示す回路図である。

【図70】実施の形態18のさらに他の変更例を示す回路図である。

【図71】図70に示した駆動回路の構成をより詳細に示す回路図である。

【図72】この発明の実施の形態19によるオフセット補償機能付プッシュ型駆動回路の構成を示す回路ブロック図である。

【図73】実施の形態20の変更例を示す回路図である。

【図74】この発明の実施の形態20によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図75】実施の形態20の変更例を示す回路図である。

【図76】実施の形態20の他の変更例を示す回路図である。

【図77】実施の形態20のさらに他の変更例を示す回路図である。

【図78】この発明の実施の形態21によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図79】この発明の実施の形態22によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図80】従来の駆動回路の構成を示す回路図である。

【発明を実施するための形態】

【0010】

[実施の形態1]

図1は、この発明の実施の形態1によるカラー液晶表示装置の構成を示すブロック図である。図1において、このカラー液晶表示装置は、液晶パネル1、垂直走査回路7および水平走査回路8を備え、たとえば携帯電話機に設けられる。

【0011】

液晶パネル1は、複数行複数列に配列された複数の液晶セル2と、各行に対応して設けられた走査線4および共通電位線5と、各列に対応して設けられたデータ線6とを含む。

【0012】

液晶セル2は、各行において3つずつ予めグループ化されている。各グループの3つの液晶セル2には、それぞれR,G,Bのカラーフィルタが設けられている。各グループの3つの液晶セル2は、1つの画素3を構成している。

【0013】

各液晶セル2には、図2に示すように、液晶駆動回路10が設けられている。液晶駆動回路10は、N型トランジスタ11およびキャパシタ12を含む。N型トランジスタ11は、データ線6と液晶セル2の一方電極2aとの間に接続され、そのゲートは走査線4に接続される。キャパシタ12は、液晶セル2の一方電極2aと共通電位線5との間に接続される。液晶セル2の他方電極には駆動電位VDDが与えられ、共通電位線5には共通電位VSSが与えられる。

【0014】

図1に戻って、垂直走査回路7は、画像信号に従って、複数の走査線4を所定時間ずつ順次選択し、選択した走査線4を選択レベルの「H」レベルにする。走査線4が選択レベルの「H」レベルにされると、図2のN型トランジスタ11が導通し、その走査線4に対応する各液晶セル2の一方電極2aとその液晶セル2に対応するデータ線6とが結合される。

【0015】

水平走査回路8は、画像信号に従って、垂直走査回路7によって1本の走査線4が選択されている間に複数のデータ線6をたとえば12本ずつ順次選択し、選択した各データ線6に階調電位VGを与える。液晶セル2の光透過率は、階調電位VGのレベルに応じて変化する。

【0016】

垂直走査回路7および水平走査回路8によって液晶パネル1の全液晶セル2が走査されると、液晶パネル1には1つの画像が表示される。

【0017】

図3は、図1に示した水平走査回路8の要部を示す回路ブロック図である。図3において、水平走査回路8は、階調電位発生回路15および駆動回路20を含む。階調電位発生回路15および駆動回路20は、水平走査回路8によって同時に選択されるデータ線6の数(この場合は12)だけ設けられている。

【0018】

階調電位発生回路15は、第1電源電位V1(5V)のノードと第2電源電位V2(0V)のノードとの間に直列接続されたn+1個(ただし、nは自然数である)の抵抗素子16.1〜16.n+1と、n+1個の抵抗素子16.1〜16.n+1の間のn個のノードと出力ノード15aとの間にそれぞれ接続されたn個のスイッチ17.1〜17.nとを含む。

【0019】

n+1個の抵抗素子16.1〜16.n+1の間のn個のノードには、それぞれn段階の電位が現われる。スイッチ17.1〜17.nは、画像濃度信号φPによって制御され、それらのうちのいずれか1つのみが導通状態にされる。出力ノード15aには、n段階の電位のうちのいずれか1つの段階の電位が階調電位VGとして出力される。駆動回路20は、選択されたデータ線6が階調電位VGになるようにデータ線6に電流を供給する。

【0020】

図4は、駆動回路20の構成を示す回路図である。図4において、駆動回路20は、レベルシフト回路21,25、キャパシタ29、プルアップ回路30およびプルダウン回路33を含む。

【0021】

レベルシフト回路21は、第3電源電位V3(15V)のノードと接地電位GNDのノードとの間に直列接続された抵抗素子22、N型トランジスタ23およびP型トランジスタ24を含む。N型トランジスタ23のゲートは、そのドレイン(ノードN22)に接続されている。N型トランジスタ23は、ダイオード素子を構成する。P型トランジスタ24のゲートは、入力ノードN20に接続される。抵抗素子22の抵抗値は、トランジスタ23,24の導通抵抗値よりも十分大きな値に設定されている。

【0022】

入力ノードN20の電位(階調電位)をVIとし、P型トランジスタのしきい値電圧をVTPとし、N型トランジスタのしきい値電圧をVTNとすると、P型トランジスタ24のソース(ノードN23)の電位V23およびN型トランジスタ23のドレイン(ノードN22)の電位V22はそれぞれ次式(1)(2)で表わされる。

V23=VI+|VTP| …(1)

V22=VI+|VTP|+VTN …(2)

したがって、レベルシフト回路21は、入力電位VIを|VTP|+VTNだけレベルシフトさせた電位V22を出力する。

【0023】

レベルシフト回路25は、第4電源電位V4(5V)のノードと第5電源電位V5(−10V)との間に直列接続されたN型トランジスタ26、P型トランジスタ27および抵抗素子28を含む。N型トランジスタ26のゲートは、入力ノードN20に接続される。P型トランジスタ27のゲートは、そのドレイン(ノードN27)に接続される。P型トランジスタ27は、ダイオード素子を構成する。抵抗素子28の抵抗値は、トランジスタ26,27の導通抵抗値よりも十分大きな値に設定されている。

【0024】

N型トランジスタ26のソース(ノードN26)の電位V26およびP型トランジスタ27のドレイン(ノードN27)の電位V27は、それぞれ次式(3)(4)で表わされる。

V26=VI−VTN …(3)

V27=VI−VTN−|VTP| …(4)

したがって、レベルシフト回路25は、入力電位VIを−VTN−|VTP|だけレベルシフトさせた電位V27を出力する。

【0025】

キャパシタ29は、レベルシフト回路21の出力ノードN22とレベルシフト回路25の出力ノードN27との間に接続される。キャパシタ29は、ノードN22の電位変化をノードN27に伝達するとともに、ノードN27の電位変化をノードN22に伝達する。

【0026】

プルアップ回路30は、第6電源電位V6(15V)のノードと出力ノードN30との間に直列接続されたN型トランジスタ31およびP型トランジスタ32を含む。出力ノードN30には、負荷容量(データ線6の寄生容量)36が接続されている。N型トランジスタ31のゲートは、レベルシフト回路21の出力電位V22を受ける。P型トランジスタ32のゲートは、そのドレインに接続されている。P型トランジスタ30は、ダイオード素子を構成する。N型トランジスタ31は飽和領域で動作するように第6電源電位V6が設定されているので、N型トランジスタ31はいわゆるソースフォロア動作を行なう。

【0027】

今、説明の都合上、図5に示すように、P型トランジスタ32のドレイン(ノードN30′)と出力ノードN30との間が非導通状態にあると仮定する。N型トランジスタ31のソース(ノードN31)の電位V31およびP型トランジスタ32のドレイン(ノードN30′)の電位V30′は、それぞれ次式(5)(6)で表わされる。

V31=V22−VTN=VI+|VTP| …(5)

V30′=V31−|VTP|=VI …(6)

図4に戻って、プルダウン回路33は、第7電源電位V7(−10V)のノードと出力ノードN30との間に直列接続されたP型トランジスタ35およびN型トランジスタ34を含む。P型トランジスタ35のゲートは、レベルシフト回路25の出力電位V27を受ける。N型トランジスタ34のゲートは、そのドレインに接続されている。N型トランジスタ34は、ダイオード素子を構成する。P型トランジスタ35は飽和領域で動作するように第7電源電位V7が設定されているので、P型トランジスタ35はいわゆるソースフォロア動作を行なう。

【0028】

今、説明の都合上、図5に示すように、N型トランジスタ34のドレイン(ノードN30″)と出力ノードN30との間が非導通状態にあると仮定する。P型トランジスタ35のソース(ノードN34)の電位V34およびN型トランジスタ34のドレイン(ノードN30″)の電位V30″は、それぞれ次式(7)(8)で表わされる。

V34=V27+|VTP|=VI−VTN …(7)

V30″=V34+VTN=VI …(8)

数式(7)(8)は、P型トランジスタ32のドレイン(ノードN30′)とN型トランジスタ34のドレイン(ノードN30″)とを接続しても第6電源電位V6のノードと第7電源電位V7のノードとの間には電流は流れず、出力ノードN30の電位VOが入力ノードN20の電位VIと同じになることを示している。したがって、抵抗素子22,28の抵抗値を十分に大きくしておけば、VO=VIとなった定常状態では、貫通電流は極めて小さくなる。

【0029】

図6は、この駆動回路20の交流動作(遷移状態での動作)を説明するためのタイムチャートである。図6において、初期状態では、VI=VLとされているものとする。これにより、V22,V27,VOは、それぞれ以下のようになっている。

V22=VL+|VTP|+VTN

V27=VL−|VTP|−VTN

VO=VL

時刻t1においてVIがVLからVHに立上げられると、V22,V27,VOは所定時間の経過後にそれぞれ以下のようになる。

V22=VH+|VTP|+VTN

V27=VH−|VTP|−VTN

VO=VH

このレベル変化の過程で、以下の動作が行なわれる。レベルシフト回路25では、時刻t1において入力電位VIがVLからVHに立上げられると、N型トランジスタ26の駆動能力が高くなり、ノードN26の電位V26が急速に上昇する。これにより、P型トランジスタ27のソース−ゲート間電圧が大きくなってP型トランジスタ27の駆動能力も高くなり、ノードN27の電位V27が急速に上昇する。

【0030】

ノードN27の電位V27が急速に上昇すると、容量結合によってキャパシタ29を介してノードN22の電位V22がVH−VL分だけ急速に上昇する。これに応じて出力ノードN30の電位VOもVLからVHに急速に立上げられる。

【0031】

また時刻t2において入力電位VIがVHからVLに立下げられると、P型トランジスタ24の駆動能力が高くなり、ノードN23の電位V23が急速に低下する。これにより、N型トランジスタ23のゲート−ソース間電圧が大きくなってN型トランジスタ23の駆動能力も高くなり、ノードN22の電位V22が急速に低下する。

【0032】

ノードN22の電位V22が急速に低下すると、容量結合によってキャパシタ29を介してノードN27の電位V27がVH−VL分だけ急速に低下する。これに応じて出力ノードN30の電位VOもVHからVLに急速に立下げられる。

【0033】

この実施の形態1では、定常状態ではプルアップ回路30およびプルダウン回路33に貫通電流は流れず、抵抗素子22,28の抵抗値をトランジスタ23,24,26,27の導通抵抗値よりも十分高くすることによりレベルシフト回路21,25の貫通電流も小さくすることができるので、直流電流の低減化を図ることができる。また、キャパシタ29を設けたので、入力電位VIの変化に対しても迅速に応答することができる。

【0034】

以下、種々の変更例について説明する。図7の駆動回路36は、図4の駆動回路20からキャパシタ29を除去したものである。負荷容量36の容量値が比較的小さい場合は、トランジスタ23,24,26,27,31,32,34,35の寸法を小さくすることができる。トランジスタ23,27,31,35の寸法を小さくするとトランジスタ23,27,31,35のゲート容量が小さくなり、ノードN22,N27の寄生容量が小さくなる。したがって、キャパシタ29がなくても抵抗素子22,28を介して行われる充放電によってノードN22,N27の電位V22,V27の立上げおよび立下げが可能となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0035】

図8の駆動回路37は、図4の駆動回路20からダイオード接続されたトランジスタ23,27,32,34を除去したものである。出力電位VOは、VO=VI+|VTP|−VTNとなる。ただし、|VTP|≒VTNと設定すれば、VO≒VIとなる。あるいは、|VTP|−VTNの値をオフセット値として使用上考慮しておけば図4の駆動回路20と同様に使用することができる。この変更例では、トランジスタ23,27,32,34を除去したので、回路の占有面積を小さくすることができる。

【0036】

図9の駆動回路38は、図8の駆動回路37からさらにキャパシタ29を除去したものである。負荷容量36の容量値が比較的小さい場合は、トランジスタ24,26,31,35の寸法を小さくすることができ、ノードN22,N27の寄生容量を小さくすることができる。したがって、キャパシタ29がなくても抵抗素子22,28を介して行われる充放電によってノードN22,N27の電位V22,V27の立上げおよび立下げが可能となる。この変更例では、キャパシタ29を除去したので、回路の占有面積をさらに小さくすることができる。

【0037】

[実施の形態2]

実施の形態1では、同一極性のトランジスタのしきい値電圧はすべて同一であると仮定したが、実際には製造条件の変動などに起因してトランジスタのしきい値電圧にばらつきが生じる場合がある。トランジスタのしきい値電圧にばらつきが生じると、VI=VOにならなくなる。この実施の形態2では、この問題の解決を図る。

【0038】

図10は、この発明の実施の形態2による駆動回路のレベルシフト回路40の構成を示す回路図であって、図4のレベルシフト回路21と対比される図である。図10を参照して、このレベルシフト回路40が図4のレベルシフト回路21と異なる点は、N型トランジスタ23およびP型トランジスタ24がヒューズ41.1〜41.m(ただし、mは自然数である)、N型トランジスタ42.0〜42.mおよびP型トランジスタ43.0〜43.mで置換されている点である。

【0039】

ヒューズ41.1〜41mの各々は、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ41.1〜41.mの一方電極は、ともにノードN22に接続される。

【0040】

N型トランジスタ42.0〜42.mのゲート幅の和は、図4のN型トランジスタ23のゲート幅と同一に設定される。N型トランジスタ42.0のゲートおよびドレインは、ノードN22に接続される。N型トランジスタ42.1〜42.mのゲートおよびドレインは、それぞれヒューズ41.1〜41.mの他方電極に接続される。N型トランジスタ42.0〜42.mの各々は、ダイオード素子を構成する。

【0041】

P型トランジスタ43.0〜43.mのゲート幅の和は、図4のP型トランジスタ24のゲート幅と同一に設定される。P型トランジスタ43.0〜43.mは、それぞれN型トランジスタ42.0〜42.mのソースと接地電位GNDのノードとの間に接続され、それらのゲートはともに入力電位VIを受ける。

【0042】

実施の形態1で説明したとおり、ノードN22の電位V22はほとんどトランジスタ42.0〜42.m,43.0〜43.mのしきい値電圧で決まる。しかし、抵抗素子22の抵抗値に対してノードN22と接地電位GNDのノードとの間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに上昇する。したがって、レーザ光線によってヒューズ41.1〜41.mのうちの適切な数のヒューズを切断することにより、ノードN22の電位V22をわずかに上昇させることができ、トランジスタ42.0〜42.m,43.0〜43.mのしきい値電圧の絶対値が設計値よりも小さい場合でもノードN22の電位V22を補正することができる。

【0043】

なお、この実施の形態2では、N型トランジスタ23およびP型トランジスタ24の両方をm+1個に分割したが、N型トランジスタ23およびP型トランジスタ24の一方のみをm+1個に分割してもよいし、N型トランジスタ23およびP型トランジスタ24のうちの一方をm+1個に分割し他方をたとえば2個に分割してもよい。具体的には、図10のP型トランジスタ43.1〜43.mのソースを短絡してP型トランジスタ43.1〜43.mを1つのP型トランジスタにしてもよい。また、ヒューズ41.1〜41.mをそれぞれN型トランジスタ42.1〜42.mのソースとP型トランジスタ43.1〜43.mのソースとの間に接続するとともに、N型トランジスタ42.1〜42.mのソースを短絡してN型トランジスタ42.1〜42.mを1つのN型トランジスタにしてもよい。

【0044】

[実施の形態3]

図11は、この発明の実施の形態3による駆動回路のレベルシフト回路45の構成を示す回路図であって、図4のレベルシフト回路25と対比される図である。図11を参照して、このレベルシフト回路45が図4のレベルシフト回路25と異なる点は、N型トランジスタ26およびP型トランジスタ27がヒューズ46.1〜46.m、N型トランジスタ47.0〜47.mおよびP型トランジスタ48.0〜48.mで置換されている点である。

【0045】

ヒューズ46.1〜46.mの各々は、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ46.1〜46.mの一方電極は、ともに第4電源電位V4のノードに接続される。

【0046】

N型トランジスタ47.0〜47.mのゲート幅の和は、図4のN型トランジスタ26のゲート幅と同一に設定される。N型トランジスタ47.0のドレインは第4電源電圧V4のノードに接続され、そのゲートは入力電位VIを受ける。N型トランジスタ47.1〜47.mのドレインはそれぞれヒューズ46.1〜46.mの他方電極に接続され、そのゲートはともに入力電位VIを受ける。

【0047】

P型トランジスタ48.0〜48.mのゲート幅の和は、図4のP型トランジスタ27のゲート幅と同一に設定される。P型トランジスタ48.0〜48.mはそれぞれN型トランジスタ47.0〜47.mのソースとノードN27との間に接続され、それらのゲートはともにノードN27に接続される。P型トランジスタ48.0〜48.mの各々は、ダイオード素子を構成する。

【0048】

実施の形態1で説明したとおり、ノードN27の電位V27はほとんどトランジスタ47.0〜47.m,48.0〜48.mのしきい値電圧で決まる。しかし、抵抗素子28の抵抗値に対して第4電源電位V4のノードとノードN27との間の抵抗値を大きくしていくと、それに応じてノードN27の電位V27がわずかに低下する。したがって、レーザ光線によってヒューズ46.1〜46.mのうちの適切な数のヒューズを切断することにより、ノードN27の電位V27をわずかに低下させることができ、トランジスタ47.0〜47.m,48.0〜48.mのしきい値電圧の絶対値が設計値よりも小さい場合でもノードN27の電位V27を補正することができる。

【0049】

なお、この実施の形態3では、N型トランジスタ26およびP型トランジスタ27の両方をm+1個に分割したが、N型トランジスタ26およびP型トランジスタ27の一方のみをm+1個に分割してもよいし、N型トランジスタ26およびP型トランジスタ27のうちの一方をm+1個に分割し他方をたとえば2個に分割してもよい。具体的には、図11のP型トランジスタ48.1〜48.mのソースを短絡してP型トランジスタ48.1〜48.mを1つのP型トランジスタにしてもよい。また、ヒューズ41.1〜41.mをそれぞれN型トランジスタ47.1〜47.mのソースとP型トランジスタ48.1〜48.mのソースとの間に接続するとともに、N型トランジスタ47.1〜47.mのソースを短絡してN型トランジスタ47.1〜47.mを1つのN型トランジスタにしてもよい。

【0050】

また、実施の形態2と3を組合せ、図4のレベルシフト回路21,25をそれぞれレベルシフト回路40,45で置換してもよいことはいうまでもない。

【0051】

[実施の形態4]

図12は、この発明の実施の形態4による駆動回路のレベルシフト回路50の構成を示す回路図であって、図4のレベルシフト回路21と対比される図である。図12を参照して、このレベルシフト回路50が図4のレベルシフト回路21と異なる点は、抵抗素子22が抵抗素子51.0〜51.i(ただし、iは自然数である)およびヒューズ52.1〜52.iで置換されている点である。

【0052】

抵抗素子51.0〜51.iの抵抗値の和は、図4の抵抗素子22の抵抗値とほぼ同一に設定されている。抵抗素子51.0〜51.iは、第3電源電位V3のノードとノードN22との間に直列接続される。

【0053】

ヒューズ52.1〜52.iは、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ52.1〜52.iは、それぞれ抵抗素子51.1〜51.iに並列接続される。

【0054】

実施の形態1で説明したとおり、ノードN22の電位V22はほとんどトランジスタ23,24のしきい値電圧で決まる。しかし、トランジスタ23,24の導通抵抗値に対して第3電源電位V3のノードとノードN22との間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに低下する。したがって、レーザ光線によってヒューズ52.1〜52.iのうちの適切な数のヒューズを切断することにより、ノードN22の電位V22をわずかに低下させることができ、トランジスタ23,24のしきい値電圧の絶対値が設計値より高い場合でもノードN22の電位V22を補正することができる。

【0055】

[実施の形態5]

図13は、この発明の実施の形態5による駆動回路のレベルシフト回路55の構成を示す回路図であって、図4のレベルシフト回路25と対比される図である。図13を参照して、このレベルシフト回路55が図4のレベルシフト回路25と異なる点は、抵抗素子28が抵抗素子56.0〜56.iおよびヒューズ57.1〜57.iで置換されている点である。

【0056】

抵抗素子56.0〜56.iの抵抗値の和は、図4の抵抗素子28の抵抗値とほぼ同一の設定されている。抵抗素子56.0〜56.iは、ノードN27と第5電源電位V5のノードとの間に直列接続される。

【0057】

ヒューズ57.1〜57.iは、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ57.1〜57.iは、それぞれ抵抗素子56.1〜56.iに並列接続される。

【0058】

実施の形態1で説明したとおり、ノードN27の電位V27はほとんどトランジスタ26,27のしきい値電圧で決まる。しかし、トランジスタ26,27の導通抵抗値に対してノードN27と第5電源電位V5のノードとの間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに上昇する。したがって、レーザ光線によってヒューズ57.1〜57.iのうちの適切な数のヒューズを切断することにより、ノードN27の電位V27をわずかに上昇させることができ、トランジスタ26,27のしきい値電圧の絶対値が設計値よりも高い場合でもノードN22の電位V22を補正することができる。

【0059】

また、実施の形態4と5を組合せ、図4のレベルシフト回路21,25をそれぞれレベルシフト回路50,55で置換してもよいことはいうまでもない。

【0060】

また、以上の実施の形態1〜5において、電界効果トランジスタはMOSトランジスタでもよいし、TFT(薄膜トランジスタ)でもよい。また、抵抗素子は、高融点金属で形成してもよいし、不純物拡散層で形成してもよいし、占有面積低減化のために電界効果トランジスタで形成してもよい。また、以上の駆動回路は、液晶表示装置およびそれ以外の装置において、階調電位を伝達するだけでなく、入力されたアナログ電位と同電位になるように出力ノードの電位を制御するアナログバッファとして使用可能であることはいうまでもない。

【0061】

[実施の形態6]

駆動回路の特性としては、図14の特性線Aのように、入力電位VIと出力電位VOが等しくなることが理想的である。しかし、実施の形態1〜5で示した駆動回路の特性は、図14の特性線Bのようになり、VOの理想値と実際値の差ΔVはVIの増大に従って増大する。

【0062】

この理由は、以下のとおりである。図15に示すレベルシフト回路21′では、抵抗素子22の抵抗値をR、抵抗素子22およびP型トランジスタ24に流れる電流の値をi、P型トランジスタ24の電流増幅率をβとすると、次式(9)(10)が成り立つ。

V22=VDD−Ri …(9)

i=(VI−VTP−V22)2β/2 …(10)

ここで、Rβ/2=Kとすると、V22は次式(11)で表わされる。

【0063】

【数1】

【0064】

この式(11)より、VIの増大に従って、V22の理想値VI−VTPと実際の値との差が増大することがわかる。このため、V4の理想値は実際の値との差ΔVもVIの増大に従って大きくなる。

【0065】

この問題点を解消するため、この実施の形態6では、図16に示すように、抵抗素子22が定電流源62で置換される。図16のレベルシフト回路では、次式(12)が成り立つ。

i=(VI−VTB−V22)2β/2 …(12)

この式(12)より次式(13)が導かれる。

【0066】

【数2】

【0067】

したがって、図16のレベルシフト回路では、V22の理想値VI−VTPと実際値の差はVIに関係なく一定になる。また、βの値を定電流値iよりも十分に大きくすることにより、VOを理想値VI−VTPに略等しくすることができる。以下、この実施の形態6の駆動回路60について具体的に説明する。

【0068】

図17は、この発明の実施の形態6による駆動回路60の構成を示す回路図である。図17を参照して、この駆動回路60が図4の駆動回路20と異なる点は、レベルシフト回路21,25がそれぞれレベルシフト回路61,63で置換されている点である。レベルシフト回路61はレベルシフト回路21の抵抗素子22を定電流源62で置換し、レベルシフト回路63はレベルシフト回路25の抵抗素子28を定電流源64で置換したものである。

【0069】

定電流源62は、図18に示すように、P型トランジスタ65,66および抵抗素子67を含む。P型トランジスタ65は第3電源電圧V3のラインとノードN22との間に接続され、P型トランジスタ66および抵抗素子67は第3電源電位3のラインと接地電位GNDのラインとの間に直列接続される。P型トランジスタ65,66のゲートは、ともにP型トランジスタ66のドレインに接続される。P型トランジスタ65,66は、カレントミラー回路を構成する。P型トランジスタ66および抵抗素子67には抵抗素子67の抵抗値に応じた値の定電流が流れ、P型トランジスタ65にはP型トランジスタ66に流れる定電流の値に応じた値の定電流が流れる。なお、抵抗素子67の一方電極は接地電位GNDのラインに接続されているが、第3電源電位V3からP型トランジスタ66のしきい値電圧の絶対値|VTP|を減算した電位よりも低い他の電源電位のラインに抵抗素子67の一方電極を接続してもよい。また、定電流源としてトランジスタ65,66および抵抗素子67の代りに、ゲートとソースを互いに接続したデプレッション型のトランジスタを第3電源電位V3のラインとノードN22との間に設けてもよい。

【0070】

また定電流源64は、抵抗素子68およびN型トランジスタ69,70を含む。抵抗素子68およびN型トランジスタ69は第4電源電位V4のラインと第5電源電位V5のラインとの間に直列接続され、N型トランジスタ70はノードN27と第5電源電位V5のラインとの間に接続される。N型トランジスタ69,74のゲートは、ともにN型トランジスタ69のドレインに接続される。N型トランジスタ69,70は、カレントミラー回路を構成する。抵抗素子68およびN型トランジスタ69には抵抗素子68の抵抗値に応じた値の定電流が流れ、N型トランジスタ70にはN型トランジスタ69に流れる定電流の値に応じた値の定電流が流れる。なお、抵抗素子68の一方電極は第4電源電位V4に接続されているが、第5電源電位V5にN型トランジスタ69のしきい値電圧VTNを加算した電位よりも高い他の電源電位のラインに抵抗素子68の一方電極を接続してもよい。また、定電流源としてトランジスタ69,70および抵抗素子68の代りに、ゲートとソースを互いに接続したデプレッション型のトランジスタを第5電源電位V5のラインとノードN27との間に設けてもよい。他の構成および動作は、図4の駆動回路20と同じであるので、その説明は繰返さない。

【0071】

この実施の形態6では、図4の駆動回路20の抵抗素子22,28をそれぞれ定電流源62,64で置換したので入力電位VIの値に関係なく、入力電位VIに等しい出力電位VOを得ることができる。

【0072】

以下、この実施の形態6の種々の変更例について説明する。図19の駆動回路71は、図18の駆動回路60からキャパシタ29を除去したものである。この変更例は、負荷容量36の容量値が比較的小さい場合に有効となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0073】

図20の駆動回路72は、図18の駆動回路60からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、回路の占有面積を小さくすることができる。ただし、出力電位VOは、VO=VI+|VTP|−VTNとなる。

【0074】

図21の駆動回路73は、図20の駆動回路72からキャパシタ29を除去したものである。この変更例は、負荷容量36の容量値が比較的小さい場合に有効となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0075】

[実施の形態7]

たとえば図4の駆動回路20において、負荷容量36を充放電する際、トランジスタ31,32,34,35の各々はいわゆるソースフォロア動作を行なう。その際、出力電位VOが入力電位VIに近づくにつれてトランジスタ31,32,34,35の各々のゲート−ソース間電圧が小さくなり、トランジスタ31,32,34,35の電流駆動能力が低下する。トランジスタ32,34についてはそれらのゲート電極幅を広くすることによって駆動能力の低下を防ぐことが可能になるが、トランジスタ31,35のゲート電極幅を広くするとゲート容量が増大し、駆動回路20の動作速度が低下してしまう。この実施の形態7では、この問題の解決が図られる。

【0076】

図22は、この発明の実施の形態7による駆動回路75の構成を示す回路図である。図22を参照して、この駆動回路75は、図19の駆動回路71にキャパシタ76,77を追加したものである。キャパシタ76の一方電極は昇圧信号φBを受け、その他方電極はノードN22に接続される。キャパシタ77の一方電極は昇圧信号φBの相補信号/φBを受け、その他方電極はノードN27に接続される。

【0077】

図23は、図22に示した駆動回路75の動作を示すタイムチャートである。図23では、理解を容易にするため、ノードN22,N27の電位V22,V27および出力電位VOの遷移時間が実際よりも長く示されている。時刻t1において、入力電位VIが「L」レベルVLから「H」レベルVHに立上げられると、電位V22,V27,VOの各々が徐々に上昇する。上述のとおり、電位V22,V27,VOの各々は、電位変化の周期は比較的速く立上がるが、最終レベルに近づくにつれて上昇速度が遅くなる。

【0078】

時刻t1から所定時間経過後の時刻t2において、昇圧信号φBが「H」レベルに立上げられるとともに信号/φBが「L」レベルに立下げられる。信号φBが「H」レベルに立上げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ上昇する。信号/φBが「L」レベルに立下げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電位ΔV2だけ低下する。このとき、出力ノードN30に「H」レベルVHを出力する動作を行なっており、N型トランジスタ31の導通抵抗値の方がP型トランジスタ35の導通抵抗値よりも低くなっているので、V22によるレベル上昇作用の方がV27によるレベル降下作用よりも強く働き、出力電位VOは時刻t2から急速に上昇する(V22を昇圧しない場合は破線で示すようになる)。

【0079】

昇圧された電位V22は、ノードN22からトランジスタ23,24を介して接地電位GNDのラインに電流が流出することにより、VI+|VTP|+VTNまで低下する。また降圧された電位V27は、第4電源電圧V4のラインからトランジスタ26,27を介してノードN27に電流が流入することにより、VI−|VTP|−VTNまで上昇する。

【0080】

時刻t3において、昇圧信号φBが「L」レベルに立下げられるとともに信号/φBが「H」レベルに立上げられる。信号φBが「L」レベルに立下げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ低下する。また信号/φBが「H」レベルに立上げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電圧ΔV2だけ上昇する。V22がΔV1だけ低下してもプルアップ回路30には出力電位VOを低下させる能力がなく、V27がΔV2だけ上昇してもプルダウン回路33には出力電位VOを上昇させる能力がないので、出力電位VOは変化しない。

【0081】

降圧された電位V22は、第3電源電位V3のラインからP型トランジスタ65を介してノードN22に電流が流入することにより、VI+|VTP|+VTNまで上昇する。ただし、低消費電力化のためP型トランジスタ65の電流駆動能力が小さく設定されているので、ノードN22の電位V22が本来のレベルVI+|VTP|+VTNに上昇するのに必要な時間は、V22がそのレベルVI+|VTP|+VTNに低下するのに必要な時間よりも長くなる。

【0082】

また昇圧された電位V27は、ノードN27からN型トランジスタ70を介して第5電源電位V5のラインに電流が流出することにより、VI−VTN−|VTP|まで低下する。ただし、低消費電力化のためN型トランジスタの電流駆動能力は小さく設定されているので、ノードN27の電位V27が本来のレベルVI−VTN−|VTP|に低下するのに必要な時間は、V22がそのレベルVI−VTN−|VTP|に上昇するのに必要な時間よりも長くなる。

【0083】

次に時刻t4において、入力電位VIが「H」レベルVHから「L」レベルVLに立下げられると、電位V22,V27,V4の各々が徐々に低下する。電位V22,V27,V4の各々は、電位変化の初期は比較的速く立下がるが、最終レベルに近づくにつれて下降速度が遅くなる。

【0084】

時刻t4から所定時間経過後の時刻t5において、昇圧信号φBが「H」レベルに立上げられるとともに信号/φBが「L」レベルに立下げられる。信号φBが「H」レベルに立上げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ上昇する。信号/φBが「L」レベルに立下げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電位ΔV2だけ低下する。このとき、出力ノードN30に「L」レベルVLを出力する動作を行なっており、P型トランジスタ35の導通抵抗値の方がN型トランジスタ31の導通抵抗値よりも低くなっているので、V27によるレベル下降作用の方がV22によるレベル上昇作用よりも強く働き、出力電位VOは時刻t5から急速に低下する(V27を降圧しない場合は破線で示すようになる)。

【0085】

昇圧された電位V22は、ノードN22からトランジスタ23,24を介して接地電位GNDのラインに電流が流出することにより、VI+|VTP|+VTNまで低下する。また降圧された電位V27は、第4電源電圧V4のラインからトランジスタ26,27を介してノードN27に電流が流入することにより、VI−|VTP|−VTNまで上昇する。

【0086】

時刻t6において、昇圧信号φBが「L」レベルに立下げられるとともに信号/φBが「H」レベルに立上げられる。信号φBが「L」レベルに立下げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ低下する。また信号/φBが「H」レベルに立上げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電圧ΔV2だけ上昇する。ΔV1が低下してもプルアップ回路30には出力電位VOを低下させる能力がなく、ΔV2が上昇してもプルダウン回路33には出力電位VOを上昇させる能力がないので、出力電位VOは変化しない。

【0087】

降圧された電位V22は、第3電源電位V3のラインからP型トランジスタ65を介してノードN22に電流が流入することにより、VI+|VTP|+VTNまで上昇する。ただし、低消費電力化のためP型トランジスタ65の電流駆動能力は小さく設定されているので、ノードN22の電位V22が本来のレベルVI+|VTP|+VTNに上昇するのに必要な時間は、V22がそのレベルVI+|VTP|+VTNに低下するのに必要な時間よりも長くなる。

【0088】

また昇圧された電位V27は、ノードN27からN型トランジスタ70を介して第5電源電位VOのラインに電流が流出することにより、VI−VTN−|VTP|まで低下する。ただし、低消費電力化のためN型トランジスタ70の電流駆動能力は小さく設定されているので、ノードN27の電位V27が本来のレベルVI−VTN−|VTP|に低下するのに必要な時間は、V22がそのレベルVI−VTN−|VTP|に上昇するのに必要な時間よりも長くなる。

【0089】

この実施の形態7では、入力電位VIが「L」レベルVLから「H」レベルVHに立上げられたことに応じてノードN22の電位V22を本来到達すべき電位VI+|VTP|+VTNよりも高い電位に昇圧するので、出力電位VOの上昇速度を速くすることができる。また、入力電位VIが「H」レベルVHから「L」レベルVLに立下げられたことに応じてノードN27の電位V27も本来到達すべき電位VI−|VTP|−VTNよりも低い電位に降圧するので、出力電位VOの下降速度を速くすることができる。したがって、駆動回路75の応答速度の高速化を図ることができる。

【0090】

図24は、この実施の形態7の変更例による駆動回路78の構成を示す回路図である。この駆動回路78は、図22の駆動回路75のトランジスタ23,27,32,34を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、出力電位VOはVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0091】

[実施の形態8]

図25は、この発明の実施の形態8による駆動回路80の構成を示す回路図である。図25を参照して、この駆動回路80は、図19の駆動回路71にP型トランジスタ81およびN型トランジスタ82を追加したものである。P型トランジスタ81は、第3電源電位V3のラインとノードN22との間に接続され、そのゲートはプルアップ信号/φPを受ける。N型トランジスタ82は、ノードN27と第5電源電位V5のラインとの間に接続され、そのゲートはプルアップ信号/φPの相補信号φPを受ける。

【0092】

信号φP,/φPは、実施の形態7で示した信号φB,/φBと同様のタイミングでレベル変化される。すなわち、入力信号VIが「L」レベルVLから「H」レベルVHに立上げられてから所定時間経過後に、信号/φP,φPがそれぞれパルス的に「L」レベルおよび「H」レベルにされて、P型トランジスタ81およびN型トランジスタ82がパルス的に導通する。これにより、ノードN22の電位V22は、第3電源電位V3をトランジスタ81とトランジスタ23,24とで分圧した電位に昇圧された後、所定値VI+|VTP|+VTNになる。また、ノードN27の電位V27は、第4電源電位V4と第5電源電位V5の間の電圧V4−V5をトランジスタ26,27とトランジスタ82とで分圧した電位に降圧された後、所定値VI−VTN−|VTP|になる。このとき、実施の形態7でも述べたように、N型トランジスタ31による充電作用の方がP型トランジスタ35による放電作用よりも強く働き、出力電位VOは急速に入力電位VIに等しくなる。入力電位VIが「H」レベルVHから「L」レベルVLに立下げられた場合は、P型トランジスタ35による放電作用の方がN型トランジスタ31による充電作用よりも強く働き、出力電位VOは急速に入力電位VIに等しくなる。

【0093】

この実施の形態8でも、実施の形態7と同じ効果が得られる。

以下、この実施の形態8の種々の変更例について説明する。図26の駆動回路83は、図25の駆動回路80からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、出力電位VOはVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0094】

図27の駆動回路85は、図25の駆動回路80にN型トランジスタ86およびP型トランジスタ87を追加したものである。N型トランジスタ86は、P型トランジスタ24のソースと接地電位GNDのラインとの間に接続され、そのゲートはプルアップ信号/φPを受ける。P型トランジスタ87は、第4電源電位V4のラインとN型トランジスタ26のドレインとの間に接続され、そのゲートはプルアップ信号/φPの相補信号φPを受ける。この変更例では、P型トランジスタ81の導通時にN型トランジスタ86が非導通になるので、第3電源電位V3のラインからトランジスタ81,23,24,86を介して接地電位GNDのラインに貫通電流が流れるのを防止することができる。また、N型トランジスタ82の導通時にP型トランジスタ87が非導通になるので、第4電源電位V4のラインからトランジスタ87,26,27,82を介して第5電源電位V5のラインに貫通電流が流れるのを防止することができる。したがって、回路61,63の消費電流が小さくてすむ。

【0095】

図28の駆動回路88は、図27の駆動回路85からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。その変更例では、トランジスタ23,27,32,34を除去したので、出力電位VOがVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0096】

図29の駆動回路90は、図25の駆動回路80のP型トランジスタ24のソースに接地電位GNDの代わりに信号φPを与えるとともにN型トランジスタのドレインに第4電源電位VOの代わりに信号/φPを与えたものである。この変更例では、P型トランジスタ81の導通時にP型トランジスタ24のドレインを「H」レベルにするので、トランジスタ81,23,24に貫通電流が流れるのを防止することができる。また、N型トランジスタ82の導通時にN型トランジスタ26のドレインを「L」レベルにするので、トランジスタ26,27,82に貫通電流が流れるのを防止することができる。したがって、回路61,63の消費電流の低減化を図ることができる。

【0097】

図30の駆動回路91は、図29の駆動回路90からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、出力電位VOはVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0098】

[実施の形態9]

図31は、この発明の実施の形態9による駆動回路95の構成を示す回路図である。図31を参照して、この駆動回路95が図22の駆動回路75と異なる点は、レベルシフト回路61,63がそれぞれレベルシフト回路96,102で置換されている点である。

【0099】

レベルシフト回路96は、レベルシフト回路61にP型トランジスタ97,98およびN型トランジスタ99〜101を追加したものである。P型トランジスタ97は、N型トランジスタ99,100およびP型トランジスタ98は第3電源電位V3のラインと接地電位GNDのラインとの間に直列接続され、N型トランジスタ101は第3電源電位V3のラインとノードN22との間に接続される。P型トランジスタ97のゲートは、P型トランジスタ66のゲートに接続される。したがって、トランジスタ97,99,100,98には、P型トランジスタ66に流れる定電流の値に応じた値の定電流が流れる。N型トランジスタ99,100のゲートは、それぞれそれらのドレインに接続される。N型トランジスタ99,100の各々はダイオードを構成する。P型トランジスタ98のゲートは、入力電位VIを受ける。トランジスタ97,99の間のノードの電位V99は、V99=VI+|VTP|+2VTNとなる。V99は、N型トランジスタ101のゲートに与えられる。N型トランジスタ101は、ノードN22をV99−VTN=VI+|VTP|+VTNに充電する。

【0100】

レベルシフト回路102は、レベルシフト回路63にN型トランジスタ103,104およびP型トランジスタ105〜107を追加したものである。N型トランジスタ103、P型トランジスタ105,106およびN型トランジスタ104は、第4電源電位V4のラインと第5電源電位V5のラインとの間に直列接続され、P型トランジスタ107はノードN27と第5電源電位V5のラインとの間に接続される。N型トランジスタ103のゲートは、入力電位VIを受ける。P型トランジスタ105,106のゲートは、それぞれそれらのドレインに接続される。P型トランジスタ105,106の各々は、ダイオードを構成する。N型トランジスタ104のゲートは、N型トランジスタ69のゲートに接続される。N型トランジスタ104には、N型トランジスタ69に流れる定電流の値に応じた値の定電流が流れる。MOSトランジスタ106と104の間のノードの電位V106は、V106=VI−VTN−2|VTP|となる。V106は、P型トランジスタ107のゲートに与えられる。P型トランジスタ107は、ノードN27をV106−|VTP|=VI−VTN−|VTP|に放電する。他の構成および動作は、図22の駆動回路75と同じであるので、その説明は繰返さない。

【0101】

図32は、図31に示した駆動回路95の動作を示すタイムチャートであって、図23と対比される図である。図32を参照して、この駆動回路95では、トランジスタ97〜101によってノードN22をVI+|VTP|+VTNに充電するので、ノードN22の電位V22が所定値VI+|VTP|+VTNよりも低下したとき(時刻t3,t6)、ノードN22の電位V22を急速に所定値VI+|VTP|+VTNに戻すことができる。また、トランジスタ103〜107によってノードN27をVI−VTN−|VTP|に放電するので、ノードN27の電位V27が所定値VI−VTN−|VTP|よりも上昇したとき(時刻t3,t6)、ノードN27の電位V27を急速に所定値VI−VTN−|VTP|に戻すことができる。したがって、回路の応答速度の高速化を図ることができる。

【0102】

図33は、この実施の形態9の変更例を示す回路図である。この駆動回路108は、図31の駆動回路95からN型トランジスタ23,34,100およびP型トランジスタ27,32,105を除去したものである。この変更例では、トランジスタ23,27,32,34,100,105を除去したので、出力電位VOはVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0103】

[実施の形態10]

図34は、この発明の実施の形態10による駆動回路110の構成を示す回路図である。図34において、この駆動回路110が図31の駆動回路95と異なる点は、レベルシフト回路96,102がレベルシフト回路111,112で置換されている点である。

【0104】

レベルシフト回路111は、レベルシフト回路96からP型トランジスタ97,98およびN型トランジスタ100を除去し、N型トランジスタ99をP型トランジスタ65のソースとノードN22との間に接続したものである。N型トランジスタ99のゲートは、N型トランジスタ99のドレインおよびN型トランジスタ101のゲートに接続される。N型トランジスタ99,101のゲートの電位V99は、V99=VI+|VTP|+2VTNとなる。N型トランジスタ101は、ノードN22をV99−VTN=VO+|VTP|+VTNに充電する。

【0105】

レベルシフト回路112は、レベルシフト回路102からN型トランジスタ103,104およびP型トランジスタ105を除去し、P型トランジスタ106をノードN27とN型トランジスタ70のドレインとの間に接続したものである。P型トランジスタ106のゲートは、そのドレインおよびP型トランジスタ107のゲートに接続される。P型トランジスタ106,107のゲートの電位V106は、V106=VI−VTN−2|VTP|となる。P型トランジスタ107は、ノードN27をV106+|VTP|=VI−VTN−|VTP|に放電する。他の構成および動作は、図31の駆動回路95と同じであるので、その説明は繰返さない。

【0106】

この実施の形態10では、実施の形態9と同じ効果が得られる他、第3電源電位V3のラインからトランジスタ97,99,100,98を介して接地電位GNDのラインに流れる電流、および第4の電源電位VOのラインからトランジスタ103,105,106,104を介して第5電源電位V5のラインに流れる電流を削減できるので、消費電流が小さくてすむ。また、トランジスタ97,98,100,103〜105を除去したので、回路の占有面積が小さくてすむ。

【0107】

図35は、この実施の形態10の変更例を示す回路図である。この駆動回路113は、図34の駆動回路110からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、出力電位VOはVO=VI+|VTP|−VTNになるが、回路の占有面積が小さくてすむ。

【0108】

[実施の形態11]

図36は、この発明の実施の形態11による半導体集積回路装置の要部を示す回路ブロック図である。図36において、この半導体集積回路装置は、j個(ただし、jは2以上の整数である)の駆動回路115.1〜115.jを備える。

【0109】

駆動回路115.1は、図37に示すように、図18の駆動回路60のレベルシフト回路61,63をそれぞれレベルシフト回路116,117で置換したものである。レベルシフト回路116はレベルシフト回路61からP型トランジスタ66および抵抗素子67を除去したものであり、レベルシフト回路117はレベルシフト回路63から抵抗素子68およびN型トランジスタ69を除去したものである。トランジスタ65,70のゲートは、それぞれバイアス電位VBP,VBNを受ける。他の駆動回路115.2〜115.jの各々も駆動回路115.1と同じ構成である。

【0110】

図36に戻って、この半導体集積回路装置では、バイアス電位VBPを生成するためのP型トランジスタ66および抵抗素子67とバイアス電位VBNを生成するための抵抗素子68およびN型トランジスタ69とが駆動回路115.1〜115.jに共通に設けられる。

【0111】

P型トランジスタ66および抵抗素子67は第3電源電位V3のラインと接地電位GNDのラインとの間に直列接続され、P型トランジスタ66のゲートはそのドレイン(ノードN66)に接続される。ノードN66には、バイアス電位VBPが現れる。ノードN66と接地電位GNDのラインとの間には、バイアス電位VBPを安定化させるためのキャパシタ118が接続される。駆動回路115.1〜115.jの各々のP型トランジスタ65には、P型トランジスタ66に流れる定電流に応じた値の定電流が流れる。

【0112】

抵抗素子68およびN型トランジスタ69は第4電源電位V4のラインと第5電源電位V5のラインとの間に接続され、N型トランジスタ69のゲートはそのドレイン(ノードN68)に接続される。ノードN68には、バイアス電位VBNが現れる。ノードN68と接地電位GNDのラインとの間には、バイアス電位VBNを安定化させるためのキャパシタ119が接続される。駆動電位115.1〜115.jの各々のN型トランジスタ70は、N型トランジスタ69に流れる定電流に応じた値の定電流が流れる。

【0113】

この実施の形態11では、実施の形態6と同じ効果が得られる他、バイアス電位VBP,VBNを生成するための回路を駆動回路115.1〜115.jに共通に設けたので、駆動回路115.1〜115.j1つ当りの占有面積が小さくてすむ。

【0114】

[実施の形態12]

図38は、この発明の実施の形態12によるオフセット補償機能付駆動回路120の構成を示す回路ブロック図である。図38において、このオフセット補償機能付駆動回路120は、駆動回路121、キャパシタ122およびスイッチS1〜S4を含む。駆動回路121は、実施の形態1〜11で示した駆動回路のうちのいずれかの駆動回路である。キャパシタ122およびスイッチS1〜S4は、駆動回路121のトランジスタのしきい値電圧のばらつきなどにより駆動回路121の入力電位と出力電位の間に電位差すなわちオフセット電圧VOFが生じた場合に、このオフセット電圧VOFを補償するためのオフセット補償回路を構成する。

【0115】

すなわち、スイッチS1は入力ノードN120と駆動回路121の入力ノードN20との間に接続され、スイッチS4は出力ノードN121と駆動回路121の出力ノードN30との間に接続される。キャパシタ122およびスイッチS2は、駆動回路121の入力ノードN20と出力ノードN30との間に直列接続される。スイッチS3は、入力ノードN120とキャパシタ122およびスイッチS2間のノードN122との間に接続される。スイッチS1〜S4の各々は、P型トランジスタでもよいし、N型トランジスタでもよいし、P型トランジスタおよびN型トランジスタを並列接続したものでもよい。スイッチS1〜S4の各々は、制御信号(図示せず)によってオン/オフ制御される。

【0116】

今、駆動回路121の出力電位が入力電位よりもオフセット電圧VOFだけ低い場合について説明する。図39に示すように、初期状態では、すべてのスイッチS1〜S4はオフ状態にされている。ある時刻t1においてスイッチS1,S2がオン状態にされると、駆動回路121の入力ノードN20の電位V20はV20=VIになり、駆動回路121の出力電位V30およびノードN122の電位V122はV30=V122=VI−VOFとなり、キャパシタ122はオフセット電圧VOFに充電される。

【0117】

次に時刻t2においてスイッチS1,S2がオフ状態にされると、オフセット電圧VOFはキャパシタ122に保持される。次いで時刻t3においてスイッチS3がオン状態にされると、ノードN122の電位V122はV122=VIになり、駆動回路121の入力電位V20はV20=VI+VOFとなる。この結果、駆動回路121の出力電位V30はV30=V20−VOF=VIとなり、駆動回路121のオフセット電圧VOFは打消されたことになる。次に時刻t4においてスイッチS4がオン状態にされると、出力電位VOがVO=VIとなり負荷に供給される。

【0118】

この実施の形態12では、駆動回路121のオフセット電圧VOFを打消すことができ、出力電位VOと入力電位VIを一致させることができる。

【0119】

なお、スイッチS4は必ずしも必要でない。ただし、スイッチS4を設けないと、負荷容量36の容量値が大きい場合は時刻t1においてスイッチS1,S2をオン状態にしてからキャパシタ122の端子間電圧VOFが安定するまでの時間が長くなる。

【0120】

[実施の形態13]

図40は、この発明の実施の形態13によるオフセット補償機能付駆動回路125の構成を示す回路ブロック図である。図40において、このオフセット補償機能付駆動回路125は、図17の駆動回路60にキャパシタ122a,122b,126a,126bおよびスイッチS1a〜S4a,S1b〜S4bを追加したものである。

【0121】

スイッチS1a,S1bは、それぞれ入力ノードN120とトランジスタ24,26のゲート(ノードN20a,N20b)との間に接続される。スイッチS4a,S4bは、それぞれ出力ノードN121とトランジスタ32,34のドレイン(ノードN30a,N30b)との間に接続される。キャパシタ122aおよびスイッチS2aは、ノードN20aとN30aの間に直列接続される。キャパシタ122bおよびスイッチS2bは、ノードN20bとN30bの間に直列接続される。スイッチS3aは、入力ノードN120とキャパシタ122aおよびスイッチS2a間のノードN122aとの間に接続される。スイッチ3bは、入力ノードN120とキャパシタ122bおよびスイッチS2b間のノードN122bとの間に接続される。キャパシタ126a,126bの一方電極はそれぞれノードN30a,N30bに接続され、それらの他方電極はそれぞれリセット信号/φRおよびその相補信号φRを受ける。

【0122】

図41は、図40に示したオフセット補償機能付駆動回路125の動作を示すタイムチャートである。定電流源62およびトランジスタ23,24,31,32からなる充電回路と、定電流源64およびトランジスタ26,27,34,35からなる放電回路とは、充電と放電の違いはあるが同様の動作をするので、図41では充電回路の動作のみについて説明する。今、N型トランジスタ31のしきい値電圧VTNがN型トランジスタのしきい値電圧VTNよりもVOFaだけ大きいために充電回路側にオフセット電圧VOFaがあり、放電回路側にオフセット電圧VOFbはないものとする。

【0123】

初期状態では、スイッチS1a〜S3aがオフ状態にされるとともにスイッチS4aがオン状態にされ、ノードN20a,N122a,N30a,N121には前回の電位VI′が保持されている。時刻t1においてスイッチS1a,S2aがオン状態にされると、ノードN20a,N122a,N30a,N121の電位V20a,V122a,V30a,VOはともに入力電位VIに等しい電位になる。また、ノードN22の電位V22は、V22=VI+|VTP|+VTNとなる。N型トランジスタ31のしきい値電圧VTN′がN型トランジスタ23のしきい値電圧VTNよりもVOFaだけ高いにもかかわらずV20a,V122a,V30a,VOがともにVIに等しい電位になるのは、出力ノードN121は放電回路によって入力電位VIまで放電されるが、それ以下には放電されないからである。

【0124】

次に、時刻t2においてスイッチS4aがオフ状態にされて、充電回路の出力ノードN30aと放電回路の出力ノードN30bとが電気的に切離される。次いで時刻t3においてリセット信号/φRが「H」レベルから「L」レベルに立下げられると、キャパシタ126aを介して容量結合により、ノードN30a,N122aの電位V30a,V122aが所定電圧だけ降圧される。これにより、トランジスタ31,32が導通してノードN30a,N122aの電位V30a,V122aがVI−VOFaまで上昇し、キャパシタ122aがVOFaに充電される。

【0125】

ノードN30a,N122aの電位V30a,V122aが安定した後、時刻t4においてスイッチS1a,S2aがオフ状態にされ、さらに時刻t5においてスイッチS3aがオン状態にされると、入力電位VIにオフセット電圧VOFaを加算した電位VI+VOFaがノードN20aに与えられる。これにより、ノードN22の電位V22はV22=VI+|VTP|+VTN+VOFaとなり、ノードN30a,N122aの電位V30a,V122aは入力電位VIと同じレベルになる。

【0126】

充電回路の出力電位V30aは時刻t1からV30a=VIになるが、時刻t1〜t2の期間は配線容量などによって保持された電位にすぎず、負極性のノイズがあった場合はV30aはVI−VOFまで低下してしまう。これに対して時刻t5以降は、負極性のノイズがあってもトランジスタ31,32によって充電されるので、V30aはVIに維持される。

【0127】

次に時刻t6においてスイッチS3aがオフ状態にされ、さらに時刻t7においてスイッチS4aがオン状態にされると、負荷容量36が駆動回路によって駆動される。時刻t8においてリセット信号/φRが「H」レベルに立上げられると、初期状態に戻る。この時刻t8では、出力インピーダンスが十分に低くなっているので、リセット信号/φRが「H」レベルに立上げられても出力電位VOはほとんど変化しない。放電回路側でも同様の動作が行なわれ、出力電位VOはVIに維持される。

【0128】

図42は、図40に示したオフセット補償機能付駆動回路125の動作を示す他のタイムチャートである。定電流源62およびトランジスタ23,24,31,32からなる充電回路と、定電流源64およびトランジスタ26,27,34,35からなる放電回路とは、充電と放電の違いはあるが同様の動作をするので、図42では放電回路の動作のみについて説明する。今、P型トランジスタ35のしきい値電圧の絶対値|VTP′|がP型トランジスタ27のしきい値電圧の絶対値|VTP|よりもVOFbだけ大きいために放電回路側にオフセット電圧VOFbがあり、充電回路側にはオフセット電圧VOFaはないものとする。

【0129】

初期状態では、スイッチS1b〜S3bがオフ状態にされるとともにスイッチS4bがオン状態にされ、ノードN20b,N122b,N30b,N121には前回の電位VI′が保持されている。時刻t1においてスイッチS1b,S2bがオン状態にされると、ノードN20b,N122b,N30b,N121の電位V20b,V122b,V30b,VOはともに入力電位VIに等しい電位になる。また、ノードN27の電位V27は、V27=VI−|VTP|−VTNとなる。P型トランジスタ35のしきい値電圧の絶対値|VTP′|がV型トランジスタ27のしきい値電圧の絶対値|VTP|よりもVOFbだけ高いにもかかわらずV20b,V122b,V30b,VOはともにVIに等しい電位になるのは、出力ノードN121が充電回路によって入力電位VIまで充電されるが、それ以上には充電されないからである。

【0130】

次に、時刻t2においてスイッチS4bがオフ状態にされて、充電回路の出力ノードN30aと放電回路の出力ノードN30bとが電気的に切離される。次いで時刻t3において信号φRが「L」レベルから「H」レベルに立上げられると、キャパシタ126bを介して容量結合により、ノードN30b,N122bの電位V30b,V122bが所定電圧だけ昇圧される。これにより、トランジスタ34,35が導通してノードN30b,N122bの電位V30b,V122bがVI+VOFbまで低下し、キャパシタ122bがVOFbに充電される。

【0131】

ノードN30b,N122bの電位V30b,V122bが安定した後、時刻t4においてスイッチS1b,S2bがオフ状態にされ、さらに時刻t5においてスイッチS3bがオン状態にされると、入力電位VIからオフセット電圧VOFbを減算した電位VI−VOFがノードN20bに与えられる。これにより、ノードN27の電位V27がV27=VI−VTN−|VTP|−VOFbとなり、ノードN30b,V122bの電位V30b,V122bは入力電位VIと同レベルになる。

【0132】

放電回路の出力電位V30bは時刻t1からV30b=VIになるが、時刻t1〜t2の期間は配線容量などによって保持された電位にすぎず、正極性のノイズがあった場合はV30bはVI+VOFbまで上昇してしまう。これに対して時刻t5以降は、正極性のノイズがあってもトランジスタ34,35によって放電されるので、V30bはVIに維持される。

【0133】

次に時刻t6においてスイッチS3bがオフ状態にされ、さらに時刻t7においてスイッチS4bがオン状態にされると、負荷容量36が駆動回路によって駆動される。時刻t8において信号φRが「L」レベルに立下げられると、初期状態に戻る。この時刻t8では、出力インピーダンスが低くなっているので、信号φRが「L」レベルに立上げられても出力電位Vはほとんど変化しない。放電回路側でも同様の動作が行なわれ、出力電位VOはVIに維持される。

【0134】

以下、この実施の形態13の種々の変更例について説明する。図43のオフセット補償機能付駆動回路127は、図40のオフセット補償機能付駆動回路125からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、回路の占有面積が小さくてすむ。

【0135】

図44のオフセット補償機能付駆動回路130は、図40のオフセット補償機能付駆動回路125のキャパシタ126a,126bをそれぞれN型トランジスタ131aおよびP型トランジスタ131bで置換したものである。N型トランジスタ131aは、第8電源電位V8のラインとノードN30aとの間に接続され、そのゲートはリセット信号φR′を受ける。P型トランジスタ131bは、ノードN30bと第9電源電位V9のラインとの間に接続され、そのゲートはリセット信号φR′の相補信号/φR′を受ける。

【0136】

通常時は信号φR′,/φR′がそれぞれ「L」レベルおよび「H」レベルにされており、N型トランジスタ131aおよびP型トランジスタ131bはともに非導通にされている。図41および図42の時刻t3において、信号φR′が所定時間だけパルス的に「H」レベルにされるとともに信号/φR′が所定時間だけパルス的に「L」レベルにされる。これにより、N型トランジスタ131aがパルス的に導通してノードN30aの電位V30aが第8電源電位V8に低下されるとともに、P型トランジスタ131bがパルス的に導通してノードN30bの電位V30bが第9電源電位V9に上昇される。この後、図41で説明した場合ではノードN30aがVI−VOFに充電され、図42で説明した場合ではノードN30bがVO+VOFに放電される。この変更例では、図41および図42の時刻t8においても、出力電位VOにノイズが発生することはない。なお、信号φR′,/φR′のパルス幅は必要最小限の値に設定される。

【0137】

図45のオフセット補償機能付駆動回路132は、図25の駆動回路80にキャパシタ122a,122b,126a,126bおよびスイッチS1a〜S4a,S1b〜S4bからなるオフセット補償回路を付加したものである。図41および図42の時刻t1〜t2の期間において信号/φPはパルス的に「L」レベルにされるとともに信号φPがパルス的に「H」レベルにされる。この変更例では、ノードN22,N27の電位V22,V27が所定値に迅速に到達するので、動作速度の高速化を図ることができる。

【0138】

図46のオフセット補償機能付駆動回路133は、図45のオフセット補償機能付駆動回路132からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、回路の占有面積が小さくてすむ。

【0139】

図47のオフセット補償機能付駆動回路135は、図27のオフセット補償機能付駆動回路85にキャパシタ122a,122b,126a,126bおよびスイッチS1a〜S4a,S1b〜S4bからなるオフセット補償回路を付加したものである。この変更例では、信号/φP,φPがそれぞれ「L」レベルおよび「H」レベルになってトランジスタ81,82が導通したときに、同時にトランジスタ86,87が非導通になるので、貫通電流が流れるのを防止することができ、消費電流が小さくてすむ。

【0140】

図48のオフセット補償機能付駆動回路136は、図47のオフセット補償機能付駆動回路135からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、回路の占有面積は小さくてすむ。

【0141】

図49のオフセット補償機能付駆動回路140は、図29の駆動回路90にキャパシタ122a,122b,126a,126bおよびスイッチS1〜S4a,S1b〜S4bからなるオフセット補償回路を付加したものである。この変更例では、信号/φPが「L」レベルにされてP型トランジスタ81が導通したときにP型トランジスタ24のドレインが「H」レベルにされ、信号φPが「H」レベルにされてN型トランジスタ82が導通したときにN型トランジスタ26のドレインが「L」レベルにされるので、貫通電流が流れることを防止することができ、消費電力が小さくてすむ。

【0142】

図50のオフセット補償機能付駆動回路141は、図49のオフセット補償機能付駆動回路140からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、回路の占有面積が小さくてすむ。

【0143】

図51のオフセット補償機能付駆動回路145は、図31のオフセット補償機能付駆動回路95にキャパシタ122a,122b,126a,126bおよびスイッチS1a〜S4a,S1b〜S4bからなるオフセット補償回路を付加したものである。図41および図42の時刻t1〜t2の期間において信号φBがパルス的に「H」レベルにされるとともに信号/φBがパルス的に「L」レベルにされる。この変更例では、ノードN22,N27の電位V22,V27が所定値に迅速に到達するので、動作速度の高速化を図ることができる。

【0144】

図52のオフセット補償機能付駆動回路146は、図51のオフセット補償機能付駆動回路145からN型トランジスタ23,34,100およびP型トランジスタ27,32,105を除去したものである。この変更例では、回路の占有面積が小さくてすむ。

【0145】

図53のオフセット補償機能付駆動回路150は、図34の駆動回路110にキャパシタ122a,122b,126a,126bおよびスイッチS1〜S4a,S1b〜S4bからなるオフセット補償回路を付加したものである。図41および図42の時刻t1〜t2の期間において信号φBがパルス的に「H」レベルにされるとともに信号/φBがパルス的に「L」レベルにされる。この変更例では、ノードN22,N27の電位V22,V27が所定値に迅速に到達するので、動作速度の高速化を図ることができる。

【0146】

図54のオフセット補償機能付駆動回路151は、図53のオフセット補償機能付駆動回路150からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、回路の占有面積が小さくてすむ。

【0147】

[実施の形態14]

図55は、この発明の実施の形態14によるオフセット補償機能付駆動回路155の構成を示す回路図である。図55において、このオフセット補償機能付駆動回路155が図51のオフセット補償機能付駆動回路145と異なる点は、スイッチS5およびキャパシタ156が追加されている点と、昇圧信号φB,/φBがそれぞれ昇圧信号φB1,/φB1で置換されている点である。

【0148】

スイッチS5は、スイッチS4a,S4b間のノードと出力ノードN121との間に接続される。キャパシタ156は、スイッチS4a,S4b間のノードと接地電位GNDのラインとの間に接続される。キャパシタ156の容量値は、負荷容量36の容量値よりも小さく設定されている。

【0149】

図56は、図55に示したオフセット補償機能付駆動回路155の動作を示すタイムチャートであって、図41と対比される図である。ここでも充電回路側の動作のみについて説明する。図56を参照して、時刻t9まではスイッチS5がオフ状態にされており、負荷容量36が電気的に切離されているので、たとえば時刻t1〜t2において電位V22,V30a,V122aが迅速に入力電位VIに到達する。

【0150】

時刻t9においてスイッチS5がオン状態にされると、出力ノードN121に接続されたデータ線の電位VOに応じてスイッチS4a,S4b間の電位V156が変化する。図56では、データ線の電位VOがV156よりも低かった場合が示されており、時刻t9において電位V156が低下した後、トランジスタ31,32によって電流が供給されて電位V156が徐々に上昇する。次いで時刻t10において信号φB1が「L」レベルから「H」レベルに立上げられてノードN22の電位V22がパルス的に上昇し、N型トランジスタ31を流れる電流が増加して電位V156=VOが急速に入力電位VIに到達する。

【0151】

図57は、図55に示したオフセット補償機能付駆動回路155の動作を示す他のタイムチャートであって、図42と対比される図である。ここでも、放電回路側の動作のみについて説明する。図57を参照して、時刻t9まではスイッチS5がオフ状態にされており、負荷容量36が電気的に切離されているので、たとえば時刻t1〜t2において電位V27,V30b,V122bが迅速に入力電位VIに到達する。

【0152】

時刻t9においてスイッチS5がオン状態にされると、出力ノードN121に接続されたデータ線の電位VOに応じてスイッチS4a,S4b間の電位V156が変化する。図57では、データ線の電位VOがV156よりも高かった場合が示されており、時刻t9において電位V156が上昇した後、トランジスタ34,35によって電流が排出されて電位V156が徐々に低下する。

【0153】

次いで時刻t10において信号/φB1が「H」レベルから「L」レベルに立下げられてノードN27の電位V27がパルス的に低下し、P型トランジスタ35に流れる電流が増加して電位V156=VOは急速に入力電位VIに到達する。

【0154】

この実施の形態14では、負荷容量36の容量値が大きい場合でも、速い動作速度を得ることができる。

【0155】

[実施の形態15]

図58は、この発明の実施の形態15によるオフセット補償機能付駆動回路157の構成を示す回路図である。図58を参照して、このオフセット補償機能付駆動回路157が図55のオフセット補償機能付駆動回路155と異なる点は、キャパシタ156が除去されている点と、スイッチS5のオン/オフのタイミングおよび信号φB1,/φB1のレベル変化のタイミングである。

【0156】

図59は、図58に示したオフセット補償機能付駆動回路157の動作を示すタイムチャートである。ここでは、N型トランジスタ31のしきい値電圧VTN′がN型トランジスタ23のしきい値電圧VTNよりもVOFだけ大きいものとする。初期状態では、スイッチS1a〜S3a,S1b〜S3bはオフ状態にされるとともにスイッチS4a,S4b,S5がオン状態にされ、ノードN30a,N30b,N20aの電位V30a,V30b,V20aはともに前回の入力電位(図ではVH)になっている。

【0157】

時刻t1においてスイッチS5がオフ状態にされてスイッチS30a,S30bの間のノードと負荷容量36とが電気的に切離される。時刻t2においてスイッチS1a,S1b,S2a,S2bがオン状態にされるとともに、入力電位VIが今回の電位(図ではVL)に設定される。このように、ノードN30a,N30b,N20bの電位V30a,V30b,V20bはともにVI=VLになる。N型トランジスタ31のしきい値電圧VTN′が他のN型トランジスタのしきい値電圧VTNよりもVOFだけ高いにもかかわらずV30a,V30bがVI=VLになるのは、放電回路がノードN30a,N30bをVI=VLまで放電するが、それ以下には放電しないからである。

【0158】

時刻t3においてスイッチS4a,S4bがオフ状態にされて、充電回路と放電回路は電気的に切離される。時刻t4においてリセット信号/φRが「H」レベルから「L」レベルに立下げられるとともに信号φRが「L」レベルから「H」レベルに立上げられる。これにより、ノードN30aの電位V30aがVLからパルス的に降圧された後VL−VOFになるととももに、ノードN30bの電位V30bがVLからパルス的に昇圧された後VLになる。

【0159】

時刻t5においてスイッチS1a,S1b,S2a,s2bがオフ状態にされ、次いで時刻t6においてスイッチS3a,S3bがオン状態にされると、ノードN20aの電位V20aがVL+VOFになり、オフセット電圧VOFが打消されてノードN30aの電位V30aはVI=VLになる。

【0160】

時刻t7においてスイッチS3a,S3bがオフ状態にされ、次いで時刻t8においてスイッチS4a,S4b,S5がオン状態にされると、負荷容量36が前回の電位であるVHに充電されているので、ノードN30a,N30bの電位V30a,V30bは一旦上昇した後、徐々に低下する。時刻t9において、信号φB1が「L」レベルから「H」レベルに立上げられるとともに、信号/φB1が「H」レベルから「L」レベルに立下げられる。

【0161】

このように、キャパシタ76を介してノードN22の電位V22が昇圧されるとともに、キャパシタ77を介してノードN27の電位V27が降圧される。このとき、出力ノードN121に「L」レベルVLを出力する動作を行なっており、P型トランジスタ35の導通抵抗値はN型トランジスタ31の導通抵抗値よりも低くなっているので、V27によるレベル降下作用の方がV22によるレベル上昇作用よりも強く働き、ノードN30a,N30b,N121の電位V30a,V30b,VOは急速に低下してVLに到達する。

【0162】

この実施の形態15では、動作速度の高速化を図ることができる。

[実施の形態16]

図60は、この発明の実施の形態16によるカラー液晶表示装置の要部を示す回路図である。図60において、このカラー液晶表示装置では、各データ線6に階調電位を与える前に各データ線6の電位をプリチャージ電位VPCにするためのイコライザ+プリチャージ回路158が設けられる。

【0163】

イコライザ+プリチャージ回路158は、各データ線6に対応して設けられたスイッチS6と、各隣接する2つのデータ線6に対応して設けられたスイッチS7とを含む。スイッチS6の一方端子はプリチャージ電位VPCを受け、その他方端子は対応のデータ線6に接続される。スイッチS6は、プリチャージ信号φPCが活性化レベルの「H」レベルにされたことに応じてオン状態にされる。スイッチS6がオン状態にされると、各データ線6はプリチャージ電位VPCにされる。スイッチS7は、2つのデータ線6間に接続され、イコライズ信号φEQが活性化レベルの「H」レベルにされたことに応じてオン状態にされる。スイッチS7がオン状態にされると、全データ線6の電位が平均化される。スイッチS6,S7がオフ状態にされた後、各データ線6に階調電位が与えられる。

【0164】

ここでは、プリチャージ電位VCPを0Vとする。階調電位は0V〜5Vであるので(図3参照)、駆動回路はデータ線6の充電を行えば良く、放電を行う必要はない。そこで、このカラー液晶表示装置では、プッシュ型の駆動回路が使用される。

【0165】

図61は、そのプッシュ型駆動回路160の構成を示す回路図である。図61において、このプッシュ型駆動回路160は、レベルシフト回路61、プルアップ回路30、および定電流源161を備える。レベルシフト回路61およびプルアップ回路30は、図17で示したものと同じである。

【0166】

すなわち、レベルシフト回路61は、第3電源電位V3(15V)のノードと接地電位GNDのノードとの間に直列接続された定電流源62、N型トランジスタ23およびP型トランジスタ24を含む。定電流源62は、図62に示すように、P型トランジスタ65,66および抵抗素子67を含む。P型トランジスタ65は第3電源電位V3のノードとN型トランジスタ23のドレイン(ノードN22)との間に接続され、P型トランジスタ66および抵抗素子67は第3電源電位V3のノードと接地電位GNDのノードとの間に直列接続される。P型トランジスタ65,66のゲートは、ともにP型トランジスタ66のドレインに接続される。P型トランジスタ65,66は、カレントミラー回路を構成する。P型トランジスタ66および抵抗素子67には抵抗素子67の抵抗値に応じた値の定電流が流れ、P型トランジスタ65にはP型トランジスタ66に流れる定電流の値に応じた値の定電流が流れる。N型トランジスタ23のゲートは、そのドレイン(ノードN22)に接続されている。N型トランジスタ23は、ダイオード素子を構成する。P型トランジスタ24のゲートは、入力ノードN20に接続される。定電流源62の電流値は、トランジスタ23,24の各々に所定のしきい値電圧を発生させるために必要な最小限の値に設定されている。

【0167】

入力ノードN20の電位(階調電位)をVIとし、P型トランジスタのしきい値電圧をVTPとし、N型トランジスタのしきい値電圧をVTNとすると、P型トランジスタ24のソース(ノードN23)の電位V23およびN型トランジスタ23のドレイン(ノードN22)の電位V22はそれぞれV23=VI+|VTP|,V22=VI+|VTP|+VTNとなる。したがって、レベルシフト回路61は、入力電位VIを|VTP|+VTNだけレベルシフトさせた電位V22を出力する。

【0168】

プルアップ回路30は、第6電源電位V6(15V)のノードと出力ノードN30との間に直列接続されたN型トランジスタ31およびP型トランジスタ32を含む。N型トランジスタ31のゲートは、レベルシフト回路61の出力電位V22を受ける。P型トランジスタ32のゲートは、そのドレインに接続されている。P型トランジスタ32は、ダイオード素子を構成する。N型トランジスタ31は飽和領域で動作するように第6電源電位V6が設定されているので、N型トランジスタ31はいわゆるソースフォロア動作を行なう。

【0169】

定電流源161は、出力ノードN30と接地電位GNDのノードとの間に接続される。定電流源161は、図62に示すように、N型トランジスタ162,163および抵抗素子164を含む。N型トランジスタ162は出力ノードN30と接地電位GNDのノードとの間に接続され、抵抗素子164およびN型トランジスタ163は第6電源電位V6のノードと接地電位GNDのノードとの間に直列接続される。N型トランジスタ162,163のゲートは、ともにN型トランジスタ163のドレインに接続される。N型トランジスタ162,163は、カレントミラー回路を構成する。抵抗素子164およびN型トランジスタ163には抵抗素子164の抵抗値に応じた値の定電流が流れ、N型トランジスタ162にはN型トランジスタ163に流れる定電流の値に応じた値の定電流が流れる。定電流源161の電流値は、トランジスタ31,32の各々に所定のしきい値電圧を発生させるために必要な最小限の値に設定されている。

【0170】

N型トランジスタ31のソース(ノードN31)の電位V31はV31=V22−VTN=VI+|VTP|となり、出力ノードN30の電位VOはVO=V31−|VTP|=VIとなる。

【0171】

この実施の形態16では、トランジスタ23,24,31,32の各々に所定のしきい値電圧を発生させるために必要な最小限の値の貫通電流を流せば足りるので、消費電流が小さくて済む。

【0172】

また、図63は、この実施の形態16の変更例によるプッシュ型駆動回路165の構成を示す回路図である。図63を参照して、この駆動回路165が図62の駆動回路160と異なる点は、抵抗素子164が除去され、抵抗素子67が2つの定電流源62と161で共用されている点である。抵抗素子67およびN型トランジスタ163は、P型トランジスタ66のソースと接地電位GNDのノードとの間に直列接続される。N型トランジスタ163のゲートはそのドレインに接続される。この変更例では、抵抗素子67と164の抵抗値のバラツキによってオフセット電圧が発生することを防止することができる。

【0173】

また、図64のプッシュ型駆動回路166は、図61のプッシュ型駆動回路160からダイオード接続されたトランジスタ23,32を除去したものである。出力電位VOは、VO=VI+|VTP|−VTNとなる。ただし、|VTP|≒VTNと設定すれば、VO≒VIとなる。あるいは、|VTP|−VTNの値をオフセット値として使用上考慮しておけば図61の駆動回路160と同様に使用することができる。この変更例では、トランジスタ23,32を除去したので、回路の占有面積を小さくすることができる。

【0174】

[実施の形態17]

図60で示したカラー液晶表装置においてプリチャージ電位VCPを5Vとすると、階調電位は0V〜5Vであるので(図3参照)、駆動回路はデータ線6の放電を行えば良く、充電を行う必要はない。そこで、このカラー液晶表示装置では、プル型の駆動回路が使用される。

【0175】

図65は、この発明の実施の形態17によるプル型駆動回路170の構成を示す回路図である。図65において、この駆動回路170は、レベルシフト回路63、定電流源171およびプルダウン回路33を含む。レベルシフト回路63およびプルダウン回路33は、図17で示したものと同じである。

【0176】

すなわち、レベルシフト回路63は、第4電源電位V4(5V)のノードと第5電源電位V5(−10V)のノードとの間に直列接続されたN型トランジスタ26、P型トランジスタ27および定電流源64を含む。N型トランジスタ26のゲートは、入力ノードN20の電位VIを受ける。P型トランジスタ27のゲートは、そのドレイン(ノードN27)に接続される。P型トランジスタ27は、ダイオード素子を構成する。定電流源64の電流値は、トランジスタ26,27の各々に所定のしきい値電圧を発生させるために必要な最小限の値に設定されている。

【0177】

N型トランジスタ26のソース(ノードN26)の電位V26はV26=VI−VTNとなる。P型トランジスタ27のドレイン(ノードN27)の電位V127は、V27=VI−VTN−|VTP|となる。したがって、レベルシフト回路63は、入力電位VIを−VTN−|VTP|だけレベルシフトさせた電位V27を出力する。

【0178】

定電流源171は、第4電源電位V4のノードと出力ノードN30との間に接続される。プルダウン回路33は、第7電源電位V7(−10V)のノードと出力ノードN30との間に直列接続されたP型トランジスタ35およびN型トランジスタ34を含む。P型トランジスタ35のゲートは、レベルシフト回路63の出力電位V27を受ける。N型トランジスタ34のゲートは、そのドレインに接続されている。N型トランジスタ34は、ダイオード素子を構成する。P型トランジスタ35は飽和領域で動作するように第7電源電位V7が設定されているので、P型トランジスタ35はいわゆるソースフォロア動作を行なう。定電流源71の電流値は、トランジスタ34,35の各々に所定のしきい値電圧を発生させるために必要な最小限の値に設定されている。

【0179】

P型トランジスタ35のソース(ノードN34)の電位V34は、V34=V27+|VTP|=VI−VTNとなる。出力ノードN30の電位VOは、VO=V34+VTN=VIとなる。

【0180】

この実施の形態17では、トランジスタ26,27,34,35の各々に所定のしきい値電圧を発生させるために必要な最小限の値の貫通電流を流せば足りるので、消費電流が小さくて済む。

【0181】

また、図66は、この実施の形態17の変更例によるプル型駆動回路172の構成を示す回路図である。図66を参照して、このプル型駆動回路172は、図65のプル型駆動回路170からダイオード接続されたトランジスタ27,34を除去したものである。出力電位VOは、VO=VI+|VTP|−VTNとなる。ただし、|VTP|≒VTNと設定すれば、VO≒VIとなる。あるいは、|VTP|−VTNの値をオフセット値として使用上考慮しておけば図65の駆動回路170と同様に使用することができる。この変更例では、トランジスタ27,34を除去したので、回路の占有面積を小さくすることができる。

【0182】

[実施の形態18]

図67は、この発明の実施の形態18による駆動回路175の構成を示す回路図である。図67において、この駆動回路175は、図61のプッシュ型駆動回路160と、図65のプル型駆動回路170とを組合せたものである。レベルシフト回路61のP型トランジスタ24のゲートおよびレベルシフト回路63のN型トランジスタ26のゲートは、入力ノードN20の電位VIを受ける。プルアップ回路30のP型トランジスタ32のドレインおよびプルダウン回路33のN型トランジスタ34のドレインは、ともに出力ノードN30に接続される。

【0183】

出力電位VOが入力電位VIよりも高い場合は、プルアップ回路30のトランジスタ31,32が非導通になるとともに、プルダウン回路33のトランジスタ34,35が導通し、出力電位VOが低下する。出力電位VOが入力電位VIよりも低い場合は、プルダウン回路33のトランジスタ34,35が非導通になるとともに、プルアップ回路30のトランジスタ31,32が導通し、出力電位VOが上昇する。したがって、VO=VIとなる。

【0184】

この駆動回路175は、プッシュ型駆動回路、プル型駆動回路、またはプッシュプル型駆動回路として用いられる。駆動回路175がプッシュ型駆動回路として用いられる場合は、プルダウン回路33のトランジスタ34,35の電流駆動能力がプルアップ回路30のトランジスタ31,32の電流駆動能力に比べて十分に小さなレベルに設定される。駆動回路175がプル型駆動回路として用いられる場合は、プルアップ回路30のトランジスタ31,32の電流駆動能力がプルダウン回路33のトランジスタ34,35の電流駆動能力に比べて十分に小さなレベルに設定される。駆動回路175がプッシュプル型駆動回路として用いられる場合は、プルアップ回路30のトランジスタ31,32の電流駆動能力とプルダウン回路33のトランジスタ34,35の電流駆動能力とは同じレベルに設定される。

【0185】

この実施の形態18でも、貫通電流が小さな駆動回路175を得ることができ、消費電力の低減化を図ることができる。

【0186】

また、図68は、この実施の形態18の変更例による駆動回路176の構成を示す回路図である。図68を参照して、この駆動回路176は、図67の駆動回路170からダイオード接続されたトランジスタ23,27,32,34を除去したものである。出力電位VOは、VO=VI+|VTP|−VTNとなる。ただし、|VTP|≒VTNと設定すれば、VO≒VIとなる。あるいは、|VTP|−VTNの値をオフセット値として使用上考慮しておけば図67の駆動回路175と同様に使用することができる。この変更例では、トランジスタ23,27,32,34を除去したので、回路の占有面積を小さくすることができる。

【0187】

また、図69は、この実施の形態18の他の変更例による駆動回路180の構成を示す回路図である。図69において、この駆動回路180は、図67の駆動回路175のレベルシフト回路61,63をそれぞれレベルシフト回路181,183で置換したものである。レベルシフト回路181は、レベルシフト回路61の定電流源62を抵抗素子182で置換したものである。レベルシフト回路183は、レベルシフト回路63の定電流源64を抵抗素子184で置換したものである。抵抗素子182,184の抵抗値は、抵抗素子182,184が定電流源62,64と同程度の電流を流すような値に設定されている。この変更例でも、図67の駆動回路175と同じ効果が得られる。

【0188】

また、図70は、この実施の形態18のさらに他の変更例による駆動回路185の構成を示す回路図である。図70を参照して、この駆動回路185が図67の駆動回路175と異なる点は、定電流源161が出力ノードN30と第5電源電位V5のノードとの間に接続され、定電流源171が第3電源電位V3のノードと出力ノードN30との間に接続されている点である。

【0189】

定電流源62,64,161,171は、図71に示すように、抵抗素子67、P型トランジスタ65,66,189、およびN型トランジスタ186〜188で構成される。P型トランジスタ66、抵抗素子67およびN型トランジスタ186は、第3電源電位V3のノードと第5電源電位V5のノードとの間に直列接続される。P型トランジスタ66のゲートはそのドレインに接続され、N型トランジスタ186のゲートはそのドレインに接続される。トランジスタ66,186の各々は、ダイオード素子を構成する。

【0190】

P型トランジスタ65は、第3電源電位V3のノードとノードN22との間に接続され、そのゲートはP型トランジスタ66のゲートに接続される。P型トランジスタ189は、第3電源電位V3のノードと出力ノードN30との間に接続され、そのゲートはP型トランジスタ66のゲートに接続される。P型トランジスタ66,65,189は、カレントミラー回路を構成する。P型トランジスタ65,189の各々には、P型トランジスタ66に流れる電流に応じた値の電流が流れる。P型トランジスタ65,189は、それぞれ定電流源62,171を構成する。

【0191】

N型トランジスタ187は、第5電源電位V5のノードとノードN27との間に接続され、そのゲートはN型トランジスタ186のゲートに接続される。N型トランジスタ188は、第5電源電位V5のノードと出力ノードN30との間に接続され、そのゲートはN型トランジスタ186のゲートに接続される。N型トランジスタ186〜188は、カレントミラー回路を構成する。N型トランジスタ187,188の各々には、N型トランジスタ186に流れる電流に応じた値の電流が流れる。N型トランジスタ187,188は、それぞれ定電流源64,161を構成する。他の構成および動作は、図67の駆動回路175と同じであるので、その説明は繰り返さない。この変更例でも、図67の駆動回路175と同じ効果が得られる。

【0192】

[実施の形態19]

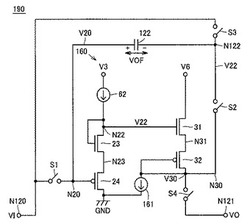

図72は、この発明の実施の形態19によるオフセット補償機能付駆動回路190の構成を示す回路ブロック図である。図72において、このオフセット補償機能付駆動回路190は、図61のプッシュ型駆動回路160にキャパシタ122およびスイッチS1〜S4を付加したものである。キャパシタ122およびスイッチS1〜S4は、プッシュ型駆動回路160のオフセット電圧VOFを補償するためのオフセット補償回路を構成する。

【0193】

すなわち、スイッチS1は入力ノードN120と駆動回路160の入力ノードN20との間に接続され、スイッチS4は出力ノードN121と駆動回路160の出力ノードN30との間に接続される。キャパシタ122およびスイッチS2は、駆動回路160の入力ノードN20と出力ノードN30との間に直列接続される。スイッチS3は、入力ノードN120とキャパシタ122およびスイッチS2間のノードN122との間に接続される。

【0194】

次に、このオフセット補償機能付駆動回路190の動作について説明する。初期状態では、すべてのスイッチS1〜S4はオフ状態にされている。ある時刻においてスイッチS1,S2がオン状態にされると、駆動回路160の入力ノードN20の電位V20はV20=VIになり、駆動回路121の出力電位V30およびノードN122の電位V122はV30=V122=VI−VOFとなり、キャパシタ122はオフセット電圧VOFに充電される。

【0195】

次に、スイッチS1,S2がオフ状態にされると、オフセット電圧VOFはキャパシタ122に保持される。次いでスイッチS3がオン状態にされると、ノードN122の電位V122はV122=VIになり、駆動回路160の入力電位V20はV20=VI+VOFとなる。この結果、駆動回路160の出力電位V30はV30=V20−VOF=VIとなり、駆動回路160のオフセット電圧VOFは打消されたことになる。次にスイッチS4がオン状態にされると、出力電位VOがVO=VIとなり負荷に供給される。

【0196】

この実施の形態19では、プッシュ型駆動回路160のオフセット電圧VOFを打消すことができ、出力電位VOと入力電位VIを一致させることができる。

【0197】

図73のオフセット補償機能付プル型駆動回路191は、図65のプル型駆動回路170にキャパシタ122およびスイッチS1〜S4を付加したものである。この変更例では、プル型駆動回路191のオフセット電圧VOFを打消すことができ、出力電位VOと入力電位VIを一致させることができる。また、駆動回路165,166,172の各々にキャパシタ122およびスイッチS1〜S4を付加しても同じ効果が得られることは言うまでもない。

【0198】

[実施の形態20]

図74は、この発明の実施の形態20によるオフセット補償機能付駆動回路195の構成を示す回路ブロック図である。図74において、このオフセット補償機能付駆動回路195は、図67の駆動回路175にキャパシタ122a,122bおよびスイッチS1a〜S4a,S1b〜S4bを付加したものである。

【0199】

スイッチS1a,S1bは、それぞれ入力ノードN120とトランジスタ24,26のゲート(ノードN20a,N20b)との間に接続される。スイッチS4a,S4bは、それぞれ出力ノードN121とトランジスタ32,34のドレイン(ノードN30a,N30b)との間に接続される。キャパシタ122aおよびスイッチS2aは、ノードN20aとN30aの間に直列接続される。キャパシタ121bおよびスイッチS2bは、ノードN20bとN30bの間に直列接続される。スイッチS3aは、入力ノードN120とキャパシタ122aおよびスイッチS2a間のノードN122aとの間に接続される。スイッチ3bは、入力ノードN120とキャパシタ122bおよびスイッチS2b間のノードN122bとの間に接続される。

【0200】

次に、この駆動回路195の動作について説明する。初期状態では、すべてのスイッチS1a〜S4a,S1b〜S4bはオフ状態にされている。ある時刻においてスイッチS1a,S2a,S1b,S2bがオン状態にされると、ノードN30a,N30bの電位V30a,V30bがそれぞれV30a=VI−VOFa,V30b=VI−VOFbとなり、キャパシタ122a,122bはそれぞれオフセット電圧VOFa,VOFbに充電される。

【0201】

次に、スイッチS1a,S2a,S1b,S2bがオフ状態にされると、オフセット電圧VOFa,VOFbがそれぞれキャパシタ122a,122bに保持される。次いでスイッチS3a,S3bがオン状態にされると、トランジスタ24,26のゲート電位がそれぞれVI+VOFa,VI+VOFbとなる。この結果、ノードN30a,N30bの電位V30a,V30bがそれぞれV30a=VI+VOFa−VOFa=VI,V30b=VI+VOFb−VOFb=VIとなり、駆動回路175のオフセット電圧VOFa、VOFbは打ち消されたことになる。最後にスイッチS4a,S4bがオン状態にされて、VO=VIとなる。

【0202】

この実施の形態20では、オフセット電圧がなく、かつ消費電力が小さな駆動回路195が得られる。

【0203】

なお、駆動回路176,180,185の各々ににキャパシタ122a,122bおよびスイッチS1a〜S4a,S1b〜S4bを付加しても同じ効果が得られることは言うまでもない。

【0204】

また、図75のオフセット補償機能付駆動回路196は、図74のオフセット補償機能付駆動回路195にキャパシタ126a,126bを追加したものである。キャパシタ126a,126bの一方電極はそれぞれノードN30a,N30bに接続され、それらの他方電極はそれぞれリセット信号/φRおよびその相補信号φRを受ける。初期状態では、信号/φR、φRはそれぞれ「H」レベルおよび「L」レベルにされている。定電流源161の電流値は小さく設定されているので、ノードN30aの電位V30aが入力電位VIよりも高い場合にスイッチS1a,S2aがオン状態にされても、ノードN30aの電位V30aは緩やかに低下する。また、定電流源171の電流値は小さく設定されているので、ノードN30bの電位V30bが入力電位VIよりも低い場合にスイッチS1b,S2bがオン状態にされても、ノードN30bの電位V30bは緩やかに上昇する。そこで、この変更例では、スイッチS1a,S2a,S1b,S2bがオン状態にされた直後に、信号/φRを「H」レベルから「L」レベルに立ち下げるとともに信号φRを「L」レベルから「H」レベルに立ち上げる。これにより、トランジスタ31,32,34,35が導通し、ノードN30a,N30bの電位V30a,V30bの各々が迅速に入力電位VIに一致する。したがって、変更例では、駆動回路の動作速度の高速化を図ることができる。

【0205】

また、図76のオフセット補償機能付駆動回路197は、図75のオフセット補償機能付駆動回路196のキャパシタ126a,126bをそれぞれN型トランジスタ131aおよびP型トランジスタ131bで置換したものである。N型トランジスタ131aは、第8電源電位V8のラインとノードN30aとの間に接続され、そのゲートはリセット信号φR′を受ける。P型トランジスタ131bは、ノードN30bと第9電源電位V9のラインとの間に接続され、そのゲートはリセット信号φR′の相補信号/φR′を受ける。通常時は信号φR′,/φR′がそれぞれ「L」レベルおよび「H」レベルにされており、N型トランジスタ131aおよびP型トランジスタ131bはともに非導通にされている。スイッチS1a,S2a,S1b,S2bがオン状態にされた直後に、信号φR′が所定時間だけパルス的に「H」レベルにされるとともに信号/φR′が所定時間だけパルス的に「L」レベルにされる。これにより、N型トランジスタ131aがパルス的に導通してノードN30aの電位V30aが第8電源電位V8に低下されるとともに、P型トランジスタ131bがパルス的に導通してノードN30bの電位V30bが第9電源電位V9に上昇される。この変更例でも動作速度の高速化を図ることができる。

【0206】

また、図77のオフセット補償機能付駆動回路198は、図75の駆動回路196にP型トランジスタ81およびN型トランジスタ82を付加したものである。P型トランジスタ81は、定電流源62に並列接続され、そのゲートは信号/φPを受ける。N型トランジスタ82は、定電流源64に並列接続され、そのゲートは信号φPを受ける。初期状態では、信号/φP、φPはそれぞれ「H」レベルおよび「L」レベルにされている。定電流源62の電流値は小さく設定されているので、ノードN22の電位V22が入力電位VIよりも低い場合にスイッチS1a,S2aがオン状態にされても、ノードN22の電位V22は緩やかにに上昇する。また、定電流源64の電流値は小さく設定されているので、ノードN27の電位V27が入力電位VIよりも高い場合にスイッチS1b,S2bがオン状態にされても、ノードN27の電位V27は緩やかに下降する。そこで、この変更例では、スイッチS1a,S2a,S1b,S2bがオン状態にされた直後に、信号/φPを所定時間だけパルス的に「L」レベルに立ち下げるとともに信号φPを所定時間だけパルス的に「H」レベルに立ち上げる。これにより、トランジスタ81,82がパルス的に導通し、ノードN22の電位V22が迅速に上昇するとともにノードN27の電位V27が迅速に低下する。したがって、変更例では、駆動回路の動作速度の高速化を図ることができる。

【0207】

[実施の形態21]

図72のオフセット補償機能付プッシュ型駆動回路190において、スイッチS1,S2をオン状態にしたときにオフセット電圧VOFを発生させるためには、トランジスタ31,32を導通させる必要がある。スイッチS1,S2をオン状態にしたときにトランジスタ31,32を必ず導通させるためには、スイッチS1,S2をオン状態にする前に、ノードN30の電位V30を入力電位VIの最低値VIminからオフセット電圧VOFの最大値ΔVmaxを減算した定電位VImin−ΔVmaxにリセットする必要がある。また、ノードN30に定電位VImin−ΔVmaxを印加したときにトランジスタ31,32に大電流流れることを防止する必要がある。この実施の形態21では、この問題が解決される。

【0208】

図78は、この発明の実施の形態21によるオフセット補償機能付プッシュ型駆動回路200の構成を示す回路ブロック図である。図78において、このオフセット補償機能付プッシュ型駆動回路200は、図72の駆動回路190にN型トランジスタ201,202,204およびP型トランジスタ203を付加したものである。トランジスタ201〜204は、ノードN30の電位V30を初期化するためのリセット回路を構成する。

【0209】

すなわち、トランジスタ201〜203は、ノードN22と接地電位GNDのノードとの間に直列接続される。N型トランジスタ201のゲートは、クロック信号CLKを受ける。N型トランジスタ202のゲートは、そのドレインに接続される。N型トランジスタ202は、ダイオード素子を構成する。P型トランジスタ203のゲートは、入力電位VIの最低値VIminからオフセット電圧VOFの最大値ΔVmaxを減算した定電位VImin−ΔVmaxを受ける。N型トランジスタ204のドレインはノードN30に接続され、そのソースは定電位VImin−ΔVmaxを受け、そのゲートはクロック信号CLKを受ける。

【0210】

スイッチS1,S2がオン状態にされている期間において、クロック信号CLKが所定時間だけパルス的に「H」レベルにされる。これにより、N型トランジスタ204が導通してノードN30の電位V30が定電位VImin−ΔVmaxにされ、トランジスタ31,32が導通してオフセット電圧VOFが発生する。また、N型トランジスタ201が導通してノードN22の電位V22が定電位VImin−ΔVmaxにP型トランジスタ203のしきい値電圧の絶対値|VTP|およびN型トランジスタ201のしきい値電圧VTNを加算した電位VImin−ΔVmax+|VTP|+VTNになる。このときノードN22とN30との電位差は|VTP|+VTNとなるので、トランジスタ31,32には微小電流しか流れない。他の構成および動作は図72の駆動回路190と同じであるので、その説明は繰り返さない。

【0211】

この実施の形態21では、出力電位VOと入力電位VIが正確に一致し、かつ低消費電力の駆動回路200が得られた。

【0212】

なお、N型トランジスタ201と204を別の信号で制御してもよい。また、N型トランジスタ201,204の各々をP型トランジスタで置換しても良い。但し、P型トランジスタのゲートには信号CLKの相補信号/CLKを与える必要がある。また、ノードN22に所定電位が現れるのであれば、P型トランジスタ203のドレインは、接地電位GND以外の電位のノードに接続しても良い。また、所定の電流が流れるのであれば、定電流源161の低電位側の端子は、接地電位GND以外の電位のノードに接続しても良い。

【0213】

[実施の形態22]

図73のオフセット補償機能付プル型駆動回路191において、スイッチS1,S2をオン状態にしたときにオフセット電圧VOFを発生させるためには、トランジスタ34,35を導通させる必要がある。スイッチS1,S2をオン状態にしたときにトランジスタ34,35を必ず導通させるためには、スイッチS1,S2をオン状態にする前に、ノードN30の電位V30を入力電位VIの最高値VImaxにオフセット電圧VOFの最大値ΔVmaxを加算した定電位VImax+ΔVmaxにリセットする必要がある。また、ノードN30に定電位VImax+ΔVmaxを印加したときにトランジスタ34,35に大電流が流れることを防止する必要がある。この実施の形態22では、この問題が解決される。

【0214】

図79は、この発明の実施の形態22によるオフセット補償機能付プル型駆動回路210の構成を示す回路ブロック図である。図79において、このオフセット補償機能付プル型駆動回路210は、図73の駆動回路191にN型トランジスタ211およびP型トランジスタ212〜214を付加したものである。トランジスタ211〜214は、ノードN30の電位V30を初期化するためのリセット回路を構成する。

【0215】

すなわち、トランジスタ211〜213は、第4電源電位V4のノードとノードN27との間に直列接続される。P型トランジスタ211のゲートは、入力電位VIの最高値VImaxにオフセット電圧VOFの最大値ΔVmaxを加算した定電位VImax+ΔVmaxを受ける。P型トランジスタ212のゲートは、そのドレインに接続される。P型トランジスタ212は、ダイオード素子を構成する。P型トランジスタ213のゲートは、相補クロック信号/CLKを受ける。P型トランジスタ214のドレインはノードN30に接続され、そのソースは定電位VImax+ΔVmaxを受け、そのゲートは相補クロック信号/CLKを受ける。

【0216】

スイッチS1,S2がオン状態にされている期間において、相補クロック信号/CLKが所定時間だけパルス的に「L」レベルにされる。これにより、P型トランジスタ214が導通してノードN30の電位V30が定電位VImax+ΔVmaxにされ、トランジスタ34,35が導通してオフセット電圧VOFが発生する。また、P型トランジスタ213が導通してノードN27の電位V27が定電位VImax+ΔVmaxからN型トランジスタ211のしきい値電圧VTNおよびP型トランジスタ212のしきい値電圧の絶対値|VTP|を減算した電位VImax+ΔVmax−VTN−|VTP|になる。このときノードN30とN27との電位差はVTN+|VTP|となるので、トランジスタ34,35には微小電流しか流れない。他の構成および動作は図73の駆動回路191と同じであるので、その説明は繰り返さない。

【0217】

この実施の形態22では、出力電位VOと入力電位VIが正確に一致し、かつ低消費電力の駆動回路210が得られた。

【0218】

なお、P型トランジスタ213と214を別の信号で制御してもよい。また、N型トランジスタ213,214の各々をN型トランジスタで置換しても良い。但し、N型トランジスタのゲートには信号/CLKの相補信号CLKを与える必要がある。また、ノードN27に所定電位が現れるのであれば、N型トランジスタ211のドレインは、第4電源電位V4以外の電位のノードに接続しても良い。また、所定の電流が流れるのであれば、定電流源165の高電位側の端子は、第4電源電位V4以外の電位のノードに接続しても良い。さらに、図78の駆動回路200と図79の駆動回路210を並列接続すれば、良好なオフセット補償機能付プッシュプル型駆動回路が得られることもいうまでもない。

【0219】

なお、以上の実施の形態1〜22において、電界効果トランジスタは、MOSトランジスタであってもよいし、薄膜トランジスタ(TFT)でもよい。薄膜トランジスタは、ポリシリコン薄膜、アモルファスシリコン薄膜などのどのような半導体薄膜で形成されたものでもよいし、樹脂基板、ガラス基板などのどのような絶縁基板上に形成されたものでもよい。

【0220】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0221】

1 液晶パネル、2 液晶セル、3 画素、4 走査線、5 共通電位線、6 データ線、7 垂直走査回路、8 水平走査回路、10 液晶駆動回路、11,23,26,31,34,42.0〜42.m,47.0〜47.m,69,70,82,86,99〜101,103,104,131a,162,163,186〜188,201,202,204,211,303,304 N型電界効果トランジスタ、12,29,76,77,118,119,122,122a,122b,126a,126b,156 キャパシタ、15 階調電位発生回路、16.1〜16.n+1,22,28,51.0〜51.i,56.1〜56.i,67,68,164 抵抗素子、17.1〜17.n,S1,S1a,S1b,S2,S2a,S2b,S3,S3a,S3b,S4,S4a,S4b,S5〜S7 スイッチ、20,36,37,38,60,71,72,73,75,78,80,83,85,88,90,91,95,108,110,113,115.1〜115.j,121,160、165,166,170,172,175,176,180,185,190,191,195〜198,200,210,300 駆動回路、21,21′,25,25′,40,45,50,55,61,61′,63,63′,96,96′、102,102′,111,111′,112,112′,116,117 レベルシフト回路、24,27,32,35,43.0〜43.m,48.0〜48.m,65,66,81,87,97,98,105〜107,131b,189,203,212〜214,301,302 P型電界効果トランジスタ、30,30′ プルアップ回路、33,33′ プルダウン回路、36 負荷容量、41.1〜41.m,46.1〜46.m,52.1〜52.i,57.1〜57.i ヒューズ、120,125,127,130,132,133,135,136,140,141,145,146,150,151,155,157 オフセット補償機能付駆動回路、62,64,161,171,305 定電流源。

【技術分野】

【0001】

この発明は駆動回路に関し、特に、入力電位に応じた電位を出力ノードに出力する駆動回路に関する。

【背景技術】

【0002】

従来より、半導体集積回路装置には、駆動能力が小さな電位発生回路で生成された電位を負荷に伝達するための駆動回路が設けられている。図80は、そのような駆動回路300の構成を示す回路図である。図80において、この駆動回路300は、P型電界効果トランジスタ(以下、P型トランジスタと称す)301,302、N型電界効果トランジスタ(以下、N型トランジスタと称す)303,304および定電流源305を含む。

【0003】

P型トランジスタ301,302は、それぞれ電源電位VCCのノードとノードN301,N302との間に接続され、それらのゲートはともにノードN301に接続される。P型トランジスタ301,302は、カレントミラー回路を構成する。N型トランジスタ303は、ノードN301とN305の間に接続され、そのゲートは入力ノードN303に接続される。N型トランジスタ304は、ノードN302とN305の間に接続され、そのゲートは出力ノードN304およびノードN302に接続される。定電流源305は、ノードN305と接地電位GNDのノードとの間に接続され、一定の電流を流す。

【0004】

N型トランジスタ303には、入力ノードN303の電位VIに応じた値の電流が流れる。N型トランジスタ303とP型トランジスタ301は直列接続され、P型トランジスタ301と302はカレントミラー回路を構成しているので、トランジスタ301〜303には同じ値の電流が流れる。出力ノードN304の電位VOが入力電位VIよりも低い場合は、トランジスタ301〜303に流れる電流よりもN型トランジスタ304に流れる電流が小さくなり、出力電位VOが上昇する。出力ノードN304の電位VOが入力電位VIよりも高い場合は、トランジスタ301〜303に流れる電流よりもN型トランジスタ304に流れる電流が大きくなり、出力電位VOが低下する。したがって、出力電位VOは入力電位VIに等しくなる。

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、従来の駆動回路300では、電源電位VCCのノードからトランジスタ301〜304および定電流源305を介して接地電位GNDのノードに一定の貫通電流が常時流れていたので、消費電流が大きいという問題があった。

【0006】

それゆえに、この発明の主たる目的は、消費電流が小さな駆動回路を提供することである。

【課題を解決するための手段】

【0007】

この発明に係る駆動回路は、入力電位に応じた電位を出力ノードに出力する駆動回路であって、入力電位を予め定められた第1の電圧だけある電位方向にレベルシフトさせた電位を出力する第1のレベルシフト回路と、第1のレベルシフト回路の出力電位をある電位方向と逆の電位方向に予め定められた第2の電圧だけレベルシフトさせた電位を出力ノードに出力する第2のレベルシフト回路と、第1および第2の電圧の差の電圧であるオフセット電圧を打消して出力ノードの電位を入力電位に一致させるオフセット補償回路とを備えたものである。第1のレベルシフト回路は、その一方電極が第1の電源電位を受ける第1の電流制限素子と、その第1の電極が第2の電源電位を受け、その入力電極が入力電位を受ける第1の導電形式の第1のトランジスタと、その第1の電極および入力電極が第1の電流制限素子の他方電極に接続され、その第2の電極が第1のトランジスタの第2の電極に接続された第2の導電形式の第2のトランジスタとを含む。第2のレベルシフト回路は、その第1の電極が第3の電源電位を受け、その入力電極が第1の電流制限素子の他方電極に接続された第2の導電形式の第3のトランジスタと、その第1の電極が第3のトランジスタの第2の電極に接続され、その第2の電極および入力電極が出力ノードに接続された第1の導電形式の第4のトランジスタとを含む。

【発明の効果】

【0008】

この発明に係る駆動回路では、入力電位を第1の電圧だけある電位方向にレベルシフトさせた電位を出力する第1のレベルシフト回路と、第1のレベルシフト回路の出力電位をある電位方向と逆の電位方向に第2の電圧だけレベルシフトさせた電位を出力ノードに出力する第2のレベルシフト回路と、第1および第2の電圧の差の電圧であるオフセット電圧を打消して出力ノードの電位を入力電位に一致させるオフセット補償回路とが設けられる。したがって、第1および第2のレベルシフト回路の貫通電流を小さく抑えることにより、消費電流が小さくてすむ。また、オフセット補償回路を設けたので、出力電位を入力電位に一致させることができる。

【図面の簡単な説明】

【0009】

【図1】この発明の実施の形態1によるカラー液晶表示装置の全体構成を示すブロック図である。

【図2】図1に示した各液晶セルに対応して設けられた液晶駆動回路の構成を示す回路図である。

【図3】図1に示した水平走査回路の要部を示す回路ブロック図である。

【図4】図3に示した駆動回路の構成を示す回路図である。

【図5】図4に示した駆動回路の動作を説明するための回路図である。

【図6】図4に示した駆動回路の動作を説明するためのタイムチャートである。

【図7】実施の形態1の変更例を示す回路図である。

【図8】実施の形態1の他の変更例を示す回路図である。

【図9】実施の形態1のさらに他の変更例を示す回路図である。

【図10】この発明の実施の形態2による駆動回路のレベルシフト回路の構成を示す回路図である。

【図11】この発明の実施の形態3による駆動回路のレベルシフトの構成を示す回路図である。

【図12】この発明の実施の形態4による駆動回路のレベルシフト回路の構成を示す回路図である。

【図13】この発明の実施の形態5による駆動回路のレベルシフト回路の構成を示す回路図である。

【図14】実施の形態1の問題点を説明するための図である。

【図15】実施の形態1の問題点を説明するための回路図である。

【図16】実施の形態6の原理を説明するための回路図である。

【図17】この発明の実施の形態6による駆動回路の構成を示す回路図である。

【図18】図17に示した駆動回路の構成をより詳細に示す回路図である。

【図19】実施の形態6の変更例を示す回路図である。

【図20】実施の形態6の他の変更例を示す回路図である。

【図21】実施の形態6のさらに他の変更例を示す回路図である。

【図22】この発明の実施の形態7による駆動回路の構成を示す回路図である。

【図23】図22に示した駆動回路の動作を示すタイムチャートである。

【図24】実施の形態7の変更例を示す回路図である。

【図25】この発明の実施の形態8による駆動回路の構成を示す回路図である。

【図26】実施の形態8の変更例を示す回路図である。

【図27】実施の形態8の他の変更例を示す回路図である。

【図28】実施の形態8のさらに他の変更例を示す回路図である。

【図29】実施の形態8のさらに他の変更例を示す回路図である。

【図30】実施の形態8のさらに他の変更例を示す回路図である。

【図31】この発明の実施の形態9による駆動回路の構成を示す回路図である。

【図32】図31に示した駆動回路の動作を示すタイムチャートである。

【図33】実施の形態9の変更例を示す回路図である。

【図34】この発明の実施の形態10による駆動回路の構成を示す回路図である。

【図35】実施の形態10の変更例を示す回路図である。

【図36】この発明の実施の形態11による駆動回路の構成を示す回路図である。

【図37】図36に示した駆動回路の構成を示す回路図である。

【図38】この発明の実施の形態12によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図39】図38に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図40】この発明の実施の形態13によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図41】図40に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図42】図40に示したオフセット補償機能付駆動回路の動作を示す他のタイムチャートである。

【図43】実施の形態13の変更例を示す回路図である。

【図44】実施の形態13の他の変更例を示す回路図である。

【図45】実施の形態13のさらに他の変更例を示す回路図である。

【図46】実施の形態13のさらに他の変更例を示す回路図である。

【図47】実施の形態13のさらに他の変更例を示す回路図である。

【図48】実施の形態13のさらに他の変更例を示す回路図である。

【図49】実施の形態13のさらに他の変更例を示す回路図である。

【図50】実施の形態13のさらに他の変更例を示す回路図である。

【図51】実施の形態13のさらに他の変更例を示す回路図である。

【図52】実施の形態13のさらに他の変更例を示す回路図である。

【図53】実施の形態13のさらに他の変更例を示す回路図である。

【図54】実施の形態13のさらに他の変更例を示す回路図である。

【図55】この発明の実施の形態14によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図56】図55に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図57】図55に示したオフセット補償機能付駆動回路の動作を示す他のタイムチャートである。

【図58】この発明の実施の形態15によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図59】図58に示したオフセット補償機能付駆動回路の動作を示すタイムチャートである。

【図60】この発明の実施の形態16によるカラー液晶表示装置の要部を示す回路図である。

【図61】図60に示したカラー液晶表示装置に含まれるプッシュ型駆動回路の構成を示す回路図である。

【図62】図60に示したプッシュ型駆動回路の構成をより詳細に示す回路図である。

【図63】実施の形態16の変更例を示す回路図である。

【図64】実施の形態16の他の変更例を示す回路図である。

【図65】この発明の実施の形態17によるプル型駆動回路の構成を示す回路図である。

【図66】実施の形態17の変更例を示す回路図である。

【図67】この発明の実施の形態18による駆動回路の構成を示す回路ブロック図である。

【図68】実施の形態18の変更例を示す回路図である。

【図69】実施の形態18の他の変更例を示す回路図である。

【図70】実施の形態18のさらに他の変更例を示す回路図である。

【図71】図70に示した駆動回路の構成をより詳細に示す回路図である。

【図72】この発明の実施の形態19によるオフセット補償機能付プッシュ型駆動回路の構成を示す回路ブロック図である。

【図73】実施の形態20の変更例を示す回路図である。

【図74】この発明の実施の形態20によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図75】実施の形態20の変更例を示す回路図である。

【図76】実施の形態20の他の変更例を示す回路図である。

【図77】実施の形態20のさらに他の変更例を示す回路図である。

【図78】この発明の実施の形態21によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図79】この発明の実施の形態22によるオフセット補償機能付駆動回路の構成を示す回路ブロック図である。

【図80】従来の駆動回路の構成を示す回路図である。

【発明を実施するための形態】

【0010】

[実施の形態1]

図1は、この発明の実施の形態1によるカラー液晶表示装置の構成を示すブロック図である。図1において、このカラー液晶表示装置は、液晶パネル1、垂直走査回路7および水平走査回路8を備え、たとえば携帯電話機に設けられる。

【0011】

液晶パネル1は、複数行複数列に配列された複数の液晶セル2と、各行に対応して設けられた走査線4および共通電位線5と、各列に対応して設けられたデータ線6とを含む。

【0012】

液晶セル2は、各行において3つずつ予めグループ化されている。各グループの3つの液晶セル2には、それぞれR,G,Bのカラーフィルタが設けられている。各グループの3つの液晶セル2は、1つの画素3を構成している。

【0013】

各液晶セル2には、図2に示すように、液晶駆動回路10が設けられている。液晶駆動回路10は、N型トランジスタ11およびキャパシタ12を含む。N型トランジスタ11は、データ線6と液晶セル2の一方電極2aとの間に接続され、そのゲートは走査線4に接続される。キャパシタ12は、液晶セル2の一方電極2aと共通電位線5との間に接続される。液晶セル2の他方電極には駆動電位VDDが与えられ、共通電位線5には共通電位VSSが与えられる。

【0014】

図1に戻って、垂直走査回路7は、画像信号に従って、複数の走査線4を所定時間ずつ順次選択し、選択した走査線4を選択レベルの「H」レベルにする。走査線4が選択レベルの「H」レベルにされると、図2のN型トランジスタ11が導通し、その走査線4に対応する各液晶セル2の一方電極2aとその液晶セル2に対応するデータ線6とが結合される。

【0015】

水平走査回路8は、画像信号に従って、垂直走査回路7によって1本の走査線4が選択されている間に複数のデータ線6をたとえば12本ずつ順次選択し、選択した各データ線6に階調電位VGを与える。液晶セル2の光透過率は、階調電位VGのレベルに応じて変化する。

【0016】

垂直走査回路7および水平走査回路8によって液晶パネル1の全液晶セル2が走査されると、液晶パネル1には1つの画像が表示される。

【0017】

図3は、図1に示した水平走査回路8の要部を示す回路ブロック図である。図3において、水平走査回路8は、階調電位発生回路15および駆動回路20を含む。階調電位発生回路15および駆動回路20は、水平走査回路8によって同時に選択されるデータ線6の数(この場合は12)だけ設けられている。

【0018】

階調電位発生回路15は、第1電源電位V1(5V)のノードと第2電源電位V2(0V)のノードとの間に直列接続されたn+1個(ただし、nは自然数である)の抵抗素子16.1〜16.n+1と、n+1個の抵抗素子16.1〜16.n+1の間のn個のノードと出力ノード15aとの間にそれぞれ接続されたn個のスイッチ17.1〜17.nとを含む。

【0019】

n+1個の抵抗素子16.1〜16.n+1の間のn個のノードには、それぞれn段階の電位が現われる。スイッチ17.1〜17.nは、画像濃度信号φPによって制御され、それらのうちのいずれか1つのみが導通状態にされる。出力ノード15aには、n段階の電位のうちのいずれか1つの段階の電位が階調電位VGとして出力される。駆動回路20は、選択されたデータ線6が階調電位VGになるようにデータ線6に電流を供給する。

【0020】

図4は、駆動回路20の構成を示す回路図である。図4において、駆動回路20は、レベルシフト回路21,25、キャパシタ29、プルアップ回路30およびプルダウン回路33を含む。

【0021】

レベルシフト回路21は、第3電源電位V3(15V)のノードと接地電位GNDのノードとの間に直列接続された抵抗素子22、N型トランジスタ23およびP型トランジスタ24を含む。N型トランジスタ23のゲートは、そのドレイン(ノードN22)に接続されている。N型トランジスタ23は、ダイオード素子を構成する。P型トランジスタ24のゲートは、入力ノードN20に接続される。抵抗素子22の抵抗値は、トランジスタ23,24の導通抵抗値よりも十分大きな値に設定されている。

【0022】

入力ノードN20の電位(階調電位)をVIとし、P型トランジスタのしきい値電圧をVTPとし、N型トランジスタのしきい値電圧をVTNとすると、P型トランジスタ24のソース(ノードN23)の電位V23およびN型トランジスタ23のドレイン(ノードN22)の電位V22はそれぞれ次式(1)(2)で表わされる。

V23=VI+|VTP| …(1)

V22=VI+|VTP|+VTN …(2)

したがって、レベルシフト回路21は、入力電位VIを|VTP|+VTNだけレベルシフトさせた電位V22を出力する。

【0023】

レベルシフト回路25は、第4電源電位V4(5V)のノードと第5電源電位V5(−10V)との間に直列接続されたN型トランジスタ26、P型トランジスタ27および抵抗素子28を含む。N型トランジスタ26のゲートは、入力ノードN20に接続される。P型トランジスタ27のゲートは、そのドレイン(ノードN27)に接続される。P型トランジスタ27は、ダイオード素子を構成する。抵抗素子28の抵抗値は、トランジスタ26,27の導通抵抗値よりも十分大きな値に設定されている。

【0024】

N型トランジスタ26のソース(ノードN26)の電位V26およびP型トランジスタ27のドレイン(ノードN27)の電位V27は、それぞれ次式(3)(4)で表わされる。

V26=VI−VTN …(3)

V27=VI−VTN−|VTP| …(4)

したがって、レベルシフト回路25は、入力電位VIを−VTN−|VTP|だけレベルシフトさせた電位V27を出力する。

【0025】

キャパシタ29は、レベルシフト回路21の出力ノードN22とレベルシフト回路25の出力ノードN27との間に接続される。キャパシタ29は、ノードN22の電位変化をノードN27に伝達するとともに、ノードN27の電位変化をノードN22に伝達する。

【0026】

プルアップ回路30は、第6電源電位V6(15V)のノードと出力ノードN30との間に直列接続されたN型トランジスタ31およびP型トランジスタ32を含む。出力ノードN30には、負荷容量(データ線6の寄生容量)36が接続されている。N型トランジスタ31のゲートは、レベルシフト回路21の出力電位V22を受ける。P型トランジスタ32のゲートは、そのドレインに接続されている。P型トランジスタ30は、ダイオード素子を構成する。N型トランジスタ31は飽和領域で動作するように第6電源電位V6が設定されているので、N型トランジスタ31はいわゆるソースフォロア動作を行なう。

【0027】

今、説明の都合上、図5に示すように、P型トランジスタ32のドレイン(ノードN30′)と出力ノードN30との間が非導通状態にあると仮定する。N型トランジスタ31のソース(ノードN31)の電位V31およびP型トランジスタ32のドレイン(ノードN30′)の電位V30′は、それぞれ次式(5)(6)で表わされる。

V31=V22−VTN=VI+|VTP| …(5)

V30′=V31−|VTP|=VI …(6)

図4に戻って、プルダウン回路33は、第7電源電位V7(−10V)のノードと出力ノードN30との間に直列接続されたP型トランジスタ35およびN型トランジスタ34を含む。P型トランジスタ35のゲートは、レベルシフト回路25の出力電位V27を受ける。N型トランジスタ34のゲートは、そのドレインに接続されている。N型トランジスタ34は、ダイオード素子を構成する。P型トランジスタ35は飽和領域で動作するように第7電源電位V7が設定されているので、P型トランジスタ35はいわゆるソースフォロア動作を行なう。

【0028】

今、説明の都合上、図5に示すように、N型トランジスタ34のドレイン(ノードN30″)と出力ノードN30との間が非導通状態にあると仮定する。P型トランジスタ35のソース(ノードN34)の電位V34およびN型トランジスタ34のドレイン(ノードN30″)の電位V30″は、それぞれ次式(7)(8)で表わされる。

V34=V27+|VTP|=VI−VTN …(7)

V30″=V34+VTN=VI …(8)

数式(7)(8)は、P型トランジスタ32のドレイン(ノードN30′)とN型トランジスタ34のドレイン(ノードN30″)とを接続しても第6電源電位V6のノードと第7電源電位V7のノードとの間には電流は流れず、出力ノードN30の電位VOが入力ノードN20の電位VIと同じになることを示している。したがって、抵抗素子22,28の抵抗値を十分に大きくしておけば、VO=VIとなった定常状態では、貫通電流は極めて小さくなる。

【0029】

図6は、この駆動回路20の交流動作(遷移状態での動作)を説明するためのタイムチャートである。図6において、初期状態では、VI=VLとされているものとする。これにより、V22,V27,VOは、それぞれ以下のようになっている。

V22=VL+|VTP|+VTN

V27=VL−|VTP|−VTN

VO=VL

時刻t1においてVIがVLからVHに立上げられると、V22,V27,VOは所定時間の経過後にそれぞれ以下のようになる。

V22=VH+|VTP|+VTN

V27=VH−|VTP|−VTN

VO=VH

このレベル変化の過程で、以下の動作が行なわれる。レベルシフト回路25では、時刻t1において入力電位VIがVLからVHに立上げられると、N型トランジスタ26の駆動能力が高くなり、ノードN26の電位V26が急速に上昇する。これにより、P型トランジスタ27のソース−ゲート間電圧が大きくなってP型トランジスタ27の駆動能力も高くなり、ノードN27の電位V27が急速に上昇する。

【0030】

ノードN27の電位V27が急速に上昇すると、容量結合によってキャパシタ29を介してノードN22の電位V22がVH−VL分だけ急速に上昇する。これに応じて出力ノードN30の電位VOもVLからVHに急速に立上げられる。

【0031】

また時刻t2において入力電位VIがVHからVLに立下げられると、P型トランジスタ24の駆動能力が高くなり、ノードN23の電位V23が急速に低下する。これにより、N型トランジスタ23のゲート−ソース間電圧が大きくなってN型トランジスタ23の駆動能力も高くなり、ノードN22の電位V22が急速に低下する。

【0032】

ノードN22の電位V22が急速に低下すると、容量結合によってキャパシタ29を介してノードN27の電位V27がVH−VL分だけ急速に低下する。これに応じて出力ノードN30の電位VOもVHからVLに急速に立下げられる。

【0033】

この実施の形態1では、定常状態ではプルアップ回路30およびプルダウン回路33に貫通電流は流れず、抵抗素子22,28の抵抗値をトランジスタ23,24,26,27の導通抵抗値よりも十分高くすることによりレベルシフト回路21,25の貫通電流も小さくすることができるので、直流電流の低減化を図ることができる。また、キャパシタ29を設けたので、入力電位VIの変化に対しても迅速に応答することができる。

【0034】

以下、種々の変更例について説明する。図7の駆動回路36は、図4の駆動回路20からキャパシタ29を除去したものである。負荷容量36の容量値が比較的小さい場合は、トランジスタ23,24,26,27,31,32,34,35の寸法を小さくすることができる。トランジスタ23,27,31,35の寸法を小さくするとトランジスタ23,27,31,35のゲート容量が小さくなり、ノードN22,N27の寄生容量が小さくなる。したがって、キャパシタ29がなくても抵抗素子22,28を介して行われる充放電によってノードN22,N27の電位V22,V27の立上げおよび立下げが可能となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0035】

図8の駆動回路37は、図4の駆動回路20からダイオード接続されたトランジスタ23,27,32,34を除去したものである。出力電位VOは、VO=VI+|VTP|−VTNとなる。ただし、|VTP|≒VTNと設定すれば、VO≒VIとなる。あるいは、|VTP|−VTNの値をオフセット値として使用上考慮しておけば図4の駆動回路20と同様に使用することができる。この変更例では、トランジスタ23,27,32,34を除去したので、回路の占有面積を小さくすることができる。

【0036】

図9の駆動回路38は、図8の駆動回路37からさらにキャパシタ29を除去したものである。負荷容量36の容量値が比較的小さい場合は、トランジスタ24,26,31,35の寸法を小さくすることができ、ノードN22,N27の寄生容量を小さくすることができる。したがって、キャパシタ29がなくても抵抗素子22,28を介して行われる充放電によってノードN22,N27の電位V22,V27の立上げおよび立下げが可能となる。この変更例では、キャパシタ29を除去したので、回路の占有面積をさらに小さくすることができる。

【0037】

[実施の形態2]

実施の形態1では、同一極性のトランジスタのしきい値電圧はすべて同一であると仮定したが、実際には製造条件の変動などに起因してトランジスタのしきい値電圧にばらつきが生じる場合がある。トランジスタのしきい値電圧にばらつきが生じると、VI=VOにならなくなる。この実施の形態2では、この問題の解決を図る。

【0038】

図10は、この発明の実施の形態2による駆動回路のレベルシフト回路40の構成を示す回路図であって、図4のレベルシフト回路21と対比される図である。図10を参照して、このレベルシフト回路40が図4のレベルシフト回路21と異なる点は、N型トランジスタ23およびP型トランジスタ24がヒューズ41.1〜41.m(ただし、mは自然数である)、N型トランジスタ42.0〜42.mおよびP型トランジスタ43.0〜43.mで置換されている点である。

【0039】

ヒューズ41.1〜41mの各々は、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ41.1〜41.mの一方電極は、ともにノードN22に接続される。

【0040】

N型トランジスタ42.0〜42.mのゲート幅の和は、図4のN型トランジスタ23のゲート幅と同一に設定される。N型トランジスタ42.0のゲートおよびドレインは、ノードN22に接続される。N型トランジスタ42.1〜42.mのゲートおよびドレインは、それぞれヒューズ41.1〜41.mの他方電極に接続される。N型トランジスタ42.0〜42.mの各々は、ダイオード素子を構成する。

【0041】

P型トランジスタ43.0〜43.mのゲート幅の和は、図4のP型トランジスタ24のゲート幅と同一に設定される。P型トランジスタ43.0〜43.mは、それぞれN型トランジスタ42.0〜42.mのソースと接地電位GNDのノードとの間に接続され、それらのゲートはともに入力電位VIを受ける。

【0042】

実施の形態1で説明したとおり、ノードN22の電位V22はほとんどトランジスタ42.0〜42.m,43.0〜43.mのしきい値電圧で決まる。しかし、抵抗素子22の抵抗値に対してノードN22と接地電位GNDのノードとの間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに上昇する。したがって、レーザ光線によってヒューズ41.1〜41.mのうちの適切な数のヒューズを切断することにより、ノードN22の電位V22をわずかに上昇させることができ、トランジスタ42.0〜42.m,43.0〜43.mのしきい値電圧の絶対値が設計値よりも小さい場合でもノードN22の電位V22を補正することができる。

【0043】

なお、この実施の形態2では、N型トランジスタ23およびP型トランジスタ24の両方をm+1個に分割したが、N型トランジスタ23およびP型トランジスタ24の一方のみをm+1個に分割してもよいし、N型トランジスタ23およびP型トランジスタ24のうちの一方をm+1個に分割し他方をたとえば2個に分割してもよい。具体的には、図10のP型トランジスタ43.1〜43.mのソースを短絡してP型トランジスタ43.1〜43.mを1つのP型トランジスタにしてもよい。また、ヒューズ41.1〜41.mをそれぞれN型トランジスタ42.1〜42.mのソースとP型トランジスタ43.1〜43.mのソースとの間に接続するとともに、N型トランジスタ42.1〜42.mのソースを短絡してN型トランジスタ42.1〜42.mを1つのN型トランジスタにしてもよい。

【0044】

[実施の形態3]

図11は、この発明の実施の形態3による駆動回路のレベルシフト回路45の構成を示す回路図であって、図4のレベルシフト回路25と対比される図である。図11を参照して、このレベルシフト回路45が図4のレベルシフト回路25と異なる点は、N型トランジスタ26およびP型トランジスタ27がヒューズ46.1〜46.m、N型トランジスタ47.0〜47.mおよびP型トランジスタ48.0〜48.mで置換されている点である。

【0045】

ヒューズ46.1〜46.mの各々は、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ46.1〜46.mの一方電極は、ともに第4電源電位V4のノードに接続される。

【0046】

N型トランジスタ47.0〜47.mのゲート幅の和は、図4のN型トランジスタ26のゲート幅と同一に設定される。N型トランジスタ47.0のドレインは第4電源電圧V4のノードに接続され、そのゲートは入力電位VIを受ける。N型トランジスタ47.1〜47.mのドレインはそれぞれヒューズ46.1〜46.mの他方電極に接続され、そのゲートはともに入力電位VIを受ける。

【0047】

P型トランジスタ48.0〜48.mのゲート幅の和は、図4のP型トランジスタ27のゲート幅と同一に設定される。P型トランジスタ48.0〜48.mはそれぞれN型トランジスタ47.0〜47.mのソースとノードN27との間に接続され、それらのゲートはともにノードN27に接続される。P型トランジスタ48.0〜48.mの各々は、ダイオード素子を構成する。

【0048】

実施の形態1で説明したとおり、ノードN27の電位V27はほとんどトランジスタ47.0〜47.m,48.0〜48.mのしきい値電圧で決まる。しかし、抵抗素子28の抵抗値に対して第4電源電位V4のノードとノードN27との間の抵抗値を大きくしていくと、それに応じてノードN27の電位V27がわずかに低下する。したがって、レーザ光線によってヒューズ46.1〜46.mのうちの適切な数のヒューズを切断することにより、ノードN27の電位V27をわずかに低下させることができ、トランジスタ47.0〜47.m,48.0〜48.mのしきい値電圧の絶対値が設計値よりも小さい場合でもノードN27の電位V27を補正することができる。

【0049】

なお、この実施の形態3では、N型トランジスタ26およびP型トランジスタ27の両方をm+1個に分割したが、N型トランジスタ26およびP型トランジスタ27の一方のみをm+1個に分割してもよいし、N型トランジスタ26およびP型トランジスタ27のうちの一方をm+1個に分割し他方をたとえば2個に分割してもよい。具体的には、図11のP型トランジスタ48.1〜48.mのソースを短絡してP型トランジスタ48.1〜48.mを1つのP型トランジスタにしてもよい。また、ヒューズ41.1〜41.mをそれぞれN型トランジスタ47.1〜47.mのソースとP型トランジスタ48.1〜48.mのソースとの間に接続するとともに、N型トランジスタ47.1〜47.mのソースを短絡してN型トランジスタ47.1〜47.mを1つのN型トランジスタにしてもよい。

【0050】

また、実施の形態2と3を組合せ、図4のレベルシフト回路21,25をそれぞれレベルシフト回路40,45で置換してもよいことはいうまでもない。

【0051】

[実施の形態4]

図12は、この発明の実施の形態4による駆動回路のレベルシフト回路50の構成を示す回路図であって、図4のレベルシフト回路21と対比される図である。図12を参照して、このレベルシフト回路50が図4のレベルシフト回路21と異なる点は、抵抗素子22が抵抗素子51.0〜51.i(ただし、iは自然数である)およびヒューズ52.1〜52.iで置換されている点である。

【0052】

抵抗素子51.0〜51.iの抵抗値の和は、図4の抵抗素子22の抵抗値とほぼ同一に設定されている。抵抗素子51.0〜51.iは、第3電源電位V3のノードとノードN22との間に直列接続される。

【0053】

ヒューズ52.1〜52.iは、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ52.1〜52.iは、それぞれ抵抗素子51.1〜51.iに並列接続される。

【0054】

実施の形態1で説明したとおり、ノードN22の電位V22はほとんどトランジスタ23,24のしきい値電圧で決まる。しかし、トランジスタ23,24の導通抵抗値に対して第3電源電位V3のノードとノードN22との間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに低下する。したがって、レーザ光線によってヒューズ52.1〜52.iのうちの適切な数のヒューズを切断することにより、ノードN22の電位V22をわずかに低下させることができ、トランジスタ23,24のしきい値電圧の絶対値が設計値より高い場合でもノードN22の電位V22を補正することができる。

【0055】

[実施の形態5]

図13は、この発明の実施の形態5による駆動回路のレベルシフト回路55の構成を示す回路図であって、図4のレベルシフト回路25と対比される図である。図13を参照して、このレベルシフト回路55が図4のレベルシフト回路25と異なる点は、抵抗素子28が抵抗素子56.0〜56.iおよびヒューズ57.1〜57.iで置換されている点である。

【0056】

抵抗素子56.0〜56.iの抵抗値の和は、図4の抵抗素子28の抵抗値とほぼ同一の設定されている。抵抗素子56.0〜56.iは、ノードN27と第5電源電位V5のノードとの間に直列接続される。

【0057】

ヒューズ57.1〜57.iは、トランジスタ相互間を接続するのに用いられるアルミ配線などで形成されている。ヒューズ57.1〜57.iは、それぞれ抵抗素子56.1〜56.iに並列接続される。

【0058】

実施の形態1で説明したとおり、ノードN27の電位V27はほとんどトランジスタ26,27のしきい値電圧で決まる。しかし、トランジスタ26,27の導通抵抗値に対してノードN27と第5電源電位V5のノードとの間の抵抗値を大きくしていくと、それに応じてノードN22の電位V22がわずかに上昇する。したがって、レーザ光線によってヒューズ57.1〜57.iのうちの適切な数のヒューズを切断することにより、ノードN27の電位V27をわずかに上昇させることができ、トランジスタ26,27のしきい値電圧の絶対値が設計値よりも高い場合でもノードN22の電位V22を補正することができる。

【0059】

また、実施の形態4と5を組合せ、図4のレベルシフト回路21,25をそれぞれレベルシフト回路50,55で置換してもよいことはいうまでもない。

【0060】

また、以上の実施の形態1〜5において、電界効果トランジスタはMOSトランジスタでもよいし、TFT(薄膜トランジスタ)でもよい。また、抵抗素子は、高融点金属で形成してもよいし、不純物拡散層で形成してもよいし、占有面積低減化のために電界効果トランジスタで形成してもよい。また、以上の駆動回路は、液晶表示装置およびそれ以外の装置において、階調電位を伝達するだけでなく、入力されたアナログ電位と同電位になるように出力ノードの電位を制御するアナログバッファとして使用可能であることはいうまでもない。

【0061】

[実施の形態6]

駆動回路の特性としては、図14の特性線Aのように、入力電位VIと出力電位VOが等しくなることが理想的である。しかし、実施の形態1〜5で示した駆動回路の特性は、図14の特性線Bのようになり、VOの理想値と実際値の差ΔVはVIの増大に従って増大する。

【0062】

この理由は、以下のとおりである。図15に示すレベルシフト回路21′では、抵抗素子22の抵抗値をR、抵抗素子22およびP型トランジスタ24に流れる電流の値をi、P型トランジスタ24の電流増幅率をβとすると、次式(9)(10)が成り立つ。

V22=VDD−Ri …(9)

i=(VI−VTP−V22)2β/2 …(10)

ここで、Rβ/2=Kとすると、V22は次式(11)で表わされる。

【0063】

【数1】

【0064】

この式(11)より、VIの増大に従って、V22の理想値VI−VTPと実際の値との差が増大することがわかる。このため、V4の理想値は実際の値との差ΔVもVIの増大に従って大きくなる。

【0065】

この問題点を解消するため、この実施の形態6では、図16に示すように、抵抗素子22が定電流源62で置換される。図16のレベルシフト回路では、次式(12)が成り立つ。

i=(VI−VTB−V22)2β/2 …(12)

この式(12)より次式(13)が導かれる。

【0066】

【数2】

【0067】

したがって、図16のレベルシフト回路では、V22の理想値VI−VTPと実際値の差はVIに関係なく一定になる。また、βの値を定電流値iよりも十分に大きくすることにより、VOを理想値VI−VTPに略等しくすることができる。以下、この実施の形態6の駆動回路60について具体的に説明する。

【0068】

図17は、この発明の実施の形態6による駆動回路60の構成を示す回路図である。図17を参照して、この駆動回路60が図4の駆動回路20と異なる点は、レベルシフト回路21,25がそれぞれレベルシフト回路61,63で置換されている点である。レベルシフト回路61はレベルシフト回路21の抵抗素子22を定電流源62で置換し、レベルシフト回路63はレベルシフト回路25の抵抗素子28を定電流源64で置換したものである。

【0069】

定電流源62は、図18に示すように、P型トランジスタ65,66および抵抗素子67を含む。P型トランジスタ65は第3電源電圧V3のラインとノードN22との間に接続され、P型トランジスタ66および抵抗素子67は第3電源電位3のラインと接地電位GNDのラインとの間に直列接続される。P型トランジスタ65,66のゲートは、ともにP型トランジスタ66のドレインに接続される。P型トランジスタ65,66は、カレントミラー回路を構成する。P型トランジスタ66および抵抗素子67には抵抗素子67の抵抗値に応じた値の定電流が流れ、P型トランジスタ65にはP型トランジスタ66に流れる定電流の値に応じた値の定電流が流れる。なお、抵抗素子67の一方電極は接地電位GNDのラインに接続されているが、第3電源電位V3からP型トランジスタ66のしきい値電圧の絶対値|VTP|を減算した電位よりも低い他の電源電位のラインに抵抗素子67の一方電極を接続してもよい。また、定電流源としてトランジスタ65,66および抵抗素子67の代りに、ゲートとソースを互いに接続したデプレッション型のトランジスタを第3電源電位V3のラインとノードN22との間に設けてもよい。

【0070】

また定電流源64は、抵抗素子68およびN型トランジスタ69,70を含む。抵抗素子68およびN型トランジスタ69は第4電源電位V4のラインと第5電源電位V5のラインとの間に直列接続され、N型トランジスタ70はノードN27と第5電源電位V5のラインとの間に接続される。N型トランジスタ69,74のゲートは、ともにN型トランジスタ69のドレインに接続される。N型トランジスタ69,70は、カレントミラー回路を構成する。抵抗素子68およびN型トランジスタ69には抵抗素子68の抵抗値に応じた値の定電流が流れ、N型トランジスタ70にはN型トランジスタ69に流れる定電流の値に応じた値の定電流が流れる。なお、抵抗素子68の一方電極は第4電源電位V4に接続されているが、第5電源電位V5にN型トランジスタ69のしきい値電圧VTNを加算した電位よりも高い他の電源電位のラインに抵抗素子68の一方電極を接続してもよい。また、定電流源としてトランジスタ69,70および抵抗素子68の代りに、ゲートとソースを互いに接続したデプレッション型のトランジスタを第5電源電位V5のラインとノードN27との間に設けてもよい。他の構成および動作は、図4の駆動回路20と同じであるので、その説明は繰返さない。

【0071】

この実施の形態6では、図4の駆動回路20の抵抗素子22,28をそれぞれ定電流源62,64で置換したので入力電位VIの値に関係なく、入力電位VIに等しい出力電位VOを得ることができる。

【0072】

以下、この実施の形態6の種々の変更例について説明する。図19の駆動回路71は、図18の駆動回路60からキャパシタ29を除去したものである。この変更例は、負荷容量36の容量値が比較的小さい場合に有効となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0073】

図20の駆動回路72は、図18の駆動回路60からN型トランジスタ23,34およびP型トランジスタ27,32を除去したものである。この変更例では、トランジスタ23,27,32,34を除去したので、回路の占有面積を小さくすることができる。ただし、出力電位VOは、VO=VI+|VTP|−VTNとなる。

【0074】

図21の駆動回路73は、図20の駆動回路72からキャパシタ29を除去したものである。この変更例は、負荷容量36の容量値が比較的小さい場合に有効となる。この変更例では、キャパシタ29を除去したので、回路の占有面積が小さくてすむ。

【0075】

[実施の形態7]

たとえば図4の駆動回路20において、負荷容量36を充放電する際、トランジスタ31,32,34,35の各々はいわゆるソースフォロア動作を行なう。その際、出力電位VOが入力電位VIに近づくにつれてトランジスタ31,32,34,35の各々のゲート−ソース間電圧が小さくなり、トランジスタ31,32,34,35の電流駆動能力が低下する。トランジスタ32,34についてはそれらのゲート電極幅を広くすることによって駆動能力の低下を防ぐことが可能になるが、トランジスタ31,35のゲート電極幅を広くするとゲート容量が増大し、駆動回路20の動作速度が低下してしまう。この実施の形態7では、この問題の解決が図られる。

【0076】

図22は、この発明の実施の形態7による駆動回路75の構成を示す回路図である。図22を参照して、この駆動回路75は、図19の駆動回路71にキャパシタ76,77を追加したものである。キャパシタ76の一方電極は昇圧信号φBを受け、その他方電極はノードN22に接続される。キャパシタ77の一方電極は昇圧信号φBの相補信号/φBを受け、その他方電極はノードN27に接続される。

【0077】

図23は、図22に示した駆動回路75の動作を示すタイムチャートである。図23では、理解を容易にするため、ノードN22,N27の電位V22,V27および出力電位VOの遷移時間が実際よりも長く示されている。時刻t1において、入力電位VIが「L」レベルVLから「H」レベルVHに立上げられると、電位V22,V27,VOの各々が徐々に上昇する。上述のとおり、電位V22,V27,VOの各々は、電位変化の周期は比較的速く立上がるが、最終レベルに近づくにつれて上昇速度が遅くなる。

【0078】

時刻t1から所定時間経過後の時刻t2において、昇圧信号φBが「H」レベルに立上げられるとともに信号/φBが「L」レベルに立下げられる。信号φBが「H」レベルに立上げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ上昇する。信号/φBが「L」レベルに立下げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電位ΔV2だけ低下する。このとき、出力ノードN30に「H」レベルVHを出力する動作を行なっており、N型トランジスタ31の導通抵抗値の方がP型トランジスタ35の導通抵抗値よりも低くなっているので、V22によるレベル上昇作用の方がV27によるレベル降下作用よりも強く働き、出力電位VOは時刻t2から急速に上昇する(V22を昇圧しない場合は破線で示すようになる)。

【0079】

昇圧された電位V22は、ノードN22からトランジスタ23,24を介して接地電位GNDのラインに電流が流出することにより、VI+|VTP|+VTNまで低下する。また降圧された電位V27は、第4電源電圧V4のラインからトランジスタ26,27を介してノードN27に電流が流入することにより、VI−|VTP|−VTNまで上昇する。

【0080】

時刻t3において、昇圧信号φBが「L」レベルに立下げられるとともに信号/φBが「H」レベルに立上げられる。信号φBが「L」レベルに立下げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ低下する。また信号/φBが「H」レベルに立上げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電圧ΔV2だけ上昇する。V22がΔV1だけ低下してもプルアップ回路30には出力電位VOを低下させる能力がなく、V27がΔV2だけ上昇してもプルダウン回路33には出力電位VOを上昇させる能力がないので、出力電位VOは変化しない。

【0081】

降圧された電位V22は、第3電源電位V3のラインからP型トランジスタ65を介してノードN22に電流が流入することにより、VI+|VTP|+VTNまで上昇する。ただし、低消費電力化のためP型トランジスタ65の電流駆動能力が小さく設定されているので、ノードN22の電位V22が本来のレベルVI+|VTP|+VTNに上昇するのに必要な時間は、V22がそのレベルVI+|VTP|+VTNに低下するのに必要な時間よりも長くなる。

【0082】

また昇圧された電位V27は、ノードN27からN型トランジスタ70を介して第5電源電位V5のラインに電流が流出することにより、VI−VTN−|VTP|まで低下する。ただし、低消費電力化のためN型トランジスタの電流駆動能力は小さく設定されているので、ノードN27の電位V27が本来のレベルVI−VTN−|VTP|に低下するのに必要な時間は、V22がそのレベルVI−VTN−|VTP|に上昇するのに必要な時間よりも長くなる。

【0083】

次に時刻t4において、入力電位VIが「H」レベルVHから「L」レベルVLに立下げられると、電位V22,V27,V4の各々が徐々に低下する。電位V22,V27,V4の各々は、電位変化の初期は比較的速く立下がるが、最終レベルに近づくにつれて下降速度が遅くなる。

【0084】

時刻t4から所定時間経過後の時刻t5において、昇圧信号φBが「H」レベルに立上げられるとともに信号/φBが「L」レベルに立下げられる。信号φBが「H」レベルに立上げられると、キャパシタ76を介して容量結合により、ノードN22の電位V22が所定電圧ΔV1だけ上昇する。信号/φBが「L」レベルに立下げられると、キャパシタ77を介して容量結合により、ノードN27の電位V27が所定電位ΔV2だけ低下する。このとき、出力ノードN30に「L」レベルVLを出力する動作を行なっており、P型トランジスタ35の導通抵抗値の方がN型トランジスタ31の導通抵抗値よりも低くなっているので、V27によるレベル下降作用の方がV22によるレベル上昇作用よりも強く働き、出力電位VOは時刻t5から急速に低下する(V27を降圧しない場合は破線で示すようになる)。

【0085】

昇圧された電位V22は、ノードN22からトランジスタ23,24を介して接地電位GNDのラインに電流が流出することにより、VI+|VTP|+VTNまで低下する。また降圧された電位V27は、第4電源電圧V4のラインからトランジスタ26,27を介してノードN27に電流が流入することにより、VI−|VTP|−VTNまで上昇する。

【0086】