駆動回路

【課題】駆動電圧を調整可能な駆動回路を提供すること。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

【解決手段】駆動回路10は、チャージポンプ回路部14を備えている。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、キャパシタC1に充電された充電電圧に基づいて駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成する。チャージポンプ回路部14では、指示信号S1に基づいてキャパシタC1に充電される充電電圧が調整可能に構成されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スイッチング素子を駆動する駆動回路に関する。

【背景技術】

【0002】

スイッチング素子は、駆動電圧を用いて特定機能を発揮することが可能な素子であり、様々な用途で広く用いられている。スイッチング素子の一例には、絶縁ゲートを備えるスイッチング素子が知れられている。この種のスイッチング素子は、ゲート電圧に基づいて電流量を制御するものであり、例えば、直流電圧を変圧するコンバータ装置、直流電圧と交流電圧の間で変換するインバータ装置に用いられている。この種のスイッチング素子の一例には、IGBT(Insulated Gate Bipolar Transistor)、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)を含むパワー半導体素子が挙げられる。

【0003】

このようなスイッチング素子のオン・オフを切換えるために、駆動回路が用いられている。例えば、駆動回路は、スイッチング素子のオンを指示する制御信号に基づいて、スイッチング素子のゲートに駆動電圧を印加してスイッチング素子のゲート電圧を上昇させる。

【0004】

この種の駆動回路では、スイッチング素子のターンオンを高速化し、スイッチング損失を低減することが望まれている。特許文献1には、スイッチング素子のターンオンを高速化するために、チャージポンプ回路部を備えた駆動回路が開示されている。この駆動回路では、スイッチング素子がターンオンする遷移期間の初期段階において、チャージポンプ回路部のキャパシタに充電された充電電圧と駆動電源の電圧を合計した駆動電圧を用いてスイッチング素子を駆動するので、スイッチング素子のターンオンが高速化される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−200560号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の技術では、チャージポンプ回路部のキャパシタを充電するときに、キャパシタに対して駆動電源が直接的に接続される。このため、キャパシタに充電される充電電圧は、駆動電源の電圧に依存した固定値である。特許文献1の技術では、駆動電源の電圧に依存した駆動電圧しか生成することができない。

【0007】

本明細書で開示される技術は、チャージポンプ回路部を備えた駆動回路において、自由度の高い駆動回路を実現することを目的としている。

【課題を解決するための手段】

【0008】

本明細書で開示される駆動回路は、切換え制御回路部とチャージポンプ回路部を備えている。切換え制御回路部は、スイッチング素子のゲートに駆動電圧を印加する状態と印加しない状態を切換える。チャージポンプ回路部は、スイッチング素子がターンオンする遷移期間の初期段階において、キャパシタに充電された充電電圧に基づいて駆動電源の電圧を昇圧して駆動電圧を生成し、その駆動電圧を切換え制御回路部に提供する。チャージポンプ回路部は、指示信号に基づいてキャパシタに充電される充電電圧を調整可能に構成されていることを特徴としている。本明細書で開示される駆動回路では、指示信号を利用してチャージポンプ回路部のキャパシタに充電される充電電圧を独立して調整可能であり、これにより、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧の大きさも独立して調整可能である。本明細書で開示される駆動回路は、指示信号を利用して、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧を柔軟に制御することができる。

【0009】

チャージポンプ回路部は、複数のキャパシタを有していてもよい。この場合、チャージポンプ回路部は、選択信号に基づいて複数のキャパシタから選択されたキャパシタを充電する。この態様の駆動回路では、指示信号と選択信号の双方を利用してスイッチング素子がターンオンする遷移期間の初期段階の駆動電圧をより高精度に制御することができる。

【0010】

チャージポンプ回路部は、ミラー期間が終了するまでに、キャパシタに蓄積された電荷を放電してもよい。この態様の駆動回路では、スイッチング素子がターンオンする遷移期間において、スイッチング素子のゲート電圧が過度に昇圧されることが抑制され、スイッチング素子のゲート絶縁膜の信頼性悪化を抑えることができる。

【発明の効果】

【0011】

本明細書で開示される技術によると、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧を独立して調整することができる。

【図面の簡単な説明】

【0012】

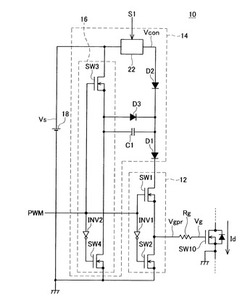

【図1】第1実施形態の駆動回路の構成を示す。

【図2A】可変電圧生成部の入力と出力の関係の一例を示す。

【図2B】可変電圧生成部の入力と出力の関係の他の一例を示す。

【図2C】可変電圧生成部の入力と出力の関係の他の一例を示す。

【図3】第1実施形態の駆動回路において、各構成要素及び電圧のタイミングチャートを示す。

【図4】第1実施形態の駆動回路において、メインスイッチング素子のゲートに駆動電圧を印加し、ゲートに電荷を充電するモードを示す(指示信号が入力しない場合)。

【図5】第1実施形態の駆動回路において、メインスイッチング素子のゲートから電荷を放電するモードを示す。

【図6】第1実施形態の駆動回路において、第1キャパシタに電荷を充電するモードを示す。

【図7】第1実施形態の駆動回路において、メインスイッチング素子のゲートに駆動電圧を印加し、ゲートに電荷を充電するモードを示す(指示信号が入力する場合)。

【図8】第1実施形態の駆動回路において、メインスイッチング素子がターンオンする遷移期間の駆動電圧及びゲート電圧のタイミングチャートの詳細を示す。

【図9】第2実施形態の駆動回路の構成を示す。

【図10】第2実施形態の駆動回路において、選択信号と各スイッチング素子の動作と選択されたキャパシタの容量の対応関係を示す。

【発明を実施するための形態】

【0013】

(第1実施形態)

図1に、車両用のインバータ装置に搭載されるメインスイッチング素子SW10(請求項に記載のスイッチング素子の一例)を駆動する駆動回路10の回路図を示す。一例では、メインスイッチング素子SW10には、nチャネル型のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が用いられており、その半導体材料には炭化珪素又は窒化ガリウム系のワイドバンドギャップの化合物半導体が用いられている。駆動回路10は、メインスイッチング素子SW10のゲート電極に対して電荷を充電又はゲート電極から電荷を放電させることで、ゲート電極のゲート電圧Vgを上昇又は降下させる。このような駆動回路10は、メインスイッチング素子SW10のゲート電圧Vgを制御することで、メインスイッチング素子SW10を流れるドレイン電流Idを制御する。

【0014】

駆動回路10は、切換え制御回路部12とチャージポンプ回路部14を備えている。切換え制御回路部12は、PWM信号に基づいて、メインスイッチング素子SW10のゲートに駆動電圧Vgprを印加する状態と駆動電圧Vgprを印加しない状態を切換える。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成し、その駆動電圧Vgprを切換え制御回路部12に提供する。

【0015】

切換え制御回路部12は、第1スイッチング素子SW1と第2スイッチング素子SW2と第1インバータINV1を有している。第1スイッチング素子SW1と第2スイッチング素子SW2は直列に接続されている。第1スイッチング素子SW1は、nチャネル型のMOSFETであり、ドレインがチャージポンプ回路部14に接続されており、ソースが第2スイッチング素子SW2に接続されている。第1スイッチング素子SW1のゲートには、PWM信号が入力している。第2スイッチング素子SW2は、nチャネル型のMOSFETであり、ドレインが第1スイッチング素子SW1に接続されており、ソースが接地されている。第2スイッチング素子SW2のゲートには、第1インバータINV1で反転したPWM信号が入力している。第1スイッチング素子SW1のソースと第2スイッチング素子SW2のドレインの接続点が、メインスイッチング素子SW10のゲート抵抗Rgに接続されている。

【0016】

チャージポンプ回路部14は、第1チャージポンプ制御回路部16と、第1ダイオードD1と第2ダイオードD2と第3ダイオードD3と第1キャパシタC1と可変電圧生成部22を有している。第1チャージポンプ制御回路部16は、第3スイッチング素子SW3と第4スイッチング素子SW4と第2インバータINV2を有している。第3スイッチング素子SW3と第4スイッチング素子SW4は直列に接続されている。第3スイッチング素子SW3は、nチャネル型のMOSFETであり、ドレインが駆動電源18の正極に接続されており、ソースが第4スイッチング素子SW4に接続されている。第3スイッチング素子SW3のゲートには、PWM信号が入力している。第4スイッチング素子SW4は、nチャネル型のMOSFETであり、ドレインが第3スイッチング素子SW3に接続されており、ソースが接地されている。第4スイッチング素子SW4のゲートには、第2インバータINV2で反転したPWM信号が入力している。

【0017】

第1ダイオードD1と第2ダイオードD2は、制御回路部12と可変電圧生成部22の間で直列に接続されており、第1ダイオードD1のカソードが制御回路部12の第1スイッチング素子SW1のドレインに接続されており、第2ダイオードD2のアノードが可変電圧生成部22に接続されている。第3ダイオードD3は、カソードが第1ダイオードD1のアノードと第2ダイオードD2のカソードの接続点に接続されており、アノードが第3スイッチング素子SW3のソースと第4スイッチング素子SW4のドレインの接続点に接続されている。第1キャパシタC1は、一端が第1ダイオードD1のアノードと第2ダイオードD2のカソードの接続点に接続されており、他端が第3スイッチング素子SW3のソースと第4スイッチング素子SW4のドレインの接続点に接続されている。可変電圧生成部22は、駆動電源18の正極と第2ダイオードD2のアノードの間に接続されている。

【0018】

可変電圧生成部22は、駆動電源18の電圧Vsと外部からの指示信号S1が入力可能に構成されている。可変電圧生成部22は、指示信号S1に基づいて駆動電源18の電圧Vsを変圧し、その変圧された電圧を制御電圧Vconとして出力する。可変電圧生成部22は、指示信号S1が入力しないときには制御電圧Vconを出力しないように構成されている。一例として、可変電圧生成部22には、可変抵抗素子を利用した可変電圧回路を利用することができる。

【0019】

可変電圧生成部22に入力する指示信号S1と出力される制御電圧Vconの関係は、図2A〜Cに例示される。図2A及び図2Bに示されるように、可変電圧生成部22に入力する指示信号S1は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idであってもよい。図2Aの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idの変動に応じて、単調に追随する制御電圧Vconを出力する。具体的には、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idが上昇すると、単調に減少する制御電圧Vconを出力する。図2Bの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idが予め決められた複数の範囲に応じて、複数の離散した制御電圧Vconを出力する。具体的には、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tjが相対的に高いときに又はドレイン電流Idが相対的に大きいときに、相対的に低い制御電圧Vconを出力する。あるいは、図2Cに示されるように、可変電圧生成部22に入力する指示信号S1は、メインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsであってもよい。図2Cの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsに応じて、テーブル制御された制御電圧Vconを出力する。

【0020】

次に、図3のタイミングチャート及び図4〜図7の各モードを参照し、駆動回路10の動作を説明する。

【0021】

(可変電圧生成部22に指示信号S1が入力しない場合)

図3に示されるように、タイミングT1でPWM信号が立上がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオンし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオフする。これにより、図4に示されるように、第3スイッチング素子SW3、第3ダイオードD3、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。駆動電圧Vgprは、概ね駆動電源18の電圧Vsから第3ダイオードD3と第1ダイオードD1の順方向降下電圧を引いた値となる。図3に示されるように、メインスイッチング素子SW10のゲート電圧Vgは、タイミングT1で駆動電圧Vgprの印加が開始してから、タイミングT2で定常状態になるまで上昇する。メインスイッチング素子SW10のゲート電圧Vgが閾値を超えると、メインスイッチング素子SW10がターンオンする。なお、メインスイッチング素子SW10のスイッチング損失は、駆動電圧Vgprの印加が開始するタイミングT1からゲート電圧Vgが定常状態となるタイミングT2までの時間に強く依存する。メインスイッチング素子SW10のスイッチング損失を低減するためには、この時間を短縮することが肝要である。

【0022】

次に、図3に示されるように、タイミングT3でPWM信号が立下がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンする。これにより、図5に示されるように、メインスイッチング素子SW10のゲート電極に充電されていた電荷は、ゲート抵抗Rgと第2スイッチング素子SW2を介して放電される。メインスイッチング素子SW10のゲート電圧Vgは、電荷の放電に応じて下降する。メインスイッチング素子SW10のゲート電圧Vgが閾値を下回ると、メインスイッチング素子SW10がターンオフする。

【0023】

(可変電圧生成部22に指示信号S1が入力する場合)

図3に示されるように、PWM信号がローのときに(第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンのときに)、タイミングT4で可変電圧生成部22に指示信号S1が入力する。可変電圧生成部22は、指示信号S1に応じて制御電圧Vconを出力する。これにより、図6に示されるように、第1キャパシタC1が充電される。すなわち、駆動回路10は、メインスイッチング素子SW10がオフのときに、指示信号S1に基づいて第1キャパシタC1を充電する。第1キャパシタC1の充電電圧VC1は、概ね可変電圧生成部22の制御電圧Vconから第2ダイオードD2の順方向降下電圧を引いた値である。

【0024】

次に、図3に示されるように、タイミングT5でPWM信号が立上がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオンし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオフする。これにより、図7に示されるように、第3スイッチング素子SW3、第1キャパシタC1、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。このとき、駆動電源18と第1キャパシタC1が直列に接続されることから、駆動電源18の電圧Vsが第1キャパシタC1の充電電圧VC1によって昇圧される。駆動電圧Vgprは、概ね駆動電源18の電圧Vsと第1キャパシタC1の充電電圧VC1の合計から第1ダイオードD1の順方向降下電圧を引いた値である。このように、第1キャパシタC1が予め充電されていることによって、駆動電圧Vgprは、駆動電源18の電圧Vsに対して概ね第1キャパシタC1の充電電圧VC1に応じて昇圧される。これにより、図3に示されるように、メインスイッチング素子SW10のゲート電圧Vgは、相対的に高速に上昇する(タイミングT1〜T2よりもタイミングT5〜T6が短い)。

【0025】

図8に、タイミングT5〜T6(メインスイッチング素子SW10がターンオンする遷移期間)の様子をより詳細に示す。駆動電圧Vgprは、メインスイッチング素子SW10のターンオンと同時に大きく立ち上がり、第1キャパシタC1に充電していた電荷がメインスイッチング素子SW10のゲート入力容量に移動するのに伴って減少する。駆動回路10では、第1キャパシタC1の容量がメインスイッチング素子SW10のゲート入力容量よりも小さく設定されているので、ミラー期間が終了するタイミングTmirrまでに、第1キャパシタC1に充電していた全ての電荷がメインスイッチング素子SW10のゲート入力容量に移動する。このため、駆動電圧Vgprは、ミラー期間が終了するタイミングTmirrまでに、第1キャパシタC1の充電電圧VC1に相当する部分が減少する。第1キャパシタC1に充電していた全ての電荷がメインスイッチング素子SW10のゲート入力容量に移動した後は、図4に示されるように、第3スイッチング素子SW3、第3ダイオードD3、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。この結果、駆動電圧Vgprは、概ね駆動電源18の電圧Vsから第3ダイオードD3と第1ダイオードD1の順方向降下電圧を引いた値となる。

【0026】

このように、駆動回路10では、メインスイッチング素子SW10がターンオンする遷移期間のうちのミラー期間において相対的に高い駆動電圧Vgprを印加し、ミラー期間の終了後には相対的に低い駆動電圧Vgprを印加する。このため、駆動回路10は、メインスイッチング素子SW10のスイッチング速度を高速化させながら、メインスイッチング素子SW10のゲート電極に過度な電圧が印加することを抑制することができる。駆動回路10は、メインスイッチング素子SW10のスイッチング損失を改善しながら、ゲート絶縁膜の信頼性悪化を抑制することができる。

【0027】

次に、図3に示されるように、タイミングT7でPWM信号が立下がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンする。これにより、図5に示されるように、メインスイッチング素子SW10のゲート電極に充電されていた電荷は、ゲート抵抗Rgと第2スイッチング素子SW2を介して放電される。メインスイッチング素子SW10のゲート電圧Vgは、電荷の放電に応じて下降する。メインスイッチング素子SW10のゲート電圧Vgが閾値を下回ると、メインスイッチング素子SW10がターンオフする。

【0028】

以下、駆動回路10の特徴を整理する。

(1)駆動回路10では、可変電圧生成部22が、外部からの指示信号S1に基づいて第1キャパシタC1に蓄積される電荷量を独立して調整可能に構成されていることを特徴としている。このため、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprも独立して調整可能である。駆動回路10は、外部からの指示信号S1を利用して、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprを柔軟に制御することができる。

【0029】

(2)通常、メインスイッチング素子SW10の特性は均一ではなく、様々なバラツキが存在している。例えば、メインスイッチング素子SW10には、ゲート電極の入力容量のバラツキ、温度特性上のバラツキが存在する。また、チャージポンプ回路部14の特性も均一ではなく、様々なバラツキが存在している。例えば、チャージポンプ回路部14には、第1キャパシタC1の容量のバラツキ、温度特性上のバラツキが存在する。駆動回路10では、図2A〜Cに例示されるように、指示信号S1にメインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsを利用することができる。これらの情報には、メインスイッチング素子SW10のバラツキが反映している。このため、可変電圧生成部22が指示信号S1に基づいて制御電圧Vconを制御することで、メインスイッチング素子SW10のバラツキに基づいて適宜に調整された駆動電圧Vgprを生成することができる。例えば、メインスイッチング素子SW10の素子温度Tjの上昇に伴ってメインスイッチング素子SW10のゲートの閾値電圧が低下してスイッチング速度が異常に高速化されるのを抑えるために、可変電圧生成部22が出力する制御電圧Vconを低く抑え、駆動電圧Vgprを低く抑えてメインスイッチング素子SW10のスイッチング速度を低速化することができる。また、メインスイッチング素子SW10のドレイン電流Idの増加に伴ってリカバリ電流が増加するのを抑えるために、可変電圧生成部22が出力する制御電圧Vconを低く抑え、駆動電圧Vgprを低く抑えてメインスイッチング素子SW10のドレイン電流Idを小さく抑えることができる。このように、駆動回路10は、指示信号S1を利用して駆動電圧Vgprを制御することにより、メインスイッチング素子SW10等のバラツキを補償することができる。

【0030】

(3)駆動回路10で駆動されるメインスイッチング素子SW10では、ターンオンの遷移期間の前半段階において相対的に高い駆動電圧Vgprを用いてゲート電圧Vgの立ち上がり速度が相対的に高速化されており、ターンオンの遷移期間の後半段階において相対的に低い駆動電圧Vgprを用いてゲート電圧Vgの立ち上がり速度が相対的に低速化されている。ターンオンの遷移期間の後半段階におけるゲート電圧Vgの立ち上がり速度は、メインスイッチング素子SW10のドレイン電流のサージ及びドレイン電流のリンギングに強く影響する。駆動回路10を用いると、ターンオンの遷移期間の後半段階におけるゲート電圧Vgの立ち上がり速度が低速化されているので、メインスイッチング素子SW10がターンオンするときのドレイン電流のサージ及びドレイン電流のリンギング現象が抑えられる。一方で、ターンオンの遷移期間の前半段階におけるゲート電圧Vgの立ち上がり速度が高速化されており、スイッチング損失の増大が抑えられている。

【0031】

(4)メインスイッチング素子SW10の半導体材料には、炭化珪素又は窒化ガリウム系のワイドバンドギャップの化合物半導体が用いられている。このようなワイドバンドギャップの化合物半導体で形成されるメインスイッチング素子SW10では、ドレイン電流のサージ及びドレイン電流のリンギングが特に問題となっている。したがって、駆動回路10は、ワイドバンドギャップの化合物半導体で形成されるメインスイッチング素子SW10を駆動する場合に特に有用である。

【0032】

(5)駆動回路10を構成する制御回路部12と第1チャージポンプ制御回路部16は、共通の回路構成である。これら回路部には、例えば、市販のゲート駆動用フォトカプラを利用することができる。また、駆動回路10を構成する可変電圧生成部22には、可変抵抗素子を利用した市販の可変電圧回路を利用することができる。このように駆動回路10を構成する各構成要素は、広く普及している汎用品を用いて構築することができる。

【0033】

(第2実施形態)

図9に示されるように、前述の駆動回路10と対比すると、駆動回路100は、第2チャージポンプ制御回路部17と第4ダイオードD4と第2キャパシタC2とを有していることを特徴としている。第2チャージポンプ制御回路部17は、第5スイッチング素子SW5と第6スイッチング素子SW6と第3インバータINV3を有している。第5スイッチング素子SW5と第6スイッチング素子SW6は直列に接続されている。第5スイッチング素子SW5は、nチャネル型のMOSFETであり、ドレインが駆動電源18の正極に接続されており、ソースが第6スイッチング素子SW6に接続されている。第6スイッチング素子SW6は、nチャネル型のMOSFETであり、ドレインが第5スイッチング素子SW5に接続されており、ソースが接地されている。

【0034】

第4ダイオードD4は、カソードが第1ダイオードD1と第2ダイオードD2の接続点に接続されており、アノードが第5スイッチング素子SW5と第6スイッチング素子SW6の接続点に接続されている。キャパシタC2は、一端が第1ダイオードD1と第2ダイオードD2の接続点に接続されており、他端が第5スイッチング素子SW5と第6スイッチング素子SW6の接続点に接続されている。

【0035】

駆動回路100は、第1選択信号S16及び第2選択信号S17に基づいて、複数のキャパシタC1,C2から可変電圧生成部22の制御電圧Vconを充電するためのキャパシタC1,C2を選択する。第1選択信号S16は、第1チャージポンプ制御回路部16を制御し、第1キャパシタC1を選択するか否かを決定する。第2選択信号S17は、第2チャージポンプ制御回路部17を制御し、第2キャパシタC2を選択するか否かを決定する。

【0036】

図10に、選択信号S16,S17と各スイッチング素子SW3,SW4,SW5,SW6の動作と選択されたキャパシタC1,C2の容量の対応表を示す。選択信号S16,S17が「0」の場合、対応するキャパシタC1,C2が選択されないことを示す。選択信号S16,S17が「1」の場合、対応するキャパシタC1,C2が選択されることを示す。ここで、図10の「連動」とは、PWM信号が各スイッチング素子SW3,SW4,SW5,SW6のゲートに入力することを示す。

【0037】

このように、駆動回路100では、複数のキャパシタC1,C2から可変電圧生成部22の制御電圧Vconを充電するためのキャパシタC1,C2を選択することができる。駆動回路100では、選択されるキャパシタC1,C2によって容量を変化させることができるので、充電される電荷量を変化させることができる。したがって、駆動回路100では、指示信号S1と選択信号S16,S17の双方を利用して、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprをより高精度に制御することができる。

【0038】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0039】

10:駆動回路

12:切換え制御回路部

14:チャージポンプ回路部

18:駆動電源

22:可変電圧生成部

C1,C2:キャパシタ

S1:指示信号

【技術分野】

【0001】

本発明は、スイッチング素子を駆動する駆動回路に関する。

【背景技術】

【0002】

スイッチング素子は、駆動電圧を用いて特定機能を発揮することが可能な素子であり、様々な用途で広く用いられている。スイッチング素子の一例には、絶縁ゲートを備えるスイッチング素子が知れられている。この種のスイッチング素子は、ゲート電圧に基づいて電流量を制御するものであり、例えば、直流電圧を変圧するコンバータ装置、直流電圧と交流電圧の間で変換するインバータ装置に用いられている。この種のスイッチング素子の一例には、IGBT(Insulated Gate Bipolar Transistor)、MOSFET(Metal Oxide Semiconductor Field Effect Transistor)を含むパワー半導体素子が挙げられる。

【0003】

このようなスイッチング素子のオン・オフを切換えるために、駆動回路が用いられている。例えば、駆動回路は、スイッチング素子のオンを指示する制御信号に基づいて、スイッチング素子のゲートに駆動電圧を印加してスイッチング素子のゲート電圧を上昇させる。

【0004】

この種の駆動回路では、スイッチング素子のターンオンを高速化し、スイッチング損失を低減することが望まれている。特許文献1には、スイッチング素子のターンオンを高速化するために、チャージポンプ回路部を備えた駆動回路が開示されている。この駆動回路では、スイッチング素子がターンオンする遷移期間の初期段階において、チャージポンプ回路部のキャパシタに充電された充電電圧と駆動電源の電圧を合計した駆動電圧を用いてスイッチング素子を駆動するので、スイッチング素子のターンオンが高速化される。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−200560号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の技術では、チャージポンプ回路部のキャパシタを充電するときに、キャパシタに対して駆動電源が直接的に接続される。このため、キャパシタに充電される充電電圧は、駆動電源の電圧に依存した固定値である。特許文献1の技術では、駆動電源の電圧に依存した駆動電圧しか生成することができない。

【0007】

本明細書で開示される技術は、チャージポンプ回路部を備えた駆動回路において、自由度の高い駆動回路を実現することを目的としている。

【課題を解決するための手段】

【0008】

本明細書で開示される駆動回路は、切換え制御回路部とチャージポンプ回路部を備えている。切換え制御回路部は、スイッチング素子のゲートに駆動電圧を印加する状態と印加しない状態を切換える。チャージポンプ回路部は、スイッチング素子がターンオンする遷移期間の初期段階において、キャパシタに充電された充電電圧に基づいて駆動電源の電圧を昇圧して駆動電圧を生成し、その駆動電圧を切換え制御回路部に提供する。チャージポンプ回路部は、指示信号に基づいてキャパシタに充電される充電電圧を調整可能に構成されていることを特徴としている。本明細書で開示される駆動回路では、指示信号を利用してチャージポンプ回路部のキャパシタに充電される充電電圧を独立して調整可能であり、これにより、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧の大きさも独立して調整可能である。本明細書で開示される駆動回路は、指示信号を利用して、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧を柔軟に制御することができる。

【0009】

チャージポンプ回路部は、複数のキャパシタを有していてもよい。この場合、チャージポンプ回路部は、選択信号に基づいて複数のキャパシタから選択されたキャパシタを充電する。この態様の駆動回路では、指示信号と選択信号の双方を利用してスイッチング素子がターンオンする遷移期間の初期段階の駆動電圧をより高精度に制御することができる。

【0010】

チャージポンプ回路部は、ミラー期間が終了するまでに、キャパシタに蓄積された電荷を放電してもよい。この態様の駆動回路では、スイッチング素子がターンオンする遷移期間において、スイッチング素子のゲート電圧が過度に昇圧されることが抑制され、スイッチング素子のゲート絶縁膜の信頼性悪化を抑えることができる。

【発明の効果】

【0011】

本明細書で開示される技術によると、スイッチング素子がターンオンする遷移期間の初期段階の駆動電圧を独立して調整することができる。

【図面の簡単な説明】

【0012】

【図1】第1実施形態の駆動回路の構成を示す。

【図2A】可変電圧生成部の入力と出力の関係の一例を示す。

【図2B】可変電圧生成部の入力と出力の関係の他の一例を示す。

【図2C】可変電圧生成部の入力と出力の関係の他の一例を示す。

【図3】第1実施形態の駆動回路において、各構成要素及び電圧のタイミングチャートを示す。

【図4】第1実施形態の駆動回路において、メインスイッチング素子のゲートに駆動電圧を印加し、ゲートに電荷を充電するモードを示す(指示信号が入力しない場合)。

【図5】第1実施形態の駆動回路において、メインスイッチング素子のゲートから電荷を放電するモードを示す。

【図6】第1実施形態の駆動回路において、第1キャパシタに電荷を充電するモードを示す。

【図7】第1実施形態の駆動回路において、メインスイッチング素子のゲートに駆動電圧を印加し、ゲートに電荷を充電するモードを示す(指示信号が入力する場合)。

【図8】第1実施形態の駆動回路において、メインスイッチング素子がターンオンする遷移期間の駆動電圧及びゲート電圧のタイミングチャートの詳細を示す。

【図9】第2実施形態の駆動回路の構成を示す。

【図10】第2実施形態の駆動回路において、選択信号と各スイッチング素子の動作と選択されたキャパシタの容量の対応関係を示す。

【発明を実施するための形態】

【0013】

(第1実施形態)

図1に、車両用のインバータ装置に搭載されるメインスイッチング素子SW10(請求項に記載のスイッチング素子の一例)を駆動する駆動回路10の回路図を示す。一例では、メインスイッチング素子SW10には、nチャネル型のMOSFET(Metal Oxide Semiconductor Field Effect Transistor)が用いられており、その半導体材料には炭化珪素又は窒化ガリウム系のワイドバンドギャップの化合物半導体が用いられている。駆動回路10は、メインスイッチング素子SW10のゲート電極に対して電荷を充電又はゲート電極から電荷を放電させることで、ゲート電極のゲート電圧Vgを上昇又は降下させる。このような駆動回路10は、メインスイッチング素子SW10のゲート電圧Vgを制御することで、メインスイッチング素子SW10を流れるドレイン電流Idを制御する。

【0014】

駆動回路10は、切換え制御回路部12とチャージポンプ回路部14を備えている。切換え制御回路部12は、PWM信号に基づいて、メインスイッチング素子SW10のゲートに駆動電圧Vgprを印加する状態と駆動電圧Vgprを印加しない状態を切換える。チャージポンプ回路部14は、メインスイッチング素子SW10がターンオンする遷移期間の初期段階において、駆動電源18の電圧Vsを昇圧して駆動電圧Vgprを生成し、その駆動電圧Vgprを切換え制御回路部12に提供する。

【0015】

切換え制御回路部12は、第1スイッチング素子SW1と第2スイッチング素子SW2と第1インバータINV1を有している。第1スイッチング素子SW1と第2スイッチング素子SW2は直列に接続されている。第1スイッチング素子SW1は、nチャネル型のMOSFETであり、ドレインがチャージポンプ回路部14に接続されており、ソースが第2スイッチング素子SW2に接続されている。第1スイッチング素子SW1のゲートには、PWM信号が入力している。第2スイッチング素子SW2は、nチャネル型のMOSFETであり、ドレインが第1スイッチング素子SW1に接続されており、ソースが接地されている。第2スイッチング素子SW2のゲートには、第1インバータINV1で反転したPWM信号が入力している。第1スイッチング素子SW1のソースと第2スイッチング素子SW2のドレインの接続点が、メインスイッチング素子SW10のゲート抵抗Rgに接続されている。

【0016】

チャージポンプ回路部14は、第1チャージポンプ制御回路部16と、第1ダイオードD1と第2ダイオードD2と第3ダイオードD3と第1キャパシタC1と可変電圧生成部22を有している。第1チャージポンプ制御回路部16は、第3スイッチング素子SW3と第4スイッチング素子SW4と第2インバータINV2を有している。第3スイッチング素子SW3と第4スイッチング素子SW4は直列に接続されている。第3スイッチング素子SW3は、nチャネル型のMOSFETであり、ドレインが駆動電源18の正極に接続されており、ソースが第4スイッチング素子SW4に接続されている。第3スイッチング素子SW3のゲートには、PWM信号が入力している。第4スイッチング素子SW4は、nチャネル型のMOSFETであり、ドレインが第3スイッチング素子SW3に接続されており、ソースが接地されている。第4スイッチング素子SW4のゲートには、第2インバータINV2で反転したPWM信号が入力している。

【0017】

第1ダイオードD1と第2ダイオードD2は、制御回路部12と可変電圧生成部22の間で直列に接続されており、第1ダイオードD1のカソードが制御回路部12の第1スイッチング素子SW1のドレインに接続されており、第2ダイオードD2のアノードが可変電圧生成部22に接続されている。第3ダイオードD3は、カソードが第1ダイオードD1のアノードと第2ダイオードD2のカソードの接続点に接続されており、アノードが第3スイッチング素子SW3のソースと第4スイッチング素子SW4のドレインの接続点に接続されている。第1キャパシタC1は、一端が第1ダイオードD1のアノードと第2ダイオードD2のカソードの接続点に接続されており、他端が第3スイッチング素子SW3のソースと第4スイッチング素子SW4のドレインの接続点に接続されている。可変電圧生成部22は、駆動電源18の正極と第2ダイオードD2のアノードの間に接続されている。

【0018】

可変電圧生成部22は、駆動電源18の電圧Vsと外部からの指示信号S1が入力可能に構成されている。可変電圧生成部22は、指示信号S1に基づいて駆動電源18の電圧Vsを変圧し、その変圧された電圧を制御電圧Vconとして出力する。可変電圧生成部22は、指示信号S1が入力しないときには制御電圧Vconを出力しないように構成されている。一例として、可変電圧生成部22には、可変抵抗素子を利用した可変電圧回路を利用することができる。

【0019】

可変電圧生成部22に入力する指示信号S1と出力される制御電圧Vconの関係は、図2A〜Cに例示される。図2A及び図2Bに示されるように、可変電圧生成部22に入力する指示信号S1は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idであってもよい。図2Aの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idの変動に応じて、単調に追随する制御電圧Vconを出力する。具体的には、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idが上昇すると、単調に減少する制御電圧Vconを出力する。図2Bの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj又はドレイン電流Idが予め決められた複数の範囲に応じて、複数の離散した制御電圧Vconを出力する。具体的には、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tjが相対的に高いときに又はドレイン電流Idが相対的に大きいときに、相対的に低い制御電圧Vconを出力する。あるいは、図2Cに示されるように、可変電圧生成部22に入力する指示信号S1は、メインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsであってもよい。図2Cの例では、可変電圧生成部22は、メインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsに応じて、テーブル制御された制御電圧Vconを出力する。

【0020】

次に、図3のタイミングチャート及び図4〜図7の各モードを参照し、駆動回路10の動作を説明する。

【0021】

(可変電圧生成部22に指示信号S1が入力しない場合)

図3に示されるように、タイミングT1でPWM信号が立上がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオンし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオフする。これにより、図4に示されるように、第3スイッチング素子SW3、第3ダイオードD3、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。駆動電圧Vgprは、概ね駆動電源18の電圧Vsから第3ダイオードD3と第1ダイオードD1の順方向降下電圧を引いた値となる。図3に示されるように、メインスイッチング素子SW10のゲート電圧Vgは、タイミングT1で駆動電圧Vgprの印加が開始してから、タイミングT2で定常状態になるまで上昇する。メインスイッチング素子SW10のゲート電圧Vgが閾値を超えると、メインスイッチング素子SW10がターンオンする。なお、メインスイッチング素子SW10のスイッチング損失は、駆動電圧Vgprの印加が開始するタイミングT1からゲート電圧Vgが定常状態となるタイミングT2までの時間に強く依存する。メインスイッチング素子SW10のスイッチング損失を低減するためには、この時間を短縮することが肝要である。

【0022】

次に、図3に示されるように、タイミングT3でPWM信号が立下がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンする。これにより、図5に示されるように、メインスイッチング素子SW10のゲート電極に充電されていた電荷は、ゲート抵抗Rgと第2スイッチング素子SW2を介して放電される。メインスイッチング素子SW10のゲート電圧Vgは、電荷の放電に応じて下降する。メインスイッチング素子SW10のゲート電圧Vgが閾値を下回ると、メインスイッチング素子SW10がターンオフする。

【0023】

(可変電圧生成部22に指示信号S1が入力する場合)

図3に示されるように、PWM信号がローのときに(第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンのときに)、タイミングT4で可変電圧生成部22に指示信号S1が入力する。可変電圧生成部22は、指示信号S1に応じて制御電圧Vconを出力する。これにより、図6に示されるように、第1キャパシタC1が充電される。すなわち、駆動回路10は、メインスイッチング素子SW10がオフのときに、指示信号S1に基づいて第1キャパシタC1を充電する。第1キャパシタC1の充電電圧VC1は、概ね可変電圧生成部22の制御電圧Vconから第2ダイオードD2の順方向降下電圧を引いた値である。

【0024】

次に、図3に示されるように、タイミングT5でPWM信号が立上がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオンし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオフする。これにより、図7に示されるように、第3スイッチング素子SW3、第1キャパシタC1、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。このとき、駆動電源18と第1キャパシタC1が直列に接続されることから、駆動電源18の電圧Vsが第1キャパシタC1の充電電圧VC1によって昇圧される。駆動電圧Vgprは、概ね駆動電源18の電圧Vsと第1キャパシタC1の充電電圧VC1の合計から第1ダイオードD1の順方向降下電圧を引いた値である。このように、第1キャパシタC1が予め充電されていることによって、駆動電圧Vgprは、駆動電源18の電圧Vsに対して概ね第1キャパシタC1の充電電圧VC1に応じて昇圧される。これにより、図3に示されるように、メインスイッチング素子SW10のゲート電圧Vgは、相対的に高速に上昇する(タイミングT1〜T2よりもタイミングT5〜T6が短い)。

【0025】

図8に、タイミングT5〜T6(メインスイッチング素子SW10がターンオンする遷移期間)の様子をより詳細に示す。駆動電圧Vgprは、メインスイッチング素子SW10のターンオンと同時に大きく立ち上がり、第1キャパシタC1に充電していた電荷がメインスイッチング素子SW10のゲート入力容量に移動するのに伴って減少する。駆動回路10では、第1キャパシタC1の容量がメインスイッチング素子SW10のゲート入力容量よりも小さく設定されているので、ミラー期間が終了するタイミングTmirrまでに、第1キャパシタC1に充電していた全ての電荷がメインスイッチング素子SW10のゲート入力容量に移動する。このため、駆動電圧Vgprは、ミラー期間が終了するタイミングTmirrまでに、第1キャパシタC1の充電電圧VC1に相当する部分が減少する。第1キャパシタC1に充電していた全ての電荷がメインスイッチング素子SW10のゲート入力容量に移動した後は、図4に示されるように、第3スイッチング素子SW3、第3ダイオードD3、第1ダイオードD1、第1スイッチング素子SW1を介して駆動電源18からメインスイッチング素子SW10のゲート抵抗Rgに駆動電圧Vgprが印加される。この結果、駆動電圧Vgprは、概ね駆動電源18の電圧Vsから第3ダイオードD3と第1ダイオードD1の順方向降下電圧を引いた値となる。

【0026】

このように、駆動回路10では、メインスイッチング素子SW10がターンオンする遷移期間のうちのミラー期間において相対的に高い駆動電圧Vgprを印加し、ミラー期間の終了後には相対的に低い駆動電圧Vgprを印加する。このため、駆動回路10は、メインスイッチング素子SW10のスイッチング速度を高速化させながら、メインスイッチング素子SW10のゲート電極に過度な電圧が印加することを抑制することができる。駆動回路10は、メインスイッチング素子SW10のスイッチング損失を改善しながら、ゲート絶縁膜の信頼性悪化を抑制することができる。

【0027】

次に、図3に示されるように、タイミングT7でPWM信号が立下がると、第1スイッチング素子SW1及び第3スイッチング素子SW3がオフし、第2スイッチング素子SW2及び第4スイッチング素子SW4がオンする。これにより、図5に示されるように、メインスイッチング素子SW10のゲート電極に充電されていた電荷は、ゲート抵抗Rgと第2スイッチング素子SW2を介して放電される。メインスイッチング素子SW10のゲート電圧Vgは、電荷の放電に応じて下降する。メインスイッチング素子SW10のゲート電圧Vgが閾値を下回ると、メインスイッチング素子SW10がターンオフする。

【0028】

以下、駆動回路10の特徴を整理する。

(1)駆動回路10では、可変電圧生成部22が、外部からの指示信号S1に基づいて第1キャパシタC1に蓄積される電荷量を独立して調整可能に構成されていることを特徴としている。このため、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprも独立して調整可能である。駆動回路10は、外部からの指示信号S1を利用して、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprを柔軟に制御することができる。

【0029】

(2)通常、メインスイッチング素子SW10の特性は均一ではなく、様々なバラツキが存在している。例えば、メインスイッチング素子SW10には、ゲート電極の入力容量のバラツキ、温度特性上のバラツキが存在する。また、チャージポンプ回路部14の特性も均一ではなく、様々なバラツキが存在している。例えば、チャージポンプ回路部14には、第1キャパシタC1の容量のバラツキ、温度特性上のバラツキが存在する。駆動回路10では、図2A〜Cに例示されるように、指示信号S1にメインスイッチング素子SW10の素子温度Tj、ドレイン電流Id及びドレイン・ソース間電圧Vdsを利用することができる。これらの情報には、メインスイッチング素子SW10のバラツキが反映している。このため、可変電圧生成部22が指示信号S1に基づいて制御電圧Vconを制御することで、メインスイッチング素子SW10のバラツキに基づいて適宜に調整された駆動電圧Vgprを生成することができる。例えば、メインスイッチング素子SW10の素子温度Tjの上昇に伴ってメインスイッチング素子SW10のゲートの閾値電圧が低下してスイッチング速度が異常に高速化されるのを抑えるために、可変電圧生成部22が出力する制御電圧Vconを低く抑え、駆動電圧Vgprを低く抑えてメインスイッチング素子SW10のスイッチング速度を低速化することができる。また、メインスイッチング素子SW10のドレイン電流Idの増加に伴ってリカバリ電流が増加するのを抑えるために、可変電圧生成部22が出力する制御電圧Vconを低く抑え、駆動電圧Vgprを低く抑えてメインスイッチング素子SW10のドレイン電流Idを小さく抑えることができる。このように、駆動回路10は、指示信号S1を利用して駆動電圧Vgprを制御することにより、メインスイッチング素子SW10等のバラツキを補償することができる。

【0030】

(3)駆動回路10で駆動されるメインスイッチング素子SW10では、ターンオンの遷移期間の前半段階において相対的に高い駆動電圧Vgprを用いてゲート電圧Vgの立ち上がり速度が相対的に高速化されており、ターンオンの遷移期間の後半段階において相対的に低い駆動電圧Vgprを用いてゲート電圧Vgの立ち上がり速度が相対的に低速化されている。ターンオンの遷移期間の後半段階におけるゲート電圧Vgの立ち上がり速度は、メインスイッチング素子SW10のドレイン電流のサージ及びドレイン電流のリンギングに強く影響する。駆動回路10を用いると、ターンオンの遷移期間の後半段階におけるゲート電圧Vgの立ち上がり速度が低速化されているので、メインスイッチング素子SW10がターンオンするときのドレイン電流のサージ及びドレイン電流のリンギング現象が抑えられる。一方で、ターンオンの遷移期間の前半段階におけるゲート電圧Vgの立ち上がり速度が高速化されており、スイッチング損失の増大が抑えられている。

【0031】

(4)メインスイッチング素子SW10の半導体材料には、炭化珪素又は窒化ガリウム系のワイドバンドギャップの化合物半導体が用いられている。このようなワイドバンドギャップの化合物半導体で形成されるメインスイッチング素子SW10では、ドレイン電流のサージ及びドレイン電流のリンギングが特に問題となっている。したがって、駆動回路10は、ワイドバンドギャップの化合物半導体で形成されるメインスイッチング素子SW10を駆動する場合に特に有用である。

【0032】

(5)駆動回路10を構成する制御回路部12と第1チャージポンプ制御回路部16は、共通の回路構成である。これら回路部には、例えば、市販のゲート駆動用フォトカプラを利用することができる。また、駆動回路10を構成する可変電圧生成部22には、可変抵抗素子を利用した市販の可変電圧回路を利用することができる。このように駆動回路10を構成する各構成要素は、広く普及している汎用品を用いて構築することができる。

【0033】

(第2実施形態)

図9に示されるように、前述の駆動回路10と対比すると、駆動回路100は、第2チャージポンプ制御回路部17と第4ダイオードD4と第2キャパシタC2とを有していることを特徴としている。第2チャージポンプ制御回路部17は、第5スイッチング素子SW5と第6スイッチング素子SW6と第3インバータINV3を有している。第5スイッチング素子SW5と第6スイッチング素子SW6は直列に接続されている。第5スイッチング素子SW5は、nチャネル型のMOSFETであり、ドレインが駆動電源18の正極に接続されており、ソースが第6スイッチング素子SW6に接続されている。第6スイッチング素子SW6は、nチャネル型のMOSFETであり、ドレインが第5スイッチング素子SW5に接続されており、ソースが接地されている。

【0034】

第4ダイオードD4は、カソードが第1ダイオードD1と第2ダイオードD2の接続点に接続されており、アノードが第5スイッチング素子SW5と第6スイッチング素子SW6の接続点に接続されている。キャパシタC2は、一端が第1ダイオードD1と第2ダイオードD2の接続点に接続されており、他端が第5スイッチング素子SW5と第6スイッチング素子SW6の接続点に接続されている。

【0035】

駆動回路100は、第1選択信号S16及び第2選択信号S17に基づいて、複数のキャパシタC1,C2から可変電圧生成部22の制御電圧Vconを充電するためのキャパシタC1,C2を選択する。第1選択信号S16は、第1チャージポンプ制御回路部16を制御し、第1キャパシタC1を選択するか否かを決定する。第2選択信号S17は、第2チャージポンプ制御回路部17を制御し、第2キャパシタC2を選択するか否かを決定する。

【0036】

図10に、選択信号S16,S17と各スイッチング素子SW3,SW4,SW5,SW6の動作と選択されたキャパシタC1,C2の容量の対応表を示す。選択信号S16,S17が「0」の場合、対応するキャパシタC1,C2が選択されないことを示す。選択信号S16,S17が「1」の場合、対応するキャパシタC1,C2が選択されることを示す。ここで、図10の「連動」とは、PWM信号が各スイッチング素子SW3,SW4,SW5,SW6のゲートに入力することを示す。

【0037】

このように、駆動回路100では、複数のキャパシタC1,C2から可変電圧生成部22の制御電圧Vconを充電するためのキャパシタC1,C2を選択することができる。駆動回路100では、選択されるキャパシタC1,C2によって容量を変化させることができるので、充電される電荷量を変化させることができる。したがって、駆動回路100では、指示信号S1と選択信号S16,S17の双方を利用して、メインスイッチング素子SW10がターンオンする遷移期間の初期段階の駆動電圧Vgprをより高精度に制御することができる。

【0038】

以上、本発明の具体例を詳細に説明したが、これらは例示に過ぎず、特許請求の範囲を限定するものではない。特許請求の範囲に記載の技術には、以上に例示した具体例を様々に変形、変更したものが含まれる。

また、本明細書または図面に説明した技術要素は、単独であるいは各種の組合せによって技術的有用性を発揮するものであり、出願時請求項記載の組合せに限定されるものではない。また、本明細書または図面に例示した技術は複数目的を同時に達成し得るものであり、そのうちの一つの目的を達成すること自体で技術的有用性を持つものである。

【符号の説明】

【0039】

10:駆動回路

12:切換え制御回路部

14:チャージポンプ回路部

18:駆動電源

22:可変電圧生成部

C1,C2:キャパシタ

S1:指示信号

【特許請求の範囲】

【請求項1】

スイッチング素子を駆動する駆動回路であって、

スイッチング素子のゲートに駆動電圧を印加する状態と印加しない状態を切換える切換え制御回路部と、

前記スイッチング素子がターンオンする遷移期間の初期段階において、キャパシタに充電された充電電圧に基づいて駆動電源の電圧を昇圧して前記駆動電圧を生成し、前記駆動電圧を前記切換え制御回路部に提供するチャージポンプ回路部と、を備えており、

前記チャージポンプ回路部では、指示信号に基づいて前記キャパシタに充電される充電電圧が調整可能に構成されている駆動回路。

【請求項2】

前記チャージポンプ回路部は、複数のキャパシタを有しており、選択信号に基づいて前記複数のキャパシタから選択されたキャパシタを充電する請求項1に記載の駆動回路。

【請求項3】

前記チャージポンプ回路部は、ミラー期間が終了するまでに、前記キャパシタに充電された電荷を放電する請求項1又は2に記載の駆動回路。

【請求項1】

スイッチング素子を駆動する駆動回路であって、

スイッチング素子のゲートに駆動電圧を印加する状態と印加しない状態を切換える切換え制御回路部と、

前記スイッチング素子がターンオンする遷移期間の初期段階において、キャパシタに充電された充電電圧に基づいて駆動電源の電圧を昇圧して前記駆動電圧を生成し、前記駆動電圧を前記切換え制御回路部に提供するチャージポンプ回路部と、を備えており、

前記チャージポンプ回路部では、指示信号に基づいて前記キャパシタに充電される充電電圧が調整可能に構成されている駆動回路。

【請求項2】

前記チャージポンプ回路部は、複数のキャパシタを有しており、選択信号に基づいて前記複数のキャパシタから選択されたキャパシタを充電する請求項1に記載の駆動回路。

【請求項3】

前記チャージポンプ回路部は、ミラー期間が終了するまでに、前記キャパシタに充電された電荷を放電する請求項1又は2に記載の駆動回路。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2A】

【図2B】

【図2C】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−99181(P2013−99181A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−241835(P2011−241835)

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月4日(2011.11.4)

【出願人】(000003609)株式会社豊田中央研究所 (4,200)

【Fターム(参考)】

[ Back to top ]