駆動装置

【課題】消費電力を低減した駆動装置を提供する。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

【解決手段】コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備えた駆動装置である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、駆動装置に関する。

【背景技術】

【0002】

一般に、単相モータや三相モータ等の駆動コイルに駆動電流を供給する回路として、駆動コイルに駆動電流を供給するソーストランジスタ及びシンクトランジスタを含む出力回路が用いられる。ここで、出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた場合、出力回路のソーストランジスタ及びシンクトランジスタにP型MOSFETを用いた場合に比べて、相対的に小さな面積で出力回路を生成できる。よって、出力回路の小型化のために、出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた構成とするのが望ましい。出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた出力回路として、例えば特許文献1に開示されたモータ駆動回路が知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−129613号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、特許文献1に開示されるモータ駆動回路は、ソーストランジスタに用いられたN型MOSFETをオフとした状態で、シンクトランジスタに用いられたN型MOSFETをオンからオフとした際に駆動コイルからモータ駆動回路に回生電流が流れるため、モータ駆動回路の消費電力を無視することができなかった。

【課題を解決するための手段】

【0005】

前述した課題を解決する主たる本発明は、コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備え、前記第1駆動信号が前記第1N型MOSFETのオンを示す信号である場合、前記第1駆動回路から前記第1N型MOSFETのゲートへ前記P型MOSFETの寄生ダイオードを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオンし、前記第1駆動信号が前記第1N型MOSFETのオフを示す信号である場合、前記第1N型MOSFETのゲートから前記第1駆動回路へ前記P型MOSFETを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオフし、前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して電流を供給することを特徴とする駆動装置である。

【0006】

本発明の他の特徴については、添付図面及び本明細書の記載により明らかとなる。

【発明の効果】

【0007】

本発明によれば、消費電力を低減した駆動装置を提供することができる。

【図面の簡単な説明】

【0008】

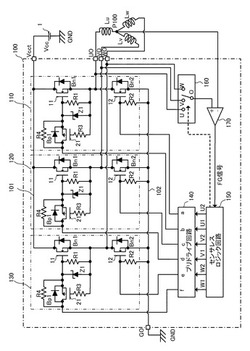

【図1】本発明の実施形態に係るモータ駆動装置を示す図である。

【図2】本発明の実施形態に係るプリドライブ回路及び出力回路の詳細を示す図である。

【図3】本発明の実施形態に係るモータ駆動装置の論理信号及びコイル電圧を示す波形図である。

【発明を実施するための形態】

【0009】

本明細書および添付図面の記載により、少なくとも以下の事項が明らかとなる。

【0010】

===駆動装置の全体構成===

図1は、本実施形態に係るモータ駆動装置を示す図である。

モータ駆動装置100は、例えば三相センサレスモータの駆動コイルに駆動電流を供給するための装置であり、出力回路110乃至130、プリドライブ回路140(第1駆動回路、第2駆動回路)、センサレスロジック回路150、スイッチ回路160、コンパレータ170及び例えば5個の端子Vcct、端子GO、端子UO、端子VO、端子WOを備えて構成される。

【0011】

モータ駆動装置100は、端子Vcctを介して電源1に接続され、端子GOを介して接地される。モータ駆動装置100の端子UO、端子VO、端子WOには、スター結線され且つ電気角120度の位相差を有して三相センサレスモータのステータに巻回された三相(U相、V相、W相)の駆動コイルLu、Lv、Lwが接続される。尚、駆動コイルLu、Lv、Lwのスター結線された地点を中性点P100とする。

【0012】

出力回路110乃至130は夫々、三相センサレスモータを回転させるための駆動電流を駆動コイルLu、Lv、Lwに夫々供給するための回路である。尚、出力回路110乃至130の詳細については後述する。

【0013】

スイッチ回路160及びコンパレータ170は、三相センサレスモータの回転速度に応じた周波数を有するFG信号を出力するための回路である。尚、FG信号、スイッチ回路160及びコンパレータ170の詳細については後述する。

【0014】

センサレスロジック回路150は、コンパレータ170から出力されたFG信号に基づいて、駆動コイルLu、Lv、Lwに駆動電流を供給するための論理信号U1、U2、V1、V2、W1、W2を生成出力する。尚、センサレスロジック回路150、論理信号U1、U2、V1、V2、W1、W2の詳細については後述する。

【0015】

プリドライブ回路140は、センサレスロジック回路150によって生成された論理信号U1、U2、V1、V2、W1、W2に基づいて駆動信号を出力回路110乃至130に出力する回路である。尚、プリドライブ回路140の詳細については後述する。

【0016】

===出力回路===

出力回路110乃至130は夫々、三相センサレスモータを回転させるための駆動電流を駆動コイルLu、Lv、Lwに夫々供給するための回路である。出力回路110は、N型MOSFET11(第1N型MOSFET)、N型MOSFET12(第2N型MOSFET)、P型MOSFET21、寄生ダイオードBn1、Bn2、Bp1、抵抗R1(第3抵抗)、抵抗R2、抵抗R3(第2抵抗)、抵抗R4(第1抵抗)、ツェナーダイオードZ1(クランプ回路)を備えて構成される。

【0017】

ここで、ソース電源ライン101は、端子Vcctを介して電源1に接続されているものとする。シンク電源ライン102は、端子GOを介して接地されているものとする。

【0018】

N型MOSFET11とN型MOSFET12は、ソース電源ライン101とシンク電源ライン102との間に直列接続される。N型MOSFET11のソースとN型MOSFET12のドレインとの接続点は、端子UOを介して駆動コイルLuの中性点P100とは反対側の一端と接続される。つまり、N型MOSFET11は、駆動コイルLuに駆動電流を供給するソーストランジスタとして動作する例えばN型パワーMOSFETであり、N型MOSFET12は、駆動コイルLuから駆動電流が供給されるシンクトランジスタとして動作する例えばN型パワーMOSFETである。N型MOSFET11に形成される寄生ダイオードBn1のカソード及びアノードは、N型MOSFET11のドレイン及びソースに夫々接続される。P型MOSFET21は、ドレインソース路がプリドライブ回路140の出力bとN型MOSFET11のゲートとの間に接続される例えばP型パワーMOSFETである。P型MOSFET21に形成される寄生ダイオードBp1のカソード及びアノードは、P型MOSFET21のソース及びドレインに夫々接続される。抵抗R4は、P型MOSFET21のドレイン及びソースの間に並列接続される。抵抗R1は、N型MOSFET11のゲート及びソースの間に接続される。尚、抵抗R1は、プリドライブ回路140の電源ラインに電圧が印加されない場合、N型MOSFET11のゲートがハイインピーダンスとなることを防止するプルダウン抵抗である。ツェナーダイオードZ1は、N型MOSFET11のゲート及びソースの間に接続されるとともにP型MOSFET21のゲート及びソースの間にも接続される。例えば、N型MOSFET12がオフしている状態においてN型MOSFET11をPWMスイッチングした場合、駆動コイルLuに発生する回生電流に起因してN型MOSFET11、P型MOSFET21のゲートソース間電圧が増大し、N型MOSFET11、P型MOSFET21を破損する虞がある。そこで、ツェナーダイオードZ1は、N型MOSFET11、P型MOSFET21のゲートソース間電圧をその耐圧を超えない範囲でクランプする。抵抗R3は、P型MOSFET21のゲートとN型MOSFET11のソース(クランプ回路を構成するツェナーダイオードZ1のアノード)との間に接続される。抵抗3は、N型MOSFET11及びP型MOSFET21がオンしている状態から、N型MOSFET11がオフした後にP型MOSFET21をオフさせる抵抗である。N型MOSFET12のゲートは、プリドライブ回路140の出力aと接続される。抵抗R2は、N型MOSFET12のゲート及びソースの間に接続される。尚、抵抗R2は、プリドライブ回路140の電源ラインに電圧が印加されない場合、N型MOSFET12のゲートがハイインピーダンスとなることを防止するプルダウン抵抗である。

【0019】

尚、出力回路120、130は出力回路110と同様の構成であるので、出力回路120、130の構成で出力回路110と同様な構成には説明の便宜上、出力回路110の構成と同じ番号を付し、出力回路120、130の説明は省略する。

【0020】

===プリドライブ回路===

図2は、本実施形態に係るプリドライブ回路及び出力回路の詳細を示す図である。尚、図2では、プリドライブ回路140のうち出力回路110に駆動信号を出力する回路1401についてのみ示されている。出力回路120、130に駆動信号を出力する回路は、出力回路110に駆動信号を出力する回路1401と同様な構成であるので、回路1401についてのみ説明し、出力回路120、130に駆動信号を出力する回路についての説明は省略する。

【0021】

回路1401は、センサレスロジック回路150によって生成出力された論理信号U1、U2に基づいて、駆動信号を出力回路110に出力する回路である。

【0022】

回路1401は、例えば4個のCMOS回路I1乃至I4を備えて構成される。

【0023】

CMOS回路I1は、P型MOSFET31及びN型MOSFET32を備えて構成される。ここで、電源ライン141は、チャージポンプ回路1402に接続されているものとする。尚、チャージポンプ回路1402は、電源1の電源電圧Vcc(例えば24V)を昇圧した電源電圧Vg(例えば29V)を生成する回路とする。P型MOSFET31とN型MOSFET32は、電源ライン141とグランドGNDとの間に直列接続される。P型MOSFET31及びN型MOSFET32のゲートは、端子Tu1に接続される。つまり、CMOS回路I1は、端子Tu1にハイレベルの論理信号U1、ローレベルの論理信号U1が夫々入力された場合、P型MOSFET31とN型MOSFET32との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0024】

CMOS回路I2は、P型MOSFET33、N型MOSFET34、抵抗R111(第4抵抗)及び抵抗R112(第5抵抗)を備えて構成される。P型MOSFET33とN型MOSFET34は、電源ライン141とグランドGNDとの間に直列接続される。P型MOSFET33のゲートとN型MOSFET34のゲートは、P型MOSFET31とN型MOSFET32との接続点に接続される。抵抗R111と抵抗R112は、直列接続された状態で、P型MOSFET33のドレインとN型MOSFET34のドレインとの間に接続される。尚、例えば抵抗R111がP型MOSFET33に接続され、例えば抵抗R112がN型MOSFET34に接続されるものとする。抵抗R111は、出力回路110のN型MOSFET11をオンする速度を調整するための抵抗である。抵抗R112は、出力回路110のN型MOSFET11をオフする速度を調整するための抵抗である。直列に接続された抵抗R111と抵抗R112との接続点は、P型MOSFET21のドレインに接続される。つまり、CMOS回路I2は、P型MOSFET33とN型MOSFET34のゲートにハイレベルの論理信号、ローレベルの論理信号が夫々入力された場合、抵抗R111と抵抗R112との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0025】

CMOS回路I3は、P型MOSFET35及びN型MOSFET36を備えて構成される。ここで、電源ライン142は、レギュレータ回路1403に接続されているものとする。尚、レギュレータ回路1403は、電源1の電源電圧Vccを降圧した電源電圧Vreg(例えば5V)を生成する回路とする。P型MOSFET35とN型MOSFET36は、電源ライン142とグランドGNDとの間に直列接続される。P型MOSFET35及びN型MOSFET36のゲートは、端子Tu2に接続される。つまり、CMOS回路I3は、端子Tu2にハイレベルの論理信号U2、ローレベルの論理信号U2が夫々入力された場合、P型MOSFET35とN型MOSFET36との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0026】

CMOS回路I4は、P型MOSFET37、N型MOSFET38、抵抗R113及び抵抗R114を備えて構成される。P型MOSFET37とN型MOSFET38は、電源ライン142とグランドGNDとの間に直列接続される。P型MOSFET37のゲートとN型MOSFET38のゲートは、P型MOSFET35とN型MOSFET36との接続点に接続される。抵抗R113と抵抗R114は、直列接続された状態で、P型MOSFET37のドレインとN型MOSFET38のドレインとの間に接続される。尚、例えば抵抗R113がP型MOSFET37に接続され、例えば抵抗R114がN型MOSFET38に接続されるものとする。抵抗R113は、出力回路110のN型MOSFET12をオンする速度を調整するための抵抗である。抵抗R114は、出力回路110のN型MOSFET12をオフする速度を調整するための抵抗である。直列に接続された抵抗R113と抵抗R114との接続点は、N型MOSFET12のゲートに接続される。つまり、CMOS回路I4は、P型MOSFET37とN型MOSFET38のゲートにハイレベルの論理信号、ローレベルの論理信号が夫々入力された場合、抵抗R113と抵抗R114との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0027】

ここで、図1、図2を参照してプリドライブ回路140がN型MOSFET11、12を夫々、オンオフする動作について説明する。

【0028】

例えば、センサレスロジック回路150からCMOS回路I1の端子Tu1にハイレベルの論理信号U1が入力された場合、CMOS回路I1は論理信号U1を反転し、CMOS回路I2にローレベルの論理信号を出力する。CMOS回路I2は、CMOS回路I1から入力されたローレベルの論理信号によって、P型MOSFET33をオンし、N型MOSFET34をオフする。チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流が供給される。チャージポンプ回路1402からN型MOSFET11のゲートに供給された電流によって、N型MOSFET11のゲートソース間にN型MOSFET11をオンさせる電圧が印加され、N型MOSFET11はオンする。尚、P型MOSFET21のゲートには、N型MOSFET11のゲートソース間に印加された電圧から抵抗R3を介して電流が供給される。N型MOSFET11のゲートソース間に印加された電圧からP型MOSFET21のゲートに供給された電流によって、P型MOSFET21のゲートソース間にP型MOSFET21をオンさせる電圧が印加され、P型MOSFET21はオンする。

【0029】

一方、例えば、センサレスロジック回路150からCMOS回路I1の端子Tu1にローレベルの論理信号U1が入力された場合、CMOS回路I1は論理信号U1を反転し、CMOS回路I2にハイレベルの論理信号を出力する。CMOS回路I2は、CMOS回路I1から入力されたハイレベルの論理信号によって、P型MOSFET33をオフし、N型MOSFET34をオンする。N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流が供給される。N型MOSFET11のゲートソース間には、N型MOSFET11をオンさせる電圧が印加されていない状態となり、N型MOSFET11はオフする。尚、P型MOSFET21のゲートソース間には、P型MOSFET21をオンさせる電圧が印加されない状態となり、P型MOSFET21はオフする。P型MOSFET21のゲートとN型MOSFET11のソース(クランプ回路を構成するツェナーダイオードZ1のアノード)との間に接続された抵抗R3によって、P型MOSFET21は、N型MOSFET11がオフした後にオフする。

【0030】

例えば、センサレスロジック回路150からCMOS回路I3の端子Tu2にハイレベルの論理信号U2が入力された場合、CMOS回路I3は論理信号U2を反転し、CMOS回路I4にローレベルの論理信号を出力する。CMOS回路I4は、CMOS回路I3から入力されたローレベルの論理信号によって、P型MOSFET37はオンし、N型MOSFET38はオフする。レギュレータ回路1403から、P型MOSFET37、抵抗R113を介してN型MOSFET12のゲートに電流が供給される。レギュレータ回路1403からN型MOSFET12のゲートに供給された電流によって、N型MOSFET12のゲートソース間にN型MOSFET12をオンさせる電圧が印加され、N型MOSFET12はオンする。

【0031】

一方、例えば、センサレスロジック回路150からCMOS回路I3の端子Tu2にローレベルの論理信号U2が入力された場合、CMOS回路I3は論理信号U2を反転し、CMOS回路I4にハイレベルの論理信号を出力する。CMOS回路I4は、CMOS回路I3から入力されたハイレベルの論理信号によって、P型MOSFET37をオフし、N型MOSFET38をオンする。N型MOSFET12のゲートから、抵抗R114、N型MOSFET38を介してグランドGNDに電流が供給される。N型MOSFET12のゲートソース間には、N型MOSFET12をオンさせる電圧が印加されていない状態となり、N型MOSFET12はオフする。

【0032】

===スイッチ回路、コンパレータ、センサレスロジック回路===

図1、図2、図3を参照してスイッチ回路160、コンパレータ170、センサレスロジック回路150について説明する。

図3は、本実施形態に係るモータ駆動装置の論理信号及びコイル電圧を示す波形図である。

【0033】

スイッチ回路160及びコンパレータ170は、三相センサレスモータの回転速度に応じた周波数を有するFG信号を出力するための回路である。スイッチ回路160は、出力端子O、入力端子U、V、Wを有する。スイッチ回路160の入力端子U、V、Wは夫々、端子UO、VO、WOを介して、駆動コイルLu、Lv、Lwの中性点P100とは反対側の一端に夫々接続される。出力端子Oは、コンパレータ170の非反転入力端子に接続される。コンパレータ170の反転入力端子は、駆動コイルLu、Lv、Lwの中性点P100に接続される。コンパレータ170の出力端子は、センサレスロジック回路150に接続される。センサレスロジック回路150は、コンパレータ170から出力されたFG信号に基づいて、駆動コイルLu、Lv、Lwに駆動電流を供給するための論理信号U1、U2、V1、V2、W1、W2を生成出力する。センサレスロジック回路150は、出力回路110乃至130のN型MOSFET11夫々に駆動信号を出力するための、電気角120度の位相差を有する論理信号U1、V1、W1をプリドライブ回路140に出力する。センサレスロジック回路150は、出力回路110乃至130のN型MOSFET12夫々に駆動信号を出力するための、電気角120度の位相差を有する論理信号U2、V2、W2をプリドライブ回路140に出力する。つまり、センサレスロジック回路150は、三相センサレスモータが回転するように、駆動電流が供給される駆動コイルが電気角60度毎に切り替わるような論理信号U1、U2、V1、V2、W1、W2をプリドライブ回路140に出力する。センサレスロジック回路150は、駆動コイルLu、Lv、Lwのうち駆動電流が供給されていない駆動コイルの一端のコイル電圧がスイッチ回路160の出力端子Oに印加されるように、スイッチ回路160における出力端子Oと入力端子U、V、Wの接続を制御する。例えば、図3の時刻T0から時刻T1の場合、センサレスロジック回路150は、スイッチ回路160の出力端子Oと入力端子Wが接続されるように、スイッチ回路160を制御する。

【0034】

出力回路110乃至130のN型MOSFET11、12が、センサレスロジック回路150の論理信号U1、U2、V1、V2、W1、W2に基づいてオンオフすると、駆動電流が、電源1から駆動コイルLu、Lv、Lwに供給される。これにより、予め定められた方向(例えば正回転)に三相センサレスモータが回転し、駆動コイルLu、Lv、Lwの端子UO、VO、WOと接続される一端には、電気角120度の位相差を有するコイル電圧Vu、Vv、Vwが発生する。尚、コイル電圧Vu、Vv、Vwは、三相センサレスモータの回転速度に応じた周波数を有している。コンパレータ170の非反転入力端子には、駆動コイルLu、Lv、Lwのうち駆動電流が供給されていない駆動コイルの一端のコイル電圧がスイッチ回路160を介して印加される。コンパレータ170の反転入力端子には、中性点P100の電圧が印加される。コンパレータ170は、コンパレータ170の非反転入力端子にスイッチ回路160を介して印加されたコイル電圧と、コンパレータ170の反転入力端子に印加された中性点P100の電圧と、が交差するゼロクロスポイントを検出する。コンパレータ170は、ゼロクロスポイントでエッジが切り替わり、矩形波状のFG信号をセンサレスロジック回路150に出力する。

【0035】

===モータ駆動装置の動作===

図1、図2、図3を参照してモータ駆動装置100の動作について説明する。

プリドライブ回路140は、センサレスロジック回路150から出力される論理信号U1、U2、V1、V2、W1、W2に基づいて、駆動信号を出力回路110乃至130のN型MOSFET11、12に出力する。出力回路110乃至130のN型MOSFET11、12は、プリドライブ回路140の駆動信号によってオンオフして、三相センサレスモータが回転するように駆動電流を駆動コイルLu、Lv、Lwに供給する。

【0036】

駆動コイルLuに駆動電流を供給するモータ駆動装置100の動作と、駆動コイルLv、Lwに駆動電流を供給するモータ駆動装置100の動作は同様であるので、駆動コイルLuに駆動電流を供給するモータ駆動装置100の動作について説明し、駆動コイルLv、Lwに駆動電流を供給するモータ駆動装置100の動作の説明は省略する。

【0037】

例えば、時刻T0から時刻T2の場合、センサレスロジック回路150は、ハイレベルの論理信号U1、ローレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11がオンし、N型MOSFET12がオフする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11がオンし、N型MOSFET12がオフするので、駆動電流は電源1から出力回路110のN型MOSFET11を介して駆動コイルLuに供給される。

【0038】

例えば、時刻T3から時刻T5の場合、センサレスロジック回路150は、ローレベルの論理信号U1、ハイレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11がオフし、N型MOSFET12がオンする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11がオフし、N型MOSFET12がオンするので、駆動電流は駆動コイルLuから出力回路110のN型MOSFET12を介してグランドGNDに供給される。

【0039】

例えば、時刻T2から時刻T3及び時刻T5から時刻T6の場合、センサレスロジック回路150は、ローレベルの論理信号U1、ローレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11、12がともにオフする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11、12がともにオフするので、駆動電流は駆動コイルLuに供給されない。

【0040】

例えば、時刻T5の場合、センサレスロジック回路150は、ローレベルの論理信号U1を出力した状態で、時刻T5にハイレベルからローレベルへ変化する論理信号U2を出力する。前述したように、出力回路110のN型MOSFET11がオフした状態で、時刻T5に出力回路110のN型MOSFET12がオンからオフとなる。尚、P型MOSFET21はオフとなっている。その場合、駆動コイルLuに発生する回生電流でキックバック電圧KBが駆動コイルLuの一端に印加される。キックバック電圧KBによって電流が駆動コイルLuからツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDへ供給される。従って、駆動コイルLuからグランドGNDへ供給される電流によって、モータ駆動装置100で電力が消費されることとなる。

【0041】

ここで、キックバック電圧KBによるモータ駆動装置100の消費電力の値の一例を示す。例えば、キックバック電圧KBを24.7V、ツェナーダイオードZ1の順方向電圧を0.7V、抵抗R4の抵抗値を50KΩ、抵抗R112の抵抗値を2KΩ、N型MOSFET34のオン抵抗値を0Ωとする。駆動コイルLuからツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDへ供給される電流の電流値は、I=(24.7V−0.7V)÷(50KΩ+2KΩ)≒0.46mAとなる。よって、キックバック電圧KBによるモータ駆動装置100の消費電力の値は、24.7V×0.46mA≒0.01Wとなる。

【0042】

前述したように、プリドライブ回路140にハイレベルの論理信号U1が入力された場合、チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流が供給される。この電流によって、N型MOSFET11のゲートソース間にN型MOSFET11をオンさせる電圧が印加され、N型MOSFET11はオンする。P型MOSFET21のゲートには、N型MOSFET11のゲートソース間に印加された電圧から抵抗R3を介して電流が供給される。この電流によって、P型MOSFET21のゲートソース間にP型MOSFET21をオンさせる電圧が印加され、P型MOSFET21はオンする。プリドライブ回路140にローレベルの論理信号U1が入力された場合、N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流が供給される。N型MOSFET11のゲートソース間には、N型MOSFET11をオンさせる電圧が印加されていない状態となり、N型MOSFET11はオフする。P型MOSFET21のゲートソース間には、P型MOSFET21をオンさせる電圧が印加されない状態となり、P型MOSFET21はオフする。尚、抵抗R3によって、P型MOSFET21は、N型MOSFET11がオフした後にオフする。N型MOSFET11がオフした状態でN型MOSFET12がオンからオフした場合、回生電流がツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDに供給される。又、プリドライブ回路140の電源ライン141に電圧が印加されない場合、抵抗R1によって、N型MOSFET11のゲートがハイインピーダンスとなるのを防止することができる。又、プリドライブ回路140の抵抗R111、R112の抵抗値を夫々調整することによって、N型MOSFET11がオンする速度、オフする速度を夫々調整することができる。

【0043】

従って、モータ駆動装置100は、チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流を供給することによって、N型MOSFETを確実にオンすることができる。又、モータ駆動装置100は、N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流を供給することによって、N型MOSFET11を確実にオフすることができる。又、モータ駆動装置100は、N型MOSFET11がオフしている状態でN型MOSFET12がオンからオフした際に駆動コイルからグランドGNDへ供給される回生電流によるモータ駆動装置100の消費電力を抵抗R4によって減少させることができる。

【0044】

尚、上記実施形態は、本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得るとともに、本発明にはその等価物も含まれる。

【0045】

本実施形態においては、三相センサレスモータの駆動コイルLu、Lv、Lwに駆動電流を供給するモータ駆動装置100について説明したが、これに限定されるものではない。例えば、端子UO、VO、WOに誘導性負荷を接続して誘導性負荷へ電流を供給する駆動装置を提供することも可能である。

【符号の説明】

【0046】

1 電源

11、12、32、34、36、38 N型MOSFET

21、31、33、35、37 P型MOSFET

100 モータ駆動装置

110、120、130 出力回路

140 プリドライブ回路

150 センサレスロジック回路

160 スイッチ回路

170 コンパレータ

1402 チャージポンプ回路

1403 レギュレータ回路

Bn1、Bn2、Bp1 寄生ダイオード

I1、I2、I3、I4 CMOS回路

Lu、Lv、Lw 駆動コイル

R1、R2、R3、R4、R111、R112、R113、R114 抵抗

Z1 ツェナーダイオード

【技術分野】

【0001】

本発明は、駆動装置に関する。

【背景技術】

【0002】

一般に、単相モータや三相モータ等の駆動コイルに駆動電流を供給する回路として、駆動コイルに駆動電流を供給するソーストランジスタ及びシンクトランジスタを含む出力回路が用いられる。ここで、出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた場合、出力回路のソーストランジスタ及びシンクトランジスタにP型MOSFETを用いた場合に比べて、相対的に小さな面積で出力回路を生成できる。よって、出力回路の小型化のために、出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた構成とするのが望ましい。出力回路のソーストランジスタ及びシンクトランジスタにN型MOSFETを用いた出力回路として、例えば特許文献1に開示されたモータ駆動回路が知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−129613号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、特許文献1に開示されるモータ駆動回路は、ソーストランジスタに用いられたN型MOSFETをオフとした状態で、シンクトランジスタに用いられたN型MOSFETをオンからオフとした際に駆動コイルからモータ駆動回路に回生電流が流れるため、モータ駆動回路の消費電力を無視することができなかった。

【課題を解決するための手段】

【0005】

前述した課題を解決する主たる本発明は、コイルに電流を供給する第1N型MOSFETと、前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、前記P型MOSFETのドレインソースに並列接続される第1抵抗と、を備え、前記第1駆動信号が前記第1N型MOSFETのオンを示す信号である場合、前記第1駆動回路から前記第1N型MOSFETのゲートへ前記P型MOSFETの寄生ダイオードを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオンし、前記第1駆動信号が前記第1N型MOSFETのオフを示す信号である場合、前記第1N型MOSFETのゲートから前記第1駆動回路へ前記P型MOSFETを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオフし、前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して電流を供給することを特徴とする駆動装置である。

【0006】

本発明の他の特徴については、添付図面及び本明細書の記載により明らかとなる。

【発明の効果】

【0007】

本発明によれば、消費電力を低減した駆動装置を提供することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の実施形態に係るモータ駆動装置を示す図である。

【図2】本発明の実施形態に係るプリドライブ回路及び出力回路の詳細を示す図である。

【図3】本発明の実施形態に係るモータ駆動装置の論理信号及びコイル電圧を示す波形図である。

【発明を実施するための形態】

【0009】

本明細書および添付図面の記載により、少なくとも以下の事項が明らかとなる。

【0010】

===駆動装置の全体構成===

図1は、本実施形態に係るモータ駆動装置を示す図である。

モータ駆動装置100は、例えば三相センサレスモータの駆動コイルに駆動電流を供給するための装置であり、出力回路110乃至130、プリドライブ回路140(第1駆動回路、第2駆動回路)、センサレスロジック回路150、スイッチ回路160、コンパレータ170及び例えば5個の端子Vcct、端子GO、端子UO、端子VO、端子WOを備えて構成される。

【0011】

モータ駆動装置100は、端子Vcctを介して電源1に接続され、端子GOを介して接地される。モータ駆動装置100の端子UO、端子VO、端子WOには、スター結線され且つ電気角120度の位相差を有して三相センサレスモータのステータに巻回された三相(U相、V相、W相)の駆動コイルLu、Lv、Lwが接続される。尚、駆動コイルLu、Lv、Lwのスター結線された地点を中性点P100とする。

【0012】

出力回路110乃至130は夫々、三相センサレスモータを回転させるための駆動電流を駆動コイルLu、Lv、Lwに夫々供給するための回路である。尚、出力回路110乃至130の詳細については後述する。

【0013】

スイッチ回路160及びコンパレータ170は、三相センサレスモータの回転速度に応じた周波数を有するFG信号を出力するための回路である。尚、FG信号、スイッチ回路160及びコンパレータ170の詳細については後述する。

【0014】

センサレスロジック回路150は、コンパレータ170から出力されたFG信号に基づいて、駆動コイルLu、Lv、Lwに駆動電流を供給するための論理信号U1、U2、V1、V2、W1、W2を生成出力する。尚、センサレスロジック回路150、論理信号U1、U2、V1、V2、W1、W2の詳細については後述する。

【0015】

プリドライブ回路140は、センサレスロジック回路150によって生成された論理信号U1、U2、V1、V2、W1、W2に基づいて駆動信号を出力回路110乃至130に出力する回路である。尚、プリドライブ回路140の詳細については後述する。

【0016】

===出力回路===

出力回路110乃至130は夫々、三相センサレスモータを回転させるための駆動電流を駆動コイルLu、Lv、Lwに夫々供給するための回路である。出力回路110は、N型MOSFET11(第1N型MOSFET)、N型MOSFET12(第2N型MOSFET)、P型MOSFET21、寄生ダイオードBn1、Bn2、Bp1、抵抗R1(第3抵抗)、抵抗R2、抵抗R3(第2抵抗)、抵抗R4(第1抵抗)、ツェナーダイオードZ1(クランプ回路)を備えて構成される。

【0017】

ここで、ソース電源ライン101は、端子Vcctを介して電源1に接続されているものとする。シンク電源ライン102は、端子GOを介して接地されているものとする。

【0018】

N型MOSFET11とN型MOSFET12は、ソース電源ライン101とシンク電源ライン102との間に直列接続される。N型MOSFET11のソースとN型MOSFET12のドレインとの接続点は、端子UOを介して駆動コイルLuの中性点P100とは反対側の一端と接続される。つまり、N型MOSFET11は、駆動コイルLuに駆動電流を供給するソーストランジスタとして動作する例えばN型パワーMOSFETであり、N型MOSFET12は、駆動コイルLuから駆動電流が供給されるシンクトランジスタとして動作する例えばN型パワーMOSFETである。N型MOSFET11に形成される寄生ダイオードBn1のカソード及びアノードは、N型MOSFET11のドレイン及びソースに夫々接続される。P型MOSFET21は、ドレインソース路がプリドライブ回路140の出力bとN型MOSFET11のゲートとの間に接続される例えばP型パワーMOSFETである。P型MOSFET21に形成される寄生ダイオードBp1のカソード及びアノードは、P型MOSFET21のソース及びドレインに夫々接続される。抵抗R4は、P型MOSFET21のドレイン及びソースの間に並列接続される。抵抗R1は、N型MOSFET11のゲート及びソースの間に接続される。尚、抵抗R1は、プリドライブ回路140の電源ラインに電圧が印加されない場合、N型MOSFET11のゲートがハイインピーダンスとなることを防止するプルダウン抵抗である。ツェナーダイオードZ1は、N型MOSFET11のゲート及びソースの間に接続されるとともにP型MOSFET21のゲート及びソースの間にも接続される。例えば、N型MOSFET12がオフしている状態においてN型MOSFET11をPWMスイッチングした場合、駆動コイルLuに発生する回生電流に起因してN型MOSFET11、P型MOSFET21のゲートソース間電圧が増大し、N型MOSFET11、P型MOSFET21を破損する虞がある。そこで、ツェナーダイオードZ1は、N型MOSFET11、P型MOSFET21のゲートソース間電圧をその耐圧を超えない範囲でクランプする。抵抗R3は、P型MOSFET21のゲートとN型MOSFET11のソース(クランプ回路を構成するツェナーダイオードZ1のアノード)との間に接続される。抵抗3は、N型MOSFET11及びP型MOSFET21がオンしている状態から、N型MOSFET11がオフした後にP型MOSFET21をオフさせる抵抗である。N型MOSFET12のゲートは、プリドライブ回路140の出力aと接続される。抵抗R2は、N型MOSFET12のゲート及びソースの間に接続される。尚、抵抗R2は、プリドライブ回路140の電源ラインに電圧が印加されない場合、N型MOSFET12のゲートがハイインピーダンスとなることを防止するプルダウン抵抗である。

【0019】

尚、出力回路120、130は出力回路110と同様の構成であるので、出力回路120、130の構成で出力回路110と同様な構成には説明の便宜上、出力回路110の構成と同じ番号を付し、出力回路120、130の説明は省略する。

【0020】

===プリドライブ回路===

図2は、本実施形態に係るプリドライブ回路及び出力回路の詳細を示す図である。尚、図2では、プリドライブ回路140のうち出力回路110に駆動信号を出力する回路1401についてのみ示されている。出力回路120、130に駆動信号を出力する回路は、出力回路110に駆動信号を出力する回路1401と同様な構成であるので、回路1401についてのみ説明し、出力回路120、130に駆動信号を出力する回路についての説明は省略する。

【0021】

回路1401は、センサレスロジック回路150によって生成出力された論理信号U1、U2に基づいて、駆動信号を出力回路110に出力する回路である。

【0022】

回路1401は、例えば4個のCMOS回路I1乃至I4を備えて構成される。

【0023】

CMOS回路I1は、P型MOSFET31及びN型MOSFET32を備えて構成される。ここで、電源ライン141は、チャージポンプ回路1402に接続されているものとする。尚、チャージポンプ回路1402は、電源1の電源電圧Vcc(例えば24V)を昇圧した電源電圧Vg(例えば29V)を生成する回路とする。P型MOSFET31とN型MOSFET32は、電源ライン141とグランドGNDとの間に直列接続される。P型MOSFET31及びN型MOSFET32のゲートは、端子Tu1に接続される。つまり、CMOS回路I1は、端子Tu1にハイレベルの論理信号U1、ローレベルの論理信号U1が夫々入力された場合、P型MOSFET31とN型MOSFET32との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0024】

CMOS回路I2は、P型MOSFET33、N型MOSFET34、抵抗R111(第4抵抗)及び抵抗R112(第5抵抗)を備えて構成される。P型MOSFET33とN型MOSFET34は、電源ライン141とグランドGNDとの間に直列接続される。P型MOSFET33のゲートとN型MOSFET34のゲートは、P型MOSFET31とN型MOSFET32との接続点に接続される。抵抗R111と抵抗R112は、直列接続された状態で、P型MOSFET33のドレインとN型MOSFET34のドレインとの間に接続される。尚、例えば抵抗R111がP型MOSFET33に接続され、例えば抵抗R112がN型MOSFET34に接続されるものとする。抵抗R111は、出力回路110のN型MOSFET11をオンする速度を調整するための抵抗である。抵抗R112は、出力回路110のN型MOSFET11をオフする速度を調整するための抵抗である。直列に接続された抵抗R111と抵抗R112との接続点は、P型MOSFET21のドレインに接続される。つまり、CMOS回路I2は、P型MOSFET33とN型MOSFET34のゲートにハイレベルの論理信号、ローレベルの論理信号が夫々入力された場合、抵抗R111と抵抗R112との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0025】

CMOS回路I3は、P型MOSFET35及びN型MOSFET36を備えて構成される。ここで、電源ライン142は、レギュレータ回路1403に接続されているものとする。尚、レギュレータ回路1403は、電源1の電源電圧Vccを降圧した電源電圧Vreg(例えば5V)を生成する回路とする。P型MOSFET35とN型MOSFET36は、電源ライン142とグランドGNDとの間に直列接続される。P型MOSFET35及びN型MOSFET36のゲートは、端子Tu2に接続される。つまり、CMOS回路I3は、端子Tu2にハイレベルの論理信号U2、ローレベルの論理信号U2が夫々入力された場合、P型MOSFET35とN型MOSFET36との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0026】

CMOS回路I4は、P型MOSFET37、N型MOSFET38、抵抗R113及び抵抗R114を備えて構成される。P型MOSFET37とN型MOSFET38は、電源ライン142とグランドGNDとの間に直列接続される。P型MOSFET37のゲートとN型MOSFET38のゲートは、P型MOSFET35とN型MOSFET36との接続点に接続される。抵抗R113と抵抗R114は、直列接続された状態で、P型MOSFET37のドレインとN型MOSFET38のドレインとの間に接続される。尚、例えば抵抗R113がP型MOSFET37に接続され、例えば抵抗R114がN型MOSFET38に接続されるものとする。抵抗R113は、出力回路110のN型MOSFET12をオンする速度を調整するための抵抗である。抵抗R114は、出力回路110のN型MOSFET12をオフする速度を調整するための抵抗である。直列に接続された抵抗R113と抵抗R114との接続点は、N型MOSFET12のゲートに接続される。つまり、CMOS回路I4は、P型MOSFET37とN型MOSFET38のゲートにハイレベルの論理信号、ローレベルの論理信号が夫々入力された場合、抵抗R113と抵抗R114との接続点からローレベルの論理信号、ハイレベルの論理信号を夫々出力するインバータとして動作する。

【0027】

ここで、図1、図2を参照してプリドライブ回路140がN型MOSFET11、12を夫々、オンオフする動作について説明する。

【0028】

例えば、センサレスロジック回路150からCMOS回路I1の端子Tu1にハイレベルの論理信号U1が入力された場合、CMOS回路I1は論理信号U1を反転し、CMOS回路I2にローレベルの論理信号を出力する。CMOS回路I2は、CMOS回路I1から入力されたローレベルの論理信号によって、P型MOSFET33をオンし、N型MOSFET34をオフする。チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流が供給される。チャージポンプ回路1402からN型MOSFET11のゲートに供給された電流によって、N型MOSFET11のゲートソース間にN型MOSFET11をオンさせる電圧が印加され、N型MOSFET11はオンする。尚、P型MOSFET21のゲートには、N型MOSFET11のゲートソース間に印加された電圧から抵抗R3を介して電流が供給される。N型MOSFET11のゲートソース間に印加された電圧からP型MOSFET21のゲートに供給された電流によって、P型MOSFET21のゲートソース間にP型MOSFET21をオンさせる電圧が印加され、P型MOSFET21はオンする。

【0029】

一方、例えば、センサレスロジック回路150からCMOS回路I1の端子Tu1にローレベルの論理信号U1が入力された場合、CMOS回路I1は論理信号U1を反転し、CMOS回路I2にハイレベルの論理信号を出力する。CMOS回路I2は、CMOS回路I1から入力されたハイレベルの論理信号によって、P型MOSFET33をオフし、N型MOSFET34をオンする。N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流が供給される。N型MOSFET11のゲートソース間には、N型MOSFET11をオンさせる電圧が印加されていない状態となり、N型MOSFET11はオフする。尚、P型MOSFET21のゲートソース間には、P型MOSFET21をオンさせる電圧が印加されない状態となり、P型MOSFET21はオフする。P型MOSFET21のゲートとN型MOSFET11のソース(クランプ回路を構成するツェナーダイオードZ1のアノード)との間に接続された抵抗R3によって、P型MOSFET21は、N型MOSFET11がオフした後にオフする。

【0030】

例えば、センサレスロジック回路150からCMOS回路I3の端子Tu2にハイレベルの論理信号U2が入力された場合、CMOS回路I3は論理信号U2を反転し、CMOS回路I4にローレベルの論理信号を出力する。CMOS回路I4は、CMOS回路I3から入力されたローレベルの論理信号によって、P型MOSFET37はオンし、N型MOSFET38はオフする。レギュレータ回路1403から、P型MOSFET37、抵抗R113を介してN型MOSFET12のゲートに電流が供給される。レギュレータ回路1403からN型MOSFET12のゲートに供給された電流によって、N型MOSFET12のゲートソース間にN型MOSFET12をオンさせる電圧が印加され、N型MOSFET12はオンする。

【0031】

一方、例えば、センサレスロジック回路150からCMOS回路I3の端子Tu2にローレベルの論理信号U2が入力された場合、CMOS回路I3は論理信号U2を反転し、CMOS回路I4にハイレベルの論理信号を出力する。CMOS回路I4は、CMOS回路I3から入力されたハイレベルの論理信号によって、P型MOSFET37をオフし、N型MOSFET38をオンする。N型MOSFET12のゲートから、抵抗R114、N型MOSFET38を介してグランドGNDに電流が供給される。N型MOSFET12のゲートソース間には、N型MOSFET12をオンさせる電圧が印加されていない状態となり、N型MOSFET12はオフする。

【0032】

===スイッチ回路、コンパレータ、センサレスロジック回路===

図1、図2、図3を参照してスイッチ回路160、コンパレータ170、センサレスロジック回路150について説明する。

図3は、本実施形態に係るモータ駆動装置の論理信号及びコイル電圧を示す波形図である。

【0033】

スイッチ回路160及びコンパレータ170は、三相センサレスモータの回転速度に応じた周波数を有するFG信号を出力するための回路である。スイッチ回路160は、出力端子O、入力端子U、V、Wを有する。スイッチ回路160の入力端子U、V、Wは夫々、端子UO、VO、WOを介して、駆動コイルLu、Lv、Lwの中性点P100とは反対側の一端に夫々接続される。出力端子Oは、コンパレータ170の非反転入力端子に接続される。コンパレータ170の反転入力端子は、駆動コイルLu、Lv、Lwの中性点P100に接続される。コンパレータ170の出力端子は、センサレスロジック回路150に接続される。センサレスロジック回路150は、コンパレータ170から出力されたFG信号に基づいて、駆動コイルLu、Lv、Lwに駆動電流を供給するための論理信号U1、U2、V1、V2、W1、W2を生成出力する。センサレスロジック回路150は、出力回路110乃至130のN型MOSFET11夫々に駆動信号を出力するための、電気角120度の位相差を有する論理信号U1、V1、W1をプリドライブ回路140に出力する。センサレスロジック回路150は、出力回路110乃至130のN型MOSFET12夫々に駆動信号を出力するための、電気角120度の位相差を有する論理信号U2、V2、W2をプリドライブ回路140に出力する。つまり、センサレスロジック回路150は、三相センサレスモータが回転するように、駆動電流が供給される駆動コイルが電気角60度毎に切り替わるような論理信号U1、U2、V1、V2、W1、W2をプリドライブ回路140に出力する。センサレスロジック回路150は、駆動コイルLu、Lv、Lwのうち駆動電流が供給されていない駆動コイルの一端のコイル電圧がスイッチ回路160の出力端子Oに印加されるように、スイッチ回路160における出力端子Oと入力端子U、V、Wの接続を制御する。例えば、図3の時刻T0から時刻T1の場合、センサレスロジック回路150は、スイッチ回路160の出力端子Oと入力端子Wが接続されるように、スイッチ回路160を制御する。

【0034】

出力回路110乃至130のN型MOSFET11、12が、センサレスロジック回路150の論理信号U1、U2、V1、V2、W1、W2に基づいてオンオフすると、駆動電流が、電源1から駆動コイルLu、Lv、Lwに供給される。これにより、予め定められた方向(例えば正回転)に三相センサレスモータが回転し、駆動コイルLu、Lv、Lwの端子UO、VO、WOと接続される一端には、電気角120度の位相差を有するコイル電圧Vu、Vv、Vwが発生する。尚、コイル電圧Vu、Vv、Vwは、三相センサレスモータの回転速度に応じた周波数を有している。コンパレータ170の非反転入力端子には、駆動コイルLu、Lv、Lwのうち駆動電流が供給されていない駆動コイルの一端のコイル電圧がスイッチ回路160を介して印加される。コンパレータ170の反転入力端子には、中性点P100の電圧が印加される。コンパレータ170は、コンパレータ170の非反転入力端子にスイッチ回路160を介して印加されたコイル電圧と、コンパレータ170の反転入力端子に印加された中性点P100の電圧と、が交差するゼロクロスポイントを検出する。コンパレータ170は、ゼロクロスポイントでエッジが切り替わり、矩形波状のFG信号をセンサレスロジック回路150に出力する。

【0035】

===モータ駆動装置の動作===

図1、図2、図3を参照してモータ駆動装置100の動作について説明する。

プリドライブ回路140は、センサレスロジック回路150から出力される論理信号U1、U2、V1、V2、W1、W2に基づいて、駆動信号を出力回路110乃至130のN型MOSFET11、12に出力する。出力回路110乃至130のN型MOSFET11、12は、プリドライブ回路140の駆動信号によってオンオフして、三相センサレスモータが回転するように駆動電流を駆動コイルLu、Lv、Lwに供給する。

【0036】

駆動コイルLuに駆動電流を供給するモータ駆動装置100の動作と、駆動コイルLv、Lwに駆動電流を供給するモータ駆動装置100の動作は同様であるので、駆動コイルLuに駆動電流を供給するモータ駆動装置100の動作について説明し、駆動コイルLv、Lwに駆動電流を供給するモータ駆動装置100の動作の説明は省略する。

【0037】

例えば、時刻T0から時刻T2の場合、センサレスロジック回路150は、ハイレベルの論理信号U1、ローレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11がオンし、N型MOSFET12がオフする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11がオンし、N型MOSFET12がオフするので、駆動電流は電源1から出力回路110のN型MOSFET11を介して駆動コイルLuに供給される。

【0038】

例えば、時刻T3から時刻T5の場合、センサレスロジック回路150は、ローレベルの論理信号U1、ハイレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11がオフし、N型MOSFET12がオンする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11がオフし、N型MOSFET12がオンするので、駆動電流は駆動コイルLuから出力回路110のN型MOSFET12を介してグランドGNDに供給される。

【0039】

例えば、時刻T2から時刻T3及び時刻T5から時刻T6の場合、センサレスロジック回路150は、ローレベルの論理信号U1、ローレベルの論理信号U2を出力する。前述したように、プリドライブ回路140は、出力回路110のN型MOSFET11、12がともにオフする駆動信号をN型MOSFET11、N型MOSFET12に出力する。よって、N型MOSFET11、12がともにオフするので、駆動電流は駆動コイルLuに供給されない。

【0040】

例えば、時刻T5の場合、センサレスロジック回路150は、ローレベルの論理信号U1を出力した状態で、時刻T5にハイレベルからローレベルへ変化する論理信号U2を出力する。前述したように、出力回路110のN型MOSFET11がオフした状態で、時刻T5に出力回路110のN型MOSFET12がオンからオフとなる。尚、P型MOSFET21はオフとなっている。その場合、駆動コイルLuに発生する回生電流でキックバック電圧KBが駆動コイルLuの一端に印加される。キックバック電圧KBによって電流が駆動コイルLuからツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDへ供給される。従って、駆動コイルLuからグランドGNDへ供給される電流によって、モータ駆動装置100で電力が消費されることとなる。

【0041】

ここで、キックバック電圧KBによるモータ駆動装置100の消費電力の値の一例を示す。例えば、キックバック電圧KBを24.7V、ツェナーダイオードZ1の順方向電圧を0.7V、抵抗R4の抵抗値を50KΩ、抵抗R112の抵抗値を2KΩ、N型MOSFET34のオン抵抗値を0Ωとする。駆動コイルLuからツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDへ供給される電流の電流値は、I=(24.7V−0.7V)÷(50KΩ+2KΩ)≒0.46mAとなる。よって、キックバック電圧KBによるモータ駆動装置100の消費電力の値は、24.7V×0.46mA≒0.01Wとなる。

【0042】

前述したように、プリドライブ回路140にハイレベルの論理信号U1が入力された場合、チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流が供給される。この電流によって、N型MOSFET11のゲートソース間にN型MOSFET11をオンさせる電圧が印加され、N型MOSFET11はオンする。P型MOSFET21のゲートには、N型MOSFET11のゲートソース間に印加された電圧から抵抗R3を介して電流が供給される。この電流によって、P型MOSFET21のゲートソース間にP型MOSFET21をオンさせる電圧が印加され、P型MOSFET21はオンする。プリドライブ回路140にローレベルの論理信号U1が入力された場合、N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流が供給される。N型MOSFET11のゲートソース間には、N型MOSFET11をオンさせる電圧が印加されていない状態となり、N型MOSFET11はオフする。P型MOSFET21のゲートソース間には、P型MOSFET21をオンさせる電圧が印加されない状態となり、P型MOSFET21はオフする。尚、抵抗R3によって、P型MOSFET21は、N型MOSFET11がオフした後にオフする。N型MOSFET11がオフした状態でN型MOSFET12がオンからオフした場合、回生電流がツェナーダイオードZ1、抵抗R4、抵抗R112、N型MOSFET34を介してグランドGNDに供給される。又、プリドライブ回路140の電源ライン141に電圧が印加されない場合、抵抗R1によって、N型MOSFET11のゲートがハイインピーダンスとなるのを防止することができる。又、プリドライブ回路140の抵抗R111、R112の抵抗値を夫々調整することによって、N型MOSFET11がオンする速度、オフする速度を夫々調整することができる。

【0043】

従って、モータ駆動装置100は、チャージポンプ回路1402から、P型MOSFET33、抵抗R111、寄生ダイオードBp1を介してN型MOSFET11のゲートに電流を供給することによって、N型MOSFETを確実にオンすることができる。又、モータ駆動装置100は、N型MOSFET11のゲートから、P型MOSFET21、抵抗R112、N型MOSFET34を介してグランドGNDに電流を供給することによって、N型MOSFET11を確実にオフすることができる。又、モータ駆動装置100は、N型MOSFET11がオフしている状態でN型MOSFET12がオンからオフした際に駆動コイルからグランドGNDへ供給される回生電流によるモータ駆動装置100の消費電力を抵抗R4によって減少させることができる。

【0044】

尚、上記実施形態は、本発明の理解を容易にするためのものであり、本発明を限定して解釈するためのものではない。本発明は、その趣旨を逸脱することなく、変更、改良され得るとともに、本発明にはその等価物も含まれる。

【0045】

本実施形態においては、三相センサレスモータの駆動コイルLu、Lv、Lwに駆動電流を供給するモータ駆動装置100について説明したが、これに限定されるものではない。例えば、端子UO、VO、WOに誘導性負荷を接続して誘導性負荷へ電流を供給する駆動装置を提供することも可能である。

【符号の説明】

【0046】

1 電源

11、12、32、34、36、38 N型MOSFET

21、31、33、35、37 P型MOSFET

100 モータ駆動装置

110、120、130 出力回路

140 プリドライブ回路

150 センサレスロジック回路

160 スイッチ回路

170 コンパレータ

1402 チャージポンプ回路

1403 レギュレータ回路

Bn1、Bn2、Bp1 寄生ダイオード

I1、I2、I3、I4 CMOS回路

Lu、Lv、Lw 駆動コイル

R1、R2、R3、R4、R111、R112、R113、R114 抵抗

Z1 ツェナーダイオード

【特許請求の範囲】

【請求項1】

コイルに電流を供給する第1N型MOSFETと、

前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、

前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、

前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、

ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、

前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、

前記P型MOSFETのドレインソースに並列接続される第1抵抗と、

を備え、

前記第1駆動信号が前記第1N型MOSFETのオンを示す信号である場合、前記第1駆動回路から前記第1N型MOSFETのゲートへ前記P型MOSFETの寄生ダイオードを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオンし、

前記第1駆動信号が前記第1N型MOSFETのオフを示す信号である場合、前記第1N型MOSFETのゲートから前記第1駆動回路へ前記P型MOSFETを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオフし、

前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して電流を供給する

ことを特徴とする駆動装置。

【請求項2】

前記P型MOSFETのゲートと前記クランプ回路との間に接続され、前記第1N型MOSFETがオフした後に前記P型MOSFETをオフさせる第2抵抗

を備えたことを特徴とする請求項1に記載の駆動装置。

【請求項3】

前記第1N型MOSFETのゲートソース間に接続され、前記第1駆動回路の電源ラインに電圧が印加されないときに前記第1N型MOSFETのゲートをプルダウンする第3抵抗

を備えたことを特徴とする請求項1又は2に記載の駆動装置。

【請求項4】

前記第1駆動回路は、

前記第1N型MOSFETのオン速度を調整する第4抵抗と、

前記第1N型MOSFETのオフ速度を調整する第5抵抗と、

前記第4抵抗又は前記第5抵抗を介して前記第1駆動信号を出力するCMOS回路と、

を有することを特徴とする請求項1乃至3の何れかに記載の駆動装置。

【請求項5】

前記コイルはモータコイルであり、

前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して供給される電流は回生電流である

ことを特徴とする請求項1乃至4の何れかに記載の駆動装置。

【請求項1】

コイルに電流を供給する第1N型MOSFETと、

前記第1N型MOSFETと直列接続され、前記コイルから電流が供給される第2N型MOSFETと、

前記第2N型MOSFETがオフしているときに前記第1N型MOSFETをオンするように第1駆動信号を出力する第1駆動回路と、

前記第1N型MOSFETがオフしているときに前記第2N型MOSFETをオンするように第2駆動信号を出力する第2駆動回路と、

ドレインソース路が前記第1駆動回路の出力及び前記第1N型MOSFETのゲートの間に接続されるP型MOSFETと、

前記第1N型MOSFET及び前記P型MOSFETのゲートソース間電圧を共に所定電圧にクランプするクランプ回路と、

前記P型MOSFETのドレインソースに並列接続される第1抵抗と、

を備え、

前記第1駆動信号が前記第1N型MOSFETのオンを示す信号である場合、前記第1駆動回路から前記第1N型MOSFETのゲートへ前記P型MOSFETの寄生ダイオードを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオンし、

前記第1駆動信号が前記第1N型MOSFETのオフを示す信号である場合、前記第1N型MOSFETのゲートから前記第1駆動回路へ前記P型MOSFETを介して電流を供給することにより、前記第1N型MOSFET及び前記P型MOSFETをオフし、

前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して電流を供給する

ことを特徴とする駆動装置。

【請求項2】

前記P型MOSFETのゲートと前記クランプ回路との間に接続され、前記第1N型MOSFETがオフした後に前記P型MOSFETをオフさせる第2抵抗

を備えたことを特徴とする請求項1に記載の駆動装置。

【請求項3】

前記第1N型MOSFETのゲートソース間に接続され、前記第1駆動回路の電源ラインに電圧が印加されないときに前記第1N型MOSFETのゲートをプルダウンする第3抵抗

を備えたことを特徴とする請求項1又は2に記載の駆動装置。

【請求項4】

前記第1駆動回路は、

前記第1N型MOSFETのオン速度を調整する第4抵抗と、

前記第1N型MOSFETのオフ速度を調整する第5抵抗と、

前記第4抵抗又は前記第5抵抗を介して前記第1駆動信号を出力するCMOS回路と、

を有することを特徴とする請求項1乃至3の何れかに記載の駆動装置。

【請求項5】

前記コイルはモータコイルであり、

前記第1N型MOSFETがオフした状態で前記第2N型MOSFETがオンからオフした場合、前記コイルから前記第1駆動回路へ前記クランプ回路及び前記第1抵抗を介して供給される電流は回生電流である

ことを特徴とする請求項1乃至4の何れかに記載の駆動装置。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−60742(P2012−60742A)

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願番号】特願2010−200159(P2010−200159)

【出願日】平成22年9月7日(2010.9.7)

【出願人】(311003743)オンセミコンダクター・トレーディング・リミテッド (166)

【Fターム(参考)】

【公開日】平成24年3月22日(2012.3.22)

【国際特許分類】

【出願日】平成22年9月7日(2010.9.7)

【出願人】(311003743)オンセミコンダクター・トレーディング・リミテッド (166)

【Fターム(参考)】

[ Back to top ]