駆動装置

【課題】バッテリから直接供給される電源電圧VCCに対応する。

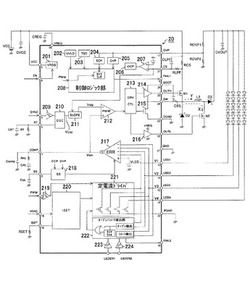

【解決手段】LEDドライバ20は、入力電圧から出力電圧を生成してLEDに供給する昇降圧DC/DCコンバータを制御する昇降圧DC/DCコントローラブロックと、LEDの出力電流を生成するカレントドライバブロックを有し、昇降圧DC/DCコンバータは、スイッチN1及びN2と、ダイオードD2及びD3と、インダクタL2と、を含み、昇降圧DC/DCコントローラブロックは、V1〜V4とVLEDとの差分を増幅してVerrを生成するエラーアンプ217と、Vslpを生成するスロープ電圧生成部211と、VerrとVslpを比較して比較信号を生成するPWMコンパレータ212と、比較信号に基づいて駆動信号を生成するドライバ制御部213と、駆動信号に基づいてN1及びN2を各々オン/オフさせるドライバ214及び215を含む。

【解決手段】LEDドライバ20は、入力電圧から出力電圧を生成してLEDに供給する昇降圧DC/DCコンバータを制御する昇降圧DC/DCコントローラブロックと、LEDの出力電流を生成するカレントドライバブロックを有し、昇降圧DC/DCコンバータは、スイッチN1及びN2と、ダイオードD2及びD3と、インダクタL2と、を含み、昇降圧DC/DCコントローラブロックは、V1〜V4とVLEDとの差分を増幅してVerrを生成するエラーアンプ217と、Vslpを生成するスロープ電圧生成部211と、VerrとVslpを比較して比較信号を生成するPWMコンパレータ212と、比較信号に基づいて駆動信号を生成するドライバ制御部213と、駆動信号に基づいてN1及びN2を各々オン/オフさせるドライバ214及び215を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、負荷(発光ダイオード等)の駆動制御を行う駆動装置に関するものである。

【背景技術】

【0002】

LCD[Liquid Crystal Display]パネル(例えばカーナビモニタ)のバックライトとして、現行では、冷陰極管蛍光ランプ(CCFL[Cold Cathode Fluorescent Lamp])が主に用いられているが、Hgフリー対応の流れや、高輝度・省電力・高寿命などの利点から、近年では、白色LED[Light Emitting Diode]が実用化されており、その駆動制御を行うLED駆動装置(いわゆるLEDドライバ)についても、様々な技術が開示・提案されている(例えば、特許文献1を参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−13183号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

PWM制御でLEDを発光させようとするとき、素子の特性で制御できるデューティ比の範囲が制限されてしまっていた。

【0005】

また、素子の特性によって、LEDを発光させる電流の精度が低かった。

【0006】

本発明は、上記の問題点に鑑み、制御可能なデューティ比の範囲を広げ、素子の変動に依らず、制御電流の精度を高めることが可能な駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成すべく、本発明に係る駆動装置は、一方の端子にパルス状の電流が入力され、更に前記一方の端子と制御端子が接続された第1のトランジスタと、一方の端子に少なくとも1つの負荷が接続され、他方の端子が前記第1のトランジスタの他方の端子と共に基準電位に接続され、制御端子が前記第1のトランジスタの制御端子にそれぞれ接続された第2のトランジスタと、前記第1のトランジスタの制御端子と前記第1のトランジスタの他方の端子との間に、抵抗素子が接続された構成(第1の構成)とされている。

【0008】

また、上記第1の構成から成る駆動装置は、前記第1のトランジスタと前記第2のトランジスタの一方の端子にそれぞれ一定の電圧を供給する第2の基準電圧供給部と第2の基準電圧供給部とを更に備えた構成(第2の構成)にするとよい。

【発明の効果】

【0009】

本発明に係る駆動装置であれば、抵抗を挿入することによって、トランジスタの立ち上がりを早めることができることにより、制御可能なデューティ比の範囲を広げることが可能となる。

【0010】

また、本発明に係る駆動装置であれば、トランジスタの一方の端子を一定電圧とすることにより、素子の変動に依らず、制御電流の精度を高めることが可能となる。

【図面の簡単な説明】

【0011】

【図1】は、本発明に係る半導体装置の第1実施形態を示すブロック図である。

【図2】は、半導体装置10のピン配置図である。

【図3】は、外部端子のピン番号、端子名、及び、機能を示した対応表である。

【図4】は、半導体装置10の外部接続を説明するための図である。

【図5】は、外部素子の定数の一例を示す設定表である。

【図6】は、外部端子の入出力等価回路図である。

【図7】は、半導体装置10の電気的特性を示す表である。

【図8】は、FAIL1信号の出力段を示す図である。

【図9】は、FAIL2信号の出力段を示す図である。

【図10】は、オープン/ショートの検出動作を説明するための図である。

【図11】は、LEDイネーブル信号LEDEN1、LEDEN2の入力論理と、LED出力端子LED1〜LED4のオン/オフ状態との相関関係を示す真理値表である。

【図12】は、電流設定部116と定電流ドライバ117の一構成例を示す回路図である。

【図13】は、抵抗RSETと出力電流ILEDとの相関関係を示すグラフである。

【図14】は、PWM調光制御の一例を示すタイミングチャートである。

【図15】は、抵抗RTと発振周波数FOSCとの相関関係を示すグラフである。

【図16】は、OCP部111の動作に関連する外部素子の接続関係を説明するための図である。

【図17】は、コイルL1の選定に関して説明するための図である。

【図18】は、出力コンデンサCVOUTの選定に関して説明するための図である。

【図19】は、入力コンデンサCVCCの選定に関して説明するための図である。

【図20】は、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して説明するための図である。

【図21】は、トランジスタQ1のゲート・ソース間容量とソフトスタート時間との相関関係を示すグラフである。

【図22】は、DC/DCコンバータのLC共振回路を示す回路図である。

【図23】は、位相進み手段の第1例(出力コンデンサのESR成分)を示す回路図である。

【図24】は、位相進み手段の第2例(COMP端子に接続されるCR成分)を示す回路図である。

【図25】は、半導体装置10の動作シーケンスを示すタイミングチャートである。

【図26】は、本発明に係る半導体装置の第2実施形態を示すブロック図である。

【図27】は、半導体装置20のピン配置図である。

【図28】は、外部端子のピン番号、端子名、及び、機能を示した対応表である。

【図29】は、半導体装置20の電気的特性を示す表である。

【図30】は、電流設定部220と定電流ドライバ221の一構成例を示す回路図である。

【図31】は、ミラー比とトランジスタサイズとの相関関係を示す模式図である。

【図32】は、抵抗を千鳥配置としたレイアウト図である。

【発明を実施するための形態】

【0012】

図1は、本発明に係る半導体装置の第1実施形態を示すブロック図である。

【0013】

まず、本実施形態の半導体装置10の概要について述べる。

【0014】

半導体装置10は、36V高耐圧の白色LEDドライバICであり、昇圧DC/DCコンバータ、並びに、4チャネル出力の定電流ドライバが1チップに集積化されている。なお、半導体装置10は、PWM[Pulse Width Modulation]制御、及び、VDAC制御のいずれによっても、白色LEDの調光制御が可能である。

【0015】

次に、本実施形態の半導体装置10の特長について述べる。

【0016】

第1の特長は、電源電圧VCCの入力電圧範囲が4.5〜30[V]である点である。第2の特長は、昇圧DC/DCコントローラを内蔵している点である。第3の特長は、LEDに出力電流ILEDを供給する4チャネルの定電流ドライバを内蔵している点である(最大電流値:150[mA])。第4の特長は、PWM調光(デューティ比:0.38〜99.5[%])に対応している点である。第5の特長は、各種保護機能部(UVLO[Under Voltage Lock Out]、OVP[Over Voltage Protection]、TSD[Thermal Shut Down]、OCP[Over Current Protection])を内蔵している点である。第6の特長は、LED異常状態(オープン/ショート)の検出機能を内蔵している点である。第7の特長は、HSOP−M28パッケージ(図2を参照)を採用した点である。

【0017】

なお、本実施形態の半導体装置10は、カーナビモニタのバックライトや、中小型LCDパネルのバックライトなどの駆動制御用として用いられる。

【0018】

上記特長を有する本実施形態の半導体装置10は、図1に示すように、基準電圧生成部101(以下では、VREG部101と呼ぶ)と、スイッチ102と、減電圧保護部103(以下では、UVLO部103と呼ぶ)と、温度保護部104(以下では、TSD部104と呼ぶ)と、過電圧保護部105(以下では、OVP部105と呼ぶ)と、入力バッファ106と、発振器部107と、PWMコンパレータ108と、制御ロジック部109と、ドライバ110と、過電流保護部111(以下では、OCP部111と呼ぶ)と、コンパレータ112と、エラーアンプ113と、ソフトスタート部114と、入力バッファ115と、電流設定部116と、定電流ドライバ117と、オープン/ショート検出部118と、入力バッファ119及び120と、を集積化して成る。

【0019】

なお、半導体装置10の上記回路部は、VREGブロック(VREG部101)と、昇圧DC/DCコントローラブロック(スイッチ102、入力バッファ106、発振器部107、PWMコンパレータ108、制御ロジック部109、ドライバ110、OCP部111、コンパレータ112、エラーアンプ113、及び、ソフトスタート部114)と、カレントドライバブロック(入力バッファ115、電流設定部116、定電流ドライバ117、オープン/ショート検出部118、及び、入力バッファ119及び120)と、保護ブロック(UVLO部103、TSD部104、OVP部105)の4ブロックに大別することができる。

【0020】

また、本実施形態の半導体装置10は、外部との電気的接続を確立する手段として、28本の外部端子(1ピン〜28ピン)を有して成る。

【0021】

図2は、半導体装置10のピン配置図であり、図3は、外部端子のピン番号、端子名、及び、機能を示した対応表である。なお、図2において、半導体装置10の中央部両サイドに設けられた幅広の端子は、サブグランドと繋がるFIN端子であり、放熱性を良くするためのものである。

【0022】

次に、半導体装置10の外部接続について詳細な説明を行う。

【0023】

図4は、半導体装置10の外部接続を説明するための図である。

【0024】

図4に示した外部素子に関して、デカップリングコンデンサCVCC、CREGは、できる限り、ICピンの直近に接続することが望ましい。

【0025】

CS端子(22ピン)、GND端子(7ピン)、及び、PGND(21ピン)には、大電流が流れる可能性があるため、それぞれ独立で配線するとともに、インピーダンスを低くすることが望ましい。

【0026】

VDAC端子(8ピン)、ISET端子(9ピン)、RT端子(26ピン)、及び、COMP端子(28ピン)には、ノイズが載らないように留意すべきである。

【0027】

PWM端子(5ピン)、SYNC端子(6ピン)、LED1端子(12ピン)、LED2端子(14ピン)、LED3端子(15ピン)、及び、LED4端子(17ピン)は、スイッチングされるため、周辺パターンに影響を与えないように留意すべきである。

【0028】

図4中の太線部分は、幅広のパターンで、かつ、できるだけ短くレイアウトすることが望ましい。

【0029】

なお、本実施形態の半導体装置10では、パワートランジスタQ2を外付けとしているので、放熱性を高めることが可能となる。

【0030】

図5は、外部素子の定数の一例を示す設定表である。なお、本図に例示した定数は、電源電圧VCC=12[V]、LED5直4並列、出力電流ILED=50[mA]のときに動作を確認した定数である。従って、使用条件などによって最適値は異なるため、十分評価の上、定数を決定することが望ましい。

【0031】

図6は、外部端子の入出力等価回路図である。

【0032】

図6に示すように、半導体装置10の外部端子には、いずれも静電保護ダイオードが接続されている。

【0033】

また、コントロール関連端子であるPWM端子(5ピン)、SYNC端子(6ピン)、VDAC端子(8ピン)、ISET端子(9ピン)、LEDEN1端子(10ピン)、LEDEN2端子(11ピン)、CS端子(22ピン)、SWOUT端子(23ピン)、EN端子(24ピン)、OVP端子(25ピン)、RT端子(26ピン)、SS端子(27ピン)、COMP端子(28ピン)については、上側(信号ラインから電源ラインに電荷を引き抜く経路側)の静電保護ダイオードのカソードを基準電圧VREGや電源電圧VCCの印加端に接続するのではなく、中間電圧CL10V(例えば10[V]、図6の最右下欄を参照)の印加端に接続する構成とされている。

【0034】

このような構成とすることにより、電源電圧VCCが印加されていない場合や、イネーブル信号ENによって基準電圧VREGが生成されていない場合に、外部端子に正電圧が印加されたとしても、静電保護ダイオードを介して基準電圧ラインや電源電圧ラインに過大電流が流れ込むことはないので、回路の破壊や誤動作を防止することが可能となる。

【0035】

図7は、上記構成から成る半導体装置10の電気的特性を示す表である。なお、図7に示す電気的特性は、特に指定のない限り、電源電圧VCC=12[V]、周囲温度Ta=25[℃]での数値を示している。

【0036】

次に、半導体装置10のVREGブロック(VREG部101)について、先出の図1などを参照しながら、詳細な説明を行う。

【0037】

VREG部101は、EN端子(24ピン)に入力されるイネーブル信号ENがハイレベルであるときに、VCC端子(1ピン)に入力される電源電圧VCC(12[V])からの基準電圧VREG(5[V](Typ.))を生成する手段である。この基準電圧VREGは、内部回路の電源として使用され、また、IC外で端子をハイレベル電圧に固定するときにも使用される。

【0038】

また、VREG部101は、UVLO機能を具備しており、2.9[V](Typ.)以上になると動作を開始し、2.8[V](Typ.)以下になると動作を停止する。

【0039】

なお、VREG端子(4ピン)は、位相補償用の容量CREG(10μF(Typ.))を接続するための外部端子である。このような位相補償用の容量CREGを接続することにより、VREG部101の回路動作を安定化することが可能となる。

【0040】

次に、半導体装置10の自己診断機能について、詳細な説明を行う。

【0041】

本実施形態の半導体装置10は、自身に内蔵された保護回路の動作状態を示すべく、FAIL1端子(3ピン)及びFAIL2端子(20ピン)から、オープンドレイン形式でFAIL1信号及びFAIL2信号を各々出力する機能を具備している。

【0042】

UVLO部103、TSD部104、OVP部105、及び、OCP部111のいずれかが異常状態を検出し、その出力信号がローレベルとされたとき、制御ロジック部109は、図8に示す出力段を介して、FAIL1信号をローレベルにするとともに、SWOUT端子(23ピン)をローレベル固定とすることで、昇圧動作を停止する。

【0043】

ただし、OCP部111は、パルスバイパルス方式であるため、昇圧DC/DCコンバータの発振周波数FOSCで決定される1周期分だけ、SWOUT端子がローレベル固定とされた後、昇圧動作が復帰される。このようなパルスバイパルス方式により、回路動作を完全に停止させないまま、電流制限をかけることができるので、誤動作で回路が停止された場合でも、遅滞なく自動復帰が行われるため、ユーザにとって使い勝手が良い。

【0044】

また、UVLO部103、TSD部104、及び、OVP部105の少なくとも一が異常状態を検出したとき、LED1端子、LED2端子、LED3端子、及び、LED4端子(12ピン、14ピン、15ピン、17ピン)は、いずれもオープン(ハイインピーダンス)とされる。

【0045】

また、FAIL1端子(3ピン)から出力されるFAIL1信号と、LOADSW端子(2ピン)から出力されるLOADSW信号とは、互いに反転信号となっており、FAIL1信号がローレベルとされると、LOADSW信号はスイッチ102を用いてハイレベルとされる。従って、UVLO部103、TSD部104、OVP部105、及び、OCP部111のいずれかが異常状態を検出したとき、LOADSW端子(2ピン)に外部接続されるロードスイッチ(図4のPチャネル型電界効果トランジスタQ1)はオフとされる。従って、半導体装置10の異常時には、昇圧動作を停止させて、ICが破壊や発煙・発火に至るのを未然に防止することが可能となる。

【0046】

一方、FAIL2端子(20ピン)から出力されるFAIL2信号は、オープン/ショート検出部118が異常状態(オープン状態またはショート状態)を検出したとき、図9に示す出力段を介してローレベル出力とされる。なお、オープン/ショート検出部118から出力されるFAIL2信号は、ラッチ方式となっており、そのラッチ解除は、イネーブル信号ENのオン/オフ(延いてはUVLO信号のオン/オフ)に基づいて行われる。

【0047】

オープン/ショート検出部118は、図10に示す通り、所定のLED制御電圧VLED(0.8[V](Typ.))に維持されているはずのLED端子電圧V1〜V4(LED1端子〜LED4端子の各端子電圧)が0.15[V](Typ.)以下となったときに、そのLED端子がオープンであると判定し、さらに、OVP端子(25ピン)の端子電圧VP(出力電圧VOUTの分圧電圧)が1.7[V](Typ.)に達したときに、オープンと判定されたLED端子に対する電流出力をオフとすべく、定電流ドライバ117に対して指示を送るとともに、FAIL2信号をローレベルに遷移させる。なお、図10の例ではLED1端子がオープンとなった場合を例示している。

【0048】

このように、LED端子のオープン検出と電流出力のオフ制御を2段階で実施することにより、不必要なシャットダウンを回避することが可能となる。

【0049】

なお、上記のオープン検出については、OVP部105による過電圧検出で代用することも可能である。すなわち、OVP部105では、OVP端子の端子電圧VPが所定の過電圧検出電圧VDOVP(2.0[V](Typ.))に達したことを検出して、DC/DCコンバータの昇圧動作が停止され、全チャネルの電流出力がオフとされるので、敢えてオープン検出を行わなくとも、過電圧検出とオープン検出とを兼ねた形で、全チャネルの電流出力をオフとすることが可能である。

【0050】

ただし、オープンとなったチャネルだけをオフしたい場合には、上記で説明した通り、LED端子電圧V1〜V4を監視することで、オープンとなったLED端子を特定し、そのチャネルのみをオフとすればよい。特に、全チャネルの電流出力をオフにすると、使用に支障を生じるアプリケーション(カーナビモニタのバックライト駆動装置など)への適用に際しては、各チャネルの電流出力を個別にオフし得る本実施形態の構成が望ましい。

【0051】

また、オープン/ショート検出部118は、LED端子電圧V1〜V4が4.5[V](Typ.)以上となったときにショートと判断する。言い換えれば、正常時と異常時との間で、LED端子電圧の差分が3.7[V](=4.5[V]−0.8[V])(Typ.)以上となったときに、ショートが検出されることになる。

【0052】

なお、白色LEDの順方向降下電圧VFは約3.4[V]であるため、上記の設定例では、LED1個がショートしただけではショート検出されず、LED2個以上がショートした場合にショート検出される。このようなスレッショルドレベルの設定により、LEDショートが生じてはいるものの、その使用に際して、さほど支障を来さない範囲については、不要なシャットダウンを回避することが可能となる。

【0053】

このように、オープン/ショート検出部118でのショート検出は、例えば、LED1端子〜LED4端子に各々外部接続されるLED列のうち、いずれか一のLED列について、これを形成する一つのLEDがショート状態(アノード/カソード間の短絡状態)となった結果、当該ショート状態となったLEDの順方向降下電圧VF分だけ、LED列全体としての順方向降下電圧が低い状態となり、一のLED端子電圧が他のLED端子電圧に比べて、LEDの順方向降下電圧VF分だけ高くなった状態を検出する動作を言う。従って、図1でも示したように、オープン/ショート検出部118とOVP部105とは、別の保護ブロックとして形成されている。

【0054】

ただし、本実施形態の半導体装置10では、一旦オープン/ショートが検出されると、以後、ショート検出信号はマスクされる。図10の例に即して述べると、LED1端子のオープンが検出されて以後、その他のLED2端子〜LED4端子については、そのショート検出信号がマスクされる。このようなマスク制御により、LED1端子がオープンとなった結果、LED端子電圧V1がほぼGNDまで低下し、これを受けて出力電圧VOUTが上昇し、それに追従してLED端子電圧V2〜V4が通常時より上昇した場合であっても、これをショートと誤検出することがなくなる。なお、オープン検出信号は、オープン/ショート検出後もマスクされることはない。

【0055】

また、上記のショート検出信号は、PWM駆動による出力電流ILEDのオフ期間にもマスクされる。このようなマスク制御により、出力電流ILEDのオフ期間において、LED端子電圧V1〜V4が跳ね上がった場合でも、これをショートと誤検出することがなくなる。なお、上記のマスク制御に関しては、PWM信号の論理変遷タイミングと、出力電流ILEDのオン/オフタイミングとの間に遅延が生じることを考慮して、出力電流ILEDを流し始めるタイミング(定電流ドライバ117の出力トランジスタがオンするタイミング)から、PWM信号がローレベルに立ち下がるタイミングまでをマスクすればよい(後出の図13を参照)。

【0056】

また、LED1端子〜LED4端子に付加的な容量が接続されると、出力オン時にLED端子電圧V1〜V4が低下するのが遅くなり、ショート検出が誤動作することがあるので、注意が必要である。また、FAIL1信号及びFAIL2信号は、いずれもオープンドレイン形式であるため、FAIL1端子及びFAIL2端子は、基準電圧VREGの印加端に対して抵抗(図4の抵抗RFL1、RFL2)でプルアップされている。

【0057】

次に、半導体装置10のカレントドライバブロック(入力バッファ115、電流設定部116、定電流ドライバ117、オープン/ショート検出部118、及び、入力バッファ119及び120)について、詳細な説明を行う。

【0058】

LED出力端子LED1〜LED4のうち、定電流ドライバ117からの出力電流ILEDを使用しない出力端子(延いては、点灯させないLED列)がある場合には、LEDEN1端子(10ピン)、及び、LEDEN2端子(11ピン)を用いて、LED出力端子LED1〜LED4に対する電流出力を各個にオフすることが可能である。

【0059】

図11は、LEDイネーブル信号LEDEN1、LEDEN2の入力論理と、LED出力端子LED1〜LED4のオン/オフ状態との相関関係を示す真理値表である。

【0060】

なお、LEDイネーブル信号LEDEN1、LEDEN2を用いることなく、使用しないLED端子をオープンすると、オープン/ショート検出部118において、オープン検出が誤動作してしまう。また、LEDイネーブル信号LEDEN1、LEDEN2を用いて、LED端子への電流出力を適宜オフさせた場合にも、エラーアンプ113の入力段は動作しているため、LED1端子〜LED4端子は、GND固定にせず、オープンもしくは定電圧VREGの印加端に接続しておくことが望ましい。また、出力電流ILEDをPWM駆動している際には、LEDイネーブル信号LEDEN1、LEDEN2を切り替えない方が望ましい。

【0061】

次に、出力電流ILEDの設定方法について、図12を参照しながら詳細に説明する。

【0062】

図12は、電流設定部116と定電流ドライバ117の一構成例を示す回路図である。

【0063】

図12に示すように、電流設定部116は、オペアンプA1と、直流電圧源A2と、npn型バイポーラトランジスタA3と、抵抗A4、A5と、pnp型バイポーラトランジスタA6〜A9と、抵抗A10(抵抗値R)と、を有して成る。

【0064】

オペアンプA1の第1非反転入力端(+)は、VDAC端子(8ピン)に接続されている。オペアンプA2の第2非反転入力端(+)は、直流電圧源A2の正極端に接続されており、所定の定電圧VISET(=2.0[V])が印加されている。直流電圧源A2の負極端は、接地端に接続されている。オペアンプA2の反転入力端(−)は、ISET端子(9ピン)に接続されている。トランジスタA3のベースは、オペアンプA1の出力端に接続されている。トランジスタA3のエミッタは、ISET端子に接続されている。

【0065】

抵抗A4、A5の各一端は、いずれも基準電圧VREGの印加端に接続されている。抵抗A4の他端は、トランジスタA6のエミッタに接続されている。抵抗R5の他端は、トランジスタA7のエミッタに接続されている。トランジスタA6、A7のベースは、互いに接続されており、その接続ノードは、トランジスタA7のコレクタに接続されている。トランジスタA6のコレクタは、トランジスタA8のエミッタに接続されている。トランジスタA7のコレクタは、トランジスタA9のエミッタに接続されている。トランジスタA8、A9のベースは、互いに接続されており、その接続ノードは、トランジスタA8のコレクタに接続されている。トランジスタA8のコレクタは、トランジスタA3のコレクタに接続されている。トランジスタA9のコレクタは、抵抗A10を介して、接地端に接続されている。

【0066】

一方、図12に示すように、定電流ドライバ117は、LED1端子〜LED4端子に対して各々出力電流ILEDを供給する4チャネルの出力段Ch1、Ch2、Ch3、Ch4を有して成る。なお、出力段Ch1は、オペアンプB1と、Nチャネル型電界効果トランジスタB2と、抵抗B3(抵抗値5R)と、カレントミラー回路B4(ミラー比1:1)と、抵抗B5(抵抗値5R)と、オペアンプB6と、Nチャネル型電界効果トランジスタB7と、抵抗B8(抵抗値5R)と、カレントミラー回路B9(ミラー比1:10)と、オペアンプB10と、直流電圧源B11と、Nチャネル型電界効果トランジスタB12〜B14と、オペアンプB15と、直流電圧源B16と、Nチャネル型電界効果トランジスタB17と、抵抗B18と、を有して成る。

【0067】

オペアンプB1の非反転入力端(+)は、トランジスタA9と抵抗A10との接続ノードに接続されている。オペアンプB1の反転入力端(−)は、抵抗B3の一端に接続されている。抵抗B3の他端は、接地端に接続されている。トランジスタB2のドレインは、カレントミラー回路B4の入力端に接続されている。トランジスタB2のソースは、抵抗B3の一端に接続されている。トランジスタB2のゲートは、オペアンプB1の出力端に接続されている。カレントミラー回路B4の電源入力端は、基準電圧VREGの印加端に接続されている。

【0068】

オペアンプB6の非反転入力端(+)は、カレントミラー回路B4の出力端と抵抗B5の一端に各々接続されている。オペアンプB6の反転入力端は、抵抗B8の一端に接続されている。抵抗B5、B8の他端は、いずれも接地端に接続されている。トランジスタB7のドレインは、カレントミラー回路B9の入力端に接続されている。トランジスタB7のソースは、抵抗B8の一端に接続されている。トランジスタB7のゲートは、オペアンプB6の出力端に接続されている。カレントミラー回路B9の電源入力端は、基準電圧VREGの印加端に接続されている。

【0069】

オペアンプB10の非反転入力端(+)は、直流電圧源B11の正極端に接続されている。直流電圧源B11の負極端は、接地端に接続されている。トランジスタB12のドレインは、カレントミラー回路B9の出力端に接続されている。トランジスタB12のソースは、オペアンプB10の反転入力端(−)に接続されている。トランジスタB12のゲートは、オペアンプB10の出力端に接続されている。

【0070】

トランジスタB13のドレインは、トランジスタB12のソースに接続されている。トランジスタB13、B14のゲートは互いに接続されており、その接続ノードは、トランジスタB12のドレインに接続される一方、抵抗B18を介して接地端にも接続されている。トランジスタB13、B14のソースは、いずれも接地端に接続されている。

【0071】

オペアンプB15の非反転入力端(+)は、直流電圧源B16の正極端に接続されている。直流電圧源B16の負極端は、接地端に接続されている。トランジスタB17のドレインは、LED1端子に接続されている。トランジスタB17のソースは、オペアンプB15の反転入力端(−)に接続される一方、トランジスタB14のドレインにも接続されている。トランジスタB17のゲートは、オペアンプB15の出力端に接続されている。

【0072】

なお、定電流ドライバ117を構成するその余の出力段Ch2〜Ch4は、上記の出力段Ch1と同様の構成から成るため、詳細な説明は割愛する。

【0073】

上記構成から成る電流設定部116、及び、定電流ドライバ117において、出力電流ILEDは、次の(1)式に基づいて設定される。

【0074】

【数1】

【0075】

上記(1)式において、min{VDAC,2.0[V]}というパラメータは、VDAC端子(8ピン)に入力される制御電圧VDACと、電流設定部116の内部で予め定められた定電圧VISET(=2.0[V])のうち、いずれか低い方の電圧値である。また、RSETというパラメータは、ISET端子(9ピン)に外部接続される抵抗RSETの抵抗値であり、3300(Typ.)というパラメータは、定電流ドライバ117の回路内部で決まる定数である。

【0076】

すなわち、ISET端子(9ピン)に抵抗RSETをプルダウン接続することで、これに流れる基準電流ISETの所定ゲイン倍(例えば3300倍)が出力電流ILEDの最大値(例えば50[mA])として設定される形となっている。

【0077】

図12の例に即して具体的に述べると、定電流ドライバ117では、まず、オペアンプB1、トランジスタB2、及び、抵抗B3(抵抗値5R)を用いて、抵抗A10の端子電圧Va(=ISET×R)が電圧/電流変換され、基準電流ISETを1/5とした中間電流Ia(=1/5ISET)が生成される。次に、カレントミラー回路B4を用いて、中間電流Iaが1:1でミラーされ、中間電流Ib(=1/5ISET)が生成される。次に、抵抗B5(抵抗値5R)を用いて、中間電流Ibが電流/電圧変換され、端子電圧Vb(=ISET×R)が生成される。次に、オペアンプB6、トランジスタB7、並びに、抵抗B8(抵抗値5R)を用いて、抵抗B5の端子電圧Vbが電圧/電流変換され、中間電流Ic(=1/5ISET)が生成される。次に、カレントミラー回路B9を用いて、中間電流Icが1:10でミラーされ、基準電流ISETを2倍とした中間電流Id(=2ISET)が生成される。そして、最終的には、トランジスタB13、B14から成るカレントミラー回路を用いて、中間電流Idが1:1650でミラーされ、基準電流ISETを3300倍とした出力電流ILED(=3300ISET)が生成される。

【0078】

なお、出力電流ILEDの精度を高めるために、最終段のカレントミラー回路については、オペアンプB10、B15を用いて、トランジスタB13、B14のドレイン・ソース間電圧が同一(例えば0.3[V])とされている。また、定電流ドライバ117は、入力される基準電流ISETに基づいて、電圧/電流変換と電流/電圧変換を繰り返しながら、所望の出力電流ILEDを生成する構成とされている。従って、上記変換処理に用いる抵抗素子(図12の例では、抵抗B3、B5、B8)が増え、延いては、そのトリミング機会が増加する。このように、トリミング可能な抵抗を数多く有する構成であれば、それらの抵抗値を微調整することにより、出力電流ILEDの相対ばらつき幅:±4%、絶対ばらつき幅:±6%を実現することができ、延いては、輝度ばらつきの低減やLEDの長寿命化に貢献することが可能となる。

【0079】

図13は、抵抗RSETと出力電流ILEDとの相関関係を示すグラフである。なお、抵抗RSETとしては、300[kΩ]以下のものを用いることが望ましい。

【0080】

また、上記の制御電圧VDACを用いて、出力電流ILEDの可変制御(LEDの調光制御)を行う場合、その入力範囲は、0.1〜2.0[V]の範囲とすればよい。このような制御電圧VDACを印加することにより、出力電流ILEDを最大値から低減していくことが可能となる。

【0081】

一方、制御電圧VDACとして2.0[V]以上が入力された場合には、上記の(1)式で与えられるように、定電圧VISETの電圧値が選択されることになるため、制御電圧VDACによる調光機能が不使用状態となる。なお、制御電圧VDACによる調光機能を使用しない場合には、誤動作を回避する観点から、VDAC端子をオープンとせず、基準電圧VREG(5[V])の印加端に接続しておくとよい。

【0082】

また、本実施形態の半導体装置10では、上記の制御電圧VDACを用いたLEDの調光制御のほか、PWM端子(5ピン)に入力されるPWM信号を用いて、基準電流ISETのオン/オフ制御を行うことで、LEDの調光制御を行うことも可能である。

【0083】

すなわち、PWM信号に基づいて、出力電流ILEDの基準となる基準電流ISETをパルス電流とすれば、PWM信号のデューティ比が出力電流ILEDのデューティ比となるので、出力電流ILEDをその最大値(ないしは、制御電圧VDACで定められた電流値)から、見かけ上低減することが可能となる。なお、PWM信号に基づく基準電流ISETのオン/オフ制御手段(パルス電流生成手段)については、電流設定部116の出力段(定電流ドライバ117の前段)に設ければよい。

【0084】

また、本実施形態の半導体装置10では、PWM信号に対する出力電流ILEDの応答性を上げるため、最終段のカレントミラー回路について、トランジスタB13、B14のゲート・ソース間にプルダウン抵抗B18(500[kΩ])が挿入されている。このようなプルダウン抵抗B18の挿入により、トランジスタB13、B14の立ち上がりを早めることができるので、PWM調光能力の向上(最低デューティ比:0.38%(150[Hz]時))を実現することが可能となる。

【0085】

一方、PWM信号による調光機能を使用しない場合(デューティ比100%)には、PWM端子をハイレベル(例えば定電圧VREG)に固定すればよい。なお、PWM端子には、ローパスフィルタ(カットオフ周波数30[kHz])を挿入することが望ましい。

【0086】

図14は、PWM調光制御の一例を示すタイミングチャートであり、PWM信号と出力電流ILEDとの相関関係を示している。なお、図14(a)は、PWM信号の周波数が150[Hz]、デューティ比が0.38[%]である場合を示しており、図14(b)は、PWM信号の周波数が150[Hz]、デューティ比が50[%]である場合を示している。また、図14(c)は、PWM信号の周波数が20[kHz]、デューティ比が50[%]である場合を示している。なお、図14(a)、(b)、(c)の横軸は、いずれも時間軸であるが、PWM信号の周波数が各々大きく異なるため、その描写レンジは互いに異なっている。通常、PWM信号の周波数は、100〜200[Hz]程度で固定的に設定される。

【0087】

次に、半導体装置10の昇圧DC/DCコントローラブロック(入力バッファ106、発振部107、PWMコンパレータ108、制御ロジック部109、ドライバ110、OCP部111、コンパレータ112、エラーアンプ113、及び、ソフトスタート部114を含む回路ブロック)について詳細に説明する。

【0088】

まず、昇圧DC/DCコントローラブロックの基本動作(昇圧動作)について、先出の図1及び図4を参照しながら、詳細に説明する。

【0089】

トランジスタQ2は、SWOUT端子(23ピン)からの出力に応じてオン/オフ制御されるNチャネル電界効果型の出力パワートランジスタである。

【0090】

トランジスタQ2がオン状態にされると、コイルL1にはトランジスタQ2を介して接地端に向けたスイッチ電流が流れ、その電気エネルギが蓄えられる。なお、トランジスタQ2のオン期間において、既に出力コンデンサCVOUTに電荷が蓄積されていた場合、負荷である発光ダイオード列(図4では明示されていないが、出力電圧VOUTの引出端とLED1端子〜LED4端子との間に接続されるLED列)には、出力コンデンサCVOUTからの電流が流れることになる。また、このとき、ダイオードD1のアノード電位は、トランジスタQ2を介して、ほぼ接地電位まで低下するため、ダイオードD1は逆バイアス状態となり、出力コンデンサCVOUTからトランジスタQ2に向けて電流が流れ込むことはない。

【0091】

一方、トランジスタQ2がオフ状態にされると、コイルL1に生じた逆起電圧によってそこに蓄積されていた電気エネルギが放出される。このとき、ダイオードD1は順バイアス状態となるため、ダイオードD1を介して流れる電流は、負荷であるLED列に流れ込むとともに、出力コンデンサCVOUTを介して接地端にも流れ込み、出力コンデンサCVOUTを充電することになる。上記の動作が繰り返されることによって、負荷であるLED列には、出力コンデンサCVOUTによって昇圧され、かつ、平滑された出力電圧VOUTが供給される。

【0092】

このように、本実施形態の半導体装置10は、トランジスタQ2のオン/オフ制御によってエネルギ貯蔵素子であるコイルL1を駆動することにより、電源電圧VCCを昇圧して出力電圧VOUTを生成するチョッパ型昇圧回路の一構成要素として機能する。

【0093】

次に、昇圧DC/DCコントローラブロックの出力帰還制御について詳細に説明する。

【0094】

エラーアンプ113は、第1〜第4の反転入力端(−)に各々印加されるLED端子電圧V1〜V4の最低値と、非反転入力端(+)に入力される所定のLED制御電圧VLEDとの差分を増幅して誤差電圧Verrを生成する。すなわち、誤差電圧Verrの電圧値は、出力電圧VOUTがその目標設定値よりも低いほど高レベルとなる。

【0095】

一方、PWMコンパレータ108は、第1、第2の非反転入力端(+)に各々印加される誤差電圧Verr及び上限電圧Vlmtのいずれか低い方と、反転入力端(−)に印加される三角波電圧(ランプ波電圧)Voscとを比較することで、その比較結果に応じたデューティの比較信号(PWM駆動波形)を生成する。すなわち、比較信号の論理は、誤差電圧Verr(或いは上限電圧Vlmt)が三角波電圧Voscよりも高ければハイレベルとなり、低ければローレベルとなる。

【0096】

従って、定常動作時における比較信号のオンデューティ(単位期間に占めるトランジスタQ2のオン期間の比)は、誤差電圧Verrと三角波電圧Voscの相対的な高低に応じて変動する。

【0097】

制御ロジック部109は、上記の比較信号がハイレベルとされている間、ドライバ110を介して、SWOUT端子の端子電圧(すなわち、トランジスタQ2のゲート電圧)をハイレベルに保持する。従って、トランジスタQ2はオン状態とされる。一方、比較信号がローレベルとされている間には、SWOUT端子の端子電圧をローレベルに保持する。従って、トランジスタQ2はオフ状態とされる。

【0098】

このように、昇圧DC/DCコントローラブロックは、LED端子電圧V1〜V4(延いては出力電圧VOUT)のモニタ結果に基づいて、トランジスタQ2の駆動制御を行う構成とされている。従って、出力電圧VOUTを所望値に維持することが可能となる。

【0099】

次に、負荷であるLED列の直列数に関して説明する。

【0100】

上述した通り、半導体装置10の昇圧DC/DCコントローラブロックは、LED列のカソード電圧(すなわちLED端子電圧V1〜V4)を検出し、これがLED制御電圧VLED(=0.8[V](Typ.))となるように、LED列のアノードに印加される出力電圧VOUTを制御する。

【0101】

上記の昇圧動作は、PWM信号がハイレベルであり、LED列に対して出力電流ILEDが流されているときにのみ行われる。また、複数のLED列を駆動しているときには、LEDの順方向降下電圧VFが最も大きい列のLED端子電圧(言い換えれば、LED端子電圧の最低値)がLED制御電圧VLEDと一致するように制御される。従って、他の列のLED端子電圧は、順方向降下電圧VFのバラツキ分だけ高い電圧となる。

【0102】

なお、順方向降下電圧VFのバラツキ許容電圧Vper(=3.7[V](Typ.))については、ショート検出電圧VDSHT(=4.5[V](Typ.))、及び、LED制御電圧VLED(=0.8[V](Typ.))に基づいて、次の(2)式で設定される。

【0103】

【数2】

【0104】

また、オープン/ショート検出部118におけるオープン検出の際には、OVP部105における過電圧検出基準電圧VDOVP(=2.0[V](Typ.))の85%がトリガ電圧(オープン検出電圧VDOP2(=1.7[V](Typ.))として設定される(図7及び図10を参照)。これを、出力電圧VOUTに換算して考えると、通常動作時における出力電圧VOUTの最大値が30.6[V]=36[V]×0.85となる。従って、LEDの直列数Nは、出力電圧VOUTの最大値30.6[V]をLED1個の順方向降下電圧VFで除した値(30.6/VF)よりも小さくなるように制限が掛かる。

【0105】

次に、OVP部105に関して説明する。OVP端子(25ピン)には、出力電圧VOUTを抵抗分割して得られる分圧電圧VPが入力される。これと比較されるOVP部105の過電圧検出基準電圧VDOVPについては、先述の通り、LED列の直列数Nと順方向降下電圧VFのバラツキ許容電圧Vperに基づいて適宜決定すればよい。また、過電圧検出基準電圧VDOVPを決定する際には、オープン検出電圧VDOP2(=VDOVP×0.85)も考慮に入れて決定すべきである。なお、OVP部105が一旦保護動作を発動した後は、出力電圧VOUTが過電圧検出基準電圧VDOVPの77.5%まで低下したときに、その保護動作が解除される。

【0106】

例えば、抵抗分割回路の抵抗値をROVP1(昇圧電圧側)、ROVP2(GND側)とした場合、出力電圧VOUTが次の(3)式を満たしたときに、OVP部105の保護動作が発動することになる。

【0107】

【数3】

【0108】

なお、ROVP1=330[kΩ]、ROVP2=22[kΩ]、VDOVP=2.0[V]のとき、VOUT=32[V]以上でOVP部105の保護動作が発動する。

【0109】

次に、昇圧DC/DCコンバータの発振周波数FOSCに関して説明を行う。RT端子(26ピン)にプルダウン抵抗RTを外部接続することにより、発振器部107の内部コンデンサに対する充放電電流が決定され、三角波電圧Voscの発振周波数FOSCを設定することが可能である。RT端子に外部接続されるプルダウン抵抗RTの抵抗値については、下記の(4)式や図15を参考に設定すればよく、62.6〜523[kΩ]の範囲が望ましい。

【0110】

【数4】

【0111】

なお、上記(4)式中において、30×106[V/A/S]は、回路内部で決まる定数(±16.6%)であり、αは補正係数となっている(RT:α=50[kΩ]:0.98,60[kΩ]:0.985,70[kΩ]:0.99,80[kΩ]:0.994,90[kΩ]:0.996,100[kΩ]:1.0,150[kΩ]:1.01、200[kΩ]:1.02,300[kΩ]:1.03,400[kΩ]:1.04,500[kΩ]:1.045)。

【0112】

また、図15の周波数範囲から外れた設定では、スイッチングが停止する可能性があるため、留意が必要である。

【0113】

次に、外部同期発振周波数FSYNCに関して説明する。昇圧DC/DCコンバータに外部同期のためのクロックをSYNC端子(6ピン)に入力しているときには、途中で内部発振に切り替えるなどの動作を行わない方がよい。SYNC端子の入力論理をハイレベルからローレベルに切り替えた後、内部発振回路が動作し始めるまでには、約30[μsec](Typ.)程度の遅延時間を要する。SYNC端子に入力されたクロックは立ち上がりエッジのみ有効となっている。また、外部入力周波数が内部発振周波数に比べて遅い場合は、上記の遅延時間後、内部発振回路が動作し始めるので、そのような入力は避けるべきである。

【0114】

上記したように、本実施形態の半導体装置10では、RT端子またはSYNC端子を用いて、昇圧DC/DCコンバータブロックの発振周波数FOSCを任意にかつ高精度に可変制御することが可能である。例えば、カーナビモニタのバックライト制御手段として、本実施形態の半導体装置10を用いている場合、ラジオ受信周波数の切替制御に合わせてSYNC端子から外部同期発振周波数FSYNCを適宜設定してやれば、昇圧DC/DCコンバータブロックの発振周波数FOSCがラジオノイズの周波数帯に重なることを回避することができるので、ラジオの受信品質を損わずに、カーナビモニタのバックライト制御を行うことが可能となる。

【0115】

次に、OCP部111に関して、図16を参照しながら詳細に説明する。

【0116】

図16は、OCP部111の動作に関連する外部素子の接続関係を説明するための図である。

【0117】

図16に示すように、昇圧DC/DCコンバータ用のパワートランジスタQ2(Nチャネル電界効果トランジスタ)のソースとGNDとの間には、検出抵抗RCSが挿入されており、その接続ノードがCS端子(22ピン)に接続されている。

【0118】

また、スイッチングノイズ(スパイクノイズ)を低減するために、CS端子と検出抵抗RCSとの間には、カットオフ周波数1〜2[MHz]のローパスフィルタLPF(抵抗RLPF及びコンデンサCLPF)が挿入されている。なお、ローパスフィルタLPFの時定数が大き過ぎると、CS端子電圧の立ち上がりが遅れ、OCP部111の検出動作が遅くなるため、例えば、発振周波数FOSC=300[kHz]のとき、RLPF=100[Ω]、CLPF=1000[pF]程度が適切である。

【0119】

また、OCP部111における検出電流IOCPは、過電流保護動作電圧VDCS(コンパレータ112の非反転入力端(+)に印加される定電圧)、及び、検出抵抗RCSに基づいて、以下の(5)式で決定される。

【0120】

【数5】

【0121】

また、OCP部111は、パルスバイパルス方式であるため、昇圧DC/DCコンバータの発振周波数FOSCで決定される1周期分だけ、SWOUT端子がローレベル固定とされた後、昇圧動作が復帰される。また、検出抵抗RCSとGNDとの間は大電流ラインとなるので、基板設計に際してはGNDまでを独立配線とすべきである。

【0122】

次に、ソフトスタート部114に関して説明する。本実施形態の半導体装置10において、SS端子(27ピン)は不使用であり、オープンとされる。また、SS端子電圧がクランプ電圧2.5[V](Typ.)に達するまで、オープン/ショート検出部118におけるオープン/ショート検出機能はマスクされる。

【0123】

次に、外付け部品の選定について、詳細な説明を行う。

【0124】

まず、コイルL1の選定に関して、図17を参照しながら詳細に説明する。

【0125】

図17は、コイルL1の選定に関して説明するための図である。なお、図17(a)には、コイル電流ILのリップル成分ΔILが示されており、図17(b)には、DC/DCコンバータの入出力段を構成する回路が示されている。

【0126】

コイルL1のインダクタ値は、コイル電流ILのリップル成分ΔIL(コイル電流ILの最大値ILMAXと最小値ILMINとの差分)に大きく影響する。具体的には、下記の(6)式で示すように、コイルL1のインダクタ値が大きいほど、また、発振周波数FOSCが高いほど、リップル成分ΔILは減少する。

【0127】

【数6】

【0128】

また、効率ηを下記の(7a)式のように表すと、コイル電流ILの最大値ILMAXは、下記の(7b)式のようになる。

【0129】

【数7】

【0130】

コイルL1の定格電流値を超えるコイル電流ILをコイルL1に流すと、コイルL1が磁気飽和を起こして効率ηが低下する。従って、コイル電流ILの最大値ILMAXがコイルL1の定格電流値を超えないように、充分なマージンをもって選定すべきである。また、コイルL1での損失を少なくし、効率ηを向上するため、コイルL1としては、抵抗成分(直流リアクトルDCR、交流リアクトルACR)の低いものを選定すべきである。

【0131】

次に、出力コンデンサCVOUTの選定に関して、図18を参照しながら詳細な説明を行う。

【0132】

図18は、出力コンデンサCVOUTの選定に関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。

【0133】

出力コンデンサCVOUTの選定については、出力電圧VOUTの安定領域を鑑み、さらに、出力電圧のリップル成分ΔVOUTを平滑化するために必要な等価直列抵抗ESR[Equivalent Series Resistance]を考慮して、適宜決定すればよい。

【0134】

出力電圧VOUTのリップル成分ΔVOUTは、下記の(8)式のように決定される。

【0135】

【数8】

【0136】

なお、上記(8)式において、ΔILは出力電流ILのリップル成分、RESRは出力コンデンサCVOUTの等価直列抵抗ESRの抵抗値、ηは効率を各々示している。

【0137】

なお、出力コンデンサCVOUTの定格は、出力電圧VOUTに対して充分なマージンをもって選定することが望ましい。

【0138】

次に、入力コンデンサCVCCの選定に関して図19を参照しながら詳細に説明する。

【0139】

図19は、入力コンデンサCVCCの選定に関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。

【0140】

入力コンデンサCVCCの選定については、大きな過渡電圧を防止すべく、大きなリップル電流IRMSに充分対応できる容量値を有する低ESRの入力コンデンサを用いることが望ましい。

【0141】

上記のリップル電流IRMSは、下記の(9)式で与えられる。

【0142】

【数9】

【0143】

また、リップル電流IRMSは、入力に使用する電源の特性、基盤の配線パターン、及び、トランジスタQ1、Q2のゲート−ドレイン容量に大きく依存するため、使用時の温度、負荷範囲、及び、トランジスタQ1、Q2の条件において、十分な確認を行うことが望ましい。

【0144】

次に、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して図20及び図21を参照しながら詳細に説明する。

【0145】

図20は、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。また、図21は、トランジスタQ1のゲート・ソース間容量とソフトスタート時間との相関関係を示すグラフである。

【0146】

通常の昇圧アプリケーションの場合、電源電圧VCCの印加端から出力電圧VOUTの引出端に至る経路上にスイッチが存在しないので、出力短絡が生じた場合には、前記経路に過大な電流が流れて、コイルL1や整流用ダイオードD1が破壊に至るおそれがある。これを回避すべく、本実施形態の半導体装置10では、電源電圧VCCの印加端とコイルL1との間に、ロードスイッチ用のPチャネル型電界効果トランジスタQ1が挿入されている。なお、トランジスタQ1としては、ゲート・ソース間耐圧、ドレイン・ソース間耐圧のいずれについても、電源電圧VCCより高いものを選定すればよい。

【0147】

また、ロードスイッチのソフトスタートをかけたい場合には、トランジスタQ1のゲート・ソース間に容量を挿入すればよい。これにより、図21に示すように、挿入する容量値に応じて、ソフトスタート時間を任意に決定することができる。ただし、ソフトスタート時間は、トランジスタQ1のゲート容量によっても変化する。

【0148】

次に、スイッチング用トランジスタQ2の選定に関して説明する。絶対最大定格電流がコイルL1の定格電流以上であり、絶対最大定格電圧が出力コンデンサCVOUTの耐圧+整流用ダイオードD1の順方向降下電圧VF以上のものであれば、いかなるMOSFETを用いても問題ないが、高速スイッチングを実現するため、ゲート容量(注入電荷量)の小さいものを選定すべきであり、望ましくは、過電流保護設定値以上のものを用いるとよい。また、オン抵抗が小さいものを選ぶと高効率を得ることが可能となる。

【0149】

次に、整流用ダイオードD1の選定に関して説明する。コイルL1の定格電流以上の電流能力を持ち、かつ、出力コンデンサCVOUTの耐圧以上の逆耐圧を持つショットキーバリアダイオードであれば、いかなるものを用いてもよく、特に、順方向降下電圧VFの低いものを選定すればよい。

【0150】

次に、位相補償設定法について、詳細な説明を行う。

【0151】

まず、アプリケーションの安定条件に関して説明する。負帰還がかえるフィードバック系が安定する条件としては、ゲインが1(0[dB])であるときの位相遅れが150°以下(すなわち位相マージン30°以上)である必要がある。

【0152】

また、DC/DCコンバータアプリケーションは、発振周波数FOSCによってサンプリングされているため、全体の系におけるGBW[Gain-Band Width](ゲインと帯域幅との積)は、発振周波数FOSCの1/10以下に設定する必要がある。

【0153】

上記をまとめると、アプリケーションが目標とする特性は、ゲインが1(0[dB])であるときの位相遅れが150°以下(すなわち位相マージン30°以上)であり、そのときのGBW(すなわちゲイン0[dB]の周波数)が発振周波数FOSCの1/10以下であればよい。そのため、GBWの制限により応答性を上げるためには、発振周波数FOSCの高周波化が必要となる。

【0154】

位相補償により安定性を確保するには、LC共振によって生じる2次の位相遅れ(−180°)を2次の位相進み(すなわち位相進みを2つ入れる)により、キャンセルすればよい。なお、位相進みを与える手段としては、出力コンデンサCVOUTのESR成分によるもの(図23を参照)と、COMP端子(28ピン)に接続されるCR成分によるもの(図24を参照)が考えられる。

【0155】

DC/DCコンバータアプリケーションでは、図22に示すように、必ず出力にLC共振回路が存在する。従って、その部分での位相遅れが−180°となる。図23に示すように、出力コンデンサCVOUTがアルミ電解コンデンサなど、ESRの大きなもの(数[Ω])の場合には、+90°の位相進みが生じ、位相遅れが−90°となる。一方、セラミックコンデンサなど、低ESRの出力コンデンサCVOUTを使用する場合には、ESR成分に相当する抵抗を挿入する必要がある。

【0156】

なお、ESRによる位相特性の変化により、挿入すべき位相進みは1つとなる。また、位相進みを挿入する周波数の設定は、LC共振をキャンセルするという目的から、理想的には、LC共振周波数付近に設定することが望ましい。

【0157】

次に、半導体装置10の動作シーケンスについて、図25を参照しながら説明を行う。

【0158】

図25は、半導体装置10の動作シーケンスを示すタイミングチャートである。

【0159】

電源電圧VCCが投入された後、イネーブル信号ENがハイレベルに立ち上がると、VREG部101にて、基準電圧VREGの生成が開始される。なお、イネーブル信号ENについては、電源電圧VCCが充分に立ち上がってから、例えば、電源電圧VCCが4.5[V]以上となってから投入するとよい。

【0160】

基準電圧VREGが2.9[V]まで到達すると、UVLO部103では、減電圧状態ではないと認識され、UVLO信号がハイレベルに立ち上がる。これにより、半導体装置10の内部回路が動作を開始する。なお、UVLO信号がローレベルとされている間、スイッチ102はオフとされ、LOADSW端子(2ピン)の端子電圧は、ハイレベルに維持される。従って、ロードスイッチ用のトランジスタQ1はオフとされるので、DC/DCコンバータの昇圧動作が停止状態に維持される。一方、UVLO信号がハイレベルに立ち上がると、スイッチ102がオンとなり、LOADSW端子の端子電圧がローレベルに立ち下がる。その結果、ロードスイッチ用のトランジスタQ1がオンとなり、DC/DCコンバータの昇圧動作が可能となる。

【0161】

外部入力信号であるVDAC信号、SYNC信号、PWM信号には、安定動作のために所定の入力シーケンスが存在する。具体的に述べると、VDAC信号とSYNC信号は、イネーブルENの入力タイミングから第1所定時間TINONの経過後に入力することが望ましく、PWM信号は、EN信号の入力タイミングから第2所定時間TPWMONの経過後に入力することが望ましい。なお、第2所定時間TPWMON>第1所定時間TINONであり、第2所定時間TPWMON>500[V/A・s]×CREG[sec]である。また、VDAC信号とSYNC信号は、EN信号よりも第3所定時間TINOFFだけ先に入力を遮断することが望ましく、PWM信号は、EN信号よりも第4所定時間TPWMOFFだけ先に入力を遮断することが望ましい。なお、第4所定時間TPWMOFF>第3所定時間TINOFFである。また、本図には示されていないが、LEDEN1信号、及び、LEDEN2信号は、EN信号のハイレベル遷移前にその論理を固定しておくことが望ましい。

【0162】

OVP部105では、OVP端子(25ピン)の端子電圧が2[V]に達したときに、過電圧状態であると認識され、DC/DCコンバータの昇圧動作が停止される。その後、OVP部105では、OVP端子の端子電圧が1.6[V]まで低下したときに、過電圧状態が解消されたと認識され、DC/DCコンバータの昇圧動作が復帰される。

【0163】

OCP部111では、CS端子(22ピン)の端子電圧が0.4[V]に達したときに過電流状態であると認識され、以後、パルスバイパルス方式で、DC/DCコンバータの昇圧動作が断続的にオン/オフされる。

【0164】

TSD部104では、半導体装置10の温度が175[℃]に達したときに、異常発熱状態であると認識され、DC/DCコンバータの昇圧動作が停止される。その後、TSD部104では、半導体装置10の温度が150[℃]まで低下したときに、異常発熱状態が解消されたと認識され、DC/DCコンバータの昇圧動作が復帰される。

【0165】

なお、EN信号がローレベルに立ち下げられると、基準電圧VREGの生成が停止される。UVLO部103では、この基準電圧VREGが2.8[V]まで低下したときに、減電圧状態であると認識され、UVLO信号がローレベルに立ち下がる。これにより、半導体装置10の内部回路が動作を停止する。

【0166】

次に、本発明に係る半導体装置の第2実施形態について、詳細な説明を行う。

【0167】

図26は、本発明に係る半導体装置の第2実施形態を示すブロック図である。

【0168】

まず、本実施形態の半導体装置20の概要について述べる。

【0169】

半導体装置20は、36V高耐圧の白色LEDドライバICであり、カレントモードの昇降圧DC/DCコンバータ、並びに、4チャネル出力の定電流ドライバが1チップに集積化されている。なお、半導体装置20は、PWM[Pulse Width Modulation]制御、及び、VDAC制御のいずれによっても、白色LEDの調光制御が可能である。

【0170】

次に、本実施形態の半導体装置20の特長のうち、特に、第1実施形態と異なる点について述べる。

【0171】

第1の特長は、バッテリから直接供給される電源電圧VCCに対応すべく、昇圧DC/DCコントローラブロックに代えて、昇降圧DC/DCコントローラブロックを内蔵している点である。第2の特長は、出力コンデンサCVOUTとして、低ESRのセラミックコンデンサを用いるべく、DC/DCコンバータの制御モードを電圧モードから電流モードに変更した点である。第3の特長は、LED発光輝度のPWM調光能力を高めるべく、0.38[%]のデューティ比(オーバーシュートなし)が実現されている点である。第4の特長は、出力電流ILEDの相対ばらつき幅:±3%、絶対ばらつき幅:±5%が実現されている点である。第5の特長は、LEDのアノード及びカソードにおけるショート(主にグランドショート)を検出し、適切な保護動作を行う保護機能部(SCP[Short Circuit Protection])を内蔵している点である。

【0172】

なお、本実施形態の半導体装置20は、カーナビモニタのバックライトや、中小型LCDパネルのバックライトなどの駆動制御用として用いられる。

【0173】

上記特長を有する本実施形態の半導体装置20は、図26に示したように、基準電圧生成部201(以下、VREG部201と呼ぶ)と、減電圧保護部202(以下、UVLO部202と呼ぶ)と、温度保護部203(以下、TSD部203と呼ぶ)と、ショート保護部204(以下、SCP部204と呼ぶ)と、過電圧保護部205(以下では、OVP部205と呼ぶ)と、過電流保護部206(以下、OCP部206と呼ぶ)と、コンパレータ207と、制御ロジック部208と、入力バッファ209と、発振器部210と、スロープ電圧生成部211と、PWMコンパレータ212と、ドライバ制御部213と、ドライバ214と、Nチャネル型電界効果トランジスタ215と、ドライバ216と、エラーアンプ217と、ソフトスタート部218と、入力バッファ219と、電流設定部220と、定電流ドライバ221と、オープン/ショート検出部222と、入力バッファ223及び224と、を集積化して成る。

【0174】

なお、半導体装置20の上記回路部は、VREGブロック(VREG部201)と、昇降圧DC/DCコントローラブロック(OCP部206、コンパレータ207、制御ロジック部208、入力バッファ209、発振器部210、スロープ電圧生成部211、PWMコンパレータ212、ドライバ制御部213、ドライバ214、トランジスタ215、ドライバ216、エラーアンプ217、及び、ソフトスタート部218)と、カレントドライバブロック(入力バッファ219、電流設定部220、定電流ドライバ221、オープン/ショート検出部222、及び、入力バッファ223及び224)と、保護ブロック(UVLO部202、TSD部203、SCP部204、及び、OVP部205)の4ブロックに大別することができる。

【0175】

また、本実施形態の半導体装置20は、外部との電気的接続を確立する手段として、28本の外部端子(1ピン〜28ピン)を有して成る。

【0176】

図27は、半導体装置20のピン配置図であり、図28は、外部端子のピン番号、端子名、及び、機能を示した対応表である。なお、図27において、半導体装置20の中央部両サイドに設けられた幅広の端子は、サブグランドと繋がるFIN端子であり、放熱性を良くするためのものである。

【0177】

図29は、上記構成から成る半導体装置20の電気的特性を示す表である。なお、図29に示す電気的特性は、特に指定のない限り、電源電圧VCC=12[V]、周囲温度Ta=25[℃]での数値を示している。

【0178】

次に、半導体装置20各部の動作について、第1実施形態とは異なる点を中心に、詳細な説明を行う。

【0179】

まず、半導体装置20のカレントドライバブロック(入力バッファ219、電流設定部220、定電流ドライバ221、オープン/ショート検出部222、及び、入力バッファ223及び224)について、詳細な説明を行う。

【0180】

図30は、電流設定部220と定電流ドライバ221の一構成例を示す回路図である。

【0181】

図30に示すように、電流設定部220は、オペアンプA1と、直流電圧源A2と、npn型バイポーラトランジスタA3と、抵抗A4、A5と、pnp型バイポーラトランジスタA6〜A9と、抵抗A10(抵抗値R)と、を有して成る。

【0182】

オペアンプA1の第1非反転入力端(+)は、VDAC端子(8ピン)に接続されている。オペアンプA2の第2非反転入力端(+)は、直流電圧源A2の正極端に接続されており、所定の定電圧VISET(=2.0[V])が印加されている。直流電圧源A2の負極端は、接地端に接続されている。オペアンプA2の反転入力端(−)は、ISET端子(9ピン)に接続されている。トランジスタA3のベースは、オペアンプA1の出力端に接続されている。トランジスタA3のエミッタは、ISET端子に接続されている。

【0183】

抵抗A4、A5の各一端は、いずれも基準電圧VREGの印加端に接続されている。抵抗A4の他端は、トランジスタA6のエミッタに接続されている。抵抗R5の他端は、トランジスタA7のエミッタに接続されている。トランジスタA6、A7のベースは、互いに接続されており、その接続ノードは、トランジスタA7のコレクタに接続されている。トランジスタA6のコレクタは、トランジスタA8のエミッタに接続されている。トランジスタA7のコレクタは、トランジスタA9のエミッタに接続されている。トランジスタA8、A9のベースは、互いに接続されており、その接続ノードは、トランジスタA8のコレクタに接続されている。トランジスタA8のコレクタは、トランジスタA3のコレクタに接続されている。トランジスタA9のコレクタは、抵抗A10を介して、接地端に接続されている。

【0184】

一方、図30に示すように、定電流ドライバ221は、LED1端子〜LED4端子に対して各々出力電流ILEDを供給する4チャネルの出力段Ch1、Ch2、Ch3、Ch4を有して成る。なお、出力段Ch1は、オペアンプB1と、Nチャネル型電界効果トランジスタB2と、抵抗B3(抵抗値4R)と、カレントミラー回路B4(ミラー比1:1)と、抵抗B5(抵抗値4R)と、オペアンプB6と、Nチャネル型電界効果トランジスタB7と、抵抗B8(抵抗値(4/12)×R)と、カレントミラー回路B9(ミラー比1:10)と、オペアンプB10と、直流電圧源B11と、Nチャネル型電界効果トランジスタB12〜B14と、オペアンプB15と、直流電圧源B16と、Nチャネル型電界効果トランジスタB17と、Nチャネル型電界効果トランジスタB19と、Pチャネル型電界効果トランジスタB20と、抵抗B21、B22と、Nチャネル型電界効果トランジスタB23と、インバータB24と、を有して成る。

【0185】

オペアンプB1の非反転入力端(+)は、トランジスタA9と抵抗A10との接続ノードに接続されている。オペアンプB1の反転入力端(−)は、抵抗B3の一端に接続されている。抵抗B3の他端は、接地端に接続されている。トランジスタB2のドレインは、カレントミラー回路B4の入力端に接続されている。トランジスタB2のソースは、抵抗B3の一端に接続されている。トランジスタB2のゲートは、オペアンプB1の出力端に接続されている。カレントミラー回路B4の電源入力端は、基準電圧VREGの印加端に接続されている。

【0186】

オペアンプB6の非反転入力端(+)は、カレントミラー回路B4の出力端と抵抗B5の一端に各々接続されている。オペアンプB6の反転入力端は、抵抗B8の一端に接続されている。抵抗B5、B8の他端は、いずれも接地端に接続されている。トランジスタB7のドレインは、カレントミラー回路B9の入力端に接続されている。トランジスタB7のソースは、抵抗B8の一端に接続されている。トランジスタB7のゲートは、オペアンプB6の出力端に接続されている。カレントミラー回路B9の電源入力端は、基準電圧VREGの印加端に接続されている。

【0187】

オペアンプB10の非反転入力端(+)は、直流電圧源B11の正極端に接続されている。直流電圧源B11の負極端は、接地端に接続されている。トランジスタB12のドレインは、カレントミラー回路B9の出力端に接続されている。トランジスタB12のソースは、オペアンプB10の反転入力端(−)に接続されている。トランジスタB12のゲートは、オペアンプB10の出力端に接続されている。

【0188】

トランジスタB13のドレインは、トランジスタB12のソースに接続されている。トランジスタB13、B14のゲートは互いに接続されており、その接続ノードは、トランジスタB12のドレインに接続される一方、トランジスタB19のドレインにも接続されている。トランジスタB13、B14、B19のソースは、いずれも接地端に接続されている。トランジスタB19のゲートは、入力バッファ219(本図では不図示)を介してPWM端子(8ピン)に接続されている。

【0189】

オペアンプB15の非反転入力端(+)は、直流電圧源B16の正極端に接続されている。直流電圧源B16の負極端は、接地端に接続されている。トランジスタB17のドレインは、LED1端子に接続されている。トランジスタB17のソースは、オペアンプB15の反転入力端(−)に接続される一方、トランジスタB14のドレインにも接続されている。トランジスタB17のゲートは、オペアンプB15の出力端に接続されている。

【0190】

トランジスタB20のソースは、基準電圧VREGの印加端に接続されている。トランジスタB20のドレインは、カレントミラー回路B9の入力端に接続されている。抵抗B21の一端は、基準電圧VREGの印加端に接続されている。抵抗B21の他端は、トランジスタB20のゲートに接続されている。抵抗B22の一端は、トランジスタB20のゲートに接続されている。抵抗B22の他端は、トランジスタB23のドレインに接続されている。トランジスタB23のソースは、接地端に接続されている。トランジスタB23のゲートは、インバータB24の出力端に接続されている。インバータB24の入力端は、入力バッファ219(本図では不図示)を介して、PWM端子に接続されている。

【0191】

なお、定電流ドライバ221を構成するその余の出力段Ch2〜Ch4は、上記の出力段Ch1と同様の構成から成るため、詳細な説明は割愛する。

【0192】

上記構成から成る電流設定部220、及び、定電流ドライバ221において、出力電流ILEDは、次の(10)式に基づいて設定される。

【0193】

【数10】

【0194】

上記(10)式において、min{VDAC,2.0[V]}というパラメータは、VDAC端子(18ピン)に入力される制御電圧VDACと、電流設定部220の内部で予め定められた定電圧VISET(=2.0[V])のうち、いずれか低い方の電圧値である。また、RSETというパラメータは、ISET端子(19ピン)に外部接続される抵抗RSETの抵抗値であり、3000(Typ.)というパラメータは、定電流ドライバ221の回路内部で決まる定数である。

【0195】

すなわち、ISET端子(19ピン)に抵抗RSETをプルダウン接続することで、これに流れる基準電流ISETの所定ゲイン倍(例えば3000倍)が出力電流ILEDの最大値(例えば50[mA])として設定される形となっている。

【0196】

図30の例に即して具体的に述べると、定電流ドライバ221では、まず、オペアンプB1、トランジスタB2、及び、抵抗B3(抵抗値4R)を用いて、抵抗A10の端子電圧Va(=ISET×R)が電圧/電流変換され、基準電流ISETを1/4とした中間電流Ia(=1/4ISET)が生成される。次に、カレントミラー回路B4を用いて、中間電流Iaが1:1でミラーされ、中間電流Ib(=1/4ISET)が生成される。次に、抵抗B5(抵抗値4R)を用いて、中間電流Ibが電流/電圧変換され、端子電圧Vb(=ISET×R)が生成される。次に、オペアンプB6、トランジスタB7、並びに、抵抗B8(抵抗値(4/12)×R)を用いて、抵抗B5の端子電圧Vbが電圧/電流変換され、基準電流ISETを3倍した中間電流Ic(=3ISET)が生成される。次に、カレントミラー回路B9を用いて、中間電流Icが1:10でミラーされ、基準電流ISETを30倍した中間電流Id(=30ISET)が生成される。そして、最終的には、トランジスタB13、B14から成るカレントミラー回路を用いて、中間電流Idが1:100でミラーされ、基準電流ISETを3000倍とした出力電流ILED(=3000ISET)が生成される。

【0197】

なお、出力電流ILEDの精度を高めるために、最終段のカレントミラー回路については、オペアンプB10、B15を用いて、トランジスタB13、B14のドレイン・ソース間電圧が同一(例えば0.3[V])とされている。また、定電流ドライバ221は、入力される基準電流ISETに基づいて、電圧/電流変換と電流/電圧変換を繰り返しながら、所望の出力電流ILEDを生成する構成とされている。従って、上記変換処理に用いる抵抗素子(図30の例では、抵抗B3、B5、B8)が増え、延いては、そのトリミング機会が増加する。このように、トリミング可能な抵抗を数多く有する構成であれば、それらの抵抗値を微調整することにより、出力電流ILEDの相対ばらつき幅、及び、絶対ばらつき幅を低減することが可能となる。

【0198】

また、本実施形態の半導体装置20は、基準電流ISETを最終段のカレントミラー回路で一気に増幅していた第1実施形態(ISET→1/5ISET→2ISET→3300ISET)と異なり、定電流ドライバ221における出力電流ILEDの生成過程で、分散的に電流増幅を行う構成(ISET→1/4ISET→3ISET→30ISET→3000ISET)とされている。

【0199】

このような構成とすることにより、図31(a)、(b)の対比で示すように、最終段のカレントミラー回路を構成するトランジスタB13、B14のトランジスタサイズの差を減じて、素子の製造ばらつきや応力の影響を軽減することができる。すなわち、トランジスタサイズの差が大きいと、片方のトランジスタにのみ大きな応力が加わり、他方のトランジスタには応力がほとんど加わらない状況が生じるなど、半導体装置20のパッケージング時に加えられる応力の影響を受けやすいが、本実施形態の構成であれば、トランジスタサイズの差が小さくなるので、両方の素子に均等な応力が加わりやすく、応力の影響を低減することが可能となる。もちろん、トランジスタの素子設計に際しては、出力電流ILEDの実使用範囲(5[mA]以上を想定)において、トランジスタが飽和領域で動作するように、各素子のW/Lを適宜設計することが望ましい。

【0200】

また、本実施形態の半導体装置20では、図32で示すように、ペアとなる抵抗R1、R2(例えば、抵抗B3と抵抗B5、若しくは、抵抗B5と抵抗B8)が千鳥状にレイアウトされている。このような配置レイアウトを採用すれば、半導体装置20のパッケージングに際して、ペアとなる抵抗R1、R2に均等な応力が加わりやすく、応力の影響を低減することが可能となる。

【0201】

以上の通り、本実施形態の半導体装置20では、抵抗トリミング機会の増大、電流増幅能力の分散、抵抗のペア性向上など、多面的に出力電流ILEDの精度向上が図られている。このような構成とすることにより、パッケージング後における出力電流ILEDの相対ばらつき幅:±3%、絶対ばらつき幅:±5%を実現することができ、延いては、輝度ばらつきの低減やLEDの長寿命化に貢献することが可能となる。

【0202】

なお、抵抗RSETの抵抗値に関しては、先出の図11を参照しながら説明した通り、300[kΩ]以下のものを用いることが望ましい。

【0203】

ここで、上記の制御電圧VDACを用いて、出力電流ILEDの可変制御(LEDの調光制御)を行う場合、その入力範囲は、0.1〜2.0[V]の範囲とすればよい。このような制御電圧VDACを印加することにより、出力電流ILEDを最大値から低減していくことが可能となる。

【0204】

一方、制御電圧VDACとして2.0[V]以上が入力された場合には、先の(10)式で与えられるように、定電圧VISETの電圧値が選択されることになるため、制御電圧VDACによる調光機能が不使用状態となる。なお、制御電圧VDACによる調光機能を使用しない場合には、誤動作を回避する観点から、VDAC端子をオープンとせず、基準電圧VREG(5[V])の印加端に接続しておくとよい。

【0205】

また、本実施形態の半導体装置20では、上記の制御電圧VDACを用いたLEDの調光制御のほか、PWM端子(8ピン)に入力されるPWM信号を用いて、定電流ドライバ221のオン/オフ(図30の例では、最終段のカレントミラー回路を構成するトランジスタB13、B14のオン/オフ、並びに、カレントミラー回路B9のオン/オフ)を制御することで、LEDの調光制御を行うことも可能である。

【0206】

すなわち、本実施形態の半導体装置20では、PWM信号に基づいて、最終段のカレントミラー回路を構成するトランジスタB13、B14のオン/オフ、並びに、カレントミラー回路B9のオン/オフが制御されることにより、PWM信号のデューティ比が出力電流ILEDのデューティ比となるので、出力電流ILEDをその最大値(ないしは、制御電圧VDACで定められた電流値)から、見かけ上低減することが可能となる。

【0207】

なお、PWM信号に基づいて基準電流ISETをパルス電流に変換する第1実施形態では、カレントミラー回路B4、B9でリンギングが発生し、これが出力電流ILEDのオーバーシュートに繋がっていたが、本実施形態の構成であれば、このような問題が生じることはない。

【0208】

また、本実施形態の半導体装置20は、さらなるオーバーシュート対策として、出力段のオペアンプB15をスルーレートの遅いものとし(例えば0.5[V/μs])、出力電流ILEDの立ち上がりに際して、トランジスタB17のゲート・ソース間電圧VGSの変動に制限をかけることで、オーバーシュートが生じないように、出力電流ILEDの立ち上がりを鈍らせる構成とされている。

【0209】

さらに、本実施形態の半導体装置20では、先述の通り、最終段のカレントミラー回路に流れ込む中間電流Idが第1実施形態の2ISETからが30ISETに増加されているため、トランジスタB13、B14の応答性が向上し、プルダウン抵抗B18を除くことが可能となることから、オーバーシュートの発生を一層抑制することが可能となる。

【0210】

以上の通り、本実施形態の半導体装置20では、最終段カレントミラー回路のPWM制御、オペアンプB15の低スルーレート化、プルダウン抵抗B18の除去など、多面的に出力電流ILEDの応答性向上、並びに、オーバーシュートの低減が図られている。このような構成とすることにより、オーバーシュートを招くことなく、PWM調光能力の向上(最低デューティ比:0.38%(150[Hz]時))を実現し、延いては、低デューティ時の調光精度を向上することが可能となる。

【0211】

一方、PWM信号による調光機能を使用しない場合(デューティ比100%)には、PWM端子をハイレベル(例えば定電圧VREG)に固定すればよい。なお、PWM端子には、ローパスフィルタ(カットオフ周波数30[kHz])を挿入することが望ましい。

【0212】

なお、PWM調光制御の一例については、先出の図14を用いて説明済みである。

【0213】

次に、半導体装置20の昇降圧DC/DCコントローラブロック(OCP部206、コンパレータ207、制御ロジック部208、入力バッファ209、発振器部210、スロープ電圧生成部211、PWMコンパレータ212、ドライバ制御部213、ドライバ214、トランジスタ215、ドライバ216、エラーアンプ217、及び、ソフトスタート部218含む回路ブロック)について、先出の図26を参照しながら詳細に説明する。

【0214】

まず、半導体装置20の外部接続について、特に昇降圧DC/DCコンバータに関連する回路要素(Nチャネル型電界効果トランジスタN1、N2、ダイオードD2、D3、コイルL2、抵抗RCS、RLPF、コンデンサCBS、CLPF)の詳細な説明を行う。

【0215】

図26に示すように、トランジスタN1のゲートは、OUTH端子(25ピン)を介して、ドライバ214の出力端に接続されている。トランジスタN1のドレインは、抵抗RCSを介して電源電圧VCCの印加端に接続されるとともに、抵抗RLPFを介して、CS端子(27ピン)にも接続されている。トランジスタN1のソースは、SW端子(24ピン)を介して、ドライバ214の第2電源端(低電位端)、及び、トランジスタ215のドレインに各々接続されている。

【0216】

コイルL2の一端は、SW端子に接続されている。コイルL2の他端は、ダイオードD3のアノードに接続されている。ダイオードD3のカソードは、出力電圧VOUTの引出端として、負荷であるLED列のアノードに接続されている。

【0217】

トランジスタN2のゲートは、OUTL端子(22ピン)を介して、ドライバ216の出力端に接続されている。トランジスタN2のドレインは、コイルL2の他端とダイオードD3のアノードとの接続ノードに接続されている。トランジスタN2のソースは、接地端に接続されている。

【0218】

ダイオードD2のカソードは、SW端子に接続されている。ダイオードD2のアノードは、接地端に接続されている。ブートストラップ用コンデンサCBSの一端は、BOOT端子(9ピン)を介して、ドライバ214の第1電源端(高電位端)に接続されている。コンデンサCBSの他端は、SW端子に接続されている。コンデンサCLPFの一端は、電源電圧VCCの印加端に接続されている。コンデンサCLPFの他端は、CS端子に接続されている。

【0219】

なお、本実施形態の半導体装置20では、トランジスタN1、N2を外付けとしているので、放熱性を高めることが可能となる。

【0220】

次に、昇降圧DC/DCコントローラブロックの基本動作(昇圧動作)について、詳細な説明を行う。

【0221】

トランジスタN1、N2がオン状態にされると、コイルL2には、経路Xを通って電流が流れ、その電気エネルギが蓄えられる。また、トランジスタN1、N2のオン期間において、コンデンサCVOUTに電荷が蓄積されていた場合、出力電圧VOUTの引出端には、コンデンサCVOUTからの電流が流れることになる。なお、このとき、コイルL2の他端電位は、トランジスタN2を介して、ほぼ接地電位まで低下しているため、ダイオードD3は逆バイアス状態となり、コンデンサCVOUTからトランジスタN2に向けて電流が流れ込むことはない。

【0222】

次に、トランジスタN1、N2がオフ状態にされると、コイルL1に生じた逆起電圧により、そこに蓄積された電気エネルギが経路Yを通って放電され、出力電圧VOUTの引出端から負荷であるLED列に流れ込むとともに、コンデンサCVOUTを介して接地端にも流れ込み、コンデンサCVOUTを充電することになる。

【0223】

従って、本実施形態の半導体装置20であれば、ドライバ制御部213を用いて、トランジスタN1、N2のデューティ比を適宜制御することにより、より具体的に述べれば、降圧動作時には、トランジスタN1、N2のデューティ比を50%より小さい値にまで低下させ、逆に、昇圧動作時には、トランジスタN1、N2のデューティ比を50%より大きい値にまで上昇させることにより、簡易な構成でありながら、容易かつ適切に、その昇降圧動作を切り換えることが可能となる。

【0224】

すなわち、本実施形態の半導体装置20であれば、電源電圧VCCが所望の出力電圧VOUTよりも高いか低いかに依ることなく、常に所望の出力電圧VOUTを得ることができるようになる。従って、例えば、出力電圧VOUTの所望値が16[V]であるのに対して、電源電圧VCCが6〜18[V]の範囲で変動する場合であっても、所望の出力電圧VOUTを得ることが可能となる。このような構成は、例えば、バッテリから直接供給される電源電圧VCCに対応する必要のあるアプリケーション(例えばカーナビモニタのバックライト制御用LEDドライバIC)に好適である。

【0225】

なお、トランジスタN2のゲートをSW端子に接続する構成でも、上記の昇降圧動作は可能であるが、本実施形態の半導体装置20は、36V高耐圧を実現したものであり、SW端子にも、このような高電圧が印加される可能性がある。一方、外付けのトランジスタN2は、そのゲート耐圧が必ずしも高くない。そのため、トランジスタN2のゲートをSW端子に接続した構成では、トランジスタN2が破壊に至るおそれがある。

【0226】

そこで、本実施形態の半導体装置20では、トランジスタN2のゲート制御を行う手段として、別途のドライバ216(基準電圧VREGで駆動)を用意し、これを用いてトランジスタのオン/オフ制御を行う構成とされている。このような構成とすることにより、電源電圧VCCが高電圧であっても、トランジスタN2が破壊に至る心配はない。

【0227】

また、本実施形態の半導体装置20は、軽負荷時或いは無負荷時におけるリンギング防止手段として、Nチャネル型電界効果トランジスタ215を集積化して成る。

【0228】

トランジスタ215のドレインは、SW端子に接続されている。トランジスタ215のソースは、接地端に接続されている。トランジスタ215のゲートは、ドライバ制御部213の制御信号出力端に接続されている。

【0229】

なお、トランジスタ215の電流能力は、不要なチップ面積の増大や変換効率の低下を招かぬように、リンギングノイズという微小電流を引き抜き得る必要最小限に設計することが望ましい。

【0230】

ドライバ制御部213は、トランジスタN1、N2のオン/オフ制御を行う一方、これとは相補的に、トランジスタ215のオン/オフ制御を行う。

【0231】

このような構成とすることにより、軽負荷時や無負荷時に、その出力電流が低下してコイル電流が全体的に引き下げられ、リンギングという波形の乱れが生じる状態(いわゆる不連続モード)に陥った場合であっても、トランジスタ215を介してリンギングノイズを接地端に逃がすことができるので、昇降圧動作の安定性を高めることが可能となる。

【0232】

なお、上記の説明中で用いた「相補的」という文言は、トランジスタN1(及びトランジスタN2)とトランジスタ215のオン/オフが完全に逆転している場合のほか、貫通電流防止等の観点から、トランジスタN1とトランジスタ215のオン/オフ遷移タイミングに所定の遅延が与えられている場合をも含むものとする。

【0233】

次に、昇圧DC/DCコントローラブロックの出力帰還制御について詳細に説明する。

【0234】

エラーアンプ217は、第1〜第4の反転入力端(−)に各々印加されるLED端子電圧V1〜V4の最低値と、非反転入力端(+)に入力される所定のLED制御電圧VLEDとの差分を増幅して誤差電圧Verrを生成する。すなわち、誤差電圧Verrの電圧値は、出力電圧VOUTがその目標設定値よりも低いほど高レベルとなる。

【0235】

一方、PWMコンパレータ212は、非反転入力端(+)に印加される誤差電圧Verrと、反転入力端(−)に印加されるスロープ電圧Vslp(発振器OSCの三角波電圧VoscとCS端子(27ピン)の端子電圧(抵抗RCSで生成される電流検出信号)との加算電圧)とを比較することで、その比較結果に応じたデューティ比の比較信号を生成する。すなわち、比較信号の論理は、誤差電圧Verrがスロープ電圧Vslpよりも高ければハイレベルとなり、低ければローレベルとなる。

【0236】

なお、定常動作時における比較信号のオンデューティ(単位期間に占めるトランジスタN1、N2のオン期間の比)は、誤差電圧Verrとスロープ電圧Vslpの相対的な高低に応じて変動する。

【0237】

ドライバ制御部213は、上記の比較信号がローレベルとされている間、ドライバ214及びドライバ216を介して、OUTH端子及びOUTL端子(すなわち、トランジスタN1、N2のゲート電圧)をハイレベルに保持する。従って、トランジスタN1、N2はオン状態とされる。一方、比較信号がローレベルとされている間には、OUTH端子及びOUTL端子の端子電圧をローレベルに保持する。従って、トランジスタN1、N2はオフ状態とされる。

【0238】

このように、昇降圧DC/DCコントローラブロックでは、LED端子電圧V1〜V4(延いては出力電圧VOUT)のモニタ結果だけでなく、トランジスタN1に流れるスイッチ電流のモニタ結果に基づいて、トランジスタN1、N2の駆動制御が行われる。従って、本実施形態の半導体装置20であれば、急峻な負荷変動に誤差電圧Verrが追従できなくても、トランジスタN1、N2に流れるスイッチ電流のモニタ結果に応じてトランジスタN1、N2を直接駆動制御することができるので、出力電圧VOUTの変動を効果的に抑制することが可能となる。すなわち、本実施形態の半導体装置であれば、出力コンデンサCVOUTを大容量化する必要がなく、また、低ESRのセラミックコンデンサを用いることができるので、不要なコストアップや出力コンデンサCVOUTの大型化を回避することが可能となる。

【0239】

次に、半導体装置20における保護系回路の改善点について説明する。

【0240】

第1に、本実施形態の半導体装置20では、オープン/ショート検出部222におけるショート検出の方式がディレイカウンタ方式に変更されている。すなわち、LED1端子〜LED4端子のいずれかが4.5[V]に達した時点で、即座に回路動作をオフラッチさせるのではなく、所定時間に亘って継続的に4.5[V]を上回っていることが確認された時点で、回路動作をオフラッチする構成とされている。このような方式を採用することにより、誤検出を効果的に防止することが可能となる。

【0241】

第2に、本実施形態の半導体装置20には、LEDのアノード及びカソードにおけるショート(主にグランドショート)を検出し、適切な保護動作を行う保護機能部が内蔵されている。具体的に述べると、SCP部204は、OVP端子の端子電圧VPが所定時間に亘って所定電圧以下となっていることを確認したときに、LED列のアノード端がグランドショート(ないしは、これに相当する低電位点に短絡)していると認識して、回路動作をオフラッチする構成とされている。また、オープン/ショート検出部222は、既存のオープン検出機能部を流用し、LED端子電圧V1〜V4のいずれかが所定時間に亘って所定電圧以下となっていることを確認したときに、LED列のカソード端がグランドショートしていると認識して、回路動作をオフラッチする構成とされている。このような保護機能部を内蔵することにより、半導体装置20の安全性を一層高めることが可能となる。

【0242】

第3に、本実施形態の半導体装置20は、回路動作の停止時にロードスイッチQ1をオフさせていた第1実施形態と異なり、ソフトスタート部218にOCP信号及びOVP信号を入力し、異常発生時には、ソフトスタート電圧(コンデンサCSSの充電電圧)を引き下げる構成とされている。このような構成とすることにより、回路動作の復帰時には、再度ソフトスタートがかかるので、復帰時の突入電流などを防止することが可能となる。

【0243】

最後に、半導体装置20における省電力機能について説明する。

【0244】

本実施形態の半導体装置20は、制御ロジック部208にタイマラッチ機能が具備されており、所定時間に亘ってPWM信号がローレベルに維持されていることを確認したときに、半導体装置20の消費電力を低下させる省電力モード(スリープモード)に移行する構成とされている。このような構成とすることにより、半導体装置20に省電力化を実現することが可能となる。なお、上記の省電力モードでは、電源電圧VCCの供給経路を遮断するのではなく、各回路部の駆動電流ICCを生成する駆動電流生成部(不図示)の動作をオフさせることが望ましい。

【0245】

なお、上記の実施形態では、本発明の適用対象として、カーナビモニタのバックライトや、中小型LCDパネルのバックライトなどの駆動制御を行う半導体装置を例に挙げて説明を行ったが、本発明の適用対象はこれに限定されるものではなく、その他の負荷駆動装置にも広く適用することが可能である。

【0246】

また、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。

【産業上の利用可能性】

【0247】

本発明は、負荷(中小型LCDパネルのLEDバックライトなど)の駆動制御を行う駆動装置に好適な技術である。

【符号の説明】

【0248】

10 半導体装置

101 基準電圧生成部(VREG部)

102 スイッチ

103 減電圧保護部(UVLO部)

104 温度保護部(TSD部)

105 過電圧保護部(OVP部)

106 入力バッファ

107 発振器部

108 PWMコンパレータ

109 制御ロジック部

110 ドライバ

111 過電流保護部 (OCP部)

112 コンパレータ

113 エラーアンプ

114 ソフトスタート部

115 入力バッファ

116 電流設定部

117 定電流ドライバ

118 オープン/ショート検出部

119 入力バッファ

120 入力バッファ

20 半導体装置

201 基準電圧生成部(VREG部)

202 減電圧保護部(UVLO部)

203 温度保護部(TSD部)

204 ショート保護部(SCP部)

205 過電圧保護部(OVP部)

206 過電流保護部 (OCP部)

207 コンパレータ

208 制御ロジック部

209 入力バッファ

210 発振器部

211 スロープ電圧生成部

212 PWMコンパレータ

213 ドライバ制御部

214 ドライバ

215 Nチャネル型電界効果トランジスタ

216 ドライバ

217 エラーアンプ

218 ソフトスタート部

219 入力バッファ

220 電流設定部

221 定電流ドライバ

222 オープン/ショート検出部

223 入力バッファ

224 入力バッファ

【技術分野】

【0001】

本発明は、負荷(発光ダイオード等)の駆動制御を行う駆動装置に関するものである。

【背景技術】

【0002】

LCD[Liquid Crystal Display]パネル(例えばカーナビモニタ)のバックライトとして、現行では、冷陰極管蛍光ランプ(CCFL[Cold Cathode Fluorescent Lamp])が主に用いられているが、Hgフリー対応の流れや、高輝度・省電力・高寿命などの利点から、近年では、白色LED[Light Emitting Diode]が実用化されており、その駆動制御を行うLED駆動装置(いわゆるLEDドライバ)についても、様々な技術が開示・提案されている(例えば、特許文献1を参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−13183号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

PWM制御でLEDを発光させようとするとき、素子の特性で制御できるデューティ比の範囲が制限されてしまっていた。

【0005】

また、素子の特性によって、LEDを発光させる電流の精度が低かった。

【0006】

本発明は、上記の問題点に鑑み、制御可能なデューティ比の範囲を広げ、素子の変動に依らず、制御電流の精度を高めることが可能な駆動装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成すべく、本発明に係る駆動装置は、一方の端子にパルス状の電流が入力され、更に前記一方の端子と制御端子が接続された第1のトランジスタと、一方の端子に少なくとも1つの負荷が接続され、他方の端子が前記第1のトランジスタの他方の端子と共に基準電位に接続され、制御端子が前記第1のトランジスタの制御端子にそれぞれ接続された第2のトランジスタと、前記第1のトランジスタの制御端子と前記第1のトランジスタの他方の端子との間に、抵抗素子が接続された構成(第1の構成)とされている。

【0008】

また、上記第1の構成から成る駆動装置は、前記第1のトランジスタと前記第2のトランジスタの一方の端子にそれぞれ一定の電圧を供給する第2の基準電圧供給部と第2の基準電圧供給部とを更に備えた構成(第2の構成)にするとよい。

【発明の効果】

【0009】

本発明に係る駆動装置であれば、抵抗を挿入することによって、トランジスタの立ち上がりを早めることができることにより、制御可能なデューティ比の範囲を広げることが可能となる。

【0010】

また、本発明に係る駆動装置であれば、トランジスタの一方の端子を一定電圧とすることにより、素子の変動に依らず、制御電流の精度を高めることが可能となる。

【図面の簡単な説明】

【0011】

【図1】は、本発明に係る半導体装置の第1実施形態を示すブロック図である。

【図2】は、半導体装置10のピン配置図である。

【図3】は、外部端子のピン番号、端子名、及び、機能を示した対応表である。

【図4】は、半導体装置10の外部接続を説明するための図である。

【図5】は、外部素子の定数の一例を示す設定表である。

【図6】は、外部端子の入出力等価回路図である。

【図7】は、半導体装置10の電気的特性を示す表である。

【図8】は、FAIL1信号の出力段を示す図である。

【図9】は、FAIL2信号の出力段を示す図である。

【図10】は、オープン/ショートの検出動作を説明するための図である。

【図11】は、LEDイネーブル信号LEDEN1、LEDEN2の入力論理と、LED出力端子LED1〜LED4のオン/オフ状態との相関関係を示す真理値表である。

【図12】は、電流設定部116と定電流ドライバ117の一構成例を示す回路図である。

【図13】は、抵抗RSETと出力電流ILEDとの相関関係を示すグラフである。

【図14】は、PWM調光制御の一例を示すタイミングチャートである。

【図15】は、抵抗RTと発振周波数FOSCとの相関関係を示すグラフである。

【図16】は、OCP部111の動作に関連する外部素子の接続関係を説明するための図である。

【図17】は、コイルL1の選定に関して説明するための図である。

【図18】は、出力コンデンサCVOUTの選定に関して説明するための図である。

【図19】は、入力コンデンサCVCCの選定に関して説明するための図である。

【図20】は、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して説明するための図である。

【図21】は、トランジスタQ1のゲート・ソース間容量とソフトスタート時間との相関関係を示すグラフである。

【図22】は、DC/DCコンバータのLC共振回路を示す回路図である。

【図23】は、位相進み手段の第1例(出力コンデンサのESR成分)を示す回路図である。

【図24】は、位相進み手段の第2例(COMP端子に接続されるCR成分)を示す回路図である。

【図25】は、半導体装置10の動作シーケンスを示すタイミングチャートである。

【図26】は、本発明に係る半導体装置の第2実施形態を示すブロック図である。

【図27】は、半導体装置20のピン配置図である。

【図28】は、外部端子のピン番号、端子名、及び、機能を示した対応表である。

【図29】は、半導体装置20の電気的特性を示す表である。

【図30】は、電流設定部220と定電流ドライバ221の一構成例を示す回路図である。

【図31】は、ミラー比とトランジスタサイズとの相関関係を示す模式図である。

【図32】は、抵抗を千鳥配置としたレイアウト図である。

【発明を実施するための形態】

【0012】

図1は、本発明に係る半導体装置の第1実施形態を示すブロック図である。

【0013】

まず、本実施形態の半導体装置10の概要について述べる。

【0014】

半導体装置10は、36V高耐圧の白色LEDドライバICであり、昇圧DC/DCコンバータ、並びに、4チャネル出力の定電流ドライバが1チップに集積化されている。なお、半導体装置10は、PWM[Pulse Width Modulation]制御、及び、VDAC制御のいずれによっても、白色LEDの調光制御が可能である。

【0015】

次に、本実施形態の半導体装置10の特長について述べる。

【0016】

第1の特長は、電源電圧VCCの入力電圧範囲が4.5〜30[V]である点である。第2の特長は、昇圧DC/DCコントローラを内蔵している点である。第3の特長は、LEDに出力電流ILEDを供給する4チャネルの定電流ドライバを内蔵している点である(最大電流値:150[mA])。第4の特長は、PWM調光(デューティ比:0.38〜99.5[%])に対応している点である。第5の特長は、各種保護機能部(UVLO[Under Voltage Lock Out]、OVP[Over Voltage Protection]、TSD[Thermal Shut Down]、OCP[Over Current Protection])を内蔵している点である。第6の特長は、LED異常状態(オープン/ショート)の検出機能を内蔵している点である。第7の特長は、HSOP−M28パッケージ(図2を参照)を採用した点である。

【0017】

なお、本実施形態の半導体装置10は、カーナビモニタのバックライトや、中小型LCDパネルのバックライトなどの駆動制御用として用いられる。

【0018】

上記特長を有する本実施形態の半導体装置10は、図1に示すように、基準電圧生成部101(以下では、VREG部101と呼ぶ)と、スイッチ102と、減電圧保護部103(以下では、UVLO部103と呼ぶ)と、温度保護部104(以下では、TSD部104と呼ぶ)と、過電圧保護部105(以下では、OVP部105と呼ぶ)と、入力バッファ106と、発振器部107と、PWMコンパレータ108と、制御ロジック部109と、ドライバ110と、過電流保護部111(以下では、OCP部111と呼ぶ)と、コンパレータ112と、エラーアンプ113と、ソフトスタート部114と、入力バッファ115と、電流設定部116と、定電流ドライバ117と、オープン/ショート検出部118と、入力バッファ119及び120と、を集積化して成る。

【0019】

なお、半導体装置10の上記回路部は、VREGブロック(VREG部101)と、昇圧DC/DCコントローラブロック(スイッチ102、入力バッファ106、発振器部107、PWMコンパレータ108、制御ロジック部109、ドライバ110、OCP部111、コンパレータ112、エラーアンプ113、及び、ソフトスタート部114)と、カレントドライバブロック(入力バッファ115、電流設定部116、定電流ドライバ117、オープン/ショート検出部118、及び、入力バッファ119及び120)と、保護ブロック(UVLO部103、TSD部104、OVP部105)の4ブロックに大別することができる。

【0020】

また、本実施形態の半導体装置10は、外部との電気的接続を確立する手段として、28本の外部端子(1ピン〜28ピン)を有して成る。

【0021】

図2は、半導体装置10のピン配置図であり、図3は、外部端子のピン番号、端子名、及び、機能を示した対応表である。なお、図2において、半導体装置10の中央部両サイドに設けられた幅広の端子は、サブグランドと繋がるFIN端子であり、放熱性を良くするためのものである。

【0022】

次に、半導体装置10の外部接続について詳細な説明を行う。

【0023】

図4は、半導体装置10の外部接続を説明するための図である。

【0024】

図4に示した外部素子に関して、デカップリングコンデンサCVCC、CREGは、できる限り、ICピンの直近に接続することが望ましい。

【0025】

CS端子(22ピン)、GND端子(7ピン)、及び、PGND(21ピン)には、大電流が流れる可能性があるため、それぞれ独立で配線するとともに、インピーダンスを低くすることが望ましい。

【0026】

VDAC端子(8ピン)、ISET端子(9ピン)、RT端子(26ピン)、及び、COMP端子(28ピン)には、ノイズが載らないように留意すべきである。

【0027】

PWM端子(5ピン)、SYNC端子(6ピン)、LED1端子(12ピン)、LED2端子(14ピン)、LED3端子(15ピン)、及び、LED4端子(17ピン)は、スイッチングされるため、周辺パターンに影響を与えないように留意すべきである。

【0028】

図4中の太線部分は、幅広のパターンで、かつ、できるだけ短くレイアウトすることが望ましい。

【0029】

なお、本実施形態の半導体装置10では、パワートランジスタQ2を外付けとしているので、放熱性を高めることが可能となる。

【0030】

図5は、外部素子の定数の一例を示す設定表である。なお、本図に例示した定数は、電源電圧VCC=12[V]、LED5直4並列、出力電流ILED=50[mA]のときに動作を確認した定数である。従って、使用条件などによって最適値は異なるため、十分評価の上、定数を決定することが望ましい。

【0031】

図6は、外部端子の入出力等価回路図である。

【0032】

図6に示すように、半導体装置10の外部端子には、いずれも静電保護ダイオードが接続されている。

【0033】

また、コントロール関連端子であるPWM端子(5ピン)、SYNC端子(6ピン)、VDAC端子(8ピン)、ISET端子(9ピン)、LEDEN1端子(10ピン)、LEDEN2端子(11ピン)、CS端子(22ピン)、SWOUT端子(23ピン)、EN端子(24ピン)、OVP端子(25ピン)、RT端子(26ピン)、SS端子(27ピン)、COMP端子(28ピン)については、上側(信号ラインから電源ラインに電荷を引き抜く経路側)の静電保護ダイオードのカソードを基準電圧VREGや電源電圧VCCの印加端に接続するのではなく、中間電圧CL10V(例えば10[V]、図6の最右下欄を参照)の印加端に接続する構成とされている。

【0034】

このような構成とすることにより、電源電圧VCCが印加されていない場合や、イネーブル信号ENによって基準電圧VREGが生成されていない場合に、外部端子に正電圧が印加されたとしても、静電保護ダイオードを介して基準電圧ラインや電源電圧ラインに過大電流が流れ込むことはないので、回路の破壊や誤動作を防止することが可能となる。

【0035】

図7は、上記構成から成る半導体装置10の電気的特性を示す表である。なお、図7に示す電気的特性は、特に指定のない限り、電源電圧VCC=12[V]、周囲温度Ta=25[℃]での数値を示している。

【0036】

次に、半導体装置10のVREGブロック(VREG部101)について、先出の図1などを参照しながら、詳細な説明を行う。

【0037】

VREG部101は、EN端子(24ピン)に入力されるイネーブル信号ENがハイレベルであるときに、VCC端子(1ピン)に入力される電源電圧VCC(12[V])からの基準電圧VREG(5[V](Typ.))を生成する手段である。この基準電圧VREGは、内部回路の電源として使用され、また、IC外で端子をハイレベル電圧に固定するときにも使用される。

【0038】

また、VREG部101は、UVLO機能を具備しており、2.9[V](Typ.)以上になると動作を開始し、2.8[V](Typ.)以下になると動作を停止する。

【0039】

なお、VREG端子(4ピン)は、位相補償用の容量CREG(10μF(Typ.))を接続するための外部端子である。このような位相補償用の容量CREGを接続することにより、VREG部101の回路動作を安定化することが可能となる。

【0040】

次に、半導体装置10の自己診断機能について、詳細な説明を行う。

【0041】

本実施形態の半導体装置10は、自身に内蔵された保護回路の動作状態を示すべく、FAIL1端子(3ピン)及びFAIL2端子(20ピン)から、オープンドレイン形式でFAIL1信号及びFAIL2信号を各々出力する機能を具備している。

【0042】

UVLO部103、TSD部104、OVP部105、及び、OCP部111のいずれかが異常状態を検出し、その出力信号がローレベルとされたとき、制御ロジック部109は、図8に示す出力段を介して、FAIL1信号をローレベルにするとともに、SWOUT端子(23ピン)をローレベル固定とすることで、昇圧動作を停止する。

【0043】

ただし、OCP部111は、パルスバイパルス方式であるため、昇圧DC/DCコンバータの発振周波数FOSCで決定される1周期分だけ、SWOUT端子がローレベル固定とされた後、昇圧動作が復帰される。このようなパルスバイパルス方式により、回路動作を完全に停止させないまま、電流制限をかけることができるので、誤動作で回路が停止された場合でも、遅滞なく自動復帰が行われるため、ユーザにとって使い勝手が良い。

【0044】

また、UVLO部103、TSD部104、及び、OVP部105の少なくとも一が異常状態を検出したとき、LED1端子、LED2端子、LED3端子、及び、LED4端子(12ピン、14ピン、15ピン、17ピン)は、いずれもオープン(ハイインピーダンス)とされる。

【0045】

また、FAIL1端子(3ピン)から出力されるFAIL1信号と、LOADSW端子(2ピン)から出力されるLOADSW信号とは、互いに反転信号となっており、FAIL1信号がローレベルとされると、LOADSW信号はスイッチ102を用いてハイレベルとされる。従って、UVLO部103、TSD部104、OVP部105、及び、OCP部111のいずれかが異常状態を検出したとき、LOADSW端子(2ピン)に外部接続されるロードスイッチ(図4のPチャネル型電界効果トランジスタQ1)はオフとされる。従って、半導体装置10の異常時には、昇圧動作を停止させて、ICが破壊や発煙・発火に至るのを未然に防止することが可能となる。

【0046】

一方、FAIL2端子(20ピン)から出力されるFAIL2信号は、オープン/ショート検出部118が異常状態(オープン状態またはショート状態)を検出したとき、図9に示す出力段を介してローレベル出力とされる。なお、オープン/ショート検出部118から出力されるFAIL2信号は、ラッチ方式となっており、そのラッチ解除は、イネーブル信号ENのオン/オフ(延いてはUVLO信号のオン/オフ)に基づいて行われる。

【0047】

オープン/ショート検出部118は、図10に示す通り、所定のLED制御電圧VLED(0.8[V](Typ.))に維持されているはずのLED端子電圧V1〜V4(LED1端子〜LED4端子の各端子電圧)が0.15[V](Typ.)以下となったときに、そのLED端子がオープンであると判定し、さらに、OVP端子(25ピン)の端子電圧VP(出力電圧VOUTの分圧電圧)が1.7[V](Typ.)に達したときに、オープンと判定されたLED端子に対する電流出力をオフとすべく、定電流ドライバ117に対して指示を送るとともに、FAIL2信号をローレベルに遷移させる。なお、図10の例ではLED1端子がオープンとなった場合を例示している。

【0048】

このように、LED端子のオープン検出と電流出力のオフ制御を2段階で実施することにより、不必要なシャットダウンを回避することが可能となる。

【0049】

なお、上記のオープン検出については、OVP部105による過電圧検出で代用することも可能である。すなわち、OVP部105では、OVP端子の端子電圧VPが所定の過電圧検出電圧VDOVP(2.0[V](Typ.))に達したことを検出して、DC/DCコンバータの昇圧動作が停止され、全チャネルの電流出力がオフとされるので、敢えてオープン検出を行わなくとも、過電圧検出とオープン検出とを兼ねた形で、全チャネルの電流出力をオフとすることが可能である。

【0050】

ただし、オープンとなったチャネルだけをオフしたい場合には、上記で説明した通り、LED端子電圧V1〜V4を監視することで、オープンとなったLED端子を特定し、そのチャネルのみをオフとすればよい。特に、全チャネルの電流出力をオフにすると、使用に支障を生じるアプリケーション(カーナビモニタのバックライト駆動装置など)への適用に際しては、各チャネルの電流出力を個別にオフし得る本実施形態の構成が望ましい。

【0051】

また、オープン/ショート検出部118は、LED端子電圧V1〜V4が4.5[V](Typ.)以上となったときにショートと判断する。言い換えれば、正常時と異常時との間で、LED端子電圧の差分が3.7[V](=4.5[V]−0.8[V])(Typ.)以上となったときに、ショートが検出されることになる。

【0052】

なお、白色LEDの順方向降下電圧VFは約3.4[V]であるため、上記の設定例では、LED1個がショートしただけではショート検出されず、LED2個以上がショートした場合にショート検出される。このようなスレッショルドレベルの設定により、LEDショートが生じてはいるものの、その使用に際して、さほど支障を来さない範囲については、不要なシャットダウンを回避することが可能となる。

【0053】

このように、オープン/ショート検出部118でのショート検出は、例えば、LED1端子〜LED4端子に各々外部接続されるLED列のうち、いずれか一のLED列について、これを形成する一つのLEDがショート状態(アノード/カソード間の短絡状態)となった結果、当該ショート状態となったLEDの順方向降下電圧VF分だけ、LED列全体としての順方向降下電圧が低い状態となり、一のLED端子電圧が他のLED端子電圧に比べて、LEDの順方向降下電圧VF分だけ高くなった状態を検出する動作を言う。従って、図1でも示したように、オープン/ショート検出部118とOVP部105とは、別の保護ブロックとして形成されている。

【0054】

ただし、本実施形態の半導体装置10では、一旦オープン/ショートが検出されると、以後、ショート検出信号はマスクされる。図10の例に即して述べると、LED1端子のオープンが検出されて以後、その他のLED2端子〜LED4端子については、そのショート検出信号がマスクされる。このようなマスク制御により、LED1端子がオープンとなった結果、LED端子電圧V1がほぼGNDまで低下し、これを受けて出力電圧VOUTが上昇し、それに追従してLED端子電圧V2〜V4が通常時より上昇した場合であっても、これをショートと誤検出することがなくなる。なお、オープン検出信号は、オープン/ショート検出後もマスクされることはない。

【0055】

また、上記のショート検出信号は、PWM駆動による出力電流ILEDのオフ期間にもマスクされる。このようなマスク制御により、出力電流ILEDのオフ期間において、LED端子電圧V1〜V4が跳ね上がった場合でも、これをショートと誤検出することがなくなる。なお、上記のマスク制御に関しては、PWM信号の論理変遷タイミングと、出力電流ILEDのオン/オフタイミングとの間に遅延が生じることを考慮して、出力電流ILEDを流し始めるタイミング(定電流ドライバ117の出力トランジスタがオンするタイミング)から、PWM信号がローレベルに立ち下がるタイミングまでをマスクすればよい(後出の図13を参照)。

【0056】

また、LED1端子〜LED4端子に付加的な容量が接続されると、出力オン時にLED端子電圧V1〜V4が低下するのが遅くなり、ショート検出が誤動作することがあるので、注意が必要である。また、FAIL1信号及びFAIL2信号は、いずれもオープンドレイン形式であるため、FAIL1端子及びFAIL2端子は、基準電圧VREGの印加端に対して抵抗(図4の抵抗RFL1、RFL2)でプルアップされている。

【0057】

次に、半導体装置10のカレントドライバブロック(入力バッファ115、電流設定部116、定電流ドライバ117、オープン/ショート検出部118、及び、入力バッファ119及び120)について、詳細な説明を行う。

【0058】

LED出力端子LED1〜LED4のうち、定電流ドライバ117からの出力電流ILEDを使用しない出力端子(延いては、点灯させないLED列)がある場合には、LEDEN1端子(10ピン)、及び、LEDEN2端子(11ピン)を用いて、LED出力端子LED1〜LED4に対する電流出力を各個にオフすることが可能である。

【0059】

図11は、LEDイネーブル信号LEDEN1、LEDEN2の入力論理と、LED出力端子LED1〜LED4のオン/オフ状態との相関関係を示す真理値表である。

【0060】

なお、LEDイネーブル信号LEDEN1、LEDEN2を用いることなく、使用しないLED端子をオープンすると、オープン/ショート検出部118において、オープン検出が誤動作してしまう。また、LEDイネーブル信号LEDEN1、LEDEN2を用いて、LED端子への電流出力を適宜オフさせた場合にも、エラーアンプ113の入力段は動作しているため、LED1端子〜LED4端子は、GND固定にせず、オープンもしくは定電圧VREGの印加端に接続しておくことが望ましい。また、出力電流ILEDをPWM駆動している際には、LEDイネーブル信号LEDEN1、LEDEN2を切り替えない方が望ましい。

【0061】

次に、出力電流ILEDの設定方法について、図12を参照しながら詳細に説明する。

【0062】

図12は、電流設定部116と定電流ドライバ117の一構成例を示す回路図である。

【0063】

図12に示すように、電流設定部116は、オペアンプA1と、直流電圧源A2と、npn型バイポーラトランジスタA3と、抵抗A4、A5と、pnp型バイポーラトランジスタA6〜A9と、抵抗A10(抵抗値R)と、を有して成る。

【0064】

オペアンプA1の第1非反転入力端(+)は、VDAC端子(8ピン)に接続されている。オペアンプA2の第2非反転入力端(+)は、直流電圧源A2の正極端に接続されており、所定の定電圧VISET(=2.0[V])が印加されている。直流電圧源A2の負極端は、接地端に接続されている。オペアンプA2の反転入力端(−)は、ISET端子(9ピン)に接続されている。トランジスタA3のベースは、オペアンプA1の出力端に接続されている。トランジスタA3のエミッタは、ISET端子に接続されている。

【0065】

抵抗A4、A5の各一端は、いずれも基準電圧VREGの印加端に接続されている。抵抗A4の他端は、トランジスタA6のエミッタに接続されている。抵抗R5の他端は、トランジスタA7のエミッタに接続されている。トランジスタA6、A7のベースは、互いに接続されており、その接続ノードは、トランジスタA7のコレクタに接続されている。トランジスタA6のコレクタは、トランジスタA8のエミッタに接続されている。トランジスタA7のコレクタは、トランジスタA9のエミッタに接続されている。トランジスタA8、A9のベースは、互いに接続されており、その接続ノードは、トランジスタA8のコレクタに接続されている。トランジスタA8のコレクタは、トランジスタA3のコレクタに接続されている。トランジスタA9のコレクタは、抵抗A10を介して、接地端に接続されている。

【0066】

一方、図12に示すように、定電流ドライバ117は、LED1端子〜LED4端子に対して各々出力電流ILEDを供給する4チャネルの出力段Ch1、Ch2、Ch3、Ch4を有して成る。なお、出力段Ch1は、オペアンプB1と、Nチャネル型電界効果トランジスタB2と、抵抗B3(抵抗値5R)と、カレントミラー回路B4(ミラー比1:1)と、抵抗B5(抵抗値5R)と、オペアンプB6と、Nチャネル型電界効果トランジスタB7と、抵抗B8(抵抗値5R)と、カレントミラー回路B9(ミラー比1:10)と、オペアンプB10と、直流電圧源B11と、Nチャネル型電界効果トランジスタB12〜B14と、オペアンプB15と、直流電圧源B16と、Nチャネル型電界効果トランジスタB17と、抵抗B18と、を有して成る。

【0067】

オペアンプB1の非反転入力端(+)は、トランジスタA9と抵抗A10との接続ノードに接続されている。オペアンプB1の反転入力端(−)は、抵抗B3の一端に接続されている。抵抗B3の他端は、接地端に接続されている。トランジスタB2のドレインは、カレントミラー回路B4の入力端に接続されている。トランジスタB2のソースは、抵抗B3の一端に接続されている。トランジスタB2のゲートは、オペアンプB1の出力端に接続されている。カレントミラー回路B4の電源入力端は、基準電圧VREGの印加端に接続されている。

【0068】

オペアンプB6の非反転入力端(+)は、カレントミラー回路B4の出力端と抵抗B5の一端に各々接続されている。オペアンプB6の反転入力端は、抵抗B8の一端に接続されている。抵抗B5、B8の他端は、いずれも接地端に接続されている。トランジスタB7のドレインは、カレントミラー回路B9の入力端に接続されている。トランジスタB7のソースは、抵抗B8の一端に接続されている。トランジスタB7のゲートは、オペアンプB6の出力端に接続されている。カレントミラー回路B9の電源入力端は、基準電圧VREGの印加端に接続されている。

【0069】

オペアンプB10の非反転入力端(+)は、直流電圧源B11の正極端に接続されている。直流電圧源B11の負極端は、接地端に接続されている。トランジスタB12のドレインは、カレントミラー回路B9の出力端に接続されている。トランジスタB12のソースは、オペアンプB10の反転入力端(−)に接続されている。トランジスタB12のゲートは、オペアンプB10の出力端に接続されている。

【0070】

トランジスタB13のドレインは、トランジスタB12のソースに接続されている。トランジスタB13、B14のゲートは互いに接続されており、その接続ノードは、トランジスタB12のドレインに接続される一方、抵抗B18を介して接地端にも接続されている。トランジスタB13、B14のソースは、いずれも接地端に接続されている。

【0071】

オペアンプB15の非反転入力端(+)は、直流電圧源B16の正極端に接続されている。直流電圧源B16の負極端は、接地端に接続されている。トランジスタB17のドレインは、LED1端子に接続されている。トランジスタB17のソースは、オペアンプB15の反転入力端(−)に接続される一方、トランジスタB14のドレインにも接続されている。トランジスタB17のゲートは、オペアンプB15の出力端に接続されている。

【0072】

なお、定電流ドライバ117を構成するその余の出力段Ch2〜Ch4は、上記の出力段Ch1と同様の構成から成るため、詳細な説明は割愛する。

【0073】

上記構成から成る電流設定部116、及び、定電流ドライバ117において、出力電流ILEDは、次の(1)式に基づいて設定される。

【0074】

【数1】

【0075】

上記(1)式において、min{VDAC,2.0[V]}というパラメータは、VDAC端子(8ピン)に入力される制御電圧VDACと、電流設定部116の内部で予め定められた定電圧VISET(=2.0[V])のうち、いずれか低い方の電圧値である。また、RSETというパラメータは、ISET端子(9ピン)に外部接続される抵抗RSETの抵抗値であり、3300(Typ.)というパラメータは、定電流ドライバ117の回路内部で決まる定数である。

【0076】

すなわち、ISET端子(9ピン)に抵抗RSETをプルダウン接続することで、これに流れる基準電流ISETの所定ゲイン倍(例えば3300倍)が出力電流ILEDの最大値(例えば50[mA])として設定される形となっている。

【0077】

図12の例に即して具体的に述べると、定電流ドライバ117では、まず、オペアンプB1、トランジスタB2、及び、抵抗B3(抵抗値5R)を用いて、抵抗A10の端子電圧Va(=ISET×R)が電圧/電流変換され、基準電流ISETを1/5とした中間電流Ia(=1/5ISET)が生成される。次に、カレントミラー回路B4を用いて、中間電流Iaが1:1でミラーされ、中間電流Ib(=1/5ISET)が生成される。次に、抵抗B5(抵抗値5R)を用いて、中間電流Ibが電流/電圧変換され、端子電圧Vb(=ISET×R)が生成される。次に、オペアンプB6、トランジスタB7、並びに、抵抗B8(抵抗値5R)を用いて、抵抗B5の端子電圧Vbが電圧/電流変換され、中間電流Ic(=1/5ISET)が生成される。次に、カレントミラー回路B9を用いて、中間電流Icが1:10でミラーされ、基準電流ISETを2倍とした中間電流Id(=2ISET)が生成される。そして、最終的には、トランジスタB13、B14から成るカレントミラー回路を用いて、中間電流Idが1:1650でミラーされ、基準電流ISETを3300倍とした出力電流ILED(=3300ISET)が生成される。

【0078】

なお、出力電流ILEDの精度を高めるために、最終段のカレントミラー回路については、オペアンプB10、B15を用いて、トランジスタB13、B14のドレイン・ソース間電圧が同一(例えば0.3[V])とされている。また、定電流ドライバ117は、入力される基準電流ISETに基づいて、電圧/電流変換と電流/電圧変換を繰り返しながら、所望の出力電流ILEDを生成する構成とされている。従って、上記変換処理に用いる抵抗素子(図12の例では、抵抗B3、B5、B8)が増え、延いては、そのトリミング機会が増加する。このように、トリミング可能な抵抗を数多く有する構成であれば、それらの抵抗値を微調整することにより、出力電流ILEDの相対ばらつき幅:±4%、絶対ばらつき幅:±6%を実現することができ、延いては、輝度ばらつきの低減やLEDの長寿命化に貢献することが可能となる。

【0079】

図13は、抵抗RSETと出力電流ILEDとの相関関係を示すグラフである。なお、抵抗RSETとしては、300[kΩ]以下のものを用いることが望ましい。

【0080】

また、上記の制御電圧VDACを用いて、出力電流ILEDの可変制御(LEDの調光制御)を行う場合、その入力範囲は、0.1〜2.0[V]の範囲とすればよい。このような制御電圧VDACを印加することにより、出力電流ILEDを最大値から低減していくことが可能となる。

【0081】

一方、制御電圧VDACとして2.0[V]以上が入力された場合には、上記の(1)式で与えられるように、定電圧VISETの電圧値が選択されることになるため、制御電圧VDACによる調光機能が不使用状態となる。なお、制御電圧VDACによる調光機能を使用しない場合には、誤動作を回避する観点から、VDAC端子をオープンとせず、基準電圧VREG(5[V])の印加端に接続しておくとよい。

【0082】

また、本実施形態の半導体装置10では、上記の制御電圧VDACを用いたLEDの調光制御のほか、PWM端子(5ピン)に入力されるPWM信号を用いて、基準電流ISETのオン/オフ制御を行うことで、LEDの調光制御を行うことも可能である。

【0083】

すなわち、PWM信号に基づいて、出力電流ILEDの基準となる基準電流ISETをパルス電流とすれば、PWM信号のデューティ比が出力電流ILEDのデューティ比となるので、出力電流ILEDをその最大値(ないしは、制御電圧VDACで定められた電流値)から、見かけ上低減することが可能となる。なお、PWM信号に基づく基準電流ISETのオン/オフ制御手段(パルス電流生成手段)については、電流設定部116の出力段(定電流ドライバ117の前段)に設ければよい。

【0084】

また、本実施形態の半導体装置10では、PWM信号に対する出力電流ILEDの応答性を上げるため、最終段のカレントミラー回路について、トランジスタB13、B14のゲート・ソース間にプルダウン抵抗B18(500[kΩ])が挿入されている。このようなプルダウン抵抗B18の挿入により、トランジスタB13、B14の立ち上がりを早めることができるので、PWM調光能力の向上(最低デューティ比:0.38%(150[Hz]時))を実現することが可能となる。

【0085】

一方、PWM信号による調光機能を使用しない場合(デューティ比100%)には、PWM端子をハイレベル(例えば定電圧VREG)に固定すればよい。なお、PWM端子には、ローパスフィルタ(カットオフ周波数30[kHz])を挿入することが望ましい。

【0086】

図14は、PWM調光制御の一例を示すタイミングチャートであり、PWM信号と出力電流ILEDとの相関関係を示している。なお、図14(a)は、PWM信号の周波数が150[Hz]、デューティ比が0.38[%]である場合を示しており、図14(b)は、PWM信号の周波数が150[Hz]、デューティ比が50[%]である場合を示している。また、図14(c)は、PWM信号の周波数が20[kHz]、デューティ比が50[%]である場合を示している。なお、図14(a)、(b)、(c)の横軸は、いずれも時間軸であるが、PWM信号の周波数が各々大きく異なるため、その描写レンジは互いに異なっている。通常、PWM信号の周波数は、100〜200[Hz]程度で固定的に設定される。

【0087】

次に、半導体装置10の昇圧DC/DCコントローラブロック(入力バッファ106、発振部107、PWMコンパレータ108、制御ロジック部109、ドライバ110、OCP部111、コンパレータ112、エラーアンプ113、及び、ソフトスタート部114を含む回路ブロック)について詳細に説明する。

【0088】

まず、昇圧DC/DCコントローラブロックの基本動作(昇圧動作)について、先出の図1及び図4を参照しながら、詳細に説明する。

【0089】

トランジスタQ2は、SWOUT端子(23ピン)からの出力に応じてオン/オフ制御されるNチャネル電界効果型の出力パワートランジスタである。

【0090】

トランジスタQ2がオン状態にされると、コイルL1にはトランジスタQ2を介して接地端に向けたスイッチ電流が流れ、その電気エネルギが蓄えられる。なお、トランジスタQ2のオン期間において、既に出力コンデンサCVOUTに電荷が蓄積されていた場合、負荷である発光ダイオード列(図4では明示されていないが、出力電圧VOUTの引出端とLED1端子〜LED4端子との間に接続されるLED列)には、出力コンデンサCVOUTからの電流が流れることになる。また、このとき、ダイオードD1のアノード電位は、トランジスタQ2を介して、ほぼ接地電位まで低下するため、ダイオードD1は逆バイアス状態となり、出力コンデンサCVOUTからトランジスタQ2に向けて電流が流れ込むことはない。

【0091】

一方、トランジスタQ2がオフ状態にされると、コイルL1に生じた逆起電圧によってそこに蓄積されていた電気エネルギが放出される。このとき、ダイオードD1は順バイアス状態となるため、ダイオードD1を介して流れる電流は、負荷であるLED列に流れ込むとともに、出力コンデンサCVOUTを介して接地端にも流れ込み、出力コンデンサCVOUTを充電することになる。上記の動作が繰り返されることによって、負荷であるLED列には、出力コンデンサCVOUTによって昇圧され、かつ、平滑された出力電圧VOUTが供給される。

【0092】

このように、本実施形態の半導体装置10は、トランジスタQ2のオン/オフ制御によってエネルギ貯蔵素子であるコイルL1を駆動することにより、電源電圧VCCを昇圧して出力電圧VOUTを生成するチョッパ型昇圧回路の一構成要素として機能する。

【0093】

次に、昇圧DC/DCコントローラブロックの出力帰還制御について詳細に説明する。

【0094】

エラーアンプ113は、第1〜第4の反転入力端(−)に各々印加されるLED端子電圧V1〜V4の最低値と、非反転入力端(+)に入力される所定のLED制御電圧VLEDとの差分を増幅して誤差電圧Verrを生成する。すなわち、誤差電圧Verrの電圧値は、出力電圧VOUTがその目標設定値よりも低いほど高レベルとなる。

【0095】

一方、PWMコンパレータ108は、第1、第2の非反転入力端(+)に各々印加される誤差電圧Verr及び上限電圧Vlmtのいずれか低い方と、反転入力端(−)に印加される三角波電圧(ランプ波電圧)Voscとを比較することで、その比較結果に応じたデューティの比較信号(PWM駆動波形)を生成する。すなわち、比較信号の論理は、誤差電圧Verr(或いは上限電圧Vlmt)が三角波電圧Voscよりも高ければハイレベルとなり、低ければローレベルとなる。

【0096】

従って、定常動作時における比較信号のオンデューティ(単位期間に占めるトランジスタQ2のオン期間の比)は、誤差電圧Verrと三角波電圧Voscの相対的な高低に応じて変動する。

【0097】

制御ロジック部109は、上記の比較信号がハイレベルとされている間、ドライバ110を介して、SWOUT端子の端子電圧(すなわち、トランジスタQ2のゲート電圧)をハイレベルに保持する。従って、トランジスタQ2はオン状態とされる。一方、比較信号がローレベルとされている間には、SWOUT端子の端子電圧をローレベルに保持する。従って、トランジスタQ2はオフ状態とされる。

【0098】

このように、昇圧DC/DCコントローラブロックは、LED端子電圧V1〜V4(延いては出力電圧VOUT)のモニタ結果に基づいて、トランジスタQ2の駆動制御を行う構成とされている。従って、出力電圧VOUTを所望値に維持することが可能となる。

【0099】

次に、負荷であるLED列の直列数に関して説明する。

【0100】

上述した通り、半導体装置10の昇圧DC/DCコントローラブロックは、LED列のカソード電圧(すなわちLED端子電圧V1〜V4)を検出し、これがLED制御電圧VLED(=0.8[V](Typ.))となるように、LED列のアノードに印加される出力電圧VOUTを制御する。

【0101】

上記の昇圧動作は、PWM信号がハイレベルであり、LED列に対して出力電流ILEDが流されているときにのみ行われる。また、複数のLED列を駆動しているときには、LEDの順方向降下電圧VFが最も大きい列のLED端子電圧(言い換えれば、LED端子電圧の最低値)がLED制御電圧VLEDと一致するように制御される。従って、他の列のLED端子電圧は、順方向降下電圧VFのバラツキ分だけ高い電圧となる。

【0102】

なお、順方向降下電圧VFのバラツキ許容電圧Vper(=3.7[V](Typ.))については、ショート検出電圧VDSHT(=4.5[V](Typ.))、及び、LED制御電圧VLED(=0.8[V](Typ.))に基づいて、次の(2)式で設定される。

【0103】

【数2】

【0104】

また、オープン/ショート検出部118におけるオープン検出の際には、OVP部105における過電圧検出基準電圧VDOVP(=2.0[V](Typ.))の85%がトリガ電圧(オープン検出電圧VDOP2(=1.7[V](Typ.))として設定される(図7及び図10を参照)。これを、出力電圧VOUTに換算して考えると、通常動作時における出力電圧VOUTの最大値が30.6[V]=36[V]×0.85となる。従って、LEDの直列数Nは、出力電圧VOUTの最大値30.6[V]をLED1個の順方向降下電圧VFで除した値(30.6/VF)よりも小さくなるように制限が掛かる。

【0105】

次に、OVP部105に関して説明する。OVP端子(25ピン)には、出力電圧VOUTを抵抗分割して得られる分圧電圧VPが入力される。これと比較されるOVP部105の過電圧検出基準電圧VDOVPについては、先述の通り、LED列の直列数Nと順方向降下電圧VFのバラツキ許容電圧Vperに基づいて適宜決定すればよい。また、過電圧検出基準電圧VDOVPを決定する際には、オープン検出電圧VDOP2(=VDOVP×0.85)も考慮に入れて決定すべきである。なお、OVP部105が一旦保護動作を発動した後は、出力電圧VOUTが過電圧検出基準電圧VDOVPの77.5%まで低下したときに、その保護動作が解除される。

【0106】

例えば、抵抗分割回路の抵抗値をROVP1(昇圧電圧側)、ROVP2(GND側)とした場合、出力電圧VOUTが次の(3)式を満たしたときに、OVP部105の保護動作が発動することになる。

【0107】

【数3】

【0108】

なお、ROVP1=330[kΩ]、ROVP2=22[kΩ]、VDOVP=2.0[V]のとき、VOUT=32[V]以上でOVP部105の保護動作が発動する。

【0109】

次に、昇圧DC/DCコンバータの発振周波数FOSCに関して説明を行う。RT端子(26ピン)にプルダウン抵抗RTを外部接続することにより、発振器部107の内部コンデンサに対する充放電電流が決定され、三角波電圧Voscの発振周波数FOSCを設定することが可能である。RT端子に外部接続されるプルダウン抵抗RTの抵抗値については、下記の(4)式や図15を参考に設定すればよく、62.6〜523[kΩ]の範囲が望ましい。

【0110】

【数4】

【0111】

なお、上記(4)式中において、30×106[V/A/S]は、回路内部で決まる定数(±16.6%)であり、αは補正係数となっている(RT:α=50[kΩ]:0.98,60[kΩ]:0.985,70[kΩ]:0.99,80[kΩ]:0.994,90[kΩ]:0.996,100[kΩ]:1.0,150[kΩ]:1.01、200[kΩ]:1.02,300[kΩ]:1.03,400[kΩ]:1.04,500[kΩ]:1.045)。

【0112】

また、図15の周波数範囲から外れた設定では、スイッチングが停止する可能性があるため、留意が必要である。

【0113】

次に、外部同期発振周波数FSYNCに関して説明する。昇圧DC/DCコンバータに外部同期のためのクロックをSYNC端子(6ピン)に入力しているときには、途中で内部発振に切り替えるなどの動作を行わない方がよい。SYNC端子の入力論理をハイレベルからローレベルに切り替えた後、内部発振回路が動作し始めるまでには、約30[μsec](Typ.)程度の遅延時間を要する。SYNC端子に入力されたクロックは立ち上がりエッジのみ有効となっている。また、外部入力周波数が内部発振周波数に比べて遅い場合は、上記の遅延時間後、内部発振回路が動作し始めるので、そのような入力は避けるべきである。

【0114】

上記したように、本実施形態の半導体装置10では、RT端子またはSYNC端子を用いて、昇圧DC/DCコンバータブロックの発振周波数FOSCを任意にかつ高精度に可変制御することが可能である。例えば、カーナビモニタのバックライト制御手段として、本実施形態の半導体装置10を用いている場合、ラジオ受信周波数の切替制御に合わせてSYNC端子から外部同期発振周波数FSYNCを適宜設定してやれば、昇圧DC/DCコンバータブロックの発振周波数FOSCがラジオノイズの周波数帯に重なることを回避することができるので、ラジオの受信品質を損わずに、カーナビモニタのバックライト制御を行うことが可能となる。

【0115】

次に、OCP部111に関して、図16を参照しながら詳細に説明する。

【0116】

図16は、OCP部111の動作に関連する外部素子の接続関係を説明するための図である。

【0117】

図16に示すように、昇圧DC/DCコンバータ用のパワートランジスタQ2(Nチャネル電界効果トランジスタ)のソースとGNDとの間には、検出抵抗RCSが挿入されており、その接続ノードがCS端子(22ピン)に接続されている。

【0118】

また、スイッチングノイズ(スパイクノイズ)を低減するために、CS端子と検出抵抗RCSとの間には、カットオフ周波数1〜2[MHz]のローパスフィルタLPF(抵抗RLPF及びコンデンサCLPF)が挿入されている。なお、ローパスフィルタLPFの時定数が大き過ぎると、CS端子電圧の立ち上がりが遅れ、OCP部111の検出動作が遅くなるため、例えば、発振周波数FOSC=300[kHz]のとき、RLPF=100[Ω]、CLPF=1000[pF]程度が適切である。

【0119】

また、OCP部111における検出電流IOCPは、過電流保護動作電圧VDCS(コンパレータ112の非反転入力端(+)に印加される定電圧)、及び、検出抵抗RCSに基づいて、以下の(5)式で決定される。

【0120】

【数5】

【0121】

また、OCP部111は、パルスバイパルス方式であるため、昇圧DC/DCコンバータの発振周波数FOSCで決定される1周期分だけ、SWOUT端子がローレベル固定とされた後、昇圧動作が復帰される。また、検出抵抗RCSとGNDとの間は大電流ラインとなるので、基板設計に際してはGNDまでを独立配線とすべきである。

【0122】

次に、ソフトスタート部114に関して説明する。本実施形態の半導体装置10において、SS端子(27ピン)は不使用であり、オープンとされる。また、SS端子電圧がクランプ電圧2.5[V](Typ.)に達するまで、オープン/ショート検出部118におけるオープン/ショート検出機能はマスクされる。

【0123】

次に、外付け部品の選定について、詳細な説明を行う。

【0124】

まず、コイルL1の選定に関して、図17を参照しながら詳細に説明する。

【0125】

図17は、コイルL1の選定に関して説明するための図である。なお、図17(a)には、コイル電流ILのリップル成分ΔILが示されており、図17(b)には、DC/DCコンバータの入出力段を構成する回路が示されている。

【0126】

コイルL1のインダクタ値は、コイル電流ILのリップル成分ΔIL(コイル電流ILの最大値ILMAXと最小値ILMINとの差分)に大きく影響する。具体的には、下記の(6)式で示すように、コイルL1のインダクタ値が大きいほど、また、発振周波数FOSCが高いほど、リップル成分ΔILは減少する。

【0127】

【数6】

【0128】

また、効率ηを下記の(7a)式のように表すと、コイル電流ILの最大値ILMAXは、下記の(7b)式のようになる。

【0129】

【数7】

【0130】

コイルL1の定格電流値を超えるコイル電流ILをコイルL1に流すと、コイルL1が磁気飽和を起こして効率ηが低下する。従って、コイル電流ILの最大値ILMAXがコイルL1の定格電流値を超えないように、充分なマージンをもって選定すべきである。また、コイルL1での損失を少なくし、効率ηを向上するため、コイルL1としては、抵抗成分(直流リアクトルDCR、交流リアクトルACR)の低いものを選定すべきである。

【0131】

次に、出力コンデンサCVOUTの選定に関して、図18を参照しながら詳細な説明を行う。

【0132】

図18は、出力コンデンサCVOUTの選定に関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。

【0133】

出力コンデンサCVOUTの選定については、出力電圧VOUTの安定領域を鑑み、さらに、出力電圧のリップル成分ΔVOUTを平滑化するために必要な等価直列抵抗ESR[Equivalent Series Resistance]を考慮して、適宜決定すればよい。

【0134】

出力電圧VOUTのリップル成分ΔVOUTは、下記の(8)式のように決定される。

【0135】

【数8】

【0136】

なお、上記(8)式において、ΔILは出力電流ILのリップル成分、RESRは出力コンデンサCVOUTの等価直列抵抗ESRの抵抗値、ηは効率を各々示している。

【0137】

なお、出力コンデンサCVOUTの定格は、出力電圧VOUTに対して充分なマージンをもって選定することが望ましい。

【0138】

次に、入力コンデンサCVCCの選定に関して図19を参照しながら詳細に説明する。

【0139】

図19は、入力コンデンサCVCCの選定に関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。

【0140】

入力コンデンサCVCCの選定については、大きな過渡電圧を防止すべく、大きなリップル電流IRMSに充分対応できる容量値を有する低ESRの入力コンデンサを用いることが望ましい。

【0141】

上記のリップル電流IRMSは、下記の(9)式で与えられる。

【0142】

【数9】

【0143】

また、リップル電流IRMSは、入力に使用する電源の特性、基盤の配線パターン、及び、トランジスタQ1、Q2のゲート−ドレイン容量に大きく依存するため、使用時の温度、負荷範囲、及び、トランジスタQ1、Q2の条件において、十分な確認を行うことが望ましい。

【0144】

次に、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して図20及び図21を参照しながら詳細に説明する。

【0145】

図20は、ロードスイッチ用トランジスタQ1の選定、及び、そのソフトスタートに関して説明するための図であり、DC/DCコンバータの入出力段を構成する回路が示されている。また、図21は、トランジスタQ1のゲート・ソース間容量とソフトスタート時間との相関関係を示すグラフである。

【0146】

通常の昇圧アプリケーションの場合、電源電圧VCCの印加端から出力電圧VOUTの引出端に至る経路上にスイッチが存在しないので、出力短絡が生じた場合には、前記経路に過大な電流が流れて、コイルL1や整流用ダイオードD1が破壊に至るおそれがある。これを回避すべく、本実施形態の半導体装置10では、電源電圧VCCの印加端とコイルL1との間に、ロードスイッチ用のPチャネル型電界効果トランジスタQ1が挿入されている。なお、トランジスタQ1としては、ゲート・ソース間耐圧、ドレイン・ソース間耐圧のいずれについても、電源電圧VCCより高いものを選定すればよい。

【0147】

また、ロードスイッチのソフトスタートをかけたい場合には、トランジスタQ1のゲート・ソース間に容量を挿入すればよい。これにより、図21に示すように、挿入する容量値に応じて、ソフトスタート時間を任意に決定することができる。ただし、ソフトスタート時間は、トランジスタQ1のゲート容量によっても変化する。

【0148】

次に、スイッチング用トランジスタQ2の選定に関して説明する。絶対最大定格電流がコイルL1の定格電流以上であり、絶対最大定格電圧が出力コンデンサCVOUTの耐圧+整流用ダイオードD1の順方向降下電圧VF以上のものであれば、いかなるMOSFETを用いても問題ないが、高速スイッチングを実現するため、ゲート容量(注入電荷量)の小さいものを選定すべきであり、望ましくは、過電流保護設定値以上のものを用いるとよい。また、オン抵抗が小さいものを選ぶと高効率を得ることが可能となる。

【0149】

次に、整流用ダイオードD1の選定に関して説明する。コイルL1の定格電流以上の電流能力を持ち、かつ、出力コンデンサCVOUTの耐圧以上の逆耐圧を持つショットキーバリアダイオードであれば、いかなるものを用いてもよく、特に、順方向降下電圧VFの低いものを選定すればよい。

【0150】

次に、位相補償設定法について、詳細な説明を行う。

【0151】

まず、アプリケーションの安定条件に関して説明する。負帰還がかえるフィードバック系が安定する条件としては、ゲインが1(0[dB])であるときの位相遅れが150°以下(すなわち位相マージン30°以上)である必要がある。

【0152】

また、DC/DCコンバータアプリケーションは、発振周波数FOSCによってサンプリングされているため、全体の系におけるGBW[Gain-Band Width](ゲインと帯域幅との積)は、発振周波数FOSCの1/10以下に設定する必要がある。

【0153】

上記をまとめると、アプリケーションが目標とする特性は、ゲインが1(0[dB])であるときの位相遅れが150°以下(すなわち位相マージン30°以上)であり、そのときのGBW(すなわちゲイン0[dB]の周波数)が発振周波数FOSCの1/10以下であればよい。そのため、GBWの制限により応答性を上げるためには、発振周波数FOSCの高周波化が必要となる。

【0154】

位相補償により安定性を確保するには、LC共振によって生じる2次の位相遅れ(−180°)を2次の位相進み(すなわち位相進みを2つ入れる)により、キャンセルすればよい。なお、位相進みを与える手段としては、出力コンデンサCVOUTのESR成分によるもの(図23を参照)と、COMP端子(28ピン)に接続されるCR成分によるもの(図24を参照)が考えられる。

【0155】

DC/DCコンバータアプリケーションでは、図22に示すように、必ず出力にLC共振回路が存在する。従って、その部分での位相遅れが−180°となる。図23に示すように、出力コンデンサCVOUTがアルミ電解コンデンサなど、ESRの大きなもの(数[Ω])の場合には、+90°の位相進みが生じ、位相遅れが−90°となる。一方、セラミックコンデンサなど、低ESRの出力コンデンサCVOUTを使用する場合には、ESR成分に相当する抵抗を挿入する必要がある。

【0156】

なお、ESRによる位相特性の変化により、挿入すべき位相進みは1つとなる。また、位相進みを挿入する周波数の設定は、LC共振をキャンセルするという目的から、理想的には、LC共振周波数付近に設定することが望ましい。

【0157】

次に、半導体装置10の動作シーケンスについて、図25を参照しながら説明を行う。

【0158】

図25は、半導体装置10の動作シーケンスを示すタイミングチャートである。

【0159】

電源電圧VCCが投入された後、イネーブル信号ENがハイレベルに立ち上がると、VREG部101にて、基準電圧VREGの生成が開始される。なお、イネーブル信号ENについては、電源電圧VCCが充分に立ち上がってから、例えば、電源電圧VCCが4.5[V]以上となってから投入するとよい。

【0160】

基準電圧VREGが2.9[V]まで到達すると、UVLO部103では、減電圧状態ではないと認識され、UVLO信号がハイレベルに立ち上がる。これにより、半導体装置10の内部回路が動作を開始する。なお、UVLO信号がローレベルとされている間、スイッチ102はオフとされ、LOADSW端子(2ピン)の端子電圧は、ハイレベルに維持される。従って、ロードスイッチ用のトランジスタQ1はオフとされるので、DC/DCコンバータの昇圧動作が停止状態に維持される。一方、UVLO信号がハイレベルに立ち上がると、スイッチ102がオンとなり、LOADSW端子の端子電圧がローレベルに立ち下がる。その結果、ロードスイッチ用のトランジスタQ1がオンとなり、DC/DCコンバータの昇圧動作が可能となる。

【0161】

外部入力信号であるVDAC信号、SYNC信号、PWM信号には、安定動作のために所定の入力シーケンスが存在する。具体的に述べると、VDAC信号とSYNC信号は、イネーブルENの入力タイミングから第1所定時間TINONの経過後に入力することが望ましく、PWM信号は、EN信号の入力タイミングから第2所定時間TPWMONの経過後に入力することが望ましい。なお、第2所定時間TPWMON>第1所定時間TINONであり、第2所定時間TPWMON>500[V/A・s]×CREG[sec]である。また、VDAC信号とSYNC信号は、EN信号よりも第3所定時間TINOFFだけ先に入力を遮断することが望ましく、PWM信号は、EN信号よりも第4所定時間TPWMOFFだけ先に入力を遮断することが望ましい。なお、第4所定時間TPWMOFF>第3所定時間TINOFFである。また、本図には示されていないが、LEDEN1信号、及び、LEDEN2信号は、EN信号のハイレベル遷移前にその論理を固定しておくことが望ましい。

【0162】

OVP部105では、OVP端子(25ピン)の端子電圧が2[V]に達したときに、過電圧状態であると認識され、DC/DCコンバータの昇圧動作が停止される。その後、OVP部105では、OVP端子の端子電圧が1.6[V]まで低下したときに、過電圧状態が解消されたと認識され、DC/DCコンバータの昇圧動作が復帰される。

【0163】

OCP部111では、CS端子(22ピン)の端子電圧が0.4[V]に達したときに過電流状態であると認識され、以後、パルスバイパルス方式で、DC/DCコンバータの昇圧動作が断続的にオン/オフされる。

【0164】

TSD部104では、半導体装置10の温度が175[℃]に達したときに、異常発熱状態であると認識され、DC/DCコンバータの昇圧動作が停止される。その後、TSD部104では、半導体装置10の温度が150[℃]まで低下したときに、異常発熱状態が解消されたと認識され、DC/DCコンバータの昇圧動作が復帰される。

【0165】

なお、EN信号がローレベルに立ち下げられると、基準電圧VREGの生成が停止される。UVLO部103では、この基準電圧VREGが2.8[V]まで低下したときに、減電圧状態であると認識され、UVLO信号がローレベルに立ち下がる。これにより、半導体装置10の内部回路が動作を停止する。

【0166】

次に、本発明に係る半導体装置の第2実施形態について、詳細な説明を行う。

【0167】

図26は、本発明に係る半導体装置の第2実施形態を示すブロック図である。

【0168】

まず、本実施形態の半導体装置20の概要について述べる。

【0169】

半導体装置20は、36V高耐圧の白色LEDドライバICであり、カレントモードの昇降圧DC/DCコンバータ、並びに、4チャネル出力の定電流ドライバが1チップに集積化されている。なお、半導体装置20は、PWM[Pulse Width Modulation]制御、及び、VDAC制御のいずれによっても、白色LEDの調光制御が可能である。

【0170】

次に、本実施形態の半導体装置20の特長のうち、特に、第1実施形態と異なる点について述べる。

【0171】

第1の特長は、バッテリから直接供給される電源電圧VCCに対応すべく、昇圧DC/DCコントローラブロックに代えて、昇降圧DC/DCコントローラブロックを内蔵している点である。第2の特長は、出力コンデンサCVOUTとして、低ESRのセラミックコンデンサを用いるべく、DC/DCコンバータの制御モードを電圧モードから電流モードに変更した点である。第3の特長は、LED発光輝度のPWM調光能力を高めるべく、0.38[%]のデューティ比(オーバーシュートなし)が実現されている点である。第4の特長は、出力電流ILEDの相対ばらつき幅:±3%、絶対ばらつき幅:±5%が実現されている点である。第5の特長は、LEDのアノード及びカソードにおけるショート(主にグランドショート)を検出し、適切な保護動作を行う保護機能部(SCP[Short Circuit Protection])を内蔵している点である。

【0172】

なお、本実施形態の半導体装置20は、カーナビモニタのバックライトや、中小型LCDパネルのバックライトなどの駆動制御用として用いられる。

【0173】

上記特長を有する本実施形態の半導体装置20は、図26に示したように、基準電圧生成部201(以下、VREG部201と呼ぶ)と、減電圧保護部202(以下、UVLO部202と呼ぶ)と、温度保護部203(以下、TSD部203と呼ぶ)と、ショート保護部204(以下、SCP部204と呼ぶ)と、過電圧保護部205(以下では、OVP部205と呼ぶ)と、過電流保護部206(以下、OCP部206と呼ぶ)と、コンパレータ207と、制御ロジック部208と、入力バッファ209と、発振器部210と、スロープ電圧生成部211と、PWMコンパレータ212と、ドライバ制御部213と、ドライバ214と、Nチャネル型電界効果トランジスタ215と、ドライバ216と、エラーアンプ217と、ソフトスタート部218と、入力バッファ219と、電流設定部220と、定電流ドライバ221と、オープン/ショート検出部222と、入力バッファ223及び224と、を集積化して成る。

【0174】

なお、半導体装置20の上記回路部は、VREGブロック(VREG部201)と、昇降圧DC/DCコントローラブロック(OCP部206、コンパレータ207、制御ロジック部208、入力バッファ209、発振器部210、スロープ電圧生成部211、PWMコンパレータ212、ドライバ制御部213、ドライバ214、トランジスタ215、ドライバ216、エラーアンプ217、及び、ソフトスタート部218)と、カレントドライバブロック(入力バッファ219、電流設定部220、定電流ドライバ221、オープン/ショート検出部222、及び、入力バッファ223及び224)と、保護ブロック(UVLO部202、TSD部203、SCP部204、及び、OVP部205)の4ブロックに大別することができる。

【0175】

また、本実施形態の半導体装置20は、外部との電気的接続を確立する手段として、28本の外部端子(1ピン〜28ピン)を有して成る。

【0176】

図27は、半導体装置20のピン配置図であり、図28は、外部端子のピン番号、端子名、及び、機能を示した対応表である。なお、図27において、半導体装置20の中央部両サイドに設けられた幅広の端子は、サブグランドと繋がるFIN端子であり、放熱性を良くするためのものである。

【0177】

図29は、上記構成から成る半導体装置20の電気的特性を示す表である。なお、図29に示す電気的特性は、特に指定のない限り、電源電圧VCC=12[V]、周囲温度Ta=25[℃]での数値を示している。

【0178】

次に、半導体装置20各部の動作について、第1実施形態とは異なる点を中心に、詳細な説明を行う。

【0179】

まず、半導体装置20のカレントドライバブロック(入力バッファ219、電流設定部220、定電流ドライバ221、オープン/ショート検出部222、及び、入力バッファ223及び224)について、詳細な説明を行う。

【0180】

図30は、電流設定部220と定電流ドライバ221の一構成例を示す回路図である。

【0181】

図30に示すように、電流設定部220は、オペアンプA1と、直流電圧源A2と、npn型バイポーラトランジスタA3と、抵抗A4、A5と、pnp型バイポーラトランジスタA6〜A9と、抵抗A10(抵抗値R)と、を有して成る。

【0182】

オペアンプA1の第1非反転入力端(+)は、VDAC端子(8ピン)に接続されている。オペアンプA2の第2非反転入力端(+)は、直流電圧源A2の正極端に接続されており、所定の定電圧VISET(=2.0[V])が印加されている。直流電圧源A2の負極端は、接地端に接続されている。オペアンプA2の反転入力端(−)は、ISET端子(9ピン)に接続されている。トランジスタA3のベースは、オペアンプA1の出力端に接続されている。トランジスタA3のエミッタは、ISET端子に接続されている。

【0183】

抵抗A4、A5の各一端は、いずれも基準電圧VREGの印加端に接続されている。抵抗A4の他端は、トランジスタA6のエミッタに接続されている。抵抗R5の他端は、トランジスタA7のエミッタに接続されている。トランジスタA6、A7のベースは、互いに接続されており、その接続ノードは、トランジスタA7のコレクタに接続されている。トランジスタA6のコレクタは、トランジスタA8のエミッタに接続されている。トランジスタA7のコレクタは、トランジスタA9のエミッタに接続されている。トランジスタA8、A9のベースは、互いに接続されており、その接続ノードは、トランジスタA8のコレクタに接続されている。トランジスタA8のコレクタは、トランジスタA3のコレクタに接続されている。トランジスタA9のコレクタは、抵抗A10を介して、接地端に接続されている。

【0184】

一方、図30に示すように、定電流ドライバ221は、LED1端子〜LED4端子に対して各々出力電流ILEDを供給する4チャネルの出力段Ch1、Ch2、Ch3、Ch4を有して成る。なお、出力段Ch1は、オペアンプB1と、Nチャネル型電界効果トランジスタB2と、抵抗B3(抵抗値4R)と、カレントミラー回路B4(ミラー比1:1)と、抵抗B5(抵抗値4R)と、オペアンプB6と、Nチャネル型電界効果トランジスタB7と、抵抗B8(抵抗値(4/12)×R)と、カレントミラー回路B9(ミラー比1:10)と、オペアンプB10と、直流電圧源B11と、Nチャネル型電界効果トランジスタB12〜B14と、オペアンプB15と、直流電圧源B16と、Nチャネル型電界効果トランジスタB17と、Nチャネル型電界効果トランジスタB19と、Pチャネル型電界効果トランジスタB20と、抵抗B21、B22と、Nチャネル型電界効果トランジスタB23と、インバータB24と、を有して成る。

【0185】

オペアンプB1の非反転入力端(+)は、トランジスタA9と抵抗A10との接続ノードに接続されている。オペアンプB1の反転入力端(−)は、抵抗B3の一端に接続されている。抵抗B3の他端は、接地端に接続されている。トランジスタB2のドレインは、カレントミラー回路B4の入力端に接続されている。トランジスタB2のソースは、抵抗B3の一端に接続されている。トランジスタB2のゲートは、オペアンプB1の出力端に接続されている。カレントミラー回路B4の電源入力端は、基準電圧VREGの印加端に接続されている。

【0186】

オペアンプB6の非反転入力端(+)は、カレントミラー回路B4の出力端と抵抗B5の一端に各々接続されている。オペアンプB6の反転入力端は、抵抗B8の一端に接続されている。抵抗B5、B8の他端は、いずれも接地端に接続されている。トランジスタB7のドレインは、カレントミラー回路B9の入力端に接続されている。トランジスタB7のソースは、抵抗B8の一端に接続されている。トランジスタB7のゲートは、オペアンプB6の出力端に接続されている。カレントミラー回路B9の電源入力端は、基準電圧VREGの印加端に接続されている。

【0187】

オペアンプB10の非反転入力端(+)は、直流電圧源B11の正極端に接続されている。直流電圧源B11の負極端は、接地端に接続されている。トランジスタB12のドレインは、カレントミラー回路B9の出力端に接続されている。トランジスタB12のソースは、オペアンプB10の反転入力端(−)に接続されている。トランジスタB12のゲートは、オペアンプB10の出力端に接続されている。

【0188】

トランジスタB13のドレインは、トランジスタB12のソースに接続されている。トランジスタB13、B14のゲートは互いに接続されており、その接続ノードは、トランジスタB12のドレインに接続される一方、トランジスタB19のドレインにも接続されている。トランジスタB13、B14、B19のソースは、いずれも接地端に接続されている。トランジスタB19のゲートは、入力バッファ219(本図では不図示)を介してPWM端子(8ピン)に接続されている。

【0189】

オペアンプB15の非反転入力端(+)は、直流電圧源B16の正極端に接続されている。直流電圧源B16の負極端は、接地端に接続されている。トランジスタB17のドレインは、LED1端子に接続されている。トランジスタB17のソースは、オペアンプB15の反転入力端(−)に接続される一方、トランジスタB14のドレインにも接続されている。トランジスタB17のゲートは、オペアンプB15の出力端に接続されている。

【0190】

トランジスタB20のソースは、基準電圧VREGの印加端に接続されている。トランジスタB20のドレインは、カレントミラー回路B9の入力端に接続されている。抵抗B21の一端は、基準電圧VREGの印加端に接続されている。抵抗B21の他端は、トランジスタB20のゲートに接続されている。抵抗B22の一端は、トランジスタB20のゲートに接続されている。抵抗B22の他端は、トランジスタB23のドレインに接続されている。トランジスタB23のソースは、接地端に接続されている。トランジスタB23のゲートは、インバータB24の出力端に接続されている。インバータB24の入力端は、入力バッファ219(本図では不図示)を介して、PWM端子に接続されている。

【0191】

なお、定電流ドライバ221を構成するその余の出力段Ch2〜Ch4は、上記の出力段Ch1と同様の構成から成るため、詳細な説明は割愛する。

【0192】

上記構成から成る電流設定部220、及び、定電流ドライバ221において、出力電流ILEDは、次の(10)式に基づいて設定される。

【0193】

【数10】

【0194】

上記(10)式において、min{VDAC,2.0[V]}というパラメータは、VDAC端子(18ピン)に入力される制御電圧VDACと、電流設定部220の内部で予め定められた定電圧VISET(=2.0[V])のうち、いずれか低い方の電圧値である。また、RSETというパラメータは、ISET端子(19ピン)に外部接続される抵抗RSETの抵抗値であり、3000(Typ.)というパラメータは、定電流ドライバ221の回路内部で決まる定数である。

【0195】

すなわち、ISET端子(19ピン)に抵抗RSETをプルダウン接続することで、これに流れる基準電流ISETの所定ゲイン倍(例えば3000倍)が出力電流ILEDの最大値(例えば50[mA])として設定される形となっている。

【0196】

図30の例に即して具体的に述べると、定電流ドライバ221では、まず、オペアンプB1、トランジスタB2、及び、抵抗B3(抵抗値4R)を用いて、抵抗A10の端子電圧Va(=ISET×R)が電圧/電流変換され、基準電流ISETを1/4とした中間電流Ia(=1/4ISET)が生成される。次に、カレントミラー回路B4を用いて、中間電流Iaが1:1でミラーされ、中間電流Ib(=1/4ISET)が生成される。次に、抵抗B5(抵抗値4R)を用いて、中間電流Ibが電流/電圧変換され、端子電圧Vb(=ISET×R)が生成される。次に、オペアンプB6、トランジスタB7、並びに、抵抗B8(抵抗値(4/12)×R)を用いて、抵抗B5の端子電圧Vbが電圧/電流変換され、基準電流ISETを3倍した中間電流Ic(=3ISET)が生成される。次に、カレントミラー回路B9を用いて、中間電流Icが1:10でミラーされ、基準電流ISETを30倍した中間電流Id(=30ISET)が生成される。そして、最終的には、トランジスタB13、B14から成るカレントミラー回路を用いて、中間電流Idが1:100でミラーされ、基準電流ISETを3000倍とした出力電流ILED(=3000ISET)が生成される。

【0197】

なお、出力電流ILEDの精度を高めるために、最終段のカレントミラー回路については、オペアンプB10、B15を用いて、トランジスタB13、B14のドレイン・ソース間電圧が同一(例えば0.3[V])とされている。また、定電流ドライバ221は、入力される基準電流ISETに基づいて、電圧/電流変換と電流/電圧変換を繰り返しながら、所望の出力電流ILEDを生成する構成とされている。従って、上記変換処理に用いる抵抗素子(図30の例では、抵抗B3、B5、B8)が増え、延いては、そのトリミング機会が増加する。このように、トリミング可能な抵抗を数多く有する構成であれば、それらの抵抗値を微調整することにより、出力電流ILEDの相対ばらつき幅、及び、絶対ばらつき幅を低減することが可能となる。

【0198】

また、本実施形態の半導体装置20は、基準電流ISETを最終段のカレントミラー回路で一気に増幅していた第1実施形態(ISET→1/5ISET→2ISET→3300ISET)と異なり、定電流ドライバ221における出力電流ILEDの生成過程で、分散的に電流増幅を行う構成(ISET→1/4ISET→3ISET→30ISET→3000ISET)とされている。

【0199】

このような構成とすることにより、図31(a)、(b)の対比で示すように、最終段のカレントミラー回路を構成するトランジスタB13、B14のトランジスタサイズの差を減じて、素子の製造ばらつきや応力の影響を軽減することができる。すなわち、トランジスタサイズの差が大きいと、片方のトランジスタにのみ大きな応力が加わり、他方のトランジスタには応力がほとんど加わらない状況が生じるなど、半導体装置20のパッケージング時に加えられる応力の影響を受けやすいが、本実施形態の構成であれば、トランジスタサイズの差が小さくなるので、両方の素子に均等な応力が加わりやすく、応力の影響を低減することが可能となる。もちろん、トランジスタの素子設計に際しては、出力電流ILEDの実使用範囲(5[mA]以上を想定)において、トランジスタが飽和領域で動作するように、各素子のW/Lを適宜設計することが望ましい。

【0200】

また、本実施形態の半導体装置20では、図32で示すように、ペアとなる抵抗R1、R2(例えば、抵抗B3と抵抗B5、若しくは、抵抗B5と抵抗B8)が千鳥状にレイアウトされている。このような配置レイアウトを採用すれば、半導体装置20のパッケージングに際して、ペアとなる抵抗R1、R2に均等な応力が加わりやすく、応力の影響を低減することが可能となる。

【0201】

以上の通り、本実施形態の半導体装置20では、抵抗トリミング機会の増大、電流増幅能力の分散、抵抗のペア性向上など、多面的に出力電流ILEDの精度向上が図られている。このような構成とすることにより、パッケージング後における出力電流ILEDの相対ばらつき幅:±3%、絶対ばらつき幅:±5%を実現することができ、延いては、輝度ばらつきの低減やLEDの長寿命化に貢献することが可能となる。

【0202】

なお、抵抗RSETの抵抗値に関しては、先出の図11を参照しながら説明した通り、300[kΩ]以下のものを用いることが望ましい。

【0203】

ここで、上記の制御電圧VDACを用いて、出力電流ILEDの可変制御(LEDの調光制御)を行う場合、その入力範囲は、0.1〜2.0[V]の範囲とすればよい。このような制御電圧VDACを印加することにより、出力電流ILEDを最大値から低減していくことが可能となる。

【0204】