高密度プリントヘッドに関する結合シリコン構造体

【課題】半導体装置製造技術を用いて、ジェット積層体を含むプリントヘッドを形成する小型形状の高解像度装置を提供する。

【解決手段】ブランケット金属層14、ブランケット圧電素子層、及びブランケット導電層を、半導体ウエハ又は半導体ウエハの部分等の半導体基板10を覆って形成することができる。圧電素子層及びブランケット導電層をパターン化して、複数のトランデューサ圧電素子20A、20B、20Cと上部電極40とをそれぞれ提供することができ、金属層により、複数のトランデューサに関する下部電極14が形成される。その後、半導体基板をパターン化して、プリントヘッドのジェット積層体に関する本体プレートを形成することができる。

【解決手段】ブランケット金属層14、ブランケット圧電素子層、及びブランケット導電層を、半導体ウエハ又は半導体ウエハの部分等の半導体基板10を覆って形成することができる。圧電素子層及びブランケット導電層をパターン化して、複数のトランデューサ圧電素子20A、20B、20Cと上部電極40とをそれぞれ提供することができ、金属層により、複数のトランデューサに関する下部電極14が形成される。その後、半導体基板をパターン化して、プリントヘッドのジェット積層体に関する本体プレートを形成することができる。

【発明の詳細な説明】

【技術分野】

【0001】

本教示は、インクジェットプリント装置の分野に関し、詳細には、高密度圧電インクジェットのプリントヘッド及び高密度圧電インクジェットのプリントヘッドを含むプリンタに関する。

【背景技術】

【0002】

印刷業界では、ドロップ・オン・デマンド式インクジェット技術が広く使われている。ドロップ・オン・デマンド式インクジェット技術を用いるプリンタは、サーマルインクジェット技術又は圧電インクジェット技術のうちのどちらかを用いることができる。圧電インクジェットは、その製造コストがサーマルインクジェットよりも高いにかかわらず、幅の広い種類のインク使用でき、コゲーションの問題を取り除くことができるため、一般的に好まれている。

【0003】

圧電インクジェットのプリントヘッドは、一般に可撓性ダイヤフラムを含み、このダイヤフラムはステンレス銅等から製造される。圧電インクジェットのプリントヘッドは、ダイヤフラムに取り付けられる個々の圧電トランデューサのアレイ(即ち、PZT又はアクチュエータ)を含むことができる。その他の構造体としては、1つ以上のレーザによりパターン化された誘電隔離層、及び各トランデューサに電気的に接続する可撓性プリント回路(フレックス回路)、又はプリント基板(PCB)を含むことができる。プリントヘッドは本体プレート、出口プレート、及び開口プレートをさらに含むことができ、これらはそれぞれステンレス銅から製造される。さらに、プリントヘッドは、レーザによりパターンされた化接着剤層等の、種々の接着剤層を含んで、各構造体を一つに結合して、インクタンクから、プリントヘッドの中を、開口プレート内の複数のノズルまで達するインクの経路を提供することができる。

【0004】

圧電プリントヘッドを使用中、一般的には、電圧源に電気的に接続するフレックス回路の電極の電気接続を通して、電圧が圧電トランデューサに印加されて、屈曲し、または、曲がり、その結果ダイヤフラムも屈曲する。圧電トランデューサがダイヤフラムを屈曲させることで、チャンバから開口プレート内の特定なノズル(即ち、1つ以上の開口)を通って一定量のインクが噴射される。さらにこの屈曲により、メインインクタンクから開口を通ってチャンバ内に次のインクが引き込まれ、噴射されたインクと入れ替わる。

【0005】

プリントヘッドの解像度と密度が増加すると、電気の相互接続が可能な領域が減少する。ヘッド内のインク供給構造体及び電気の相互接続等のその他の機能のルーティングにより、この減少したスペースが奪い合われ、使用する種類の材料に規制が加えられる。例えば、600ドット・パー・インチ(DPI)のプリントヘッドを用いて使用する現在の技術では、各配線がフレックス回路のパッドアレイ(即ち、電極アレイ)内のパッド(即ち、電極)と電気的に接続した状態で、並列の電気配線を、このフレックス回路上に含むことができる。この並列配線は、38マイクロメータ(μm)のピッチ及び16μmの配線幅を含むことができ、これにより、各配線間で22μmのスペースを残せる。プリントヘッドの密度が増加すると、現在のフレックス回路の設計では、慣例により、より厳しい公差と、より小さな形状を有する配線及びパッドの形状が要求される。

【発明の概要】

【発明が解決しようとする課題】

【0006】

信頼性、生産性、及び拡張性が向上したプリントヘッドを製造する方法、及びその方法により製造される、プリントヘッドが望まれることになる。

【課題を解決するための手段】

【0007】

本教示の一実施形態では、複数のトランデューサを有するプリントヘッドのジェット積層体を形成する方法を含むことができ、この方法は、半導体基板を覆って金属層を形成するステップと、この金属層を覆って圧電層を形成するステップと、この圧電層を覆って導電層を形成するステップと、を含む。導電層をエッチングして、複数のトランデューサに関する、複数のトランデューサの上部電極を形成することができる。さらに、圧電層をエッチングして複数のトランデューサに関する複数の圧電素子を形成することができ、半導体基板をエッチングし、本体プレートを、プリントヘッドのジェット積層体に関する半導体基板から形成することができる。

【0008】

別の実施形態では、プリントヘッドのジェット積層体が、複数のトランデューサを含むことができ、このプリントヘッドのジェット積層体は、半導体基板の本体プレートと、半導体基板の本体プレートを覆うダイヤフラムと、このダイヤフラムを覆うパターン化圧電層と、このパターン化圧電層を覆うパターン化導電層とを含む。一実施形態では、このダイヤフラムは、複数のトランデューサの導電性下部電極を含み、パターン化圧電層は、複数のトランデューサに関する複数の圧電素子を含み、このパターン化導電層は、複数のトランデューサに関する複数の上部電極を含む。

【0009】

本教示の別の実施形態では、プリンタが、プリントヘッドのジェット積層体を有するプリントヘッドを含むことができる。プリントヘッドのジェット積層体は、複数のトランデューサと、半導体基板の本体プレートと、半導体基板の本体プレートを覆うダイヤフラムと、ダイヤフラムを覆うパターン化圧電層と、パターン化圧電層を覆うパターン化導電層と、を含むことができる。一実施形態では、このダイヤフラムは、複数のトランデューサの導電性の下部電極を含み、パターン化圧電層は、複数のトランデューサに関する複数の圧電素子を含み、パターン化導電層は、複数のトランデューサに関する複数の上部電極を含む。またプリンタは、プリントヘッドを取り囲むプリンタ収納室をさらに含むことができる。

【図面の簡単な説明】

【0010】

【図1】図1は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図2】図2は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図3】図3は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図4】図4は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図5】図5は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

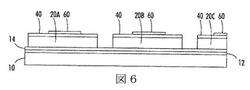

【図6】図6は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図7】図7は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図8】図8は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図9】図9は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図10】図10は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図11】図11は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図12】図12は、本教示の一実施形態による、インクジェットのプリントヘッドを含むプリンタの斜視図である。

【図13】図13は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図14】図14は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図15】図15は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図16】図16は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【発明を実施するための形態】

【0011】

図面内の詳細部のいくつかのは、構造体の正確さ、詳細さ、縮尺を厳密に維持するよりもむしろ、本教示を理解し易くするために簡略化して示されていることを理解されたい。

【0012】

本明細書で使用される「プリンタ」という用語は、他に特に規定がない限り、デジタル複写機、製本機、ファクシミリ、多機能装置、作図装置等の、あらゆる目的で印刷物を出力する機能を実行する全ての装置を包含する。

【0013】

圧電プリントヘッドの設計は、種々の故障モードが含まれることで知られている。例えば、複数の材料及び積層は、離脱、即ち層間剥離を起し易く、これにより、インク漏れ、や圧電トランデューサの電気的接続の腐食が発生する可能性がある。さらに、汚れによりノズルが詰まる可能性もあり、これが印刷品質の低下につながる。また、パターン化接着剤層と隔離層との位置ずれにより、インク経路のインク流が制限される可能性がある。プリントヘッドの耐用期間に渡る、温度サイクル、及びその他の誘発ストレスによる障害により信頼性が悪影響を受ける可能性もある。

【0014】

さらに、各圧電トランデューサへ個々の配線(即ち、リード線)を走らせるスペースが、フレックス回路又はPCB上で制限される。圧電トランデューサの数が増えて、より高い解像度のプリントヘッドが提供されると、利用可能なスペースに多くの配線を提供することがさらに困難となる。

【0015】

本教示の一実施形態では、半導体ウエハ組立体製造技術等の、半導体素子の(ミクロ電子工学の)製造技術を用いた、様々なプリントヘッドの機械的構造及び電気的構造の製造過程を含むことができる。下記により詳細に記載するが、例えば、従来のステンレス銅の本体プレートを、エッチングされた半導体基板から製造される構造体に置き換えることができる。従来のステンレス銅のダイヤフラムを、半導体基板を覆って形成される金属層に置き換えることができる。従来、フレックス回路又はPCBを用いて形成された種々のパッド及び配線を、半導体素子の金属皮膜技術を含む過程を用いて、提供することができる。一般に光学フォトリソグラフィ、ケイ素、金属、絶縁体材料のエッチング、化学気相蒸着(CVD)、スパッタリング等の、半導体素子の製造技術を使用することで、高密度プリントヘッド及び高密度プリントヘッドを用いたプリンタを提供することができる。半導体素子の処理技術を用いて形成された、これらの材料の層間剥離の可能性は従来の構造体ほど高くない。

【0016】

本教示の一実施形態を図1〜図11に示す。図1には半導体基板10が示され、この半導体基板10は、シリコンウエハ、ガリウムウエハ等の、半導体ウエハでよい。他の実施形態では、半導体基板10は、エピタキシャルシリコン層、石英、セラミック、ガラス、及びこれらの材料の組成物よい。本明細書で使用される「半導体基板」という用語には、他に特に規定がない限り、これらの材料全てを含が含まれる。半導体基板10は、半導体のウエハの一部又はその他の好適な大きさの材料でもよいことは言うまでもない。例えば、半導体ウエハから材料をダイスカットすることができる、又は形成してダイスカットする必要のない好適な大きさにすることもできる。半導体基板10は、導電構造体、誘電構造体、又はドープ領域等の、その他の様々な構造体を含むことができるがこれらは簡略化のために図示しない。

【0017】

処理の中のこの段階で、特定な設計次第では、半導体基板10を約200μmから約600μmの間の厚みを有することができる。一実施形態では、ウエハの厚みは、約500μmから約600μmの間でよい。別の実施形態では、ウエハの厚みは約200μmから約300μmの間でよく、例えば、約250μm、又は別の好適な厚みを作る。下記に記載する通り、少なくとも、半導体の層は、完成したプリントヘッドのジェット積層体の本体プレートの部分として機能する。

【0018】

図1に示す通り、材料を蒸着、即ち、シリコンウエハを酸化させることによる二酸化ケイ素の成長等の周知の技術を用いて、二酸化ケイ素又は窒化ケイ素等の、ブランケット誘電体のエッチング停止層12を、半導体基板を覆って形成することができる。エッチング停止層12をシリコンウエハ上で成長させて、又は半導体基板10上に蒸着させて、約1μmから約10μmまでの厚み、又はその他の好適な厚みを作ることができる。別の実施形態では、構造体12は半導体基板10内のドープ領域を表すことができ、エッチング停止層により、構造体に厚みが加えられないように、ホウ素注入等を用いてエッチング停止層を提供することができる。

【0019】

その後、このエッチング停止層12が、ブランケット金属層14と半導体基板10との間に配置されるように、半導体基板10の表面を覆ってブランケット金属層14をエッチング停止層12の上に形成する。例えば、スパッタリング又は化学気相蒸着(CVD)等を用いて、ブランケット金属層14を形成して、約5μmから約10μmまでの間の厚み、又は約7μmから約8μmまでの間の厚み、あるいは、その他の好適な厚みを作ることができる。一実施形態では、金属層14は、ニッケル、クロミウム、又はチタニウム、合金、及び/又は、これらの金属の組合せ、あるいは、その他の好適な金属を含むことができる。別の実施形態では、金属層14は、異なる金属からなる複数の層を含むことができる。金属層14は、その他に接着層等の1枚以上の層を含むことができ、この接着層がエッチング停止層12と物理的に接して、金属層14とエッチング停止層12との間の接着を確保する、又は、この接着層は主要な中心金属層の上部に形成され、その上の層との接着を確保する。下記に記載する通り、この金属層14は、完成したプリントヘッドのジェット積層体のダイヤフラムの部分、及び、各圧電トランデューサの下部電極(又は、底部プレート、あるいは、底部キャパシタプレート)として少なくとも機能することができる。この段階で、又は別の処理段階で、金属層14及びエッチング停止層12のうちのどちらかを、又は両方をパターン化して、完成したプリントヘッドのダイヤフラムの中のインク流に関するインクポートを形成することができる。ダイヤフラムを通してインクポートを形成するための処理段階は、特定なプリントヘッドの設計に依存する。

【0020】

図1に示す構造体と同等の構造体が形成された後、図2に示す通り、この金属層14を覆って圧電層20を形成することができる。この圧電層20は、例えば、金属層14に結合する鉛・ジルコネート・タイタネートのモノリシック層でよい。別の実施形態では、圧電層20は、例えば、ゾルゲル法によって化学沈殿された膜でよい。さらに別の実施形態では、例えば、スパッタリング過程を用いて機械的に圧電層20を堆積させることができる。また、その他の好適な処理技術を用いることもできる。一実施形態では、圧電層20を形成して約5μmから約5μmの間の厚み、又は、その他の好適な厚みを作ることができる。下記に記載する通り、この圧電層20はトランデューサの圧電層として機能する。

【0021】

その後、例えば、エッチバック、研削、又は研磨処理を用いて、半導体基板10の厚みを減らして、図3の構造体を形成することができる。半導体基板10の厚みを減らすことで、ジェット積層体を本体プレートとして用いるための好適な厚みの構造体を形成する。一実施形態では、半導体基板10の厚みを、約50μmから約125μmの間、又は約75μmから約100μmの間まで減らすことができる。プリントヘッドの製造を開始した直後に、半導体基板の厚みを減らすことにより、傷つき易いウエハへの損傷を抑えることができる。最終的なウエハの厚みは、プリントヘッドの製造工程の初期段階、又は後段階で確定させることができる。

【0022】

その後、図4に示す通り、この圧電層20を覆って導電層40を形成することができる。この導電層40は、1枚以上のニッケル、金、アルミニウム、1つ以上の合金、又はその他の好適な材料の層を含むことができる。一実施形態では、圧電層20の上に接着層(簡略化のため個々に図示せず)を形成して、導電層40の圧電層20への付着を確保することができる。一実施形態では、導電層40は約0.05μmから約2.0μmの間の厚みでよく、スパッタリング、CVD、又はその他の好適な処理を用いて形成することができる。導電層40は、完成したジェット積層体の圧電トランデューサアレイ内の各トランデューサの上部電極(又は、上部プレート又は上部キャパシタプレート)として機能することができる。図4には、この導電層40上に光学フォトリソグラフィを用いて、形成可能なパターン化フォトレジストマスク等の、パターン化マスク層42がさらに示されている。

【0023】

図4に示す構造体と同等の構造体が形成された後、エッチングを行って、導電層40及び圧電層20の露出した部分を取り除き、金属層14の上でエッチングを停止させて、図5の構造体を形成する。一実施形態では、第1のエッチングにより、導電層40を取り除くことができ、別の第2のエッチングにより、導電層40及び金属層14に対して選択された圧電層20を取り除くことができる。別の実施形態では、単一のエッチングを行って導電層40及び圧電層20の露出した部分を取り除き、上部金属層14の上でエッチングを停止させることができる。金属層14の上での停止は、時限エッチングの使用を通して、又は金属層14に対して選択された導電層40及び圧電層20を取り除く化学エッチングの使用を通して行うことができる。このエッチングで、導電層40及び圧電層20は、分離されて別々の圧電素子になる。これらの圧電素子が圧電トランデューサに関するキャパシタ誘電体として機能する。図4の導電層40により、図5の個々のトランデューサの上部電極40が提供され、一方、圧電層20により、各トランデューサに関する圧電材料が提供される。この金属層14により、完成した構造体の各トランデューサに関する下部電極を提供することができる。したがって、各トランデューサは上部電極40、誘電20、及び下部電極14を含むことができる。

【0024】

その後、パターン化マスク層42を取り除き、各トランデューサの上部電極40の上にパターン化導体層(導体)60を形成することができる。図6に示す通り、導体60は、複数の導電性バンプを含むことができ、各トランデューサの上部電極40の上に1つ以上のバンプが含まれる。導体60を、はんだ等の金属から形成することができる。一実施形態では、導体60を、トランデューサ上部電極40銀充填ペースト等の、導体ペーストとして分配することができる。処理のこの段階の間で、導体60を形成することができる、又は現在の処理段階の前後で形成することもできる。図6には、完成した2つの圧電素子20A及び20Bと、圧電素子20Cの一部の断面が示されている。各トランデューサは、下部電極14、圧電素子20、及び上部電極40を含む。トランデューサのアレイには、数百個のトランデューサ格子が含まれ得ることは言うまでもない。

【0025】

次に、図7に示す通り、例えばフォトレジスト層の光学フォトリソグラフィ、又は刷り込み等の、その他の好適な処理を用いて、半導体基板10を覆ってパターン化マスク70を形成する。図示する通り、パターン化マスク70により、圧電材料20の下に位置する半導体基板10が露出される。

【0026】

その後、マスク層70を雛形として用いて、半導体基板10のエッチングを行うことができる。化学エッチングを用いて、エッチング停止層12の材料(例えば、二酸化ケイ素、窒化ケイ素、又は基板のホウ素ドーピング)に対して選択された、半導体基板10の材料(例えばシリコン)を取り除くことができる。別の実施形態では、時限エッチングを用いることができ、この時限エッチングは、エッチング停止層12を露出させると、終了することができる。図8に示す通り、このエッチングにより、図7の半導体基板10はパターン化されて、パターン化ジェット積層体の本体プレート80を提供する。パターン化マスク70が取り除かれた後、図8に示す構造体と同等の構造体を残すことができる。

【0027】

次に、追加の処理が図8の構造体に対して行われる。この処理には、接着剤92を用いて入口/出口プレート90を本体プレート80に取り付ける処理が含まれる。さらに、接着剤98を用いて、入口/出口プレート90に、複数のノズル96を含む開口プレート94を取り付けて、図9に示す構造体と同等の構造体を作成することができる。入口/出口プレート90及び開口プレート94は、ステンレス銅、又はその他の好適な材料から形成することができる。

【0028】

次に、図10に示す通り、図9の構造体の上面にパターン化隔離層100を取り付けることができる。パターン化隔離層100は、1つ以上の誘電層を含むことができ、これらの誘電層は、例えば、レーザを用いて型抜きされて開口を提供し、これにより導体60及びトランデューサの上部電極40が露出される。図10に示す通り、フレックス回路は、複数の導電パッド102、導電配線104、及び1つ以上の誘電層106を含み、図9の構造体に物理的・電導的に取り付けられる。導電パッド102を導体60に物理的に接続させることができ、次いで、導体60を加熱及び冷却(金属又ははんだ導電性バンプの場合)して、又は、好適な技術を用いて硬化(導体ペーストの場合)して、複数のフレックス回路のパッド102と、複数のトランデューサの上部電極40と、を、導体60を用いて、電気的に接続させる。これにより、トランデューサアレイ内の複数のトランデューサは、フレックス回路の配線104を通して、個々にアドレス指定が可能となる。図10に示す通り、あらゆる付加的な処理を、完成したジェット積層体108に対して施すことができる。

【0029】

次に、ジェット積層体108の上面にマニホールド110を接続することができ、このマニホールド110を、物理的にジェット積層体108に取り付ける。マニホールド11取り付けには、接着剤等の、流体密着シール接続112を含むことができ、これにより、図11に示す、インクジェットのプリントヘッド114が形成される。インクジェットのプリントヘッド114は、マニホールド110の表面とジェット積層体108の上面により形成されたインクタンク116を含むことができ、このインクタンクが一定量のインクを蓄える。インクは、タンク116からジェット積層体108内のポート(個々には図示せず)を通って供給される。このインクポートは部分的には、フレックス回路106、隔離層100、ダイヤフラム14、及びエッチング停止層12を連続して貫通する開口により提供される。図11が簡略化された図であることは言うまでもない。実際にはプリントヘッドは、種々の構造体を含むことができ、図11には、それらの相違点は示されていない、例えば左右に対して付加構造を有するが、これらは説明を簡素化するために図示していない。

【0030】

使用中、プリントヘッド114のマニホールド110内のタンク116は、一定量のインクを含む。最初にプリントヘッドにインクで呼び水をして、ジェット積層体108内に、タンク116からのインクポート(個々には図示せず)を通るインク流を発生させる。配線104に電圧122が印加され、フレックス回路のパッドアレイ内のパッド102、導体60、圧電電極の上部プレート40に伝わり、これに反応して、それに応じた適切な時間で各圧電トランデューサが、屈曲、即ち、曲げられる。このトランデューサの屈曲により、ダイヤフラム14が曲がり、これによりジェット積層体108のチャンバ124内に圧力パルスが生成され、ノズル96からインク滴が噴射される。

【0031】

上記に記載した方法及び構造により、インクジェットプリンタに関するジェット積層体108が形成される。一実施形態では、図12に示す通り、ジェット積層体108をインクジェットのプリントヘッド114の構成部品として用いることができる。

【0032】

図12には、本教示の実施形態による、プリンタ120が示され、このプリンタ120は1つ以上のプリントヘッド114及び1つ以上のノズル96から噴射されるインク132を含む。デジタル命令に従って動作して、紙シート、プラスティック等の印刷媒体134の上に所望の画像を生成するよう、各プリントヘッド114を構成する。各プリントヘッド114は、走査動作において、印刷媒体134に対して前後に移動して、印刷画像を列ごとに生成することができる。あるいは、プリントヘッド114を固定して保持し、これに対し印刷媒体134を動かし、単一のパスにおいてプリントヘッド114と同じ幅の画像を生成することができる。プリントヘッド114の幅は、印刷媒体134の幅よりもせまくてよい、又は印刷媒体と同じ幅でよい。プリントヘッド114を含むプリンタのハードウェアは、プリンタ収納室136に収納される。別の実施形態では、プリントヘッド114が、回転ドラム又はベルト(簡略化のために図示せず)等の、中間面に印刷して、その後印刷媒体に転写することができる。

【0033】

本教示の別の実施形態を、図13〜図16に示す。この実施形態では、フレックス回路又はPCBにより一般に提供されている、いくつかの又は全ての配線及び/又はパッドの金属配線を、半導体素子製造技術を用いて置き換えることができる。一実施形態では、導体60が省かれていることを除き図9に示す構造体と同等の構造体を形成することができる。図13に示す通り、平面の誘電体層間層130を設けて、ほぼ平面の上面を提供することができる。誘電体層間層130は、例えば、ポリイミド、ポリマー、二酸化ケイ素、SU−8、ベンゾシクロブテン(BCB)、フォトレジスト等の、感光性エポキシを含むことができる。この実施形態では、図示する通り、圧電トランデューサの上部電極40を含む全ての素子構造体を覆って、誘電体層間層130を形成することができる。またこの実施形態では、隣接するトランデューサの間にも誘電体層間層130を形成する。次に、光学リソグラフィ等を用いて、パターン化マスク層132を形成して、フォトレジスト層をパターン化して、このパターン化マスク層132が開口を含み、これらの開口が各圧電トランデューサの上部プレート40の部分を露出するようにする。素子の設計によっては、マスク層132が別の開口を含んで、その他の素子構造体を露出させて、インクポートの開口(簡略化のため個々には図示せず)等の別の形状を形成することもでき、このインクポートの開口が、印刷中にインクを流すことができるダイヤフラム14を貫通する。

【0034】

図14に示す通り、エッチングを行って露出した誘電体層間層130を取り除き、次いでマスク132を取り除いて、パターン化誘電体層間層130を形成する。次に、アルミニウム、銅、アルミニウム/銅の積層等のブランケット金属層140を形成して、トランデューサの上部電極40に接触させる。図14には、簡略化のために平面的なブランケット金属層140が示されているが、ブランケット金属層140は共形でもよいことは言うまでもない。その後、光学フォトリソグラフィ等を用いて、パターン化マスク層142を形成して、フォトレジスト層をパターン化する。パターン化マスク層142を用いて、トランデューサの上部電極40との接点(即ち、パッド)、及び電圧を接点まで導く導電配線を画定することができ、それに伴って、トランデューサの上部電極も画定することができる。マスク142内の別の位置の開口を設けて、それ以前に形成された全てのポート(簡単にするために個々には図示せず)取り除くことができる。

【0035】

次に、図14の構造体をエッチングし、マスク142を取り除いて、図15の構造体を形成する。この図15には、金属層140から形成されたパッド150及び配線152が示される。

【0036】

図16は、図15の構造体の平面図であるが、半導体基板10のより広い領域が示されている。図16の構造体には、4x4のトランデューサのアレイが含まれているが、これより多くのトランデューサ、例えば1200個以上のトランデューサを有するアレイを含む格子を形成することができることは言うまでもない。図16では、配線152は、この配線152の第1の端がパッド150と、各配線の第2の端がパッド160と、電気的に接続することができる。したがって、装置が動作中に各配線152は、パッド150とパッド160の間に電圧を送ることができる。各配線152第2の端と接続するパッド160は、特定用途向け集積回路(ASIC)162等の半導体素子の下部に位置することができ、したがって、図16の構造体では見ることはできないはずであるが、説明のために図示する。ASIC162は、半導体基板10上に取り付けられたフリップチップでよく、例えば、ボールグリッドアレイ(BGA)又はバンプダイを用いて、ASIC162上の接続パッド(簡略化のために図示せず)を、各配線152の第2の端の上のパッド160に電気的に接続させる。さらに、配線、即ち、制御線164はパッド160と、パッド166と、の間に信号を通し、このパッド166は、基板10の端に沿って配置される。同様に、フレックス回路(簡略化のために図示せず)にパッド166を接続し、ドライブ基板(簡略化のために図示せず)に通すことができる。したがって、ドライブ基板、及び/又は、ASIC162により、複数の配線152及び複数のパッド150を用いて、各トランデューサを個々にアドレス指定することができる。上記に議論した通り、各パッド150は、トランデューサの上部電極40と電気的に接続する。ASIC162は、さらに接続パッドを含んでドライブ基板から、さらなる操作信号を受信し、論理機能や制御機能等の、その他の機能を提供することができる。

【0037】

図13〜図16の実施形態を用いて、超小型パッド150、160、166と、超細型配線152、164と、高解像度のプリントヘッドと、を形成することができる。半導体素子の加工技術、例えば、集積ディバイスを形成するためのフォトリソグラフィ、スパッタリング、及びCVD等の金属皮膜、エッチン技術を用いることで、超小型の形状の形成が可能となる。この実施形態では、ASIC162への制御線164を通して入力/出力機能を行うことができる。制御線164の数は、トランデューサアレイからの出力152のリード線の本数よりもはるかに少なくてもよい。20本又は24本のリード線を通してASIC162にアクセスすることができるが、トランデューサアレイからのリード線本数は、トランデューサの数と同じ、又は、ほとんど同じである。また、従来の方法を用いて形成された配線は、約38μmのピッチを有することができるが、リソグラフィを用いて形成された配線では、素子トポグラフィ、及びその他の要因により約3μmのピッチを有することができる。

【0038】

さらに、接着剤、及び、その結合/固化工程を省くことにより、生産量の向上を実現することができる。これらの構造体の層間剥離を低減、又は無くすことができる。さらに、クリーンルームでの加工では、従来のプリントヘッド加工よりも汚れが少ないため、ノズル閉塞等の故障モードを少なくすることができる。さらに、本明細書で議論した製造技術を用いることで、従来の技術を用いて製造されたプリントヘッドに比べて、温度サイクルに関連する故障が減ることが見込まれる。

【0039】

既存の方法に対して、このアプローチの優位性には、超小型形状に対する可能性が含まれる。シリコン加工を、複数の請負(半導体製造工場の)半導体ウエハ製造施設のうちのいずれかに委託することができ、これにより、部品、材料、及び組立工程を省くことで、製造工程を簡素化することができる。この他にも、さらに高い密度により可能な高解像度、及び、レーザ加工部品を無くすことにより清浄度が向上するといった恩恵がもたらされる。PZTの層間剥離、及びチャンバ間のインク漏れ等の数多くの現状の故障モードを無くすことで、生産量を向上させることができる。プリントヘッド標準化の廃止を可能にする可能性がある、繰り返しが著しく可能な半導体製造工程により、プリントヘッドの均一性を向上させることができる。さらに、材料設定を簡易化することで、インクジェットのプリントヘッド特有のインク及びその他の環境材料との互換性を向上させることができる。

【技術分野】

【0001】

本教示は、インクジェットプリント装置の分野に関し、詳細には、高密度圧電インクジェットのプリントヘッド及び高密度圧電インクジェットのプリントヘッドを含むプリンタに関する。

【背景技術】

【0002】

印刷業界では、ドロップ・オン・デマンド式インクジェット技術が広く使われている。ドロップ・オン・デマンド式インクジェット技術を用いるプリンタは、サーマルインクジェット技術又は圧電インクジェット技術のうちのどちらかを用いることができる。圧電インクジェットは、その製造コストがサーマルインクジェットよりも高いにかかわらず、幅の広い種類のインク使用でき、コゲーションの問題を取り除くことができるため、一般的に好まれている。

【0003】

圧電インクジェットのプリントヘッドは、一般に可撓性ダイヤフラムを含み、このダイヤフラムはステンレス銅等から製造される。圧電インクジェットのプリントヘッドは、ダイヤフラムに取り付けられる個々の圧電トランデューサのアレイ(即ち、PZT又はアクチュエータ)を含むことができる。その他の構造体としては、1つ以上のレーザによりパターン化された誘電隔離層、及び各トランデューサに電気的に接続する可撓性プリント回路(フレックス回路)、又はプリント基板(PCB)を含むことができる。プリントヘッドは本体プレート、出口プレート、及び開口プレートをさらに含むことができ、これらはそれぞれステンレス銅から製造される。さらに、プリントヘッドは、レーザによりパターンされた化接着剤層等の、種々の接着剤層を含んで、各構造体を一つに結合して、インクタンクから、プリントヘッドの中を、開口プレート内の複数のノズルまで達するインクの経路を提供することができる。

【0004】

圧電プリントヘッドを使用中、一般的には、電圧源に電気的に接続するフレックス回路の電極の電気接続を通して、電圧が圧電トランデューサに印加されて、屈曲し、または、曲がり、その結果ダイヤフラムも屈曲する。圧電トランデューサがダイヤフラムを屈曲させることで、チャンバから開口プレート内の特定なノズル(即ち、1つ以上の開口)を通って一定量のインクが噴射される。さらにこの屈曲により、メインインクタンクから開口を通ってチャンバ内に次のインクが引き込まれ、噴射されたインクと入れ替わる。

【0005】

プリントヘッドの解像度と密度が増加すると、電気の相互接続が可能な領域が減少する。ヘッド内のインク供給構造体及び電気の相互接続等のその他の機能のルーティングにより、この減少したスペースが奪い合われ、使用する種類の材料に規制が加えられる。例えば、600ドット・パー・インチ(DPI)のプリントヘッドを用いて使用する現在の技術では、各配線がフレックス回路のパッドアレイ(即ち、電極アレイ)内のパッド(即ち、電極)と電気的に接続した状態で、並列の電気配線を、このフレックス回路上に含むことができる。この並列配線は、38マイクロメータ(μm)のピッチ及び16μmの配線幅を含むことができ、これにより、各配線間で22μmのスペースを残せる。プリントヘッドの密度が増加すると、現在のフレックス回路の設計では、慣例により、より厳しい公差と、より小さな形状を有する配線及びパッドの形状が要求される。

【発明の概要】

【発明が解決しようとする課題】

【0006】

信頼性、生産性、及び拡張性が向上したプリントヘッドを製造する方法、及びその方法により製造される、プリントヘッドが望まれることになる。

【課題を解決するための手段】

【0007】

本教示の一実施形態では、複数のトランデューサを有するプリントヘッドのジェット積層体を形成する方法を含むことができ、この方法は、半導体基板を覆って金属層を形成するステップと、この金属層を覆って圧電層を形成するステップと、この圧電層を覆って導電層を形成するステップと、を含む。導電層をエッチングして、複数のトランデューサに関する、複数のトランデューサの上部電極を形成することができる。さらに、圧電層をエッチングして複数のトランデューサに関する複数の圧電素子を形成することができ、半導体基板をエッチングし、本体プレートを、プリントヘッドのジェット積層体に関する半導体基板から形成することができる。

【0008】

別の実施形態では、プリントヘッドのジェット積層体が、複数のトランデューサを含むことができ、このプリントヘッドのジェット積層体は、半導体基板の本体プレートと、半導体基板の本体プレートを覆うダイヤフラムと、このダイヤフラムを覆うパターン化圧電層と、このパターン化圧電層を覆うパターン化導電層とを含む。一実施形態では、このダイヤフラムは、複数のトランデューサの導電性下部電極を含み、パターン化圧電層は、複数のトランデューサに関する複数の圧電素子を含み、このパターン化導電層は、複数のトランデューサに関する複数の上部電極を含む。

【0009】

本教示の別の実施形態では、プリンタが、プリントヘッドのジェット積層体を有するプリントヘッドを含むことができる。プリントヘッドのジェット積層体は、複数のトランデューサと、半導体基板の本体プレートと、半導体基板の本体プレートを覆うダイヤフラムと、ダイヤフラムを覆うパターン化圧電層と、パターン化圧電層を覆うパターン化導電層と、を含むことができる。一実施形態では、このダイヤフラムは、複数のトランデューサの導電性の下部電極を含み、パターン化圧電層は、複数のトランデューサに関する複数の圧電素子を含み、パターン化導電層は、複数のトランデューサに関する複数の上部電極を含む。またプリンタは、プリントヘッドを取り囲むプリンタ収納室をさらに含むことができる。

【図面の簡単な説明】

【0010】

【図1】図1は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図2】図2は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図3】図3は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図4】図4は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図5】図5は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図6】図6は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図7】図7は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図8】図8は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図9】図9は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図10】図10は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図11】図11は、本教示の一実施形態による、インクジェットのプリントヘッドに関する構造体の製造過程を示す断面図である。

【図12】図12は、本教示の一実施形態による、インクジェットのプリントヘッドを含むプリンタの斜視図である。

【図13】図13は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図14】図14は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図15】図15は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【図16】図16は、本教示の別の実施形態による、インクジェットのプリントヘッドの構造体の製造過程を示す平面図である。

【発明を実施するための形態】

【0011】

図面内の詳細部のいくつかのは、構造体の正確さ、詳細さ、縮尺を厳密に維持するよりもむしろ、本教示を理解し易くするために簡略化して示されていることを理解されたい。

【0012】

本明細書で使用される「プリンタ」という用語は、他に特に規定がない限り、デジタル複写機、製本機、ファクシミリ、多機能装置、作図装置等の、あらゆる目的で印刷物を出力する機能を実行する全ての装置を包含する。

【0013】

圧電プリントヘッドの設計は、種々の故障モードが含まれることで知られている。例えば、複数の材料及び積層は、離脱、即ち層間剥離を起し易く、これにより、インク漏れ、や圧電トランデューサの電気的接続の腐食が発生する可能性がある。さらに、汚れによりノズルが詰まる可能性もあり、これが印刷品質の低下につながる。また、パターン化接着剤層と隔離層との位置ずれにより、インク経路のインク流が制限される可能性がある。プリントヘッドの耐用期間に渡る、温度サイクル、及びその他の誘発ストレスによる障害により信頼性が悪影響を受ける可能性もある。

【0014】

さらに、各圧電トランデューサへ個々の配線(即ち、リード線)を走らせるスペースが、フレックス回路又はPCB上で制限される。圧電トランデューサの数が増えて、より高い解像度のプリントヘッドが提供されると、利用可能なスペースに多くの配線を提供することがさらに困難となる。

【0015】

本教示の一実施形態では、半導体ウエハ組立体製造技術等の、半導体素子の(ミクロ電子工学の)製造技術を用いた、様々なプリントヘッドの機械的構造及び電気的構造の製造過程を含むことができる。下記により詳細に記載するが、例えば、従来のステンレス銅の本体プレートを、エッチングされた半導体基板から製造される構造体に置き換えることができる。従来のステンレス銅のダイヤフラムを、半導体基板を覆って形成される金属層に置き換えることができる。従来、フレックス回路又はPCBを用いて形成された種々のパッド及び配線を、半導体素子の金属皮膜技術を含む過程を用いて、提供することができる。一般に光学フォトリソグラフィ、ケイ素、金属、絶縁体材料のエッチング、化学気相蒸着(CVD)、スパッタリング等の、半導体素子の製造技術を使用することで、高密度プリントヘッド及び高密度プリントヘッドを用いたプリンタを提供することができる。半導体素子の処理技術を用いて形成された、これらの材料の層間剥離の可能性は従来の構造体ほど高くない。

【0016】

本教示の一実施形態を図1〜図11に示す。図1には半導体基板10が示され、この半導体基板10は、シリコンウエハ、ガリウムウエハ等の、半導体ウエハでよい。他の実施形態では、半導体基板10は、エピタキシャルシリコン層、石英、セラミック、ガラス、及びこれらの材料の組成物よい。本明細書で使用される「半導体基板」という用語には、他に特に規定がない限り、これらの材料全てを含が含まれる。半導体基板10は、半導体のウエハの一部又はその他の好適な大きさの材料でもよいことは言うまでもない。例えば、半導体ウエハから材料をダイスカットすることができる、又は形成してダイスカットする必要のない好適な大きさにすることもできる。半導体基板10は、導電構造体、誘電構造体、又はドープ領域等の、その他の様々な構造体を含むことができるがこれらは簡略化のために図示しない。

【0017】

処理の中のこの段階で、特定な設計次第では、半導体基板10を約200μmから約600μmの間の厚みを有することができる。一実施形態では、ウエハの厚みは、約500μmから約600μmの間でよい。別の実施形態では、ウエハの厚みは約200μmから約300μmの間でよく、例えば、約250μm、又は別の好適な厚みを作る。下記に記載する通り、少なくとも、半導体の層は、完成したプリントヘッドのジェット積層体の本体プレートの部分として機能する。

【0018】

図1に示す通り、材料を蒸着、即ち、シリコンウエハを酸化させることによる二酸化ケイ素の成長等の周知の技術を用いて、二酸化ケイ素又は窒化ケイ素等の、ブランケット誘電体のエッチング停止層12を、半導体基板を覆って形成することができる。エッチング停止層12をシリコンウエハ上で成長させて、又は半導体基板10上に蒸着させて、約1μmから約10μmまでの厚み、又はその他の好適な厚みを作ることができる。別の実施形態では、構造体12は半導体基板10内のドープ領域を表すことができ、エッチング停止層により、構造体に厚みが加えられないように、ホウ素注入等を用いてエッチング停止層を提供することができる。

【0019】

その後、このエッチング停止層12が、ブランケット金属層14と半導体基板10との間に配置されるように、半導体基板10の表面を覆ってブランケット金属層14をエッチング停止層12の上に形成する。例えば、スパッタリング又は化学気相蒸着(CVD)等を用いて、ブランケット金属層14を形成して、約5μmから約10μmまでの間の厚み、又は約7μmから約8μmまでの間の厚み、あるいは、その他の好適な厚みを作ることができる。一実施形態では、金属層14は、ニッケル、クロミウム、又はチタニウム、合金、及び/又は、これらの金属の組合せ、あるいは、その他の好適な金属を含むことができる。別の実施形態では、金属層14は、異なる金属からなる複数の層を含むことができる。金属層14は、その他に接着層等の1枚以上の層を含むことができ、この接着層がエッチング停止層12と物理的に接して、金属層14とエッチング停止層12との間の接着を確保する、又は、この接着層は主要な中心金属層の上部に形成され、その上の層との接着を確保する。下記に記載する通り、この金属層14は、完成したプリントヘッドのジェット積層体のダイヤフラムの部分、及び、各圧電トランデューサの下部電極(又は、底部プレート、あるいは、底部キャパシタプレート)として少なくとも機能することができる。この段階で、又は別の処理段階で、金属層14及びエッチング停止層12のうちのどちらかを、又は両方をパターン化して、完成したプリントヘッドのダイヤフラムの中のインク流に関するインクポートを形成することができる。ダイヤフラムを通してインクポートを形成するための処理段階は、特定なプリントヘッドの設計に依存する。

【0020】

図1に示す構造体と同等の構造体が形成された後、図2に示す通り、この金属層14を覆って圧電層20を形成することができる。この圧電層20は、例えば、金属層14に結合する鉛・ジルコネート・タイタネートのモノリシック層でよい。別の実施形態では、圧電層20は、例えば、ゾルゲル法によって化学沈殿された膜でよい。さらに別の実施形態では、例えば、スパッタリング過程を用いて機械的に圧電層20を堆積させることができる。また、その他の好適な処理技術を用いることもできる。一実施形態では、圧電層20を形成して約5μmから約5μmの間の厚み、又は、その他の好適な厚みを作ることができる。下記に記載する通り、この圧電層20はトランデューサの圧電層として機能する。

【0021】

その後、例えば、エッチバック、研削、又は研磨処理を用いて、半導体基板10の厚みを減らして、図3の構造体を形成することができる。半導体基板10の厚みを減らすことで、ジェット積層体を本体プレートとして用いるための好適な厚みの構造体を形成する。一実施形態では、半導体基板10の厚みを、約50μmから約125μmの間、又は約75μmから約100μmの間まで減らすことができる。プリントヘッドの製造を開始した直後に、半導体基板の厚みを減らすことにより、傷つき易いウエハへの損傷を抑えることができる。最終的なウエハの厚みは、プリントヘッドの製造工程の初期段階、又は後段階で確定させることができる。

【0022】

その後、図4に示す通り、この圧電層20を覆って導電層40を形成することができる。この導電層40は、1枚以上のニッケル、金、アルミニウム、1つ以上の合金、又はその他の好適な材料の層を含むことができる。一実施形態では、圧電層20の上に接着層(簡略化のため個々に図示せず)を形成して、導電層40の圧電層20への付着を確保することができる。一実施形態では、導電層40は約0.05μmから約2.0μmの間の厚みでよく、スパッタリング、CVD、又はその他の好適な処理を用いて形成することができる。導電層40は、完成したジェット積層体の圧電トランデューサアレイ内の各トランデューサの上部電極(又は、上部プレート又は上部キャパシタプレート)として機能することができる。図4には、この導電層40上に光学フォトリソグラフィを用いて、形成可能なパターン化フォトレジストマスク等の、パターン化マスク層42がさらに示されている。

【0023】

図4に示す構造体と同等の構造体が形成された後、エッチングを行って、導電層40及び圧電層20の露出した部分を取り除き、金属層14の上でエッチングを停止させて、図5の構造体を形成する。一実施形態では、第1のエッチングにより、導電層40を取り除くことができ、別の第2のエッチングにより、導電層40及び金属層14に対して選択された圧電層20を取り除くことができる。別の実施形態では、単一のエッチングを行って導電層40及び圧電層20の露出した部分を取り除き、上部金属層14の上でエッチングを停止させることができる。金属層14の上での停止は、時限エッチングの使用を通して、又は金属層14に対して選択された導電層40及び圧電層20を取り除く化学エッチングの使用を通して行うことができる。このエッチングで、導電層40及び圧電層20は、分離されて別々の圧電素子になる。これらの圧電素子が圧電トランデューサに関するキャパシタ誘電体として機能する。図4の導電層40により、図5の個々のトランデューサの上部電極40が提供され、一方、圧電層20により、各トランデューサに関する圧電材料が提供される。この金属層14により、完成した構造体の各トランデューサに関する下部電極を提供することができる。したがって、各トランデューサは上部電極40、誘電20、及び下部電極14を含むことができる。

【0024】

その後、パターン化マスク層42を取り除き、各トランデューサの上部電極40の上にパターン化導体層(導体)60を形成することができる。図6に示す通り、導体60は、複数の導電性バンプを含むことができ、各トランデューサの上部電極40の上に1つ以上のバンプが含まれる。導体60を、はんだ等の金属から形成することができる。一実施形態では、導体60を、トランデューサ上部電極40銀充填ペースト等の、導体ペーストとして分配することができる。処理のこの段階の間で、導体60を形成することができる、又は現在の処理段階の前後で形成することもできる。図6には、完成した2つの圧電素子20A及び20Bと、圧電素子20Cの一部の断面が示されている。各トランデューサは、下部電極14、圧電素子20、及び上部電極40を含む。トランデューサのアレイには、数百個のトランデューサ格子が含まれ得ることは言うまでもない。

【0025】

次に、図7に示す通り、例えばフォトレジスト層の光学フォトリソグラフィ、又は刷り込み等の、その他の好適な処理を用いて、半導体基板10を覆ってパターン化マスク70を形成する。図示する通り、パターン化マスク70により、圧電材料20の下に位置する半導体基板10が露出される。

【0026】

その後、マスク層70を雛形として用いて、半導体基板10のエッチングを行うことができる。化学エッチングを用いて、エッチング停止層12の材料(例えば、二酸化ケイ素、窒化ケイ素、又は基板のホウ素ドーピング)に対して選択された、半導体基板10の材料(例えばシリコン)を取り除くことができる。別の実施形態では、時限エッチングを用いることができ、この時限エッチングは、エッチング停止層12を露出させると、終了することができる。図8に示す通り、このエッチングにより、図7の半導体基板10はパターン化されて、パターン化ジェット積層体の本体プレート80を提供する。パターン化マスク70が取り除かれた後、図8に示す構造体と同等の構造体を残すことができる。

【0027】

次に、追加の処理が図8の構造体に対して行われる。この処理には、接着剤92を用いて入口/出口プレート90を本体プレート80に取り付ける処理が含まれる。さらに、接着剤98を用いて、入口/出口プレート90に、複数のノズル96を含む開口プレート94を取り付けて、図9に示す構造体と同等の構造体を作成することができる。入口/出口プレート90及び開口プレート94は、ステンレス銅、又はその他の好適な材料から形成することができる。

【0028】

次に、図10に示す通り、図9の構造体の上面にパターン化隔離層100を取り付けることができる。パターン化隔離層100は、1つ以上の誘電層を含むことができ、これらの誘電層は、例えば、レーザを用いて型抜きされて開口を提供し、これにより導体60及びトランデューサの上部電極40が露出される。図10に示す通り、フレックス回路は、複数の導電パッド102、導電配線104、及び1つ以上の誘電層106を含み、図9の構造体に物理的・電導的に取り付けられる。導電パッド102を導体60に物理的に接続させることができ、次いで、導体60を加熱及び冷却(金属又ははんだ導電性バンプの場合)して、又は、好適な技術を用いて硬化(導体ペーストの場合)して、複数のフレックス回路のパッド102と、複数のトランデューサの上部電極40と、を、導体60を用いて、電気的に接続させる。これにより、トランデューサアレイ内の複数のトランデューサは、フレックス回路の配線104を通して、個々にアドレス指定が可能となる。図10に示す通り、あらゆる付加的な処理を、完成したジェット積層体108に対して施すことができる。

【0029】

次に、ジェット積層体108の上面にマニホールド110を接続することができ、このマニホールド110を、物理的にジェット積層体108に取り付ける。マニホールド11取り付けには、接着剤等の、流体密着シール接続112を含むことができ、これにより、図11に示す、インクジェットのプリントヘッド114が形成される。インクジェットのプリントヘッド114は、マニホールド110の表面とジェット積層体108の上面により形成されたインクタンク116を含むことができ、このインクタンクが一定量のインクを蓄える。インクは、タンク116からジェット積層体108内のポート(個々には図示せず)を通って供給される。このインクポートは部分的には、フレックス回路106、隔離層100、ダイヤフラム14、及びエッチング停止層12を連続して貫通する開口により提供される。図11が簡略化された図であることは言うまでもない。実際にはプリントヘッドは、種々の構造体を含むことができ、図11には、それらの相違点は示されていない、例えば左右に対して付加構造を有するが、これらは説明を簡素化するために図示していない。

【0030】

使用中、プリントヘッド114のマニホールド110内のタンク116は、一定量のインクを含む。最初にプリントヘッドにインクで呼び水をして、ジェット積層体108内に、タンク116からのインクポート(個々には図示せず)を通るインク流を発生させる。配線104に電圧122が印加され、フレックス回路のパッドアレイ内のパッド102、導体60、圧電電極の上部プレート40に伝わり、これに反応して、それに応じた適切な時間で各圧電トランデューサが、屈曲、即ち、曲げられる。このトランデューサの屈曲により、ダイヤフラム14が曲がり、これによりジェット積層体108のチャンバ124内に圧力パルスが生成され、ノズル96からインク滴が噴射される。

【0031】

上記に記載した方法及び構造により、インクジェットプリンタに関するジェット積層体108が形成される。一実施形態では、図12に示す通り、ジェット積層体108をインクジェットのプリントヘッド114の構成部品として用いることができる。

【0032】

図12には、本教示の実施形態による、プリンタ120が示され、このプリンタ120は1つ以上のプリントヘッド114及び1つ以上のノズル96から噴射されるインク132を含む。デジタル命令に従って動作して、紙シート、プラスティック等の印刷媒体134の上に所望の画像を生成するよう、各プリントヘッド114を構成する。各プリントヘッド114は、走査動作において、印刷媒体134に対して前後に移動して、印刷画像を列ごとに生成することができる。あるいは、プリントヘッド114を固定して保持し、これに対し印刷媒体134を動かし、単一のパスにおいてプリントヘッド114と同じ幅の画像を生成することができる。プリントヘッド114の幅は、印刷媒体134の幅よりもせまくてよい、又は印刷媒体と同じ幅でよい。プリントヘッド114を含むプリンタのハードウェアは、プリンタ収納室136に収納される。別の実施形態では、プリントヘッド114が、回転ドラム又はベルト(簡略化のために図示せず)等の、中間面に印刷して、その後印刷媒体に転写することができる。

【0033】

本教示の別の実施形態を、図13〜図16に示す。この実施形態では、フレックス回路又はPCBにより一般に提供されている、いくつかの又は全ての配線及び/又はパッドの金属配線を、半導体素子製造技術を用いて置き換えることができる。一実施形態では、導体60が省かれていることを除き図9に示す構造体と同等の構造体を形成することができる。図13に示す通り、平面の誘電体層間層130を設けて、ほぼ平面の上面を提供することができる。誘電体層間層130は、例えば、ポリイミド、ポリマー、二酸化ケイ素、SU−8、ベンゾシクロブテン(BCB)、フォトレジスト等の、感光性エポキシを含むことができる。この実施形態では、図示する通り、圧電トランデューサの上部電極40を含む全ての素子構造体を覆って、誘電体層間層130を形成することができる。またこの実施形態では、隣接するトランデューサの間にも誘電体層間層130を形成する。次に、光学リソグラフィ等を用いて、パターン化マスク層132を形成して、フォトレジスト層をパターン化して、このパターン化マスク層132が開口を含み、これらの開口が各圧電トランデューサの上部プレート40の部分を露出するようにする。素子の設計によっては、マスク層132が別の開口を含んで、その他の素子構造体を露出させて、インクポートの開口(簡略化のため個々には図示せず)等の別の形状を形成することもでき、このインクポートの開口が、印刷中にインクを流すことができるダイヤフラム14を貫通する。

【0034】

図14に示す通り、エッチングを行って露出した誘電体層間層130を取り除き、次いでマスク132を取り除いて、パターン化誘電体層間層130を形成する。次に、アルミニウム、銅、アルミニウム/銅の積層等のブランケット金属層140を形成して、トランデューサの上部電極40に接触させる。図14には、簡略化のために平面的なブランケット金属層140が示されているが、ブランケット金属層140は共形でもよいことは言うまでもない。その後、光学フォトリソグラフィ等を用いて、パターン化マスク層142を形成して、フォトレジスト層をパターン化する。パターン化マスク層142を用いて、トランデューサの上部電極40との接点(即ち、パッド)、及び電圧を接点まで導く導電配線を画定することができ、それに伴って、トランデューサの上部電極も画定することができる。マスク142内の別の位置の開口を設けて、それ以前に形成された全てのポート(簡単にするために個々には図示せず)取り除くことができる。

【0035】

次に、図14の構造体をエッチングし、マスク142を取り除いて、図15の構造体を形成する。この図15には、金属層140から形成されたパッド150及び配線152が示される。

【0036】

図16は、図15の構造体の平面図であるが、半導体基板10のより広い領域が示されている。図16の構造体には、4x4のトランデューサのアレイが含まれているが、これより多くのトランデューサ、例えば1200個以上のトランデューサを有するアレイを含む格子を形成することができることは言うまでもない。図16では、配線152は、この配線152の第1の端がパッド150と、各配線の第2の端がパッド160と、電気的に接続することができる。したがって、装置が動作中に各配線152は、パッド150とパッド160の間に電圧を送ることができる。各配線152第2の端と接続するパッド160は、特定用途向け集積回路(ASIC)162等の半導体素子の下部に位置することができ、したがって、図16の構造体では見ることはできないはずであるが、説明のために図示する。ASIC162は、半導体基板10上に取り付けられたフリップチップでよく、例えば、ボールグリッドアレイ(BGA)又はバンプダイを用いて、ASIC162上の接続パッド(簡略化のために図示せず)を、各配線152の第2の端の上のパッド160に電気的に接続させる。さらに、配線、即ち、制御線164はパッド160と、パッド166と、の間に信号を通し、このパッド166は、基板10の端に沿って配置される。同様に、フレックス回路(簡略化のために図示せず)にパッド166を接続し、ドライブ基板(簡略化のために図示せず)に通すことができる。したがって、ドライブ基板、及び/又は、ASIC162により、複数の配線152及び複数のパッド150を用いて、各トランデューサを個々にアドレス指定することができる。上記に議論した通り、各パッド150は、トランデューサの上部電極40と電気的に接続する。ASIC162は、さらに接続パッドを含んでドライブ基板から、さらなる操作信号を受信し、論理機能や制御機能等の、その他の機能を提供することができる。

【0037】

図13〜図16の実施形態を用いて、超小型パッド150、160、166と、超細型配線152、164と、高解像度のプリントヘッドと、を形成することができる。半導体素子の加工技術、例えば、集積ディバイスを形成するためのフォトリソグラフィ、スパッタリング、及びCVD等の金属皮膜、エッチン技術を用いることで、超小型の形状の形成が可能となる。この実施形態では、ASIC162への制御線164を通して入力/出力機能を行うことができる。制御線164の数は、トランデューサアレイからの出力152のリード線の本数よりもはるかに少なくてもよい。20本又は24本のリード線を通してASIC162にアクセスすることができるが、トランデューサアレイからのリード線本数は、トランデューサの数と同じ、又は、ほとんど同じである。また、従来の方法を用いて形成された配線は、約38μmのピッチを有することができるが、リソグラフィを用いて形成された配線では、素子トポグラフィ、及びその他の要因により約3μmのピッチを有することができる。

【0038】

さらに、接着剤、及び、その結合/固化工程を省くことにより、生産量の向上を実現することができる。これらの構造体の層間剥離を低減、又は無くすことができる。さらに、クリーンルームでの加工では、従来のプリントヘッド加工よりも汚れが少ないため、ノズル閉塞等の故障モードを少なくすることができる。さらに、本明細書で議論した製造技術を用いることで、従来の技術を用いて製造されたプリントヘッドに比べて、温度サイクルに関連する故障が減ることが見込まれる。

【0039】

既存の方法に対して、このアプローチの優位性には、超小型形状に対する可能性が含まれる。シリコン加工を、複数の請負(半導体製造工場の)半導体ウエハ製造施設のうちのいずれかに委託することができ、これにより、部品、材料、及び組立工程を省くことで、製造工程を簡素化することができる。この他にも、さらに高い密度により可能な高解像度、及び、レーザ加工部品を無くすことにより清浄度が向上するといった恩恵がもたらされる。PZTの層間剥離、及びチャンバ間のインク漏れ等の数多くの現状の故障モードを無くすことで、生産量を向上させることができる。プリントヘッド標準化の廃止を可能にする可能性がある、繰り返しが著しく可能な半導体製造工程により、プリントヘッドの均一性を向上させることができる。さらに、材料設定を簡易化することで、インクジェットのプリントヘッド特有のインク及びその他の環境材料との互換性を向上させることができる。

【特許請求の範囲】

【請求項1】

複数のトランデューサを含むプリントヘッドのジェット積層体を形成する方法であって、

半導体基板を覆って金属層を形成するステップと、

前記金属層を覆って圧電層を形成するステップと、

前記圧電層を覆って導電層を形成するステップと、

前記導電層をエッチングして、前記複数のトランデューサに関する複数のトランデューサの上部電極を形成するステップと、

前記圧電層をエッチングして、前記複数のトランデューサに関する複数の圧電素子を形成するステップと、

前記半導体基板をエッチングして、前記プリントヘッドのジェット積層体に関する本体プレートを前記半導体基板から形成するステップと、を含む方法。

【請求項2】

前記半導体基板を覆って前記金属層を形成して、前記複数のトランデューサに関する底部プレート、及び前記プリントヘッドのジェット積層体に関するダイヤフラムを形成するステップをさらに含む請求項1に記載の方法。

【請求項3】

前記半導体基板を覆ってエッチング停止層を形成するステップと、

前記エッチング停止層を覆って前記金属層を形成するステップと、

前記半導体基板をエッチングする間、エッチ停止として前記エッチング停止層を用いるステップと、をさらに含む請求項1に記載の方法。

【請求項4】

前記半導体基板を覆ってパターン化フォトレジスト層を形成するステップと、

前記パターン化フォトレジスト層を用いて、前記半導体基板をエッチングして、前記半導体基板をパターン化して、前記プリントヘッドのジェット積層体に関する前記本体プレートを形成するステップと、をさらに含む請求項1に記載の方法。

【請求項5】

前記複数のトランデューサの上部電極を覆って、且つ、隣接するトランデューサ間に、誘電体層間層を形成するステップと、

前記誘電体層間層をエッチングして、前記複数のトランデューサの上部電極を露出させるステップと、

前記誘電体層間層を覆ってブランケット金属層を形成して、前記複数のトランデューサの上部電極と電気的に接触させるステップと、

リソグラフィを用いて、前記ブランケット金属層を覆ってパターン化マスクを形成するステップと、

前記ブランケット金属層をエッチングして、前記複数のトランデューサと電気的に接続する複数の配線及び複数のパッドを形成し、前記各トランデューサは、前記複数の配線及び前記複数のパッドを通して個々にアドレス指定可能である、ステップと、をさらに含む請求項4に記載の方法。

【請求項6】

複数のトランデューサを含むプリントヘッドのジェット積層体であって、

半導体基板の本体プレートと、

前記半導体基板本体プレートの下に位置するダイヤフラムと、

前記ダイヤフラムの下に位置するパターン化圧電層と、

前記パターン化圧電層の下に位置するパターン化導電層と、を含み、

前記ダイヤフラムは、前記複数のトランデューサの導電性下部電極を含み、前記パターン化圧電層は、前記複数のトランデューサに関する複数の圧電素子を含み、前記パターン化導電層は、前記複数のトランデューサに関する複数の上部電極を含む、プリントヘッドのジェット積層体。

【請求項7】

1つ導電パッドが、前記複数のトランデューサのうちの各トランデューサに電気的に接続する、複数の導電パッドと、

1つの配線が、前記複数のパッドのうちの各導電パッドに電気的に接続する、複数の導電配線と、をさらに含み、

前記複数の導電パッド、及び前記複数の導電配線は、それぞれ化学気相蒸着(CVD)法による金属、及びスパッタ法による金属のうちの一方である、請求項6に記載のプリントヘッドのジェット積層体。

【請求項8】

前記半導体基板に物理的に取り付けられ、前記複数のトランデューサに関する前記複数の上部電極と電気的に接続する、特定用途向け集積回路(ASIC)をさらに含む請求項7に記載のプリントヘッドのジェット積層体。

【請求項9】

プリンタであって、

プリントヘッドのジェット積層体を含むプリントヘッドであって、前記プリントヘッドのジェット積層体が、

複数のトランデューサと、

半導体基板の本体プレートと、

前記半導体基板本体プレートの下に位置するダイヤフラムと、

前記ダイヤフラムの下に位置するパターン化圧電層と、

前記パターン化圧電層の下に位置するパターン化導電層と、を含み、

前記ダイヤフラムは、前記複数のトランデューサの導電性下部電極を含み、前記パターン化圧電層は、前記複数のトランデューサに関する複数の圧電素子を含み、前記パターン化導電層は、前記複数のトランデューサに関する複数の上部電極を含む、プリントヘッドと、

前記プリントヘッドを収納するプリンタ収納室と、を含むプリンタ。

【請求項10】

前記ジェット積層体が、

1つ導電パッドが、前記複数のトランデューサのうちの各トランデューサに電気的に接続する、複数の導電パッドと、

1つの配線が、前記複数のパッドのうちの各導電パッドに電気的に接続する、複数の導電配線と、をさらに含み、

前記複数の導電パッド、及び前記複数の導電配線は、それぞれ化学気相蒸着(CVD)法による金属、及びスパッタ法による金属のうちの一方である、請求項9に記載のプリンタ。

【請求項1】

複数のトランデューサを含むプリントヘッドのジェット積層体を形成する方法であって、

半導体基板を覆って金属層を形成するステップと、

前記金属層を覆って圧電層を形成するステップと、

前記圧電層を覆って導電層を形成するステップと、

前記導電層をエッチングして、前記複数のトランデューサに関する複数のトランデューサの上部電極を形成するステップと、

前記圧電層をエッチングして、前記複数のトランデューサに関する複数の圧電素子を形成するステップと、

前記半導体基板をエッチングして、前記プリントヘッドのジェット積層体に関する本体プレートを前記半導体基板から形成するステップと、を含む方法。

【請求項2】

前記半導体基板を覆って前記金属層を形成して、前記複数のトランデューサに関する底部プレート、及び前記プリントヘッドのジェット積層体に関するダイヤフラムを形成するステップをさらに含む請求項1に記載の方法。

【請求項3】

前記半導体基板を覆ってエッチング停止層を形成するステップと、

前記エッチング停止層を覆って前記金属層を形成するステップと、

前記半導体基板をエッチングする間、エッチ停止として前記エッチング停止層を用いるステップと、をさらに含む請求項1に記載の方法。

【請求項4】

前記半導体基板を覆ってパターン化フォトレジスト層を形成するステップと、

前記パターン化フォトレジスト層を用いて、前記半導体基板をエッチングして、前記半導体基板をパターン化して、前記プリントヘッドのジェット積層体に関する前記本体プレートを形成するステップと、をさらに含む請求項1に記載の方法。

【請求項5】

前記複数のトランデューサの上部電極を覆って、且つ、隣接するトランデューサ間に、誘電体層間層を形成するステップと、

前記誘電体層間層をエッチングして、前記複数のトランデューサの上部電極を露出させるステップと、

前記誘電体層間層を覆ってブランケット金属層を形成して、前記複数のトランデューサの上部電極と電気的に接触させるステップと、

リソグラフィを用いて、前記ブランケット金属層を覆ってパターン化マスクを形成するステップと、

前記ブランケット金属層をエッチングして、前記複数のトランデューサと電気的に接続する複数の配線及び複数のパッドを形成し、前記各トランデューサは、前記複数の配線及び前記複数のパッドを通して個々にアドレス指定可能である、ステップと、をさらに含む請求項4に記載の方法。

【請求項6】

複数のトランデューサを含むプリントヘッドのジェット積層体であって、

半導体基板の本体プレートと、

前記半導体基板本体プレートの下に位置するダイヤフラムと、

前記ダイヤフラムの下に位置するパターン化圧電層と、

前記パターン化圧電層の下に位置するパターン化導電層と、を含み、

前記ダイヤフラムは、前記複数のトランデューサの導電性下部電極を含み、前記パターン化圧電層は、前記複数のトランデューサに関する複数の圧電素子を含み、前記パターン化導電層は、前記複数のトランデューサに関する複数の上部電極を含む、プリントヘッドのジェット積層体。

【請求項7】

1つ導電パッドが、前記複数のトランデューサのうちの各トランデューサに電気的に接続する、複数の導電パッドと、

1つの配線が、前記複数のパッドのうちの各導電パッドに電気的に接続する、複数の導電配線と、をさらに含み、

前記複数の導電パッド、及び前記複数の導電配線は、それぞれ化学気相蒸着(CVD)法による金属、及びスパッタ法による金属のうちの一方である、請求項6に記載のプリントヘッドのジェット積層体。

【請求項8】

前記半導体基板に物理的に取り付けられ、前記複数のトランデューサに関する前記複数の上部電極と電気的に接続する、特定用途向け集積回路(ASIC)をさらに含む請求項7に記載のプリントヘッドのジェット積層体。

【請求項9】

プリンタであって、

プリントヘッドのジェット積層体を含むプリントヘッドであって、前記プリントヘッドのジェット積層体が、

複数のトランデューサと、

半導体基板の本体プレートと、

前記半導体基板本体プレートの下に位置するダイヤフラムと、

前記ダイヤフラムの下に位置するパターン化圧電層と、

前記パターン化圧電層の下に位置するパターン化導電層と、を含み、

前記ダイヤフラムは、前記複数のトランデューサの導電性下部電極を含み、前記パターン化圧電層は、前記複数のトランデューサに関する複数の圧電素子を含み、前記パターン化導電層は、前記複数のトランデューサに関する複数の上部電極を含む、プリントヘッドと、

前記プリントヘッドを収納するプリンタ収納室と、を含むプリンタ。

【請求項10】

前記ジェット積層体が、

1つ導電パッドが、前記複数のトランデューサのうちの各トランデューサに電気的に接続する、複数の導電パッドと、

1つの配線が、前記複数のパッドのうちの各導電パッドに電気的に接続する、複数の導電配線と、をさらに含み、

前記複数の導電パッド、及び前記複数の導電配線は、それぞれ化学気相蒸着(CVD)法による金属、及びスパッタ法による金属のうちの一方である、請求項9に記載のプリンタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2013−103499(P2013−103499A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2012−231290(P2012−231290)

【出願日】平成24年10月19日(2012.10.19)

【出願人】(596170170)ゼロックス コーポレイション (1,961)

【氏名又は名称原語表記】XEROX CORPORATION

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成24年10月19日(2012.10.19)

【出願人】(596170170)ゼロックス コーポレイション (1,961)

【氏名又は名称原語表記】XEROX CORPORATION

【Fターム(参考)】

[ Back to top ]