高導電性のソース/ドレイン接点を有するIII族窒化物トランジスタ及びその製造方法

【課題】III族窒化物トランジスタのドレイン及びソース接点と、下位のドレイン及びソース領域の各々との間の抵抗を低減させる。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的に半導体の分野に関し、特に、半導体トランジスタの製造の分野に関する。

【0002】

定義

本明細書において、「III族窒化物」、「III族窒化物デバイス」、「III族窒化物トランジスタ」、「III族窒化物半導体」などは、例えば、GaN、AlGaN、InN、AlN、InGaN、InAlGaN、などのような、これらに限定されない、窒素と少なくとも1つのIII族元素とを含む化合物半導体を意味する。

【背景技術】

【0003】

本発明に先立って、金属の拡散バリアがゲート、ソース、及びドレイン領域に用いられている。このような拡散バリアに用いる材料には、窒化チタンが含まれる。このような拡散バリアは、下の層に電気を伝え、且つ例えば、III族窒化物技術で電界効果トランジスタ(FET)及び/又は高電子移動度トランジスタ(HEMT)におけるゲート領域のような様々な領域を形成する場合に、その後の不所望な材料の下位領域への拡散に対してバリアを提供するといったような、有効な機能を提供するも特定の欠点がある。例えば、このような拡散バリアを追加すると、FET又はHEMTのソース/ドレイン接点とソース/ドレイン領域との間の抵抗が増大する。このような増大抵抗は、III族窒化物HEMTのようなIII族窒化物パワートランジスタにとって特に重要である、例えばトランジスタの電流搬送能力及びスイッチング速度といったようなトランジスタの性能を低下させる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、FET及び/又はHEMTにおけるゲートの一部として、トランジスタの残部に、窒化チタンのような拡散バリアを用いつつも、ドレイン及びソース接点と、それぞれの下位のドレイン及びソース領域との間の抵抗を低減させるのが有利である。

【課題を解決するための手段】

【0005】

本発明は、実質的に少なくとも1つの図に示され及び/又は、その少なくとも1つの図に関連して説明され、特許請求の範囲に記載したように、III族窒化物トランジスタにおける高導電性のソース/ドレイン接点を対象とする。

【図面の簡単な説明】

【0006】

【図1A】本発明の一実施形態に従う、高導電性のソース/ドレイン接点を製造する方法を示す例示的なフローチャートの一部である。

【図1B】本発明の一実施形態に従う、高導電性のソース/ドレイン接点を製造する方法を示す例示的なフローチャートの一部である。

【図2A】図1A及び図1Bのフローチャートに従う、最初のステップを実行することにより得られる例示的な構造を示す図である。

【図2B】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2C】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2D】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2E】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2F】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2G】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2H】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2I】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2J】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2K】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

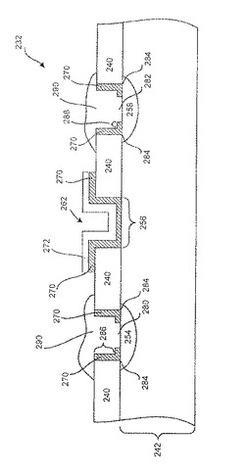

【図2L】図1A及び図1Bのフローチャートに従う、最終ステップを実行することにより得られる例示的な構造を示す図である。

【発明を実施するための形態】

【0007】

本発明はIII族窒化物トランジスタにおける高導電性のソース/ドレイン接点を対象とする。本発明を特定の実施形態について記載するが、本発明の原理は、添付の特許請求の範囲によって規定されるように、本願明細書において記載される特定の実施形態を超えて適用することができることは明らかである。また、本発明の説明において、特定の詳細は、本発明の独創的な態様を不明瞭にしないようにするために省略する。省略する詳細は、当業者の知識の範囲内である。

【0008】

本願の図面及びそれらに関連する詳細な説明は、本発明の単なる例示的な実施形態に向けられている。簡潔さを維持するために、本発明の原理を用いる本発明の他の実施形態は、本願では特に記載せず、本願の図面でも特に示していない。特に断りのない限り、図の中の類似の又は対応する要素は、類似の又は対応する参照番号によって示されることに留意されたい。

【0009】

図1A及び図1Bは、高導電性のソース/ドレイン接点並びに特別な拡散バリアで保護されるゲートを製造するための、本発明の一実施形態に従う例示的な方法を示すフローチャート100を示す。当業者にとって明らかである特定の詳細及び特徴部は、フローチャート100から省いてある。例えば、あるステップは、この分野において既知のように、1つ以上のサブステップを含むか、あるいは、特殊な器具又は材料を伴うことができる。フローチャート100に示すステップ110から132は、本発明の一実施形態を説明するのに十分であるが、本発明の他の実施形態では、フローチャート100に示したステップとは異なるステップを用いることができる。

【0010】

例えば図2Aから図2Lのような、本願の図面は、概して実寸図示したものでなく、様々な層及び領域の相対的な寸法及び相対的な厚さは、実際に図面に示されるのと異なっていることに留意すべきである。図2Aから図2Lに示す構造は、本発明の原理の特定の実装として提供するものであり、特別な実施例を用いて発明概念をより簡単に例証する目的でこのように特別に示していることにも留意すべきである。さらに、例えば、構造210から232を形成するのに用いる材料及び描写した様々な特徴部を製造するのに用いる技術のような特定の詳細は、例として提供されるものであり、これに限定されるものであると解釈すべきでないことを理解されよう。例えば、図2Aから図2Lに示す実施形態は、特定の材料、形状、配置及び/又はアーキテクチャを有する特定のソース、ゲート及びドレイン構造の製造物を示すが、本発明の他の実施形態では、異なる材料又は様々な形状、配置及び/又はアーキテクチャを有することができる。

【0011】

図1Aのステップ110及び図2Aの構造210から始めるに、フローチャート100のステップ110は、例示的なIII族窒化物半導体本体242上に延在するフィールド誘電体層240を設けるステップを含む。例示的なIII族窒化物半導体本体242は、電界効果トランジスタ(FET)及び/又は高電子移動度トランジスタ(HEMT) 及び/又は他の半導体デバイスとするか、あるいは、最終的にそのようなデバイスを形成することができる。図2Aに示すように、III族窒化物半導体本体242は、基板層244、基板層244上に延在する核生成/遷移層246、核生成/遷移層246上に延在する窒化ガリウム(GaN)層248、及び窒化ガリウム(GaN)層248上に延在するアルミニウム窒化ガリウム(AlGaN)層250を有する。GaNの薄膜層252を、AlGaN層250とフィールド誘電体層240との間に、随意配置することができる。

【0012】

フィールド誘電体層240は、例えば、窒化シリコンのような、化学量論的窒化シリコンでもそうでなくてもよい、既知のフィールド誘電材料を含むことができる。また、1つ以上の実施形態において、かようなフィールド誘電体層240の堆積は、減圧化学気相成長(LPCVD)又は他のプロセスによって形成することができる。フィールド誘電体層240は、一般的に、上方に延在する相互接続線と下方に延在するIII族窒化物半導体本体242との間の電界を低減させることになる。一実施形態において、フィールド誘電体層240は、下方に延在するAlGaN層をパッシベーションするのにも役立つ。他の実施形態では、かようなパシベーションは、随意の薄いGaN層252単独で又はフィールド誘電層240と共に生じさせることもできる。

【0013】

図2Bから図2Lを参照するに、対応する構造212から232は、構造210に、図1A及び図1Bのフローチャート100のステップ112から132をそれぞれ実行した結果を示している。例えば、構造212は、処理ステップ112の後に得られる構造を示し、構造214は、処理ステップ114の後に得られる構造を示し、以下同様である。

【0014】

図1Aのステップ112及び図2Bの構造212に示すように、フローチャート100のステップ112は、フィールド誘電体層240をエッチングして、誘電体トレンチ260、262及び264をそれぞれ形成するステップである。図2Bの構造212に示すように、誘電体トレンチ260は、一般的に、III族窒化物半導体本体242に内在するソース領域254上に延在し、誘電体トレンチ262は、III族窒化物半導体本体242に内在するゲート領域256上に延在し、誘電体トレンチ264は、III族窒化物半導体本体242に内在するドレイン領域258上に延在する。

【0015】

次に、フローチャート100のステップ114及び図2Cの構造214に示すように、ステップ114は、誘電体トレンチ260、262及び264を有するフィールド誘電体層240内に存在する新規なトポグラフィーの上にゲート誘電体270の薄膜層を形成するステップである。ゲート誘電体270は、例えば、化学量論的窒化シリコンでも非化学量論的窒化シリコンでもよい窒化シリコンのような誘電体とすることができる。ゲート誘電体270は、例えば、LPCVD堆積のような様々な堆積方法によって形成することができる。

【0016】

フローチャート100のステップ116及び図2Dの構造216に示すように、ステップ116は、図2Cの構造214の上に例えば窒化チタンのような拡散バリア材料のブランケット層272を形成するステップを含む。この後に、図1Aのフローチャート100のステップ118及び図2Eの構造218が続き、ステップ118は、図2Dの構造216の拡散バリア層272上に、例えば二酸化シリコンのようなハードマスク層274を堆積するステップを含む。

【0017】

次に、フローチャート100のステップ120及び図2Fの構造220に示すように、ステップ120は、ゲートトレンチ領域及びハードマスク層274の関連する部分の上のみにフォトレジスト層276を塗布するステップを含む。

【0018】

フローチャート100の残りのステップのための図1Bへと続いて、フローチャート100のステップ122にて説明し、図2Gの構造222に示すように、ステップ122は、図2Fに示す構造220の誘電体トレンチ260及び264からハードマスク層274を除去するステップであり、すなわち、ソース及びドレイン領域254及び258の上にあるハードマスク層274の部分を除去する。このプロセスの間、フォトレジスト層276は維持され、ゲートトレンチ領域上に延在するハードマスク層274も、他の誘電体トレンチ260及び264からはハードマスク層が除去されるにもかかわらず、維持されることに留意すべきである。これは、ソース及びドレイン領域254及び258上に延在する誘電体トレンチ260及び264上の拡散バリア層272を露出させるものの、ゲートトレンチ領域上に延在する拡散バリア層272の上は被覆したままにする働きをする。

【0019】

図2Hの構造224に示すように、フローチャート100のステップ124は、誘電体トレンチ260及び264から拡散バリア層272を除去するステップである。一実施形態においては、誘電体トレンチ260及び264から拡散バリア層272のこの部分を除去するのに湿式エッチング処理を行うのが好ましい。

【0020】

図2Iの構造226に示すように、ステップ126は、誘電体トレンチ262上を延在するフォトレジスト層276を除去して、ゲート領域上のハードマスク層274を露出させるステップである。図2Jに示す対応する得られる構造228と共にフローチャート100のステップ128にて説明するように、ステップ128は、誘電体トレンチ262上に延在するハードマスク層274を除去して、ゲート領域上の拡散バリア層272を露出させるステップである。

【0021】

図2Jに示すこの中間構造228は、本発明による高導電性のソース/ドレイン接点の1つ以上の実施形態を達成するための出発点として役立てることができる。そのようなものとして、他の処理及び/又は処理ステップを用いて、図2Jに示す中間構造を得ることもでき、これも本発明の範囲内に含まれる。

【0022】

次に、図1Bのフローチャート100のステップ130及び図2Kの構造230に示すように、誘電体トレンチ260及び/又は誘電体トレンチ264内の露出したゲート誘電体層270をエッチングするか、そうでなければ除去して、開口部280及び/又は282をそれぞれ設けて、III族窒化物半導体本体242のソース及び/又はドレイン領域254及び258に内在する下位層の半導体物質を露出させることができる。

【0023】

一実施形態において、ステップ130の後に残るゲート誘電体の部分には、ソース/ドレインのトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288が含まれる。好ましい実施形態において、ステップ130は、ゲート誘電体270の側壁ゲート誘電体286及びゲート誘電体水平突起288をとどめて、誘電体トレンチ260及び264の隅部284を覆うステップである。残存したトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288は、改良された又は「スタッフド隅部(stuffed−corner)」のソース及びドレイン接点となり、これらの接点は、ソース及びドレインの寸法を画定する領域へのその後のダメージからの保護を提供し、ソース及びドレインの配置及び機構をより一層予測通りのものとすることができる。

【0024】

従って、図2Kに示すように、また上述したように、実施形態のステップ130では、誘電体トレンチ260及び264の中心に向かって突出するゲート誘電体水平突起288が形成されることになる。ゲート誘電体水平突起288及びトレンチ側壁ゲート誘電体286の厚さは、約0.1〜0.2ミクロン(μm)とすることができる。図2Kに示す、本実施形態において、外接するトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288を残存させることにより、ゲート誘電体層270の中心部のみが、誘電体トレンチ260及び264の底部から除去され、ソース開口部280及びドレイン開口282が設けられる。

【0025】

代替の実施形態では、ステップ130によって、ゲート誘電体水平突起288、あるいは、ゲート誘電体水平突起288とトレンチ側壁ゲート誘電体286の双方を除去することができる。これらの実施形態は、図面に明示的には図示していない。

【0026】

ステップ130および構造230に従って、一旦、ゲート誘電体層270を誘電体トレンチ260及び264の底部から除去したら、図1Bのフローチャート100のステップ132に従い、図2Lの構造232に示すように、接点金属290を誘電体トレンチ260及び264内に堆積させて、ソース及びドレイン領域254及び258の頂面にオーミック金属接触を形成することができる。

【0027】

図1A及び図1Bのフローチャート100に示すステップが完了した時点で、例えばGaNトランジスタのような、特にIII族窒化物トランジスタ用の(これに限定されない)高導電性のソース/ドレイン接点が設けられた半導体構造が提供される。本発明によれば、本願明細書に記載した、新規な高導電性のソース/ドレイン接点、関連する構造及びその製造方法は、例えば、本発明の接点がかなり低減した抵抗、例えば2倍以上(例えば、0.7Ωmmから0.3Ωmmまで)を提供するという事実のような、従来技術に勝る本発明の重要な有利な点を提供する。かなり低減したソース/ドレイン接触抵抗は、次に、例えばIII族窒化物HEMT及びFETのようなパワートランジスタにおいて、特に重要であり、望ましい、より高速且つより大きな電流搬送能力をもたらす。

【0028】

本発明の上述の説明から、様々な技術を、本発明の趣旨を逸脱することなく、本発明の概念を実行するのに用いることができることは明らかである。さらに、本発明を特定の実施形態を特別に参照して説明したが、当業者は、本発明の範囲から逸脱することなく、形及び細部に変更を加えることができることを理解されよう。記載された実施形態は、あらゆる意味で例示的であり限定的でないものと理解されなければならない。本発明は、本願明細書において記載されている特定の実施形態に限定されず、本発明の範囲を逸脱することなく、多くの再構成、修正及び置換ができると理解されなければならない。

【符号の説明】

【0029】

240 フィールド誘電体層

242 III族窒化物半導体本体

254 ソース領域

256 ゲート領域

258 ドレイン領域

260、262、264 誘電体トレンチ

270 ゲート誘電体

272 拡散バリア層

274 ハードマスク層

276 フォトレジスト層

280、282 開口部

284 隅部

286 トレンチ側壁ゲート誘電体

288 ゲート誘電体水平突起

290 接点金属

【技術分野】

【0001】

本発明は、一般的に半導体の分野に関し、特に、半導体トランジスタの製造の分野に関する。

【0002】

定義

本明細書において、「III族窒化物」、「III族窒化物デバイス」、「III族窒化物トランジスタ」、「III族窒化物半導体」などは、例えば、GaN、AlGaN、InN、AlN、InGaN、InAlGaN、などのような、これらに限定されない、窒素と少なくとも1つのIII族元素とを含む化合物半導体を意味する。

【背景技術】

【0003】

本発明に先立って、金属の拡散バリアがゲート、ソース、及びドレイン領域に用いられている。このような拡散バリアに用いる材料には、窒化チタンが含まれる。このような拡散バリアは、下の層に電気を伝え、且つ例えば、III族窒化物技術で電界効果トランジスタ(FET)及び/又は高電子移動度トランジスタ(HEMT)におけるゲート領域のような様々な領域を形成する場合に、その後の不所望な材料の下位領域への拡散に対してバリアを提供するといったような、有効な機能を提供するも特定の欠点がある。例えば、このような拡散バリアを追加すると、FET又はHEMTのソース/ドレイン接点とソース/ドレイン領域との間の抵抗が増大する。このような増大抵抗は、III族窒化物HEMTのようなIII族窒化物パワートランジスタにとって特に重要である、例えばトランジスタの電流搬送能力及びスイッチング速度といったようなトランジスタの性能を低下させる。

【発明の概要】

【発明が解決しようとする課題】

【0004】

例えば、FET及び/又はHEMTにおけるゲートの一部として、トランジスタの残部に、窒化チタンのような拡散バリアを用いつつも、ドレイン及びソース接点と、それぞれの下位のドレイン及びソース領域との間の抵抗を低減させるのが有利である。

【課題を解決するための手段】

【0005】

本発明は、実質的に少なくとも1つの図に示され及び/又は、その少なくとも1つの図に関連して説明され、特許請求の範囲に記載したように、III族窒化物トランジスタにおける高導電性のソース/ドレイン接点を対象とする。

【図面の簡単な説明】

【0006】

【図1A】本発明の一実施形態に従う、高導電性のソース/ドレイン接点を製造する方法を示す例示的なフローチャートの一部である。

【図1B】本発明の一実施形態に従う、高導電性のソース/ドレイン接点を製造する方法を示す例示的なフローチャートの一部である。

【図2A】図1A及び図1Bのフローチャートに従う、最初のステップを実行することにより得られる例示的な構造を示す図である。

【図2B】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2C】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2D】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2E】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2F】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2G】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2H】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2I】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2J】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2K】図1A及び図1Bのフローチャートに従う、中間のステップを実行することにより得られる例示的な構造を示す図である。

【図2L】図1A及び図1Bのフローチャートに従う、最終ステップを実行することにより得られる例示的な構造を示す図である。

【発明を実施するための形態】

【0007】

本発明はIII族窒化物トランジスタにおける高導電性のソース/ドレイン接点を対象とする。本発明を特定の実施形態について記載するが、本発明の原理は、添付の特許請求の範囲によって規定されるように、本願明細書において記載される特定の実施形態を超えて適用することができることは明らかである。また、本発明の説明において、特定の詳細は、本発明の独創的な態様を不明瞭にしないようにするために省略する。省略する詳細は、当業者の知識の範囲内である。

【0008】

本願の図面及びそれらに関連する詳細な説明は、本発明の単なる例示的な実施形態に向けられている。簡潔さを維持するために、本発明の原理を用いる本発明の他の実施形態は、本願では特に記載せず、本願の図面でも特に示していない。特に断りのない限り、図の中の類似の又は対応する要素は、類似の又は対応する参照番号によって示されることに留意されたい。

【0009】

図1A及び図1Bは、高導電性のソース/ドレイン接点並びに特別な拡散バリアで保護されるゲートを製造するための、本発明の一実施形態に従う例示的な方法を示すフローチャート100を示す。当業者にとって明らかである特定の詳細及び特徴部は、フローチャート100から省いてある。例えば、あるステップは、この分野において既知のように、1つ以上のサブステップを含むか、あるいは、特殊な器具又は材料を伴うことができる。フローチャート100に示すステップ110から132は、本発明の一実施形態を説明するのに十分であるが、本発明の他の実施形態では、フローチャート100に示したステップとは異なるステップを用いることができる。

【0010】

例えば図2Aから図2Lのような、本願の図面は、概して実寸図示したものでなく、様々な層及び領域の相対的な寸法及び相対的な厚さは、実際に図面に示されるのと異なっていることに留意すべきである。図2Aから図2Lに示す構造は、本発明の原理の特定の実装として提供するものであり、特別な実施例を用いて発明概念をより簡単に例証する目的でこのように特別に示していることにも留意すべきである。さらに、例えば、構造210から232を形成するのに用いる材料及び描写した様々な特徴部を製造するのに用いる技術のような特定の詳細は、例として提供されるものであり、これに限定されるものであると解釈すべきでないことを理解されよう。例えば、図2Aから図2Lに示す実施形態は、特定の材料、形状、配置及び/又はアーキテクチャを有する特定のソース、ゲート及びドレイン構造の製造物を示すが、本発明の他の実施形態では、異なる材料又は様々な形状、配置及び/又はアーキテクチャを有することができる。

【0011】

図1Aのステップ110及び図2Aの構造210から始めるに、フローチャート100のステップ110は、例示的なIII族窒化物半導体本体242上に延在するフィールド誘電体層240を設けるステップを含む。例示的なIII族窒化物半導体本体242は、電界効果トランジスタ(FET)及び/又は高電子移動度トランジスタ(HEMT) 及び/又は他の半導体デバイスとするか、あるいは、最終的にそのようなデバイスを形成することができる。図2Aに示すように、III族窒化物半導体本体242は、基板層244、基板層244上に延在する核生成/遷移層246、核生成/遷移層246上に延在する窒化ガリウム(GaN)層248、及び窒化ガリウム(GaN)層248上に延在するアルミニウム窒化ガリウム(AlGaN)層250を有する。GaNの薄膜層252を、AlGaN層250とフィールド誘電体層240との間に、随意配置することができる。

【0012】

フィールド誘電体層240は、例えば、窒化シリコンのような、化学量論的窒化シリコンでもそうでなくてもよい、既知のフィールド誘電材料を含むことができる。また、1つ以上の実施形態において、かようなフィールド誘電体層240の堆積は、減圧化学気相成長(LPCVD)又は他のプロセスによって形成することができる。フィールド誘電体層240は、一般的に、上方に延在する相互接続線と下方に延在するIII族窒化物半導体本体242との間の電界を低減させることになる。一実施形態において、フィールド誘電体層240は、下方に延在するAlGaN層をパッシベーションするのにも役立つ。他の実施形態では、かようなパシベーションは、随意の薄いGaN層252単独で又はフィールド誘電層240と共に生じさせることもできる。

【0013】

図2Bから図2Lを参照するに、対応する構造212から232は、構造210に、図1A及び図1Bのフローチャート100のステップ112から132をそれぞれ実行した結果を示している。例えば、構造212は、処理ステップ112の後に得られる構造を示し、構造214は、処理ステップ114の後に得られる構造を示し、以下同様である。

【0014】

図1Aのステップ112及び図2Bの構造212に示すように、フローチャート100のステップ112は、フィールド誘電体層240をエッチングして、誘電体トレンチ260、262及び264をそれぞれ形成するステップである。図2Bの構造212に示すように、誘電体トレンチ260は、一般的に、III族窒化物半導体本体242に内在するソース領域254上に延在し、誘電体トレンチ262は、III族窒化物半導体本体242に内在するゲート領域256上に延在し、誘電体トレンチ264は、III族窒化物半導体本体242に内在するドレイン領域258上に延在する。

【0015】

次に、フローチャート100のステップ114及び図2Cの構造214に示すように、ステップ114は、誘電体トレンチ260、262及び264を有するフィールド誘電体層240内に存在する新規なトポグラフィーの上にゲート誘電体270の薄膜層を形成するステップである。ゲート誘電体270は、例えば、化学量論的窒化シリコンでも非化学量論的窒化シリコンでもよい窒化シリコンのような誘電体とすることができる。ゲート誘電体270は、例えば、LPCVD堆積のような様々な堆積方法によって形成することができる。

【0016】

フローチャート100のステップ116及び図2Dの構造216に示すように、ステップ116は、図2Cの構造214の上に例えば窒化チタンのような拡散バリア材料のブランケット層272を形成するステップを含む。この後に、図1Aのフローチャート100のステップ118及び図2Eの構造218が続き、ステップ118は、図2Dの構造216の拡散バリア層272上に、例えば二酸化シリコンのようなハードマスク層274を堆積するステップを含む。

【0017】

次に、フローチャート100のステップ120及び図2Fの構造220に示すように、ステップ120は、ゲートトレンチ領域及びハードマスク層274の関連する部分の上のみにフォトレジスト層276を塗布するステップを含む。

【0018】

フローチャート100の残りのステップのための図1Bへと続いて、フローチャート100のステップ122にて説明し、図2Gの構造222に示すように、ステップ122は、図2Fに示す構造220の誘電体トレンチ260及び264からハードマスク層274を除去するステップであり、すなわち、ソース及びドレイン領域254及び258の上にあるハードマスク層274の部分を除去する。このプロセスの間、フォトレジスト層276は維持され、ゲートトレンチ領域上に延在するハードマスク層274も、他の誘電体トレンチ260及び264からはハードマスク層が除去されるにもかかわらず、維持されることに留意すべきである。これは、ソース及びドレイン領域254及び258上に延在する誘電体トレンチ260及び264上の拡散バリア層272を露出させるものの、ゲートトレンチ領域上に延在する拡散バリア層272の上は被覆したままにする働きをする。

【0019】

図2Hの構造224に示すように、フローチャート100のステップ124は、誘電体トレンチ260及び264から拡散バリア層272を除去するステップである。一実施形態においては、誘電体トレンチ260及び264から拡散バリア層272のこの部分を除去するのに湿式エッチング処理を行うのが好ましい。

【0020】

図2Iの構造226に示すように、ステップ126は、誘電体トレンチ262上を延在するフォトレジスト層276を除去して、ゲート領域上のハードマスク層274を露出させるステップである。図2Jに示す対応する得られる構造228と共にフローチャート100のステップ128にて説明するように、ステップ128は、誘電体トレンチ262上に延在するハードマスク層274を除去して、ゲート領域上の拡散バリア層272を露出させるステップである。

【0021】

図2Jに示すこの中間構造228は、本発明による高導電性のソース/ドレイン接点の1つ以上の実施形態を達成するための出発点として役立てることができる。そのようなものとして、他の処理及び/又は処理ステップを用いて、図2Jに示す中間構造を得ることもでき、これも本発明の範囲内に含まれる。

【0022】

次に、図1Bのフローチャート100のステップ130及び図2Kの構造230に示すように、誘電体トレンチ260及び/又は誘電体トレンチ264内の露出したゲート誘電体層270をエッチングするか、そうでなければ除去して、開口部280及び/又は282をそれぞれ設けて、III族窒化物半導体本体242のソース及び/又はドレイン領域254及び258に内在する下位層の半導体物質を露出させることができる。

【0023】

一実施形態において、ステップ130の後に残るゲート誘電体の部分には、ソース/ドレインのトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288が含まれる。好ましい実施形態において、ステップ130は、ゲート誘電体270の側壁ゲート誘電体286及びゲート誘電体水平突起288をとどめて、誘電体トレンチ260及び264の隅部284を覆うステップである。残存したトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288は、改良された又は「スタッフド隅部(stuffed−corner)」のソース及びドレイン接点となり、これらの接点は、ソース及びドレインの寸法を画定する領域へのその後のダメージからの保護を提供し、ソース及びドレインの配置及び機構をより一層予測通りのものとすることができる。

【0024】

従って、図2Kに示すように、また上述したように、実施形態のステップ130では、誘電体トレンチ260及び264の中心に向かって突出するゲート誘電体水平突起288が形成されることになる。ゲート誘電体水平突起288及びトレンチ側壁ゲート誘電体286の厚さは、約0.1〜0.2ミクロン(μm)とすることができる。図2Kに示す、本実施形態において、外接するトレンチ側壁ゲート誘電体286及びゲート誘電体水平突起288を残存させることにより、ゲート誘電体層270の中心部のみが、誘電体トレンチ260及び264の底部から除去され、ソース開口部280及びドレイン開口282が設けられる。

【0025】

代替の実施形態では、ステップ130によって、ゲート誘電体水平突起288、あるいは、ゲート誘電体水平突起288とトレンチ側壁ゲート誘電体286の双方を除去することができる。これらの実施形態は、図面に明示的には図示していない。

【0026】

ステップ130および構造230に従って、一旦、ゲート誘電体層270を誘電体トレンチ260及び264の底部から除去したら、図1Bのフローチャート100のステップ132に従い、図2Lの構造232に示すように、接点金属290を誘電体トレンチ260及び264内に堆積させて、ソース及びドレイン領域254及び258の頂面にオーミック金属接触を形成することができる。

【0027】

図1A及び図1Bのフローチャート100に示すステップが完了した時点で、例えばGaNトランジスタのような、特にIII族窒化物トランジスタ用の(これに限定されない)高導電性のソース/ドレイン接点が設けられた半導体構造が提供される。本発明によれば、本願明細書に記載した、新規な高導電性のソース/ドレイン接点、関連する構造及びその製造方法は、例えば、本発明の接点がかなり低減した抵抗、例えば2倍以上(例えば、0.7Ωmmから0.3Ωmmまで)を提供するという事実のような、従来技術に勝る本発明の重要な有利な点を提供する。かなり低減したソース/ドレイン接触抵抗は、次に、例えばIII族窒化物HEMT及びFETのようなパワートランジスタにおいて、特に重要であり、望ましい、より高速且つより大きな電流搬送能力をもたらす。

【0028】

本発明の上述の説明から、様々な技術を、本発明の趣旨を逸脱することなく、本発明の概念を実行するのに用いることができることは明らかである。さらに、本発明を特定の実施形態を特別に参照して説明したが、当業者は、本発明の範囲から逸脱することなく、形及び細部に変更を加えることができることを理解されよう。記載された実施形態は、あらゆる意味で例示的であり限定的でないものと理解されなければならない。本発明は、本願明細書において記載されている特定の実施形態に限定されず、本発明の範囲を逸脱することなく、多くの再構成、修正及び置換ができると理解されなければならない。

【符号の説明】

【0029】

240 フィールド誘電体層

242 III族窒化物半導体本体

254 ソース領域

256 ゲート領域

258 ドレイン領域

260、262、264 誘電体トレンチ

270 ゲート誘電体

272 拡散バリア層

274 ハードマスク層

276 フォトレジスト層

280、282 開口部

284 隅部

286 トレンチ側壁ゲート誘電体

288 ゲート誘電体水平突起

290 接点金属

【特許請求の範囲】

【請求項1】

III族窒化物半導体本体上にIII族窒化物トランジスタを製造する方法であって、

前記III族窒化物半導体本体のゲート、ソース、及びドレイン領域上に延在するフィールド誘電体層に誘電体トレンチをエッチングするステップと、

前記ゲート、ソース、及びドレイン領域上にゲート誘電体層を形成するステップと、

前記ゲート誘電体層上にブランケット拡散バリア層を形成するステップと、

前記ソース及びドレイン領域から前記ブランケット拡散バリア層のそれぞれの部分を除去するステップと、

前記ソース及びドレイン領域から前記ゲート誘電体層を除去し、前記ソース及びドレイン領域をほぼ露出させるステップと、

前記ソース及びドレイン領域に接点金属を堆積することにより、オーミック接触を形成するステップと、

を含む、III族窒化物トランジスタの製造方法。

【請求項2】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域の部分上にゲート誘電体水平突起部を残存させるステップを含む、請求項1に記載の方法。

【請求項3】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域上に延在する前記誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させるステップを含む、請求項1に記載の方法。

【請求項4】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域の部分上にゲート誘電体水平突起部を残存させるステップと、前記ソース及びドレイン領域上に延在する前記誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させるステップとを含む、請求項1に記載の方法。

【請求項5】

前記フィールド誘電体層は、窒化シリコンである、請求項1に記載の方法。

【請求項6】

前記ゲート誘電体層は、窒化シリコンである、請求項1に記載の方法。

【請求項7】

前記拡散バリア層は、窒化チタンである、請求項1に記載の方法。

【請求項8】

前記III族窒化物半導体本体は、GaN及びAlGaNの層を備える、請求項1に記載の方法。

【請求項9】

前記III族窒化物トランジスタは、GaNトランジスタである、請求項1に記載の方法。

【請求項10】

III族窒化物半導体本体上に製造したIII族窒化物トランジスタであって、

前記III族窒化物本体上に形成されたゲート領域、ソース領域、及びドレイン領域と、

前記ゲート領域上に位置するゲート誘電体層と、

前記ソース及びドレイン領域に堆積される接点金属でオーミック接触を形成するために、前記ソース及びドレイン領域をほぼ露出させるように、前記ソース及びドレイン領域上ではない前記ゲート誘電体層上に形成した拡散バリアと、を備えることを特徴とする、III族窒化物半導体基板上に製造したIII族窒化物トランジスタ。

【請求項11】

前記ソース及びドレイン領域内に前記ゲート誘電体層の水平突起部を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項12】

前記ソース及びドレイン領域上に延在する誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項13】

前記ソース及びドレイン領域上に延在する誘電体トレンチ内にゲート誘電体水平突起部及びトレンチ側壁ゲート誘電体を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項14】

前記ゲート、ソース、及びドレイン領域上にフィールド誘電体の誘電体トレンチが延在する、請求項10に記載のIII族窒化物トランジスタ。

【請求項15】

前記フィールド誘電体層は、窒化シリコンである、請求項14に記載のIII族窒化物トランジスタ。

【請求項16】

前記ゲート誘電体層は、窒化シリコンである、請求項10に記載のIII族窒化物トランジスタ。

【請求項17】

前記拡散バリアは、窒化チタンである、請求項10に記載のIII族窒化物トランジスタ。

【請求項18】

前記III族窒化物半導体本体は、GaN及びAlGaNの層を備える、請求項10に記載のIII族窒化物トランジスタ。

【請求項1】

III族窒化物半導体本体上にIII族窒化物トランジスタを製造する方法であって、

前記III族窒化物半導体本体のゲート、ソース、及びドレイン領域上に延在するフィールド誘電体層に誘電体トレンチをエッチングするステップと、

前記ゲート、ソース、及びドレイン領域上にゲート誘電体層を形成するステップと、

前記ゲート誘電体層上にブランケット拡散バリア層を形成するステップと、

前記ソース及びドレイン領域から前記ブランケット拡散バリア層のそれぞれの部分を除去するステップと、

前記ソース及びドレイン領域から前記ゲート誘電体層を除去し、前記ソース及びドレイン領域をほぼ露出させるステップと、

前記ソース及びドレイン領域に接点金属を堆積することにより、オーミック接触を形成するステップと、

を含む、III族窒化物トランジスタの製造方法。

【請求項2】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域の部分上にゲート誘電体水平突起部を残存させるステップを含む、請求項1に記載の方法。

【請求項3】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域上に延在する前記誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させるステップを含む、請求項1に記載の方法。

【請求項4】

前記ゲート誘電体層を除去するステップは、前記ソース及びドレイン領域の部分上にゲート誘電体水平突起部を残存させるステップと、前記ソース及びドレイン領域上に延在する前記誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させるステップとを含む、請求項1に記載の方法。

【請求項5】

前記フィールド誘電体層は、窒化シリコンである、請求項1に記載の方法。

【請求項6】

前記ゲート誘電体層は、窒化シリコンである、請求項1に記載の方法。

【請求項7】

前記拡散バリア層は、窒化チタンである、請求項1に記載の方法。

【請求項8】

前記III族窒化物半導体本体は、GaN及びAlGaNの層を備える、請求項1に記載の方法。

【請求項9】

前記III族窒化物トランジスタは、GaNトランジスタである、請求項1に記載の方法。

【請求項10】

III族窒化物半導体本体上に製造したIII族窒化物トランジスタであって、

前記III族窒化物本体上に形成されたゲート領域、ソース領域、及びドレイン領域と、

前記ゲート領域上に位置するゲート誘電体層と、

前記ソース及びドレイン領域に堆積される接点金属でオーミック接触を形成するために、前記ソース及びドレイン領域をほぼ露出させるように、前記ソース及びドレイン領域上ではない前記ゲート誘電体層上に形成した拡散バリアと、を備えることを特徴とする、III族窒化物半導体基板上に製造したIII族窒化物トランジスタ。

【請求項11】

前記ソース及びドレイン領域内に前記ゲート誘電体層の水平突起部を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項12】

前記ソース及びドレイン領域上に延在する誘電体トレンチ内にトレンチ側壁ゲート誘電体層を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項13】

前記ソース及びドレイン領域上に延在する誘電体トレンチ内にゲート誘電体水平突起部及びトレンチ側壁ゲート誘電体を残存させた、請求項10に記載のIII族窒化物トランジスタ。

【請求項14】

前記ゲート、ソース、及びドレイン領域上にフィールド誘電体の誘電体トレンチが延在する、請求項10に記載のIII族窒化物トランジスタ。

【請求項15】

前記フィールド誘電体層は、窒化シリコンである、請求項14に記載のIII族窒化物トランジスタ。

【請求項16】

前記ゲート誘電体層は、窒化シリコンである、請求項10に記載のIII族窒化物トランジスタ。

【請求項17】

前記拡散バリアは、窒化チタンである、請求項10に記載のIII族窒化物トランジスタ。

【請求項18】

前記III族窒化物半導体本体は、GaN及びAlGaNの層を備える、請求項10に記載のIII族窒化物トランジスタ。

【図1A】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図2L】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図2E】

【図2F】

【図2G】

【図2H】

【図2I】

【図2J】

【図2K】

【図2L】

【公開番号】特開2011−181893(P2011−181893A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【外国語出願】

【出願番号】特願2010−269323(P2010−269323)

【出願日】平成22年12月2日(2010.12.2)

【出願人】(597161115)インターナショナル レクティフィアー コーポレイション (71)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2010−269323(P2010−269323)

【出願日】平成22年12月2日(2010.12.2)

【出願人】(597161115)インターナショナル レクティフィアー コーポレイション (71)

【Fターム(参考)】

[ Back to top ]