高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタ

【課題】 マスク工程を簡略化しながらも、レイアウト面積を縮小した高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法を提供することを目的とする。

【解決手段】 基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の一方の側に位置する基板の内部に形成されたドレイン領域と、ゲート電極の他方の側に位置する基板の内部に形成されたソース領域と、ドレイン領域上に形成され、且つ不純物拡散領域を介してドレイン領域と電気的に接続された堆積型ドレイン層と、ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、ゲート電極の前記ドレイン側の側壁に形成され、堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有する。

【解決手段】 基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の一方の側に位置する基板の内部に形成されたドレイン領域と、ゲート電極の他方の側に位置する基板の内部に形成されたソース領域と、ドレイン領域上に形成され、且つ不純物拡散領域を介してドレイン領域と電気的に接続された堆積型ドレイン層と、ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、ゲート電極の前記ドレイン側の側壁に形成され、堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタに関するものである。

【背景技術】

【0002】

高耐圧MOSトランジスタでは良好な高周波特性のみならず、ソース・ドレイン耐圧が大きいことが期待されている。

【0003】

このような高耐圧MOSトランジスタでは、ある程度以上大きな電圧がドレイン領域にかかると、ドレイン領域とチャネル領域との境界に大きな電界が発生し、この境界部分でジャンクションブレイクダウン(降伏現象)が発生する。このため、如何にしてドレイン領域とチャネル部分との境界の間に発生する電界を緩和するかが高耐圧化の課題である。

【0004】

そのような電界を緩和するために、高耐圧MOSトランジスタを形成する際、電界を緩和するための不純物濃度分布を持たせたドレイン領域をレジストによってマスクして形成するプロセスを用いた高耐圧MOSトランジスタの製造方法が提案されている(例えば、特許文献1参照)。特許文献1によれば、ドレイン領域において不純物濃度が低い領域(LDD(Lightly Doped Drain)領域)を形成するために、レジストパターンによって不純物濃度が高い領域を形成するためのイオン注入をマスクしている。

【特許文献1】特開平11−186543号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1によれば、不純物濃度分布を持つ不純物拡散層からなるドレイン領域を形成するマスク工程の際、位置合わせのための余分な領域が必要となる。また、ゲート電極、ドレイン領域の不純物濃度が低い部分、及びドレイン領域の不純物濃度が高い部分の形成位置にばらつきが発生するため、MOSトランジスタの特性のばらつきが大きくなる懸念があった。その結果、マスクの位置合わせの余裕を確保するためにゲート電極の微細化も困難になる。また、素子の微細化ができず、レイアウト面積は増加してしまう。

【0006】

本発明は、マスク工程を簡略化しながらも、レイアウト面積を縮小した高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る高耐圧MOSトランジスタの製造方法は、基板上にゲート絶縁膜を形成する工程と、前記基板の第1領域における前記ゲート絶縁膜を除去し、前記第1領域の前記基板を露出させる工程と、前記ゲート絶縁膜上にゲート電極を形成し、前記領域に堆積型ドレイン層を離間して形成する工程と、前記ゲート電極と前記堆積型ドレイン層とをマスクとして、前記基板に第1の不純物を注入する工程と、前記ゲート電極と前記堆積型ドレイン層の間隙に絶縁膜を埋め込む工程と、前記ゲート電極、前記堆積型ドレイン層、及び前記絶縁膜をマスクとして前記基板に第2不純物を注入してソース領域を形成する工程と、第1熱処理を行い、前記堆積型ドレイン層に注入された前記第1不純物又は前記第2不純物を前記基板中に拡散させ不純物拡散層を形成する工程と、を有することを特徴とする。

【0008】

本発明に係る高耐圧MOSトランジスタは、基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の一方の側に位置する前記基板の内部に形成されたドレイン領域と、前記ゲート電極の他方の側に位置する前記基板の内部に形成されたソース領域と、前記ドレイン領域上に形成され、且つ不純物拡散領域を介して前記ドレイン領域と電気的に接続された堆積型ドレイン層と、前記ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、前記ゲート電極の前記ドレイン側の側壁に形成され、前記堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有し、前記ソース領域は、前記ドレイン領域よりも深いことを特徴とする。

【発明の効果】

【0009】

本発明に係る高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタによれば、トランジスタのドレイン側には通常の高濃度の不純物による接合が存在せず、LDD領域がゲート電極と堆積型ドレイン層との間に形成されているため、ドレイン領域とチャネル領域との境界に印加される電界を緩和することができ、且つドレイン領域と基板間の耐圧を高めることができる。

【0010】

また、LDD領域がゲート電極及びプラグに対して自己整合的に形成されるので、LDD領域をマスクで形成する場合のような位置あわせが不要であり、MOSトランジスタの特性のばらつきが改善されると共に、ゲート長の微細化も可能になる。

【0011】

また、ゲートと堆積型ドレイン層の間のギャップ領域に埋め込まれる絶縁膜はシリサイドブロックとしても働くため、CMOSのロジックプロセスとの整合性がよく、追加工程無しで高耐圧トランジスタを作製でき、高耐圧トランジスタを用いたパワーアンプと制御用ロジック回路の集積化を低コストで実現できる。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施例にかかる高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタの実施例について説明する。ただし、本発明は各実施例に限定されるものではない。

(実施例1)

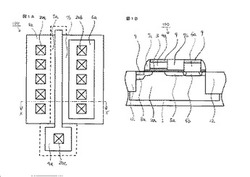

本発明の第1の実施例を、n型高耐圧MOSトランジスタ、n型高耐圧MOSトランジスタの製造方法を例に、図1A〜図1Bを用いて詳細に説明する。第1実施例にかかる高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法は、LDD領域がゲート電極及び堆積型ドレイン層に対して自己整合的に形成されることを特徴とするものである。

【0013】

図1A〜図1Bは、本発明の第1の実施例に係る半導体装置の各要部図である。

【0014】

図1Aは、本発明の第1実施例に係る高耐圧MOSトランジスタの平面図である。図1Aは高耐圧MOSトランジスタ100を示し、ゲート電極4a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、ソース領域に配線を接続するためのコンタクトプラグ20a、ドレイン領域に配線を接続するためのコンタクトプラグ20b、ゲート電極4aに配線を接続するためのコンタクトプラグ20c、からなる。なお、ゲート電極4a、堆積型ドレイン層6a、ソース領域8aの表面上には、シリサイド層9、図示しない層間絶縁膜が形成されている。

【0015】

ゲート電極4a、堆積型ドレイン層6a、ソース領域8aはポリシリコンに高濃度の導電性不純物を注入して形成されている。ゲート電極4a、堆積型ドレイン層6a、ソース領域8aにはリン(P)イオンが注入されており、リン(P)濃度が例えば、5.0×1020cm−3である。第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bは絶縁性を有し、例えば酸化シリコン(SiO2)からなる。ソース領域8aに配線を接続するためのコンタクトプラグ20a、堆積型ドレイン層に配線を接続するためのコンタクトプラグ20b、ゲート電極4aに配線を接続するためのコンタクトプラグ20cは、タングステン(W)からなり、ソース領域8a、堆積型ドレイン層6a、及びゲート電極4aと電気的に接続するものである。

【0016】

図1Aに示すように、堆積型ドレイン層6aはゲート電極4aの一方の側の基板上に形成されている。ソース領域8aはゲート電極4aの他方の側の基板内に形成されている。第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bは、ゲート電極4a、堆積型ドレイン層6aの周囲に形成されている。なお、高耐圧MOSトランジスタ100の周囲には素子分離領域12が形成されている。

【0017】

図1Bは第1の実施例の第1例に係る高耐圧MOSトランジスタの要部断面模式図である。なお、図1Bは図1Aの線X−X'における断面を示す。図1Bは高耐圧MOSトランジスタ100を示し、p型シリコン基板1、p型ウエル領域2a、ゲート絶縁膜3、ゲート電極4a、n型ドレイン領域5a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、n型ソース領域8a、コバルト(Co)シリサイド層9、素子分離領域12からなる。なお、図1B中、先の図1Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。

【0018】

基板1は、p型不純物濃度が例えば1.0×1015cm−3のp型シリコン基板である。素子分離領域12は、シャロートレンチアイソレーション(Shallow Trench Isolation)構造である。p型ウエル領域2は、基板1にボロン(B)をイオン注入することにより形成されている。p型ウエル領域2は、ボロン(B)濃度が例えば1.0×1016cm−3で深さが350nmである。ゲート絶縁膜3は酸化シリコン(SiO2)からなり、基板1上に形成されている。ゲート絶縁膜3の厚さは、例えば6nmである。ゲート電極4aは、ゲート絶縁膜3の表面上に形成されている。ドレイン領域5aは、ゲート電極4aの一方の側の基板1の内部に形成されている。ドレイン領域5aは、低濃度のn型導電性不純物であるリン(P)がイオン注入されている。なお、低濃度の導電性不純物が拡散されている領域をLDD(Lightly Doped Drain)領域という。ドレイン領域5aのリン(P)濃度は1.0×1019cm−3で深さが50nmである。堆積型ドレイン層6aは、ドレイン領域5aに接続されている。不純物拡散層6bは、堆積型ドレイン層6aに注入されている第1不純物又は第2不純物が基板1の表面から内部に向かって拡散されることにより形成されている。第1側壁スペーサを構成する絶縁膜7aはゲート電極4aのソース領域8a側の側壁に形成されている。第2側壁スペーサを構成する絶縁膜7bは、ゲート電極4aのドレイン5a側の側壁に形成され、堆積型ドレイン層6aとゲート電極4aとの間隙に埋め込まれている。ソース領域8aは、ゲート電極4aの他方の側の基板1の内部に形成されている。シリサイド層9は、低抵抗相のコバルト(Co)シリサイドからなる。シリサイド層9は、ソース領域8a、ゲート電極4a、及び堆積型ドレイン層6aの表面上に形成されている。

【0019】

次に、図2A〜図2D、図3A〜図3D、図4A〜図4Dを参照に、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程を説明する。

【0020】

図2Aは、基板を用意する工程を示す要部断面模式図である。図2Aは、基板1、p型ウエル領域2a、素子分離領域12を示す。基板1は、p型不純物濃度が例えば1.0×1015cm−3のp型シリコン基板である。素子分離領域12は、シャロートレンチアイソレーション構造である。p型ウエル領域2aは、基板1にボロン(B)をイオン注入することにより形成されている。p型ウエル領域2aは、ボロン(B)濃度が例えば1.0×1016cm−3で深さが350nmである。

【0021】

図2Bは、基板の表面上にゲート絶縁膜を形成する工程を示す要部断面模式図である。図2Bは、図2Aに加えて、ゲート絶縁膜3を示す。ゲート絶縁膜3は酸化シリコン(SiO2)からなる。

【0022】

図2Bに示すように、基板1の表面上に熱酸化処理を行うことによって、基板1の表面に厚さが、例えば、6nmのゲート絶縁膜3を形成する。

【0023】

図2Cは、堆積型ドレイン層を形成する領域内のゲート絶縁膜3を約300nm幅に渡ってエッチング除去する工程を示す要部拡大断面図である。

【0024】

図2Dは、基板及びゲート絶縁膜3の表面上にポリシリコン16を堆積する工程を示す要部拡大断面図である。図2Dは、図2Cに加えて、ポリシリコン16を示す。

【0025】

図3Aは、ゲート絶縁膜上にゲート電極と、ドレイン領域に堆積型ドレイン層を同時に離間して形成する工程を示す要部拡大模式図である。図3Eは、図2Dに加えて、ゲート電極4、堆積型ドレイン層6aを示す。ゲート電極4aの幅、及び堆積型ドレイン層6aの幅は300nmとする。

【0026】

図3Aに示すように、フォトリソグラフィーによりポリシリコン16をパターニングすることにより、ゲート電極4aと堆積型ドレイン層6aを形成する。なお、ゲート電極4aと堆積型ドレイン層6aとの間隙は、例えば0.2〜0.3μmが望ましい。後述するように、第2側壁スペーサを構成する絶縁膜7bがゲート電極4aと堆積型ドレイン層6aとの間隙に埋め込まれるからである。

【0027】

図3Bは、ゲート電極と堆積型ドレイン層との間隙に、低濃度の導電性不純物である第1不純物を注入する工程を示す要部拡大模式図である。図3Fは、図3Eに次いで、低濃度不純物領域17を示す。基板1において、低濃度不純物領域17は、リン(P)濃度が1.0×1019cm−3で深さが50nmである。なお、本実施例における第1不純物は、リン(P)である。

【0028】

図3Bに示すように、ゲート電極4aと堆積型ドレイン層6aをマスクとして、ゲート電極4aとプラグ6aとの間隙から、ドレイン領域5aに低濃度のn型導電性不純物であるリン(P)を低濃度不純物領域17に注入する。

【0029】

図3C、図3Dは、間隙を埋め込むように絶縁膜を形成する工程を示す要部拡大模式図である。図3Gは、図3Fに加えて、絶縁膜18を示す。絶縁膜18は、例えば酸化シリコン(SiO2)からなる。

【0030】

図3Cに示すように、絶縁膜18を、ゲート電極4aの表面上、プラグ6aの表面上、及び間隙の表面上に、かつその間隙を完全に埋め込むように厚く堆積させる。

【0031】

図3Dは、図3Gに加えて第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bを示す。絶縁膜7a、7bは例えば酸化シリコン(SiO2)からなる。

【0032】

図3Dに示すように、異方性エッチングを施すことによって、第1側壁スペーサを構成する絶縁膜7aをゲート電極4aのソース領域8a側の側壁に形成すると同時に、第2側壁スペーサを構成する絶縁膜7bをゲート電極4aのドレイン5a側の側壁に形成する。この時、ゲート電極4aと堆積型ドレイン層6aとの間隙は第2側壁スペーサを構成する絶縁膜7bで埋め込まれる。

【0033】

図4Aは、ソース領域、ゲート電極、及び堆積型ドレイン層に第2不純物である高濃度の導電性不純物を注入する工程を示す要部拡大模式図である。図4Aは、図3Dに加えて、ソース領域8aを示す。図4Aに示すように、ゲート電極4a、プラグ6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bをマスクとして第2不純物としての高濃度の導電性不純物であるリン(P)をイオン注入することによって、リン(P)濃度が例えば、5.0×1020cm−3で深さが100nmのn型ソース領域8aを形成する。

【0034】

図4Bは、堆積型ドレイン層6aに注入された第1不純物又は第2不純物を活性化するとともに、堆積型ドレイン層6aから第1不純物又は第2不純物を基板中に拡散させるための熱処理をする工程を示す要部拡大模式図である。この工程により、堆積型ドレイン層6aの下に、浅いドレイン領域5aに接続される不純物拡散層6bが形成される。図4Bは、図4Aに加えて、ドレイン領域5aを示す。図4Bに示すように、活性化アニール処理を行うことによって、前述した工程で注入した第1不純物又は第2不純物を活性化する。その際、堆積型ドレイン層6aに注入されている第1不純物又は第2不純物が基板1の表面から内部に向かって拡散することにより、不純物拡散層6bが形成される。

【0035】

図4Cは、ソース領域、ゲート電極、及び堆積型ドレイン層の表面上にシリサイド層を形成する工程を示す要部拡大模式図である。図4Cは、図4Bに加えて、コバルト(Co)シリサイド層9を示す。

【0036】

図4Cに示すように、ソース領域8a、ゲート電極4a、及び堆積型ドレイン層6aの表面上を含む基板1の表面上に金属膜、例えばコバルト(Co)膜を堆積させたのち、熱処理を行うことによってソース領域8a、8b、ゲート電極4a、及び堆積型ドレイン層6aの表面上に金属シリサイドとしてコバルト(Co)シリサイド層9を形成する。次いで、未反応のCo(コバルト)膜を除去したのち、第2熱処理を行うことによってコバルト(Co)シリサイド層9を低抵抗相のコバルト(Co)シリサイドに変換する。

【0037】

その後は、図1Aに図示される各コンタクトプラグ20a〜20c、図示しない層間絶縁膜、配線を形成する工程を経て、本実施例に係る高耐圧MOSトランジスタ100を完成させる。

【0038】

図5は本発明の第1実施例に係る高耐圧MOSトランジスタのソース・ドレイン領域間における電圧の推移を示している。横軸はドレイン領域5aの形成深さ[μm]を示し、縦軸はゲート電極4aと堆積型ドレイン層6a間に10V電圧を印加したときに、ゲート端に印加される電圧[V]を示す。なお、図中のオフセット(OFFSET)とは、ゲート電極4aと堆積型ドレイン層6aとの間隔[μm]を示す。点線はゲート電極4aと堆積型ドレイン層6aとの間隔が0.1[μm]の時の電圧の推移を示す。実線はゲート電極4aと堆積型ドレイン層6aとの間隔が0.2[μm]の時の電圧の推移を示す。その他の線は堆積型ドレイン層6aとの間隔が0.3[μm]以上の時の電圧の推移を示す。

【0039】

図5に示すように、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.3[μm]以上となると、ゲート端に印加される電圧の最大値は約3.7[V]となる。通常、高耐圧MOSトランジスタにおいて、ドレイン領域5aの長さはゲート端の電界を緩和するために大きくする構成が用いられる。しかしながら、図5から、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.3[μm]以上に設定しても、電界緩和の効果は見られないことがわかる。また、ゲート電極4aと堆積型ドレイン層6aとの間隔は、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bで埋め込まれる程度に狭いことが望ましい。

【0040】

また、高耐圧MOSトランジスタにおけるゲート電極4aと堆積型ドレイン層6aとの間隔の最適値は耐圧だけでなく、耐圧とトレードオフの関係にあるオン抵抗も考慮して決定される。そのため、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.2[μm]以下の設定とすることも可能である。この場合、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bを0.1[μm]堆積すれば、ゲート電極4aと堆積型ドレイン層6aとの間隔を埋め込むことが可能になる。

【0041】

このような高耐圧MOSトランジスタによれば、LDD領域がゲート電極4aと堆積型ドレイン層6aとの間に形成されているため、ドレイン領域5aとチャネル領域との境界に印加される電界を緩和することができる。そのため、ドレイン領域5aと基板1間の耐圧を高めることができる。

【0042】

また、堆積型ドレイン層6aとゲート電極4aとの間隙に低濃度の導電性不純物を注入する工程と、堆積型ドレイン層6aより導電性不純物を基板に拡散させるための熱処理をする工程とによって、ソース領域に比べて浅いドレイン(不純物拡散層6b)を自己整合的に形成できる。そのため、LDD領域をマスクで形成する場合のような位置あわせが不要であり、MOSトランジスタの特性のばらつきが改善されると共に、ゲート長の微細化も可能になる。

【0043】

また、堆積型ドレイン層6aとゲート電極4aは同一のマスク工程によって形成されるため、堆積型ドレイン層6aとゲート電極4aとの間隔を設定する際、複数のマスク工程の組み合わせに必要な位置合わせ余裕(マージン)が不要となる。そのため、ゲート電極4aと堆積型ドレイン層6aとの間隔を、ドレイン領域5aにおける寄生抵抗と電界緩和とのトレードオフの関係で決定される最適値に確実に設定できるようになる。

【0044】

また、上記の実施例においては、高耐圧MOSトランジスタをn型MOSトランジスタとして説明しているが、p型高耐圧MOSトランジスタとして形成しても良いものであり、その場合には、上述のn型高耐圧MOSトランジスタにおける導電型を逆にすれば良い。

【0045】

また、本発明の実施例を説明してきたが、本発明は実施例に記載された構成・条件等に限られるものではなく各種の変更が可能であり、例えば、上記の実施例1に記載した、不純物濃度、深さ、厚さ、ゲート長、間隙長は単なる一例であり、必要とする高耐圧特性及び高周波特性に応じて適宜設定されるものである。

【0046】

また、ゲート電極と堆積型ドレイン層の間に埋め込まれる絶縁膜はシリサイドブロックとしても働くため、CMOSのロジックプロセスとの整合性がよく、追加工程無しで高耐圧トランジスタを作製でき、高耐圧トランジスタを用いたパワーアンプと制御用ロジック回路の集積化を低コストで実現できる。

【0047】

例えば、高耐圧トランジスタを高周波のパワーアンプ用に用いる場合、制御用のCMOSロジック回路と混載することが多い。今後、RF回路とベースバンドの回路を1チップ化する場合も、当然、CMOSとの混載が必要であり、ロジック用CMOSプロセスと相性のいい本発明の製造法は望ましいものである。

(実施例2)

本発明の第2実施例に係る高耐圧MOSトランジスタを、図6A〜図6Bを用いて詳細に説明する。第2実施例に係る高耐圧MOSトランジスタは、ゲート電極がドレイン領域を取り囲むようにして形成されている。そのため、ドレイン領域の形成面積が小さくなり、ドレイン領域に寄生する容量を低減することができることを特徴とするものである。

【0048】

図6Aは、本発明の第2実施例に係る高耐圧MOSトランジスタの平面図である。図6Aは高耐圧MOSトランジスタ110を示し、ゲート電極4a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、ソース領域に配線を接続するためのコンタクトプラグ20a、堆積型ドレイン層に配線を接続するためのコンタクトプラグ20c、ゲート電極4aに配線を接続するためのコンタクトプラグ20c、からなる。なお、ゲート電極4a、堆積型ドレイン層6a、ソース領域8aの表面上にはシリサイド層9、及び図示しない層間絶縁膜が形成されている。図6A中、先の図1Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。図6Aで示すように、ゲート電極4aが堆積型ドレイン層6aを取り囲むように形成されている。

【0049】

図6Bは第2実施例に係る高耐圧MOSトランジスタの要部断面模式図である。なお、図6Bは図6Aの線X−X'における断面を示す。図6Bは高耐圧MOSトランジスタ110を示し、基板1、p型ウエル領域2、ゲート絶縁膜3、ゲート電極4a、ドレイン領域5a、堆積型ドレイン層6a、不純物拡散層6b、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、コバルト(Co)シリサイド層9、素子分離領域12からなる。なお、図6B中、先の図5Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。

【0050】

第2実施例に係る高耐圧MOSトランジスタの構成的特長は、ゲート電極4aがドレイン領域5a、及び堆積型ドレイン層6aを取り囲むようにして形成されている。このような構成によれば、ゲート電極4aとドレイン領域5a間に電界が集中する箇所(エッジ部)を可及的に減少させることができる。また、ドレイン領域5aの形成面積が小さくなるため、ドレイン領域に寄生する容量を低減することができる。そのため、ドレイン領域5aにおける電界緩和をさらに促進させることができるようになる。

【産業上の利用可能性】

【0051】

本発明の活用例としては、携帯電話などの移動体通信機器の送信部分で用いられる高周波の電力増幅素子が典型的なものであるが、他の用途において高耐圧と高周波特性が求められる場合にも適用されるものである。

【図面の簡単な説明】

【0052】

【図1】図1Aは、本発明の第1実施例に係る高耐圧MOSトランジスタの平面図である。図1Bは、本発明の第1実施例に係る高耐圧MOSトランジスタの要部断面模式図である。

【図2】図2A〜図2Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図3】図3A〜図3Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図4】図4A〜図4Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図5】図5は、本発明の第1実施例に係る高耐圧MOSトランジスタのソース・ドレイン領域間における電圧の推移を示した図である。

【図6】図6Aは、本発明の第2実施例に係る高耐圧MOSトランジスタの平面図である。図6Bは、本発明の第2実施例に係る高耐圧MOSトランジスタの要部断面模式図である。

【符号の説明】

【0053】

1 p型シリコン基板

2a p型ウエル領域

3 ゲート絶縁膜

4a ゲート電極

5a n型ドレイン領域

6a 堆積型ドレイン層

6b 不純物拡散層

7a 第1側壁スペーサを構成する絶縁膜

7b 第2側壁スペーサを構成する絶縁膜

8a n型ソース領域

9 コバルト(Co)シリサイド層

12 素子分離領域(STI)

16 ポリシリコン(Si)

17 低濃度導電性不純物領域

20a ソース領域に配線を接続するためのコンタクトプラグ

20b 堆積型ドレイン層に配線を接続するためのコンタクトプラグ

20c ゲート電極に配線を接続するためのコンタクトプラグ

100 高耐圧MOSトランジスタ

110 高耐圧MOSトランジスタ

【技術分野】

【0001】

本発明は、高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタに関するものである。

【背景技術】

【0002】

高耐圧MOSトランジスタでは良好な高周波特性のみならず、ソース・ドレイン耐圧が大きいことが期待されている。

【0003】

このような高耐圧MOSトランジスタでは、ある程度以上大きな電圧がドレイン領域にかかると、ドレイン領域とチャネル領域との境界に大きな電界が発生し、この境界部分でジャンクションブレイクダウン(降伏現象)が発生する。このため、如何にしてドレイン領域とチャネル部分との境界の間に発生する電界を緩和するかが高耐圧化の課題である。

【0004】

そのような電界を緩和するために、高耐圧MOSトランジスタを形成する際、電界を緩和するための不純物濃度分布を持たせたドレイン領域をレジストによってマスクして形成するプロセスを用いた高耐圧MOSトランジスタの製造方法が提案されている(例えば、特許文献1参照)。特許文献1によれば、ドレイン領域において不純物濃度が低い領域(LDD(Lightly Doped Drain)領域)を形成するために、レジストパターンによって不純物濃度が高い領域を形成するためのイオン注入をマスクしている。

【特許文献1】特開平11−186543号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1によれば、不純物濃度分布を持つ不純物拡散層からなるドレイン領域を形成するマスク工程の際、位置合わせのための余分な領域が必要となる。また、ゲート電極、ドレイン領域の不純物濃度が低い部分、及びドレイン領域の不純物濃度が高い部分の形成位置にばらつきが発生するため、MOSトランジスタの特性のばらつきが大きくなる懸念があった。その結果、マスクの位置合わせの余裕を確保するためにゲート電極の微細化も困難になる。また、素子の微細化ができず、レイアウト面積は増加してしまう。

【0006】

本発明は、マスク工程を簡略化しながらも、レイアウト面積を縮小した高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る高耐圧MOSトランジスタの製造方法は、基板上にゲート絶縁膜を形成する工程と、前記基板の第1領域における前記ゲート絶縁膜を除去し、前記第1領域の前記基板を露出させる工程と、前記ゲート絶縁膜上にゲート電極を形成し、前記領域に堆積型ドレイン層を離間して形成する工程と、前記ゲート電極と前記堆積型ドレイン層とをマスクとして、前記基板に第1の不純物を注入する工程と、前記ゲート電極と前記堆積型ドレイン層の間隙に絶縁膜を埋め込む工程と、前記ゲート電極、前記堆積型ドレイン層、及び前記絶縁膜をマスクとして前記基板に第2不純物を注入してソース領域を形成する工程と、第1熱処理を行い、前記堆積型ドレイン層に注入された前記第1不純物又は前記第2不純物を前記基板中に拡散させ不純物拡散層を形成する工程と、を有することを特徴とする。

【0008】

本発明に係る高耐圧MOSトランジスタは、基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の一方の側に位置する前記基板の内部に形成されたドレイン領域と、前記ゲート電極の他方の側に位置する前記基板の内部に形成されたソース領域と、前記ドレイン領域上に形成され、且つ不純物拡散領域を介して前記ドレイン領域と電気的に接続された堆積型ドレイン層と、前記ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、前記ゲート電極の前記ドレイン側の側壁に形成され、前記堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有し、前記ソース領域は、前記ドレイン領域よりも深いことを特徴とする。

【発明の効果】

【0009】

本発明に係る高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタによれば、トランジスタのドレイン側には通常の高濃度の不純物による接合が存在せず、LDD領域がゲート電極と堆積型ドレイン層との間に形成されているため、ドレイン領域とチャネル領域との境界に印加される電界を緩和することができ、且つドレイン領域と基板間の耐圧を高めることができる。

【0010】

また、LDD領域がゲート電極及びプラグに対して自己整合的に形成されるので、LDD領域をマスクで形成する場合のような位置あわせが不要であり、MOSトランジスタの特性のばらつきが改善されると共に、ゲート長の微細化も可能になる。

【0011】

また、ゲートと堆積型ドレイン層の間のギャップ領域に埋め込まれる絶縁膜はシリサイドブロックとしても働くため、CMOSのロジックプロセスとの整合性がよく、追加工程無しで高耐圧トランジスタを作製でき、高耐圧トランジスタを用いたパワーアンプと制御用ロジック回路の集積化を低コストで実現できる。

【発明を実施するための最良の形態】

【0012】

以下、本発明の実施例にかかる高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタの実施例について説明する。ただし、本発明は各実施例に限定されるものではない。

(実施例1)

本発明の第1の実施例を、n型高耐圧MOSトランジスタ、n型高耐圧MOSトランジスタの製造方法を例に、図1A〜図1Bを用いて詳細に説明する。第1実施例にかかる高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法は、LDD領域がゲート電極及び堆積型ドレイン層に対して自己整合的に形成されることを特徴とするものである。

【0013】

図1A〜図1Bは、本発明の第1の実施例に係る半導体装置の各要部図である。

【0014】

図1Aは、本発明の第1実施例に係る高耐圧MOSトランジスタの平面図である。図1Aは高耐圧MOSトランジスタ100を示し、ゲート電極4a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、ソース領域に配線を接続するためのコンタクトプラグ20a、ドレイン領域に配線を接続するためのコンタクトプラグ20b、ゲート電極4aに配線を接続するためのコンタクトプラグ20c、からなる。なお、ゲート電極4a、堆積型ドレイン層6a、ソース領域8aの表面上には、シリサイド層9、図示しない層間絶縁膜が形成されている。

【0015】

ゲート電極4a、堆積型ドレイン層6a、ソース領域8aはポリシリコンに高濃度の導電性不純物を注入して形成されている。ゲート電極4a、堆積型ドレイン層6a、ソース領域8aにはリン(P)イオンが注入されており、リン(P)濃度が例えば、5.0×1020cm−3である。第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bは絶縁性を有し、例えば酸化シリコン(SiO2)からなる。ソース領域8aに配線を接続するためのコンタクトプラグ20a、堆積型ドレイン層に配線を接続するためのコンタクトプラグ20b、ゲート電極4aに配線を接続するためのコンタクトプラグ20cは、タングステン(W)からなり、ソース領域8a、堆積型ドレイン層6a、及びゲート電極4aと電気的に接続するものである。

【0016】

図1Aに示すように、堆積型ドレイン層6aはゲート電極4aの一方の側の基板上に形成されている。ソース領域8aはゲート電極4aの他方の側の基板内に形成されている。第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bは、ゲート電極4a、堆積型ドレイン層6aの周囲に形成されている。なお、高耐圧MOSトランジスタ100の周囲には素子分離領域12が形成されている。

【0017】

図1Bは第1の実施例の第1例に係る高耐圧MOSトランジスタの要部断面模式図である。なお、図1Bは図1Aの線X−X'における断面を示す。図1Bは高耐圧MOSトランジスタ100を示し、p型シリコン基板1、p型ウエル領域2a、ゲート絶縁膜3、ゲート電極4a、n型ドレイン領域5a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、n型ソース領域8a、コバルト(Co)シリサイド層9、素子分離領域12からなる。なお、図1B中、先の図1Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。

【0018】

基板1は、p型不純物濃度が例えば1.0×1015cm−3のp型シリコン基板である。素子分離領域12は、シャロートレンチアイソレーション(Shallow Trench Isolation)構造である。p型ウエル領域2は、基板1にボロン(B)をイオン注入することにより形成されている。p型ウエル領域2は、ボロン(B)濃度が例えば1.0×1016cm−3で深さが350nmである。ゲート絶縁膜3は酸化シリコン(SiO2)からなり、基板1上に形成されている。ゲート絶縁膜3の厚さは、例えば6nmである。ゲート電極4aは、ゲート絶縁膜3の表面上に形成されている。ドレイン領域5aは、ゲート電極4aの一方の側の基板1の内部に形成されている。ドレイン領域5aは、低濃度のn型導電性不純物であるリン(P)がイオン注入されている。なお、低濃度の導電性不純物が拡散されている領域をLDD(Lightly Doped Drain)領域という。ドレイン領域5aのリン(P)濃度は1.0×1019cm−3で深さが50nmである。堆積型ドレイン層6aは、ドレイン領域5aに接続されている。不純物拡散層6bは、堆積型ドレイン層6aに注入されている第1不純物又は第2不純物が基板1の表面から内部に向かって拡散されることにより形成されている。第1側壁スペーサを構成する絶縁膜7aはゲート電極4aのソース領域8a側の側壁に形成されている。第2側壁スペーサを構成する絶縁膜7bは、ゲート電極4aのドレイン5a側の側壁に形成され、堆積型ドレイン層6aとゲート電極4aとの間隙に埋め込まれている。ソース領域8aは、ゲート電極4aの他方の側の基板1の内部に形成されている。シリサイド層9は、低抵抗相のコバルト(Co)シリサイドからなる。シリサイド層9は、ソース領域8a、ゲート電極4a、及び堆積型ドレイン層6aの表面上に形成されている。

【0019】

次に、図2A〜図2D、図3A〜図3D、図4A〜図4Dを参照に、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程を説明する。

【0020】

図2Aは、基板を用意する工程を示す要部断面模式図である。図2Aは、基板1、p型ウエル領域2a、素子分離領域12を示す。基板1は、p型不純物濃度が例えば1.0×1015cm−3のp型シリコン基板である。素子分離領域12は、シャロートレンチアイソレーション構造である。p型ウエル領域2aは、基板1にボロン(B)をイオン注入することにより形成されている。p型ウエル領域2aは、ボロン(B)濃度が例えば1.0×1016cm−3で深さが350nmである。

【0021】

図2Bは、基板の表面上にゲート絶縁膜を形成する工程を示す要部断面模式図である。図2Bは、図2Aに加えて、ゲート絶縁膜3を示す。ゲート絶縁膜3は酸化シリコン(SiO2)からなる。

【0022】

図2Bに示すように、基板1の表面上に熱酸化処理を行うことによって、基板1の表面に厚さが、例えば、6nmのゲート絶縁膜3を形成する。

【0023】

図2Cは、堆積型ドレイン層を形成する領域内のゲート絶縁膜3を約300nm幅に渡ってエッチング除去する工程を示す要部拡大断面図である。

【0024】

図2Dは、基板及びゲート絶縁膜3の表面上にポリシリコン16を堆積する工程を示す要部拡大断面図である。図2Dは、図2Cに加えて、ポリシリコン16を示す。

【0025】

図3Aは、ゲート絶縁膜上にゲート電極と、ドレイン領域に堆積型ドレイン層を同時に離間して形成する工程を示す要部拡大模式図である。図3Eは、図2Dに加えて、ゲート電極4、堆積型ドレイン層6aを示す。ゲート電極4aの幅、及び堆積型ドレイン層6aの幅は300nmとする。

【0026】

図3Aに示すように、フォトリソグラフィーによりポリシリコン16をパターニングすることにより、ゲート電極4aと堆積型ドレイン層6aを形成する。なお、ゲート電極4aと堆積型ドレイン層6aとの間隙は、例えば0.2〜0.3μmが望ましい。後述するように、第2側壁スペーサを構成する絶縁膜7bがゲート電極4aと堆積型ドレイン層6aとの間隙に埋め込まれるからである。

【0027】

図3Bは、ゲート電極と堆積型ドレイン層との間隙に、低濃度の導電性不純物である第1不純物を注入する工程を示す要部拡大模式図である。図3Fは、図3Eに次いで、低濃度不純物領域17を示す。基板1において、低濃度不純物領域17は、リン(P)濃度が1.0×1019cm−3で深さが50nmである。なお、本実施例における第1不純物は、リン(P)である。

【0028】

図3Bに示すように、ゲート電極4aと堆積型ドレイン層6aをマスクとして、ゲート電極4aとプラグ6aとの間隙から、ドレイン領域5aに低濃度のn型導電性不純物であるリン(P)を低濃度不純物領域17に注入する。

【0029】

図3C、図3Dは、間隙を埋め込むように絶縁膜を形成する工程を示す要部拡大模式図である。図3Gは、図3Fに加えて、絶縁膜18を示す。絶縁膜18は、例えば酸化シリコン(SiO2)からなる。

【0030】

図3Cに示すように、絶縁膜18を、ゲート電極4aの表面上、プラグ6aの表面上、及び間隙の表面上に、かつその間隙を完全に埋め込むように厚く堆積させる。

【0031】

図3Dは、図3Gに加えて第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bを示す。絶縁膜7a、7bは例えば酸化シリコン(SiO2)からなる。

【0032】

図3Dに示すように、異方性エッチングを施すことによって、第1側壁スペーサを構成する絶縁膜7aをゲート電極4aのソース領域8a側の側壁に形成すると同時に、第2側壁スペーサを構成する絶縁膜7bをゲート電極4aのドレイン5a側の側壁に形成する。この時、ゲート電極4aと堆積型ドレイン層6aとの間隙は第2側壁スペーサを構成する絶縁膜7bで埋め込まれる。

【0033】

図4Aは、ソース領域、ゲート電極、及び堆積型ドレイン層に第2不純物である高濃度の導電性不純物を注入する工程を示す要部拡大模式図である。図4Aは、図3Dに加えて、ソース領域8aを示す。図4Aに示すように、ゲート電極4a、プラグ6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bをマスクとして第2不純物としての高濃度の導電性不純物であるリン(P)をイオン注入することによって、リン(P)濃度が例えば、5.0×1020cm−3で深さが100nmのn型ソース領域8aを形成する。

【0034】

図4Bは、堆積型ドレイン層6aに注入された第1不純物又は第2不純物を活性化するとともに、堆積型ドレイン層6aから第1不純物又は第2不純物を基板中に拡散させるための熱処理をする工程を示す要部拡大模式図である。この工程により、堆積型ドレイン層6aの下に、浅いドレイン領域5aに接続される不純物拡散層6bが形成される。図4Bは、図4Aに加えて、ドレイン領域5aを示す。図4Bに示すように、活性化アニール処理を行うことによって、前述した工程で注入した第1不純物又は第2不純物を活性化する。その際、堆積型ドレイン層6aに注入されている第1不純物又は第2不純物が基板1の表面から内部に向かって拡散することにより、不純物拡散層6bが形成される。

【0035】

図4Cは、ソース領域、ゲート電極、及び堆積型ドレイン層の表面上にシリサイド層を形成する工程を示す要部拡大模式図である。図4Cは、図4Bに加えて、コバルト(Co)シリサイド層9を示す。

【0036】

図4Cに示すように、ソース領域8a、ゲート電極4a、及び堆積型ドレイン層6aの表面上を含む基板1の表面上に金属膜、例えばコバルト(Co)膜を堆積させたのち、熱処理を行うことによってソース領域8a、8b、ゲート電極4a、及び堆積型ドレイン層6aの表面上に金属シリサイドとしてコバルト(Co)シリサイド層9を形成する。次いで、未反応のCo(コバルト)膜を除去したのち、第2熱処理を行うことによってコバルト(Co)シリサイド層9を低抵抗相のコバルト(Co)シリサイドに変換する。

【0037】

その後は、図1Aに図示される各コンタクトプラグ20a〜20c、図示しない層間絶縁膜、配線を形成する工程を経て、本実施例に係る高耐圧MOSトランジスタ100を完成させる。

【0038】

図5は本発明の第1実施例に係る高耐圧MOSトランジスタのソース・ドレイン領域間における電圧の推移を示している。横軸はドレイン領域5aの形成深さ[μm]を示し、縦軸はゲート電極4aと堆積型ドレイン層6a間に10V電圧を印加したときに、ゲート端に印加される電圧[V]を示す。なお、図中のオフセット(OFFSET)とは、ゲート電極4aと堆積型ドレイン層6aとの間隔[μm]を示す。点線はゲート電極4aと堆積型ドレイン層6aとの間隔が0.1[μm]の時の電圧の推移を示す。実線はゲート電極4aと堆積型ドレイン層6aとの間隔が0.2[μm]の時の電圧の推移を示す。その他の線は堆積型ドレイン層6aとの間隔が0.3[μm]以上の時の電圧の推移を示す。

【0039】

図5に示すように、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.3[μm]以上となると、ゲート端に印加される電圧の最大値は約3.7[V]となる。通常、高耐圧MOSトランジスタにおいて、ドレイン領域5aの長さはゲート端の電界を緩和するために大きくする構成が用いられる。しかしながら、図5から、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.3[μm]以上に設定しても、電界緩和の効果は見られないことがわかる。また、ゲート電極4aと堆積型ドレイン層6aとの間隔は、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bで埋め込まれる程度に狭いことが望ましい。

【0040】

また、高耐圧MOSトランジスタにおけるゲート電極4aと堆積型ドレイン層6aとの間隔の最適値は耐圧だけでなく、耐圧とトレードオフの関係にあるオン抵抗も考慮して決定される。そのため、ゲート電極4aと堆積型ドレイン層6aとの間隔が0.2[μm]以下の設定とすることも可能である。この場合、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7bを0.1[μm]堆積すれば、ゲート電極4aと堆積型ドレイン層6aとの間隔を埋め込むことが可能になる。

【0041】

このような高耐圧MOSトランジスタによれば、LDD領域がゲート電極4aと堆積型ドレイン層6aとの間に形成されているため、ドレイン領域5aとチャネル領域との境界に印加される電界を緩和することができる。そのため、ドレイン領域5aと基板1間の耐圧を高めることができる。

【0042】

また、堆積型ドレイン層6aとゲート電極4aとの間隙に低濃度の導電性不純物を注入する工程と、堆積型ドレイン層6aより導電性不純物を基板に拡散させるための熱処理をする工程とによって、ソース領域に比べて浅いドレイン(不純物拡散層6b)を自己整合的に形成できる。そのため、LDD領域をマスクで形成する場合のような位置あわせが不要であり、MOSトランジスタの特性のばらつきが改善されると共に、ゲート長の微細化も可能になる。

【0043】

また、堆積型ドレイン層6aとゲート電極4aは同一のマスク工程によって形成されるため、堆積型ドレイン層6aとゲート電極4aとの間隔を設定する際、複数のマスク工程の組み合わせに必要な位置合わせ余裕(マージン)が不要となる。そのため、ゲート電極4aと堆積型ドレイン層6aとの間隔を、ドレイン領域5aにおける寄生抵抗と電界緩和とのトレードオフの関係で決定される最適値に確実に設定できるようになる。

【0044】

また、上記の実施例においては、高耐圧MOSトランジスタをn型MOSトランジスタとして説明しているが、p型高耐圧MOSトランジスタとして形成しても良いものであり、その場合には、上述のn型高耐圧MOSトランジスタにおける導電型を逆にすれば良い。

【0045】

また、本発明の実施例を説明してきたが、本発明は実施例に記載された構成・条件等に限られるものではなく各種の変更が可能であり、例えば、上記の実施例1に記載した、不純物濃度、深さ、厚さ、ゲート長、間隙長は単なる一例であり、必要とする高耐圧特性及び高周波特性に応じて適宜設定されるものである。

【0046】

また、ゲート電極と堆積型ドレイン層の間に埋め込まれる絶縁膜はシリサイドブロックとしても働くため、CMOSのロジックプロセスとの整合性がよく、追加工程無しで高耐圧トランジスタを作製でき、高耐圧トランジスタを用いたパワーアンプと制御用ロジック回路の集積化を低コストで実現できる。

【0047】

例えば、高耐圧トランジスタを高周波のパワーアンプ用に用いる場合、制御用のCMOSロジック回路と混載することが多い。今後、RF回路とベースバンドの回路を1チップ化する場合も、当然、CMOSとの混載が必要であり、ロジック用CMOSプロセスと相性のいい本発明の製造法は望ましいものである。

(実施例2)

本発明の第2実施例に係る高耐圧MOSトランジスタを、図6A〜図6Bを用いて詳細に説明する。第2実施例に係る高耐圧MOSトランジスタは、ゲート電極がドレイン領域を取り囲むようにして形成されている。そのため、ドレイン領域の形成面積が小さくなり、ドレイン領域に寄生する容量を低減することができることを特徴とするものである。

【0048】

図6Aは、本発明の第2実施例に係る高耐圧MOSトランジスタの平面図である。図6Aは高耐圧MOSトランジスタ110を示し、ゲート電極4a、堆積型ドレイン層6a、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、ソース領域に配線を接続するためのコンタクトプラグ20a、堆積型ドレイン層に配線を接続するためのコンタクトプラグ20c、ゲート電極4aに配線を接続するためのコンタクトプラグ20c、からなる。なお、ゲート電極4a、堆積型ドレイン層6a、ソース領域8aの表面上にはシリサイド層9、及び図示しない層間絶縁膜が形成されている。図6A中、先の図1Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。図6Aで示すように、ゲート電極4aが堆積型ドレイン層6aを取り囲むように形成されている。

【0049】

図6Bは第2実施例に係る高耐圧MOSトランジスタの要部断面模式図である。なお、図6Bは図6Aの線X−X'における断面を示す。図6Bは高耐圧MOSトランジスタ110を示し、基板1、p型ウエル領域2、ゲート絶縁膜3、ゲート電極4a、ドレイン領域5a、堆積型ドレイン層6a、不純物拡散層6b、第1側壁スペーサを構成する絶縁膜7a、第2側壁スペーサを構成する絶縁膜7b、ソース領域8a、コバルト(Co)シリサイド層9、素子分離領域12からなる。なお、図6B中、先の図5Aで記した構成要素と完全に同一である構成要素には、同一の参照番号を付す。

【0050】

第2実施例に係る高耐圧MOSトランジスタの構成的特長は、ゲート電極4aがドレイン領域5a、及び堆積型ドレイン層6aを取り囲むようにして形成されている。このような構成によれば、ゲート電極4aとドレイン領域5a間に電界が集中する箇所(エッジ部)を可及的に減少させることができる。また、ドレイン領域5aの形成面積が小さくなるため、ドレイン領域に寄生する容量を低減することができる。そのため、ドレイン領域5aにおける電界緩和をさらに促進させることができるようになる。

【産業上の利用可能性】

【0051】

本発明の活用例としては、携帯電話などの移動体通信機器の送信部分で用いられる高周波の電力増幅素子が典型的なものであるが、他の用途において高耐圧と高周波特性が求められる場合にも適用されるものである。

【図面の簡単な説明】

【0052】

【図1】図1Aは、本発明の第1実施例に係る高耐圧MOSトランジスタの平面図である。図1Bは、本発明の第1実施例に係る高耐圧MOSトランジスタの要部断面模式図である。

【図2】図2A〜図2Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図3】図3A〜図3Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図4】図4A〜図4Dは、本発明の第1実施例に係る高耐圧MOSトランジスタの製造工程の各要部断面模式図である。

【図5】図5は、本発明の第1実施例に係る高耐圧MOSトランジスタのソース・ドレイン領域間における電圧の推移を示した図である。

【図6】図6Aは、本発明の第2実施例に係る高耐圧MOSトランジスタの平面図である。図6Bは、本発明の第2実施例に係る高耐圧MOSトランジスタの要部断面模式図である。

【符号の説明】

【0053】

1 p型シリコン基板

2a p型ウエル領域

3 ゲート絶縁膜

4a ゲート電極

5a n型ドレイン領域

6a 堆積型ドレイン層

6b 不純物拡散層

7a 第1側壁スペーサを構成する絶縁膜

7b 第2側壁スペーサを構成する絶縁膜

8a n型ソース領域

9 コバルト(Co)シリサイド層

12 素子分離領域(STI)

16 ポリシリコン(Si)

17 低濃度導電性不純物領域

20a ソース領域に配線を接続するためのコンタクトプラグ

20b 堆積型ドレイン層に配線を接続するためのコンタクトプラグ

20c ゲート電極に配線を接続するためのコンタクトプラグ

100 高耐圧MOSトランジスタ

110 高耐圧MOSトランジスタ

【特許請求の範囲】

【請求項1】

基板上にゲート絶縁膜を形成する工程と、

前記基板の第1領域における前記ゲート絶縁膜を除去し、前記第1領域の前記基板を露出させる工程と、

前記ゲート絶縁膜上にゲート電極を形成し、前記領域に堆積型ドレイン層を離間して形成する工程と、

前記ゲート電極と前記堆積型ドレイン層とをマスクとして、前記基板に第1の不純物を注入する工程と、

前記ゲート電極と前記堆積型ドレイン層の間隙に絶縁膜を埋め込む工程と、

前記ゲート電極、前記堆積型ドレイン層、及び前記絶縁膜をマスクとして前記基板に第2不純物を注入してソース領域を形成する工程と、

第1熱処理を行い、前記堆積型ドレイン層に注入された前記第1不純物又は前記第2不純物を前記基板中に拡散させ不純物拡散層を形成する工程と、

を有することを特徴とするMOSトランジスタの製造方法。

【請求項2】

前記絶縁膜を埋め込む工程の後、全面に金属膜を堆積させ、第2熱処理を行なって前記ソース領域、前記ゲート電極、及び前記堆積型ドレイン層上に金属シリサイド層を形成する工程を更に有することを特徴とする請求項1に記載のMOSトランジスタの製造方法。

【請求項3】

前記第2不純物を注入する工程は、前記第1不純物よりも深い位置まで前記第2不純物を注入することを特徴とする請求項1又は請求項2に記載のMOSトランジスタの製造方法。

【請求項4】

前記不純物拡散層は、前記第2不純物の注入深さよりも浅く形成されることを特徴とする請求項1乃至請求項3のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項5】

前記ゲート電極及び前記堆積型ドレイン層はポリシリコンからなることを特徴とする請求項1乃至請求項4のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項6】

前記絶縁膜を埋め込む工程は、全面に前記絶縁膜を堆積させる工程と、

前記全面に堆積された前記絶縁膜を異方性エッチングによりエッチングすることを特徴とする請求項1乃至請求項5のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項7】

基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

前記ゲート電極の一方の側に位置する前記基板の内部に形成されたドレイン領域と、

前記ゲート電極の他方の側に位置する前記基板の内部に形成されたソース領域と、

前記ドレイン領域上に形成され、且つ不純物拡散領域を介して前記ドレイン領域と電気的に接続された堆積型ドレイン層と、

前記ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、

前記ゲート電極の前記ドレイン側の側壁に形成され、前記堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有し、

前記ソース領域は、前記ドレイン領域よりも深いことを特徴とするMOSトランジスタ。

【請求項8】

前記堆積型ドレイン層は、導電性不純物を含有していることを特徴とする請求項7に記載のMOSトランジスタ。

【請求項9】

前記ソース領域、前記ゲート電極、及び前記堆積型ドレイン層の表面上に形成されているシリサイド層をさらに有することを特徴とする請求項7又は請求項8に記載のMOSトランジスタ。

【請求項10】

前記ゲート電極は、前記堆積型ドレイン層を取り囲むようにして形成されていることを特徴とする請求項7乃至請求項9のいずれかに記載のMOSトランジスタ。

【請求項1】

基板上にゲート絶縁膜を形成する工程と、

前記基板の第1領域における前記ゲート絶縁膜を除去し、前記第1領域の前記基板を露出させる工程と、

前記ゲート絶縁膜上にゲート電極を形成し、前記領域に堆積型ドレイン層を離間して形成する工程と、

前記ゲート電極と前記堆積型ドレイン層とをマスクとして、前記基板に第1の不純物を注入する工程と、

前記ゲート電極と前記堆積型ドレイン層の間隙に絶縁膜を埋め込む工程と、

前記ゲート電極、前記堆積型ドレイン層、及び前記絶縁膜をマスクとして前記基板に第2不純物を注入してソース領域を形成する工程と、

第1熱処理を行い、前記堆積型ドレイン層に注入された前記第1不純物又は前記第2不純物を前記基板中に拡散させ不純物拡散層を形成する工程と、

を有することを特徴とするMOSトランジスタの製造方法。

【請求項2】

前記絶縁膜を埋め込む工程の後、全面に金属膜を堆積させ、第2熱処理を行なって前記ソース領域、前記ゲート電極、及び前記堆積型ドレイン層上に金属シリサイド層を形成する工程を更に有することを特徴とする請求項1に記載のMOSトランジスタの製造方法。

【請求項3】

前記第2不純物を注入する工程は、前記第1不純物よりも深い位置まで前記第2不純物を注入することを特徴とする請求項1又は請求項2に記載のMOSトランジスタの製造方法。

【請求項4】

前記不純物拡散層は、前記第2不純物の注入深さよりも浅く形成されることを特徴とする請求項1乃至請求項3のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項5】

前記ゲート電極及び前記堆積型ドレイン層はポリシリコンからなることを特徴とする請求項1乃至請求項4のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項6】

前記絶縁膜を埋め込む工程は、全面に前記絶縁膜を堆積させる工程と、

前記全面に堆積された前記絶縁膜を異方性エッチングによりエッチングすることを特徴とする請求項1乃至請求項5のいずれか1項に記載のMOSトランジスタの製造方法。

【請求項7】

基板上に形成されたゲート絶縁膜と、

前記ゲート絶縁膜上に形成されたゲート電極と、

前記ゲート電極の一方の側に位置する前記基板の内部に形成されたドレイン領域と、

前記ゲート電極の他方の側に位置する前記基板の内部に形成されたソース領域と、

前記ドレイン領域上に形成され、且つ不純物拡散領域を介して前記ドレイン領域と電気的に接続された堆積型ドレイン層と、

前記ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、

前記ゲート電極の前記ドレイン側の側壁に形成され、前記堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有し、

前記ソース領域は、前記ドレイン領域よりも深いことを特徴とするMOSトランジスタ。

【請求項8】

前記堆積型ドレイン層は、導電性不純物を含有していることを特徴とする請求項7に記載のMOSトランジスタ。

【請求項9】

前記ソース領域、前記ゲート電極、及び前記堆積型ドレイン層の表面上に形成されているシリサイド層をさらに有することを特徴とする請求項7又は請求項8に記載のMOSトランジスタ。

【請求項10】

前記ゲート電極は、前記堆積型ドレイン層を取り囲むようにして形成されていることを特徴とする請求項7乃至請求項9のいずれかに記載のMOSトランジスタ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2008−244008(P2008−244008A)

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願番号】特願2007−80159(P2007−80159)

【出願日】平成19年3月26日(2007.3.26)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

【公開日】平成20年10月9日(2008.10.9)

【国際特許分類】

【出願日】平成19年3月26日(2007.3.26)

【出願人】(308014341)富士通マイクロエレクトロニクス株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]