高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高耐圧MOSFETの回路シミュレーション技術に関し、特に、回路シミュレーション用モデルの作成方法と装置並びにプログラムに関する。

【背景技術】

【0002】

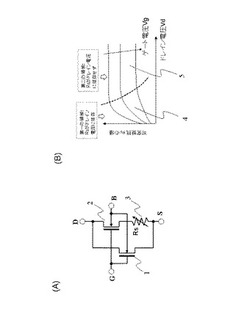

高耐圧MOSFET(Metal Oxide Semiconductor Field Effect Transistor)の回路シミュレーション用モデルの高精度化を図るために、通常のMOSFETを表現する素子モデルに可変抵抗を組み合わせたマクロモデルを用いる技術が、例えば特許文献1等に記載されている。その例を図19(A)、(B)に示す。

【0003】

図19(A)は、MOSFET102のドレイン側に可変抵抗101を接続した回路ブロックを一つの高耐圧MOSFETを表現するマクロモデルとするものである。可変抵抗101の端子のうちMOSFET102のドレインに接続されない側の端子をマクロモデルのドレイン端子(D)とする。マクロモデルのゲート端子(G)、ソース端子(S)、バックゲート端子(「バルク端子」ともいう)(B)は、それぞれMOSFET102のゲート端子、ソース端子、バックゲート端子(バルク端子)と同一である。このマクロモデルにより、チャネル領域とドレイン電極(高濃度ドレイン拡散層)の間に位置する低濃度ドレイン拡散層が原因となるゲート・ソース間電圧(単に「ゲート電圧」ともいう)とドレイン・ソース間電圧(単に「ドレイン電圧」ともいう)に依存した寄生抵抗成分を表現することができる。

【0004】

図19(B)は、図19(A)における可変抵抗101を、接合型トランジスタ(JFET:Junction FET)103に置き換えたものである。図19(B)のマクロモデルも、図19(A)のマクロモデルと同様の効果を奏する。

【0005】

また、非特許文献1の14章には、チャネル領域とドレイン電極の間に位置する低濃度ドレイン拡散層の寄生抵抗成分をトランジスタモデルのモデル式の中に含ませる技術が開示されている。この場合、図19(A)や図19(B)のマクロモデルは、例えば図19(C)に示すような、単一のMOSFET104により置き換えられる。図19(C)には、図19(A)の可変抵抗101、あるいは図19(B)のJFET103が、モデルの中に予め組み込まれている。このため、MOSFET104のドレインがマクロモデルのドレイン端子(D)とされる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−190328号公報

【特許文献2】特開2001−189449号公報

【特許文献3】特許第3120389号公報

【非特許文献】

【0007】

【非特許文献1】Hiroshima University & STARC、"HiSIM_HV 1.2.0 User's Manual" (2009) [平成23年9月12日検索] <インターネットURL: http://home.hiroshima-u.ac.jp/usdl/HiSIM_HV/C-Code/HiSIM_HV_C.html>

【発明の概要】

【発明が解決しようとする課題】

【0008】

以下に、関連技術の分析を与える。

【0009】

図20に示したレイアウト構造の高耐圧MOSFETに対して、特許文献1や非特許文献1に記載された関連技術を用いても、精度の良い回路シミュレーション用のモデルが得られないことを、本願発明者らは、全く独自に知見した。なお、ソース領域に図20に示したレイアウト構造を備えたトランジスタに関する関連技術として、例えば特許文献2、特許文献3等の記載が参照される。

【0010】

図20に示すように、高耐圧MOSFETは、ソース側に特殊な構造、すなわち、ソース拡散層112(高濃度N+拡散層)と、Pウェル(不図示)に電源電圧を供給するためのウェルコンタクト拡散層(「ウェル電極拡散層」ともいう)111(高濃度P+拡散層)とが、ゲート電極115(シリコン基板上にゲート絶縁膜を介して配置される)のソース領域側の辺に沿って、交互に隣接して配置されたレイアウト構造を備えている。このような高耐圧MOSFETにおいて、図19等を参照して説明したMOSFETモデルを用いた場合、ドレイン電流を、広いバイアス範囲で精度良く求めることはできない(この点については、後に詳細に説明する)。

【0011】

本願発明者らは、その原因を解析・検討した結果、このたび、上記問題点を解決する全く新規なマクロモデルを開発し、該マクロモデルのシミュレーション精度を検証したので、以下に提案する。すなわち、本発明の目的は、ソース領域にソース拡散層とウェルコンタクト拡散層が隣接して配置された構造を備えた高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーション精度を向上させる装置、方法、プログラム、記録媒体を提供することにある。

【課題を解決するための手段】

【0012】

前記課題の少なくとも1つを解決するため、本発明は、概略以下の構成とされる(だたし、以下に限定されるものでないことは勿論である)。

【0013】

本発明の1つの側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルとして、ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、を備え、前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端との接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成する手段と、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶手段と、

前記記憶手段から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子の抵抗値を調整する手段と、を備えたモデル作成装置が提供される。

【0014】

本発明の別の側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルを情報処理装置で作成するにあたり、

ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、

前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、

を備え、

前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端の接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成する処理と、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶装置から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記第1の可変抵抗素子の抵抗値を調整する処理を、

前記情報処理装置に実行させるプログラムが提供される。

【0015】

本発明のさらに別の側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルを情報処理装置で作成するにあたり、

ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、

前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、

を備え、

前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端との接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成し、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶手段から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子の抵抗値を調整する、モデル作成方法が提供される。

【発明の効果】

【0016】

本発明によれば、ソース領域にソース拡散層とウェルコンタクト拡散層が隣接して配置された構造を備えた高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーション精度を向上させることができる。

【図面の簡単な説明】

【0017】

【図1】本発明の概要を説明する図である。

【図2】本発明の第1の実施形態を説明する図である。

【図3】本発明の第1の実施形態を説明する図である。

【図4】本発明の第2の実施形態のシステムを説明する図である。

【図5】本発明の第2の実施形態の動作を説明する図である。

【図6】本発明の原理を説明する図である。

【図7】本発明の効果を説明する図である。

【図8】本発明の効果を説明する図である。

【図9】本発明の第3の実施形態を説明する図である。

【図10】本発明の第3の実施形態を説明する図である。

【図11】本発明の第4の実施形態を説明する図である。

【図12】本発明の第4の実施形態の動作を説明する図である。

【図13】本発明の第2の実施形態を説明する図である。

【図14】本発明の第5の実施形態を説明する図である。

【図15】本発明の第6の実施形態を説明する図である。

【図16】本発明の第6の実施形態を説明する図である。

【図17】本発明の第7の実施形態を説明する図である。

【図18】本発明の第7の実施形態を説明する図である。

【図19】(A)、(B)、(C)は 関連技術を説明する図である。

【図20】関連技術を説明する図である。

【図21】関連技術の問題点を説明する図である。

【図22】関連技術の問題点を説明する図である。

【図23】関連技術の問題点を説明する図である。

【図24】関連技術の問題点を説明する図である。

【発明を実施するための形態】

【0018】

本発明によれば、半導体基板上にゲート絶縁膜を介して配置されるゲート電極を間に挟んで半導体基板表面に対向配置される第1及び第2の拡散領域(diffused region)の一方の前記第1の拡散領域が、第1導電型の第1の拡散層(例えば図2の12)と、前記第1拡散層と逆導電型のウェルコンタクト拡散層(図2の11)とがチャネル幅方向に沿って隣接して配置されたMOSFETの回路シミュレーション用のMOSFETのモデルとして、前記第2の拡散領域(例えば図1のドレイン)同士が共通接続され、ゲート同士が共通接続され、バックゲート同士が共通接続され、前記第1の拡散領域の前記第1の拡散層(図2の12)の幅と前記ウェルコンタクト拡散層(図2の11)の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET(図1の1、2)と、前記第2のMOSFET(図1の2)の前記第1の拡散領域(例えば図1のソース)に一端が接続された第1の可変抵抗素子(図1の3)と、を備え、前記第1のMOSFET(図1の1)の前記第1の拡散領域と、前記第1の可変抵抗素子(図1の3)の他端との接続点を、第1端子(S)とし、前記第1及び第2のMOSFET(図1の1、2)の前記共通接続した前記第2の拡散領域、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、第2端子(D)、ゲート端子(G)、バックゲート端子(B)とするモデルを用いる。モデリング対象の前記高耐圧MOSFETの電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子(図1の3)の抵抗値(Rs)を調整する。

【0019】

以下では、上記した本発明についてその基本原理を説明し、つづいて実施形態を説明する。

【0020】

上記したように、特許文献1、非特許文献1等に記載の関連技術を用いても、図20に示すレイアウト構造のMOSFETに対しては、精度の良い回路シミュレーションモデルが得られないことが、本願発明者らによるこの度の検討から明らかになったので、以下に説明する。

【0021】

図20において、ゲート電極115の左側のソース側には、N+型のソース拡散層112と、P+型のウェルコンタクト拡散層111(P+拡散層)がチャネル幅方向に隣接して配置されている。図20の例では、P+型のウェルコンタクト拡散層(P+拡散層)111、N+型のソース拡散層(N+拡散層)112が交互に隣接して配置されている。図20では、P+型のウェルコンタクト拡散層(P+拡散層)111が3つ、これらの間に、N+型のソース拡散層(N+拡散層)112が2つ配置されている。なお、図20のレイアウト構成はあくまで説明のために簡略化して例示したものであって、P+型のウェルコンタクト拡散層(P+拡散層)111、N+型のソース拡散層(N+拡散層)112の数、配置形態は図20の構成に制限されるものでない。なお、N+型のソース拡散層112とP+型のウェルコンタクト拡散層111は、通常、電気的に接続するように形成される。

【0022】

図20において、ゲート電極115の右側のドレイン側には、ゲート電極115に隣接するN−型の低濃度ドレイン拡散層114と、低濃度ドレイン拡散層114に隣接したN+型のドレイン拡散層113(ドレインコンタクト用のN+拡散層)が設けられる。

【0023】

図20において、ゲート電極115への電圧の印加により、ゲート電極115下部のシリコン基板表面に反転層(チャネル)が形成され、ソースとドレイン間が導通する。

【0024】

なお、図20に示す例では、NチャネルMOSFETはP型ウェル内に形成されているが、NチャネルMOSFETをP型シリコン基板表面に形成する場合、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト(Substrate Contact)拡散層となる。したがって、以下では、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト拡散層であってもよい。ウェルコンタクト拡散層(基板コンタクト拡散層)は、単に、ウェルコンタクト(基板コンタクト)とも呼ばれる。なお、NチャネルMOSFETのP+型のウェルコンタクト拡散層(基板コンタクト)は例えば電源VSS(0V)に接続される。また図20では、NチャネルMOSFETのレイアウト構成を例示したが、PチャネルMOSFETの場合、極性が反転することを除いて同様である。

【0025】

図20において、

Wnは、N+型のソース拡散層112一つ当たりの幅、

Wpは、P+型のウェルコンタクト拡散層111一つ当たりの幅、

Wは全チャネル幅

である。このWは、各ソース拡散層112の幅Wnの総和(=ΣWn)と、各ウェルコンタクト拡散層111の幅Wpの総和(=ΣWp)を加算した値となる(W=ΣWn+ΣWp)。

【0026】

なお、Wnは、ソース領域のすべてのN+型ソース拡散層112について同じ値である場合もあれば、ソース拡散層112毎に異なる場合もある。Wpについても、同様である。すなわち、ソース領域のすべてのP+型ウェルコンタクト拡散層111の幅が同一である場合もあれば、P+型ウェルコンタクト拡散層111毎にその幅が異なる場合もある。

【0027】

また、図20では、P+型ウェルコンタクト拡散層111とN+型ソース拡散層112のゲート電極115とは反対側の端部が面一に整列しているが、必ずしも整列している必要はない。例えば、N+型ソース拡散層112が、ゲート電極115と対向する側と反対側にさらに延在し隣のN+型ソース拡散層112と接続し、間のP+型ウェルコンタクト拡散層111を囲むようにしてもよい。図20に示したレイアウト構造は、P+型ウェルコンタクト拡散層111とN+型ソース拡散層112が接続しているため、「ソース基板接続構造」とも称呼される。

【0028】

図21(A)と図21(B)は、図20の高耐圧MOSFETの異なるWnratioに関して、ドレイン電流−ドレイン電圧特性(Id−Vd特性)をモデリングした結果と、実測値をそれぞれ示す図である(本願発明者らによって為された分析結果)。ここで、Wnratioは、図20の全チャネル幅W(=ΣWn+ΣWp)に対して、各N+型ソース拡散層112の幅Wnの合計(=ΣWn)が占める割合であり、%表記を用いると、以下で与えられる。

【0029】

Wnratio={(ΣWn)/(ΣWn+ΣWp)}×100

【0030】

図21(A)では、Wnratio=48%、図21(B)では、Wnratio=40%としている。なお、図21(A)、(B)において、横軸はドレイン電圧(drain−to−source voltage)Vds(単位:電圧(Voltage))、縦軸はドレイン電流(drain−to−source current)Id(単位:Ampere)であり、ゲート電圧(gate−to−source voltage)Vgsを0〜5Vまで1Vステップで変化させたId−Vd特性曲線が示されている。ゲート・ソース間電圧Vgs=0Vでは、NチャネルMOSFETはオフ状態であり、ドレイン電流Id=0である。

【0031】

図21(A)の例では、▲マークで示した実測値と、破線で示す関連技術によるモデリング結果(従来モデル)とは、ドレイン・ソース間電圧Vdsの全範囲(0〜20V)に亘って、ゲート・ソース間電圧Vgs=0、1、2、・・・、5Vの全てについて、比較的良く一致している。

【0032】

これに対して、同じモデルを、Wnratioが40%の場合の実測値(▲マークで示す)と比較した図21(B)の例では、実測値(▲)と、破線で示すモデルリング結果(従来モデル)とが合っていない。特に、ドレイン電流Idが、ドレイン・ソース間電圧Vdsに依存せずにほぼ一定となる領域のうち、ゲート・ソース間電圧Vgsが高い領域で実測値(▲)との差異が顕著となる。

【0033】

これは、図20に示したレイアウト構成において、Wnratioの値の相違により、MOSFETのドレイン電流−ドレイン・ソース間電圧(Id−Vds)特性が変化していることによるものと思料される。

【0034】

本願発明者らは、図19に示した関連技術のMOSFETモデルに関して、そのモデルパラメータの調整を試みたが、40%と48%というWnratioの値の相違によるドレイン電流−ドレイン・ソース間電圧(Id−Vds)特性の変化を、図19に示したMOSFETモデルによって表現することはできなかった。

【0035】

このようなMOSFETモデル(例えば図19に示したモデル)のフィッティング誤差に対して、本願発明者らは、より詳細な検討を行ったので、以下にその結果を説明する。

【0036】

図22(A)と図22(B)は、図20に示したレイアウト構造のNチャネルMOSFETがオンした状態におけるドレイン・ソース間電流Idsを、Wnratioが異なる素子(MOSFET)間で比較したものである(本願発明者らによって為された分析結果である)。なお、図22において、縦軸は、ドレイン・ソース間電流Idsを全チャネル幅W(=ΣWn+ΣWp)で規格化し、Ids/Wとしている。図22において、横軸の素子(MOSFET)AのWnratioは40%、素子(MOSFET)B、CのWnratioはともに48%である(なお、素子BとCは、Wnratioは共通であるが、別のMOSFETである)。

【0037】

図22(A)及び図22(B)において、マーク●は実測値を表している。また、破線で示す従来モデル(素子A、B、Cと破線との交点)は、例えば図19(A)のMOSFETモデルを用いてそのパラメータ(例えば図19(A)の可変抵抗素子101の抵抗値やその他のパラメータ)のフィティング等を行って得られたMOSFETモデルに対してシミュレーションを行い、Ids/Wを求めたものである。破線は、素子A、B、Cのそれぞれのモデリング結果を直線で結んだ線である(破線…の各ドットがモデリング結果を表しているのではなく、素子A、B、Cと破線との交点が、素子A、B、CのIds/Wである。図22(B)も同様である)。

【0038】

図22(A)に示した線形領域(ドレイン・ソース間電圧Vds=0.1V、ゲート電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●)は、Wnratio=40%の素子Aと、Wnratio=48%の素子B、Cでほぼ等しく、Wnratioにほとんど依存しないことが示されている。また、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果Ids/Wは、図22(A)に示すように、線形領域では、素子AのWnratio=40%、素子B、CのWnratio=48%のいずれの実測値(●)とも交差しており、ほぼ一致していることが分かる。

【0039】

一方、図22(B)に示した飽和領域(ドレイン・ソース間電圧Vds=12V、ゲート・ソース間電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●で示す)は、Wnratioに依存して変化する。すなわち、Wnratio=40%の素子Aでは、Ids/Wの実測値(●で示す)と、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果(破線と素子Aの交差部)とは一致しない(差異がある)。しかしながら、Wnratio=48%の素子B、Cでは、Ids/Wの実測値(●で示す)と、破線と素子B、Cとの交点であるモデリング結果(従来モデル)とはほぼ一致しており、Wnratio=40%の素子Aのような、顕著な差異は認められない。

【0040】

図19等に示した関連技術では、Wnratio依存性は、例えば抵抗成分(図19(A)の可変抵抗101の抵抗値)を調整することにより、全体の電流レベルを上下させることが可能である。

【0041】

しかしながら、図22(A)、図22(B)に見られるように、ドレイン電圧(ドレイン・ソース間電圧)に依存して、ドレイン・ソース間電流Idsに異なるWnratio依存性が現れる、という傾向をうまくモデリングすることはできない。

【0042】

特に、図22(A)及び図22(B)に示したように、

線形領域では、ドレイン・ソース間電流IdsはWnratioに依存せず、

飽和領域でのみ、ドレイン・ソース間電流IdsがWnratioに依存する、

という傾向が認められる。

【0043】

通常の構造のMOSFET(例えば、後述する図3の高耐圧MOSFET参照)においては、線形領域の特性は、素子のレイアウト構造に依存して変化せず、飽和領域の特性だけが、素子のレイアウト構造に依存して変化する、ということはない。

【0044】

線形領域の特性は、素子のレイアウト構造に依存して変化せず、飽和領域の特性だけが素子のレイアウト構造に依存して変化する、ということは、図20に示したレイアウト構造のMOSFETに特有の特性である(本願発明者らによって為された分析結果)。

【0045】

このため、図19(A)乃至(C)に示した関連技術(MOSFETのドレインに接続した可変抵抗)のモデリングで表現することは、著しく、困難である。

【0046】

図23(A)と図23(B)は、それぞれ線形領域と飽和領域で、ドレイン・ソース間電流Idsのゲート・ソース間電圧Vgsによる微分値である相互コンダクタンス

をゲート幅Wで規格化した値Gm/Wを、Wnratio=40%(破線)とWnratio=48%(実線)で比較した結果である(本願発明者らによって為された分析結果である)。

【0047】

図23(A)及び図23(B)において、横軸はゲート・ソース間電圧Vgs(0〜5V)、縦軸はGm/W(実測値)である。なお、Wnratio=40%(破線)とWnratio=48%(実線)の特性極性は、ゲート・ソース間電圧Vgsを0〜5Vの範囲で所定の電圧ステップ(1V以下のステップ、例えば0.25Vステップ)で可変させて実測した複数点のGm/Wをカーブフィッティングして表示したものである。

【0048】

図22(A)に示したドレイン電流Idsの場合と同様に、線形領域Vds=0.1Vでは、Gm/Wは、図23(A)に示すように、Wnratioに依存しない。すなわち、Wnratio=40%(破線)とWnratio=48%(実線)とが、Vgs=0〜5Vの範囲でほぼ一致する(破線と実線がほぼ重なる)。なお、その原因は不明だが、1V<Vgs<1.25V付近の一部区間では差異が現れている。

【0049】

一方、飽和領域Vds=12Vでは、図23(B)に示すように、Gm/Wは、Wnratioに依存する。すなわち、Wnratio=40%(実線)と、Wnratio=48%(破線)とで特性が異なる(1V<Vgs≦5Vの広い範囲で、破線と実線とが重ならない)。

【0050】

この原因について、電気伝導に寄与するキャリアが誘起される領域である反転層(inversion layer)の形成条件に着目して考察した。その結果を、図24(A)及び図24(B)を参照して以下に説明する。

【0051】

図24(A)及び図24(B)のいずれも、モデリング対象とする高耐圧MOSFETのレイアウトを簡略化し模式的に例示したものであり、本願発明者らによって為された分析結果を説明するための図である。図24(A)及び図24(B)において、参照番号117で示す領域は、反転層が形成されない(あるいは、反転層が形成にくい)領域である。

【0052】

図24(A)には、ドレイン・ソース間電圧(ドレイン電圧)Vdsが低く、NチャネルMOSFETが線形領域で動作する場合に、反転層が形成される様子が模式的に例示されている。ゲート電極115へのゲート電圧の印加によって、ゲート電極115下部(ゲート酸化膜直下)のシリコン基板表面付近に誘起される反転層116は、ソースからドレインにかけての電位差が小さいため、ドレイン側まで広がった形状で形成されると考えられる。P+型のウェルコンタクト拡散層111付近では、ゲート電極115下部のシリコン基板表面に反転層は形成されないと考えられる。これを、図24(A)では、反転層が形成されにくい領域117として表している。

【0053】

しかし、図24(A)に示すように、反転層116はゲート電極115下部のドレイン114側の端部まで広い範囲にわたって形成されることから、反転層116の電荷の全体量について考えると、P+型のウェルコンタクト拡散層111近傍で反転層が形成されないことの影響は小さい。

【0054】

したがって、線形領域では、P+型のウェルコンタクト拡散層111の幅の合計(=ΣWp)が全チャネル幅Wに対して占める割合Wpratio(=ΣWp/(ΣWn+ΣWp)×100)がドレイン・ソース間電流Idsに与える影響が小さいと考えられる。

【0055】

また、ソース拡散層であるN+拡散層112の幅の合計(=ΣWn)が全チャネル幅Wに占める割合Wnratio(%表記)は、Wnratio=(100−Wpratio)%であることから、線形領域では、Wnratioが反転層116の全電荷量に与える影響は小さく、Wnratioがドレイン電流Idsに与える影響は小さいと考えられる。このため、線形領域におけるドレイン・ソース間電流−ドレイン・ソース間電圧特性(Ids−Vds特性)やGm/Wは、N+拡散層のチャネル幅の割合Wnratioには依存しない。

【0056】

図24(B)には、ドレイン・ソース間電圧Vdsが高く、NチャネルMOSFETが飽和領域で動作する場合に反転層が形成される様子が模式的に例示されている。飽和領域では、ソースからドレインにかけての電位差が大きく、反転層116はシリコン基板表面の電位が低い領域に形成される性質を持つ。このため、反転層116は、チャネル電位の低いソース近傍だけに形成されるものと思料される(ピンチオフ:ドレイン拡散層とウェル(基板)間のpn接合に逆方向電圧が印加され空乏層が広がり、チャネルが狭くなる)。

【0057】

この場合、P+型のウェルコンタクト拡散層111近傍で反転層が形成されないことが、反転層16全体の電荷量に与える影響が大きくなる。この結果、飽和領域では、N+拡散層112の幅ΣWnの全チャネル幅Wに対する割合Wnratioが、ドレイン電流Idsに与える影響が増すものと思料される。

【0058】

そして、図24(B)に示すように、反転層16は、ゲート電極115直下のシリコン基板表面のソース側の限られた範囲に形成されるため(図24(B)では、反転層116の先端はゲート電極115の中間よりもソース側に近い領域に限られる)、反転層116の全電荷量は、N+拡散層112の幅の合計(=ΣWn)が全チャネル幅Wに占める割合Wnratioの値の相違に敏感である。換言すれば、図24(B)の飽和領域においては、ゲート電極115直下の反転層115のドレイン側の縁とソース側の縁(N+拡散層112)で囲まれる領域の面積における反転層が形成されにくい領域117の占める面積の割合が、図24(A)の線形領域の場合よりも増大し、P+型のウェルコンタクト拡散層111の幅の合計(=ΣWp)が全チャネル幅Wに対して占める割合Wpratioがドレイン・ソース間電流(ドレイン電流)Idsに与える影響が大きくなるものと思料される。

【0059】

図23(A)及び図23(B)に示したような効果(Gm/WのWnratio依存性)は、図19等に示した関連技術のMOSFETモデルでは、一切考慮されていないため、取り扱うことができない。これが、図20の高耐圧MOSFET対して、精度の良い回路シミュレーション用モデルを作成することが困難であることの理由(原因)と考えられる。

【0060】

以上、ソース領域において、ゲート電極の辺に沿って、ソース拡散層112とウェルコンタクト拡散層111が隣接して交互に配置される高耐圧MOSFETにおいて、ソース拡散層112とウェルコンタクト拡散層111の幅の割合(Wnratio)に依存して変化する電気特性の特徴を表現できる回路シミュレーション用のMOSFETモデルが存在せず、このため、その実現の必要性を説明した。

【0061】

すなわち、飽和領域では、ドレイン・ソース間電流IdsのWnratio依存性が大きく、線形領域では,ドレイン・ソース間電流IdsのWnratio依存性が小さい,という特徴を表現できる回路シミュレーション用のMOSFETのモデルの実現が必要である。

【0062】

そして、MOSFETのモデルとしては、これらの電気的特性の特徴をできるだけ、少数のモデリングパラメータを用いて表現することができるMOSFETモデルの実現が望ましい。

【0063】

さらに、回路シミュレーション用のMOSFETモデルに対して、回路シミュレータに、Wnratioの値を受け渡す仕組み、あるいは、MOSFETモデル内においてWnratioの値を決定するための仕組みが望まれる。

【0064】

また、これらの特徴を表現するMOSFETモデルの抽出するための手順を確立することも望まれる。

【0065】

特に、モデル抽出に用いるTEG(Test Element Group:評価用ウェハ)の構造、抽出アルゴリズム、抽出ツールを含めた形でモデル抽出の手順が確立されることが望まれる。

【0066】

本発明によれば、ソース領域において、ソースの拡散層(NチャネルMOSFETの場合、N+拡散層、PチャネルMOSFETの場合、P+拡散層)と、ウェルコンタクト拡散層(NチャネルMOSFETの場合、P+層、PチャネルMOSFETの場合、N+層)が互いに隣接して交互に配置されたLDMOS(Laterally Diffused MOS)構造(横方向拡散MOS構造)を有する高耐圧MOSFET(横型パワーMOSトランジスタ)の回路シミュレーション用のモデル、該モデルの作成方法、及びモデル作成装置が提供される。

【0067】

図1(A)は、本発明の一つの形態による高耐圧MOSFET(NチャネルMOSFET)のマクロモデルの構成を示す図である。図1(A)に示すように、第1のMOSFET(1)、第2のMOSFET(2)、可変抵抗素子(3)から構成され、第1のMOSFET(1)のドレイン、ゲート、バックゲート(バルク)をそれぞれ第2のMOSFET(2)のドレイン、ゲート、バックゲート(バルク)に接続して、それぞれ、高耐圧MOSFETマクロモデルのドレイン端子D、ゲート端子G、バックゲート(バルク)端子Bとし、第2のMOSFET(2)のソースに可変抵抗素子(3)の一端を接続し、該可変抵抗素子(3)の他端を、第1のMOSFET(1)のソースと並列に前記高耐圧MOSFETマクロモデルのソース端子Sへ接続する。特に制限されないが、第1のMOSFET(1)、第2のMOSFET(2)は、ともにNチャネルMOSFETである。

【0068】

第1のMOSFET(1)のチャネル幅は、モデリング対象の高耐圧MOSFETのソース領域のN+拡散層12の幅Wn(図2参照)の総和(=ΣWn)とし、

第2のMOSFET(2)のチャネル幅は、モデリング対象の高耐圧MOSFETのソース領域のP+拡散層11の幅Wp(図2参照)の総和(=ΣWp)とする。

【0069】

第2のMOSFET(2)のソースに接続する可変抵抗素子(3)は、ウェルコンタクト拡散層(図2の11;P+拡散層)近傍の寄生抵抗成分が、高耐圧MOSFETのドレイン電流(ドレイン・ソース間電流)に与える影響を表現するための等価抵抗である。

【0070】

図1(A)の可変抵抗素子(3)の抵抗値Rsは、典型的には、図1(B)に示すようなゲート電圧(ゲート・ソース間電圧)Vgの依存性と、ドレイン電圧(ドレイン・ソース間電圧)Vdの依存性を反映するように、設定される。なお、ソースがGND(グランド電位)の場合、ゲート・ソース間電圧はゲート電圧と等しく、ドレイン・ソース間電圧はドレイン電圧と等しいことから、単に、ゲート電圧、ドレイン電圧ともいう。図1(B)の横軸はドレイン電圧、縦軸は可変抵抗素子(3)の抵抗値Rsである。図1(B)には、ゲート電圧一定の条件でのRs−Vd特性が、いくつかの異なるゲート電圧Vgに対してプロットされている。

【0071】

図1(B)に示すように、可変抵抗素子(3)の抵抗値Rsのバイアス依存性は、

・ドレイン電圧Vdの増加に伴い増加する第1の領域4と、

・抵抗値Rsがドレイン電圧に依存しない第2の領域5と、

の二つの領域からなる。

【0072】

図1(A)のMOSFETのモデルにおいて、第1の領域4と第2の領域5の境界で、抵抗値Rsが滑らかに接続されるように設定する。

【0073】

また、図1(A)のMOSFETのモデルにおいて、可変抵抗素子(3)の抵抗値Rsは、ゲート電圧Vgの上昇とともに、低下するように設定する。すなわち、ドレイン電圧Vdが一定の場合、ゲート電圧Vgが高くなるほど、可変抵抗素子(3)の抵抗値Rsは小さくなる。

【0074】

第1のMOSFET(1)及び第2のMOSFET(2)には、ソース領域がすべてN+拡散層12(ソース拡散層)からなる、通常構造の高耐圧MOSFET7(図3参照)に対して、抽出したモデルパラメータをそのまま、あるいは若干の修正を加えて適用する。

【0075】

なお、上記では、NチャネルMOSFETについて説明したが、PチャネルMOSFETについても、極性を反転させることで、本発明を適用することができる。

【0076】

本発明によれば、簡易かつ明確な手順に基づいて、ソース基板接続型の高耐圧MOSFETの特性を正確に表現する回路シミュレーションモデルを得ることができる。以下、いくつかの実施形態について説明する。

【0077】

<実施形態1>

図1は、本発明の実施形態1を説明する図である。図1(A)には、高耐圧MOSFETの回路シミュレーション用マクロモデルの等価回路が示されている。図1(A)において、

参照符号Dは高耐圧MOSFETシミュレーション用マクロモデルのドレイン端子、

参照符号Gは前記マクロモデルのゲート端子、

参照符号Sは前記マクロモデルのソース端子、

参照符号Bは前記マクロモデルのバックゲート(バルク)端子である。

【0078】

図1(B)に示すように、MOSFETマクロモデルは、第1のMOSFET(1)、第2のMOSFET(2)、可変抵抗素子(3)から構成され、第1のMOSFET(1)のドレイン、ゲート、バックゲート(バルク)を、第2のMOSFET(2)のドレイン、ゲート、バックゲート(バルク)にそれぞれ共通接続し、それぞれ、高耐圧MOSFETマクロモデルのドレイン端子、ゲート端子、バックゲート(バルク)端子とし、第2のMOSFET(2)のソースに可変抵抗素子(3)の一端を接続し、可変抵抗素子(3)の他端を第1のMOSFET(1)のソースとともに、高耐圧MOSFETマクロモデルのソース端子へ接続している。

【0079】

可変抵抗素子(3)は、モデリング対象の高耐圧マクロモデルのバイアス依存性、例えば、ゲート・ソース間電圧依存性(ゲート電圧依存性)とドレイン・ソース間電圧依存性(ドレイン電圧依存性)を有する。

【0080】

図2は、実施形態1のマクロモデルに対応する高耐圧NチャネルMOSFETのレイアウトを模式的に示す図である。図2において、11はソース領域のウェルコンタクト拡散層(P+拡散層)、12はソース拡散層(N+拡散層)、13はドレイン領域のN+拡散層(ドレインコンタクト用N+拡散層)、14はドレインのN−拡散層、15はゲート電極(シリコン基板上のゲート絶縁膜の上に形成されている)である。なお、N+拡散層は高濃度のN型拡散層、N−拡散層は低濃度のN型拡散層、P+拡散層は高濃度のP型拡散層をそれぞれ表している。

【0081】

なお、図2において、Nチャネル型のMOSFETは、P型ウェル内に形成されているが、例えばNチャネルMOSFETをP型シリコン基板表面に形成する場合、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト拡散層となる。この場合、ウェルコンタクトを基板コンタクトと読み替えることで、以下の実施形態がそのまま適用される。

【0082】

高耐圧化のため、シリコン半導体基板表面において、ドレイン側のN+拡散層13とゲート電極15の間に低濃度N−拡散層14が配置されている。ソース側は、P+型のウェルコンタクト拡散層(P+拡散層)11とN+型のソース拡散層(N+拡散層)12が、一定の間隔で交互に配置された構造とされている。図2に例示したソース側の構造を、図20と同様に、「ソース基板接続構造」という。ソース領域の複数のウェルコンタクト拡散層(P+拡散層)11はバックゲート端子(B)に共通に接続され、複数のソース拡散層(N+拡散層)12はソース端子(S)に共通に接続され、ドレイン領域のN+拡散層13(ドレインコンタクト)はドレイン端子(D)に接続されている。

【0083】

図1(A)のMOSFETモデルにおいて、第1のMOSFET(1)のチャネル幅は、図2のソース領域のN+拡散層12の幅Wnの総和(=ΣWn)とし、第2のMOSFET(2)のチャネル幅は図2のソース領域のP+拡散層11(ウェルコンタクト)の幅Wpの総和(=ΣWp)とする。

【0084】

図1(A)のMOSFETモデルにおいて、可変抵抗素子(3)の抵抗値Rsは、図1(B)に示すように、ゲート電圧(ゲート・ソース間電圧)Vgの依存性と、ドレイン電圧(ドレイン・ソース間電圧)Vdの依存性を反映するように、設定される。すなわち、可変抵抗素子3の抵抗値Rsは、図1(B)に示すように、可変抵抗素子(3)の抵抗値Rsがドレイン電圧Vdに依存する第1の領域4と、可変抵抗素子(3)の抵抗値Rsがドレイン電圧Vdに依存しない第2の領域5を有し、第1の領域4と第2に領域5の境界で滑らかに接続されるように設定される。

【0085】

また、可変抵抗素子3の抵抗値Rsは、図1(B)に示すように、ゲート電圧Vgの上昇(低下)とともに、低下(上昇)するという特性を反映するように設定される。

【0086】

図3は、実施形態1のマクロモデル内の第1のMOSFET(1)及び第2のMOSFET(2)のモデルパラメータの初期値を抽出するために使用する通常構造の高耐圧MOSFETのレイアウトを模式的に示す図である。

【0087】

図3に示すように、通常構造7のレイアウトは、図2のソース基板接続構造6とは、ソース側の構造が異なり、ソースはN+拡散層12(チャネル幅=W)のみとなり、ウェルコンタクト層(P+拡散層)11は、N+拡散層12のゲート電極15に対向する側と反対側の領域に配置されている。

【0088】

<実施形態2>

次に、本発明の第2の実施形態を説明する。図4は、図1及び図2を参照して説明した前記実施形態1のMOSFETモデル(「マクロモデル」という)を作成するための第2の実施形態2に係るモデル作成装置の構成を示す図である。

【0089】

図4において、ウェファ21として、図2のソース基板接続構造6と、図3の通常構造7の2種類のレイアウトパターンのMOSFETを搭載したものを用意する。

【0090】

電気特性測定装置22で、ウェファ21上のソース基板接続構造の高耐圧MOSFET(図2)と、通常構造の高耐圧MOSFET(図3)のId−Vg特性(ドレイン電流−ゲート電圧特性)やId−Vd特性(ドレイン電流−ドレイン電圧特性)等の電気特性を測定する。

【0091】

記録媒体23は、ソース基板接続構造と通常構造の電気特性データ41/42、MOSFET抽出プログラム43、MOSFETモデル44、マクロモデル抽出プログラム45、マクロモデル48、モデル検証プログラム49等を記録する。なお、記録媒体23は、記録媒体を備えた記憶装置(例えばHDD(Hard Disk Drive)等の磁気ディスク記憶装置、あるいはDVD(Digital Versatile Disk)等の光ディスク記憶装置等)であってもよいことは勿論である。

【0092】

情報処理装置24は、記録媒体23から、各種測定データや各種モデルを読み込み、モデル抽出やモデル検証等の処理を行う装置である。特に制限されないが、情報処理装置24において、本実施形態で作製されたマクロモデルを用いて、例えばSPICE系シミュレータ等による回路シミュレーション等を実行してもよい。あるいは、他の情報処理装置で回路シミュレーションを実行してもよい。

【0093】

図5は、図4に示した装置によるマクロモデル作成の手順を示すフローチャートである。図4及び図5を参照して、実施形態1におえるマクロモデルの作成処理を説明する。

【0094】

処理31において、電気特性測定装置22を用いて、ウェファ21の電気特性を測定し、記録媒体23に電気特性データを格納する。この時、ソース基板接続構造の高耐圧MOSFETと通常構造の高耐圧MOSFETの2種類に関して、モデル抽出に必要な電気特性(ドレイン電流−ゲート電圧特性(Id−Vg特性)、ドレイン電流−ドレイン電圧特性(Id−Vd特性)等)を測定し、電気特性データ41、42(通常構造電気特性データ、ソース基板接続構造電気特性データ)を格納する。

【0095】

次に、処理32において、記録媒体23の電気特性データと、MOSFET抽出プログラム43を情報処理装置24に読み込み、情報処理装置24でMOSFET抽出プログラム43を実行することで、通常構造の高耐圧MOSFETモデルを作成し、記録媒体23のMOSFETモデル44に格納する。この時に使用するMOSFETモデルは、ドレイン抵抗のバイアス依存性を表現することができる高耐圧専用モデル(HiSIM_HV:Hiroshima University Starc IGFET Model High Voltage/large current)等、図19(C)参照)を用い、また、ドレイン電流のチャネル長Lの依存性もある程度合わせておく。

【0096】

次に、処理33において、記録媒体23のMOSFETモデル44とマクロモデル抽出プログラム45を情報処理装置24に読み込み、マクロモデル抽出プログラム45を実行することで、図1(A)に示した、ソース基板接続構造の高耐圧MOSFETのマクロモデルを作成し、記憶媒体23にマクロモデル48として格納する。この時、MOSFETモデル(図4の44)の中身は変更せずに、図1(A)の可変抵抗素子3のみを調整する。すなわち、可変抵抗素子3には、ゲート電圧Vg依存性とドレイン電圧Vd依存性を取り入れる。

【0097】

次に、処理34において、ソース基板接続構造の高耐圧MOSFETのマクロモデル48を再調整する(必要に応じて記録媒体23のマクロモデル48とマクロモデル抽出プログラム45を情報処理装置24に読み込む)。処理34では、特に、MOSFETのドレイン抵抗に関するパラメータに注目して調整する。図1(A)では、ドレイン抵抗((図19(A)の可変抵抗素子101参照)に関するパラメータは、モデルに組み込まれており、処理34では、このドレイン抵抗に関するパラメータを調整する。

【0098】

次に、処理35において、記録媒体23のマクロモデル48とモデル検証プログラム49を情報処理装置24に読み込み、モデル検証プログラム49を実行することで、マクロモデル48の検証を行う。

【0099】

次に、処理36において、モデル検証プログラム49で実行されたマクロモデルの検証結果を判断し(例えば情報処理装置24の出力装置に出力されたマクロモデルの検証結果を見てユーザが判断してもよいし、情報処理装置24で自動で判断してもよい)、問題がなければ終了し(処理36のOK分岐)、問題がある場合には(処理36のNG分岐)、処理34へ戻り、処理36での検証結果がOKになるまで繰り返す。

【0100】

次に、図13を参照して、図4に示した実施形態2の装置によるマクロモデルの作成手順を詳細に説明する。

【0101】

電気特性測定装置22を用いて、ウェファ21に搭載されたソース基板接続構造の高耐圧MOSFET(図2)と通常構造の高耐圧MOSFET(図3)の2種類のパターンの電気特性を測定する。通常構造の高耐圧MOSFET(図3)とソース基板接続構造の高耐圧MOSFET(図2)の測定データは、通常構造電気特性データ41、ソース基板接続構造電気特性データ42として、それぞれ記録媒体(図4の23)に格納する。

【0102】

次に、情報処理装置24(図4)は、MOSFET抽出プログラム43を用いて、通常構造電気特性データ41を読み込み、MOSFETの閾値電圧やドレイン電流特性(例えばId−Vg特性、Id−Vd特性)が、前記通常構造電気特性データ41と一致するようにモデル抽出を行い、MOSFETモデル44として、記録媒体(図4の23)へ格納する。

【0103】

MOSFETモデルは、ドレイン抵抗のバイアス依存性が表現できる高耐圧専用モデル(HiSIM_HV等、図19(C)参照)を用い、ドレイン電流のチャネル長依存性もある程度合わせておく。

【0104】

次に、情報処理装置24(図4)は、マクロモデル抽出プログラム45を用いて、記録媒体23(図4)から、MOSFETモデル44とソース基板接続構造電気特性データ42を読み込み、ソース基板接続構造のマクロモデルを作成し、MOSFETの閾値電圧やドレイン電流特性(例えばId−Vg特性、Id−Vd特性)が、ソース基板接続構造電気特性データ42と一致するように、モデル抽出を行い、仮マクロモデル46として、記録媒体へ格納する。

【0105】

この時、情報処理装置24(図4)のマクロモデル抽出プログラム45は、MOSFETモデル44の中身は変更せずに、可変抵抗素子3のみを調整する。

【0106】

可変抵抗素子3の抵抗値Rsは、ゲート電圧Vg依存性とドレイン電圧Vd依存性を組み込む。その一例を以下に示す。

【0107】

Rs' = (Rs0 + Rs1 * Vg + Rs2 * Vg2)/W (1)

【0108】

Rs = Rs' * (f(Vd,δ)* 0.5 + 0.5) (2)

【0109】

f(Vd,δ) = (Vg - 0.5 * (Vg - Vd -δ + sqrt((Vg - Vd -δ)2 + 4 *δ*Vg)))/Vg (3)

【0110】

δ = 0.01 (4)

【0111】

ここで、Vgはゲート電圧(ゲート・ソース間電圧)、Vdはドレイン電圧(ドレイン・ソース間電圧)である。また、Wは全チャネル幅(W=ΣWn+ΣWp)である。Rsは可変抵抗素子3の抵抗値である。

【0112】

また式(3)の関数f(Vd,δ)は、スムージング関数であり、座標(Vd,f(Vd))において、原点(0,0)を通る傾き1/Vgの直線(0≦Vd<Vg)と、Vd>Vgでf(Vd)=1となり、ドレイン電圧Vd=Vg前後で滑らかに接続する。δの値を大きくすると、Vd=Vg近辺で緩やかに変化する。

【0113】

したがって、式(2)のRs(可変抵抗素子3の抵抗値)は、Vd=0でRs、0<Vd<Vgで傾き1/Vgの直線、Vd>Vgで、Rs'となり、Vd=Vg前後で滑らかに接続する。

【0114】

また、可変抵抗素子3の別の例を次式(1')〜(3')に示す。

【0115】

Rs = ((Rs0 + Rs1 * Vg + Rs2 * Vg2 ) * f (Vd) + Rs3)/W (1')

【0116】

f (Vd,δ) = (Vdsat - 0.5 * (Vdsat-Vd-δ + ((Vdsat-Vd-δ)2 + 4*δ*Vdsat)0.5 ))/Vdsat (2')

【0117】

Vdsat = (Vg - Vt) fac1/fac2 (3')

【0118】

式(3')の飽和ドレイン電圧Vdsatにおけるパラメータfac1 と fac2はドリフト抵抗での電圧ドロップの影響により生じる、測定される見かけの飽和電圧と、MOSFET(トランジスタ)内のピンチオフ電圧の差を補正するためのフィッティングパラメータである。VtはMOSFETの閾値電圧である。MOSFETのピンチオフ電圧は、ドリフト領域の有無に余り依存しないが、高耐圧MOSFETではドリフト領域寄生抵抗による電圧降下により、この電圧降下がない場合に比べて、見かけ上高い電圧でMOSFETのピンチオフが起こることを補正するものである。この補正は、ゲート長が短いトランジスタの場合に特に必要となる。

【0119】

次に、情報処理装置24(図4)は、マクロモデル調整プログラム47を用いて、記録媒体23(図4)から、仮マクロモデル46と、ソース基板接続構造電気特性データ42を読み込み、特にId−Vd特性の線形領域と飽和領域の境界付近が合うように、仮マクロモデル46内のMOSFETモデルのドレイン抵抗関係のパラメータを調整し、マクロモデル48として記録媒体23(図4)へ格納する。

【0120】

次に、情報処理装置24(図4)は、マクロモデル検証プログラム49を用いて、記録媒体23(図4)から、マクロモデル48とソース基板接続構造電気特性データ42を読み込み、マクロモデルの検証を行う。

【0121】

ここでは、様々なチャネル長、チャネル幅の測定データに対して、電気特性の一致精度及び、チャネル長依存性、チャネル幅依存性を検証し、その結果を、マクロモデル検証結果50として記録媒体23(図4)へ格納する。

【0122】

次に、マクロモデル検証結果50を判断し、問題がなければ、前記マクロモデル48を最終結果として終了し、問題ある場合には、マクロモデル調整処理(前記マクロモデル調整プログラム47)へ戻り、検証結果がOK(可)となるまで繰り返す。この時の入力データは、仮マクロモデル46の代わりに、記録媒体23(図4)からマクロモデル48を読み込む。

【0123】

実施形態1、2の作用効果について説明する。

【0124】

モデル対象のソース基板接続構造を有する高耐圧MOSFETにおいて、

N+拡散層(図2の12)に隣接する領域の電流を、第1のMOSFET(図1の1)で表わし、

P+拡散層(ウェルコンタクト拡散層、図2の11)に隣接する領域の電流を可変抵抗素子(図1の3)と第2のMOSFET(図1の2)の直列接続回路によって表わし、

N+拡散層(図2の12)のチャネル幅Wn(総和)と、P+拡散層(ウェルコンタクト拡散層、図2の11)のチャネル幅Wp(総和)を、それぞれ、第1のMOSFET1のチャネル幅と、第2のMOSFET2のチャネル幅としてマクロモデルに取り入れることにより、N+拡散層(図2の12)とP+拡散層(図2の11)のチャネル幅の割合(例えばWnratio=ΣWn/(ΣWn+ΣWp))に依存して変化するMOSFETの特性を、高精度にフィッティングすることができた。

【0125】

ソース基板接続構造の高耐圧MOSFETに特有のP+拡散層(ウェルコンタクト拡散層、図2の11)近傍でのバイアスに依存したキャリアの流れについては、高耐圧MOSFETのドレイン・ソース間電流Idsに与える影響を表現することができる等価抵抗を、可変抵抗素子3(図1参照)として、第2のMOSFET(2)のソースに直列に接続することで解決した。

【0126】

ソース基板接続構造の高耐圧MOSFETでは、図24(A)及び図24(B)を参照して説明したように、P+拡散層111(ウェルコンタクト拡散層)近傍のチャネル領域では、反転層116が形成されにくいため(領域117参照)、見かけ上、抵抗が付加された形となり、しかも、P+拡散層11の近傍は、ゲート電極115で覆われているので、この抵抗値は、ゲート電圧(ゲート・ソース間電圧)Vgs依存性を持つことになる。

【0127】

本実施形態では、P+拡散層(図2の11)近傍の抵抗成分(寄生抵抗)を、抵抗値Rsがゲート・ソース間電圧Vgsに依存する抵抗(図1の可変抵抗素子3)で表現している。より具体的には、ゲート・ソース間電圧Vgsが高いときは、ゲート・ソース間電圧Vgsが低い場合に比べ、P+拡散層11(図2の11)の周囲のチャネル領域には、相対的に、反転層が形成され易くなり、寄生抵抗の抵抗値は低下すると考えられる。このことから、寄生抵抗は、ゲート・ソース間電圧Vgsが高くなると、その抵抗値が下がるようなゲート・ソース間電圧Vgs依存性を持たせた(図1(B)のRs参照)。

【0128】

また、ソース基板接続構造の高耐圧MOSFETに特有の特性(図22乃至図24、及びそれらの関連説明参照)を表現するため、可変抵抗素子3(図1参照)に、ドレイン・ソース間電圧(ドレイン電圧)Vds依存性を持たせた。その典型的な形態について、図6を参照して説明する。

【0129】

図6(A)は、図2のレイアウト構造のMOSFETのゲート電極15直下のシリコン半導体基板表面に形成されるチャネルを模式的に等価回路で示した図である。図6(B)は、図6(A)の可変抵抗素子3の抵抗値Rsのドレイン・ソース間電圧(ドレイン電圧)依存特性を示す図であり、横軸はドレイン電圧、縦軸は可変抵抗素子3の抵抗値Rsである。

【0130】

図6(A)に示すように、ソース領域のN+拡散層12とドレイン(低濃度ドレイン拡散層(N−拡散層)14、ドレイン拡散層(N+拡散層)13)間には、図1の第1のMOSFET1が接続され、ウェルコンタクト拡散層であるP+拡散層11とドレイン(14、13)間には、図1の第2のMOSFET2が接続され、第2のMOSFET2のソースとP+拡散層11(図1の端子S)間には、抵抗値Rsが可変の可変抵抗素子3が接続されている。図6(A)では、第1のMOSFET1がドレインとN+拡散層12間に2個、第2のMOSFET2と可変抵抗素子3の直列回路がドレインとP+拡散層11間に3組、並列に接続されている。これら第1、第2のMOSFET1、2(計5個)のゲートは共通接続され、MOSFETモデルのゲート端子(図1のG)に接続され、ドレインは共通接続され、MOSFETモデルのドレイン端子(図1のD)に接続される。2個のN+拡散層11は共通接続され、MOSFETモデルのソース端子(図1のS)に接続され、3個のP+拡散層11は共通接続され、MOSFETモデルのバックゲート(バルク)端子(図1のB)に接続される。

【0131】

図6(B)において、可変抵抗素子3の抵抗値Rsのドレイン電圧依存性は、抵抗値Rsがドレイン電圧Vdの増加に伴い増加する第1の領域4と、抵抗値Rsがドレイン電圧Vdに依存しない第2の領域5の二つの領域から構成される。

【0132】

より典型的には、第1の領域4と第2の領域5の境界では、式(3)のスムージング関数f(Vd,δ)により、抵抗値Rsが滑らかに接続されるように構成される。

【0133】

また、より典型的には、第1の領域4と第2の領域5の境界は、モデリング対象とする高耐圧MOSFETの線形領域と飽和領域の境界、あるいは、その付近に設定される。これは、図24(A)に示すように、ドレイン電圧Vdの低い領域(線形領域)では、P+拡散層111の存在がドレイン電流Id(ドレイン・ソース間電流Ids)に与える影響が小さく、図24(B)に示すように、ドレイン電圧Vdの高い領域(飽和領域)では、P+拡散層111の存在がドレイン電流Id(ドレイン・ソース間電流Ids)に与える影響が大きい、ことを表現したものである。

【0134】

本実施形態によれば、以上の作用によって、ソース基板接続構造を持つ高耐圧MOSFETに特有のバイアス電圧依存性を高精度に表現することができた。

【0135】

また、図6(A)において、P+拡散層11に隣接する反転層が充分に形成されない領域(図24(A)、(B)の117)がドレイン電流Idに与える影響を、ドレイン電圧Vd及びゲート電圧Vgに依存する可変抵抗素子3によって表現する。このため、マクロモデル作成にあたり、追加が必要なパラメータは、可変抵抗素子3に係わる少数のパラメータ(例えば式(1)のRs0、Rs1、Rs2等)である。

【0136】

すなわち、本実施形態によれば、MOSFETモデルの調整や改良を行った場合に予想されるフィッティング対象パラメータの大きな増大はなく、フィッティング方法が確立されている通常構造の高耐圧MOSFETモデルを起点に、可変抵抗素子3に関する少数のモデリングパラメータ(式(1)、(2)等のRs0、Rs1、Rs2等)をフィッティングすることにより、精度の良いマクロモデルを形成することができた。

【0137】

また、本実施形態のマクロモデルの構成によれば、回路シミュレーションの実行にあたり、MOSFETモデルに対して、

Wnratioの値をインスタンスパラメータ(インスタンス名で特定される素子に設定するパラメータ)として受け渡す、あるいは、

図2、図6のN+拡散層12とP+拡散層11のそれぞれに対応するチャネル幅Wn、Wpを受け渡す、あるいは、

モデル内においてチャネル幅Wの関数としてWnratioの値を計算する、

ことにより、マクロモデル内において用いるWnratioの値を特定することができる。

【0138】

また、ソース領域が全てN+拡散層12により形成される通常構造の高耐圧MOSFET(図3参照)の特性測定パターンを用意して電気特性の測定を行い、その測定結果に基づき通常構造の高耐圧MOSFETモデルを一旦作成したあと、通常構造の高耐圧MOSFETモデルと可変抵抗素子3により構成される高耐圧MOSFETモデルのマクロモデルを作成し、可変抵抗素子3の少数のパラメータを調整するという、簡易で、手順が明確な方法により、回路シミュレーション用のモデルを作成することができる。

【0139】

なお、本実施形態では、図6(B)に示すように、可変抵抗素子3を、抵抗値がドレイン電圧Vdの増加に伴い増加する第1の領域4と、抵抗値がドレイン電圧に依存しない第2の領域5の二つの領域から構成される例を示したが、精度に対する要求が低い場合は、単一の領域からなるモデルで可変抵抗素子3を表現しても良い。但し、モデルの精度が要求される場合には、前記の通り二つの領域からなるモデル、あるいは、以下に実施形態4で説明するように、三つ以上の領域からなるモデルで、可変抵抗素子3を表現することが好ましい。

【0140】

可変抵抗素子3のモデルにおける、第1の領域4と第2の領域5の境界は、例えば、モデル対象とするMOSFETの線形領域と飽和領域の境界付近のドレイン電圧Vdを選択する。あるいは、モデル対象とするMOSFETの線形領域と飽和領域の境界よりも高めのドレイン電圧Vd、典型的には、線形領域と飽和領域の境界となるドレイン電圧Vdの1〜2.5倍程度の値としてもよい。なお、MOSFETの線形領域と飽和領域の境界のドレイン電圧は、「飽和電圧」と呼ばれる。

【0141】

なお、上記実施形態1、2においては、NチャネルMOSFETについて記載したが、PチャネルMOSFETについても実施形態1の極性を反転させることで、同様にして本発明を適用することができる(PチャネルMOSFETではソース端子電圧がドレイン端子電圧よりも高電圧とされ、ゲート・ソース間電圧Vgsは負値又は0となる)。

【0142】

図7(A)と図7(B)は、本実施形態による高耐圧MOSFETについて、異なるWnratioに関して、ドレイン電流−ドレイン電圧特性(Id−Vd特性)をモデリングした結果(実線)と、実測値(▲)と、図19の従来モデル(破線、図21に対応)を比較して示す図である。ここで、Wnratioは、図2の全チャネル幅W(=ΣWn+ΣWp)に対して、各N+型ソース拡散層(N+拡散層)12の幅Wnの合計ΣWnが占める割合(%表記)である。

【0143】

Wnratio={(ΣWn)/(ΣWn+ΣWp)}×100

【0144】

図7(A)では、Wnratio=48%、図7(B)では、Wnratio=40%としている。なお、図7(A)、図7(B)において、横軸はドレイン電圧(drain−to−source voltage)Vds(単位:Voltage)、縦軸はドレイン電流(drain−to−source current)Id(単位:Ampere)であり、ゲート電圧(gate−to−source voltage)Vgsを0〜5Vまで1Vステップで変化させたId−Vdカーブが示されている。Vgs=0Vでは、MOSFETはオフ状態であり、ドレイン電流Id=0である。

【0145】

図7(A)では、▲マークで示した実測値と、実線で示す実施形態と、破線で示す関連技術によるモデリング結果(従来モデル)とは、Vdsの全範囲、ゲート・ソース間電圧(ゲート電圧)Vgs=0、1、2、・・・、5Vの全てについて、比較的良く一致している。

【0146】

図7(B)では、実測値(▲)と、実線で示す実施形態のモデルリング結果とは、線形領域、及び、飽和領域のいずれについてもほぼ一致している。

【0147】

一方、図7(B)において、破線で示す従来モデルでは、飽和領域で一致しない(特に、飽和領域のうち、ゲート電圧Vgsが高い領域で実測値(▲)との差異が顕著となる)。

【0148】

図8(A)と図8(B)は、NチャネルMOSFETがオンした状態におけるドレイン電流(ドレイン・ソース間電流)Idsを、Wnratioが異なる素子(MOSFET)間で比較したものである。なお、図8において、縦軸のドレイン電流は全チャネル幅Wで規格化し、Ids/Wとしている。横軸の素子(MOSFET)AのWnratioは40%、素子(MOSFET)B、CのWnratioは48%である(なお、素子BとCは、Wnratioは共通であるが、別のMOSFETである)。図8(A)に示すように、実線で示す本発明の実施形態と、●で示す実測値とはほぼ一致している(破線で示す従来モデルもほぼ一致している)。

【0149】

図8(A)に示した線形領域(ドレイン・ソース間電圧Vds=0.1V、ゲート電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●)は、Wnratio=40%の素子Aと、Wnratio=48%の素子B、Cでほぼ略等しく、Wnratioにほとんど依存しない。また図2、図6に示した実施形態を用いたモデリング結果Ids/Wは、図8(A)に示すように、線形領域では、素子AのWnratio=40%、素子B、CのWnratio=48%のいずれの実測値(●)とも交差しており、ほぼ一致していることが分かる。なお、図22(A)を参照して説明したように、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果Ids/Wは、図8(A)に示すように、線形領域では、Wnratio=40%の素子A、Wnratio=48%の素子B、Cのいずれの実測値(●)とも交差しており、ほぼ一致している。

【0150】

図8(B)に示した飽和領域(ドレイン・ソース間電圧Vds=12V、ゲート電圧Vg=5V)では、全チャネル幅W(=ΣWn+ΣWp)で規格化したドレイン電流Ids/Wの実測値(●で示す)は、Wnratioに依存して変化する。

【0151】

図8(B)に示した飽和領域において、Wnratio=40%の素子Aでは、Ids/Wの実測値(●で示す)と、図2、図6に示した実施形態を用いたモデリング結果Ids/Wは一致している。一方、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果(破線と素子Aの交差部)では、Ids/Wは、Wnratio=40%の素子Aに関して、実測値との差異が顕著である。

【0152】

なお、図8(B)において、Wnratio=48%の素子B、Cについても、実施形態(実線)は実測値(●)と一致している。なお、破線で示す従来モデルも、Wnratio=48%の素子B、Cについて、実測値(●)とほぼ一致している。

【0153】

<実施形態3>

図9は、本発明の実施形態3において、高耐圧MOSFETの回路シミュレーション用マクロモデルを等価回路で示す図である。

【0154】

図9において、

参照符号Dは、高耐圧MOSFETシミュレーション用マクロモデルのドレイン端子、

参照符号Gは、該マクロモデルのゲート端子、

参照符号Sは、該記マクロモデルのソース端子、

参照符号Bは、該マクロモデルのウェル端子

である。

【0155】

図9を参照すると、このマクロモデルは、

第1のMOSFET(151)、

第2のMOSFET(152)、

第1の可変抵抗素子(153)、

第2の可変抵抗素子(154)、

第3の可変抵抗素子(155)

から構成されている。

【0156】

第1のMOSFET(151)のゲート、バルク(バックゲート)を第2のMOSFET(152)のゲート、バルクにそれぞれ共通接続し、それぞれ高耐圧MOSFETマクロモデルのゲート端子(G)、バルク端子(B)としている。

【0157】

第1のMOSFET(151)のドレインに第1の可変抵抗素子(153)の一端を接続し、第2のMOSFET(152)のドレインに第2の可変抵抗素子(154)の一端を接続し、第1の可変抵抗素子(153)の他端と、第2の可変抵抗素子(154)の他端をともに高耐圧MOSFETマクロモデルのドレイン端子(D)へ接続している。

【0158】

第2のMOSFET(152)のソースに、第3の可変抵抗素子(155)の一端を接続し、第3の可変抵抗素子(155)の他端を、第1のMOSFET(151)のソースとともに高耐圧MOSFETマクロモデルのソース端子(S)へ接続している。

【0159】

第1及び第2の可変抵抗素子(153、154)は、高耐圧マクロモデルのドレイン電圧に対する依存性を有する。

【0160】

第3の可変抵抗素子(155)は、図1の可変抵抗素子(3)に相当し、高耐圧マクロモデルのゲート電圧Vgに対する依存性とドレイン電圧Vdに対する依存性を有する。

【0161】

前記実施形態1、2と本実施形態との相違点は、第1のMOSFET(151)及び第2のMOSFET(152)のドレインにそれぞれ第1の可変抵抗素子(153)と第2の可変抵抗素子(154)を直列に挿入した点である。

【0162】

前記実施形態1、2では、ドレイン抵抗のドレイン電圧依存性を表現できる高耐圧専用モデル(HiSIM_HV等)を必要とするが、実施形態3では、通常のMOSFETモデル(BSIM3(Berkley Short−channel IGFET(Insulated Gate FET) Model)、BSIM4等)を使用することできる。

【0163】

<実施形態4>

次に、本発明の実施形態4について説明する。本実施形態は、図9に示した実施形態3のマクロモデルを作成するための装置に関する実施形態である。図11は、実施形態4の構成を示す図である。なお、図11において、図4と同一又は同等の要素には、同一の参照符号が付されている。

【0164】

図11を参照すると、ウェファ21は、ソース基板接続構造(図2)と通常構造(図3)の2種類のパターンのMOSFETを搭載したものを用意する。

【0165】

電気特性測定装置22で、ウェファ21のMOSFET(ソース基板接続構造と通常構造)のId−Vg、Id−Vd特性等の電気特性を測定する。

【0166】

記録媒体25(あるいは記憶装置)は、電気特性データ41/42、MOSFET抽出プログラム43、MOSFETモデル44、マクロモデル1抽出プログラム45−1、マクロモデル1(48−1)、マクロモデル2抽出プログラム45−2、マクロモデル2(48−2)、モデル検証プログラム49等を記録する。

【0167】

情報処理装置24は、各種測定データや各種モデルを読み込み、モデル抽出やモデル検証を行う装置である。

【0168】

本実施形態と、前記実施形態2との相違点は、マクロモデルの作成が2種類に分かれている点である。

【0169】

図12は、図11の装置において、マクロモデルの作成手順を示すフローチャートである。なお、図12において、図5と同一又は同等の処理を行う処理は、同一の参照番号が付されている。

【0170】

まず、処理31において、電気特性測定装置22を用いて、ウェファ21の電気特性を測定し、記録媒体25に、電気特性データ41/42を格納する。この時、ソース基板接続構造と通常構造の2種類のパターンでモデル抽出に必要な電気特性(ドレイン電流−ゲート電圧特性(Id−Vg特性)、ドレイン電流−ドレイン電圧特性(Id−Vd特性)等)を測定し電気特性データ41、42として記録する。

【0171】

次に、処理32において、記録媒体25の電気特性データ41/42とMOSFET抽出プログラム43を情報処理装置24に読み込み、通常構造の高耐圧MOSFETモデル44を作成する。この時に使用するモデルは、通常のMOSFETモデル(BSIM3、BSIM4等)を用い、ドレイン電流のチャネル長依存性もある程度合わせておく。ドレイン電流−ドレイン電圧特性(Id−Vd特性)において、ゲート電圧Vgの高い領域が合わない場合があるが、そのまま次へ進む。

【0172】

次に、処理37において記録媒体25の電気特性データ41/42とMOSFETモデル44とマクロモデル1抽出プログラム45−1を情報処理装置24に読み込み、図10に示す通常構造の高耐圧MOSFETのマクロモデル1(48−1)を作成する。

【0173】

図10に示すように、MOSFET(151)のドレインとマクロモデルのドレイン端子D間に可変抵抗素子(153)が接続されている。この時、MOSFETのパラメータは、なるべく変えず、図10の可変抵抗素子(153)のみで調整する。可変抵抗素子(153)には、ドレイン電圧Vd依存性を持たせる。

【0174】

次に、処理33において記録媒体25のマクロモデル1(48−1)とマクロモデル2抽出プログラム45−2を、情報処理装置24に読み込み、マクロモデル2抽出プログラム45−2を実行して、ソース基板接続構造の高耐圧MOSFETのマクロモデル2(48−2)を作成する。

【0175】

図9の等価回路において、第1のMOSFET(151)と第2のMOSFET(152)は同じモデルとし、第1の変抵抗素子(153)と第2の可変抵抗素子(154)も同一とする。この時、マクロモデル1の中身は変更せずに、可変抵抗素子(155)のみを調整する。可変抵抗素子(155)は、前記実施形態1の例えば式(1)〜式(4)(あるいは式(1’)〜(3’))と同様に、ゲート電圧Vgの依存性と、ドレイン電圧Vdの依存性を持たせる。

【0176】

次に、処理34において記録媒体25のマクロモデル2(48−2)とマクロモデル2抽出プログラム(45−2)を情報処理装置24に読み込み、マクロモデル2抽出プログラム(45−2)を実行することで、ソース基板接続構造の高耐圧MOSFETのマクロモデル2(48−2)を再調整する。この時、特にドレイン抵抗(図9の152、153)に関するパラメータに注目して調整する。

【0177】

次に、処理35において記録媒体25のマクロモデル2(48−2)とモデル検証プログラム49を情報処理装置24に読み込み、マクロモデル2(48−2)の検証を行う。

【0178】

処理36においてモデルの検証結果を判断し、問題なければ終了し、問題がある場合には(処理36のNG分岐)、処理34へ戻り検証結果がOKとなるまで繰り返す。

【0179】

詳細なフローに関しては、前記実施形態2で説明で参照した図13において、MOSFETモデル44とマクロモデル抽出プログラム45の間に、可変抵抗素子153の調整が追加されるのみであることから、その説明は省略する。実施形態4においても、前記実施形態1、2と同様の効果を奏する。

【0180】

<実施形態5>

次に、本発明の実施形態5を説明する。図14は、実施形態5のマクロモデルの作成手順を説明する図である。前記実施形態2との相違点は、差分データ生成プログラム52と電気特性差分データ53が追加された点である。図4及び図14を参照して、本実施形態の手順を以下に説明する。

【0181】

電気特性測定装置22を用いて、ウェファ21に搭載されたソース基板接続構造の高耐圧MOSFET(図2)と通常構造の高耐圧MOSFET(図3)の2種類のパターンの電気特性を測定する。通常構造の高耐圧MOSFET(図3)とソース基板接続構造の高耐圧MOSFET(図2)の測定データは、通常構造電気特性データ41とソース基板接続構造電気特性データ42として、それぞれ記録媒体23へ格納する。

【0182】

次に、情報処理装置24は、MOSFET抽出プログラム43を用いて、記録媒体23から、通常構造電気特性データ41を読み込み、MOSFETの閾値電圧やドレイン電流特性が前記通常構造電気特性データ41と一致するようにモデル抽出を行い、MOSFETモデル44として記録媒体23へ格納する。

【0183】

MOSFETモデルはドレイン抵抗のバイアス依存性が表現できる高耐圧専用モデル(例えばHiSIM_HV等)を用い、チャネル長依存性もある程度合わせておく。

【0184】

次に、情報処理装置24は、差分データ生成プログラム52を用いて、記録媒体23から、通常構造電気特性データ41と、ソース基板接続構造電気特性データ42を読み込み、通常構造電気特性データ41に対して、ソース拡散層(12)の幅が全チャネル幅に占める割合(ΣWn/W:図2)を乗じた値を、ソース基板接続構造電気特性データ42から差し引いた電気特性差分データ53を、記録媒体23に格納する。

【0185】

情報処理装置24では、通常構造電気特性データ41と前記ソース基板接続構造電気特性データ42の測定点が異なる場合には、例えば内挿又は外挿演算を実行して補間を行う。

【0186】

次に、情報処理装置24は、マクロモデル抽出プログラム45を用いて、前記MOSFETモデル44と前記電気特性差分データ53を読み込み、MOSFETの全チャネル幅Wを、ウェルコンタクト拡散層の幅の合計(ΣWp:図2)として、MOSFETモデル44のソースに可変抵抗素子3(図1参照)を挿入し、可変抵抗素子3を、前記実施形態2と同様に調整する。

【0187】

その後、情報処理装置24は、ソース基板接続構造のマクロモデル(図1又は図9)を作成し、仮マクロモデル46として、記録媒体23へ格納する。これ以降は、前記実施形態2と同一の手順であるため、説明は省略する。

【0188】

本実施形態のマクロモデル抽出プログラム45は、電気特性差分データ53の波形(データの値)に対するフィッティング(例えば最小二乗法等を用いたカーブ・フィッティング)を行うことによって、マクロモデルにおける可変抵抗素子3のモデリングパラメータを決定する。

【0189】

また、本実施形態の変形例として、マクロモデル抽出プログラム45は、可変抵抗素子3の抵抗値Rsの値をモデリングするにあたり、電気特性差分データ53の波形(データの値)に基づき、第1の領域4(図1(B)参照)と第2の領域5(図1(B)参照)の境界を検出する機能を備えてもよい。

【0190】

また、マクロモデル抽出プログラム45は、検出した当該境界に基づいて、マクロモデルにおける可変抵抗素子3の抵抗値Rsを表現する数式中のパラメータ、あるいは、そのパラメータの初期値を決定する機能を備えてもよい。

【0191】

あるいは、マクロモデル抽出プログラム45は、モデル作成者が、マクロモデルの抽出において参照できるよう、第1の領域4(図1(B)参照)と第2の領域5(図1(B)参照)の境界を検出し表示する機能を備えてもよい。

【0192】

また、マクロモデル抽出プログラム45は、マクロモデルが表現する電気特性における第1の領域4(図1(B)参照)と第2の領域5(図1(B)参照)の境界を、電気特性差分データ53における、これら境界と比較検証し、検証結果を表示する機能を備えてもよい。

【0193】

例えば、マクロモデル抽出プログラム45は、電気特性差分データ53を用いて各ゲート電圧において、ドレイン電流Idのドレイン電圧Vdによる微分値がゼロになるドレイン電圧Vd_gds0を検出し、その値を第1の領域4と第2の領域5の境界としてもよい。

【0194】

あるいは、マクロモデル抽出プログラム45は、可変抵抗素子3の抵抗値Rsを表現する数式中のパラメータをフィッティングする際の初期値として用いる。ドレイン電流のドレイン電圧による微分値がゼロになるドレイン電圧Vd_gds0が複数存在する場合には、その一方、あるいは、二点の中間点を第1の領域4と第2の領域5の境界としてもよい。

【0195】

さらに、マクロモデル抽出プログラム45は、複数のVd_gds0の一方だけを用いる場合の一例として、ドレインバイアスの小さい領域はRsがドレイン電圧Vdに伴い変化する特性の中に含めることができるので、ドレインバイアスの大きいほうのVd_gds0の値を境界として用いるようにしてもよい。

【0196】

本実施形態は、前記実施形態1、2と同様の効果を奏する。

【0197】

また、本実施形態においては、電気特性差分データ53を作成することにより、電気特性差分データ53を作成しない場合と比べて、マクロモデルにおける可変抵抗素子3のモデルパラメータを、より高精度に決定することができる。

【0198】

これは、電気特性差分データ53は、P+拡散層11(図1(A)参照)の存在に起因する寄生抵抗の影響を強く受ける電流成分を抜き出したものであり、P+拡散層11による寄生抵抗の影響がより顕著に現れるので、可変抵抗素子3のモデルパラメータのフィッティングが容易になるためである。

【0199】

また、電気特性差分データ53を作成することで、可変抵抗素子3の抵抗値Rsを高精度にモデリングするに当たって、必要な第1の領域4と第2の領域5の境界(図1(B)、図6(B)参照)の検出が容易になる。

【0200】

さらに、本実施形態によれば、情報処理装置24で実行されるプログラムが、

第1の電気特性実測データ(通常構造の電気特性データ41)と、第2の電気特性実測データ(ソース基板接続構造の電気特性データ42)とを用いた演算により、第3の電気特性データ(電気特性差分データ53)を生成する処理(機能)と、

第3の電気特性を対象として回路シミュレーション用素子モデルを生成する処理(機能)と、

を備えたことにより、可変抵抗素子3のモデルパラメータのフィッティング、あるいはモデリングを行うにあたり、可変抵抗素子3の抵抗値Rsを高精度にモデリングするために必要とされる、第1の領域4と第2の領域5(図1(B)、図6(B)参照)の境界の検出を容易化している。

【0201】

また、本実施形態においては、MOSFETを、チャネル幅W方向に、仮想的に複数に分割し(図6(A)参照)、分割したチャネル幅のうち、特定の仮想的な領域の電気特性において、第2のMOSFET2と、可変抵抗素子3(Rs)の直列接続を流れる電流を、第1の電気特性実測データ(通常構造電気特性データ41)と、第2の電気特性実測データ(ソース基板接続構造電気特性データ42)とを用いた演算により、求めている。これにより、可変抵抗素子3のモデルパラメータのフィッティング、あるいはモデリングするにあたり、可変抵抗素子3の抵抗値Rsを高精度にモデリングするために必要とされる、第1の領域4と第2の領域5の境界の検出を容易化している。

【0202】

<実施形態6>

次に、本発明の実施形態6を説明する。本実施形態は、前記実施形態1乃至5において、可変抵抗素子3の抵抗値Rsの領域分割を二つから三つ以上に変更した例である。

【0203】

本実施形態では、可変抵抗素子3の抵抗値Rsが、

低電圧側のドレイン・ソース間電圧Vdsに依存しないバイアス領域と、

ドレイン・ソース間電圧Vdsに依存するバイアス領域と、

高電圧側のドレイン・ソース間電圧Vdsに依存しないバイアス領域の

三つの領域からなる。また、この三つの領域の隣接する領域間が互いに滑らかに接続される。

【0204】

図15は、可変抵抗素子3の抵抗値Rsを、三つの領域に分割する例を説明する図である。図15の横軸はドレイン電圧Vd、縦軸は可変抵抗素子3の抵抗値Rsである。

【0205】

本実施形態においては、図1(B)の抵抗値Rsがドレイン電圧Vdに依存する第1の領域4を、低ドレイン電圧側で抵抗値Rsがドレイン電圧Vdに依存しない第1の領域の低VD側領域(8)と、抵抗値Rsがドレイン電圧Vdに依存する第1の領域の高VD側領域(9)の二つの領域に分割して表現する。

【0206】

第1の領域の低VD側領域(8)と第1の領域の高VD側領域(9)の境界、及び、

第1の領域の高VD側領域(9)と第2の領域5との境界は、

典型的には、ともに、ゲート電圧Vgが高い場合に、ドレイン電圧Vdが高い側に移動する。

【0207】

また、より典型的には、第1の領域の低VD側領域(8)と、第1の領域の高VD側領域(9)の境界、及び、

第1の領域の高VD側領域(9)と第3の領域(8)との境界、

はともに滑らかに接続される。

【0208】

可変抵抗素子3の抵抗値Rsは、一例として例えば、式(5)〜式(13)を用いて表現することができる。

【0209】

Voffset01= Vg + Voffset1 (5)

【0210】

Voffset02 = Vg + Voffset2 (6)

【0211】

Rs01 = (Rs0 + Rs1 * Vg + Rs2 *Vg2) / W (7)

【0212】

Rs02 = Rs01 * Voffset02 / Voffset01 (8)

【0213】

Rs10 = Rs01 * Rs3 (9)

【0214】

Rs11 = Rs01 * (Voffset01 - 0.5 * (Voffset01-Vd-δ+ sqrt((Voffset01- Vd-δ)2 + 4 *δ* Voffset01))) / Voffset01 (10)

【0215】

Rs12 = Rs02 * (Voffset02 - 0.5 * (Voffset02-Vd-δ+ sqrt((Voffset02-Vd-δ)2 + 4 *δ* Voffset02))) / Voffset02 (11)

【0216】

Rs = Rs10 + (Rs01 / (Rs02 − Rs01)) * (Rs12 − Rs11) (12)

【0217】

δ = 0.01 (13)

【0218】

ここで、

Voffset1は第1の領域の低ドレイン電圧側領域(8)と、第1の領域の高ドレイン電圧側領域(9)の境界を表現するためのフィッティングパラメータ、

Voffset2は、第1の領域の高ドレイン電圧側領域(9)と、第2の領域(5)の境界を表現するためのフィッティングパラメータ、

Rs1、Rs2、Rs3、Rs4は、抵抗値Rsのゲートバイアス依存性を表現するためのフィッティングパラメータである。

【0219】

また、実施形態6におけるマクロモデル抽出プログラム45のより好ましい一形態では、実施形態3のマクロモデル抽出プログラム45において、第1の領域4(図1(B)参照)と、第2の領域5(図1(B)参照)の境界を検出する手順に代えて、

第1の領域の低VD側領域(8)と第1の領域の高VD側領域(9)の境界、及び、

第1の領域の高VD側領域(9)と第2の領域(5)との境界

を検出し、実施形態3と同様の処理を実行する機能を有する。

【0220】

実施形態6において、マクロモデル抽出プログラム45は,電気特性差分データ53を用いて各ゲート電圧において、ドレイン電流のドレイン電圧による微分値がゼロになるドレイン電圧Vd_gds0を二つ検出し、

低ドレインバイアス側のVd_gds0を、第1の領域の低VD側領域(8)と第1の領域の高VD側領域(9)の境界とし、

高ドレインバイアス側のVd_gds0を、第1の領域の高VD側領域(9)と第2の領域(5)との境界、

とする機能を、マクロモデル抽出プログラム45において備える。

【0221】

実施形態6において、図1又は図9の可変抵抗素子3の抵抗値Rsを三つの領域に分割する理由について、図16を参照して説明する。

【0222】

図16(A)は、第1の領域の低VD側領域(8)で反転層が形成される形態を示す。第1の領域の低VD側領域(8)は、ドレイン電圧Vdが低い領域でMOSFETは線形領域で動作しており、反転層116はゲート電力のドレイン端近傍まで伸びている。

【0223】

このため、P+拡散層(ウェルコンタクト拡散層)11近傍に形成される反転層が形成されない領域117(従がって、チャネル電荷が少ない領域)が、全反転層の電荷に与える影響は小さい。よって、図1又は図9の可変抵抗素子3としてモデリングされる寄生抵抗Rsの値は小さい。

【0224】

また,反転層が116ゲート電極115のドレイン近傍まで常に伸びているため、図1又は図9の可変抵抗素子3としてモデリングされる寄生抵抗Rsのドレイン電圧依存性は小さい。

【0225】

図16(B)は、第1の領域の高VD側領域(9)で反転層が形成される形態を示す。これは、第1の領域の低VD側領域(8)と第2領域(5)の中間的なドレインバイアス条件における形態である。第1の領域の低VD側領域(8)よりもドレイン電圧Vdが高くトランジスタは飽和領域、あるいは線形領域から飽和領域への遷移領域で動作する。

【0226】

反転層116が形成される範囲は、まだ反転層が形成されない領域117よりもドレイン側に広がっているので、反転層が形成されない領域117が、全反転層電荷に与える影響は、反転層116がドレイン領域近傍のごく狭い範囲に形成される場合と比べると、小さい。

【0227】

また、第1の領域の高VD側領域(9)では、反転層116の形成される範囲のドレイン領域側の境界が、ドレイン電圧Vdの上昇とともに、ゲート電極115のドレイン領域側の端部から、ソース領域寄りに移動する。

【0228】

従って、ドレイン電圧Vdの上昇とともに、反転層が形成されない領域117が全反転層電荷に与える影響が増す。このため、第1の領域の高VD側領域(9)では、ドレイン電圧Vdの上昇とともに、図1又は図9の可変抵抗素子3としてモデリングされる寄生抵抗Rsの値は増加する。

【0229】

図16(C)は、第2の領域(5)で反転層が形成される形態を示す。第2の領域(5)は、第1の領域の高VD側領域(9)よりもドレイン電圧Vdが高い状態であり、MOSトランジスタは飽和領域で動作している。このとき、反転層116は、ソース領域近傍の狭い範囲に形成される。このため、反転層が形成されない領域117(したがってチャネル電荷が少ない領域)が、全反転層電荷に与える影響は大きく、図1又は図9の可変抵抗素子3としてモデリングされる寄生抵抗Rsの値は大きい。

【0230】

また、この状態では、反転層116のドレイン領域側の境界は、すでに反転層が形成されない領域117が存在する領域のドレイン側の境界よりも、ソース領域に近い位置となるので、ドレイン電圧Vdの変化に伴う、反転層が形成されない領域117が、全反転層電荷に与える影響の変化も小さくなる。このため、図1又は図9の可変抵抗素子3としてモデリングされる寄生抵抗Rsの値は、ドレイン電圧に依存しないか、あるいは、ドレイン電圧に対する依存性は、第1の領域の高VD側領域(9)の場合よりも、小さい。

【0231】

第1の領域の低VD側領域(8)と第1の領域の高VD側領域(9)の境界は、モデリング対象とするMOSFETの線形領域と飽和領域の境界となるドレイン電圧Vd、すなわち、飽和電圧と同程度とする。あるいは、飽和電圧よりも若干低めの値、例えば、典型的には、飽和電圧の0.2倍から1倍程の値とする。

【0232】

第1の領域の高VD側領域(9)と、第2の領域(5)の境界は、モデリング対象とするMOSFETの飽和電圧と同程度とする。あるいは、飽和電圧よりも高めの値、例えば、典型的には、飽和電圧の1倍から2.5倍程の値とする。

【0233】

また、第1の領域の高VD側領域(9)と第2の領域(5)の境界となるドレイン電圧は、第1の領域の低VD側領域(8)と第1の領域の高VD側領域(9)の境界となるドレイン電圧よりも高い。

【0234】

なお、本実施形態では、可変抵抗素子3の抵抗値Rs(寄生抵抗Rsを表す)が、三つの領域に分割される例を示したが、必要に応じて、さらに四つ以上に分割しても良い。

【0235】

また、本実施形態では、前記実施形態1〜5の抽出手順において、可変抵抗素子3の抵抗値Rsを、二つの領域から構成されるようにモデリングする手順において、可変抵抗素子3の抵抗値Rsを三つの領域、あるいは四つ以上の領域から構成されるように、モデリングすることにより、モデルを抽出する。

【0236】

本実施形態では、可変抵抗素子3の抵抗値Rsを、前記実施形態1等で説明した、二つの領域よりも、さらに多く分割した領域によってモデリングを行う構成としたことにより、可変抵抗素子3のモデリング精度を向上することができる。その結果、回路シミュレーション用マクロモデルの精度を向上し、このマクロモデルを用いた回路シミュレーションの精度を向上する。

【0237】

また、本実施形態において、前記実施形態5に記載した電気特性差分データ53を作成することで、可変抵抗素子3の抵抗値Rsの値を高精度にモデリングするに当たって必要な第1の領域の低VD側領域(8)と、第1の領域の高VD側領域(9)の境界、及び第1の領域の高VD側領域(9)と第2の領域(5)との境界の検出をより容易化している。

【0238】

<実施形態7>

次に、本発明の実施形態7を説明する。本実施形態は、前記実施形態5、6におけるマクロモデル抽出プログラム45に、以下の形態、あるいは以下のうち一部の形態が追加される。本実施形態では、MOSFETのソース側に付加された寄生抵抗に対するMOSFETの電流感度を表す寄生抵抗感度データ61を求めることにより、可変抵抗素子3のモデル及びマクロモデルを生成する。実施形態7について、図17及び図18を参照して説明する。

【0239】

図18は、図17におけるMOSFETモデル44を使用する手順の一部を、通常構造電気特性データ41を使用する手順に置き換えたものである。

【0240】

本実施形態7においては、通常構造電気特性データ41又は通常構造電気特性データ41に対応するMOSFETモデル44を用いて、寄生抵抗感度解析プログラム64により、MOSFETのソース側に付加された寄生抵抗に対するMOSFETの電流感度を表す寄生抵抗感度データ61を求める。寄生抵抗感度データとは、各バイアス条件において、ソース側にある大きさの寄生抵抗が付いた時に、MOSFETのドレイン電流がどれだけ変動するかを表すデータである。

【0241】

なお、MOSFETモデル44の代わりに、通常構造電気特性データ41を用いて寄生抵抗感度データ61を求める場合には、通常構造電気特性データ41をテーブルモデルとして扱い寄生抵抗感度データ61を求める。ここで、テーブルモデルとは、数式により表現したMOSFETのモデルとは異なり、各バイアス点でのMOSFETの電流値データの集まりから与えられたバイアス条件におけるMOSFETの電流(ドレイン電流)を求めるしくみのことをいう。

【0242】

次に、通常構造電気特性データ41、又は通常構造電気特性データに対応する通常構造のMOSFETモデル44、電気特性差分データ53、得られた寄生抵抗感度データ61を用いることによって、寄生抵抗成分抽出プログラム65により、図1の可変抵抗素子3(図9の155)の抵抗値Rsのバイアス依存性を推定したデータであるRsバイアス依存性推定データ62を作成する。すなわち、ソース側に寄生抵抗Rsが付かない電気特性である通常構造電気特性データ41と、ソース側に寄生抵抗Rsが付く電気特性である電気特性差分データ53(第2のMOSFET2に流れる電流に相当)とを比較することによって、各バイアス条件での単位チャネル幅当たりの寄生抵抗による電流変動量を求める。

【0243】

そして、得られた電流変動量と、各バイアス条件で寄生抵抗が電流に与える影響を示す寄生抵抗感度データ61を用いて、各バイアス条件での寄生抵抗である抵抗値Rsバイアス依存性推定データ62、具体的には、各バイアス条件での可変抵抗素子3(図9の155)の抵抗値Rsについて、Rsバイアス依存性推定データ62を求める手順である。Rsバイアス依存性推定データは、例えば図1(B)、図6(B)、図15に示したような特性データである。

【0244】

また、図17のマクロモデル抽出プログラム45は、Rsのバイアス依存性推定データ62を用いて、可変抵抗モデルパラメータ抽出プログラム66によって、可変抵抗素子3(図9の155)の抵抗値Rsのバイアス依存性を表すパラメータである可変抵抗モデル63を作成する、

【0245】

そして、マクロモデル抽出プログラム45は、Rsバイアス依存性推定データ62を、可変抵抗素子3(図9の155)の抵抗値Rsのバイアス依存性を表すパラメータを作成するための初期値モデルの作成に使用し、可変抵抗モデル63を作成する。

【0246】

可変抵抗モデルパラメータ抽出プログラム66は、可変抵抗モデル63を自動生成するようにしてもよい。あるいは、可変抵抗モデルパラメータ抽出プログラム66は、可変抵抗モデルパラメータ抽出プログラム66を実行する情報処理装置(図4の24)において、適宜、操作者からの操作・指示等に応じて、可変抵抗モデル63を生成するようにしてもよい。

【0247】

また、得られた可変抵抗モデル63及び通常構造電気特性データに対応するMOSFETモデル44を用いて、仮マクロモデル作成プログラム67により、図1(A)と同様の構成を持つ仮マクロモデル46が生成される。上記のとおり、実施形態7は、可変抵抗素子3の抵抗値Rsのバイアス依存性を表すパラメータを高精度に抽出することを可能としている。

【0248】

なお、上記の特許文献、非特許文献の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0249】

1、151 第1のMOSFET

2、152 第2のMOSFET

3、155 可変抵抗素子

6 ソース基板接続構造

7 通常構造

11、111 P+拡散層(ウェルコンタクト拡散層)

12、112 N+拡散層(ソース拡散層)

13、113 ドレイン拡散層

14、114 低濃度ドレイン拡散層

15、115 ゲート電極

21 ウェファ

22 電気特性測定装置

23、25 記録媒体

24 情報処理装置

31〜37 処理

41、42 電気特性データ

43 MOSFET抽出プログラム

44 MOSFETモデル

45、45−1、45−2 マクロモデル抽出プログラム

46 仮マクロモデル

47 マクロモデル調整プログラム

48、48−1、48−2 マクロモデル

49 モデル検証プログラム

50 モデル検証結果

51 結果判定

52 差分データ生成プログラム

53 電気特性差分データ

61 寄生抵抗感度データ

62 Rsバイアス依存性推定データ

63 可変抵抗モデル

64 寄生抵抗感度解析プログラム

65 寄生抵抗成分抽出プログラム

66 可変抵抗モデルパラメータ抽出プログラム

67 仮マクロモデル作成プログラム

101 可変抵抗

102、104 MOSFET

103 JFET

116 反転層

117 反転層が形成されにくい領域(反転層が形成されない領域)

153、154、155 可変抵抗素子

【技術分野】

【0001】

本発明は、高耐圧MOSFETの回路シミュレーション技術に関し、特に、回路シミュレーション用モデルの作成方法と装置並びにプログラムに関する。

【背景技術】

【0002】

高耐圧MOSFET(Metal Oxide Semiconductor Field Effect Transistor)の回路シミュレーション用モデルの高精度化を図るために、通常のMOSFETを表現する素子モデルに可変抵抗を組み合わせたマクロモデルを用いる技術が、例えば特許文献1等に記載されている。その例を図19(A)、(B)に示す。

【0003】

図19(A)は、MOSFET102のドレイン側に可変抵抗101を接続した回路ブロックを一つの高耐圧MOSFETを表現するマクロモデルとするものである。可変抵抗101の端子のうちMOSFET102のドレインに接続されない側の端子をマクロモデルのドレイン端子(D)とする。マクロモデルのゲート端子(G)、ソース端子(S)、バックゲート端子(「バルク端子」ともいう)(B)は、それぞれMOSFET102のゲート端子、ソース端子、バックゲート端子(バルク端子)と同一である。このマクロモデルにより、チャネル領域とドレイン電極(高濃度ドレイン拡散層)の間に位置する低濃度ドレイン拡散層が原因となるゲート・ソース間電圧(単に「ゲート電圧」ともいう)とドレイン・ソース間電圧(単に「ドレイン電圧」ともいう)に依存した寄生抵抗成分を表現することができる。

【0004】

図19(B)は、図19(A)における可変抵抗101を、接合型トランジスタ(JFET:Junction FET)103に置き換えたものである。図19(B)のマクロモデルも、図19(A)のマクロモデルと同様の効果を奏する。

【0005】

また、非特許文献1の14章には、チャネル領域とドレイン電極の間に位置する低濃度ドレイン拡散層の寄生抵抗成分をトランジスタモデルのモデル式の中に含ませる技術が開示されている。この場合、図19(A)や図19(B)のマクロモデルは、例えば図19(C)に示すような、単一のMOSFET104により置き換えられる。図19(C)には、図19(A)の可変抵抗101、あるいは図19(B)のJFET103が、モデルの中に予め組み込まれている。このため、MOSFET104のドレインがマクロモデルのドレイン端子(D)とされる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−190328号公報

【特許文献2】特開2001−189449号公報

【特許文献3】特許第3120389号公報

【非特許文献】

【0007】

【非特許文献1】Hiroshima University & STARC、"HiSIM_HV 1.2.0 User's Manual" (2009) [平成23年9月12日検索] <インターネットURL: http://home.hiroshima-u.ac.jp/usdl/HiSIM_HV/C-Code/HiSIM_HV_C.html>

【発明の概要】

【発明が解決しようとする課題】

【0008】

以下に、関連技術の分析を与える。

【0009】

図20に示したレイアウト構造の高耐圧MOSFETに対して、特許文献1や非特許文献1に記載された関連技術を用いても、精度の良い回路シミュレーション用のモデルが得られないことを、本願発明者らは、全く独自に知見した。なお、ソース領域に図20に示したレイアウト構造を備えたトランジスタに関する関連技術として、例えば特許文献2、特許文献3等の記載が参照される。

【0010】

図20に示すように、高耐圧MOSFETは、ソース側に特殊な構造、すなわち、ソース拡散層112(高濃度N+拡散層)と、Pウェル(不図示)に電源電圧を供給するためのウェルコンタクト拡散層(「ウェル電極拡散層」ともいう)111(高濃度P+拡散層)とが、ゲート電極115(シリコン基板上にゲート絶縁膜を介して配置される)のソース領域側の辺に沿って、交互に隣接して配置されたレイアウト構造を備えている。このような高耐圧MOSFETにおいて、図19等を参照して説明したMOSFETモデルを用いた場合、ドレイン電流を、広いバイアス範囲で精度良く求めることはできない(この点については、後に詳細に説明する)。

【0011】

本願発明者らは、その原因を解析・検討した結果、このたび、上記問題点を解決する全く新規なマクロモデルを開発し、該マクロモデルのシミュレーション精度を検証したので、以下に提案する。すなわち、本発明の目的は、ソース領域にソース拡散層とウェルコンタクト拡散層が隣接して配置された構造を備えた高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーション精度を向上させる装置、方法、プログラム、記録媒体を提供することにある。

【課題を解決するための手段】

【0012】

前記課題の少なくとも1つを解決するため、本発明は、概略以下の構成とされる(だたし、以下に限定されるものでないことは勿論である)。

【0013】

本発明の1つの側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルとして、ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、を備え、前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端との接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成する手段と、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶手段と、

前記記憶手段から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子の抵抗値を調整する手段と、を備えたモデル作成装置が提供される。

【0014】

本発明の別の側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルを情報処理装置で作成するにあたり、

ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、

前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、

を備え、

前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端の接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成する処理と、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶装置から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記第1の可変抵抗素子の抵抗値を調整する処理を、

前記情報処理装置に実行させるプログラムが提供される。

【0015】

本発明のさらに別の側面によれば、ソース拡散層と、前記ソース拡散層と逆導電型のウェルコンタクト拡散層とがチャネル幅方向に沿って隣接して配置されたソース領域を有する高耐圧MOSFETの回路シミュレーション用のMOSFETのモデルを情報処理装置で作成するにあたり、

ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、前記ソース領域の前記ソース拡散層の幅と前記ウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFETと、

前記第2のMOSFETのソースに一端が接続された第1の可変抵抗素子と、

を備え、

前記第1のMOSFETのソースと前記第1の可変抵抗素子の他端との接続点をソース端子とし、前記第1及び第2のMOSFETの前記共通接続したドレイン、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、ドレイン端子、ゲート端子、バックゲート端子とするモデルを作成し、

モデリング対象の前記高耐圧MOSFETの電気特性データを記憶する記憶手段から、前記高耐圧MOSFETの電気特性データを読み出し、前記電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子の抵抗値を調整する、モデル作成方法が提供される。

【発明の効果】

【0016】

本発明によれば、ソース領域にソース拡散層とウェルコンタクト拡散層が隣接して配置された構造を備えた高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーション精度を向上させることができる。

【図面の簡単な説明】

【0017】

【図1】本発明の概要を説明する図である。

【図2】本発明の第1の実施形態を説明する図である。

【図3】本発明の第1の実施形態を説明する図である。

【図4】本発明の第2の実施形態のシステムを説明する図である。

【図5】本発明の第2の実施形態の動作を説明する図である。

【図6】本発明の原理を説明する図である。

【図7】本発明の効果を説明する図である。

【図8】本発明の効果を説明する図である。

【図9】本発明の第3の実施形態を説明する図である。

【図10】本発明の第3の実施形態を説明する図である。

【図11】本発明の第4の実施形態を説明する図である。

【図12】本発明の第4の実施形態の動作を説明する図である。

【図13】本発明の第2の実施形態を説明する図である。

【図14】本発明の第5の実施形態を説明する図である。

【図15】本発明の第6の実施形態を説明する図である。

【図16】本発明の第6の実施形態を説明する図である。

【図17】本発明の第7の実施形態を説明する図である。

【図18】本発明の第7の実施形態を説明する図である。

【図19】(A)、(B)、(C)は 関連技術を説明する図である。

【図20】関連技術を説明する図である。

【図21】関連技術の問題点を説明する図である。

【図22】関連技術の問題点を説明する図である。

【図23】関連技術の問題点を説明する図である。

【図24】関連技術の問題点を説明する図である。

【発明を実施するための形態】

【0018】

本発明によれば、半導体基板上にゲート絶縁膜を介して配置されるゲート電極を間に挟んで半導体基板表面に対向配置される第1及び第2の拡散領域(diffused region)の一方の前記第1の拡散領域が、第1導電型の第1の拡散層(例えば図2の12)と、前記第1拡散層と逆導電型のウェルコンタクト拡散層(図2の11)とがチャネル幅方向に沿って隣接して配置されたMOSFETの回路シミュレーション用のMOSFETのモデルとして、前記第2の拡散領域(例えば図1のドレイン)同士が共通接続され、ゲート同士が共通接続され、バックゲート同士が共通接続され、前記第1の拡散領域の前記第1の拡散層(図2の12)の幅と前記ウェルコンタクト拡散層(図2の11)の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET(図1の1、2)と、前記第2のMOSFET(図1の2)の前記第1の拡散領域(例えば図1のソース)に一端が接続された第1の可変抵抗素子(図1の3)と、を備え、前記第1のMOSFET(図1の1)の前記第1の拡散領域と、前記第1の可変抵抗素子(図1の3)の他端との接続点を、第1端子(S)とし、前記第1及び第2のMOSFET(図1の1、2)の前記共通接続した前記第2の拡散領域、前記共通接続したゲート、前記共通接続したバックゲートを、それぞれ、第2端子(D)、ゲート端子(G)、バックゲート端子(B)とするモデルを用いる。モデリング対象の前記高耐圧MOSFETの電気特性データに基づき、前記回路シミュレーション用のMOSFETのモデルの前記第1の可変抵抗素子(図1の3)の抵抗値(Rs)を調整する。

【0019】

以下では、上記した本発明についてその基本原理を説明し、つづいて実施形態を説明する。

【0020】

上記したように、特許文献1、非特許文献1等に記載の関連技術を用いても、図20に示すレイアウト構造のMOSFETに対しては、精度の良い回路シミュレーションモデルが得られないことが、本願発明者らによるこの度の検討から明らかになったので、以下に説明する。

【0021】

図20において、ゲート電極115の左側のソース側には、N+型のソース拡散層112と、P+型のウェルコンタクト拡散層111(P+拡散層)がチャネル幅方向に隣接して配置されている。図20の例では、P+型のウェルコンタクト拡散層(P+拡散層)111、N+型のソース拡散層(N+拡散層)112が交互に隣接して配置されている。図20では、P+型のウェルコンタクト拡散層(P+拡散層)111が3つ、これらの間に、N+型のソース拡散層(N+拡散層)112が2つ配置されている。なお、図20のレイアウト構成はあくまで説明のために簡略化して例示したものであって、P+型のウェルコンタクト拡散層(P+拡散層)111、N+型のソース拡散層(N+拡散層)112の数、配置形態は図20の構成に制限されるものでない。なお、N+型のソース拡散層112とP+型のウェルコンタクト拡散層111は、通常、電気的に接続するように形成される。

【0022】

図20において、ゲート電極115の右側のドレイン側には、ゲート電極115に隣接するN−型の低濃度ドレイン拡散層114と、低濃度ドレイン拡散層114に隣接したN+型のドレイン拡散層113(ドレインコンタクト用のN+拡散層)が設けられる。

【0023】

図20において、ゲート電極115への電圧の印加により、ゲート電極115下部のシリコン基板表面に反転層(チャネル)が形成され、ソースとドレイン間が導通する。

【0024】

なお、図20に示す例では、NチャネルMOSFETはP型ウェル内に形成されているが、NチャネルMOSFETをP型シリコン基板表面に形成する場合、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト(Substrate Contact)拡散層となる。したがって、以下では、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト拡散層であってもよい。ウェルコンタクト拡散層(基板コンタクト拡散層)は、単に、ウェルコンタクト(基板コンタクト)とも呼ばれる。なお、NチャネルMOSFETのP+型のウェルコンタクト拡散層(基板コンタクト)は例えば電源VSS(0V)に接続される。また図20では、NチャネルMOSFETのレイアウト構成を例示したが、PチャネルMOSFETの場合、極性が反転することを除いて同様である。

【0025】

図20において、

Wnは、N+型のソース拡散層112一つ当たりの幅、

Wpは、P+型のウェルコンタクト拡散層111一つ当たりの幅、

Wは全チャネル幅

である。このWは、各ソース拡散層112の幅Wnの総和(=ΣWn)と、各ウェルコンタクト拡散層111の幅Wpの総和(=ΣWp)を加算した値となる(W=ΣWn+ΣWp)。

【0026】

なお、Wnは、ソース領域のすべてのN+型ソース拡散層112について同じ値である場合もあれば、ソース拡散層112毎に異なる場合もある。Wpについても、同様である。すなわち、ソース領域のすべてのP+型ウェルコンタクト拡散層111の幅が同一である場合もあれば、P+型ウェルコンタクト拡散層111毎にその幅が異なる場合もある。

【0027】

また、図20では、P+型ウェルコンタクト拡散層111とN+型ソース拡散層112のゲート電極115とは反対側の端部が面一に整列しているが、必ずしも整列している必要はない。例えば、N+型ソース拡散層112が、ゲート電極115と対向する側と反対側にさらに延在し隣のN+型ソース拡散層112と接続し、間のP+型ウェルコンタクト拡散層111を囲むようにしてもよい。図20に示したレイアウト構造は、P+型ウェルコンタクト拡散層111とN+型ソース拡散層112が接続しているため、「ソース基板接続構造」とも称呼される。

【0028】

図21(A)と図21(B)は、図20の高耐圧MOSFETの異なるWnratioに関して、ドレイン電流−ドレイン電圧特性(Id−Vd特性)をモデリングした結果と、実測値をそれぞれ示す図である(本願発明者らによって為された分析結果)。ここで、Wnratioは、図20の全チャネル幅W(=ΣWn+ΣWp)に対して、各N+型ソース拡散層112の幅Wnの合計(=ΣWn)が占める割合であり、%表記を用いると、以下で与えられる。

【0029】

Wnratio={(ΣWn)/(ΣWn+ΣWp)}×100

【0030】

図21(A)では、Wnratio=48%、図21(B)では、Wnratio=40%としている。なお、図21(A)、(B)において、横軸はドレイン電圧(drain−to−source voltage)Vds(単位:電圧(Voltage))、縦軸はドレイン電流(drain−to−source current)Id(単位:Ampere)であり、ゲート電圧(gate−to−source voltage)Vgsを0〜5Vまで1Vステップで変化させたId−Vd特性曲線が示されている。ゲート・ソース間電圧Vgs=0Vでは、NチャネルMOSFETはオフ状態であり、ドレイン電流Id=0である。

【0031】

図21(A)の例では、▲マークで示した実測値と、破線で示す関連技術によるモデリング結果(従来モデル)とは、ドレイン・ソース間電圧Vdsの全範囲(0〜20V)に亘って、ゲート・ソース間電圧Vgs=0、1、2、・・・、5Vの全てについて、比較的良く一致している。

【0032】

これに対して、同じモデルを、Wnratioが40%の場合の実測値(▲マークで示す)と比較した図21(B)の例では、実測値(▲)と、破線で示すモデルリング結果(従来モデル)とが合っていない。特に、ドレイン電流Idが、ドレイン・ソース間電圧Vdsに依存せずにほぼ一定となる領域のうち、ゲート・ソース間電圧Vgsが高い領域で実測値(▲)との差異が顕著となる。

【0033】

これは、図20に示したレイアウト構成において、Wnratioの値の相違により、MOSFETのドレイン電流−ドレイン・ソース間電圧(Id−Vds)特性が変化していることによるものと思料される。

【0034】

本願発明者らは、図19に示した関連技術のMOSFETモデルに関して、そのモデルパラメータの調整を試みたが、40%と48%というWnratioの値の相違によるドレイン電流−ドレイン・ソース間電圧(Id−Vds)特性の変化を、図19に示したMOSFETモデルによって表現することはできなかった。

【0035】

このようなMOSFETモデル(例えば図19に示したモデル)のフィッティング誤差に対して、本願発明者らは、より詳細な検討を行ったので、以下にその結果を説明する。

【0036】

図22(A)と図22(B)は、図20に示したレイアウト構造のNチャネルMOSFETがオンした状態におけるドレイン・ソース間電流Idsを、Wnratioが異なる素子(MOSFET)間で比較したものである(本願発明者らによって為された分析結果である)。なお、図22において、縦軸は、ドレイン・ソース間電流Idsを全チャネル幅W(=ΣWn+ΣWp)で規格化し、Ids/Wとしている。図22において、横軸の素子(MOSFET)AのWnratioは40%、素子(MOSFET)B、CのWnratioはともに48%である(なお、素子BとCは、Wnratioは共通であるが、別のMOSFETである)。

【0037】

図22(A)及び図22(B)において、マーク●は実測値を表している。また、破線で示す従来モデル(素子A、B、Cと破線との交点)は、例えば図19(A)のMOSFETモデルを用いてそのパラメータ(例えば図19(A)の可変抵抗素子101の抵抗値やその他のパラメータ)のフィティング等を行って得られたMOSFETモデルに対してシミュレーションを行い、Ids/Wを求めたものである。破線は、素子A、B、Cのそれぞれのモデリング結果を直線で結んだ線である(破線…の各ドットがモデリング結果を表しているのではなく、素子A、B、Cと破線との交点が、素子A、B、CのIds/Wである。図22(B)も同様である)。

【0038】

図22(A)に示した線形領域(ドレイン・ソース間電圧Vds=0.1V、ゲート電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●)は、Wnratio=40%の素子Aと、Wnratio=48%の素子B、Cでほぼ等しく、Wnratioにほとんど依存しないことが示されている。また、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果Ids/Wは、図22(A)に示すように、線形領域では、素子AのWnratio=40%、素子B、CのWnratio=48%のいずれの実測値(●)とも交差しており、ほぼ一致していることが分かる。

【0039】

一方、図22(B)に示した飽和領域(ドレイン・ソース間電圧Vds=12V、ゲート・ソース間電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●で示す)は、Wnratioに依存して変化する。すなわち、Wnratio=40%の素子Aでは、Ids/Wの実測値(●で示す)と、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果(破線と素子Aの交差部)とは一致しない(差異がある)。しかしながら、Wnratio=48%の素子B、Cでは、Ids/Wの実測値(●で示す)と、破線と素子B、Cとの交点であるモデリング結果(従来モデル)とはほぼ一致しており、Wnratio=40%の素子Aのような、顕著な差異は認められない。

【0040】

図19等に示した関連技術では、Wnratio依存性は、例えば抵抗成分(図19(A)の可変抵抗101の抵抗値)を調整することにより、全体の電流レベルを上下させることが可能である。

【0041】

しかしながら、図22(A)、図22(B)に見られるように、ドレイン電圧(ドレイン・ソース間電圧)に依存して、ドレイン・ソース間電流Idsに異なるWnratio依存性が現れる、という傾向をうまくモデリングすることはできない。

【0042】

特に、図22(A)及び図22(B)に示したように、

線形領域では、ドレイン・ソース間電流IdsはWnratioに依存せず、

飽和領域でのみ、ドレイン・ソース間電流IdsがWnratioに依存する、

という傾向が認められる。

【0043】

通常の構造のMOSFET(例えば、後述する図3の高耐圧MOSFET参照)においては、線形領域の特性は、素子のレイアウト構造に依存して変化せず、飽和領域の特性だけが、素子のレイアウト構造に依存して変化する、ということはない。

【0044】

線形領域の特性は、素子のレイアウト構造に依存して変化せず、飽和領域の特性だけが素子のレイアウト構造に依存して変化する、ということは、図20に示したレイアウト構造のMOSFETに特有の特性である(本願発明者らによって為された分析結果)。

【0045】

このため、図19(A)乃至(C)に示した関連技術(MOSFETのドレインに接続した可変抵抗)のモデリングで表現することは、著しく、困難である。

【0046】

図23(A)と図23(B)は、それぞれ線形領域と飽和領域で、ドレイン・ソース間電流Idsのゲート・ソース間電圧Vgsによる微分値である相互コンダクタンス

をゲート幅Wで規格化した値Gm/Wを、Wnratio=40%(破線)とWnratio=48%(実線)で比較した結果である(本願発明者らによって為された分析結果である)。

【0047】

図23(A)及び図23(B)において、横軸はゲート・ソース間電圧Vgs(0〜5V)、縦軸はGm/W(実測値)である。なお、Wnratio=40%(破線)とWnratio=48%(実線)の特性極性は、ゲート・ソース間電圧Vgsを0〜5Vの範囲で所定の電圧ステップ(1V以下のステップ、例えば0.25Vステップ)で可変させて実測した複数点のGm/Wをカーブフィッティングして表示したものである。

【0048】

図22(A)に示したドレイン電流Idsの場合と同様に、線形領域Vds=0.1Vでは、Gm/Wは、図23(A)に示すように、Wnratioに依存しない。すなわち、Wnratio=40%(破線)とWnratio=48%(実線)とが、Vgs=0〜5Vの範囲でほぼ一致する(破線と実線がほぼ重なる)。なお、その原因は不明だが、1V<Vgs<1.25V付近の一部区間では差異が現れている。

【0049】

一方、飽和領域Vds=12Vでは、図23(B)に示すように、Gm/Wは、Wnratioに依存する。すなわち、Wnratio=40%(実線)と、Wnratio=48%(破線)とで特性が異なる(1V<Vgs≦5Vの広い範囲で、破線と実線とが重ならない)。

【0050】

この原因について、電気伝導に寄与するキャリアが誘起される領域である反転層(inversion layer)の形成条件に着目して考察した。その結果を、図24(A)及び図24(B)を参照して以下に説明する。

【0051】

図24(A)及び図24(B)のいずれも、モデリング対象とする高耐圧MOSFETのレイアウトを簡略化し模式的に例示したものであり、本願発明者らによって為された分析結果を説明するための図である。図24(A)及び図24(B)において、参照番号117で示す領域は、反転層が形成されない(あるいは、反転層が形成にくい)領域である。

【0052】

図24(A)には、ドレイン・ソース間電圧(ドレイン電圧)Vdsが低く、NチャネルMOSFETが線形領域で動作する場合に、反転層が形成される様子が模式的に例示されている。ゲート電極115へのゲート電圧の印加によって、ゲート電極115下部(ゲート酸化膜直下)のシリコン基板表面付近に誘起される反転層116は、ソースからドレインにかけての電位差が小さいため、ドレイン側まで広がった形状で形成されると考えられる。P+型のウェルコンタクト拡散層111付近では、ゲート電極115下部のシリコン基板表面に反転層は形成されないと考えられる。これを、図24(A)では、反転層が形成されにくい領域117として表している。

【0053】

しかし、図24(A)に示すように、反転層116はゲート電極115下部のドレイン114側の端部まで広い範囲にわたって形成されることから、反転層116の電荷の全体量について考えると、P+型のウェルコンタクト拡散層111近傍で反転層が形成されないことの影響は小さい。

【0054】

したがって、線形領域では、P+型のウェルコンタクト拡散層111の幅の合計(=ΣWp)が全チャネル幅Wに対して占める割合Wpratio(=ΣWp/(ΣWn+ΣWp)×100)がドレイン・ソース間電流Idsに与える影響が小さいと考えられる。

【0055】

また、ソース拡散層であるN+拡散層112の幅の合計(=ΣWn)が全チャネル幅Wに占める割合Wnratio(%表記)は、Wnratio=(100−Wpratio)%であることから、線形領域では、Wnratioが反転層116の全電荷量に与える影響は小さく、Wnratioがドレイン電流Idsに与える影響は小さいと考えられる。このため、線形領域におけるドレイン・ソース間電流−ドレイン・ソース間電圧特性(Ids−Vds特性)やGm/Wは、N+拡散層のチャネル幅の割合Wnratioには依存しない。

【0056】

図24(B)には、ドレイン・ソース間電圧Vdsが高く、NチャネルMOSFETが飽和領域で動作する場合に反転層が形成される様子が模式的に例示されている。飽和領域では、ソースからドレインにかけての電位差が大きく、反転層116はシリコン基板表面の電位が低い領域に形成される性質を持つ。このため、反転層116は、チャネル電位の低いソース近傍だけに形成されるものと思料される(ピンチオフ:ドレイン拡散層とウェル(基板)間のpn接合に逆方向電圧が印加され空乏層が広がり、チャネルが狭くなる)。

【0057】

この場合、P+型のウェルコンタクト拡散層111近傍で反転層が形成されないことが、反転層16全体の電荷量に与える影響が大きくなる。この結果、飽和領域では、N+拡散層112の幅ΣWnの全チャネル幅Wに対する割合Wnratioが、ドレイン電流Idsに与える影響が増すものと思料される。

【0058】

そして、図24(B)に示すように、反転層16は、ゲート電極115直下のシリコン基板表面のソース側の限られた範囲に形成されるため(図24(B)では、反転層116の先端はゲート電極115の中間よりもソース側に近い領域に限られる)、反転層116の全電荷量は、N+拡散層112の幅の合計(=ΣWn)が全チャネル幅Wに占める割合Wnratioの値の相違に敏感である。換言すれば、図24(B)の飽和領域においては、ゲート電極115直下の反転層115のドレイン側の縁とソース側の縁(N+拡散層112)で囲まれる領域の面積における反転層が形成されにくい領域117の占める面積の割合が、図24(A)の線形領域の場合よりも増大し、P+型のウェルコンタクト拡散層111の幅の合計(=ΣWp)が全チャネル幅Wに対して占める割合Wpratioがドレイン・ソース間電流(ドレイン電流)Idsに与える影響が大きくなるものと思料される。

【0059】

図23(A)及び図23(B)に示したような効果(Gm/WのWnratio依存性)は、図19等に示した関連技術のMOSFETモデルでは、一切考慮されていないため、取り扱うことができない。これが、図20の高耐圧MOSFET対して、精度の良い回路シミュレーション用モデルを作成することが困難であることの理由(原因)と考えられる。

【0060】

以上、ソース領域において、ゲート電極の辺に沿って、ソース拡散層112とウェルコンタクト拡散層111が隣接して交互に配置される高耐圧MOSFETにおいて、ソース拡散層112とウェルコンタクト拡散層111の幅の割合(Wnratio)に依存して変化する電気特性の特徴を表現できる回路シミュレーション用のMOSFETモデルが存在せず、このため、その実現の必要性を説明した。

【0061】

すなわち、飽和領域では、ドレイン・ソース間電流IdsのWnratio依存性が大きく、線形領域では,ドレイン・ソース間電流IdsのWnratio依存性が小さい,という特徴を表現できる回路シミュレーション用のMOSFETのモデルの実現が必要である。

【0062】

そして、MOSFETのモデルとしては、これらの電気的特性の特徴をできるだけ、少数のモデリングパラメータを用いて表現することができるMOSFETモデルの実現が望ましい。

【0063】

さらに、回路シミュレーション用のMOSFETモデルに対して、回路シミュレータに、Wnratioの値を受け渡す仕組み、あるいは、MOSFETモデル内においてWnratioの値を決定するための仕組みが望まれる。

【0064】

また、これらの特徴を表現するMOSFETモデルの抽出するための手順を確立することも望まれる。

【0065】

特に、モデル抽出に用いるTEG(Test Element Group:評価用ウェハ)の構造、抽出アルゴリズム、抽出ツールを含めた形でモデル抽出の手順が確立されることが望まれる。

【0066】

本発明によれば、ソース領域において、ソースの拡散層(NチャネルMOSFETの場合、N+拡散層、PチャネルMOSFETの場合、P+拡散層)と、ウェルコンタクト拡散層(NチャネルMOSFETの場合、P+層、PチャネルMOSFETの場合、N+層)が互いに隣接して交互に配置されたLDMOS(Laterally Diffused MOS)構造(横方向拡散MOS構造)を有する高耐圧MOSFET(横型パワーMOSトランジスタ)の回路シミュレーション用のモデル、該モデルの作成方法、及びモデル作成装置が提供される。

【0067】

図1(A)は、本発明の一つの形態による高耐圧MOSFET(NチャネルMOSFET)のマクロモデルの構成を示す図である。図1(A)に示すように、第1のMOSFET(1)、第2のMOSFET(2)、可変抵抗素子(3)から構成され、第1のMOSFET(1)のドレイン、ゲート、バックゲート(バルク)をそれぞれ第2のMOSFET(2)のドレイン、ゲート、バックゲート(バルク)に接続して、それぞれ、高耐圧MOSFETマクロモデルのドレイン端子D、ゲート端子G、バックゲート(バルク)端子Bとし、第2のMOSFET(2)のソースに可変抵抗素子(3)の一端を接続し、該可変抵抗素子(3)の他端を、第1のMOSFET(1)のソースと並列に前記高耐圧MOSFETマクロモデルのソース端子Sへ接続する。特に制限されないが、第1のMOSFET(1)、第2のMOSFET(2)は、ともにNチャネルMOSFETである。

【0068】

第1のMOSFET(1)のチャネル幅は、モデリング対象の高耐圧MOSFETのソース領域のN+拡散層12の幅Wn(図2参照)の総和(=ΣWn)とし、

第2のMOSFET(2)のチャネル幅は、モデリング対象の高耐圧MOSFETのソース領域のP+拡散層11の幅Wp(図2参照)の総和(=ΣWp)とする。

【0069】

第2のMOSFET(2)のソースに接続する可変抵抗素子(3)は、ウェルコンタクト拡散層(図2の11;P+拡散層)近傍の寄生抵抗成分が、高耐圧MOSFETのドレイン電流(ドレイン・ソース間電流)に与える影響を表現するための等価抵抗である。

【0070】

図1(A)の可変抵抗素子(3)の抵抗値Rsは、典型的には、図1(B)に示すようなゲート電圧(ゲート・ソース間電圧)Vgの依存性と、ドレイン電圧(ドレイン・ソース間電圧)Vdの依存性を反映するように、設定される。なお、ソースがGND(グランド電位)の場合、ゲート・ソース間電圧はゲート電圧と等しく、ドレイン・ソース間電圧はドレイン電圧と等しいことから、単に、ゲート電圧、ドレイン電圧ともいう。図1(B)の横軸はドレイン電圧、縦軸は可変抵抗素子(3)の抵抗値Rsである。図1(B)には、ゲート電圧一定の条件でのRs−Vd特性が、いくつかの異なるゲート電圧Vgに対してプロットされている。

【0071】

図1(B)に示すように、可変抵抗素子(3)の抵抗値Rsのバイアス依存性は、

・ドレイン電圧Vdの増加に伴い増加する第1の領域4と、

・抵抗値Rsがドレイン電圧に依存しない第2の領域5と、

の二つの領域からなる。

【0072】

図1(A)のMOSFETのモデルにおいて、第1の領域4と第2の領域5の境界で、抵抗値Rsが滑らかに接続されるように設定する。

【0073】

また、図1(A)のMOSFETのモデルにおいて、可変抵抗素子(3)の抵抗値Rsは、ゲート電圧Vgの上昇とともに、低下するように設定する。すなわち、ドレイン電圧Vdが一定の場合、ゲート電圧Vgが高くなるほど、可変抵抗素子(3)の抵抗値Rsは小さくなる。

【0074】

第1のMOSFET(1)及び第2のMOSFET(2)には、ソース領域がすべてN+拡散層12(ソース拡散層)からなる、通常構造の高耐圧MOSFET7(図3参照)に対して、抽出したモデルパラメータをそのまま、あるいは若干の修正を加えて適用する。

【0075】

なお、上記では、NチャネルMOSFETについて説明したが、PチャネルMOSFETについても、極性を反転させることで、本発明を適用することができる。

【0076】

本発明によれば、簡易かつ明確な手順に基づいて、ソース基板接続型の高耐圧MOSFETの特性を正確に表現する回路シミュレーションモデルを得ることができる。以下、いくつかの実施形態について説明する。

【0077】

<実施形態1>

図1は、本発明の実施形態1を説明する図である。図1(A)には、高耐圧MOSFETの回路シミュレーション用マクロモデルの等価回路が示されている。図1(A)において、

参照符号Dは高耐圧MOSFETシミュレーション用マクロモデルのドレイン端子、

参照符号Gは前記マクロモデルのゲート端子、

参照符号Sは前記マクロモデルのソース端子、

参照符号Bは前記マクロモデルのバックゲート(バルク)端子である。

【0078】

図1(B)に示すように、MOSFETマクロモデルは、第1のMOSFET(1)、第2のMOSFET(2)、可変抵抗素子(3)から構成され、第1のMOSFET(1)のドレイン、ゲート、バックゲート(バルク)を、第2のMOSFET(2)のドレイン、ゲート、バックゲート(バルク)にそれぞれ共通接続し、それぞれ、高耐圧MOSFETマクロモデルのドレイン端子、ゲート端子、バックゲート(バルク)端子とし、第2のMOSFET(2)のソースに可変抵抗素子(3)の一端を接続し、可変抵抗素子(3)の他端を第1のMOSFET(1)のソースとともに、高耐圧MOSFETマクロモデルのソース端子へ接続している。

【0079】

可変抵抗素子(3)は、モデリング対象の高耐圧マクロモデルのバイアス依存性、例えば、ゲート・ソース間電圧依存性(ゲート電圧依存性)とドレイン・ソース間電圧依存性(ドレイン電圧依存性)を有する。

【0080】

図2は、実施形態1のマクロモデルに対応する高耐圧NチャネルMOSFETのレイアウトを模式的に示す図である。図2において、11はソース領域のウェルコンタクト拡散層(P+拡散層)、12はソース拡散層(N+拡散層)、13はドレイン領域のN+拡散層(ドレインコンタクト用N+拡散層)、14はドレインのN−拡散層、15はゲート電極(シリコン基板上のゲート絶縁膜の上に形成されている)である。なお、N+拡散層は高濃度のN型拡散層、N−拡散層は低濃度のN型拡散層、P+拡散層は高濃度のP型拡散層をそれぞれ表している。

【0081】

なお、図2において、Nチャネル型のMOSFETは、P型ウェル内に形成されているが、例えばNチャネルMOSFETをP型シリコン基板表面に形成する場合、P+型のウェルコンタクト拡散層111はP+型の基板コンタクト拡散層となる。この場合、ウェルコンタクトを基板コンタクトと読み替えることで、以下の実施形態がそのまま適用される。

【0082】

高耐圧化のため、シリコン半導体基板表面において、ドレイン側のN+拡散層13とゲート電極15の間に低濃度N−拡散層14が配置されている。ソース側は、P+型のウェルコンタクト拡散層(P+拡散層)11とN+型のソース拡散層(N+拡散層)12が、一定の間隔で交互に配置された構造とされている。図2に例示したソース側の構造を、図20と同様に、「ソース基板接続構造」という。ソース領域の複数のウェルコンタクト拡散層(P+拡散層)11はバックゲート端子(B)に共通に接続され、複数のソース拡散層(N+拡散層)12はソース端子(S)に共通に接続され、ドレイン領域のN+拡散層13(ドレインコンタクト)はドレイン端子(D)に接続されている。

【0083】

図1(A)のMOSFETモデルにおいて、第1のMOSFET(1)のチャネル幅は、図2のソース領域のN+拡散層12の幅Wnの総和(=ΣWn)とし、第2のMOSFET(2)のチャネル幅は図2のソース領域のP+拡散層11(ウェルコンタクト)の幅Wpの総和(=ΣWp)とする。

【0084】

図1(A)のMOSFETモデルにおいて、可変抵抗素子(3)の抵抗値Rsは、図1(B)に示すように、ゲート電圧(ゲート・ソース間電圧)Vgの依存性と、ドレイン電圧(ドレイン・ソース間電圧)Vdの依存性を反映するように、設定される。すなわち、可変抵抗素子3の抵抗値Rsは、図1(B)に示すように、可変抵抗素子(3)の抵抗値Rsがドレイン電圧Vdに依存する第1の領域4と、可変抵抗素子(3)の抵抗値Rsがドレイン電圧Vdに依存しない第2の領域5を有し、第1の領域4と第2に領域5の境界で滑らかに接続されるように設定される。

【0085】

また、可変抵抗素子3の抵抗値Rsは、図1(B)に示すように、ゲート電圧Vgの上昇(低下)とともに、低下(上昇)するという特性を反映するように設定される。

【0086】

図3は、実施形態1のマクロモデル内の第1のMOSFET(1)及び第2のMOSFET(2)のモデルパラメータの初期値を抽出するために使用する通常構造の高耐圧MOSFETのレイアウトを模式的に示す図である。

【0087】

図3に示すように、通常構造7のレイアウトは、図2のソース基板接続構造6とは、ソース側の構造が異なり、ソースはN+拡散層12(チャネル幅=W)のみとなり、ウェルコンタクト層(P+拡散層)11は、N+拡散層12のゲート電極15に対向する側と反対側の領域に配置されている。

【0088】

<実施形態2>

次に、本発明の第2の実施形態を説明する。図4は、図1及び図2を参照して説明した前記実施形態1のMOSFETモデル(「マクロモデル」という)を作成するための第2の実施形態2に係るモデル作成装置の構成を示す図である。

【0089】

図4において、ウェファ21として、図2のソース基板接続構造6と、図3の通常構造7の2種類のレイアウトパターンのMOSFETを搭載したものを用意する。

【0090】

電気特性測定装置22で、ウェファ21上のソース基板接続構造の高耐圧MOSFET(図2)と、通常構造の高耐圧MOSFET(図3)のId−Vg特性(ドレイン電流−ゲート電圧特性)やId−Vd特性(ドレイン電流−ドレイン電圧特性)等の電気特性を測定する。

【0091】

記録媒体23は、ソース基板接続構造と通常構造の電気特性データ41/42、MOSFET抽出プログラム43、MOSFETモデル44、マクロモデル抽出プログラム45、マクロモデル48、モデル検証プログラム49等を記録する。なお、記録媒体23は、記録媒体を備えた記憶装置(例えばHDD(Hard Disk Drive)等の磁気ディスク記憶装置、あるいはDVD(Digital Versatile Disk)等の光ディスク記憶装置等)であってもよいことは勿論である。

【0092】

情報処理装置24は、記録媒体23から、各種測定データや各種モデルを読み込み、モデル抽出やモデル検証等の処理を行う装置である。特に制限されないが、情報処理装置24において、本実施形態で作製されたマクロモデルを用いて、例えばSPICE系シミュレータ等による回路シミュレーション等を実行してもよい。あるいは、他の情報処理装置で回路シミュレーションを実行してもよい。

【0093】

図5は、図4に示した装置によるマクロモデル作成の手順を示すフローチャートである。図4及び図5を参照して、実施形態1におえるマクロモデルの作成処理を説明する。

【0094】

処理31において、電気特性測定装置22を用いて、ウェファ21の電気特性を測定し、記録媒体23に電気特性データを格納する。この時、ソース基板接続構造の高耐圧MOSFETと通常構造の高耐圧MOSFETの2種類に関して、モデル抽出に必要な電気特性(ドレイン電流−ゲート電圧特性(Id−Vg特性)、ドレイン電流−ドレイン電圧特性(Id−Vd特性)等)を測定し、電気特性データ41、42(通常構造電気特性データ、ソース基板接続構造電気特性データ)を格納する。

【0095】

次に、処理32において、記録媒体23の電気特性データと、MOSFET抽出プログラム43を情報処理装置24に読み込み、情報処理装置24でMOSFET抽出プログラム43を実行することで、通常構造の高耐圧MOSFETモデルを作成し、記録媒体23のMOSFETモデル44に格納する。この時に使用するMOSFETモデルは、ドレイン抵抗のバイアス依存性を表現することができる高耐圧専用モデル(HiSIM_HV:Hiroshima University Starc IGFET Model High Voltage/large current)等、図19(C)参照)を用い、また、ドレイン電流のチャネル長Lの依存性もある程度合わせておく。

【0096】

次に、処理33において、記録媒体23のMOSFETモデル44とマクロモデル抽出プログラム45を情報処理装置24に読み込み、マクロモデル抽出プログラム45を実行することで、図1(A)に示した、ソース基板接続構造の高耐圧MOSFETのマクロモデルを作成し、記憶媒体23にマクロモデル48として格納する。この時、MOSFETモデル(図4の44)の中身は変更せずに、図1(A)の可変抵抗素子3のみを調整する。すなわち、可変抵抗素子3には、ゲート電圧Vg依存性とドレイン電圧Vd依存性を取り入れる。

【0097】

次に、処理34において、ソース基板接続構造の高耐圧MOSFETのマクロモデル48を再調整する(必要に応じて記録媒体23のマクロモデル48とマクロモデル抽出プログラム45を情報処理装置24に読み込む)。処理34では、特に、MOSFETのドレイン抵抗に関するパラメータに注目して調整する。図1(A)では、ドレイン抵抗((図19(A)の可変抵抗素子101参照)に関するパラメータは、モデルに組み込まれており、処理34では、このドレイン抵抗に関するパラメータを調整する。

【0098】

次に、処理35において、記録媒体23のマクロモデル48とモデル検証プログラム49を情報処理装置24に読み込み、モデル検証プログラム49を実行することで、マクロモデル48の検証を行う。

【0099】

次に、処理36において、モデル検証プログラム49で実行されたマクロモデルの検証結果を判断し(例えば情報処理装置24の出力装置に出力されたマクロモデルの検証結果を見てユーザが判断してもよいし、情報処理装置24で自動で判断してもよい)、問題がなければ終了し(処理36のOK分岐)、問題がある場合には(処理36のNG分岐)、処理34へ戻り、処理36での検証結果がOKになるまで繰り返す。

【0100】

次に、図13を参照して、図4に示した実施形態2の装置によるマクロモデルの作成手順を詳細に説明する。

【0101】

電気特性測定装置22を用いて、ウェファ21に搭載されたソース基板接続構造の高耐圧MOSFET(図2)と通常構造の高耐圧MOSFET(図3)の2種類のパターンの電気特性を測定する。通常構造の高耐圧MOSFET(図3)とソース基板接続構造の高耐圧MOSFET(図2)の測定データは、通常構造電気特性データ41、ソース基板接続構造電気特性データ42として、それぞれ記録媒体(図4の23)に格納する。

【0102】

次に、情報処理装置24(図4)は、MOSFET抽出プログラム43を用いて、通常構造電気特性データ41を読み込み、MOSFETの閾値電圧やドレイン電流特性(例えばId−Vg特性、Id−Vd特性)が、前記通常構造電気特性データ41と一致するようにモデル抽出を行い、MOSFETモデル44として、記録媒体(図4の23)へ格納する。

【0103】

MOSFETモデルは、ドレイン抵抗のバイアス依存性が表現できる高耐圧専用モデル(HiSIM_HV等、図19(C)参照)を用い、ドレイン電流のチャネル長依存性もある程度合わせておく。

【0104】

次に、情報処理装置24(図4)は、マクロモデル抽出プログラム45を用いて、記録媒体23(図4)から、MOSFETモデル44とソース基板接続構造電気特性データ42を読み込み、ソース基板接続構造のマクロモデルを作成し、MOSFETの閾値電圧やドレイン電流特性(例えばId−Vg特性、Id−Vd特性)が、ソース基板接続構造電気特性データ42と一致するように、モデル抽出を行い、仮マクロモデル46として、記録媒体へ格納する。

【0105】

この時、情報処理装置24(図4)のマクロモデル抽出プログラム45は、MOSFETモデル44の中身は変更せずに、可変抵抗素子3のみを調整する。

【0106】

可変抵抗素子3の抵抗値Rsは、ゲート電圧Vg依存性とドレイン電圧Vd依存性を組み込む。その一例を以下に示す。

【0107】

Rs' = (Rs0 + Rs1 * Vg + Rs2 * Vg2)/W (1)

【0108】

Rs = Rs' * (f(Vd,δ)* 0.5 + 0.5) (2)

【0109】

f(Vd,δ) = (Vg - 0.5 * (Vg - Vd -δ + sqrt((Vg - Vd -δ)2 + 4 *δ*Vg)))/Vg (3)

【0110】

δ = 0.01 (4)

【0111】

ここで、Vgはゲート電圧(ゲート・ソース間電圧)、Vdはドレイン電圧(ドレイン・ソース間電圧)である。また、Wは全チャネル幅(W=ΣWn+ΣWp)である。Rsは可変抵抗素子3の抵抗値である。

【0112】

また式(3)の関数f(Vd,δ)は、スムージング関数であり、座標(Vd,f(Vd))において、原点(0,0)を通る傾き1/Vgの直線(0≦Vd<Vg)と、Vd>Vgでf(Vd)=1となり、ドレイン電圧Vd=Vg前後で滑らかに接続する。δの値を大きくすると、Vd=Vg近辺で緩やかに変化する。

【0113】

したがって、式(2)のRs(可変抵抗素子3の抵抗値)は、Vd=0でRs、0<Vd<Vgで傾き1/Vgの直線、Vd>Vgで、Rs'となり、Vd=Vg前後で滑らかに接続する。

【0114】

また、可変抵抗素子3の別の例を次式(1')〜(3')に示す。

【0115】

Rs = ((Rs0 + Rs1 * Vg + Rs2 * Vg2 ) * f (Vd) + Rs3)/W (1')

【0116】

f (Vd,δ) = (Vdsat - 0.5 * (Vdsat-Vd-δ + ((Vdsat-Vd-δ)2 + 4*δ*Vdsat)0.5 ))/Vdsat (2')

【0117】

Vdsat = (Vg - Vt) fac1/fac2 (3')

【0118】

式(3')の飽和ドレイン電圧Vdsatにおけるパラメータfac1 と fac2はドリフト抵抗での電圧ドロップの影響により生じる、測定される見かけの飽和電圧と、MOSFET(トランジスタ)内のピンチオフ電圧の差を補正するためのフィッティングパラメータである。VtはMOSFETの閾値電圧である。MOSFETのピンチオフ電圧は、ドリフト領域の有無に余り依存しないが、高耐圧MOSFETではドリフト領域寄生抵抗による電圧降下により、この電圧降下がない場合に比べて、見かけ上高い電圧でMOSFETのピンチオフが起こることを補正するものである。この補正は、ゲート長が短いトランジスタの場合に特に必要となる。

【0119】

次に、情報処理装置24(図4)は、マクロモデル調整プログラム47を用いて、記録媒体23(図4)から、仮マクロモデル46と、ソース基板接続構造電気特性データ42を読み込み、特にId−Vd特性の線形領域と飽和領域の境界付近が合うように、仮マクロモデル46内のMOSFETモデルのドレイン抵抗関係のパラメータを調整し、マクロモデル48として記録媒体23(図4)へ格納する。

【0120】

次に、情報処理装置24(図4)は、マクロモデル検証プログラム49を用いて、記録媒体23(図4)から、マクロモデル48とソース基板接続構造電気特性データ42を読み込み、マクロモデルの検証を行う。

【0121】

ここでは、様々なチャネル長、チャネル幅の測定データに対して、電気特性の一致精度及び、チャネル長依存性、チャネル幅依存性を検証し、その結果を、マクロモデル検証結果50として記録媒体23(図4)へ格納する。

【0122】

次に、マクロモデル検証結果50を判断し、問題がなければ、前記マクロモデル48を最終結果として終了し、問題ある場合には、マクロモデル調整処理(前記マクロモデル調整プログラム47)へ戻り、検証結果がOK(可)となるまで繰り返す。この時の入力データは、仮マクロモデル46の代わりに、記録媒体23(図4)からマクロモデル48を読み込む。

【0123】

実施形態1、2の作用効果について説明する。

【0124】

モデル対象のソース基板接続構造を有する高耐圧MOSFETにおいて、

N+拡散層(図2の12)に隣接する領域の電流を、第1のMOSFET(図1の1)で表わし、

P+拡散層(ウェルコンタクト拡散層、図2の11)に隣接する領域の電流を可変抵抗素子(図1の3)と第2のMOSFET(図1の2)の直列接続回路によって表わし、

N+拡散層(図2の12)のチャネル幅Wn(総和)と、P+拡散層(ウェルコンタクト拡散層、図2の11)のチャネル幅Wp(総和)を、それぞれ、第1のMOSFET1のチャネル幅と、第2のMOSFET2のチャネル幅としてマクロモデルに取り入れることにより、N+拡散層(図2の12)とP+拡散層(図2の11)のチャネル幅の割合(例えばWnratio=ΣWn/(ΣWn+ΣWp))に依存して変化するMOSFETの特性を、高精度にフィッティングすることができた。

【0125】

ソース基板接続構造の高耐圧MOSFETに特有のP+拡散層(ウェルコンタクト拡散層、図2の11)近傍でのバイアスに依存したキャリアの流れについては、高耐圧MOSFETのドレイン・ソース間電流Idsに与える影響を表現することができる等価抵抗を、可変抵抗素子3(図1参照)として、第2のMOSFET(2)のソースに直列に接続することで解決した。

【0126】

ソース基板接続構造の高耐圧MOSFETでは、図24(A)及び図24(B)を参照して説明したように、P+拡散層111(ウェルコンタクト拡散層)近傍のチャネル領域では、反転層116が形成されにくいため(領域117参照)、見かけ上、抵抗が付加された形となり、しかも、P+拡散層11の近傍は、ゲート電極115で覆われているので、この抵抗値は、ゲート電圧(ゲート・ソース間電圧)Vgs依存性を持つことになる。

【0127】

本実施形態では、P+拡散層(図2の11)近傍の抵抗成分(寄生抵抗)を、抵抗値Rsがゲート・ソース間電圧Vgsに依存する抵抗(図1の可変抵抗素子3)で表現している。より具体的には、ゲート・ソース間電圧Vgsが高いときは、ゲート・ソース間電圧Vgsが低い場合に比べ、P+拡散層11(図2の11)の周囲のチャネル領域には、相対的に、反転層が形成され易くなり、寄生抵抗の抵抗値は低下すると考えられる。このことから、寄生抵抗は、ゲート・ソース間電圧Vgsが高くなると、その抵抗値が下がるようなゲート・ソース間電圧Vgs依存性を持たせた(図1(B)のRs参照)。

【0128】

また、ソース基板接続構造の高耐圧MOSFETに特有の特性(図22乃至図24、及びそれらの関連説明参照)を表現するため、可変抵抗素子3(図1参照)に、ドレイン・ソース間電圧(ドレイン電圧)Vds依存性を持たせた。その典型的な形態について、図6を参照して説明する。

【0129】

図6(A)は、図2のレイアウト構造のMOSFETのゲート電極15直下のシリコン半導体基板表面に形成されるチャネルを模式的に等価回路で示した図である。図6(B)は、図6(A)の可変抵抗素子3の抵抗値Rsのドレイン・ソース間電圧(ドレイン電圧)依存特性を示す図であり、横軸はドレイン電圧、縦軸は可変抵抗素子3の抵抗値Rsである。

【0130】

図6(A)に示すように、ソース領域のN+拡散層12とドレイン(低濃度ドレイン拡散層(N−拡散層)14、ドレイン拡散層(N+拡散層)13)間には、図1の第1のMOSFET1が接続され、ウェルコンタクト拡散層であるP+拡散層11とドレイン(14、13)間には、図1の第2のMOSFET2が接続され、第2のMOSFET2のソースとP+拡散層11(図1の端子S)間には、抵抗値Rsが可変の可変抵抗素子3が接続されている。図6(A)では、第1のMOSFET1がドレインとN+拡散層12間に2個、第2のMOSFET2と可変抵抗素子3の直列回路がドレインとP+拡散層11間に3組、並列に接続されている。これら第1、第2のMOSFET1、2(計5個)のゲートは共通接続され、MOSFETモデルのゲート端子(図1のG)に接続され、ドレインは共通接続され、MOSFETモデルのドレイン端子(図1のD)に接続される。2個のN+拡散層11は共通接続され、MOSFETモデルのソース端子(図1のS)に接続され、3個のP+拡散層11は共通接続され、MOSFETモデルのバックゲート(バルク)端子(図1のB)に接続される。

【0131】

図6(B)において、可変抵抗素子3の抵抗値Rsのドレイン電圧依存性は、抵抗値Rsがドレイン電圧Vdの増加に伴い増加する第1の領域4と、抵抗値Rsがドレイン電圧Vdに依存しない第2の領域5の二つの領域から構成される。

【0132】

より典型的には、第1の領域4と第2の領域5の境界では、式(3)のスムージング関数f(Vd,δ)により、抵抗値Rsが滑らかに接続されるように構成される。

【0133】

また、より典型的には、第1の領域4と第2の領域5の境界は、モデリング対象とする高耐圧MOSFETの線形領域と飽和領域の境界、あるいは、その付近に設定される。これは、図24(A)に示すように、ドレイン電圧Vdの低い領域(線形領域)では、P+拡散層111の存在がドレイン電流Id(ドレイン・ソース間電流Ids)に与える影響が小さく、図24(B)に示すように、ドレイン電圧Vdの高い領域(飽和領域)では、P+拡散層111の存在がドレイン電流Id(ドレイン・ソース間電流Ids)に与える影響が大きい、ことを表現したものである。

【0134】

本実施形態によれば、以上の作用によって、ソース基板接続構造を持つ高耐圧MOSFETに特有のバイアス電圧依存性を高精度に表現することができた。

【0135】

また、図6(A)において、P+拡散層11に隣接する反転層が充分に形成されない領域(図24(A)、(B)の117)がドレイン電流Idに与える影響を、ドレイン電圧Vd及びゲート電圧Vgに依存する可変抵抗素子3によって表現する。このため、マクロモデル作成にあたり、追加が必要なパラメータは、可変抵抗素子3に係わる少数のパラメータ(例えば式(1)のRs0、Rs1、Rs2等)である。

【0136】

すなわち、本実施形態によれば、MOSFETモデルの調整や改良を行った場合に予想されるフィッティング対象パラメータの大きな増大はなく、フィッティング方法が確立されている通常構造の高耐圧MOSFETモデルを起点に、可変抵抗素子3に関する少数のモデリングパラメータ(式(1)、(2)等のRs0、Rs1、Rs2等)をフィッティングすることにより、精度の良いマクロモデルを形成することができた。

【0137】

また、本実施形態のマクロモデルの構成によれば、回路シミュレーションの実行にあたり、MOSFETモデルに対して、

Wnratioの値をインスタンスパラメータ(インスタンス名で特定される素子に設定するパラメータ)として受け渡す、あるいは、

図2、図6のN+拡散層12とP+拡散層11のそれぞれに対応するチャネル幅Wn、Wpを受け渡す、あるいは、

モデル内においてチャネル幅Wの関数としてWnratioの値を計算する、

ことにより、マクロモデル内において用いるWnratioの値を特定することができる。

【0138】

また、ソース領域が全てN+拡散層12により形成される通常構造の高耐圧MOSFET(図3参照)の特性測定パターンを用意して電気特性の測定を行い、その測定結果に基づき通常構造の高耐圧MOSFETモデルを一旦作成したあと、通常構造の高耐圧MOSFETモデルと可変抵抗素子3により構成される高耐圧MOSFETモデルのマクロモデルを作成し、可変抵抗素子3の少数のパラメータを調整するという、簡易で、手順が明確な方法により、回路シミュレーション用のモデルを作成することができる。

【0139】

なお、本実施形態では、図6(B)に示すように、可変抵抗素子3を、抵抗値がドレイン電圧Vdの増加に伴い増加する第1の領域4と、抵抗値がドレイン電圧に依存しない第2の領域5の二つの領域から構成される例を示したが、精度に対する要求が低い場合は、単一の領域からなるモデルで可変抵抗素子3を表現しても良い。但し、モデルの精度が要求される場合には、前記の通り二つの領域からなるモデル、あるいは、以下に実施形態4で説明するように、三つ以上の領域からなるモデルで、可変抵抗素子3を表現することが好ましい。

【0140】

可変抵抗素子3のモデルにおける、第1の領域4と第2の領域5の境界は、例えば、モデル対象とするMOSFETの線形領域と飽和領域の境界付近のドレイン電圧Vdを選択する。あるいは、モデル対象とするMOSFETの線形領域と飽和領域の境界よりも高めのドレイン電圧Vd、典型的には、線形領域と飽和領域の境界となるドレイン電圧Vdの1〜2.5倍程度の値としてもよい。なお、MOSFETの線形領域と飽和領域の境界のドレイン電圧は、「飽和電圧」と呼ばれる。

【0141】

なお、上記実施形態1、2においては、NチャネルMOSFETについて記載したが、PチャネルMOSFETについても実施形態1の極性を反転させることで、同様にして本発明を適用することができる(PチャネルMOSFETではソース端子電圧がドレイン端子電圧よりも高電圧とされ、ゲート・ソース間電圧Vgsは負値又は0となる)。

【0142】

図7(A)と図7(B)は、本実施形態による高耐圧MOSFETについて、異なるWnratioに関して、ドレイン電流−ドレイン電圧特性(Id−Vd特性)をモデリングした結果(実線)と、実測値(▲)と、図19の従来モデル(破線、図21に対応)を比較して示す図である。ここで、Wnratioは、図2の全チャネル幅W(=ΣWn+ΣWp)に対して、各N+型ソース拡散層(N+拡散層)12の幅Wnの合計ΣWnが占める割合(%表記)である。

【0143】

Wnratio={(ΣWn)/(ΣWn+ΣWp)}×100

【0144】

図7(A)では、Wnratio=48%、図7(B)では、Wnratio=40%としている。なお、図7(A)、図7(B)において、横軸はドレイン電圧(drain−to−source voltage)Vds(単位:Voltage)、縦軸はドレイン電流(drain−to−source current)Id(単位:Ampere)であり、ゲート電圧(gate−to−source voltage)Vgsを0〜5Vまで1Vステップで変化させたId−Vdカーブが示されている。Vgs=0Vでは、MOSFETはオフ状態であり、ドレイン電流Id=0である。

【0145】

図7(A)では、▲マークで示した実測値と、実線で示す実施形態と、破線で示す関連技術によるモデリング結果(従来モデル)とは、Vdsの全範囲、ゲート・ソース間電圧(ゲート電圧)Vgs=0、1、2、・・・、5Vの全てについて、比較的良く一致している。

【0146】

図7(B)では、実測値(▲)と、実線で示す実施形態のモデルリング結果とは、線形領域、及び、飽和領域のいずれについてもほぼ一致している。

【0147】

一方、図7(B)において、破線で示す従来モデルでは、飽和領域で一致しない(特に、飽和領域のうち、ゲート電圧Vgsが高い領域で実測値(▲)との差異が顕著となる)。

【0148】

図8(A)と図8(B)は、NチャネルMOSFETがオンした状態におけるドレイン電流(ドレイン・ソース間電流)Idsを、Wnratioが異なる素子(MOSFET)間で比較したものである。なお、図8において、縦軸のドレイン電流は全チャネル幅Wで規格化し、Ids/Wとしている。横軸の素子(MOSFET)AのWnratioは40%、素子(MOSFET)B、CのWnratioは48%である(なお、素子BとCは、Wnratioは共通であるが、別のMOSFETである)。図8(A)に示すように、実線で示す本発明の実施形態と、●で示す実測値とはほぼ一致している(破線で示す従来モデルもほぼ一致している)。

【0149】

図8(A)に示した線形領域(ドレイン・ソース間電圧Vds=0.1V、ゲート電圧Vg=5V)では、全チャネル幅Wで規格化したドレイン電流Ids/Wの実測値(●)は、Wnratio=40%の素子Aと、Wnratio=48%の素子B、Cでほぼ略等しく、Wnratioにほとんど依存しない。また図2、図6に示した実施形態を用いたモデリング結果Ids/Wは、図8(A)に示すように、線形領域では、素子AのWnratio=40%、素子B、CのWnratio=48%のいずれの実測値(●)とも交差しており、ほぼ一致していることが分かる。なお、図22(A)を参照して説明したように、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果Ids/Wは、図8(A)に示すように、線形領域では、Wnratio=40%の素子A、Wnratio=48%の素子B、Cのいずれの実測値(●)とも交差しており、ほぼ一致している。

【0150】

図8(B)に示した飽和領域(ドレイン・ソース間電圧Vds=12V、ゲート電圧Vg=5V)では、全チャネル幅W(=ΣWn+ΣWp)で規格化したドレイン電流Ids/Wの実測値(●で示す)は、Wnratioに依存して変化する。

【0151】

図8(B)に示した飽和領域において、Wnratio=40%の素子Aでは、Ids/Wの実測値(●で示す)と、図2、図6に示した実施形態を用いたモデリング結果Ids/Wは一致している。一方、図19等の関連技術のモデル(従来モデル)を用いたモデリング結果(破線と素子Aの交差部)では、Ids/Wは、Wnratio=40%の素子Aに関して、実測値との差異が顕著である。

【0152】

なお、図8(B)において、Wnratio=48%の素子B、Cについても、実施形態(実線)は実測値(●)と一致している。なお、破線で示す従来モデルも、Wnratio=48%の素子B、Cについて、実測値(●)とほぼ一致している。

【0153】

<実施形態3>

図9は、本発明の実施形態3において、高耐圧MOSFETの回路シミュレーション用マクロモデルを等価回路で示す図である。

【0154】

図9において、

参照符号Dは、高耐圧MOSFETシミュレーション用マクロモデルのドレイン端子、

参照符号Gは、該マクロモデルのゲート端子、

参照符号Sは、該記マクロモデルのソース端子、

参照符号Bは、該マクロモデルのウェル端子

である。

【0155】

図9を参照すると、このマクロモデルは、

第1のMOSFET(151)、

第2のMOSFET(152)、

第1の可変抵抗素子(153)、

第2の可変抵抗素子(154)、

第3の可変抵抗素子(155)

から構成されている。

【0156】

第1のMOSFET(151)のゲート、バルク(バックゲート)を第2のMOSFET(152)のゲート、バルクにそれぞれ共通接続し、それぞれ高耐圧MOSFETマクロモデルのゲート端子(G)、バルク端子(B)としている。

【0157】

第1のMOSFET(151)のドレインに第1の可変抵抗素子(153)の一端を接続し、第2のMOSFET(152)のドレインに第2の可変抵抗素子(154)の一端を接続し、第1の可変抵抗素子(153)の他端と、第2の可変抵抗素子(154)の他端をともに高耐圧MOSFETマクロモデルのドレイン端子(D)へ接続している。

【0158】

第2のMOSFET(152)のソースに、第3の可変抵抗素子(155)の一端を接続し、第3の可変抵抗素子(155)の他端を、第1のMOSFET(151)のソースとともに高耐圧MOSFETマクロモデルのソース端子(S)へ接続している。

【0159】

第1及び第2の可変抵抗素子(153、154)は、高耐圧マクロモデルのドレイン電圧に対する依存性を有する。

【0160】

第3の可変抵抗素子(155)は、図1の可変抵抗素子(3)に相当し、高耐圧マクロモデルのゲート電圧Vgに対する依存性とドレイン電圧Vdに対する依存性を有する。

【0161】

前記実施形態1、2と本実施形態との相違点は、第1のMOSFET(151)及び第2のMOSFET(152)のドレインにそれぞれ第1の可変抵抗素子(153)と第2の可変抵抗素子(154)を直列に挿入した点である。

【0162】

前記実施形態1、2では、ドレイン抵抗のドレイン電圧依存性を表現できる高耐圧専用モデル(HiSIM_HV等)を必要とするが、実施形態3では、通常のMOSFETモデル(BSIM3(Berkley Short−channel IGFET(Insulated Gate FET) Model)、BSIM4等)を使用することできる。

【0163】

<実施形態4>

次に、本発明の実施形態4について説明する。本実施形態は、図9に示した実施形態3のマクロモデルを作成するための装置に関する実施形態である。図11は、実施形態4の構成を示す図である。なお、図11において、図4と同一又は同等の要素には、同一の参照符号が付されている。

【0164】

図11を参照すると、ウェファ21は、ソース基板接続構造(図2)と通常構造(図3)の2種類のパターンのMOSFETを搭載したものを用意する。

【0165】

電気特性測定装置22で、ウェファ21のMOSFET(ソース基板接続構造と通常構造)のId−Vg、Id−Vd特性等の電気特性を測定する。

【0166】

記録媒体25(あるいは記憶装置)は、電気特性データ41/42、MOSFET抽出プログラム43、MOSFETモデル44、マクロモデル1抽出プログラム45−1、マクロモデル1(48−1)、マクロモデル2抽出プログラム45−2、マクロモデル2(48−2)、モデル検証プログラム49等を記録する。

【0167】

情報処理装置24は、各種測定データや各種モデルを読み込み、モデル抽出やモデル検証を行う装置である。

【0168】

本実施形態と、前記実施形態2との相違点は、マクロモデルの作成が2種類に分かれている点である。

【0169】

図12は、図11の装置において、マクロモデルの作成手順を示すフローチャートである。なお、図12において、図5と同一又は同等の処理を行う処理は、同一の参照番号が付されている。

【0170】

まず、処理31において、電気特性測定装置22を用いて、ウェファ21の電気特性を測定し、記録媒体25に、電気特性データ41/42を格納する。この時、ソース基板接続構造と通常構造の2種類のパターンでモデル抽出に必要な電気特性(ドレイン電流−ゲート電圧特性(Id−Vg特性)、ドレイン電流−ドレイン電圧特性(Id−Vd特性)等)を測定し電気特性データ41、42として記録する。

【0171】

次に、処理32において、記録媒体25の電気特性データ41/42とMOSFET抽出プログラム43を情報処理装置24に読み込み、通常構造の高耐圧MOSFETモデル44を作成する。この時に使用するモデルは、通常のMOSFETモデル(BSIM3、BSIM4等)を用い、ドレイン電流のチャネル長依存性もある程度合わせておく。ドレイン電流−ドレイン電圧特性(Id−Vd特性)において、ゲート電圧Vgの高い領域が合わない場合があるが、そのまま次へ進む。

【0172】

次に、処理37において記録媒体25の電気特性データ41/42とMOSFETモデル44とマクロモデル1抽出プログラム45−1を情報処理装置24に読み込み、図10に示す通常構造の高耐圧MOSFETのマクロモデル1(48−1)を作成する。

【0173】