高速スイッチング動作回路

【課題】より高電圧をより高速にスイッチングできる高速スイッチング動作回路を提供する。

【解決手段】DC/DCコンバータ1は、活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子10を有する。駆動回路11は、スイッチング素子10を1MHz以上の駆動周波数で駆動する。スイッチング素子10のスイッチング時の電圧変化速度は5×109V/秒以上である。前記MISFETは、活性領域に形成されたトレンチと、トレンチの底面および壁面を絶縁膜と、絶縁膜を介して活性領域に対向するゲート電極とを含むトレンチゲート構造を有していてもよい。

【解決手段】DC/DCコンバータ1は、活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子10を有する。駆動回路11は、スイッチング素子10を1MHz以上の駆動周波数で駆動する。スイッチング素子10のスイッチング時の電圧変化速度は5×109V/秒以上である。前記MISFETは、活性領域に形成されたトレンチと、トレンチの底面および壁面を絶縁膜と、絶縁膜を介して活性領域に対向するゲート電極とを含むトレンチゲート構造を有していてもよい。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、高速スイッチング動作回路に関する。高速スイッチング動作回路の例は、DC/DCコンバータ、AC/DCコンバータ、ワイヤレス給電回路を含む。

【背景技術】

【0002】

DC/DCコンバータその他の高速スイッチング動作回路は、電源電圧を高速でスイッチングするスイッチング素子を含む。スイッチング素子には、シリコン半導体で活性層を形成したMOSFET(Metal-Oxide-Semiconductor Field-Effect-Transistor)が適用されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−41388号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

シリコンデバイスの高耐圧化および高速化は、限界に近づいてきており、より高い電圧をより高速にスイッチングできるスイッチング素子を用いた高速スイッチング動作回路を実現することができない。

そこで、この発明の目的は、より高電圧をより高速にスイッチングできる高速スイッチング動作回路を提供することである。

【課題を解決するための手段】

【0005】

この発明は、活性領域がSiC半導体からなるMISFET(Metal-Insulator-Semiconductor Field-Effect-Transistor)で構成されたスイッチング素子を有し、前記スイッチング素子が1MHz以上の駆動周波数で駆動され、かつスイッチング時の電圧変化速度が5×109V/秒以上である、高速スイッチング動作回路を提供する。

一つの実施形態においては、前記MISFETが、前記活性領域に形成されたトレンチと、前記トレンチの底面および壁面を絶縁膜と、前記絶縁膜を介して前記活性領域に対向するゲート電極とを含む、トレンチゲート構造を有している。

【0006】

前記絶縁膜は、前記トレンチの底面を覆う底面被覆部の厚さが、前記トレンチの壁面を覆う壁面被覆部の厚さよりも厚いことが好ましい。

一つの実施形態においては、前記MISFETの動作電圧が100V以上であり、前記MISFETの破壊電圧が900V以上である。

一つの実施形態においては、前記MISFETのドレイン−ソース間の電圧を0.1Vとし、前記MISFETのゲートに1MHzの振動周波数の信号を与えて測定したときに、前記MISFETの入力容量が700pF未満であり、前記MISFETの出力容量が600pF未満であり、かつ前記MISFETの帰還容量が400pF未満である。

【0007】

一つの実施形態においては、前記MISFETのゲート−ソース間電圧が18Vのときに、前記MISFETのオン抵抗が4mΩcm2以下である。

一つの実施形態においては、前記MISFETは、オン抵抗Ronと全ゲート電荷量Qgとの積で表される性能指数Ron・Qgが5ΩnC未満である。

前記MISFETの寄生ゲート抵抗は、30Ω以下であることが好ましい。

【0008】

一つの実施形態においては、前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ドレイン電極を支持基板(たとえばリードフレームのアイランド)に接合したフェースアップ方式で前記チップが実装されており、前記ゲート電極およびソース電極にそれぞれゲートワイヤおよびソースワイヤが接続されていて、前記ゲートワイヤは、直径100μm以上、長さ5mm以下であり、前記ソースワイヤは、直径300μm以上、長さ5mm以下である。

【0009】

別の実施形態においては、前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ゲート電極およびソース電極を支持基板(たとえばリードフレームのアイランド)に接合したフェースダウン方式で前記チップが実装されている。

一つの実施形態に係る高速スイッチング動作回路は、前記スイッチング素子に一端が接続されたチョークコイルを有する。

【0010】

一つの実施形態においては、電源電圧ラインとグランドラインとが互いに平行に形成されている。

一つの実施形態においては、前記グランドラインが形成された第1配線層と、前記電源電圧ラインが前記グランドラインにオーバレイするように形成された第2配線層とを含む多層配線基板上に前記MISFETが実装されている。

【図面の簡単な説明】

【0011】

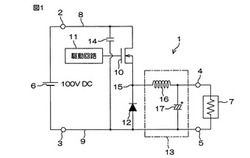

【図1】図1は、この発明の第1の実施形態に係る高速スイッチング動作回路であるDC/DCコンバータの電気回路図である。

【図2】図2は、スイッチング素子の構造を説明するための図解的な平面図である。

【図3】図3は、MOSFETチップのソース電極から下の構成を示す部分拡大平面図である。

【図4】図4は、図3の切断面線IV−IVから見た断面図である。

【図5】図5は、SiCで活性領域を構成したMOSFETチップと、Si半導体で活性領域を構成したスーパージャンクション型MOSFETとの性能指数比較結果を示す。

【図6】図6は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとで容量を比較した測定結果を示す。

【図7】図7は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとにおいて、スイッチング特性を測定した結果を示す。

【図8】図8は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとのターンオフ遅延時間および下降時間の測定結果を比較して示す図である。

【図9】図9は、図1に示したDC/DCコンバータにおいて、スイッチング素子として、SiC・MOSFETチップを内蔵したもの(実施例)と、SiC・MOSFETチップに代えてSiスーパージャンクション型MOSFETを適用した比較例とで、効率を測定した測定結果を示す。

【図10】図10は、スイッチング素子のパッケージ構造に関する変形例を示す図解的な平面図である。

【図11】図11は、この発明の第2の実施形態に係る高速スイッチング動作回路であるAC/DC電源回路(いわゆるACアダプタ)の構成を示す電気回路図である。

【図12】図12は、スイッチング素子をターンオフした後のソース−ドレイン間電圧の時間変化を示す波形図である。

【図13】図13は、この発明の第3の実施形態に係る高速スイッチング動作回路であるワイヤレス給電装置の電気的構成を示す回路図である。

【図14】図14は、駆動回路から第1スイッチング素子のゲートに供給される第1制御信号と、駆動回路から第2スイッチング素子のゲートに供給される第2制御信号と、高周波トランスの二次側巻線に導出される電圧波形とを示す波形図である。

【図15】図15は、ワイヤレス給電装置の具体的な構成例を説明するための図解的な斜視図である。

【図16】図16は、電極保持板に対する出力電極およびコイルの取付構造例を説明するための図解的な拡大断面図である。

【図17】図17は、高周波回路の構成例を示す図解的な斜視図である。

【図18】図18は、第1配線層、第2配線層および第3配線層にそれぞれ形成された配線パターンの例を説明するための図解的な斜視図である。

【図19】図19は、図15および図16に示した電極保持板に代えて用いることができる電極保持板の構造例を示す部分拡大断面図である。

【発明を実施するための形態】

【0012】

以下では、この発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、この発明の第1の実施形態に係る高速スイッチング動作回路であるDC/DCコンバータの電気回路図である。DC/DCコンバータ1は、電源端子2,3に供給される直流電源電圧を変換して(この実施形態では降圧して)、変換後の直流電圧を出力端子4,5の間に出力するように構成されている。電源端子2,3の間には直流電源6が接続される。より具体的には、電源端子2に直流電源6の正極が接続され、電源端子3に直流電源6の負極が接続される。一方、出力端子4,5の間には変換後の直流電圧を供給すべき負荷7が接続される。

【0013】

DC/DCコンバータ1は、スイッチング素子10と、駆動回路11と、整流用素子としてのダイオード12と、平滑回路13と、電解コンデンサ14とを備えている。電源端子2は電源電圧ライン8に接続されており、電源端子3はグランドライン9に接続されている。整流用素子としては、ダイオードに限らず、SiC・MOSFETを使用してもよく、それによりさらに効率向上を期待できる。電解コンデンサ14は、電源電圧ライン8とグランドライン9との間に接続されている。スイッチング素子10は、この実施形態では、nチャネル型MOSFETで構成されていて、そのドレイン端子が電源電圧ライン8に接続され、そのソース端子がダイオード12のカソードに接続されている。ダイオード12のアノードは、グランドライン9に接続されている。ダイオード12は、ショットキバリアダイオードであってもよい。後述するように、スイッチング素子10は、SiC(炭化シリコン)を半導体活性領域に適用したMOSFETで構成されている。スイッチング素子10のゲート端子には、駆動回路11が接続されている。駆動回路11は、スイッチング素子10をスイッチングするための制御信号を供給するように構成されている。制御信号は、矩形波信号であってもよいし、正弦波信号であってもよい。

【0014】

平滑回路13は、スイッチング素子10とダイオード12との接続点15に導出される電圧を平滑して出力端子4に供給するように構成されている。平滑回路13は、チョークコイル16と電解コンデンサ17とを含む。チョークコイル16は、その一方の端子が接続点15に接続されており、その他方の端子が出力端子4に接続されている。そして、当該他方の端子とグランドライン9との間に電解コンデンサ17が接続されている。電解コンデンサ17は、その正極側の端子が出力端子4側となるように接続されている。

【0015】

駆動回路11からの制御信号がスイッチング素子10のゲートに供給されることにより、スイッチング素子10がターンオンすると、直流電源6から供給される電流がチョークコイル16へと流れ込み、このチョークコイル16にエネルギーが蓄えられるとともに、電解コンデンサ17が充電されて、出力端子4の電位が上がる。その後、駆動回路11からの制御信号によってスイッチング素子10がターンオフすると、チョークコイル16は、接続点15から出力端子4へと向かう電流を保とうとするので、ダイオード12を通って電流が流れ、出力端子4に導出される電圧が保持される。チョークコイル16の出力端子4側に現れる電圧が電解コンデンサ14によって平滑されることにより、出力端子4には安定した電圧が導出される。このような動作により、電源端子2,3の間に供給される直流電圧がスイッチング素子10のゲートに与えられる制御信号のデューティ比に応じて降圧され、その降圧された直流電圧が出力端子4,5の間に導出される。

【0016】

電解コンデンサ14は、直流電源6から供給される電圧を保持し、スイッチング素子10の近くから当該スイッチング素子10に電流を供給することにより、直流電源6から電源端子2,3に至るケーブルのインダクタンスの影響を低減する。

図2は、スイッチング素子10の構造を説明するための図解的な平面図である。スイッチング素子10は、MOSFETチップ20と、リードフレーム21と、モールド樹脂22(図2では二点鎖線で示す)とを含む。

【0017】

MOSFETチップ20は、一方の表面にゲート電極(パッド)23およびソース電極(パッド)24を有し、他方の表面にドレイン電極25(図4参照)を有している。

リードフレーム21は、ゲート端子を構成するゲートリード26と、ソース端子を構成するソースリード27と、ドレイン端子を構成するドレインリード28とを有している。この実施形態では、ゲートリード26、ソースリード27およびドレインリード28は、同一平面上に位置するように配置された板状体からなっていて、ドレインリード28がゲートリード26およびソースリード27の間に配置されている。ドレインリード28には、MOSFETチップ20を支持するチップ支持部(アイランド)29が一体的に形成されている。

【0018】

MOSFETチップ20は、チップ支持部29に対してドレイン電極25を対向させて、いわゆるフェースアップ方式で当該チップ支持部29上に実装(ダイボンディング)されている。これにより、ドレイン電極25がドレインリード28に電気的に接続されている。ゲート電極23およびソース電極24は、ゲートリード26およびソースリード27にそれぞれワイヤボンディングによって電気的に接続されている。より具体的には、ゲート電極23にゲートワイヤ30の一端が接続されており、そのゲートワイヤ30の他端がゲートリード26に接続されている。同様に、ソース電極24に、ソースワイヤ31の一端が接続されていて、そのソースワイヤ31の他端がソースリード27に接続されている。

【0019】

ゲートワイヤ30は、直径100μm以上で、かつ長さ5mm以下であることが好ましく、ソースワイヤ31は、直径300μm以上で、かつ長さ5mm以下であることが好ましい。この実施形態では、ゲートワイヤ30は、直径150μm、長さ4mmであり、ソースワイヤ31は、直径350μm、長さ4mmである。

この実施形態ではMOSFETチップ20は、平面視においてほぼ矩形に形成されている。そして、その矩形のMOSFETチップ20の一方表面において、一辺の中央付近にゲート電極23が形成されている。そして、その他の領域を覆うようにソース電極24が形成されており、このソース電極24は、ゲート電極23に対応する凹部を一辺の中央付近に有している。

【0020】

モールド樹脂22は、MOSFETチップ、ゲートワイヤ30、ソースワイヤ31、ならびにゲートリード26、ソースリード27およびドレインリードの各根本部を覆うように形成されている。チップ支持部29の一方表面は、MOSFET20が搭載されてモールド樹脂22によって封止されたチップ搭載面である。チップ支持部29の他方表面は、モールド樹脂22から露出した放熱面とされていてもよい。また、チップ支持部29は、ソースリード27とは反対側の端部がモールド樹脂22から突出していてもよい。

【0021】

図3は、MOSFETチップ20のソース電極24から下の構成を示す部分拡大平面図であり、図4は、図3の切断面線IV−IVから見た断面図である。MOSFETチップ20は、平面視において格子状に形成されたゲートトレンチ35を有するトレンチゲート型MOSFETとしての基本構造を有している。格子状のゲートトレンチ35によって、平面視矩形(たとえばほぼ正方形)の複数のソース領域44が区画されており、各ソース領域44の中央にはボディ領域43が露出している。

【0022】

図4に最もよく現れているように、MOSFETチップ20は、n+型SiC基板40と、このSiC基板40の表面にエピタキシャル成長させられたSiCエピタキシャル層41とを有している。n+型SiC基板40およびエピタキシャル層41は、MOSFETチップ20の半導体活性領域を構成している。エピタキシャル層41は、SiC基板40に接するn−型ドレイン領域42と、ドレイン領域42上に積層されたp型ボディ領域43と、p型ボディ領域43上に積層されたn+型ソース領域44とを有している。前述のとおり、ボディ領域43は、平面視矩形のソース領域44のほぼ中央部でエピタキシャル層41の表面に露出するように形成されている。

【0023】

ゲートトレンチ35内には、ゲートトレンチ35の底面および側壁面を覆うゲート絶縁膜46が形成されている。すなわち、ゲート絶縁膜46は、ゲートトレンチ35の底面を覆う底面被覆部47と、ゲートトレンチ35の側壁面を覆う側壁被覆部48とを有し、これらの底面被覆部および側壁被覆部48は互いに連続している。そして、底面被覆部47の厚さは、側壁被覆部48の厚さよりも大きくされており、これにより、ゲート−ドレイン間寄生容量の低減が図られている。ゲート絶縁膜46は、酸化膜であってもよいし、酸化膜以外の材料からなる絶縁膜であってもよいし、酸化膜と酸化膜以外の材料との組合せであってもよい。

【0024】

ゲートトレンチ35は、エピタキシャル層41の表面からソース領域44およびボディ領域43を貫通して、その底面がドレイン領域42に達する深さに形成されている。そして、このゲートトレンチ35内にポリシリコンゲート50が埋め込まれている。よって、ポリシリコンゲート50は、ゲート絶縁膜46の側壁被覆部48を介して、p型ボディ領域43に臨んでいる。ポリシリコンゲート50にしきい値以上の制御電圧を与えると、p型ボディ領域43においてゲートトレンチ35の側壁を形成する部分(チャネル領域)の表面付近に反転層(チャネル)が形成される。このチャネルを介して、ソース領域44およびドレイン領域42の間が導通することになる。ポリシリコンゲート50に与えられる制御電圧がしきい値未満のときは、チャネルが形成されず、ソース領域44およびドレイン領域42の間は遮断状態となる。

【0025】

ゲートトレンチ35上には、ゲートトレンチ35の上方領域からソース領域44にまではみ出す領域にわたって、層間絶縁膜51が形成されている。この層間絶縁膜51上に、ソース電極24を形成する金属膜が形成されている。この金属膜は、層間絶縁膜51が形成されていない領域において、ソース領域44およびボディ領域43に接している。ポリシリコンゲート50は、図4には表れていない場所で、エピタキシャル層41の表面上へと引き出され、ゲート電極23に接続されている。ドレイン電極25は、SiC基板40の裏面(エピタキシャル層41とは反対側の表面)にオーミック接触するように形成されている。

【0026】

SiCで活性領域を構成したMOSFETチップ20は、900V以上の破壊電圧を有することができる。

図5は、SiCで活性領域を構成したMOSFETチップ20と、Si(シリコン)半導体で活性領域を構成したスーパージャンクション型MOSFETとの性能指数比較結果を示す。性能指数として、オン抵抗Ronと、全ゲート電荷量Qgとの積Ron・Qgを用い、耐圧900Vで設計したSiC・MOSFETチップ20および耐圧600VのSiスーパージャンクション型MOSFETについて比較を行った。オン抵抗Ronは、MOSFETがオン状態のときのソース・ドレイン間の電気抵抗であり、全ゲート電荷量Qgは、MOSFETをオンからオフに切り換えるときにゲートに注入する必要がある電荷量である。すなわち、全ゲート電荷量Qgが少ないほど、高速なスイッチングが可能である。オン抵抗Ronはチップ面積が大きいほど小さくなり、全ゲート電荷量Qgはチップ面積が大きくなるほど大きくなる。すなわち、オン抵抗Ronと全ゲート電荷量Qgとはトレードオフの関係にあって、これらの積Ron・Qgが小さいほど高性能なMOSFETであるといえる。

【0027】

図5に示す通り、SiCで半導体活性領域を構成したMOSFETチップ20における性能指数Ron・Qgは5ΩnC未満(図5に示す測定値は4.4)であるのに対し、Siスーパージャンクション型MOSFETにおける性能指数Ron・Qgは、14ΩnCよりも大きく(図5に示す測定値は14.6)なっている。つまり、SiCを半導体活性領域に用いたMOSFETチップ20は、Siスーパージャンクション型MOSFETよりもはるかに高性能であること、すなわち低オン抵抗および高速スイッチングを実現した素子であることがわかる。

【0028】

なお、性能指数Ron・Qgの測定に際し、SiC・MOSFETチップ20については、ゲート電圧Vgs=18V、ドレイン電流Ids=10Aとする一方、Siスーパージャンクション型MOSFETについてはゲート電圧Vgs=10V、ドレイン電流Ids=8Aとした。ゲート電圧およびドレイン電流ともに、SiC・MOSFETチップ20に不利な条件であり、SiC・MOSFETチップ20に関する測定条件をSiスーパージャンクションMOSFETと同等とすれば、性能指数Ron・Qgはより一層小さくなる。測定時のソース・ドレイン電圧Vdsは、SiC・MOSFETチップ20およびSiスーパージャンクション型MOSFETのいずれにおいても300Vとし、また、いずれもゲート抵抗Rgは10Ωとした。

【0029】

図6は、SiC・MOSFETチップ20とSiスーパージャンクション型MOSFETとで容量を比較した測定結果を示す。容量には、入力容量Cissと、出力容量Cossと、帰還容量Crssとがある。入力容量Cissとは、ゲート−ソース間寄生容量Cgsとゲート−ドレイン間寄生容量Cgdとの和であり、ゲートの充放電速度に関係するパラメータである。出力容量Cossとは、ドレイン−ソース間寄生容量Cdsとゲート−ドレイン間寄生容量Cgdとの和であり、ソース−ドレイン間のスイッチング速度に関係するパラメータである。帰還容量Crssは、ゲート−ドレイン間寄生容量Cgdに等しい。ゲート電圧をスイッチングさせるときに見えるミラー効果成分は、帰還容量Crssに電荷をチャージしている期間に相当している。つまり、帰還容量Crssが小さければ、ゲート電圧が速くスイッチングし、立ち上がり遅延時間および立ち下がり遅延時間が低減する。したがって、上昇時間および下降時間がゲート電圧のスイッチングの遅さで制限されてしまっている場合に、帰還容量Crssを低減することで、スイッチング時間を改善できる。また、上昇時間および下降時間が制限されていない場合でも、ブリッジ回路でFETを動作させるときに必須であるデッドタイム(ブリッジ内全てのFETをオフさせておく時間)の制御を容易にできるメリットもある。

【0030】

ゲート寄生容量を測定する際は、ゲート電極に印加する基本電圧を0Vとしてソース−ドレイン間に大きな電流が流れないようにして、ドレイン-ソース間に任意の電圧(たとえば0.1V)が印加される。その状態で、ゲート電圧を基本電圧の周辺で高周波振動させる。たとえば、振動電圧Levelを0.1Vとし、振動周波数fを1MHzとしてもよい。こうして、ゲート電圧を高速振動させたときに流れる電流およびその変化率に基づいて、ゲート寄生容量を算出でき、併せてゲート抵抗を算出できる。

【0031】

図6に示すとおり、Siスーパージャンクション型MOSFETにおいては、入力容量が1150pF程度、出力容量が1950pF程度、帰還容量が540pF程度である。これに対して、SiC・MOSFETチップ20においては入力容量が600pF程度、出力容量が560pF程度、帰還容量が350pF程度であり、いずれもSiスーパージャンクション型MOSFETの値よりも小さくなっている。この結果からも、SiC・MOSFETチップ20は、Siスーパージャンクション型MOSFETよりもはるかに高速なスイッチングが可能な素子であることがわかる。

【0032】

SiC・MOSFETチップ20は、ドレイン-ソース間電圧Vds=0.1V、振動周波数f=1MHzで測定したときに、入力容量が700pF未満、出力容量が600pF未満、帰還容量が400pF未満であることが好ましい。さらにまた、SiC・MOSFETチップ20は、耐圧が900V以上であることが好ましく、また、性能指数Ron・Qgが5ΩnC未満であることが好ましく、さらに、ゲート−ソース間電圧Vgsが18Vのときに、面積で規格化したオン抵抗が4mΩcm2以下であることが好ましい。

【0033】

図7は、SiC・MOSFETチップ20とSiスーパージャンクション型MOSFETとにおいて、スイッチング特性を測定した結果を示す。SiC・MOSFETチップ20のゲート電圧Vgsの変化が曲線L1で示されており、SiC・MOSFETチップ20のドレイン−ソース間の電圧Vdsの時間変化が曲線L2で示されている。一方、Siスーパージャンクション型MOSFETにおけるゲート電圧Vgsの時間変化が曲線L3で示されていて、そのドレイン−ソース間電圧Vdsの時間変化が曲線L4で示されている。曲線L1,L3に示すように、ゲート電圧Vgsをオン電圧からオフ電圧に降下させると、それに応答して、MOSFETがターンオフし、ドレイン−ソース間電圧Vdsが0V(導通状態)から100V(遮断状態)へと変化する。ゲート電圧Vgsが下がり始めてからドレイン−ソース間電圧Vdsが立ち上がり始めるまでの時間は「ターンオフ遅延時間」と呼ばれる。また、ドレイン−ソース電圧Vdsが立ち上がり始めてから遮断電圧に達するまでの時間は、ソース・ドレイン間で電流が遮断されるのに要する時間であり、「下降時間」と呼ばれる。

【0034】

図8は、スイッチング素子10(Ron=3.2mΩcm2、900V耐圧)とSiスーパージャンクション型MOSFET(Ron=28mΩcm2、600V耐圧)とのターンオフ遅延時間および下降時間の測定結果を比較して示す図である。スイッチング素子10においては、ターンオフ遅延時間は19nsecであり、下降時間は15nsecである。これに対して、Siスーパージャンクション型MOSFETにおいては、ターンオフ遅延時間が34nsecであり、下降時間が22.5nsecである。スイッチング素子10における下降時間15nsecは、電圧変化速度に換算すると、6.7×109V/秒(=100V/15nsec)であり、Siデバイスでは実現できない、5×109V/秒以上(下降時間に換算して20nsec以下)の電圧変化速度が実現されている。このように、スイッチング素子10においては、Siスーパージャンクション型MOSFETに対して、ターンオフ遅延時間および下降時間が著しく短縮されていることがわかる。すなわち、スイッチング素子10は、Siスーパージャンクション型MOSFETよりもはるかに高速なスイッチングが可能なスイッチング素子である。Siスーパージャンクション型MOSFETでは、Ronを犠牲にしてチップを小さくして高速化を図っているにも拘わらず、SiCデバイスを用いたスイッチング素子10の方がより電圧変化速度が速いのである。

【0035】

図9は、図1に示したDC/DCコンバータ1において、スイッチング素子10として、SiC・MOSFETチップ20を内蔵したもの(実施例)と、SiC・MOSFETチップ20に代えてSiスーパージャンクション型MOSFETを適用した比較例とで、効率を測定した測定結果を示す。スイッチング素子10の駆動周波数、すなわちスイッチング周波数を、400kHzから1300kHzの範囲で変化させながら、入力電力に対する出力電力の比を測定した。入力電力とは、入力電流および入力電圧の各平均値の積であり、出力電力とは出力電流および出力電圧の各平均値の積である。電源電圧(動作電圧)は100Vとし、スイッチング素子10を駆動するときのデューティ比は20%とした。また、負荷7として20Ωの電気抵抗を接続し、チョークコイル16のインダクタンスを47μHとし、電解コンデンサ17には定格電圧50V、容量470μFのものを用いた。

【0036】

図9に示されているように、Siスーパージャンクション型MOSFETを用いた場合は、400〜600kHzの周波数域では88%を超える効率を達成しているものの、1000kHz以上の周波数域では効率が87%未満にまで落ち込んでいる。一方、SiC・MOSFETチップ20を内蔵したスイッチング素子10を適用した場合は、1000kHz付近の周波数域までほとんど効率が低下せず、1200kHz以上の周波数域においても87%を超える効率が達成されている。すなわち、ゲート寄生容量が小さく、かつオン抵抗も低いSiC・MOSFETチップ20を内蔵したスイッチング素子10を用いることによって、高速なスイッチングが可能であり、その結果、DC/DCコンバータ1を1MHz以上の高速な駆動周波数でかつ高効率に駆動することが可能となる。

【0037】

図10は、スイッチング素子10のパッケージ構造に関する変形例を示す図解的な平面図である。この変形例では、SiC・MOSFETチップ20が、ゲート電極23およびソース電極24をリードフレーム61に対向させたフェースダウン方式でリードフレーム61上に実装されている。

リードフレーム61は、ゲートリード62、ソースリード63、およびドレインリード64を含む。ゲートリード62、ソースリード63およびドレインリード64は、たとえば同一平面上に位置するように配列された板状体からなる。ドレインリード64は、ゲートリード62およびソースリード63の間に配置されており、ドレインワイヤ65を介してMOSFETチップ20のドレイン電極25に接続されている。すなわち、ドレインワイヤ65の一端がドレインリード64に接続されており、その他端がドレイン電極25に接続されている。

【0038】

MOSFETチップ20のゲート電極23およびソース電極24は、ボンディングワイヤを用いることなく、すなわちワイヤフリーで、ゲートリード62およびソースリード63にそれぞれ接続されている。具体的には、ソースリード63は、MOSFETチップ20を支持するためのチップ支持部66を一体的に有しており、このチップ支持部66にダイボンディング材(はんだ等)を用いてソース電極24がダイボンディングされている。

【0039】

ソースリード63のチップ支持部66には、ゲートリード62からMOSFETチップ20のゲート電極23に至る経路に対応した切り欠き部67が形成されている。ゲートリード62には、切り欠き部67によって区画された領域に沿って延びるゲートリード延長部68が一体的に形成されている。このゲートリード延長部68の先端部は、MOSFETチップ20のゲート電極23に対向する位置に達している。この先端部に、はんだ等のダイボンディング材を用いてゲート電極23がダイボンディングされている。

【0040】

このようにして、MOSFETチップ20のゲート電極23がワイヤフリーでゲートリード62に接続されているので、寄生ゲート抵抗を低減(たとえば30Ω以下)でき、かつゲート電極23につながる信号線のインダクタンスを低減できる。同様に、ソース電極24とソースリード63とをワイヤフリーで接続することができるので、電源電圧とMOSFETチップ20との間のインダクタンスを低減できる。こうして、より高速で高効率のスイッチングを実現できる。

【0041】

図11は、この発明の第2の実施形態に係る高速スイッチング動作回路であるAC/DC電源回路(いわゆるACアダプタ)の構成(フィードバック回路は省略)を示す電気回路図である。AC/DC電源回路71は、交流電源76に接続される電源端子72,73と、直流電圧を出力する出力端子74,75とを有している。すなわち、AC/DC電源回路71は、交流電源76からの交流電圧(たとえば100V)を整流して、予め定められたレベルの直流電圧を出力端子74,75の間に出力するように構成されている。AC/DC電源回路71は、整流回路77と、平滑コンデンサ78と、高周波トランス79と、スイッチング素子80と、駆動回路81とを含む。交流電源76からの電力は、一対の給電ライン87,88を介して、ダイオードブリッジで構成された整流回路77の一対の入力端子に供給される。一方の給電ライン88には、ヒューズ89が介装されている。ヒューズ89と整流回路77との間には、ノイズフィルタ(入力ラインフィルタ)92が設けられている。この例では、ノイズフィルタ92は、バルントランス90と、給電ライン87,88の間に接続されたバイパスコンデンサ91とを含む。ヒューズ89とノイズフィルタ92の間において、給電ライン87,88間には、ノイズ吸収のための電気抵抗93が接続されている。

【0042】

整流回路77の一対の出力端子は、高電圧ライン85および低電圧ライン86にそれぞれ接続されている。平滑コンデンサ78は、高電圧ライン85および低電圧ライン86の間に接続された電解コンデンサからなる。高周波トランス79の1次側巻線79pの一方の端子は高電圧ライン85に接続されており、その他方の端子は低電圧ライン86に接続されている。低電圧ライン86には、高周波トランス79の1次側巻線79pと整流回路77との間に、スイッチング素子80および電気抵抗94が直列に接続されている。

【0043】

さらに、高電圧ライン85と低電圧ライン86との間には、スイッチング素子80よりも高周波トランス79側において、1次側巻線79pと並列にスナバ回路82が接続されている。スナバ回路82は、電気抵抗95およびコンデンサ96の並列回路と、この並列回路に直列に接続されたダイオード97とを含む。スナバ回路は、スイッチング素子80のスイッチングに伴うスパイク状の高電圧を吸収して電磁ノイズを最小化する。

【0044】

高周波トランス79の2次側巻線79sは、この実施形態では、1次側巻線79pとは反対方向に巻かれている。この2次側巻線79sの一端は出力高電圧ライン98に接続されており、その他端は出力低電圧ライン99に接続されている。

出力高電圧ライン98には、整流素子としてのダイオード83が介装されている。より具体的には、ダイオード83のアノードが2次側巻線79sに接続されており、そのカソードが出力端子74に接続されている。また、出力低電圧ライン99は出力端子75接続されている。出力高電圧ライン98と出力低電圧ライン99との間には、平滑用の電解コンデンサ84が接続されている。電解コンデンサ84の正極側端子は、ダイオード83と出力端子74との間において出力高電圧ライン98に接続されている。

【0045】

スイッチング素子80は、前述の第1の実施形態におけるスイッチング素子10と同様の構成を有し、SiC半導体を活性領域に用いたトレンチゲート型MOSFETチップ20を内蔵している。このスイッチング素子80は、nチャネル型電界効果トランジスタであって、ドレインが高周波トランス79の1次側巻線79pに接続され、そのソースが電気抵抗94を介して整流回路77へと接続されている。この実施形態では、一次側巻線79pは、スイッチング素子80に接続されたチョークコイルと見なすことができる。

【0046】

スイッチング素子80のゲート端子には、駆動回路81が出力する制御信号が入力されるようになっている。駆動回路81は、たとえば1MHz以上の周波数の矩形波駆動パルスを、制御信号として、スイッチング素子80のゲートに供給する。

スイッチング素子80がターンオンすると、高周波トランス79の1次側巻線79pに電流が流れ、その2次側巻線79sに誘導起電力が生じる。この誘導起電力は、ダイオード83に対して逆方向の電流を流そうとする向きの起電力であるため、高周波トランス79の2次側では電流が流れず、2次側巻線79sにエネルギーが蓄えられる。その後、スイッチング素子80がターンオフすると、ダイオード83に対して順方向の電流を流そうとする起電力が2次側巻線79sに生じ、ダイオード83が導通する。こうして、フライバック方式によって、高周波トランス79の1次側巻線79pから2次側巻線79sへとエネルギーが伝達され、1次側巻線79pおよび2次側巻線79sの巻数の比に応じて変圧された電圧が2次側巻線79sに生じる。この電圧が、ダイオード83によって整流され、かつ電解コンデンサ84によって平滑化されることにより、出力端子74,75には、予め定められたレベルの直流電圧が導出される。

【0047】

図12は、スイッチング素子80をターンオフした後のソース−ドレイン間電圧の時間変化を示す波形図である。スイッチング素子80は、ドレイン−ソース間容量Cdsを有しているので、この容量Cdsと1次側巻線79pとでLC共振回路が構成される。そのため、スイッチング素子80をターンオフすると、一次側巻線79pの起電によって、ソース−ドレイン間電圧が電源電圧以上の値に立ち上がり、しばらくすると、整流回路77の出力電圧(たとえば144V)を基準にドレイン−ソース間電圧が振動することになる。

【0048】

そこで、ドレイン−ソース間電圧が極小値をとるタイミングにおいてスイッチング素子80をターンオフするように駆動回路81が構成されている。たとえば、交流電源76からAC100Vが供給される場合に、整流回路77の出力電圧は144Vとなる。したがって、共振による振幅が288V以上(たとえば300V)であれば、ドレイン−ソース間電圧Vdsの極小値は0V以下になる。よって、ソース・ドレイン間電圧Vds=0となるタイミングでスイッチング素子80をターンオンさせることによって、スイッチングロスをなくすことができる。このような動作は、完全電圧共振と呼ばれる。

【0049】

SiCを活性領域に適用したMOSFETチップ20を含むスイッチング素子80では、十分な耐圧を有しているため、ドレイン−ソース間電圧Vdsの振幅が288V以上となるように1次側巻線79pのインダクタンス等の回路定数を設定することができ、スイッチングロスをなくすことが可能である。これに対して、Si半導体を活性領域に適用したスイッチング素子を用いると、その耐圧による制限のために、ドレイン−ソース間電圧Vdsの振幅を288Vよりも低くしておかなければならない。そのため、ドレイン−ソース間電圧Vdsの極小点であっても、Vds>0であるので、スイッチングロスをなくすことができない。したがって、SiCを半導体活性領域に適用したMOSFETチップ20を有するスイッチング素子80を用いることで、完全電圧共振を用いたスイッチング動作が可能となり、それにより、AC/DC電源回路71の効率を向上することができる。

【0050】

図13は、この発明の第3の実施形態に係る高速スイッチング動作回路であるワイヤレス給電装置の電気的構成を示す回路図である。ワイヤレス給電装置111は、受電機器112に対して、ワイヤレスで、すなわち給電部端の電極と受電部端の電極とが非接触状態で、電力を供給するための装置である。ワイヤレス給電装置111は、高周波回路113と、駆動回路114と、共振回路115(115A,115B)とを含む。

【0051】

高周波回路113は、直流電源116からの電力供給を受けるための電源端子117,118を備えている。電源端子117は、直流電源116の正極に接続され、電源電圧ライン119に電源電圧を供給する。一方、電源端子118は、直流電源116の負極に接続され、グランドライン120にグランド電位を与える。高周波回路113は、第1および第2のスイッチング素子121,122と、高周波トランス123と、共振インダクタ124と、平滑コンデンサ125とを含む。電源電圧ライン119は、第1分岐ライン119Aと、第2分岐ライン119Bとに分岐している。第1分岐ライン119Aに第1スイッチング素子121が介装されており、第2分岐ライン119Bに第2スイッチング素子122が介装されている。第1スイッチング素子121および第2スイッチング素子122は、前述の第1の実施形態におけるスイッチング素子10と同様の構成を有し、SiC半導体からなる活性領域を有するMOSFETチップ20を内蔵したnチャネル型電界効果トランジスタとしての基本構成を有している。第1スイッチング素子121および第2スイッチング素子122の各ゲートには、駆動回路114からの制御信号が供給されるようになっている。

【0052】

高周波トランス123は、第1一次側巻線127と、第2一次側巻線128と、二次側巻線129とを備えている。第1一次側巻線127と第2一次側巻線128とは、各一端が互いに接続されており、その接続点126にグランドライン120が接続されている。そして、グランドライン120に共振インダクタ124が介装されている。第1一次側巻線127において第2一次側巻線128の接続点126と反対側の端子に、第1スイッチング素子121が接続されている。同様に、第2一次側巻線128において第1一次側巻線127との接続点126と反対側の端子に第2スイッチング素子122が接続されている。第1スイッチング素子121および第2スイッチング素子122に対して高周波トランス123側において、第1分岐ライン119Aと第2分岐ライン119Bとの間に平滑コンデンサ125が接続されている。この実施形態では、第1一次側巻線127は、第1スイッチング素子121に接続されたチョークコイルと見なすことができ、第2一次側巻線128は、第2スイッチング素子122に接続されたチョークコイルと見なすことができる。

【0053】

高周波トランス123の二次側巻線129には複数の共振回路115が接続されている。より具体的には、複数の共振回路115は、二次側巻線129の一方側端子に接続された複数の第1共振回路115Aと、二次側巻線129の他方の端子に接続された複数の第2共振回路115Bとを含む。各共振回路115は、コイル131と、出力電極132とを直列接続して構成されている。出力電極132は、受電機器112に備えられた入力電極133に対してギャップ134を介して容量結合しており、これらの出力電極132および入力電極133によってコンデンサ135が形成されるようになっている。このコンデンサ135と、コイル131とで、予め定める共振周波数(たとえば6.78MHz)において共振する共振回路が構成されている。

【0054】

受電機器112は、複数の入力電極133と、各入力電極133に対応した整流回路140と、平滑コンデンサ141と、DC/DCコンバータ142と、内蔵された負荷143とを含む。各整流回路140は、電源電圧ライン144とグランドライン145との間に直列接続された一対のダイオードを有しており、それらの一対のダイオードの間の接続点に入力電極133が接続されている。平滑コンデンサ141は、電源電圧ライン144とグランドライン145との間に接続されている。DC/DCコンバータ142は、電源電圧ライン144に接続されたnpnトランジスタ146と、トランジスタ146のベースに接続されたスイッチング駆動回路147と、トランジスタ146のエミッタとグランドライン145との間に接続された整流素子としてのダイオード148と、トランジスタ146と負荷143との間に接続されたチョークコイル149と、チョークコイル149と負荷143との間においてグランドライン145との間に接続された平滑コンデンサ150とを含む。

【0055】

図14は、駆動回路114から第1スイッチング素子121のゲートに供給される第1制御信号と、駆動回路114から第2スイッチング素子122のゲートに供給される第2制御信号と、高周波トランス123の二次側巻線129に導出される電圧波形とを示す波形図である。

第1および第2制御信号は、第1スイッチング素子121および第2スイッチング素子122を、交互にオン/オフさせるための矩形波信号である。第1制御信号がハイレベルの期間には第2制御信号がローレベルとなり、第2制御信号がハイレベルの期間には第1制御信号がローレベルとなる。第1制御信号のハイレベル期間と第2制御信号のハイレベル期間との間には、所定長のデッドタイムが確保されている。

【0056】

第1制御信号のハイレベル期間に第1スイッチング素子121が導通し、第1制御信号のローレベル期間に第1スイッチング素子121が遮断される。同様に、第2制御信号のハイレベル期間に第2スイッチング素子122が導通し、第2制御信号のローレベル期間に第2スイッチング素子122が遮断状態となる。よって、第1スイッチング素子121および第2スイッチング素子122は、交互に導通して、直流電源116からの電流をそれぞれ第1一次側巻線127および第2一次側巻線128に供給する。

【0057】

第1スイッチング素子121が導通すると、第1一次側巻線127には第1分岐ライン119Aからグランドライン120に向かって電流が流れる。また第2スイッチング素子122が導通すると、第2一次側巻線128には、第2分岐ライン119Bからグランドライン120に向かって電流が流れる。

第1スイッチング素子121が遮断されると、第1一次側巻線127はグランドライン120から第1分岐ライン119Aに向かって電流を流そうとする起電力を生じ、この起電力と第2スイッチング素子122の導通によって第2一次側巻線128に現れる電圧とが加算されて、大きな振幅の電圧が発生する。同様に、第2スイッチング素子122が遮断されると、第2一次側巻線128はグランドライン120から第2分岐ライン119Bに向かって電流を流そうとする起電力を生じ、第1スイッチング素子121の導通によって第1一次側巻線127に現れる電圧がこれに加算されることによって、大きな電圧が生じる。

【0058】

こうして、第1スイッチング素子および第2スイッチング素子121,122をプッシュプル動作させることによって、高周波トランス123の一次側から二次側へと高効率でエネルギーを伝達することができる。そして、二次側巻線129が発生する交流電圧が、共振回路115によって共振することにより、コンデンサ135を構成する出力電極132から入力電極133へと高効率で電力を供給することができる。

【0059】

受電機器112においては、入力電極133から入力される交流電圧が整流回路140によって整流され、さらに平滑コンデンサ141によって平滑化されることにより、直流電圧に変換される。この直流電圧がDC/DCコンバータ142に入力される。npnトランジスタ146が、スイッチング駆動回路147から出力される所定デューティ比の駆動信号によってオン/オフされることにより、そのデューティ比に応じた電圧に降圧された直流電圧が生じる。すなわち、npnトランジスタ146が導通するとチョークコイル149に電流が供給され、npnトランジスタ146が遮断されるとチョークコイル149が生じる起電力によってダイオード148が導通して負荷143に向かって電流が供給される。そして、平滑コンデンサ150の働きにより、安定した直流電圧が負荷143に供給されることになる。

【0060】

負荷143は、受電機器112に備えられたバッテリを充電する充電回路を含んでいてもよい。

図15は、ワイヤレス給電装置111の具体的な構成例を説明するための図解的な斜視図である。複数の出力電極132は、プラスチック等の絶縁材料で構成された電極保持板155に配列されて固定されている。より具体的には、電極保持板155の表面には、複数の出力電極132をそれぞれ埋設するための凹所156が所定の配列パターンで間隔をあけて形成されている。各凹所156に出力電極132が1つずつ埋設されて固定されている。その状態で、電極保持板155の表面には、絶縁材料からなるシート体157(図15では明瞭化のために電極保持板155から分離した状態で表してある。)が貼り付けられ、これによって、出力電極132が凹所156内に保持されている。

【0061】

電極保持板155の裏面側には、出力電極132とともに共振回路115を形成するコイル131が保持されていて、出力電極132の裏面側に直付けされて電気的に接続されている。各コイル131の他方の出力端子はケーブル158を介して高周波回路113に接続されている。高周波回路113には、電源ケーブル159を介して直流電源116が接続されている。さらに、高周波回路113には、信号ケーブル160を介して駆動回路114が接続されている。

【0062】

図16は、電極保持板155に対する出力電極132およびコイル131の取付構造例を説明するための図解的な拡大断面図である。出力電極132を収容する凹所156の底面には貫通孔161が形成されている。この貫通孔161をコイル131の一方の端子131Aが貫通して、出力電極132の裏面にはんだ付けされている。こうして、コイル131が、出力電極132に対して、ケーブル等を介することなく直付けされており、コイル131と出力電極132との間のインダクタンスが最小化されている。具体的には、コイル131から引き出された端子131Aの長さは5mm以下であることが好ましい。コイル131は、電極保持板155の裏面にボルト162によって固定された保持キャップ163によって保持されている。保持キャップ163には貫通孔164が形成されていて、この貫通孔からコイル131の他方の端子131Bが引き出されている。端子131Bにケーブル158の一端がはんだ付けされている。

【0063】

受電機器112は、電極保持板155の表面の任意の位置に置かれ、その状態で給電を受けることができる。すなわち、電極保持板155の表面に複数の出力電極132が広い範囲にわたって分布しているので、受電機器112の入力電極133は、いずれかの出力電極132と容量結合して、コンデンサ135を形成する。これにより、受電機器112は、共振回路115を介して、高周波回路113から高周波電力の供給を受けることができる。

【0064】

駆動回路114は、第1および第2スイッチング素子121,122を1MHz以上の高周波域の駆動周波数(好ましくは共振回路115の共振周波数)で駆動する。これにより、高周波電力は、出力電極132および入力電極133によって形成されるコンデンサ135を通過して、受電機器112へと効率的に供給される。

受電機器112側に設けられる入力電極133は、少なくとも一対設けられればよいが、広い面積の電極保持板155の表面上のいずれの位置においても効率的な高周波給電を可能とするためには、複数対の入力電極133を受電機器112に設けることが好ましい。多数の入力電極133を設けることによって、電極保持板155の表面上のいずれの位置に受電機器112が置かれた場合であっても、出力電極132と入力電極133とによって形成されるコンデンサ135の容量をある程度一定にすることができる。これによって、共振回路115における共振を保証することができるので、高周波回路から受電機器112への効率的なワイヤレス給電が可能となる。とくに、第1および第2スイッチング素子121,122にSiC半導体のMOSFETを適用して、大電力を高周波で伝達するには、共振回路115における共振を保証することが重要であり、この観点から、多数対の入力電極133を受電機器112に備えることが好ましい。

【0065】

図17は、高周波回路113の構成例を示す図解的な斜視図である。高周波回路113は、多層プリント配線基板167を有している。この多層プリント配線基板167に、第1スイッチング素子121、第2スイッチング素子122、高周波トランス123、共振インダクタ124、および平滑コンデンサ125が実装されている。多層プリント配線基板167は、絶縁層168,169,170と、絶縁層169,170を挟んで積層された第1〜第3配線層171,172,173とを含む。すなわち、下側から順に、絶縁層168、第1配線層171、絶縁層169、第2配線層172、絶縁層170、第3配線層171の順に、絶縁層と配線層とが交互に積層されている。

【0066】

図18は、第1配線層171、第2配線層172および第3配線層173にそれぞれ形成された配線パターンの例を説明するための図解的な斜視図である。第1配線層171は、それぞれ矩形に形成された第1グランドパターン175および第2グランドパターン176を有している。第1および第2グランドパターン175,176は互いに絶縁されている。第1および第2グランドパターン175および176は、平面視において、多層プリント配線基板167のほぼ全域を占めるように形成されている。第2グランドパターン176は、多層プリント配線基板167の厚さ方向に沿って層間を貫通するビア208によって、第3配線層173に形成されたグランド用ランド209に接続されている。

【0067】

第2配線層172には、第1分岐ライン119Aおよび第2分岐ライン119Bにそれぞれ対応する第1電源電圧パターン181および第2電源電圧パターン182が互いに分離されて形成されている。第1および第2電源電圧パターン181,182は、平面視において、第1グランドパターン175から第2グランドパターン176に跨がり、かつ大部分が第1および第2グランドパターン175,176とオーバレイするように形成されている。

【0068】

第1電源電圧パターン181は、たとえば細長い長方形の帯状に形成されており、その一端付近の直上には、第3配線層173にランド183が形成されている。ランド183と第1電源電圧パターン181とはビア186を介して接続されている。ランド183には高周波トランス123の第1一次側巻線127の一端が接続されている。第1一次側巻線127の他端は、同じく第3配線層173に形成されたランド184に接続されている。第2電源電圧パターン182も、第1電源電圧パターン181と同様に、細長い長方形の帯状に形成されており、その一方端には、ビア187を介して、第3配線層173に形成されたランド185が接続されている。このランド185に、第2一次側巻線128の一方の端子が接続されている。第2一次側巻線128の他方の端子は、前述のランド184に接続されている。ランド184は、ビア188を介して、第1配線層171の第1グランドパターン175に接続されている。

【0069】

高周波トランス123の二次側巻線129は、第1および第2一次側巻線127,128と磁気的に結合されるように、それらの近傍において多層プリント配線基板167の表面に実装されている。第3配線層173は、二次側巻線129の一端に接続されたランド191と、二次側巻線129に接続された別のランド192とを有している。これらのランド191,192は、ケーブル158を介して電極保持板155に保持されたコイル131に電気的に接続されることになる(図15参照)。

【0070】

第3配線層173には、さらに、共振インダクタ124の一対の端子が接続されるランド177,178が形成されている。ランド177は多層プリント配線基板167の厚さ方向に層間を貫通するビア179によって第1グランドパターン175に接続されている。もう1つのランド178は、多層プリント配線基板167の厚さ方向に層間を貫通するビア180によって第2グランドパターン176に接続されている。共振インダクタ124の一対の端子は、ランド177,178にはんだ付けされ、これによって多層プリント配線基板167上に共振インダクタ124が実装されている。こうして、第1グランドパターン175と第2グランドパターン176との間に共振インダクタ124が電気的に介装されることになる。

【0071】

平滑コンデンサ125は、第3配線層173に形成されたランド195,196に一対の端子がそれぞれはんだ付けされて多層プリント配線基板167上に実装されている。ランド195は、ビア189を介して第1電源電圧パターン181に接続されており、ランド196は別のビア190を介して第2電源電圧パターン182に接続されている。

第1電源電圧パターン181において第1一次側巻線127とは反対側の端部は、幅狭に形成されており、これによって、第1電源電圧パターン181には平面視矩形の切り欠き部181aが形成されている。同様に、第2電源電圧パターン182は、第2一次側巻線128とは反対側の端部に幅狭部を有していて、これにより平面視矩形の切り欠き部182aが形成されている。第2配線層172は、第1および第2電源電圧パターン181,182から分離された第3電源電圧パターン200を有している。第3電源電圧パターン200は、切り欠き部181a,182aにそれぞれ入り込む第1接続部198および第2接続部199を有している。

【0072】

第1電源電圧パターン181の幅狭部の直上には、第3配線層173にソース用ランド201が形成されており、ビア211を介して第1電源電圧パターン181に接続されている。また、第3電源電圧パターン200の第1接続部198の直上には、第3配線層173にドレイン用ランド202が形成されていて、ビア212を介して第1接続部198に接続されている。ドレイン用ランド202の側方には帯状に形成されたゲート用ランド203の一端部が位置している。ソース用ランド201、ドレイン用ランド202、およびゲート用ランド203の端部には、第1スイッチング素子121のソースリード27、ドレインリード28およびゲートリード26がはんだ付されて接合されている。これにより、第1スイッチング素子121が多層プリント配線基板167上に実装されている。

【0073】

同様に、第2電源電圧パターン182の幅狭部の直上には、第3配線層173にソース用ランド205が形成されており、ビア215を介して第2電源電圧パターン182に接続されている。さらに、第3電源電圧パターン200の第2接続部199の直上において第3配線層173には、ドレイン用ランド206が形成されており、ビア216を介して第第2接続部199に接続されている。ドレイン用ランド206の側方には、帯状に形成されたゲート用ランド207の一端部が位置している。ソース用ランド205、ドレイン用ランド206およびゲート用ランド207の端部には、第2スイッチング素子122のソースリード27、ドレインリード28およびゲートリード26がそれぞれはんだ付けされて接続されている。これにより、第2スイッチング素子122が、多層プリント配線基板167の表面に実装されている。

【0074】

第3電源電圧パターン200の一端部の直上には、第3配線層173に、電源接続用ランド210が形成されており、ビア217を介して電源電圧パターン200に接続されている。

ゲート用ランド203,207には、信号ケーブル160(図15参照)が接続される。また、電源接続用ランド210およびグランド用ランド209には、電源ケーブル159(図15参照)が接続される。

【0075】

図13から理解されるとおり、第1および第2分岐ライン119Aおよび119Bに流れる電流の方向と、グランドライン120に流れる電流の方向とは逆向きになる。そこで、第1および第2分岐ライン119Aおよび119Bとグランドライン120とを互いに平行にしておくことによって、これらの間の相互インダクタンスを低減することができる。図17および図18に示した構成では、第1配線層171の第1および第2グランドパターン175,176にオーバレイするように、第2配線層172の第1、第2および第3電源電圧パターン181,182,200が形成されている。これによって、第1および第2分岐ライン119A,119Bとグランドライン120との大部分を平行にすることができるので、相互インダクタンスを低減できる。これによって、高周波回路113の寄生インピーダンスを小さくすることができるので、ケーブル158(図15参照)のインピーダンスと高周波回路113のインピーダンスとを整合させることができ、効率の一層の向上を図ることができる。

【0076】

図19は、図15および図16に示した電極保持板155に代えて用いることができる電極保持板220の構造例を示す部分拡大断面図である。電極保持板220は、プリント配線基板としての基本形態を有しており、その一方表面に出力電極132を構成する薄膜電極が形成されている。そして、電極保持板220の他方の表面にコイル131が実装されている。コイル131の一方の端子131Aは、電極保持板220の他方表面に形成されたランド221にはんだ付けされている。ランド221は、電極保持板220に形成された貫通ビア222を介して出力電極132としての薄膜電極に接続されている。このような構成によっても、出力電極132およびコイル131を電極保持板220に共通に保持し、かつコイル131と出力電極132とを5mm以下の配線長で互いに電気的に接続することができる。

【0077】

以上、この発明の一実施形態について説明したが、この発明は、さらに他の形態で実施することもできる。たとえば、第1の実施形態では、降圧型のDC/DCコンバータを例示したが、昇圧型のDC/DCコンバータにこの発明を適用してもよい。さらに、その他のスイッチング電源に対しても、この発明を適用することができる。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0078】

1 DC/DCコンバータ

6 直流電源

7 負荷

10 スイッチング素子

11 駆動回路

12 ダイオード(整流用素子)

13 平滑回路

14 電解コンデンサ

16 チョークコイル

17 電解コンデンサ

20 MOSFETチップ

21 リードフレーム

22 モールド樹脂

23 ゲート電極

24 ソース電極

25 ドレイン電極

26 ゲートリード

27 ソースリード

28 ドレインリード

29 チップ支持部

30 ゲートワイヤ

31 ソースワイヤ

35 ゲートトレンチ

40 n+型SiC基板

41 SiCエピタキシャル層

42 n−型ドレイン領域

43 p型ボディ領域

44 n+型ソース領域

46 ゲート絶縁膜

47 底面被覆部

48 側壁被覆部

50 ポリシリコンゲート

51 層間絶縁膜

61 リードフレーム

62 ゲートリード

63 ソースリード

64 ドレインリード

65 ドレインワイヤ

66 チップ支持部

71 AC/DC電源回路

76 交流電源

77 整流回路

78 平滑コンデンサ

79 高周波トランス

79p 一次側巻線

79s 二次側巻線

80 スイッチング素子

81 駆動回路

82 スナバ回路

83 ダイオード(整流素子)

84 電解コンデンサ

111 ワイヤレス給電装置

112 受電機器

113 高周波回路

114 駆動回路

115 共振回路

116 直流電源

119 電源電圧ライン

119A 第1分岐ライン

119B 第2分岐ライン

120 グランドライン

121 第1スイッチング素子

122 第2スイッチング素子

123 高周波トランス

124 共振インダクタ

125 平滑コンデンサ

127 第1一次側巻線

128 第2一次側巻線

129 二次側巻線

131 コイル

132 出力電極

133 入力電極

135 コンデンサ

140 整流回路

141 平滑コンデンサ

142 DC/DCコンバータ

143 負荷

146 npnトランジスタ

147 スイッチング駆動回路

148 ダイオード

149 チョークコイル

150 平滑コンデンサ

155 電極保持板

156 凹所

157 シート体

158 ケーブル

159 電源ケーブル

160 信号ケーブル

161 貫通孔

167 多層プリント配線基板

171 第1配線層

172 第2配線層

173 第3配線層

175 第1グランドパターン

176 第2グランドパターン

181 第1電源電圧パターン

182 第2電源電圧パターン

220 電極保持板

【技術分野】

【0001】

この発明は、高速スイッチング動作回路に関する。高速スイッチング動作回路の例は、DC/DCコンバータ、AC/DCコンバータ、ワイヤレス給電回路を含む。

【背景技術】

【0002】

DC/DCコンバータその他の高速スイッチング動作回路は、電源電圧を高速でスイッチングするスイッチング素子を含む。スイッチング素子には、シリコン半導体で活性層を形成したMOSFET(Metal-Oxide-Semiconductor Field-Effect-Transistor)が適用されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2011−41388号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

シリコンデバイスの高耐圧化および高速化は、限界に近づいてきており、より高い電圧をより高速にスイッチングできるスイッチング素子を用いた高速スイッチング動作回路を実現することができない。

そこで、この発明の目的は、より高電圧をより高速にスイッチングできる高速スイッチング動作回路を提供することである。

【課題を解決するための手段】

【0005】

この発明は、活性領域がSiC半導体からなるMISFET(Metal-Insulator-Semiconductor Field-Effect-Transistor)で構成されたスイッチング素子を有し、前記スイッチング素子が1MHz以上の駆動周波数で駆動され、かつスイッチング時の電圧変化速度が5×109V/秒以上である、高速スイッチング動作回路を提供する。

一つの実施形態においては、前記MISFETが、前記活性領域に形成されたトレンチと、前記トレンチの底面および壁面を絶縁膜と、前記絶縁膜を介して前記活性領域に対向するゲート電極とを含む、トレンチゲート構造を有している。

【0006】

前記絶縁膜は、前記トレンチの底面を覆う底面被覆部の厚さが、前記トレンチの壁面を覆う壁面被覆部の厚さよりも厚いことが好ましい。

一つの実施形態においては、前記MISFETの動作電圧が100V以上であり、前記MISFETの破壊電圧が900V以上である。

一つの実施形態においては、前記MISFETのドレイン−ソース間の電圧を0.1Vとし、前記MISFETのゲートに1MHzの振動周波数の信号を与えて測定したときに、前記MISFETの入力容量が700pF未満であり、前記MISFETの出力容量が600pF未満であり、かつ前記MISFETの帰還容量が400pF未満である。

【0007】

一つの実施形態においては、前記MISFETのゲート−ソース間電圧が18Vのときに、前記MISFETのオン抵抗が4mΩcm2以下である。

一つの実施形態においては、前記MISFETは、オン抵抗Ronと全ゲート電荷量Qgとの積で表される性能指数Ron・Qgが5ΩnC未満である。

前記MISFETの寄生ゲート抵抗は、30Ω以下であることが好ましい。

【0008】

一つの実施形態においては、前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ドレイン電極を支持基板(たとえばリードフレームのアイランド)に接合したフェースアップ方式で前記チップが実装されており、前記ゲート電極およびソース電極にそれぞれゲートワイヤおよびソースワイヤが接続されていて、前記ゲートワイヤは、直径100μm以上、長さ5mm以下であり、前記ソースワイヤは、直径300μm以上、長さ5mm以下である。

【0009】

別の実施形態においては、前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ゲート電極およびソース電極を支持基板(たとえばリードフレームのアイランド)に接合したフェースダウン方式で前記チップが実装されている。

一つの実施形態に係る高速スイッチング動作回路は、前記スイッチング素子に一端が接続されたチョークコイルを有する。

【0010】

一つの実施形態においては、電源電圧ラインとグランドラインとが互いに平行に形成されている。

一つの実施形態においては、前記グランドラインが形成された第1配線層と、前記電源電圧ラインが前記グランドラインにオーバレイするように形成された第2配線層とを含む多層配線基板上に前記MISFETが実装されている。

【図面の簡単な説明】

【0011】

【図1】図1は、この発明の第1の実施形態に係る高速スイッチング動作回路であるDC/DCコンバータの電気回路図である。

【図2】図2は、スイッチング素子の構造を説明するための図解的な平面図である。

【図3】図3は、MOSFETチップのソース電極から下の構成を示す部分拡大平面図である。

【図4】図4は、図3の切断面線IV−IVから見た断面図である。

【図5】図5は、SiCで活性領域を構成したMOSFETチップと、Si半導体で活性領域を構成したスーパージャンクション型MOSFETとの性能指数比較結果を示す。

【図6】図6は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとで容量を比較した測定結果を示す。

【図7】図7は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとにおいて、スイッチング特性を測定した結果を示す。

【図8】図8は、SiC・MOSFETチップとSiスーパージャンクション型MOSFETとのターンオフ遅延時間および下降時間の測定結果を比較して示す図である。

【図9】図9は、図1に示したDC/DCコンバータにおいて、スイッチング素子として、SiC・MOSFETチップを内蔵したもの(実施例)と、SiC・MOSFETチップに代えてSiスーパージャンクション型MOSFETを適用した比較例とで、効率を測定した測定結果を示す。

【図10】図10は、スイッチング素子のパッケージ構造に関する変形例を示す図解的な平面図である。

【図11】図11は、この発明の第2の実施形態に係る高速スイッチング動作回路であるAC/DC電源回路(いわゆるACアダプタ)の構成を示す電気回路図である。

【図12】図12は、スイッチング素子をターンオフした後のソース−ドレイン間電圧の時間変化を示す波形図である。

【図13】図13は、この発明の第3の実施形態に係る高速スイッチング動作回路であるワイヤレス給電装置の電気的構成を示す回路図である。

【図14】図14は、駆動回路から第1スイッチング素子のゲートに供給される第1制御信号と、駆動回路から第2スイッチング素子のゲートに供給される第2制御信号と、高周波トランスの二次側巻線に導出される電圧波形とを示す波形図である。

【図15】図15は、ワイヤレス給電装置の具体的な構成例を説明するための図解的な斜視図である。

【図16】図16は、電極保持板に対する出力電極およびコイルの取付構造例を説明するための図解的な拡大断面図である。

【図17】図17は、高周波回路の構成例を示す図解的な斜視図である。

【図18】図18は、第1配線層、第2配線層および第3配線層にそれぞれ形成された配線パターンの例を説明するための図解的な斜視図である。

【図19】図19は、図15および図16に示した電極保持板に代えて用いることができる電極保持板の構造例を示す部分拡大断面図である。

【発明を実施するための形態】

【0012】

以下では、この発明の実施の形態を、添付図面を参照して詳細に説明する。

図1は、この発明の第1の実施形態に係る高速スイッチング動作回路であるDC/DCコンバータの電気回路図である。DC/DCコンバータ1は、電源端子2,3に供給される直流電源電圧を変換して(この実施形態では降圧して)、変換後の直流電圧を出力端子4,5の間に出力するように構成されている。電源端子2,3の間には直流電源6が接続される。より具体的には、電源端子2に直流電源6の正極が接続され、電源端子3に直流電源6の負極が接続される。一方、出力端子4,5の間には変換後の直流電圧を供給すべき負荷7が接続される。

【0013】

DC/DCコンバータ1は、スイッチング素子10と、駆動回路11と、整流用素子としてのダイオード12と、平滑回路13と、電解コンデンサ14とを備えている。電源端子2は電源電圧ライン8に接続されており、電源端子3はグランドライン9に接続されている。整流用素子としては、ダイオードに限らず、SiC・MOSFETを使用してもよく、それによりさらに効率向上を期待できる。電解コンデンサ14は、電源電圧ライン8とグランドライン9との間に接続されている。スイッチング素子10は、この実施形態では、nチャネル型MOSFETで構成されていて、そのドレイン端子が電源電圧ライン8に接続され、そのソース端子がダイオード12のカソードに接続されている。ダイオード12のアノードは、グランドライン9に接続されている。ダイオード12は、ショットキバリアダイオードであってもよい。後述するように、スイッチング素子10は、SiC(炭化シリコン)を半導体活性領域に適用したMOSFETで構成されている。スイッチング素子10のゲート端子には、駆動回路11が接続されている。駆動回路11は、スイッチング素子10をスイッチングするための制御信号を供給するように構成されている。制御信号は、矩形波信号であってもよいし、正弦波信号であってもよい。

【0014】

平滑回路13は、スイッチング素子10とダイオード12との接続点15に導出される電圧を平滑して出力端子4に供給するように構成されている。平滑回路13は、チョークコイル16と電解コンデンサ17とを含む。チョークコイル16は、その一方の端子が接続点15に接続されており、その他方の端子が出力端子4に接続されている。そして、当該他方の端子とグランドライン9との間に電解コンデンサ17が接続されている。電解コンデンサ17は、その正極側の端子が出力端子4側となるように接続されている。

【0015】

駆動回路11からの制御信号がスイッチング素子10のゲートに供給されることにより、スイッチング素子10がターンオンすると、直流電源6から供給される電流がチョークコイル16へと流れ込み、このチョークコイル16にエネルギーが蓄えられるとともに、電解コンデンサ17が充電されて、出力端子4の電位が上がる。その後、駆動回路11からの制御信号によってスイッチング素子10がターンオフすると、チョークコイル16は、接続点15から出力端子4へと向かう電流を保とうとするので、ダイオード12を通って電流が流れ、出力端子4に導出される電圧が保持される。チョークコイル16の出力端子4側に現れる電圧が電解コンデンサ14によって平滑されることにより、出力端子4には安定した電圧が導出される。このような動作により、電源端子2,3の間に供給される直流電圧がスイッチング素子10のゲートに与えられる制御信号のデューティ比に応じて降圧され、その降圧された直流電圧が出力端子4,5の間に導出される。

【0016】

電解コンデンサ14は、直流電源6から供給される電圧を保持し、スイッチング素子10の近くから当該スイッチング素子10に電流を供給することにより、直流電源6から電源端子2,3に至るケーブルのインダクタンスの影響を低減する。

図2は、スイッチング素子10の構造を説明するための図解的な平面図である。スイッチング素子10は、MOSFETチップ20と、リードフレーム21と、モールド樹脂22(図2では二点鎖線で示す)とを含む。

【0017】

MOSFETチップ20は、一方の表面にゲート電極(パッド)23およびソース電極(パッド)24を有し、他方の表面にドレイン電極25(図4参照)を有している。

リードフレーム21は、ゲート端子を構成するゲートリード26と、ソース端子を構成するソースリード27と、ドレイン端子を構成するドレインリード28とを有している。この実施形態では、ゲートリード26、ソースリード27およびドレインリード28は、同一平面上に位置するように配置された板状体からなっていて、ドレインリード28がゲートリード26およびソースリード27の間に配置されている。ドレインリード28には、MOSFETチップ20を支持するチップ支持部(アイランド)29が一体的に形成されている。

【0018】

MOSFETチップ20は、チップ支持部29に対してドレイン電極25を対向させて、いわゆるフェースアップ方式で当該チップ支持部29上に実装(ダイボンディング)されている。これにより、ドレイン電極25がドレインリード28に電気的に接続されている。ゲート電極23およびソース電極24は、ゲートリード26およびソースリード27にそれぞれワイヤボンディングによって電気的に接続されている。より具体的には、ゲート電極23にゲートワイヤ30の一端が接続されており、そのゲートワイヤ30の他端がゲートリード26に接続されている。同様に、ソース電極24に、ソースワイヤ31の一端が接続されていて、そのソースワイヤ31の他端がソースリード27に接続されている。

【0019】

ゲートワイヤ30は、直径100μm以上で、かつ長さ5mm以下であることが好ましく、ソースワイヤ31は、直径300μm以上で、かつ長さ5mm以下であることが好ましい。この実施形態では、ゲートワイヤ30は、直径150μm、長さ4mmであり、ソースワイヤ31は、直径350μm、長さ4mmである。

この実施形態ではMOSFETチップ20は、平面視においてほぼ矩形に形成されている。そして、その矩形のMOSFETチップ20の一方表面において、一辺の中央付近にゲート電極23が形成されている。そして、その他の領域を覆うようにソース電極24が形成されており、このソース電極24は、ゲート電極23に対応する凹部を一辺の中央付近に有している。

【0020】

モールド樹脂22は、MOSFETチップ、ゲートワイヤ30、ソースワイヤ31、ならびにゲートリード26、ソースリード27およびドレインリードの各根本部を覆うように形成されている。チップ支持部29の一方表面は、MOSFET20が搭載されてモールド樹脂22によって封止されたチップ搭載面である。チップ支持部29の他方表面は、モールド樹脂22から露出した放熱面とされていてもよい。また、チップ支持部29は、ソースリード27とは反対側の端部がモールド樹脂22から突出していてもよい。

【0021】

図3は、MOSFETチップ20のソース電極24から下の構成を示す部分拡大平面図であり、図4は、図3の切断面線IV−IVから見た断面図である。MOSFETチップ20は、平面視において格子状に形成されたゲートトレンチ35を有するトレンチゲート型MOSFETとしての基本構造を有している。格子状のゲートトレンチ35によって、平面視矩形(たとえばほぼ正方形)の複数のソース領域44が区画されており、各ソース領域44の中央にはボディ領域43が露出している。

【0022】

図4に最もよく現れているように、MOSFETチップ20は、n+型SiC基板40と、このSiC基板40の表面にエピタキシャル成長させられたSiCエピタキシャル層41とを有している。n+型SiC基板40およびエピタキシャル層41は、MOSFETチップ20の半導体活性領域を構成している。エピタキシャル層41は、SiC基板40に接するn−型ドレイン領域42と、ドレイン領域42上に積層されたp型ボディ領域43と、p型ボディ領域43上に積層されたn+型ソース領域44とを有している。前述のとおり、ボディ領域43は、平面視矩形のソース領域44のほぼ中央部でエピタキシャル層41の表面に露出するように形成されている。

【0023】

ゲートトレンチ35内には、ゲートトレンチ35の底面および側壁面を覆うゲート絶縁膜46が形成されている。すなわち、ゲート絶縁膜46は、ゲートトレンチ35の底面を覆う底面被覆部47と、ゲートトレンチ35の側壁面を覆う側壁被覆部48とを有し、これらの底面被覆部および側壁被覆部48は互いに連続している。そして、底面被覆部47の厚さは、側壁被覆部48の厚さよりも大きくされており、これにより、ゲート−ドレイン間寄生容量の低減が図られている。ゲート絶縁膜46は、酸化膜であってもよいし、酸化膜以外の材料からなる絶縁膜であってもよいし、酸化膜と酸化膜以外の材料との組合せであってもよい。

【0024】

ゲートトレンチ35は、エピタキシャル層41の表面からソース領域44およびボディ領域43を貫通して、その底面がドレイン領域42に達する深さに形成されている。そして、このゲートトレンチ35内にポリシリコンゲート50が埋め込まれている。よって、ポリシリコンゲート50は、ゲート絶縁膜46の側壁被覆部48を介して、p型ボディ領域43に臨んでいる。ポリシリコンゲート50にしきい値以上の制御電圧を与えると、p型ボディ領域43においてゲートトレンチ35の側壁を形成する部分(チャネル領域)の表面付近に反転層(チャネル)が形成される。このチャネルを介して、ソース領域44およびドレイン領域42の間が導通することになる。ポリシリコンゲート50に与えられる制御電圧がしきい値未満のときは、チャネルが形成されず、ソース領域44およびドレイン領域42の間は遮断状態となる。

【0025】

ゲートトレンチ35上には、ゲートトレンチ35の上方領域からソース領域44にまではみ出す領域にわたって、層間絶縁膜51が形成されている。この層間絶縁膜51上に、ソース電極24を形成する金属膜が形成されている。この金属膜は、層間絶縁膜51が形成されていない領域において、ソース領域44およびボディ領域43に接している。ポリシリコンゲート50は、図4には表れていない場所で、エピタキシャル層41の表面上へと引き出され、ゲート電極23に接続されている。ドレイン電極25は、SiC基板40の裏面(エピタキシャル層41とは反対側の表面)にオーミック接触するように形成されている。

【0026】

SiCで活性領域を構成したMOSFETチップ20は、900V以上の破壊電圧を有することができる。

図5は、SiCで活性領域を構成したMOSFETチップ20と、Si(シリコン)半導体で活性領域を構成したスーパージャンクション型MOSFETとの性能指数比較結果を示す。性能指数として、オン抵抗Ronと、全ゲート電荷量Qgとの積Ron・Qgを用い、耐圧900Vで設計したSiC・MOSFETチップ20および耐圧600VのSiスーパージャンクション型MOSFETについて比較を行った。オン抵抗Ronは、MOSFETがオン状態のときのソース・ドレイン間の電気抵抗であり、全ゲート電荷量Qgは、MOSFETをオンからオフに切り換えるときにゲートに注入する必要がある電荷量である。すなわち、全ゲート電荷量Qgが少ないほど、高速なスイッチングが可能である。オン抵抗Ronはチップ面積が大きいほど小さくなり、全ゲート電荷量Qgはチップ面積が大きくなるほど大きくなる。すなわち、オン抵抗Ronと全ゲート電荷量Qgとはトレードオフの関係にあって、これらの積Ron・Qgが小さいほど高性能なMOSFETであるといえる。

【0027】

図5に示す通り、SiCで半導体活性領域を構成したMOSFETチップ20における性能指数Ron・Qgは5ΩnC未満(図5に示す測定値は4.4)であるのに対し、Siスーパージャンクション型MOSFETにおける性能指数Ron・Qgは、14ΩnCよりも大きく(図5に示す測定値は14.6)なっている。つまり、SiCを半導体活性領域に用いたMOSFETチップ20は、Siスーパージャンクション型MOSFETよりもはるかに高性能であること、すなわち低オン抵抗および高速スイッチングを実現した素子であることがわかる。

【0028】

なお、性能指数Ron・Qgの測定に際し、SiC・MOSFETチップ20については、ゲート電圧Vgs=18V、ドレイン電流Ids=10Aとする一方、Siスーパージャンクション型MOSFETについてはゲート電圧Vgs=10V、ドレイン電流Ids=8Aとした。ゲート電圧およびドレイン電流ともに、SiC・MOSFETチップ20に不利な条件であり、SiC・MOSFETチップ20に関する測定条件をSiスーパージャンクションMOSFETと同等とすれば、性能指数Ron・Qgはより一層小さくなる。測定時のソース・ドレイン電圧Vdsは、SiC・MOSFETチップ20およびSiスーパージャンクション型MOSFETのいずれにおいても300Vとし、また、いずれもゲート抵抗Rgは10Ωとした。

【0029】

図6は、SiC・MOSFETチップ20とSiスーパージャンクション型MOSFETとで容量を比較した測定結果を示す。容量には、入力容量Cissと、出力容量Cossと、帰還容量Crssとがある。入力容量Cissとは、ゲート−ソース間寄生容量Cgsとゲート−ドレイン間寄生容量Cgdとの和であり、ゲートの充放電速度に関係するパラメータである。出力容量Cossとは、ドレイン−ソース間寄生容量Cdsとゲート−ドレイン間寄生容量Cgdとの和であり、ソース−ドレイン間のスイッチング速度に関係するパラメータである。帰還容量Crssは、ゲート−ドレイン間寄生容量Cgdに等しい。ゲート電圧をスイッチングさせるときに見えるミラー効果成分は、帰還容量Crssに電荷をチャージしている期間に相当している。つまり、帰還容量Crssが小さければ、ゲート電圧が速くスイッチングし、立ち上がり遅延時間および立ち下がり遅延時間が低減する。したがって、上昇時間および下降時間がゲート電圧のスイッチングの遅さで制限されてしまっている場合に、帰還容量Crssを低減することで、スイッチング時間を改善できる。また、上昇時間および下降時間が制限されていない場合でも、ブリッジ回路でFETを動作させるときに必須であるデッドタイム(ブリッジ内全てのFETをオフさせておく時間)の制御を容易にできるメリットもある。

【0030】

ゲート寄生容量を測定する際は、ゲート電極に印加する基本電圧を0Vとしてソース−ドレイン間に大きな電流が流れないようにして、ドレイン-ソース間に任意の電圧(たとえば0.1V)が印加される。その状態で、ゲート電圧を基本電圧の周辺で高周波振動させる。たとえば、振動電圧Levelを0.1Vとし、振動周波数fを1MHzとしてもよい。こうして、ゲート電圧を高速振動させたときに流れる電流およびその変化率に基づいて、ゲート寄生容量を算出でき、併せてゲート抵抗を算出できる。

【0031】

図6に示すとおり、Siスーパージャンクション型MOSFETにおいては、入力容量が1150pF程度、出力容量が1950pF程度、帰還容量が540pF程度である。これに対して、SiC・MOSFETチップ20においては入力容量が600pF程度、出力容量が560pF程度、帰還容量が350pF程度であり、いずれもSiスーパージャンクション型MOSFETの値よりも小さくなっている。この結果からも、SiC・MOSFETチップ20は、Siスーパージャンクション型MOSFETよりもはるかに高速なスイッチングが可能な素子であることがわかる。

【0032】

SiC・MOSFETチップ20は、ドレイン-ソース間電圧Vds=0.1V、振動周波数f=1MHzで測定したときに、入力容量が700pF未満、出力容量が600pF未満、帰還容量が400pF未満であることが好ましい。さらにまた、SiC・MOSFETチップ20は、耐圧が900V以上であることが好ましく、また、性能指数Ron・Qgが5ΩnC未満であることが好ましく、さらに、ゲート−ソース間電圧Vgsが18Vのときに、面積で規格化したオン抵抗が4mΩcm2以下であることが好ましい。

【0033】

図7は、SiC・MOSFETチップ20とSiスーパージャンクション型MOSFETとにおいて、スイッチング特性を測定した結果を示す。SiC・MOSFETチップ20のゲート電圧Vgsの変化が曲線L1で示されており、SiC・MOSFETチップ20のドレイン−ソース間の電圧Vdsの時間変化が曲線L2で示されている。一方、Siスーパージャンクション型MOSFETにおけるゲート電圧Vgsの時間変化が曲線L3で示されていて、そのドレイン−ソース間電圧Vdsの時間変化が曲線L4で示されている。曲線L1,L3に示すように、ゲート電圧Vgsをオン電圧からオフ電圧に降下させると、それに応答して、MOSFETがターンオフし、ドレイン−ソース間電圧Vdsが0V(導通状態)から100V(遮断状態)へと変化する。ゲート電圧Vgsが下がり始めてからドレイン−ソース間電圧Vdsが立ち上がり始めるまでの時間は「ターンオフ遅延時間」と呼ばれる。また、ドレイン−ソース電圧Vdsが立ち上がり始めてから遮断電圧に達するまでの時間は、ソース・ドレイン間で電流が遮断されるのに要する時間であり、「下降時間」と呼ばれる。

【0034】

図8は、スイッチング素子10(Ron=3.2mΩcm2、900V耐圧)とSiスーパージャンクション型MOSFET(Ron=28mΩcm2、600V耐圧)とのターンオフ遅延時間および下降時間の測定結果を比較して示す図である。スイッチング素子10においては、ターンオフ遅延時間は19nsecであり、下降時間は15nsecである。これに対して、Siスーパージャンクション型MOSFETにおいては、ターンオフ遅延時間が34nsecであり、下降時間が22.5nsecである。スイッチング素子10における下降時間15nsecは、電圧変化速度に換算すると、6.7×109V/秒(=100V/15nsec)であり、Siデバイスでは実現できない、5×109V/秒以上(下降時間に換算して20nsec以下)の電圧変化速度が実現されている。このように、スイッチング素子10においては、Siスーパージャンクション型MOSFETに対して、ターンオフ遅延時間および下降時間が著しく短縮されていることがわかる。すなわち、スイッチング素子10は、Siスーパージャンクション型MOSFETよりもはるかに高速なスイッチングが可能なスイッチング素子である。Siスーパージャンクション型MOSFETでは、Ronを犠牲にしてチップを小さくして高速化を図っているにも拘わらず、SiCデバイスを用いたスイッチング素子10の方がより電圧変化速度が速いのである。

【0035】

図9は、図1に示したDC/DCコンバータ1において、スイッチング素子10として、SiC・MOSFETチップ20を内蔵したもの(実施例)と、SiC・MOSFETチップ20に代えてSiスーパージャンクション型MOSFETを適用した比較例とで、効率を測定した測定結果を示す。スイッチング素子10の駆動周波数、すなわちスイッチング周波数を、400kHzから1300kHzの範囲で変化させながら、入力電力に対する出力電力の比を測定した。入力電力とは、入力電流および入力電圧の各平均値の積であり、出力電力とは出力電流および出力電圧の各平均値の積である。電源電圧(動作電圧)は100Vとし、スイッチング素子10を駆動するときのデューティ比は20%とした。また、負荷7として20Ωの電気抵抗を接続し、チョークコイル16のインダクタンスを47μHとし、電解コンデンサ17には定格電圧50V、容量470μFのものを用いた。

【0036】

図9に示されているように、Siスーパージャンクション型MOSFETを用いた場合は、400〜600kHzの周波数域では88%を超える効率を達成しているものの、1000kHz以上の周波数域では効率が87%未満にまで落ち込んでいる。一方、SiC・MOSFETチップ20を内蔵したスイッチング素子10を適用した場合は、1000kHz付近の周波数域までほとんど効率が低下せず、1200kHz以上の周波数域においても87%を超える効率が達成されている。すなわち、ゲート寄生容量が小さく、かつオン抵抗も低いSiC・MOSFETチップ20を内蔵したスイッチング素子10を用いることによって、高速なスイッチングが可能であり、その結果、DC/DCコンバータ1を1MHz以上の高速な駆動周波数でかつ高効率に駆動することが可能となる。

【0037】

図10は、スイッチング素子10のパッケージ構造に関する変形例を示す図解的な平面図である。この変形例では、SiC・MOSFETチップ20が、ゲート電極23およびソース電極24をリードフレーム61に対向させたフェースダウン方式でリードフレーム61上に実装されている。

リードフレーム61は、ゲートリード62、ソースリード63、およびドレインリード64を含む。ゲートリード62、ソースリード63およびドレインリード64は、たとえば同一平面上に位置するように配列された板状体からなる。ドレインリード64は、ゲートリード62およびソースリード63の間に配置されており、ドレインワイヤ65を介してMOSFETチップ20のドレイン電極25に接続されている。すなわち、ドレインワイヤ65の一端がドレインリード64に接続されており、その他端がドレイン電極25に接続されている。

【0038】

MOSFETチップ20のゲート電極23およびソース電極24は、ボンディングワイヤを用いることなく、すなわちワイヤフリーで、ゲートリード62およびソースリード63にそれぞれ接続されている。具体的には、ソースリード63は、MOSFETチップ20を支持するためのチップ支持部66を一体的に有しており、このチップ支持部66にダイボンディング材(はんだ等)を用いてソース電極24がダイボンディングされている。

【0039】

ソースリード63のチップ支持部66には、ゲートリード62からMOSFETチップ20のゲート電極23に至る経路に対応した切り欠き部67が形成されている。ゲートリード62には、切り欠き部67によって区画された領域に沿って延びるゲートリード延長部68が一体的に形成されている。このゲートリード延長部68の先端部は、MOSFETチップ20のゲート電極23に対向する位置に達している。この先端部に、はんだ等のダイボンディング材を用いてゲート電極23がダイボンディングされている。

【0040】

このようにして、MOSFETチップ20のゲート電極23がワイヤフリーでゲートリード62に接続されているので、寄生ゲート抵抗を低減(たとえば30Ω以下)でき、かつゲート電極23につながる信号線のインダクタンスを低減できる。同様に、ソース電極24とソースリード63とをワイヤフリーで接続することができるので、電源電圧とMOSFETチップ20との間のインダクタンスを低減できる。こうして、より高速で高効率のスイッチングを実現できる。

【0041】

図11は、この発明の第2の実施形態に係る高速スイッチング動作回路であるAC/DC電源回路(いわゆるACアダプタ)の構成(フィードバック回路は省略)を示す電気回路図である。AC/DC電源回路71は、交流電源76に接続される電源端子72,73と、直流電圧を出力する出力端子74,75とを有している。すなわち、AC/DC電源回路71は、交流電源76からの交流電圧(たとえば100V)を整流して、予め定められたレベルの直流電圧を出力端子74,75の間に出力するように構成されている。AC/DC電源回路71は、整流回路77と、平滑コンデンサ78と、高周波トランス79と、スイッチング素子80と、駆動回路81とを含む。交流電源76からの電力は、一対の給電ライン87,88を介して、ダイオードブリッジで構成された整流回路77の一対の入力端子に供給される。一方の給電ライン88には、ヒューズ89が介装されている。ヒューズ89と整流回路77との間には、ノイズフィルタ(入力ラインフィルタ)92が設けられている。この例では、ノイズフィルタ92は、バルントランス90と、給電ライン87,88の間に接続されたバイパスコンデンサ91とを含む。ヒューズ89とノイズフィルタ92の間において、給電ライン87,88間には、ノイズ吸収のための電気抵抗93が接続されている。

【0042】

整流回路77の一対の出力端子は、高電圧ライン85および低電圧ライン86にそれぞれ接続されている。平滑コンデンサ78は、高電圧ライン85および低電圧ライン86の間に接続された電解コンデンサからなる。高周波トランス79の1次側巻線79pの一方の端子は高電圧ライン85に接続されており、その他方の端子は低電圧ライン86に接続されている。低電圧ライン86には、高周波トランス79の1次側巻線79pと整流回路77との間に、スイッチング素子80および電気抵抗94が直列に接続されている。

【0043】

さらに、高電圧ライン85と低電圧ライン86との間には、スイッチング素子80よりも高周波トランス79側において、1次側巻線79pと並列にスナバ回路82が接続されている。スナバ回路82は、電気抵抗95およびコンデンサ96の並列回路と、この並列回路に直列に接続されたダイオード97とを含む。スナバ回路は、スイッチング素子80のスイッチングに伴うスパイク状の高電圧を吸収して電磁ノイズを最小化する。

【0044】

高周波トランス79の2次側巻線79sは、この実施形態では、1次側巻線79pとは反対方向に巻かれている。この2次側巻線79sの一端は出力高電圧ライン98に接続されており、その他端は出力低電圧ライン99に接続されている。

出力高電圧ライン98には、整流素子としてのダイオード83が介装されている。より具体的には、ダイオード83のアノードが2次側巻線79sに接続されており、そのカソードが出力端子74に接続されている。また、出力低電圧ライン99は出力端子75接続されている。出力高電圧ライン98と出力低電圧ライン99との間には、平滑用の電解コンデンサ84が接続されている。電解コンデンサ84の正極側端子は、ダイオード83と出力端子74との間において出力高電圧ライン98に接続されている。

【0045】

スイッチング素子80は、前述の第1の実施形態におけるスイッチング素子10と同様の構成を有し、SiC半導体を活性領域に用いたトレンチゲート型MOSFETチップ20を内蔵している。このスイッチング素子80は、nチャネル型電界効果トランジスタであって、ドレインが高周波トランス79の1次側巻線79pに接続され、そのソースが電気抵抗94を介して整流回路77へと接続されている。この実施形態では、一次側巻線79pは、スイッチング素子80に接続されたチョークコイルと見なすことができる。

【0046】

スイッチング素子80のゲート端子には、駆動回路81が出力する制御信号が入力されるようになっている。駆動回路81は、たとえば1MHz以上の周波数の矩形波駆動パルスを、制御信号として、スイッチング素子80のゲートに供給する。

スイッチング素子80がターンオンすると、高周波トランス79の1次側巻線79pに電流が流れ、その2次側巻線79sに誘導起電力が生じる。この誘導起電力は、ダイオード83に対して逆方向の電流を流そうとする向きの起電力であるため、高周波トランス79の2次側では電流が流れず、2次側巻線79sにエネルギーが蓄えられる。その後、スイッチング素子80がターンオフすると、ダイオード83に対して順方向の電流を流そうとする起電力が2次側巻線79sに生じ、ダイオード83が導通する。こうして、フライバック方式によって、高周波トランス79の1次側巻線79pから2次側巻線79sへとエネルギーが伝達され、1次側巻線79pおよび2次側巻線79sの巻数の比に応じて変圧された電圧が2次側巻線79sに生じる。この電圧が、ダイオード83によって整流され、かつ電解コンデンサ84によって平滑化されることにより、出力端子74,75には、予め定められたレベルの直流電圧が導出される。

【0047】

図12は、スイッチング素子80をターンオフした後のソース−ドレイン間電圧の時間変化を示す波形図である。スイッチング素子80は、ドレイン−ソース間容量Cdsを有しているので、この容量Cdsと1次側巻線79pとでLC共振回路が構成される。そのため、スイッチング素子80をターンオフすると、一次側巻線79pの起電によって、ソース−ドレイン間電圧が電源電圧以上の値に立ち上がり、しばらくすると、整流回路77の出力電圧(たとえば144V)を基準にドレイン−ソース間電圧が振動することになる。

【0048】

そこで、ドレイン−ソース間電圧が極小値をとるタイミングにおいてスイッチング素子80をターンオフするように駆動回路81が構成されている。たとえば、交流電源76からAC100Vが供給される場合に、整流回路77の出力電圧は144Vとなる。したがって、共振による振幅が288V以上(たとえば300V)であれば、ドレイン−ソース間電圧Vdsの極小値は0V以下になる。よって、ソース・ドレイン間電圧Vds=0となるタイミングでスイッチング素子80をターンオンさせることによって、スイッチングロスをなくすことができる。このような動作は、完全電圧共振と呼ばれる。

【0049】

SiCを活性領域に適用したMOSFETチップ20を含むスイッチング素子80では、十分な耐圧を有しているため、ドレイン−ソース間電圧Vdsの振幅が288V以上となるように1次側巻線79pのインダクタンス等の回路定数を設定することができ、スイッチングロスをなくすことが可能である。これに対して、Si半導体を活性領域に適用したスイッチング素子を用いると、その耐圧による制限のために、ドレイン−ソース間電圧Vdsの振幅を288Vよりも低くしておかなければならない。そのため、ドレイン−ソース間電圧Vdsの極小点であっても、Vds>0であるので、スイッチングロスをなくすことができない。したがって、SiCを半導体活性領域に適用したMOSFETチップ20を有するスイッチング素子80を用いることで、完全電圧共振を用いたスイッチング動作が可能となり、それにより、AC/DC電源回路71の効率を向上することができる。

【0050】

図13は、この発明の第3の実施形態に係る高速スイッチング動作回路であるワイヤレス給電装置の電気的構成を示す回路図である。ワイヤレス給電装置111は、受電機器112に対して、ワイヤレスで、すなわち給電部端の電極と受電部端の電極とが非接触状態で、電力を供給するための装置である。ワイヤレス給電装置111は、高周波回路113と、駆動回路114と、共振回路115(115A,115B)とを含む。

【0051】

高周波回路113は、直流電源116からの電力供給を受けるための電源端子117,118を備えている。電源端子117は、直流電源116の正極に接続され、電源電圧ライン119に電源電圧を供給する。一方、電源端子118は、直流電源116の負極に接続され、グランドライン120にグランド電位を与える。高周波回路113は、第1および第2のスイッチング素子121,122と、高周波トランス123と、共振インダクタ124と、平滑コンデンサ125とを含む。電源電圧ライン119は、第1分岐ライン119Aと、第2分岐ライン119Bとに分岐している。第1分岐ライン119Aに第1スイッチング素子121が介装されており、第2分岐ライン119Bに第2スイッチング素子122が介装されている。第1スイッチング素子121および第2スイッチング素子122は、前述の第1の実施形態におけるスイッチング素子10と同様の構成を有し、SiC半導体からなる活性領域を有するMOSFETチップ20を内蔵したnチャネル型電界効果トランジスタとしての基本構成を有している。第1スイッチング素子121および第2スイッチング素子122の各ゲートには、駆動回路114からの制御信号が供給されるようになっている。

【0052】

高周波トランス123は、第1一次側巻線127と、第2一次側巻線128と、二次側巻線129とを備えている。第1一次側巻線127と第2一次側巻線128とは、各一端が互いに接続されており、その接続点126にグランドライン120が接続されている。そして、グランドライン120に共振インダクタ124が介装されている。第1一次側巻線127において第2一次側巻線128の接続点126と反対側の端子に、第1スイッチング素子121が接続されている。同様に、第2一次側巻線128において第1一次側巻線127との接続点126と反対側の端子に第2スイッチング素子122が接続されている。第1スイッチング素子121および第2スイッチング素子122に対して高周波トランス123側において、第1分岐ライン119Aと第2分岐ライン119Bとの間に平滑コンデンサ125が接続されている。この実施形態では、第1一次側巻線127は、第1スイッチング素子121に接続されたチョークコイルと見なすことができ、第2一次側巻線128は、第2スイッチング素子122に接続されたチョークコイルと見なすことができる。

【0053】

高周波トランス123の二次側巻線129には複数の共振回路115が接続されている。より具体的には、複数の共振回路115は、二次側巻線129の一方側端子に接続された複数の第1共振回路115Aと、二次側巻線129の他方の端子に接続された複数の第2共振回路115Bとを含む。各共振回路115は、コイル131と、出力電極132とを直列接続して構成されている。出力電極132は、受電機器112に備えられた入力電極133に対してギャップ134を介して容量結合しており、これらの出力電極132および入力電極133によってコンデンサ135が形成されるようになっている。このコンデンサ135と、コイル131とで、予め定める共振周波数(たとえば6.78MHz)において共振する共振回路が構成されている。

【0054】

受電機器112は、複数の入力電極133と、各入力電極133に対応した整流回路140と、平滑コンデンサ141と、DC/DCコンバータ142と、内蔵された負荷143とを含む。各整流回路140は、電源電圧ライン144とグランドライン145との間に直列接続された一対のダイオードを有しており、それらの一対のダイオードの間の接続点に入力電極133が接続されている。平滑コンデンサ141は、電源電圧ライン144とグランドライン145との間に接続されている。DC/DCコンバータ142は、電源電圧ライン144に接続されたnpnトランジスタ146と、トランジスタ146のベースに接続されたスイッチング駆動回路147と、トランジスタ146のエミッタとグランドライン145との間に接続された整流素子としてのダイオード148と、トランジスタ146と負荷143との間に接続されたチョークコイル149と、チョークコイル149と負荷143との間においてグランドライン145との間に接続された平滑コンデンサ150とを含む。

【0055】

図14は、駆動回路114から第1スイッチング素子121のゲートに供給される第1制御信号と、駆動回路114から第2スイッチング素子122のゲートに供給される第2制御信号と、高周波トランス123の二次側巻線129に導出される電圧波形とを示す波形図である。

第1および第2制御信号は、第1スイッチング素子121および第2スイッチング素子122を、交互にオン/オフさせるための矩形波信号である。第1制御信号がハイレベルの期間には第2制御信号がローレベルとなり、第2制御信号がハイレベルの期間には第1制御信号がローレベルとなる。第1制御信号のハイレベル期間と第2制御信号のハイレベル期間との間には、所定長のデッドタイムが確保されている。

【0056】

第1制御信号のハイレベル期間に第1スイッチング素子121が導通し、第1制御信号のローレベル期間に第1スイッチング素子121が遮断される。同様に、第2制御信号のハイレベル期間に第2スイッチング素子122が導通し、第2制御信号のローレベル期間に第2スイッチング素子122が遮断状態となる。よって、第1スイッチング素子121および第2スイッチング素子122は、交互に導通して、直流電源116からの電流をそれぞれ第1一次側巻線127および第2一次側巻線128に供給する。

【0057】

第1スイッチング素子121が導通すると、第1一次側巻線127には第1分岐ライン119Aからグランドライン120に向かって電流が流れる。また第2スイッチング素子122が導通すると、第2一次側巻線128には、第2分岐ライン119Bからグランドライン120に向かって電流が流れる。

第1スイッチング素子121が遮断されると、第1一次側巻線127はグランドライン120から第1分岐ライン119Aに向かって電流を流そうとする起電力を生じ、この起電力と第2スイッチング素子122の導通によって第2一次側巻線128に現れる電圧とが加算されて、大きな振幅の電圧が発生する。同様に、第2スイッチング素子122が遮断されると、第2一次側巻線128はグランドライン120から第2分岐ライン119Bに向かって電流を流そうとする起電力を生じ、第1スイッチング素子121の導通によって第1一次側巻線127に現れる電圧がこれに加算されることによって、大きな電圧が生じる。

【0058】

こうして、第1スイッチング素子および第2スイッチング素子121,122をプッシュプル動作させることによって、高周波トランス123の一次側から二次側へと高効率でエネルギーを伝達することができる。そして、二次側巻線129が発生する交流電圧が、共振回路115によって共振することにより、コンデンサ135を構成する出力電極132から入力電極133へと高効率で電力を供給することができる。

【0059】

受電機器112においては、入力電極133から入力される交流電圧が整流回路140によって整流され、さらに平滑コンデンサ141によって平滑化されることにより、直流電圧に変換される。この直流電圧がDC/DCコンバータ142に入力される。npnトランジスタ146が、スイッチング駆動回路147から出力される所定デューティ比の駆動信号によってオン/オフされることにより、そのデューティ比に応じた電圧に降圧された直流電圧が生じる。すなわち、npnトランジスタ146が導通するとチョークコイル149に電流が供給され、npnトランジスタ146が遮断されるとチョークコイル149が生じる起電力によってダイオード148が導通して負荷143に向かって電流が供給される。そして、平滑コンデンサ150の働きにより、安定した直流電圧が負荷143に供給されることになる。

【0060】

負荷143は、受電機器112に備えられたバッテリを充電する充電回路を含んでいてもよい。

図15は、ワイヤレス給電装置111の具体的な構成例を説明するための図解的な斜視図である。複数の出力電極132は、プラスチック等の絶縁材料で構成された電極保持板155に配列されて固定されている。より具体的には、電極保持板155の表面には、複数の出力電極132をそれぞれ埋設するための凹所156が所定の配列パターンで間隔をあけて形成されている。各凹所156に出力電極132が1つずつ埋設されて固定されている。その状態で、電極保持板155の表面には、絶縁材料からなるシート体157(図15では明瞭化のために電極保持板155から分離した状態で表してある。)が貼り付けられ、これによって、出力電極132が凹所156内に保持されている。

【0061】

電極保持板155の裏面側には、出力電極132とともに共振回路115を形成するコイル131が保持されていて、出力電極132の裏面側に直付けされて電気的に接続されている。各コイル131の他方の出力端子はケーブル158を介して高周波回路113に接続されている。高周波回路113には、電源ケーブル159を介して直流電源116が接続されている。さらに、高周波回路113には、信号ケーブル160を介して駆動回路114が接続されている。

【0062】

図16は、電極保持板155に対する出力電極132およびコイル131の取付構造例を説明するための図解的な拡大断面図である。出力電極132を収容する凹所156の底面には貫通孔161が形成されている。この貫通孔161をコイル131の一方の端子131Aが貫通して、出力電極132の裏面にはんだ付けされている。こうして、コイル131が、出力電極132に対して、ケーブル等を介することなく直付けされており、コイル131と出力電極132との間のインダクタンスが最小化されている。具体的には、コイル131から引き出された端子131Aの長さは5mm以下であることが好ましい。コイル131は、電極保持板155の裏面にボルト162によって固定された保持キャップ163によって保持されている。保持キャップ163には貫通孔164が形成されていて、この貫通孔からコイル131の他方の端子131Bが引き出されている。端子131Bにケーブル158の一端がはんだ付けされている。

【0063】

受電機器112は、電極保持板155の表面の任意の位置に置かれ、その状態で給電を受けることができる。すなわち、電極保持板155の表面に複数の出力電極132が広い範囲にわたって分布しているので、受電機器112の入力電極133は、いずれかの出力電極132と容量結合して、コンデンサ135を形成する。これにより、受電機器112は、共振回路115を介して、高周波回路113から高周波電力の供給を受けることができる。

【0064】

駆動回路114は、第1および第2スイッチング素子121,122を1MHz以上の高周波域の駆動周波数(好ましくは共振回路115の共振周波数)で駆動する。これにより、高周波電力は、出力電極132および入力電極133によって形成されるコンデンサ135を通過して、受電機器112へと効率的に供給される。

受電機器112側に設けられる入力電極133は、少なくとも一対設けられればよいが、広い面積の電極保持板155の表面上のいずれの位置においても効率的な高周波給電を可能とするためには、複数対の入力電極133を受電機器112に設けることが好ましい。多数の入力電極133を設けることによって、電極保持板155の表面上のいずれの位置に受電機器112が置かれた場合であっても、出力電極132と入力電極133とによって形成されるコンデンサ135の容量をある程度一定にすることができる。これによって、共振回路115における共振を保証することができるので、高周波回路から受電機器112への効率的なワイヤレス給電が可能となる。とくに、第1および第2スイッチング素子121,122にSiC半導体のMOSFETを適用して、大電力を高周波で伝達するには、共振回路115における共振を保証することが重要であり、この観点から、多数対の入力電極133を受電機器112に備えることが好ましい。

【0065】

図17は、高周波回路113の構成例を示す図解的な斜視図である。高周波回路113は、多層プリント配線基板167を有している。この多層プリント配線基板167に、第1スイッチング素子121、第2スイッチング素子122、高周波トランス123、共振インダクタ124、および平滑コンデンサ125が実装されている。多層プリント配線基板167は、絶縁層168,169,170と、絶縁層169,170を挟んで積層された第1〜第3配線層171,172,173とを含む。すなわち、下側から順に、絶縁層168、第1配線層171、絶縁層169、第2配線層172、絶縁層170、第3配線層171の順に、絶縁層と配線層とが交互に積層されている。

【0066】

図18は、第1配線層171、第2配線層172および第3配線層173にそれぞれ形成された配線パターンの例を説明するための図解的な斜視図である。第1配線層171は、それぞれ矩形に形成された第1グランドパターン175および第2グランドパターン176を有している。第1および第2グランドパターン175,176は互いに絶縁されている。第1および第2グランドパターン175および176は、平面視において、多層プリント配線基板167のほぼ全域を占めるように形成されている。第2グランドパターン176は、多層プリント配線基板167の厚さ方向に沿って層間を貫通するビア208によって、第3配線層173に形成されたグランド用ランド209に接続されている。

【0067】

第2配線層172には、第1分岐ライン119Aおよび第2分岐ライン119Bにそれぞれ対応する第1電源電圧パターン181および第2電源電圧パターン182が互いに分離されて形成されている。第1および第2電源電圧パターン181,182は、平面視において、第1グランドパターン175から第2グランドパターン176に跨がり、かつ大部分が第1および第2グランドパターン175,176とオーバレイするように形成されている。

【0068】

第1電源電圧パターン181は、たとえば細長い長方形の帯状に形成されており、その一端付近の直上には、第3配線層173にランド183が形成されている。ランド183と第1電源電圧パターン181とはビア186を介して接続されている。ランド183には高周波トランス123の第1一次側巻線127の一端が接続されている。第1一次側巻線127の他端は、同じく第3配線層173に形成されたランド184に接続されている。第2電源電圧パターン182も、第1電源電圧パターン181と同様に、細長い長方形の帯状に形成されており、その一方端には、ビア187を介して、第3配線層173に形成されたランド185が接続されている。このランド185に、第2一次側巻線128の一方の端子が接続されている。第2一次側巻線128の他方の端子は、前述のランド184に接続されている。ランド184は、ビア188を介して、第1配線層171の第1グランドパターン175に接続されている。

【0069】

高周波トランス123の二次側巻線129は、第1および第2一次側巻線127,128と磁気的に結合されるように、それらの近傍において多層プリント配線基板167の表面に実装されている。第3配線層173は、二次側巻線129の一端に接続されたランド191と、二次側巻線129に接続された別のランド192とを有している。これらのランド191,192は、ケーブル158を介して電極保持板155に保持されたコイル131に電気的に接続されることになる(図15参照)。

【0070】

第3配線層173には、さらに、共振インダクタ124の一対の端子が接続されるランド177,178が形成されている。ランド177は多層プリント配線基板167の厚さ方向に層間を貫通するビア179によって第1グランドパターン175に接続されている。もう1つのランド178は、多層プリント配線基板167の厚さ方向に層間を貫通するビア180によって第2グランドパターン176に接続されている。共振インダクタ124の一対の端子は、ランド177,178にはんだ付けされ、これによって多層プリント配線基板167上に共振インダクタ124が実装されている。こうして、第1グランドパターン175と第2グランドパターン176との間に共振インダクタ124が電気的に介装されることになる。

【0071】

平滑コンデンサ125は、第3配線層173に形成されたランド195,196に一対の端子がそれぞれはんだ付けされて多層プリント配線基板167上に実装されている。ランド195は、ビア189を介して第1電源電圧パターン181に接続されており、ランド196は別のビア190を介して第2電源電圧パターン182に接続されている。

第1電源電圧パターン181において第1一次側巻線127とは反対側の端部は、幅狭に形成されており、これによって、第1電源電圧パターン181には平面視矩形の切り欠き部181aが形成されている。同様に、第2電源電圧パターン182は、第2一次側巻線128とは反対側の端部に幅狭部を有していて、これにより平面視矩形の切り欠き部182aが形成されている。第2配線層172は、第1および第2電源電圧パターン181,182から分離された第3電源電圧パターン200を有している。第3電源電圧パターン200は、切り欠き部181a,182aにそれぞれ入り込む第1接続部198および第2接続部199を有している。

【0072】

第1電源電圧パターン181の幅狭部の直上には、第3配線層173にソース用ランド201が形成されており、ビア211を介して第1電源電圧パターン181に接続されている。また、第3電源電圧パターン200の第1接続部198の直上には、第3配線層173にドレイン用ランド202が形成されていて、ビア212を介して第1接続部198に接続されている。ドレイン用ランド202の側方には帯状に形成されたゲート用ランド203の一端部が位置している。ソース用ランド201、ドレイン用ランド202、およびゲート用ランド203の端部には、第1スイッチング素子121のソースリード27、ドレインリード28およびゲートリード26がはんだ付されて接合されている。これにより、第1スイッチング素子121が多層プリント配線基板167上に実装されている。

【0073】

同様に、第2電源電圧パターン182の幅狭部の直上には、第3配線層173にソース用ランド205が形成されており、ビア215を介して第2電源電圧パターン182に接続されている。さらに、第3電源電圧パターン200の第2接続部199の直上において第3配線層173には、ドレイン用ランド206が形成されており、ビア216を介して第第2接続部199に接続されている。ドレイン用ランド206の側方には、帯状に形成されたゲート用ランド207の一端部が位置している。ソース用ランド205、ドレイン用ランド206およびゲート用ランド207の端部には、第2スイッチング素子122のソースリード27、ドレインリード28およびゲートリード26がそれぞれはんだ付けされて接続されている。これにより、第2スイッチング素子122が、多層プリント配線基板167の表面に実装されている。

【0074】

第3電源電圧パターン200の一端部の直上には、第3配線層173に、電源接続用ランド210が形成されており、ビア217を介して電源電圧パターン200に接続されている。

ゲート用ランド203,207には、信号ケーブル160(図15参照)が接続される。また、電源接続用ランド210およびグランド用ランド209には、電源ケーブル159(図15参照)が接続される。

【0075】

図13から理解されるとおり、第1および第2分岐ライン119Aおよび119Bに流れる電流の方向と、グランドライン120に流れる電流の方向とは逆向きになる。そこで、第1および第2分岐ライン119Aおよび119Bとグランドライン120とを互いに平行にしておくことによって、これらの間の相互インダクタンスを低減することができる。図17および図18に示した構成では、第1配線層171の第1および第2グランドパターン175,176にオーバレイするように、第2配線層172の第1、第2および第3電源電圧パターン181,182,200が形成されている。これによって、第1および第2分岐ライン119A,119Bとグランドライン120との大部分を平行にすることができるので、相互インダクタンスを低減できる。これによって、高周波回路113の寄生インピーダンスを小さくすることができるので、ケーブル158(図15参照)のインピーダンスと高周波回路113のインピーダンスとを整合させることができ、効率の一層の向上を図ることができる。

【0076】

図19は、図15および図16に示した電極保持板155に代えて用いることができる電極保持板220の構造例を示す部分拡大断面図である。電極保持板220は、プリント配線基板としての基本形態を有しており、その一方表面に出力電極132を構成する薄膜電極が形成されている。そして、電極保持板220の他方の表面にコイル131が実装されている。コイル131の一方の端子131Aは、電極保持板220の他方表面に形成されたランド221にはんだ付けされている。ランド221は、電極保持板220に形成された貫通ビア222を介して出力電極132としての薄膜電極に接続されている。このような構成によっても、出力電極132およびコイル131を電極保持板220に共通に保持し、かつコイル131と出力電極132とを5mm以下の配線長で互いに電気的に接続することができる。

【0077】

以上、この発明の一実施形態について説明したが、この発明は、さらに他の形態で実施することもできる。たとえば、第1の実施形態では、降圧型のDC/DCコンバータを例示したが、昇圧型のDC/DCコンバータにこの発明を適用してもよい。さらに、その他のスイッチング電源に対しても、この発明を適用することができる。

その他、特許請求の範囲に記載された事項の範囲で種々の設計変更を施すことが可能である。

【符号の説明】

【0078】

1 DC/DCコンバータ

6 直流電源

7 負荷

10 スイッチング素子

11 駆動回路

12 ダイオード(整流用素子)

13 平滑回路

14 電解コンデンサ

16 チョークコイル

17 電解コンデンサ

20 MOSFETチップ

21 リードフレーム

22 モールド樹脂

23 ゲート電極

24 ソース電極

25 ドレイン電極

26 ゲートリード

27 ソースリード

28 ドレインリード

29 チップ支持部

30 ゲートワイヤ

31 ソースワイヤ

35 ゲートトレンチ

40 n+型SiC基板

41 SiCエピタキシャル層

42 n−型ドレイン領域

43 p型ボディ領域

44 n+型ソース領域

46 ゲート絶縁膜

47 底面被覆部

48 側壁被覆部

50 ポリシリコンゲート

51 層間絶縁膜

61 リードフレーム

62 ゲートリード

63 ソースリード

64 ドレインリード

65 ドレインワイヤ

66 チップ支持部

71 AC/DC電源回路

76 交流電源

77 整流回路

78 平滑コンデンサ

79 高周波トランス

79p 一次側巻線

79s 二次側巻線

80 スイッチング素子

81 駆動回路

82 スナバ回路

83 ダイオード(整流素子)

84 電解コンデンサ

111 ワイヤレス給電装置

112 受電機器

113 高周波回路

114 駆動回路

115 共振回路

116 直流電源

119 電源電圧ライン

119A 第1分岐ライン

119B 第2分岐ライン

120 グランドライン

121 第1スイッチング素子

122 第2スイッチング素子

123 高周波トランス

124 共振インダクタ

125 平滑コンデンサ

127 第1一次側巻線

128 第2一次側巻線

129 二次側巻線

131 コイル

132 出力電極

133 入力電極

135 コンデンサ

140 整流回路

141 平滑コンデンサ

142 DC/DCコンバータ

143 負荷

146 npnトランジスタ

147 スイッチング駆動回路

148 ダイオード

149 チョークコイル

150 平滑コンデンサ

155 電極保持板

156 凹所

157 シート体

158 ケーブル

159 電源ケーブル

160 信号ケーブル

161 貫通孔

167 多層プリント配線基板

171 第1配線層

172 第2配線層

173 第3配線層

175 第1グランドパターン

176 第2グランドパターン

181 第1電源電圧パターン

182 第2電源電圧パターン

220 電極保持板

【特許請求の範囲】

【請求項1】

活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子を有し、前記スイッチング素子が1MHz以上の駆動周波数で駆動され、かつスイッチング時の電圧変化速度が5×109V/秒以上である、高速スイッチング動作回路。

【請求項2】

前記MISFETが、前記活性領域に形成されたトレンチと、前記トレンチの底面および壁面を絶縁膜と、前記絶縁膜を介して前記活性領域に対向するゲート電極とを含む、トレンチゲート構造を有している、請求項1に記載の高速スイッチング動作回路。

【請求項3】

前記絶縁膜は、前記トレンチの底面を覆う底面被覆部の厚さが、前記トレンチの壁面を覆う壁面被覆部の厚さよりも厚い、請求項2に記載の高速スイッチング動作回路。

【請求項4】

前記MISFETの動作電圧が100V以上であり、前記MISFETの破壊電圧が900V以上である、請求項1〜3のいずれか一項に記載の高速スイッチング動作回路。

【請求項5】

前記MISFETのドレイン−ソース間の電圧を0.1Vとし、前記MISFETのゲートに1MHzの振動周波数の信号を与えて測定したときに、前記MISFETの入力容量が700pF未満であり、前記MISFETの出力容量が600pF未満であり、かつ前記MISFETの帰還容量が400pF未満である、請求項1〜4のいずれか一項に記載の高速スイッチング動作回路。

【請求項6】

前記MISFETのゲート−ソース間電圧が18Vのときに、前記MISFETのオン抵抗が4mΩcm2以下である、請求項1〜5のいずれか一項に記載の高速スイッチング動作回路。

【請求項7】

前記MISFETは、オン抵抗Ronと全ゲート電荷量Qgとの積で表される性能指数Ron・Qgが5ΩnC未満である、請求項1〜6のいずれか一項に記載の高速スイッチング動作回路。

【請求項8】

前記MISFETの寄生ゲート抵抗が30Ω以下である、請求項1〜7のいずれか一項に記載の高速スイッチング動作回路。

【請求項9】

前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ドレイン電極を支持基板に接合したフェースアップ方式で前記チップが実装されており、前記ゲート電極およびソース電極にそれぞれゲートワイヤおよびソースワイヤが接続されていて、前記ゲートワイヤは、直径100μm以上、長さ5mm以下であり、前記ソースワイヤは、直径300μm以上、長さ5mm以下である、請求項1〜8のいずれか一項に記載の高速スイッチング動作回路。

【請求項10】

前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ゲート電極およびソース電極を支持基板に接合したフェースダウン方式で前記チップが実装されている、請求項1〜8のいずれか一項に記載の高速スイッチング動作回路。

【請求項11】

前記スイッチング素子に一端が接続されたチョークコイルを有する、請求項1〜10のいずれか一項に記載の高速スイッチング動作回路。

【請求項12】

電源電圧ラインとグランドラインとが互いに平行に形成されている、請求項1〜11のいずれか一項に記載の高速スイッチング動作回路。

【請求項13】

前記グランドラインが形成された第1配線層と、前記電源電圧ラインが前記グランドラインにオーバレイするように形成された第2配線層とを含む多層配線基板上に前記MISFETが実装されている、請求項12に記載の高速スイッチング動作回路。

【請求項1】

活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子を有し、前記スイッチング素子が1MHz以上の駆動周波数で駆動され、かつスイッチング時の電圧変化速度が5×109V/秒以上である、高速スイッチング動作回路。

【請求項2】

前記MISFETが、前記活性領域に形成されたトレンチと、前記トレンチの底面および壁面を絶縁膜と、前記絶縁膜を介して前記活性領域に対向するゲート電極とを含む、トレンチゲート構造を有している、請求項1に記載の高速スイッチング動作回路。

【請求項3】

前記絶縁膜は、前記トレンチの底面を覆う底面被覆部の厚さが、前記トレンチの壁面を覆う壁面被覆部の厚さよりも厚い、請求項2に記載の高速スイッチング動作回路。

【請求項4】

前記MISFETの動作電圧が100V以上であり、前記MISFETの破壊電圧が900V以上である、請求項1〜3のいずれか一項に記載の高速スイッチング動作回路。

【請求項5】

前記MISFETのドレイン−ソース間の電圧を0.1Vとし、前記MISFETのゲートに1MHzの振動周波数の信号を与えて測定したときに、前記MISFETの入力容量が700pF未満であり、前記MISFETの出力容量が600pF未満であり、かつ前記MISFETの帰還容量が400pF未満である、請求項1〜4のいずれか一項に記載の高速スイッチング動作回路。

【請求項6】

前記MISFETのゲート−ソース間電圧が18Vのときに、前記MISFETのオン抵抗が4mΩcm2以下である、請求項1〜5のいずれか一項に記載の高速スイッチング動作回路。

【請求項7】

前記MISFETは、オン抵抗Ronと全ゲート電荷量Qgとの積で表される性能指数Ron・Qgが5ΩnC未満である、請求項1〜6のいずれか一項に記載の高速スイッチング動作回路。

【請求項8】

前記MISFETの寄生ゲート抵抗が30Ω以下である、請求項1〜7のいずれか一項に記載の高速スイッチング動作回路。

【請求項9】

前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ドレイン電極を支持基板に接合したフェースアップ方式で前記チップが実装されており、前記ゲート電極およびソース電極にそれぞれゲートワイヤおよびソースワイヤが接続されていて、前記ゲートワイヤは、直径100μm以上、長さ5mm以下であり、前記ソースワイヤは、直径300μm以上、長さ5mm以下である、請求項1〜8のいずれか一項に記載の高速スイッチング動作回路。

【請求項10】

前記MISFETは、前記活性領域の一方表面にゲート電極およびソース電極を有し、他方表面にドレイン電極を有するチップからなり、前記ゲート電極およびソース電極を支持基板に接合したフェースダウン方式で前記チップが実装されている、請求項1〜8のいずれか一項に記載の高速スイッチング動作回路。

【請求項11】

前記スイッチング素子に一端が接続されたチョークコイルを有する、請求項1〜10のいずれか一項に記載の高速スイッチング動作回路。

【請求項12】

電源電圧ラインとグランドラインとが互いに平行に形成されている、請求項1〜11のいずれか一項に記載の高速スイッチング動作回路。

【請求項13】

前記グランドラインが形成された第1配線層と、前記電源電圧ラインが前記グランドラインにオーバレイするように形成された第2配線層とを含む多層配線基板上に前記MISFETが実装されている、請求項12に記載の高速スイッチング動作回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−93444(P2013−93444A)

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願番号】特願2011−234771(P2011−234771)

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年5月16日(2013.5.16)

【国際特許分類】

【出願日】平成23年10月26日(2011.10.26)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]