高速プリアンプ回路、検出電子機器、および放射線検出システム

【課題】高速プリアンプ回路、検出電子機器、および放射線検出システムを提供する。

【解決手段】プリアンプ回路は、放射線検出器から電流信号を受信して、増幅電圧信号を生成するトランスインピーダンス・アンプを備える。トランスインピーダンス・アンプの出力は、第2増幅ステージに接続される。検出電子機器は、検出器上の第1位置から電流信号を受信して第1電圧信号を生成する第1トランスインピーダンス・アンプと、検出器上の第2位置から電流信号を受信して第2電圧信号を生成する第2トランスインピーダンス・アンプとを有する。第2増幅ステージは、第1増幅電圧信号と第2増幅電圧信号とを与える。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を受信し、各々から一対の出力を提供する。読取回路類は、一対の出力の各々を処理する処理構造を有する。処理構造は、タイムスタンプを有する単一のデジタル出力を提供する。

【解決手段】プリアンプ回路は、放射線検出器から電流信号を受信して、増幅電圧信号を生成するトランスインピーダンス・アンプを備える。トランスインピーダンス・アンプの出力は、第2増幅ステージに接続される。検出電子機器は、検出器上の第1位置から電流信号を受信して第1電圧信号を生成する第1トランスインピーダンス・アンプと、検出器上の第2位置から電流信号を受信して第2電圧信号を生成する第2トランスインピーダンス・アンプとを有する。第2増幅ステージは、第1増幅電圧信号と第2増幅電圧信号とを与える。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を受信し、各々から一対の出力を提供する。読取回路類は、一対の出力の各々を処理する処理構造を有する。処理構造は、タイムスタンプを有する単一のデジタル出力を提供する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、高速プリアンプ回路、ならびに関連する検出電子機器、および放射線検出システムに関する。

【背景技術】

【0002】

広角チョッパ分光計(ARCS)は、破砕中性子源(SNS)用に開発される中性子散乱機器である。広角チョッパ分光計は、サンプルでの高中性子束を提供し、大立体角検出器を提供する。

【0003】

破砕中性子源での中性子は、破砕処理によって生成され、高エネルギ陽子が目標物に衝突して短期間に多くのエネルギで大きな中性子束を生成する。破砕中性子源機器は、中性子のエネルギを判断するために飛行時間(TOF)測定を使用する。検出された中性子の飛行時間を判断するために、検出電子機器は、陽子が破砕目標物に当たる時間を示す計時マーカを必要とする。

【0004】

広角チョッパ分光計は、20mev〜2,000meVの入射エネルギ(Ei)を持った中性子を使用する、エネルギ( )中の適度な分解能と大きな運動量(Q)伝達範囲を持ったフェルミ・チョッパ分光計である。広角チョッパ分光計は、材料における力学的処理の科学を前進させるために使用できる。それは、従来の高エネルギ・チョッパ分光計よりも良い効率で、数meV〜数百meVのエネルギを有する材料と凝縮物質の励起を測定するように設計される。広角チョッパ分光計の用途は、(i)相関電子を持った材料を含む材料の振動励起、ならびにそれらの状態図と状態方程式の関係に関する研究と、(ii)磁石、超伝導体、および金属絶縁体転移に近い材料におけるスピン相関に関する研究とを含むが、これらに限定されるものではない。

【0005】

図1は、典型的な広角チョッパ分光計100の模式図である。目標物(図示略)の陽子衝撃によって生成された中性子は、分離された周囲水モデレータ101によって緩和される。その後、中性子は、サンプル室106に収容されたサンプル110に入射ビームラインを通じて伝播する。入射ビームラインに沿って中核容器インサートがあり、それは、シャッタから周囲水モデレータ101および中性子ガイドの近くへの中性子光学機器の配置を可能にする。

【0006】

広角チョッパ分光計100のビームラインは、周囲水モデレータ101と、T0チョッパ102と、フェルミ・チョッパ103とを具備した中性子ガイド105を備える。T0チョッパ102は、陽子が目標物に当たる場合に中性子を遮蔽するために周囲水モデレータ101から約8.5mに配置される。フェルミ・チョッパ103は、600Hzまでの速度で動作し、それは、Eiを規定する。検出器115は、サンプル110によって散乱された中性子を検出する。検出器115は、真空容器120内に配置されるように示される。

【0007】

サンプル110とその向こうのすべてのものが二次分光計を構成する。中性子は、真空のサンプル室(容器)120内のサンプル110で散乱し、10気圧(1.0MPa)の圧力でHe3を充填された複数の線形位置感応検出器(LPSD)115に移動する。中性子飛行時間は、散乱中性子の最終エネルギ(Ef)を判断するために、これらの検出器によって測定される。

【0008】

広角チョッパ分光計100は、20meV<Ei<2000meVの中性子で動作する

ように設計される。このエネルギ範囲の中性子を提供するように最適化された周囲水モデレータ101は、分離水モデレータである。その深さは、機器のエネルギ分解能に対して無視可能な貢献をする程度の狭い時間分布で殆どの束を提供するように最適化される。更に、この深さは、この周囲水モデレータの同一の面を見た場合の他の機器への性能劣化を最小限にする制約の下で最適化される。

【0009】

検出器115に関して、広角チョッパ分光計100は、線形位置感応検出器を利用するように設計される。広角チョッパ分光計100上の検出器アレイは、それぞれ25mm径の複数の線形位置感応検出器によって、約9001.0mの長さを備えるように設計される。それぞれ線形位置感応検出器は、10気圧(1.0MPa)の圧力でHe3を充填される。検出器115の長さは、電子機器によって長さ約15mmのピクセルに分割され、合計約60,000個の個々の検出器要素に分割される。各ピクセルは、約0.5°の角度範囲を定める。各ピクセルは、1マイクロ秒の計時分解能を有するべきであり、70,000n/s未満では飽和すべきではない。飽和後、チューブは、10マイクロ秒内の測定の準備ができる。検出器は、真空容器内の8個のモジュールにグループ化される。必要に応じて、それらは、操作とヒストグラム生成用のデータ取得ソフトウェアにデータを与える。

【0010】

線形位置感応検出器115に関連した検出電子機器(図1では図示略)は、広角チョッパ分光計100の重要な部分である。検出電子機器のフロントエンドには、プリアンプ回路類が備えられる。現在の最先端技術のプリアンプ設計は、大きなフィードバック抵抗器(典型的には、>1MΩ)を有する第1オペアンプを利用し、それは、検出器によって検出される入力電荷を積分するように操作可能である。第1オペアンプは、ガウス式のパルス整形フィルタに接続(結合)される。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】国際公開第2006/072848号

【発明の概要】

【発明が解決しようとする課題】

【0012】

広角チョッパ分光計100は、図1に示すように検出器と、関連する電子機器とを真空容器内に配置することによって単純化できる。しかしながら、検出電子機器を真空内に配置することは、主として多量のワット損による従来のプリアンプ回路類と互換性を持たない。加えて、そのような環境に有用な他の搭載支援回路類(たとえば温度センサ)は、一般的には使用されない。更に、特に、広角チョッパ分光計100のような用途に対して、100kHzよりもずっと速く動作する高速電子機器は、改良された高電圧保護回路類および雑音除去と同様に、必要とされる。

【課題を解決するための手段】

【0013】

本発明の一態様は、放射線検出器によって与えられる信号を処理するプリアンプ回路である。本発明の一態様によれば、プリアンプ回路は、検出器から電流信号を受信するトランスインピーダンス・アンプを備えることができる。トランスインピーダンス・アンプは、出力で増幅電圧信号を生成するように接続される。第2増幅ステージは、トランスインピーダンス・アンプの出力に接続された入力を具備できる。第2増幅ステージは、オペアンプを備えることができる。プリアンプ回路は、電圧オフセットまたは電流オフセットを補償するオフセット補償構造を有する。オペアンプの反転入力は、トランスインピーダンス・アンプの出力に接続される。オフセット補償構造は、第2オペアンプの非反転入力に接続される。オフセット補償構造は、分圧器を駆動する外部電圧源を備えることができる。分圧器の一端は、接地される。分圧器の中心タップは、第2オペアンプの非反転入力に

直接接続される。プリアンプ回路は更に、第2増幅ステージに接続された差動出力ステージを備えることができる。差動出力ステージは、増幅電圧信号を受信し、第1出力と第2出力を提供する。一実施形態では、検出器は、線形位置検出器を備える。

【0014】

別の態様は、プリアンプ回路を備える検出電子機器である。プリアンプ回路は、検出器上の第1位置から電流信号を受信し、出力で第1電圧信号を生成するように接続された第1トランスインピーダンス・アンプを有する。更にプリアンプ回路は、検出器上の第2位置から電流信号を受信し、出力で第2電圧信号を生成するように接続された第2トランスインピーダンス・アンプを有する。第2増幅ステージは、第1トランスインピーダンス・アンプの出力と、第2トランスインピーダンス・アンプの出力とに接続された入力を具備できる。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を与える。差動出力ステージは、第2増幅ステージに接続できる。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を受信し、第1増幅電圧信号と第2増幅電圧信号の各々から一対の出力を提供する。読取回路類は、一対の出力の両方を受信するように接続された入力を有する。読取回路類は、一対の出力の各々を処理する処理構造を有する。処理構造は、結果として生じる単一のタイムスタンプがなされたデジタル出力を提供する。

【0015】

処理構造は、一対の出力を、単一の出力(AとB)に変換する差動アンプのシリアル接続と;単一の出力を合計出力に合計する合計ステージと;集積回路類と;A/D変換器とを備えることができる。合計ステージは、単一の出力の信号レベルの平衡を保つ、プログラム可能なゲイン平衡回路類を備えることができる。検出電子機器は更に、合計ステージと集積回路類とにそれぞれ接続された弁別子回路類を備えることができる。弁別子回路類は、合計出力を受信する信号検出チャネルと、合計出力の負(反転)を受信する雑音検出チャネルとを有する。信号検出チャネル上の論理「1」の検出は、集積回路類の計時を開始させる。信号検出チャネルと雑音検出チャネルはそれぞれ、比較器を備えることができる。

【0016】

本発明は、放射線検出器、プリアンプを含む検出電子機器、および関連する放射線検出システムによって与えられる信号を処理するプリアンプ回路に向けられている。本発明の一態様では、プリアンプ回路は、低電流を出力する線形位置検出器のような検出器から電流信号を受信し、その出力で電圧信号を生成するように接続されたトランスインピーダンス・アンプを備える。第2増幅ステージは、電圧信号を増幅するトランスインピーダンス・アンプの出力に接続された入力を有する。有意には、従来の最先端技術のプリアンプ回路類とは異なり、第1ステージのトランスインピーダンス・アンプは、検出された電荷を積分しない。第2増幅ステージは、パルス整形を提供しない。

【0017】

第2増幅ステージは、主として第2オペアンプを備える。好ましくは、第2オペアンプの反転入力には、電圧オフセットまたは電流オフセットを補償するオフセット補償構造が接続される。たとえば電圧または電流のオフセット補償構造は、一端が接地された分圧器を駆動する外部電圧源を備えることができる。分圧器の中心タップは、第2オペアンプの非反転入力に直接接続される。補償回路類は更に、プログラム可能なDAコンバータ(デジタルアナログ変換器)を備えることができ、それはオフセットの動的補償を可能にする。そのような回路は、周囲温度が大きく変化する用途において、特に有用であろう。

【0018】

一または複数の追加のステージが、第2プリアンプ・ステージに続くことができる。一実施形態では、第3すなわち最終の差動出力ステージは、ツイストペア線上の増幅信号を駆動する。ツイストペア線上の信号は、良い共通モードの雑音除去を提供するものとして知られている。

【0019】

一実施形態では、検出器は、線形位置ガス検出器である。放射線は、中性子を含む。本

発明に係る検出電子機器を備えた複数の検出器は、広角チョッパ分光計システムに一体化される。しかしながら、当業者には容易に明白であるように、本発明は、ピコアンペアまたはフェムトアンペア範囲の電流のような小さな電荷または小さな電流を出力するか、あるいは低インピーダンスの電圧源である任意の検出器システムに、容易に適合できる。従って、主として広角チョッパ分光計システムに関して記述されたが、本発明は、他の放射線検出システムを支援でき、中性子に関する以外に放射線に対して利用できる。たとえば本発明は、シンチレータに基づく用途での光電管と、共に使用されるように修正できる。シンチレータの修正によって、X線のように異なる種類の放射線を検出できる。

【0020】

好ましい実施形態では、検出器は、図1に示すような広角チョッパ分光計100容器内の真空に設置される。これは、典型的には0気圧〜1気圧の間の多サイクルの圧力差に耐えなければならない薄いアルミニウム製の窓の必要性を排除し、それはさもなければ、真空室に記憶された凄まじい機械的エネルギのために、問題を引き起こす場合がある。検出器および窓の取付部からの容器の構造上の一体性の分離は、検出器が角度的に略連続することがあることも意味する。これは、単結晶分光法における一番の問題である。

【0021】

本発明ならびにその特徴と利点についての更に十分な理解は、添付図面と共に次の詳細な記述の閲覧の際に得られるであろう。

【図面の簡単な説明】

【0022】

【図1】広角チョッパ分光計の模式図(検出器は真空容器内に示され、その構成は、望ましいが従来の構成ではない)。

【図2】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2A】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2B】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2C】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図3】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3A】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3B】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3C】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3D】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3E】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図4】本発明の実施形態に係る、関連する通信リンクを概観する検出電子機器の模式概観図。

【図5】本発明の実施形態に係る、フロントエンド回路のブロック図であり、それは、プリアンプ回路類から受信した差動信号を単一端の電圧信号に変換する差動アンプを利用する。

【図6】本発明の実施形態に係る、フロントエンド電子機器の模式図であり、それは、プリアンプから受信した差動信号を単一端の電圧信号に変換する。

【図7】本発明の実施形態に係る、ゲイン平衡/加算回路の模式図。

【図8】本発明の実施形態に係る、差動弁別子ステージの模式図。

【図9】本発明の実施形態に係る、積分回路の模式図であり、異なるチャネルAとB用の別個の同一積分ステージがある。

【図10】本発明の実施形態に係る、アナログデジタル変換ステージの模式図。

【図11】本発明の実施形態に係る、データ取得システムのレイアウトのブロック図であり、この図は、ブロックのうちの1つとしての検出電子機器の配置を示す。

【図12】本発明の実施形態に係る、読出カードについての高レベルの模式図。

【図13】本発明の実施形態に係る、読出カード(ROC)のアナログ部のうちの1つのチャネルのブロック図。

【図14】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図15】本発明の実施形態に係る、読出カード制御器の模式概観図。

【図16】本発明の実施形態に係る、読出カードチャネルのデジタル構造についての模式図。

【図17】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図18】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図19】本発明の実施形態に係る、信号の送信方式の模式説明図。

【図20】本発明の実施形態に係る、信号インタフェースの模式図。

【図21】本発明の実施形態に係る、計時と制御信号の模式説明図。

【発明を実施するための形態】

【0023】

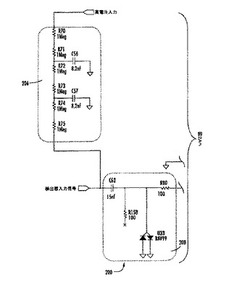

本発明の非限定の実施形態は、併せて見られる図2と図2A〜図2Cで模式的に示されたプリアンプ回路200である。注記しない限り、構成要素の選択(MOSに対向するようなバイポーラ技術のような)および特定の値は、単に典型的なものであり、限定するものではない。特に図2に示すSIGINは、検出器(図示略)からの信号としての検出器入力信号である。

【0024】

図示のように、フロントエンド・アンプ210は、バイポーラ・オペアンプである。入力信号は、抵抗器R80を介して、検出器から受信され、フロントエンド・アンプ210の入力(ピン2)を反転させ、それは、フィードバック抵抗器R82とコンデンサC65と共に、フィードバック抵抗器R82が約100KΩ未満である限り高速であるトランスインピーダンス・アンプを生成する。検出器用の従来のプリアンプとは異なり、フィードバック抵抗器R82が典型的にずっと大きい(>1メガΩ)である場合、この第1増幅ステージは、入力電荷/電流を積分しない。代わりに、このステージの出力は、ピン2での入力電流に比例した電圧である(つまり、Vout(t)=cIin(t)であり、ここでは、cが定数である)。このように、フロントエンド・アンプ210とその関連する構成要素は、トランスインピーダンス機能を実施する。しかしながら、合計コンデンサ・インピーダンス(寄生か故意かに拘わらず)がフィードバック・ループを支配する場合、フロントエンド・アンプ210は、トランスインピーダンス・アンプとして機能しない。特定の周波数とこれが生じる抵抗の特定の値は、主としてオペアンプ選択と検出器の出力インピーダンスに依存する。

【0025】

フロントエンド・アンプ210によって提供される第1ステージからの出力は、抵抗器R79を介して、第2増幅ステージに直流接続される。抵抗器R83と共にこの抵抗器は、第2増幅ステージの直流電圧ゲインを判断する。コンデンサC63は、第2オペアンプ230の安定化のために使用される。抵抗器R76,R81と基準電圧DACInputは、第2と第1ステージの電圧と電流のオフセットを補償する構成を提供し、その結果、第2増幅ステージからの信号出力は、0Vに近づく。第2増幅ステージからの出力電圧を「トリミングする」方法は、抵抗器R76の特定の値の修正(各チャネルで異なることがある)によって、または、基準電圧DACInputの修正によってなされることができる。これは、DACInputがDAコンバータ(デジタルアナログ変換器)から生成される場合、プログラムによってなされることができる。パルス整形は、例示された第2増

幅ステージでは行なわれない。上で注記したように、従来や本実施形態とは対照的に、このステージは、典型的にはガウス式のパルス整形フィルタである。

【0026】

第2増幅ステージに関して、第2増幅ステージの出力(第2オペアンプ230の出力)は、抵抗器R77を介して、差動最終出力ステージに接続される。最終ステージの目的は、ツイストペア線上の増幅信号を駆動することにある。そのような信号は、共通モードの雑音除去を提供するものとして知られている。抵抗器R77,R78,R84,R85,およびR86は、アンプ250に対するゲインと共通モードの出力電圧を設定する。Out−とOut+は、好ましくは適切なツイストペア・コネクタに接続される。好ましい実施形態では、これは、低コストのイーサネット(登録商標)配線の使用を可能にするRJ45コネクタになるであろう。

【0027】

入力と保護回路類に関して、コンデンサC62、抵抗器R80とR158、ならびにダイオードU33とU17は、入力と保護回路類(集合的に208)を構築する。C62は、大きな公称静電容量の高電圧コンデンサである。これは、検出器にバイアスを掛ける高電圧から低電圧電子機器を保護する。抵抗器R158,R80は、AC電流をトランスインピーダンス・ステージ・フロントエンド・アンプ210に接続する。これらの抵抗器は、フロントエンド・アンプ210の入力ステージへの保護の提供に加えて、更に、入力ステージの周波数依存入力抵抗を平坦にする新しい方法を提供する(従って、線形性と分解能の両方を向上させる)。これは、検出器の低い出力抵抗(一般に、約5,000Ω)のために重要である。ダイオードU33,U17は、入力電圧の変位を接地に固定する。抵抗器(R158,R80)とダイオードのU33,U17は、真空下で動作する場合に回路類を高電圧アークの閃光から保護する新しい保護方式を生成する(そのようなアークの閃光は、真空の予期しない消失を生じさせることがある)。

【0028】

抵抗器R70〜R75と高コンデンサC56,C57(集合的に206)は、検出器のための高電圧バイアス・ストリングを提供する。単一の抵抗器(従来の構成のように)ではなく、直列接続した抵抗器の使用は、抵抗の等価静電容量を低下させ、従って、更に良い雑音除去を提供する。

【0029】

図3と図3A〜図3Eは、併せて見て、本発明の実施形態に係る8個パック(チャネル)のプリアンプ回路300を模式的に示す。図示のように、図2に示す既に記述したプリアンプ回路類は、8回複製され、図中でプリアンプ回路類301〜308として表示され、それに接続された検出器入力信号(SIGIN)と、高電圧(HIGHVIN)と、オフセット・トリミングのためのD/A変換器入力(DACInput)と、第1出力OUT1と第2出力OUT2を有する(図2で示すように)。

【0030】

コネクタに関して、J12は、上述した高電圧フィルタ回路類206を提供する高電圧接続部である。J2,J4,J5,J6,J9,J10,J11,J13は、検出器出力を、検出器入力信号SIGINに接続するための接続部を提供する。J14は、取付シャシーに対する接地接続を提供する。好ましい実施形態では、これらは、プリアンプ回路基板上のバイアスである。

【0031】

J7とJ8は、プリアンプ部分からの出力信号用のコネクタである。一方、J3は、ローカルの基板温度と供給電圧の状態を読取ることを可能にするコネクタである。好ましい実施形態では、これらは、RJ45イーサネット(登録商標)コネクタである。J1は、パワー入力、2個の電圧、および接地である。好ましい実施形態では、その電圧は、公称で±4.0Vである。

【0032】

U5および関連するバイアス抵抗器R9とR10(集合的に311)は、プリアンプ基

板のローカル温度を読取る能力を提供する。L1,L2,C3,C4,C7,C8(集合的に312)は、入力パワー電圧の雑音フィルタリングを提供する。一方、U1,U2およびそれらに関連する受動素子(集合的に315)は、残りの電子機器への±3.3Vの規制された供給電圧用のシステムを備える。

【0033】

U3CとU3D、ならびに関連する抵抗分圧器R13,R15とR14,R18(集合的に318)は、供給電圧を監視する方法を提供する。オペアンプの出力は、入力電圧がU1とU2に規制できる値未満に低下する場合には常に、高電圧状態になる。

【0034】

U3A,U3B,およびU4は、それらに関連する受動素子と共に、プリアンプ中の直流補償に対する基準電圧を提供する。この電圧は、図2に示すDACInputと等価である。

【0035】

低電圧用のオペアンプと最低限の回路類の使用は、このシステムが真空内で動作することを可能にする。8つの検出器プリアンプ基板の各々は、好ましい実施形態では約1.5Wを使い、それは、真空で約5℃の温度上昇をもたらす。

【0036】

回路基板の実現として記述したが、本発明に係る、オペアンプのようなプリアンプ回路、基準電圧、および温度センサの能動部分は、単一チップ上に集積できる。

図4は、本発明の実施形態に係る検出電子機器の概観と関連する通信リンク400を示す。各バンクは、2つの8チャネル・プリアンプ・カードに接続する8本のチューブからなる(各チューブ端に対して1個)。各チューブ/検出器401に関連する第1プリアンプ・カード402と第2プリアンプ・カード403は、それぞれ、読出カード(ROC)405に接続される。読出カード405は、第1プリアンプ・カード402と第2プリアンプ・カード403からのパルスを処理し、デジタル化してそれにタイムスタンプを付与し、送信用のデータ・パケットを形成する。最大8個の読出カード405のグループは、単一のフロントエンドモジュール(FEM)415に接続される。フロントエンドモジュール415は、デジタル信号処理カード420からの計時と制御信号を分配し、読出カード405からデータを収集する。このように、フロントエンドモジュール415は、最大64本のチューブからデータを収集する。フロントエンドモジュールは、デジタル信号処理カード420にデータを再送信し、それは、次に、光ファイバ・リンク425を介して、それをプリプロセッサに送信する。

【0037】

図5は、好ましい読出カード500の実施形態のシステム・レベルのブロック図の記述を示す。個々のチャネル電子機器505の詳細は、更に下で説明される。好ましい実施形態では、信号処理電子機器は、制御フィールドプログラマブルゲートアレイ(FPGA)515と、8個のチャネルフィールドプログラマブルゲートアレイ520(各チャネルに対して1個)と、8個のチャネル電子機器(各チャネルに対して1個)505と、ハードウェア識別子チップ530と、温度センサ535と、様々な通信リンク(ボックス/リンク1〜5、集合的に540として示される)とを備える。

【0038】

制御フィールドプログラマブルゲートアレイ515は、操作可能に次の機能を提供する:

・内部通信バスを介して、チャネルフィールドプログラマブルゲートアレイ520間で情報調整する(本発明の他の実施形態では、チャネルフィールドプログラマブルゲートアレイ520と制御フィールドプログラマブルゲートアレイ515は、単一の更に大きな制御フィールドプログラマブルゲートアレイに組合せ可能である)。

【0039】

・ボックス3から受信した、様々な外部コマンドを扱う。

・外部リンク2を介して、データと状態を送信する。

・外部リンク1上で受信した様々な計時信号でデータ取得を同期する(なお、リンク1,2,3はRJ45コネクタを使用し、従って、低コストのイーサネット(登録商標)配線の使用を可能にする)。

【0040】

・リンク5と4上のSPIとRS232シリアル通信を扱う。

・ハードウェアIDチップを読取り、これを固有の通信アドレスとして使用する。

・温度センサ535を読取る(これは、真空内で動作する場合に、基板温度が操作仕様を超えるか否かを判断させるのに特に有用である)。

【0041】

・検出された中性子の位置の演算。

中性子がチャネル電子機器505によって検出される場合には常に、この情報は、制御フィールドプログラマブルゲートアレイ515に転送される。この時点で、制御フィールドプログラマブルゲートアレイ515は、中性子の位置を演算する。この演算からの結果は、タイムスタンプと共に、チャネルフィールドプログラマブルゲートアレイ520(更に特に下で記述する)によって伝えられ、その後、図5に示すLVDSリンク2上に出力される。

【0042】

チャネル電子機器505について記述する。中性子信号がどのようにチャネル電子機器によって検出されるかについての簡潔な記述から始める。一般に、中性子の位置を判断するために、2個の信号が提供されなければならない。本実施形態では、これらの信号は、図5に示すように、プリアンプ入力A端とプリアンプ入力B端としてラベル付けされる。これらは、線形位置感応チューブ(検出器)の各端から始まる増幅信号である。これらの信号は合計され、弁別子をトリガするために使用される電圧信号を与える。弁別子は、合計信号が所定大きさを超える場合には常に、トリガする(つまり、論理高電圧出力を出力する)。制御フィールドプログラマブルゲートアレイ515は、弁別子出力を監視し、そして、弁別子出力がトリガする場合には常に、チャネルフィールドプログラマブルゲートアレイ520は、プリアンプ・チャネルの各々(AとB)から中性子信号パルスの積分を開始する。

【0043】

これは、好ましくは遅延信号の積分によって達成される。この遅延信号は、遅延信号パルスの到達に先立って積分回路類に計時を開始させる(非遅延信号をトリガする)。パイプライン積分器の使用によって、積分の開始に先立って基準プリアンプ信号値を読取り、記憶できる。これは、動的基準修正技術の使用に際して重要である。加えて、合計信号の監視することによって、動的に積分時間を変更できる。これは、多岐に亘るパルス幅によって、中性子検出にとっては重要であり、積分時間をパルス幅に一致させることによって全体の信号対雑音比を改善する。チャネルフィールドプログラマブルゲートアレイ520は、基準ならびにチャネルAとB上の積分電圧の測定に加えて、中性子事象にタイムスタンプを付与する。タイムスタンプは、同期パルスと、中性子が実際に検出された場合との間の時間差として規定される。基準と積分値は、タイムスタンプと共に、位置演算を行なう制御フィールドプログラマブルゲートアレイ515に送られる。同期パルスとタイムスタンプ・クロックは、制御フィールドプログラマブルゲートアレイ515から各チャネルフィールドプログラマブルゲートアレイ520に送られる。

【0044】

図6は、プリアンプから受信した差動信号を単一端の電圧信号に変換するのを担う典型的なフロントエンド電子機器用の模式図である。各線形位置チューブの各々の側に対する2個の差動入力(AとBの両方に対してプラスとマイナス)があり(たとえば図4では、チューブ/検出器401に関連したプリアンプ402と403)、チャネルA(INPLUSAとINMIMUSA)ならびにチャネルB(INPLUSBとINMIMUSB)として表示される。抵抗器R2(A)とR52(B)は、プリアンプからの差動信号線を終わらせるのを担い、R1,3(A)とR51,55(B)は、必要ならば、信号のデシ

メーションに使用される。差動アンプ605と610は、差動信号(図2におけるOUT−とOUT+に対応する)を、残りの電子機器によって処理される単一端の電圧信号に変換する。差動アンプ605と610のオフセット出力は、プログラム可能なDAコンバータ(デジタルアナログ変換器。DAC)からの出力によって調整できる。プログラム可能なDAコンバータ(図6では図示略)は、これも図6では図示略のチャネルフィールドプログラマブルゲートアレイ520によってプログラムされる。差動アンプ605(ピン6)と差動アンプ610(ピン6)の出力は、ゲイン平衡/加算ステージに提供される(下で図7に関連して記述される)。差動アンプ605の出力もまた、チャネルA用の積分ステージに供給される。一方、差動アンプ610の出力は、チャネルB用の積分ステージに供給される。

【0045】

図7は、典型的なゲイン平衡/加算回路700を模式的に示す。抵抗器R654,R655,R657,R665,R666,およびR669は、プログラム可能なインピーダンスを提供するデジタル電位差計720と共に、R656とオペアンプ725を備えた加算回路に先立ってAとBチャネルのゲインの平衡を保つことを可能にする。デジタル電位差計720からの出力GAINADJAとGAINADJBは、図7に示すようにオペアンプ725に接続される。平衡後、各チャネル(AとB)は、弁別子(図8に関して記述する)をトリガさせる等しい確率を有し、従って、線形位置チューブ/検出器の各端での中性子捕獲と検出の確率の平衡を保つ。このゲイン調整は、図7に示すデジタル電位差計を使用して接地するために0Ωと、典型的には100kΩとの間のデジタル電位差計720の抵抗を変更することによってなされる。当業者は、アンプ725とその関連する抵抗器が加算回路を備えることを認識するであろう。アンプ725(ピン6)からの合計出力は、弁別子ステージ800に出力される。

【0046】

図8は、本発明で使用可能である典型的な弁別子ステージ800の模式図である。弁別子ステージ800は、2個の高速比較器、すなわち中性子信号検出比較器810と、雑音検出比較器815とを備える。中性子信号検出比較器810の回路類は、更に特に下で記述される。なお、弁別子ステージ800からの出力が雑音検出比較器815に入力される前にまず反転される以外は、同一の回路類が雑音検出器として使用できる。抵抗器R664,R670は、中性子信号検出比較器810に対する入力信号のレベルシフトを提供する。D42は、入力を電源レールに固定し、比較器に電圧保護を提供する。R661,R662および第1閾値信号(threshold1)として表示された基準電圧は、U215に対してヒステリシスと共に基準電圧を提供する。

【0047】

中性子信号検出比較器810と雑音検出比較器815の作用は、中性子が検出される場合には常に、制御フィールドプログラマブルゲートアレイ論理(図8では図示略。図4と図5を参照)によって論理「1」と考慮される電圧を生成することである。雑音が伴う場合のように、検出された中性子から反対の極性の信号が受信される場合には常に、雑音検出比較器815は、論理「1」を出力する。中性子信号検出比較器810上の論理「1」の検出は、図9に関して下で記述する積分回路の計時を開始させる。それは、更に、チャネルフィールドプログラマブルゲートアレイ520に、検出された中性子の飛行時間を判断するために使用できるタイムスタンプ・カウンタの値を記憶させる。チャネルフィールドプログラマブルゲートアレイ520による雑音検出比較器815からの論理「1」の検出は、信号を拒絶させる。この拒絶構造は、様々な種類の雑音が中性子信号検出比較器810にも不当にトリガさせるので、重要である。第1閾値信号threshold1と第3閾値信号threshold3は、好ましくは、プログラム可能なデジタル・アナログ変換器(DAC)からの出力によって設定される。

【0048】

図9は、本発明に係る典型的な積分回路900の模式図である。チャネルAとBに対する別個の同一積分ステージがある。チャネルA用の積分回路だけが、図9に関連して記述

される。図6の入力ステージからの出力は、遅延線915に入力される。この遅延線915は、スイッチ920に作用するためにデジタル回路類に与える入力信号を、チャネルフィールドプログラマブルゲートアレイ時間遅延させる。プリアンプからの信号が有効な中性子であると、制御フィールドプログラマブルゲートアレイが判断した場合(弁別子からの出力に基づく。特に、中性子信号検出比較器810が高)、それは、プログラム可能な設定に基づき一度に入力信号の積分を開始させる。遅延線からの出力は、オペアンプ925と、スイッチ920と、コンデンサC854と、抵抗器R642,644および645とを備えた積分回路に入力される。抵抗器R648は、正しい線インピーダンスを持った遅延を終わらせる。一方、R644,645およびC854は、積分器のゲインを判断する。弁別子回路類800からの信号のアサートに先立って、スイッチ920が閉じられ、従って、積分回路を統一ゲインモードに入れる(当業者は、R642,R644,645およびオペアンプ925が統一ゲインアンプであると容易に認識するであろう)。統一ゲインモードの場合、積分の開始に先立って基準電圧を判断できる。そのような基準判断は、相関サンプリングとしても知られている。チャネルフィールドプログラマブルゲートアレイ520におけるデジタル回路類が、信号が中性子であると判断した場合、スイッチ920は開かれ、積分器を形成する。プログラム可能な積分時間の後で、スイッチ920は、再び閉じられ、コンデンサC854から積分電荷を取り除く。この時点で、回路は、別の中性子パルスの準備ができる。積分ステージ900からの出力は、図10に関連して記述されるAD変換ステージ1000に入力される。

【0049】

図10は、本発明に係る典型的なAD変換ステージ(アナログデジタル変換ステージ)1000の模式図を示す。AD変換ステージ1000は、アナログデジタル変換器としてのADコンバータ(ADC)1005と、基準入力ADC_DACP1(ピン26へ)およびADC_DACN1(ピン18へ)と、抵抗器R643およびR646と、基準電圧ADC_OFFSET1とを備える。関連するコンデンサは、電源バイパス・コンデンサである。ADコンバータ1005の基準電圧は、ADC_DACP1とADC_DACN1の間のインピーダンスを変更することによって設定される。これは、プログラム可能な電位差計(図示略)のインピーダンスを変更することによってなされる。これは、ADコンバータ1005の動的なスケーリングを可能にする。基準ADC_OFFSET1と抵抗器R643,646は、積分ステージからの電圧オフセットを、図9に示されたスイッチ920からのスイッチング電流が積分器出力(INTOUTA)を接地よりも低下させないような値に設定可能にし、この時点では、ADコンバータ1005は、信号電圧を正確に記録しない。このオフセット電圧は、好ましくは、プログラム可能である。ADコンバータ1005は、パイプライン変換器であり、従って、ADコンバータクロック信号のすべての立上りで連続的な値を提供する。いずれの電圧値が記録されるかは、積分時間と共に、動的に変更でき、従って、ユーザに信号の信号対雑音値を改善可能にし、その帯域幅は、中性子の場合のように広い範囲で変化する。

【0050】

図4を再び参照して、それぞれの制御フィールドプログラマブルゲートアレイからのデータは、単一のフロントエンドモジュール(FEM)に接続される。フロントエンドモジュールは、デジタル信号処理カードからの計時と制御信号を分配し、読出カード405からのデータを収集する。フロントエンドモジュールは、そのデータをデジタル信号処理カードに再送信し、それは、次に、図示の光ファイバ・リンクを介して、プリプロセッサとしても知られている外部コンピュータにそれを送信する。

【0051】

図11は、破砕中性子源1100用の典型的なデータ取得システムのためのシステム・ブロックについての模式図であり、検出器1105、プリプロセッサ1110、制御コンピュータ1125、および解析コンピュータ1130と共に、そこへの発明の検出電子機器1110の配置を示す。上述したように、検出電子機器1110は、検出器1105からのアナログ信号の信号調整、信号のアナログデジタル変換、および各々の検出された中

性子に対する固有の位置とタイムスタンプの割当を担う。検出電子機器1110は、更に、中性子事象データをプリプロセッサ・メモリ(PRM)1115に送信するのに必要な電子機器を提供する。この送信は、好ましくは、双方向の高速データリンクによって達成される。

【0052】

高速データリンク(プリプロセッサ・メモリ1115と検出電子機器1110の間の両方向矢印によって表わされる)は、好しくは、光ファイバに基づくデータリンクである。検出された中性子事象を表わすデータ・バイトは、検出電子機器1110でフォーマットされ、連続化され、データ・フレームにおける光学リンクを介して、送られる。データリンクは、更に、データがプリプロセッサ・メモリ1115から検出電子機器1110に送られるように提供される。

【0053】

プリプロセッサ・メモリ1115は、検出電子機器1110と制御コンピュータ1125の間のインタフェースとして作用する。プリプロセッサ・メモリ1115は、各機器に適切であると判断されるような生データまたは変形データの記憶を担う。データは、生事象情報からリアルタイムで変形できる。プリプロセッサ・メモリ1115におけるプリプロセッサ・メモリ記憶部は、この目的を達成するために必要なルックアップ・テーブルとプロセッサ速度を有する。プリプロセッサ・メモリ1115は、更に、制御コンピュータ1125と検出電子機器1110の間の通信リンクとして作用する。このリンクは、ルックアップ・テーブルのデータまたは弁別子設定のような適切な操作に必要な検出器電子情報に、制御コンピュータ1125がダウンロードすることを可能にする。

【0054】

プリプロセッサ・メモリ1115と制御コンピュータ1125の間の通信は、制御コンピュータ1125にリアルタイムで表示データおよび/またはヒストグラム・データを送信するのに十分な速度のデータリンクを通じて達成される。実験的なアイドル期間中に、プリプロセッサ・メモリ1115は、データの解析用の分散型コンピューティング・システムとして、解析コンピュータ1130と制御コンピュータ1125と共に使用可能である。「生」またはヒストグラム・データを解析コンピュータ1130に転送するために使用できる、プリプロセッサ・メモリ1115から解析コンピュータ1130への付加的なポイント間リンクがある。データ転送に対するこの2重の方法は、潜在的なデータ帯域幅を2倍にするだけではなく、それは、データがどのように表示され、ユーザに転送されるかについての柔軟性を持たせる。

【0055】

制御コンピュータ1125は、実験的タスクの制御とシーケンスを担う。それは、更に、チョッパ調整、サンプル温度、および他の機器の特定の変数のようなパラメータの監視を担う。それは、包括的な制御と他のサイト全体に亘る情報に関連した変数へのアクセスを機器に提供する。更に、制御コンピュータ1125は、好ましくは、サイト全体のイーサネット(登録商標)へのリンクを提供し、機器科学者の指導の下、実験的な遠隔の監視または制御に可能にする。

【0056】

上述したように、プリアンプ・モジュールは、8チャネルを備えることができ、各々は、He3チューブ用のHVバイアス・ネットワークと、トランスインピーダンス・プリアンプと、ゲインおよびフィルタリング・ステージと、差動出力バッファとからなる。更に、1個のプリアンプ・モジュールは、チューブのバンクの各端に対して使用でき、上述もしたように、チューブからのパルスは、増幅され、フィルタリングされ、読出カードに接続するケーブル内に駆動される。

【0057】

図12は、8本のチューブから信号を受信する読出カード1200についての高レベルの模式図を提供し、それは、8個の読出カードチャネル1202a,1202bによって処理される。読出カードチャネル1202a,1202bの各々は、アナログ部1204

とデジタル部1206から構成できる。読出カードは、フロントエンドモジュールを介して、デジタル信号処理カードから制御、計時、およびセットアップ信号を受信できる。代わりに、しかしながら、読出カード制御器は、デジタル信号処理機基板からの信号をエミュレートでき、従って、デジタル信号処理カードは、計時発生に対して必要ではない。読出カードは、フロントエンドモジュールを介して、デジタル信号処理カードにデータを送信する。

【0058】

図13は、読出カードのアナログ部1204の1個のチャネル1300を模式的に示すブロック図であり、プリアンプへの、およびデジタル部1206への接続を示す。先に記述したように、読出カードの各チャネルは、2個の差動受信器を有しており、1つは、チューブ(AとB)ならびに対応するプリアンプの2個の端の各々に対する。これらの2つの信号は、加算アンプ1302によって合計され、合計信号は、弁別子によって最初の範囲閾値と比較される。中性子検出の特定の状況では、パルスがこの閾値を超える場合、パルスが中性子によるもの(単なる雑音ではない)であると想定でき、パルス処理プロセスが開始される。弁別子がトリガした時刻は、事象タイムスタンプとして記録される。図14を更に参照して、この種の事象の例は、図示のタイミング図1400によって示される。合計信号もまた、積分されるかまたはローパス・フィルタリングされ、且つ、再び識別される(パルスOK弁別子)。この第2弁別子が第1弁別子の約200ナノ秒内にトリガした場合、パルスが中性子によると想定され、事象の処理を継続すべきである。第2弁別子がトリガしない場合、第1弁別子が雑音に対してトリガしたものと想定され、事象を拒絶し、処理すべきではない。

【0059】

2個の差動受信器もまた、それぞれ、長さ約400ナノ秒の遅延線を駆動する。加算アンプもまた、同様の遅延線1304を駆動する。遅延線の各々に続いて、ゲート積分器1306がある。遅延線の使用は、ゲート制御の遅延によって如何なる信号も失うことなく、パルス高弁別子が積分器のゲートをオンにすることを可能にする。タイミング図で見られるように、デジタル論理は、第1パルス弁別子からの時間を計り、約300ナノ秒後に積分器のリセット・スイッチを開く。この遅延および弁別子遅延は、遅延線の長さ未満であるべきであり、従って、パルスは、完全に積分される。パルスOK弁別子出力が300ナノ秒の遅延中に真にならない場合、積分器はリセットされ、システムは別のパルスを待つ。真になった場合、積分器は、それらがそれらのADコンバータ1005によってサンプリングされるまでリセットされない。

【0060】

十分な積分時間の後で(これは、プリアンプからのパルスの形状に依存する)、積分器は、複数のADコンバータ1005によって同時にサンプリングされる。これは、1マイクロ秒の積分時間の場合の変換開始信号によってタイミング図に示される。その変換には、典型的には約0.5マイクロ秒掛かり、変換器が終えた場合に、それは変換終了(EOC)信号を生成する。この信号は、論理に積分器をリセットさせ、読出カードは、別のパルスを処理する準備ができる。パルス検出とEOCの間で掛かる時間は、この構成に対して約2マイクロ秒である。

【0061】

ADコンバータ1005は、たとえば内蔵トラックを備えた10ビットのユニットであることができ、アンプを保持できる。この構成は、複数のサンプルおよび保持回路、マルチプレクサ、および単一の更に高速なADコンバータ1005を必要とする、従来の構成よりも更にコンパクトで安価である。トラックと保持は、積分器がもっと早くリセットされることを可能にし(ADコンバータ1005開始の直後)、これは、第1パルスが依然としてデジタル化される間であっても、第2パルスを積分することを可能にすることによって、更に高いパルス処理速度を可能にできる。

【0062】

読出カードのデジタル部1206は、読出カード制御器1500と読出カードチャネル

1202a,1202bの2つのレベルの制御を備える。読出カード制御器1500と各読出カードチャネル1202a,1202bの両方は、個々の状態と構成を有する。すべての読出カードチャネル1202a,1202bは、読出カード制御器1500からの或る計時制御と動作モード制御を除き独立してプログラム可能である。読出カード制御器1500、読出カードチャネル1202a,1202bのデジタル部1206、およびアナログ部1204からのパルスが有効になる方法が、これから更に記述される。

【0063】

図15は、読出カード制御器1500の模式概観図である。フロントエンドモジュール/デジタル信号処理機からのコマンド・パケットはすべて、コマンド・プリプロセッサ1502を通じてフィルタリングされる。コマンド・プリプロセッサは、コマンドFIFO(1024語x20ビット)にパケットを書込む前に、パケットのハードウェアIDアドレスのチェックを行なう。このプリプロセッサは、他の読出カードのためのコマンドを除去し、従って、フロントエンドモジュール/デジタル信号処理機は、すべての読出カードのコマンドFIFOをオーバーフローさせることなく多量のデータをブロードキャストできる。コマンド・インターラプタは、コマンドFIFOからの情報を解析し、ローカルのハードウェアIDに対するハードウェアIDを再確認する。読出カードのローカルの32ビットのハードウェアIDは、64ビットの通し番号から生成される。読出カード制御器1500は、コマンド・パケットをパリティとフォーマットのチェックを行なう。チェック処理中に、すべてのコマンドは、一時的なコマンド(CMDTMP)FIFO/RAMに配置される。コマンド・プロトコルの如何なる違反もホストにエラー・メッセージを生成し、コマンド・パケットは実行されない。読出カード制御器1500は、コマンドを実行できるか、または、読出カードチャネル1202a,1202bに情報を送信できる(20ビットのDIOバスを介して)。読出カード制御器1500は、読出カードコマンド・パケットに対する長さとコマンド文をチェックするだけである。同様に、読出カードチャネル1202a,1202bは、そのパケットに対する長さとコマンド文をチェックし、従って、読出カードチャネル1202a,1202bへの新しいコマンドは、読出カード制御器1500に修正を要求しない。読出カードチャネル1202a,1202bと制御器の両方は、コマンドが実行に成功した場合、ホストに肯定応答を送る。読出カード制御器1500は、読出カードチャネル1202a,1202bへ送られたパケットを了解しない。コマンド・パケットの最大長さは、255語である。

【0064】

この制御フィールドプログラマブルゲートアレイに関して、読出カード制御器1500によって使用されるすべてのパラメータは、構成RAMとシャドー・レジスタに記憶される。ローカル動作は、シャドー・レジスタを使用する。構成RAMにおけるパラメータの記憶は、効率的なデータの書込み確認を主とする。更に、周辺装置(高電圧カード、preamp1カード、preamp2カード)からのすべての応答は、構成RAMに記憶される。読出カード制御器1500は、すべての周辺装置からデータを同時に受信できる。しかしながら、読出カード制御器1500は、周辺装置にコマンドを1つずつだけ送ることができる。周辺装置の点では、読出カード制御器1500は、受動装置であり、それは情報を単に送受信する。

【0065】

読出カードチャネル1202a,1202bからのすべての情報は、チャネル・データFIFOに書込まれる。このデータは、2つの方法でポスト処理できる。第1に、ローカルのハードウェアIDは、コマンド応答に加えられることができる。第2に、ADコンバータ情報は、位置情報を演算するために使用される。読出カード制御器1500は、検出器1105における事象の位置を判断するために2つの独立した演算エンジンを有する。これらのエンジンは、並列動作し、位置に対する効率的な演算時間を減少させる。具体的には、エンジンは、演算を完了させるのに21クロック周期掛かるが、読出カードチャネル1202a,1202bからのデータは、12サイクル未満でロードできる。複数のエンジンが実行する間、データ転送時間は、演算処理におけるボトルネックになる。すべて

のポスト処理読出カード情報は、最終読出に対してFIFOに配置される。最終出力フォーマッタは、読出カード制御器1500からコマンド応答を生成し、処理されたチャネル情報を出力し、デジタル信号処理機によって使用されるパリティ情報を生成する。

【0066】

最後に、読出カード制御器1500は、チャネルが何をしているかを判断する読出カードチャネル1202a,1202bに或る制御信号を与える。DO_ACQ信号は、読出カードチャネル1202a,1202bがデータを取得できる期間を示す。これらの期間は、10MHzのクロック(TCLK)で増分される時間カウンタ(32ビット)に基づく。下側時間拒否と上側時間拒否パラメータ(32ビット)は、チャネルがいつデータを取得できるかを判断する。別のパラメータは、各読出カードチャネル1202a,1202bへのイネーブルを規定するチューブ・マスクである。読出カードチャネル1202a,1202bに対する他の制御は、読出カード制御器1500から独立する。

【0067】

図16は、読出カードチャネル1202a,1202bのデジタル構造1600を模式的に示す。読出カードチャネル1202a,1202bは、コマンドがその一時コマンドFIFOに書込まれる前に、コマンドのチャネル・アドレスをチェックし、有効にする。コマンドの長さが正しい場合、そのコマンドは、良いものとしてマークを付けられ、また、コマンドは、復号化され、実行される。肯定応答(失敗または成功)は、ホストに送り返される。読出カード制御器1500のように、構成データは、シャドー・レジスタと構成RAMに書込まれる。パルス事象をエミュレートするための偽データが、構成RAMに記憶される。

【0068】

A/D変換処理は、チューブ(A,B)の各端に対する10ビットの結果と合計を生成する。各チャネルで使用されるADコンバータ1005は、パイプライン化されており、従って、データ取得は、パルス検出後の7つのADコンバータクロック周期である。能動パルス検出は、INIT_DISC_POS信号の立上りで開始する。この時点で、チャネルは、2個のカウンタを開始させ、タイムスタンプをラッチする。1つのカウンタは、ADコンバータクロック速度のサンプル基準であり、他のカウンタは、固定された40MHzのパルス基準である。或る取得パラメータは、サンプル基準カウンタに基づく。一方、他のパラメータは、パルス基準カウンタに基づく。ADコンバータ1005のパイプライン化のために、サンプル基準は、0〜FFFの代わりにFFA〜FF9に及んでいる。各読出カードチャネル1202a,1202bでは、時間カウンタ(32ビット)は、10MHzのクロック(TCLK)で増分される。読出カードチャネル1202a,1202bにおける様々な時間カウンタは、TSYNCの立上りで同期される。

【0069】

パルス確認中に、取得処理は、非標準のADコンバータ FIFO構造に情報を書込む。このADコンバータ FIFOは、パルスが有効でない場合に書込まれたデータを廃棄できるので、非標準である。一旦パルスが有効になれば、ADコンバータ FIFOからのタイムスタンプとデータは、出力FIFOに、そして次に、出力キャッシュに移動される。すべてのデータ応答は、ユーザ定義可能な32ビットの位置インデックス(ポジション・スタンプ)を必要とする。従って、位置インデックスは、読出カードチャネル1202a,1202bがデータを取得する前に定義されなければならない。コマンド応答は、読出カード制御器1500内のハードウェアIDを使用する(ポスト処理が読出カードハードウェアIDを加える)。チャネルにおけるキャッシュは、読出カード制御器1500による高速データ・アクセス、および生成情報に対する大きなデータ記憶領域を可能にする。

【0070】

チャネルは、入力信号が有効であるか否かを判断するための様々なパラメータを有する。読出カードチャネル1202a,1202bは、本発明の実施形態によれば、有効パルス判断をするために3つの信号と3つの値を使用する:

・INIT_DISC_POS:初期弁別子が正。この信号は、良いパルス・シーケンスを開始させる。

【0071】

・MIN_DISC_POS:最小弁別子が正。この信号は、INIT_DISC_POS信号が有効であったことを示す。

・INIT_DISC_NEG:初期弁別子が負。この信号は、初期弁別子パルスがアナログ閾値未満に低下したことを示す。恐らくは、そのチャネルは、偽のトリガを得た。

【0072】

・ADC_A:SUMのA部分に対するADコンバータ出力。

・ADC_B:SUMのB部分に対するADコンバータ出力。

・ADC_S:AとBの積分SUMに対するADコンバータ出力。

【0073】

次のものは、パルスが有効であるか否かを判断する際になされた判断を概略する(それぞれ拒否と有効なパルス取得の計時詳細を示す図17と図18のタイミング図):

・有効なパルス時間窓:有効なパルス時間窓は、時間拒否が低と、時間拒否が高とによって定義される。時間拒否が低に先立ち、時間拒否が高の後に生じるすべてのパルスは無効であり、拒否されるものと考えられる。図9におけるパルス#1と#5は、時間拒否のために無視される。

【0074】

・負のパルス拒否:イネーブルにされた場合に、INIT_DISC_NEG信号は、潜在的に有効なパルスを拒否する。負の信号の立上りは、有効なパルスシーケンスを終了させ、信号の立下りの後の或る期間(負の初期弁別子タイムアウト)から将来の有効なパルスの検出を防止する。図9では、パルス#3と#4は、負のパルス・タイムアウト特徴のために拒否される。第2パラメータ(拒否禁止時間)は、初期弁別子の後でパルス拒否を可能にする時間の長さを判断する。この後では、パルスは、拒否できない。

【0075】

・最小弁別子チェック・ポイント:最小弁別子(MIN_DISC_POS)信号は、図10に示すような最小弁別子チェック・ポイントの前に生じなければならない。さもなければ、パルスは、最小弁別子チェック・ポイントに拒否される。最小弁別子(MIN_DISC_POS)信号は、図10に示すような最小弁別子チェック・ポイントの前に生じなければならない。さもなければ、パルスは拒否される。

【0076】

或るチェック・ポイント判断は、INIT_DISC_POS(立上り)が40MHzのクロックに対していつ生じたかに基づく。チャネルに対する他の計時パラメータは、サンプリング時間(サンプル1,2,3,4)と積分器リセット時間(INT_RST)のようなADコンバータ計時にリンクされたパルス基準タイマに基づく。ここでは、計時制約の定義上、幾つかの制限がある:

・Sample1時間<Sample2時間<Sample3時間<Sample4時間。

【0077】

・「最小弁別子チェック・ポイント」は「良いパルス・チェック・ポイント」に先立って生じなければならない。

データ及び計時と制御信号は、上述したように、低電圧差分信号リンク(LVDSリンク。LVDS:Low voltage differential signaling

)を介して、検出電子機器の様々なサブセクションに送信される。データは、データリンクを介して、送信され、ここで、データワードが連続化され、高速(240MHz超)低電圧差分信号リンクを通じて送信され、非連続化される。計時と制御信号は、低電圧差分信号ドライバと受信器を使用して送信される。使用されるチップ・セットは、様々なソースから得ることができるが、一般に、好しくは、ナショナル・セミコンダクター社の高速シリアルリンク用の部品番号DS90CR216,DS90CR215、ならびに、計時

と制御信号用のSN65LVDS32ADとSN65LVDS31NSと等価であるかまたは更に良い。

【0078】

高速送信データリンクの各々は、3つの低電圧差分信号対に連続化される21個の信号からなる。データ・クロックからなる第4低電圧差分信号もまた、データリンクの一部として送られる。受信端では、3個の低電圧差分信号データ信号が非連続化され、データ・クロックを使用して、元の21個のデータリンク信号に回復される。図19は、送信1900のこの特定の方式を示す。矢印の方向を反転させることによって、および、連続化器を非連続化器に置換することによって、受信側の等価図が容易に得られる。

【0079】

高速データリンクは、読出カード、フロントエンドモジュール、およびデジタル信号処理機基板の間でデータを送信するポイント間リンクである。次の信号は、高速データリンクに対して定義される(注:DVは、アクティブが低である):

・CLK(クロック):この信号は、21データ・ビットを連続化器にクロックさせるために使用される。

【0080】

・D0−D15:データワード。

・EPB(偶数パリティ・ビット):すべてのリンクが、偶数パリティを使用する(D20は、パリティ・チェックに対して考慮されない)。

【0081】

・FW(第1語):データワードがデータまたはコマンドのシーケンスの第1語であることを示す。

・LW(最終語)は、データワードがデータまたはコマンドのシーケンスの最終語であることを示す。

【0082】

・DV(データ有効・アクティブ低):アサートされた場合に(アクティブ低!)データワードが有効であることを示す。

・CMD(コマンド):アサートされた場合にデータワードがコマンドであることを示し、アサートされない場合にはデータワードがデータであることを示す(注:当業者には容易に理解されるように、データはリトル・エンディアンのフォーマットで送られる)。

【0083】

セットアップと時間保持は、ナショナル・セミコンダクター社のチップ・セットと互換性があるべきである。実際には、これは、DVがアサートされる場合には常に(既に注記したように、アクティブ低)、ナショナル・セミコンダクター社のチップを駆動するクロック立上りでデータのクロック・インとアウトすることによって容易に実施できる。図20は、典型的なインタフェースを模式的に示し、従って、データリンクは、第1語失敗モードで動作する2個のFIFO間の直接通信を可能にする。送信FIFOのORピンは、クロック信号の立上り後の数ナノ秒で低になる。その後、この信号と利用可能なデータは、次の立上りでCR215にラッチされる。受信端上で、D20が低になる場合には常に、そのデータは、回復されたクロック信号(RXCLK)のクロック立上りで第2FIFOにラッチされる。

【0084】

FIFOからFIFOへのデータ・フローは、低電圧差分信号高速リンクを介してのものである。制御信号は、読出カード基板上のタイムスタンプから使用される計時クロック(10MHz)、リセット信号(アクティブ低)、タイムスタンプ・カウンタをリセットする同期パルス、および送信イネーブル(アクティブ低)である。次のものは、図21に模式的に示された計時と制御信号に対する信号定義である:

RST*(リセット):フロントエンドモジュールと読出カード基板を既知の状態に設定するが、その構成要素の本構成は、リセットされることがある。リセット・パルスは、少なくとも25.6usecの長さが必要とされる。その信号は、アクティブ低である。

【0085】

TCLK(計時クロック):それは、グローバルな10MHzの計時クロックである。立上りの各々は、タイムスタンプ・カウンタを1だけ増分する。

TSYNC(計時クロック同期):タイムスタンプ・カウンタは、この信号の立上りで0にリセットされる。公称で、このパルスは、16.7ミリ秒毎に見られる(60Hz)。

【0086】

TXEN*(送信イネーブル):データ送信をイネーブルにする。この信号は、アクティブ低である。この信号は、更に高いレベルの構成要素がその情報を扱うことができない場合に、更に低いレベルの構成要素がデータを送信するのを防止する。

【0087】

図示のように、読出カード基板上に3つのRJ−45通信リンクがあり、これらは、データ・イン、データ・アウト、ならびに計時と制御インである。3つのリンクはすべて、特定の実施形態によれば、8個の接触シールドRJ−45ジャックを使用する。通信リンクに加えて、3つのRJ−11リンクがあり、2つはプリアンプ基板へ、そして、1つは高電圧基板へのものである。RJ−45ジャックは、当業者には容易に理解されるように、好しくは、Cat5eに互換性がある。図示の構成では、データ通信リンクに対するピン・アウトは、1=D0−、2=D0+、3=D1−、6=D1+、4=D2−、5=D2+、7=CLK−、8=CLK+である。計時と制御リンクに対するピン・アウトは、1=10MHz+、2=10MHz−、3=TSYNC+、4=RESET+、5=RESET−、6=TSYNC−である(ピン7と8は不確定であるが、既知の状態にされるべきである(たとえば7を接地へ、8をVccへ))。特にこの実施形態については、プリアンプ・リンクに対するピン・アウトは、1=試験パルス・トリガ、2=I2Cクロック、3=I2Cデータ、4=スペアである。高電圧基板リンクに対するピン・アウトは、この実施形態によれば、再び、1=リセット、2=I2Cクロック、3=I2Cデータ、4=スペアである。

【0088】

読出カード通信に関して、一実施形態によれば、すべてのコマンドは、ブロードキャスト・モードで発行され、約1Kの量のコマンド語は、入力コマンドFIFOがオーバーフローする前に、特定の読出カードによって受信できる。本システムにおける各20ビット語に対する一般的なフォーマットが表1に示される。

【0089】

【表1】

【0090】

すべての語は、パケットの一部として送られる。このシステムでのパケットはすべて、

第1と最終語インジケータを使用することによって変数長を定義する。各パケットは、開始と停止インジケータを有するか、または、パケットは処理されない。コマンド・ビットは、アップロード(デジタル信号処理機へ)とダウンロード(読出カードへ)で異なって使用される。ダウンロード・パケットでは、第1語だけがコマンドとして示す。コマンド・パケットにおけるすべての他の語は、データとしてマークを付けられる。アップロード・パケットでは、検出器からの測定値がデータとして示す。コマンドに対するすべての他の応答は、それらと通常のデータから区別するためにコマンドとしてマークを付けられる。更に、偶数パリティ・ビット・インジケータがある。残りの16ビットは、データまたはコマンドに使用される。すべての構造は、リトル・エンディアンのフォーマットで送られる。つまり、LSWが最初に送られる。本システムに対するコマンド・セットは、表2に定義される。

【0091】

【表2】

【0092】

【0093】

コマンド語の一部は、読出カード構造をプログラムするためのアドレス定義であることができる。他の構成要素の種類(フロントエンドモジュール、デジタル信号処理機)は、アドレス仕様を無視する。アップロード構成要素の定義は、特定の構成要素の種類に対して同一のアドレス・ビットを使用できる。表2では、アドレスはXXで示され、構成要素の種類の定義は、ZZで示される。

【0094】

表3は、読出カードの特定の要素にアクセスし、構成要素の種類ZZを定義するためのXXの値を指定する。WRITE構成コマンドについては、4ビットの変数Yは、ローカルとグローバルの制約で構成サブ定義を可能とするように定義される。WRITE_CNFGコマンド用のY定義上の制約は、表3に定義される。構成情報のこの区分は、構成要素における解析とコマンド・エラー論理を最小限にし、構成要素の更に汎用で、更に包括的なプログラミングを可能にするようになされた。

【0095】

【表3】

【0096】

【0097】

プログラミング処理を開始するために、本システムは、まず初期化される。初期化手順は、実施形態によれば、次の必要条件とオプションのステップを含む:

1. デジタル信号処理機は、DISCOVERコマンドを発行する。このコマンドは、デジタル信号処理機に本システムでの構成要素を知らしめる(必要条件)。

【0098】

2. デジタル信号処理機は、すべての読出カード基板に構成情報をダウンロードする。読出カードは、すべての構成情報が書込まれた場合に限り構成される(必要条件)。

3. 適切なダウンロードを確実にするために各構成要素の構成を読込む(オプション)。

【0099】

4. 各構成要素の状態を読込む(オプション)。

5. 周辺装置(高電圧モジュール、preamp1とpreamp2基番)に情報を書込む(オプション)。

【0100】

6. 周辺装置の状態をチェックする(オプション)。

7. データ取得を開始するためにSTARTコマンドを発行する。ステップ2が読出カードチャネル1202a,1202bに対して行われなければ、取得処理は読出カードで止められる。ERROR応答は、構成されていない各イネーブル・チャネルによってデジタル信号処理機に送られる。

【0101】

次の段落は、本発明の実施形態に係る、典型的なコマンド・セットについて記述する。なお、或るコマンドは、この実施形態によれば、HID(ハードウェアID)なしで送られる。或る単一語のグローバル・コマンドもまた、ハードウェアIDを必要としない。

【0102】

[ACKNOWLEDGE<ハードウェアID>]

アップロード(デジタル信号処理機へ):コマンドが読出カードまたは読出カードチャネル1202a,1202bによって受信され、実行に成功したという本システムへの応答コマンド。ERRORコマンドは、エラーが発生し、コマンドが処理されない場合に生成される。

【0103】

【表4】

【0104】

[ERROR<ハードウェアID>]

アップロード(デジタル信号処理機へ):エラーが発生し、コマンドが処理されないという本システムへの応答コマンド。本システムは、読出カードまたは読出カードチャネル1202a,1202bの状態レジスタにおけるエラーをクリアするのを担う。ACKNOWLEDGEコマンドは、コマンド実行の成功の際に送られる。

【0105】

【表5】

【0106】

[DISCOVER]

この一般的なコマンドは、本システムの初期化処理を開始させる。特に、すべての読出カードに対して、本システムは、それらのハードウェアIDで応答する。そのコマンドは、下記のようなものである。

【0107】

【表6】

【0108】

読出カードに対する特定の応答は、下記のようなものである。

【0109】

【表7】

【0110】

[HV UPLOAD]

高電圧カードは、一実施形態によれば、RS232(9600ボー)インタフェースを使用して情報を本システムにアップロードする。各バイトは、個々に送られることができる。

【0111】

【表8】

【0112】

[HV DOWNLOAD]

最大128バイトのRS232(9600ボー)インタフェースを使用して高電圧基板にコマンドとデータを送る。

【0113】

【表9】

【0114】

[READ_STATUS<ハードウェアID>]

構成要素は、その状態を本システムにアップロードする。このコマンドを受信した後で、構成要素中の或るフラグがクリアされる(*)。各構成要素の状態は異なる。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、コマンド語の停止ビットが設定されなければならない。

【0115】

【表10】

【0116】

[読出カード状態]

【0117】

【表11】

【0118】

【0119】

【0120】

[読出カードチャネル状態]

【0121】

【表12】

【0122】

[READ_TEMPERATURES<ハードウェアID>]

読出カード基板は、その温度と2個のプリアンプ基板(AとB端)の温度を本システムにアップロードする。

【0123】

【表13】

【0124】

その応答は、下記のようなものである。

【0125】

【表14】

【0126】

温度値は、その出力を0.25℃で乗じることによって決定される。

[READ_VERSION<アドレス>]

構成要素は、そのバージョンを本システムにアップロードする。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、最初のコマンド語の停止ビットが設定されなければならない。

【0127】

【表15】

【0128】

殆どの構成要素については、応答は、基板とファームウェア情報を含む。

【0129】

【表16】

【0130】

しかしながら、制御器読出カードバージョン情報が基板情報を含むので、読出カードチャネル1202a,1202bは、ファームウェア仕様を必要とするだけである。読出カードチャネル応答は、次のようなものである。

【0131】

【表17】

【0132】

[RESET]

RESETコマンドは、すべての構成要素をそれらのデフォルト状態(パワー上昇)に戻す。具体的には、すべての制御フィールドプログラマブルゲートアレイは、それらのPROM情報を再びロードする。

【0133】

【表18】

【0134】

[START]

すべての適切なプロトコルが充足されたと想定してデータの取得を開始する。適切に構成されていない構成要素には、ERRORコマンドで応答する。STARTは、エラーを発生させずに複数回送られることができる。更に、STARTコマンドは、TSYNC選択ビットが読出カード制御器1500に設定される場合に、TSYNCを生成する。

【0135】

【表19】

【0136】

[停止]

データの取得を止める。

【0137】

【表20】

【0138】

[READ_CNFG]

構成要素は、その構成を本システムにアップロードする。各構成要素に対する応答は異

なる。本システムにおけるデータワードに対する十分な定義は、WRITE_CNFGコマンドに定義される。構成情報は返されて、Y=0から始まり、Y=15−で終わる。異なるサブ構成は、単一シーケンスに共にスタックされる。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、コマンド語の停止ビットは設定されなければならない。

【0139】

【表21】

【0140】

構成要素に書込まれる情報と、構成要素から返される情報との間の唯一の差は、COMMANDビットが、それを取得データから区別するために、返された情報で送られることである。たとえば読出カード構成READからの応答は、次のようなものである。

【0141】

【表22】

【0142】

[WRITE_CNFG]

構成要素の構成をダウンロードする。構成要素の構成はそれぞれ異なる。Yの定義は、情報量とその情報がどのくらいグローバルに一般的かに基づく。一般の規定では、構成0〜7は、特定の構成要素に特有である。一方、構成F〜8は、グローバルに定義可能である。一般的なコマンドは、下記のようなものである。

【0143】

【表23】

【0144】

このコマンドは、取得中に発行できないか、または、エラーが生成される。一旦取得が開始すれば、読出カードの構成は、変更できない。読出カード構成バッチ(Y=0)は、1つのコマンドでY=8、Y=14、およびY=15の構成情報を書込む。各種類のデータを、つまり、Y=8データ、Y=14データ、Y=15データの順に連鎖させる。

【0145】

[読出カード演算パラメータ(Y=8)]

これらのパラメータは、AとB入力に基づきパルスの位置の演算するために使用される変数を定義する。範囲値は、固定小数点12ビット値であり、オフセットは、固定小数点12ビット値である。これらのパラメータは、以下のように読出カード制御器1500における位置を演算するために使用される。オフセットは、偽のトリガ・モードで多くの読取結果の平均を取り、次に、その数値に64を乗じることによって決定され、最終値を整数として割当ている。従って、LSBは、=1/64のカウントである。範囲は、2048が1.0として定義され、従って、範囲=1/2048のLSBをなすことを注記することによって決定される。あるいは、範囲に0.0005の分解能を提供する。

【0146】

【表24】

【0147】

【0148】

【0149】

操作パラメータ(Y=14)

【0150】

【表25】

【0151】

【0152】

モード・パラメータ(Y=15)

【0153】

【表26】

【0154】

【0155】

読出カードチャネル構成(WRITE)Y=0は、Y=1、Y=8の順に連鎖させたすべてのチャネル情報を送る。

[固有の情報(Y=1)]

読出カードチャネル1202a,1202bの構成Y=1情報は、限定された定義によるものである。位置インデックスは、各チャネルに対して固有でなければならず、各チャネルに対するアナログ情報は、典型的には、様々な検出器とプリアンプに対して異なる。これらのパラメータは、チャネルがデータを取得する前に構成されなければならない。v変数は、電圧と抵抗の電位差計値を表わす。p変数は、固定位置値を表わす。x変数は、パリティを意味するか、または、条件に依存しない。

【0156】

【表27】

【0157】

【0158】

チャネルのアナログ部1204に対するデフォルト値が下に定義され、従って、チャネルのアナログ部1204は、一次に機能するべきである。

【0159】

【表28】

【0160】

[判断パラメータ(Y=8)]

読出カードチャネル1202a,1202b用の判断パラメータは、本システムに亘って包括的且つ一般的であるべきである。これらのパラメータの変化は、様々な検出器の種類または様々な読出カードアナログ電子機器においてのみ生じる。s変数は、ADコンバータサンプリング・レートに基づく。p変数は、40MHz(25ナノ秒周期)の読出カ

ード基板クロック基づく。x変数は、パリティを意味するか、または、条件に依存しない。

【0161】

【表29】

【0162】

【0163】

デフォルト・パラメータ値は、次のようなものである。

【0164】

【表30】

【0165】

[DATA_MODES]

構成要素の構成をダウンロードする。構成要素の構成は、それぞれ異なる。Yの定義は、情報量とその情報がどのくらいグローバルに一般的かに基づく。一般の規定では、構成0〜7は、特定の構成要素に特有なものである。

【0166】

[事象モード]

すべてのサンプリング情報は、位置を演算するために使用される(cで示す)。

【0167】

【表31】

【0168】

[詳細データ・モード]

詳細モードと名付けられたこのモードでは、チャネルは、情報を出力する前に、検出される入力信号を待つ。有効時間窓判断だけが、このモードで使用される。チャネル情報は、sample4時間に達するまで出力される。詳細パケットの長さは、ハードウェア限定を有し、それらは、イネーブルになったチャネルの数、パルスがどのくらいの頻度で生じているか、サンプリング・レート、およびサンプリング時間に依存する。詳細データ・パケットの長さは、任意の内部データFIFOがオーバーフローする場合に変わることがある。

【0169】

【表32】

【0170】

[生データ・モード]

生データ・モードとして示すこのモードでは、読出カードは、事象中に測定されたA/D変換値を出力する。

【0171】

【表33】

【0172】

[拡張生データ・モード]

別のモード、拡張生データ・モードでは、読出カードは、事象中に測定されたA/D変換値を出力する。加えて、位置についての制御フィールドプログラマブルゲートアレイ演算が報告される。

【0173】

【表34】

【0174】

[POSITON_CALCULATION]

位置演算は、以下のように行なわれる。AとBに対する生カウントが左に6つシフトされる。次に、AとBのオフセットは、その結果から減じられる。次に、各々のオフセット訂正値は、AとBの範囲で乗じられる。次に、(A−B)/(A+B)+1が演算され、ここでは、その区分は、少なくとも28ビットの分解能を維持される。結果として生じる数は、0〜2の間にある。この数は、高分解能モードの場合に128を乗じられ、さもなければ64を乗じられる。整数である際に統計的に正しいビンを生成するために、0.5に等しい適切な固定小数点がその数に加算される。次に、その数は、チューブの位置インデックスに加算される整数になり、これは、報告されるピクセルIDである。

【0175】

次の典型的なxmlリストは、32型の検出器に対する要求されたデフォルト構成ファイルを提供する。

【0176】

【表35】

【0177】

【0178】

本発明がその好ましい特定の実施形態に関連して記述されるが、先の記述とそれに続く例が本発明の範囲を例示し、且つ、それを限定しないように意図されることが理解されるべきである。本発明の範囲内の他の態様、利点、および修正は、本発明が関連する当業者には明白であろう。

【技術分野】

【0001】

本発明は、高速プリアンプ回路、ならびに関連する検出電子機器、および放射線検出システムに関する。

【背景技術】

【0002】

広角チョッパ分光計(ARCS)は、破砕中性子源(SNS)用に開発される中性子散乱機器である。広角チョッパ分光計は、サンプルでの高中性子束を提供し、大立体角検出器を提供する。

【0003】

破砕中性子源での中性子は、破砕処理によって生成され、高エネルギ陽子が目標物に衝突して短期間に多くのエネルギで大きな中性子束を生成する。破砕中性子源機器は、中性子のエネルギを判断するために飛行時間(TOF)測定を使用する。検出された中性子の飛行時間を判断するために、検出電子機器は、陽子が破砕目標物に当たる時間を示す計時マーカを必要とする。

【0004】

広角チョッパ分光計は、20mev〜2,000meVの入射エネルギ(Ei)を持った中性子を使用する、エネルギ( )中の適度な分解能と大きな運動量(Q)伝達範囲を持ったフェルミ・チョッパ分光計である。広角チョッパ分光計は、材料における力学的処理の科学を前進させるために使用できる。それは、従来の高エネルギ・チョッパ分光計よりも良い効率で、数meV〜数百meVのエネルギを有する材料と凝縮物質の励起を測定するように設計される。広角チョッパ分光計の用途は、(i)相関電子を持った材料を含む材料の振動励起、ならびにそれらの状態図と状態方程式の関係に関する研究と、(ii)磁石、超伝導体、および金属絶縁体転移に近い材料におけるスピン相関に関する研究とを含むが、これらに限定されるものではない。

【0005】

図1は、典型的な広角チョッパ分光計100の模式図である。目標物(図示略)の陽子衝撃によって生成された中性子は、分離された周囲水モデレータ101によって緩和される。その後、中性子は、サンプル室106に収容されたサンプル110に入射ビームラインを通じて伝播する。入射ビームラインに沿って中核容器インサートがあり、それは、シャッタから周囲水モデレータ101および中性子ガイドの近くへの中性子光学機器の配置を可能にする。

【0006】

広角チョッパ分光計100のビームラインは、周囲水モデレータ101と、T0チョッパ102と、フェルミ・チョッパ103とを具備した中性子ガイド105を備える。T0チョッパ102は、陽子が目標物に当たる場合に中性子を遮蔽するために周囲水モデレータ101から約8.5mに配置される。フェルミ・チョッパ103は、600Hzまでの速度で動作し、それは、Eiを規定する。検出器115は、サンプル110によって散乱された中性子を検出する。検出器115は、真空容器120内に配置されるように示される。

【0007】

サンプル110とその向こうのすべてのものが二次分光計を構成する。中性子は、真空のサンプル室(容器)120内のサンプル110で散乱し、10気圧(1.0MPa)の圧力でHe3を充填された複数の線形位置感応検出器(LPSD)115に移動する。中性子飛行時間は、散乱中性子の最終エネルギ(Ef)を判断するために、これらの検出器によって測定される。

【0008】

広角チョッパ分光計100は、20meV<Ei<2000meVの中性子で動作する

ように設計される。このエネルギ範囲の中性子を提供するように最適化された周囲水モデレータ101は、分離水モデレータである。その深さは、機器のエネルギ分解能に対して無視可能な貢献をする程度の狭い時間分布で殆どの束を提供するように最適化される。更に、この深さは、この周囲水モデレータの同一の面を見た場合の他の機器への性能劣化を最小限にする制約の下で最適化される。

【0009】

検出器115に関して、広角チョッパ分光計100は、線形位置感応検出器を利用するように設計される。広角チョッパ分光計100上の検出器アレイは、それぞれ25mm径の複数の線形位置感応検出器によって、約9001.0mの長さを備えるように設計される。それぞれ線形位置感応検出器は、10気圧(1.0MPa)の圧力でHe3を充填される。検出器115の長さは、電子機器によって長さ約15mmのピクセルに分割され、合計約60,000個の個々の検出器要素に分割される。各ピクセルは、約0.5°の角度範囲を定める。各ピクセルは、1マイクロ秒の計時分解能を有するべきであり、70,000n/s未満では飽和すべきではない。飽和後、チューブは、10マイクロ秒内の測定の準備ができる。検出器は、真空容器内の8個のモジュールにグループ化される。必要に応じて、それらは、操作とヒストグラム生成用のデータ取得ソフトウェアにデータを与える。

【0010】

線形位置感応検出器115に関連した検出電子機器(図1では図示略)は、広角チョッパ分光計100の重要な部分である。検出電子機器のフロントエンドには、プリアンプ回路類が備えられる。現在の最先端技術のプリアンプ設計は、大きなフィードバック抵抗器(典型的には、>1MΩ)を有する第1オペアンプを利用し、それは、検出器によって検出される入力電荷を積分するように操作可能である。第1オペアンプは、ガウス式のパルス整形フィルタに接続(結合)される。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】国際公開第2006/072848号

【発明の概要】

【発明が解決しようとする課題】

【0012】

広角チョッパ分光計100は、図1に示すように検出器と、関連する電子機器とを真空容器内に配置することによって単純化できる。しかしながら、検出電子機器を真空内に配置することは、主として多量のワット損による従来のプリアンプ回路類と互換性を持たない。加えて、そのような環境に有用な他の搭載支援回路類(たとえば温度センサ)は、一般的には使用されない。更に、特に、広角チョッパ分光計100のような用途に対して、100kHzよりもずっと速く動作する高速電子機器は、改良された高電圧保護回路類および雑音除去と同様に、必要とされる。

【課題を解決するための手段】

【0013】

本発明の一態様は、放射線検出器によって与えられる信号を処理するプリアンプ回路である。本発明の一態様によれば、プリアンプ回路は、検出器から電流信号を受信するトランスインピーダンス・アンプを備えることができる。トランスインピーダンス・アンプは、出力で増幅電圧信号を生成するように接続される。第2増幅ステージは、トランスインピーダンス・アンプの出力に接続された入力を具備できる。第2増幅ステージは、オペアンプを備えることができる。プリアンプ回路は、電圧オフセットまたは電流オフセットを補償するオフセット補償構造を有する。オペアンプの反転入力は、トランスインピーダンス・アンプの出力に接続される。オフセット補償構造は、第2オペアンプの非反転入力に接続される。オフセット補償構造は、分圧器を駆動する外部電圧源を備えることができる。分圧器の一端は、接地される。分圧器の中心タップは、第2オペアンプの非反転入力に

直接接続される。プリアンプ回路は更に、第2増幅ステージに接続された差動出力ステージを備えることができる。差動出力ステージは、増幅電圧信号を受信し、第1出力と第2出力を提供する。一実施形態では、検出器は、線形位置検出器を備える。

【0014】

別の態様は、プリアンプ回路を備える検出電子機器である。プリアンプ回路は、検出器上の第1位置から電流信号を受信し、出力で第1電圧信号を生成するように接続された第1トランスインピーダンス・アンプを有する。更にプリアンプ回路は、検出器上の第2位置から電流信号を受信し、出力で第2電圧信号を生成するように接続された第2トランスインピーダンス・アンプを有する。第2増幅ステージは、第1トランスインピーダンス・アンプの出力と、第2トランスインピーダンス・アンプの出力とに接続された入力を具備できる。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を与える。差動出力ステージは、第2増幅ステージに接続できる。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を受信し、第1増幅電圧信号と第2増幅電圧信号の各々から一対の出力を提供する。読取回路類は、一対の出力の両方を受信するように接続された入力を有する。読取回路類は、一対の出力の各々を処理する処理構造を有する。処理構造は、結果として生じる単一のタイムスタンプがなされたデジタル出力を提供する。

【0015】

処理構造は、一対の出力を、単一の出力(AとB)に変換する差動アンプのシリアル接続と;単一の出力を合計出力に合計する合計ステージと;集積回路類と;A/D変換器とを備えることができる。合計ステージは、単一の出力の信号レベルの平衡を保つ、プログラム可能なゲイン平衡回路類を備えることができる。検出電子機器は更に、合計ステージと集積回路類とにそれぞれ接続された弁別子回路類を備えることができる。弁別子回路類は、合計出力を受信する信号検出チャネルと、合計出力の負(反転)を受信する雑音検出チャネルとを有する。信号検出チャネル上の論理「1」の検出は、集積回路類の計時を開始させる。信号検出チャネルと雑音検出チャネルはそれぞれ、比較器を備えることができる。

【0016】

本発明は、放射線検出器、プリアンプを含む検出電子機器、および関連する放射線検出システムによって与えられる信号を処理するプリアンプ回路に向けられている。本発明の一態様では、プリアンプ回路は、低電流を出力する線形位置検出器のような検出器から電流信号を受信し、その出力で電圧信号を生成するように接続されたトランスインピーダンス・アンプを備える。第2増幅ステージは、電圧信号を増幅するトランスインピーダンス・アンプの出力に接続された入力を有する。有意には、従来の最先端技術のプリアンプ回路類とは異なり、第1ステージのトランスインピーダンス・アンプは、検出された電荷を積分しない。第2増幅ステージは、パルス整形を提供しない。

【0017】

第2増幅ステージは、主として第2オペアンプを備える。好ましくは、第2オペアンプの反転入力には、電圧オフセットまたは電流オフセットを補償するオフセット補償構造が接続される。たとえば電圧または電流のオフセット補償構造は、一端が接地された分圧器を駆動する外部電圧源を備えることができる。分圧器の中心タップは、第2オペアンプの非反転入力に直接接続される。補償回路類は更に、プログラム可能なDAコンバータ(デジタルアナログ変換器)を備えることができ、それはオフセットの動的補償を可能にする。そのような回路は、周囲温度が大きく変化する用途において、特に有用であろう。

【0018】

一または複数の追加のステージが、第2プリアンプ・ステージに続くことができる。一実施形態では、第3すなわち最終の差動出力ステージは、ツイストペア線上の増幅信号を駆動する。ツイストペア線上の信号は、良い共通モードの雑音除去を提供するものとして知られている。

【0019】

一実施形態では、検出器は、線形位置ガス検出器である。放射線は、中性子を含む。本

発明に係る検出電子機器を備えた複数の検出器は、広角チョッパ分光計システムに一体化される。しかしながら、当業者には容易に明白であるように、本発明は、ピコアンペアまたはフェムトアンペア範囲の電流のような小さな電荷または小さな電流を出力するか、あるいは低インピーダンスの電圧源である任意の検出器システムに、容易に適合できる。従って、主として広角チョッパ分光計システムに関して記述されたが、本発明は、他の放射線検出システムを支援でき、中性子に関する以外に放射線に対して利用できる。たとえば本発明は、シンチレータに基づく用途での光電管と、共に使用されるように修正できる。シンチレータの修正によって、X線のように異なる種類の放射線を検出できる。

【0020】

好ましい実施形態では、検出器は、図1に示すような広角チョッパ分光計100容器内の真空に設置される。これは、典型的には0気圧〜1気圧の間の多サイクルの圧力差に耐えなければならない薄いアルミニウム製の窓の必要性を排除し、それはさもなければ、真空室に記憶された凄まじい機械的エネルギのために、問題を引き起こす場合がある。検出器および窓の取付部からの容器の構造上の一体性の分離は、検出器が角度的に略連続することがあることも意味する。これは、単結晶分光法における一番の問題である。

【0021】

本発明ならびにその特徴と利点についての更に十分な理解は、添付図面と共に次の詳細な記述の閲覧の際に得られるであろう。

【図面の簡単な説明】

【0022】

【図1】広角チョッパ分光計の模式図(検出器は真空容器内に示され、その構成は、望ましいが従来の構成ではない)。

【図2】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2A】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2B】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図2C】本発明の実施形態に係る、プリアンプ回路類の模式図。

【図3】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3A】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3B】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3C】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3D】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図3E】本発明の実施形態に係る、支援回路類を伴った8個パックのプリアンプの実施形態の模式図。

【図4】本発明の実施形態に係る、関連する通信リンクを概観する検出電子機器の模式概観図。

【図5】本発明の実施形態に係る、フロントエンド回路のブロック図であり、それは、プリアンプ回路類から受信した差動信号を単一端の電圧信号に変換する差動アンプを利用する。

【図6】本発明の実施形態に係る、フロントエンド電子機器の模式図であり、それは、プリアンプから受信した差動信号を単一端の電圧信号に変換する。

【図7】本発明の実施形態に係る、ゲイン平衡/加算回路の模式図。

【図8】本発明の実施形態に係る、差動弁別子ステージの模式図。

【図9】本発明の実施形態に係る、積分回路の模式図であり、異なるチャネルAとB用の別個の同一積分ステージがある。

【図10】本発明の実施形態に係る、アナログデジタル変換ステージの模式図。

【図11】本発明の実施形態に係る、データ取得システムのレイアウトのブロック図であり、この図は、ブロックのうちの1つとしての検出電子機器の配置を示す。

【図12】本発明の実施形態に係る、読出カードについての高レベルの模式図。

【図13】本発明の実施形態に係る、読出カード(ROC)のアナログ部のうちの1つのチャネルのブロック図。

【図14】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図15】本発明の実施形態に係る、読出カード制御器の模式概観図。

【図16】本発明の実施形態に係る、読出カードチャネルのデジタル構造についての模式図。

【図17】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図18】本発明の実施形態に従って行なわれる信号処理タスクの実行に対応するタイミング図。

【図19】本発明の実施形態に係る、信号の送信方式の模式説明図。

【図20】本発明の実施形態に係る、信号インタフェースの模式図。

【図21】本発明の実施形態に係る、計時と制御信号の模式説明図。

【発明を実施するための形態】

【0023】

本発明の非限定の実施形態は、併せて見られる図2と図2A〜図2Cで模式的に示されたプリアンプ回路200である。注記しない限り、構成要素の選択(MOSに対向するようなバイポーラ技術のような)および特定の値は、単に典型的なものであり、限定するものではない。特に図2に示すSIGINは、検出器(図示略)からの信号としての検出器入力信号である。

【0024】

図示のように、フロントエンド・アンプ210は、バイポーラ・オペアンプである。入力信号は、抵抗器R80を介して、検出器から受信され、フロントエンド・アンプ210の入力(ピン2)を反転させ、それは、フィードバック抵抗器R82とコンデンサC65と共に、フィードバック抵抗器R82が約100KΩ未満である限り高速であるトランスインピーダンス・アンプを生成する。検出器用の従来のプリアンプとは異なり、フィードバック抵抗器R82が典型的にずっと大きい(>1メガΩ)である場合、この第1増幅ステージは、入力電荷/電流を積分しない。代わりに、このステージの出力は、ピン2での入力電流に比例した電圧である(つまり、Vout(t)=cIin(t)であり、ここでは、cが定数である)。このように、フロントエンド・アンプ210とその関連する構成要素は、トランスインピーダンス機能を実施する。しかしながら、合計コンデンサ・インピーダンス(寄生か故意かに拘わらず)がフィードバック・ループを支配する場合、フロントエンド・アンプ210は、トランスインピーダンス・アンプとして機能しない。特定の周波数とこれが生じる抵抗の特定の値は、主としてオペアンプ選択と検出器の出力インピーダンスに依存する。

【0025】

フロントエンド・アンプ210によって提供される第1ステージからの出力は、抵抗器R79を介して、第2増幅ステージに直流接続される。抵抗器R83と共にこの抵抗器は、第2増幅ステージの直流電圧ゲインを判断する。コンデンサC63は、第2オペアンプ230の安定化のために使用される。抵抗器R76,R81と基準電圧DACInputは、第2と第1ステージの電圧と電流のオフセットを補償する構成を提供し、その結果、第2増幅ステージからの信号出力は、0Vに近づく。第2増幅ステージからの出力電圧を「トリミングする」方法は、抵抗器R76の特定の値の修正(各チャネルで異なることがある)によって、または、基準電圧DACInputの修正によってなされることができる。これは、DACInputがDAコンバータ(デジタルアナログ変換器)から生成される場合、プログラムによってなされることができる。パルス整形は、例示された第2増

幅ステージでは行なわれない。上で注記したように、従来や本実施形態とは対照的に、このステージは、典型的にはガウス式のパルス整形フィルタである。

【0026】

第2増幅ステージに関して、第2増幅ステージの出力(第2オペアンプ230の出力)は、抵抗器R77を介して、差動最終出力ステージに接続される。最終ステージの目的は、ツイストペア線上の増幅信号を駆動することにある。そのような信号は、共通モードの雑音除去を提供するものとして知られている。抵抗器R77,R78,R84,R85,およびR86は、アンプ250に対するゲインと共通モードの出力電圧を設定する。Out−とOut+は、好ましくは適切なツイストペア・コネクタに接続される。好ましい実施形態では、これは、低コストのイーサネット(登録商標)配線の使用を可能にするRJ45コネクタになるであろう。

【0027】

入力と保護回路類に関して、コンデンサC62、抵抗器R80とR158、ならびにダイオードU33とU17は、入力と保護回路類(集合的に208)を構築する。C62は、大きな公称静電容量の高電圧コンデンサである。これは、検出器にバイアスを掛ける高電圧から低電圧電子機器を保護する。抵抗器R158,R80は、AC電流をトランスインピーダンス・ステージ・フロントエンド・アンプ210に接続する。これらの抵抗器は、フロントエンド・アンプ210の入力ステージへの保護の提供に加えて、更に、入力ステージの周波数依存入力抵抗を平坦にする新しい方法を提供する(従って、線形性と分解能の両方を向上させる)。これは、検出器の低い出力抵抗(一般に、約5,000Ω)のために重要である。ダイオードU33,U17は、入力電圧の変位を接地に固定する。抵抗器(R158,R80)とダイオードのU33,U17は、真空下で動作する場合に回路類を高電圧アークの閃光から保護する新しい保護方式を生成する(そのようなアークの閃光は、真空の予期しない消失を生じさせることがある)。

【0028】

抵抗器R70〜R75と高コンデンサC56,C57(集合的に206)は、検出器のための高電圧バイアス・ストリングを提供する。単一の抵抗器(従来の構成のように)ではなく、直列接続した抵抗器の使用は、抵抗の等価静電容量を低下させ、従って、更に良い雑音除去を提供する。

【0029】

図3と図3A〜図3Eは、併せて見て、本発明の実施形態に係る8個パック(チャネル)のプリアンプ回路300を模式的に示す。図示のように、図2に示す既に記述したプリアンプ回路類は、8回複製され、図中でプリアンプ回路類301〜308として表示され、それに接続された検出器入力信号(SIGIN)と、高電圧(HIGHVIN)と、オフセット・トリミングのためのD/A変換器入力(DACInput)と、第1出力OUT1と第2出力OUT2を有する(図2で示すように)。

【0030】

コネクタに関して、J12は、上述した高電圧フィルタ回路類206を提供する高電圧接続部である。J2,J4,J5,J6,J9,J10,J11,J13は、検出器出力を、検出器入力信号SIGINに接続するための接続部を提供する。J14は、取付シャシーに対する接地接続を提供する。好ましい実施形態では、これらは、プリアンプ回路基板上のバイアスである。

【0031】

J7とJ8は、プリアンプ部分からの出力信号用のコネクタである。一方、J3は、ローカルの基板温度と供給電圧の状態を読取ることを可能にするコネクタである。好ましい実施形態では、これらは、RJ45イーサネット(登録商標)コネクタである。J1は、パワー入力、2個の電圧、および接地である。好ましい実施形態では、その電圧は、公称で±4.0Vである。

【0032】

U5および関連するバイアス抵抗器R9とR10(集合的に311)は、プリアンプ基

板のローカル温度を読取る能力を提供する。L1,L2,C3,C4,C7,C8(集合的に312)は、入力パワー電圧の雑音フィルタリングを提供する。一方、U1,U2およびそれらに関連する受動素子(集合的に315)は、残りの電子機器への±3.3Vの規制された供給電圧用のシステムを備える。

【0033】

U3CとU3D、ならびに関連する抵抗分圧器R13,R15とR14,R18(集合的に318)は、供給電圧を監視する方法を提供する。オペアンプの出力は、入力電圧がU1とU2に規制できる値未満に低下する場合には常に、高電圧状態になる。

【0034】

U3A,U3B,およびU4は、それらに関連する受動素子と共に、プリアンプ中の直流補償に対する基準電圧を提供する。この電圧は、図2に示すDACInputと等価である。

【0035】

低電圧用のオペアンプと最低限の回路類の使用は、このシステムが真空内で動作することを可能にする。8つの検出器プリアンプ基板の各々は、好ましい実施形態では約1.5Wを使い、それは、真空で約5℃の温度上昇をもたらす。

【0036】

回路基板の実現として記述したが、本発明に係る、オペアンプのようなプリアンプ回路、基準電圧、および温度センサの能動部分は、単一チップ上に集積できる。

図4は、本発明の実施形態に係る検出電子機器の概観と関連する通信リンク400を示す。各バンクは、2つの8チャネル・プリアンプ・カードに接続する8本のチューブからなる(各チューブ端に対して1個)。各チューブ/検出器401に関連する第1プリアンプ・カード402と第2プリアンプ・カード403は、それぞれ、読出カード(ROC)405に接続される。読出カード405は、第1プリアンプ・カード402と第2プリアンプ・カード403からのパルスを処理し、デジタル化してそれにタイムスタンプを付与し、送信用のデータ・パケットを形成する。最大8個の読出カード405のグループは、単一のフロントエンドモジュール(FEM)415に接続される。フロントエンドモジュール415は、デジタル信号処理カード420からの計時と制御信号を分配し、読出カード405からデータを収集する。このように、フロントエンドモジュール415は、最大64本のチューブからデータを収集する。フロントエンドモジュールは、デジタル信号処理カード420にデータを再送信し、それは、次に、光ファイバ・リンク425を介して、それをプリプロセッサに送信する。

【0037】

図5は、好ましい読出カード500の実施形態のシステム・レベルのブロック図の記述を示す。個々のチャネル電子機器505の詳細は、更に下で説明される。好ましい実施形態では、信号処理電子機器は、制御フィールドプログラマブルゲートアレイ(FPGA)515と、8個のチャネルフィールドプログラマブルゲートアレイ520(各チャネルに対して1個)と、8個のチャネル電子機器(各チャネルに対して1個)505と、ハードウェア識別子チップ530と、温度センサ535と、様々な通信リンク(ボックス/リンク1〜5、集合的に540として示される)とを備える。

【0038】

制御フィールドプログラマブルゲートアレイ515は、操作可能に次の機能を提供する:

・内部通信バスを介して、チャネルフィールドプログラマブルゲートアレイ520間で情報調整する(本発明の他の実施形態では、チャネルフィールドプログラマブルゲートアレイ520と制御フィールドプログラマブルゲートアレイ515は、単一の更に大きな制御フィールドプログラマブルゲートアレイに組合せ可能である)。

【0039】

・ボックス3から受信した、様々な外部コマンドを扱う。

・外部リンク2を介して、データと状態を送信する。

・外部リンク1上で受信した様々な計時信号でデータ取得を同期する(なお、リンク1,2,3はRJ45コネクタを使用し、従って、低コストのイーサネット(登録商標)配線の使用を可能にする)。

【0040】

・リンク5と4上のSPIとRS232シリアル通信を扱う。

・ハードウェアIDチップを読取り、これを固有の通信アドレスとして使用する。

・温度センサ535を読取る(これは、真空内で動作する場合に、基板温度が操作仕様を超えるか否かを判断させるのに特に有用である)。

【0041】

・検出された中性子の位置の演算。

中性子がチャネル電子機器505によって検出される場合には常に、この情報は、制御フィールドプログラマブルゲートアレイ515に転送される。この時点で、制御フィールドプログラマブルゲートアレイ515は、中性子の位置を演算する。この演算からの結果は、タイムスタンプと共に、チャネルフィールドプログラマブルゲートアレイ520(更に特に下で記述する)によって伝えられ、その後、図5に示すLVDSリンク2上に出力される。

【0042】

チャネル電子機器505について記述する。中性子信号がどのようにチャネル電子機器によって検出されるかについての簡潔な記述から始める。一般に、中性子の位置を判断するために、2個の信号が提供されなければならない。本実施形態では、これらの信号は、図5に示すように、プリアンプ入力A端とプリアンプ入力B端としてラベル付けされる。これらは、線形位置感応チューブ(検出器)の各端から始まる増幅信号である。これらの信号は合計され、弁別子をトリガするために使用される電圧信号を与える。弁別子は、合計信号が所定大きさを超える場合には常に、トリガする(つまり、論理高電圧出力を出力する)。制御フィールドプログラマブルゲートアレイ515は、弁別子出力を監視し、そして、弁別子出力がトリガする場合には常に、チャネルフィールドプログラマブルゲートアレイ520は、プリアンプ・チャネルの各々(AとB)から中性子信号パルスの積分を開始する。

【0043】

これは、好ましくは遅延信号の積分によって達成される。この遅延信号は、遅延信号パルスの到達に先立って積分回路類に計時を開始させる(非遅延信号をトリガする)。パイプライン積分器の使用によって、積分の開始に先立って基準プリアンプ信号値を読取り、記憶できる。これは、動的基準修正技術の使用に際して重要である。加えて、合計信号の監視することによって、動的に積分時間を変更できる。これは、多岐に亘るパルス幅によって、中性子検出にとっては重要であり、積分時間をパルス幅に一致させることによって全体の信号対雑音比を改善する。チャネルフィールドプログラマブルゲートアレイ520は、基準ならびにチャネルAとB上の積分電圧の測定に加えて、中性子事象にタイムスタンプを付与する。タイムスタンプは、同期パルスと、中性子が実際に検出された場合との間の時間差として規定される。基準と積分値は、タイムスタンプと共に、位置演算を行なう制御フィールドプログラマブルゲートアレイ515に送られる。同期パルスとタイムスタンプ・クロックは、制御フィールドプログラマブルゲートアレイ515から各チャネルフィールドプログラマブルゲートアレイ520に送られる。

【0044】

図6は、プリアンプから受信した差動信号を単一端の電圧信号に変換するのを担う典型的なフロントエンド電子機器用の模式図である。各線形位置チューブの各々の側に対する2個の差動入力(AとBの両方に対してプラスとマイナス)があり(たとえば図4では、チューブ/検出器401に関連したプリアンプ402と403)、チャネルA(INPLUSAとINMIMUSA)ならびにチャネルB(INPLUSBとINMIMUSB)として表示される。抵抗器R2(A)とR52(B)は、プリアンプからの差動信号線を終わらせるのを担い、R1,3(A)とR51,55(B)は、必要ならば、信号のデシ

メーションに使用される。差動アンプ605と610は、差動信号(図2におけるOUT−とOUT+に対応する)を、残りの電子機器によって処理される単一端の電圧信号に変換する。差動アンプ605と610のオフセット出力は、プログラム可能なDAコンバータ(デジタルアナログ変換器。DAC)からの出力によって調整できる。プログラム可能なDAコンバータ(図6では図示略)は、これも図6では図示略のチャネルフィールドプログラマブルゲートアレイ520によってプログラムされる。差動アンプ605(ピン6)と差動アンプ610(ピン6)の出力は、ゲイン平衡/加算ステージに提供される(下で図7に関連して記述される)。差動アンプ605の出力もまた、チャネルA用の積分ステージに供給される。一方、差動アンプ610の出力は、チャネルB用の積分ステージに供給される。

【0045】

図7は、典型的なゲイン平衡/加算回路700を模式的に示す。抵抗器R654,R655,R657,R665,R666,およびR669は、プログラム可能なインピーダンスを提供するデジタル電位差計720と共に、R656とオペアンプ725を備えた加算回路に先立ってAとBチャネルのゲインの平衡を保つことを可能にする。デジタル電位差計720からの出力GAINADJAとGAINADJBは、図7に示すようにオペアンプ725に接続される。平衡後、各チャネル(AとB)は、弁別子(図8に関して記述する)をトリガさせる等しい確率を有し、従って、線形位置チューブ/検出器の各端での中性子捕獲と検出の確率の平衡を保つ。このゲイン調整は、図7に示すデジタル電位差計を使用して接地するために0Ωと、典型的には100kΩとの間のデジタル電位差計720の抵抗を変更することによってなされる。当業者は、アンプ725とその関連する抵抗器が加算回路を備えることを認識するであろう。アンプ725(ピン6)からの合計出力は、弁別子ステージ800に出力される。

【0046】

図8は、本発明で使用可能である典型的な弁別子ステージ800の模式図である。弁別子ステージ800は、2個の高速比較器、すなわち中性子信号検出比較器810と、雑音検出比較器815とを備える。中性子信号検出比較器810の回路類は、更に特に下で記述される。なお、弁別子ステージ800からの出力が雑音検出比較器815に入力される前にまず反転される以外は、同一の回路類が雑音検出器として使用できる。抵抗器R664,R670は、中性子信号検出比較器810に対する入力信号のレベルシフトを提供する。D42は、入力を電源レールに固定し、比較器に電圧保護を提供する。R661,R662および第1閾値信号(threshold1)として表示された基準電圧は、U215に対してヒステリシスと共に基準電圧を提供する。

【0047】

中性子信号検出比較器810と雑音検出比較器815の作用は、中性子が検出される場合には常に、制御フィールドプログラマブルゲートアレイ論理(図8では図示略。図4と図5を参照)によって論理「1」と考慮される電圧を生成することである。雑音が伴う場合のように、検出された中性子から反対の極性の信号が受信される場合には常に、雑音検出比較器815は、論理「1」を出力する。中性子信号検出比較器810上の論理「1」の検出は、図9に関して下で記述する積分回路の計時を開始させる。それは、更に、チャネルフィールドプログラマブルゲートアレイ520に、検出された中性子の飛行時間を判断するために使用できるタイムスタンプ・カウンタの値を記憶させる。チャネルフィールドプログラマブルゲートアレイ520による雑音検出比較器815からの論理「1」の検出は、信号を拒絶させる。この拒絶構造は、様々な種類の雑音が中性子信号検出比較器810にも不当にトリガさせるので、重要である。第1閾値信号threshold1と第3閾値信号threshold3は、好ましくは、プログラム可能なデジタル・アナログ変換器(DAC)からの出力によって設定される。

【0048】

図9は、本発明に係る典型的な積分回路900の模式図である。チャネルAとBに対する別個の同一積分ステージがある。チャネルA用の積分回路だけが、図9に関連して記述

される。図6の入力ステージからの出力は、遅延線915に入力される。この遅延線915は、スイッチ920に作用するためにデジタル回路類に与える入力信号を、チャネルフィールドプログラマブルゲートアレイ時間遅延させる。プリアンプからの信号が有効な中性子であると、制御フィールドプログラマブルゲートアレイが判断した場合(弁別子からの出力に基づく。特に、中性子信号検出比較器810が高)、それは、プログラム可能な設定に基づき一度に入力信号の積分を開始させる。遅延線からの出力は、オペアンプ925と、スイッチ920と、コンデンサC854と、抵抗器R642,644および645とを備えた積分回路に入力される。抵抗器R648は、正しい線インピーダンスを持った遅延を終わらせる。一方、R644,645およびC854は、積分器のゲインを判断する。弁別子回路類800からの信号のアサートに先立って、スイッチ920が閉じられ、従って、積分回路を統一ゲインモードに入れる(当業者は、R642,R644,645およびオペアンプ925が統一ゲインアンプであると容易に認識するであろう)。統一ゲインモードの場合、積分の開始に先立って基準電圧を判断できる。そのような基準判断は、相関サンプリングとしても知られている。チャネルフィールドプログラマブルゲートアレイ520におけるデジタル回路類が、信号が中性子であると判断した場合、スイッチ920は開かれ、積分器を形成する。プログラム可能な積分時間の後で、スイッチ920は、再び閉じられ、コンデンサC854から積分電荷を取り除く。この時点で、回路は、別の中性子パルスの準備ができる。積分ステージ900からの出力は、図10に関連して記述されるAD変換ステージ1000に入力される。

【0049】

図10は、本発明に係る典型的なAD変換ステージ(アナログデジタル変換ステージ)1000の模式図を示す。AD変換ステージ1000は、アナログデジタル変換器としてのADコンバータ(ADC)1005と、基準入力ADC_DACP1(ピン26へ)およびADC_DACN1(ピン18へ)と、抵抗器R643およびR646と、基準電圧ADC_OFFSET1とを備える。関連するコンデンサは、電源バイパス・コンデンサである。ADコンバータ1005の基準電圧は、ADC_DACP1とADC_DACN1の間のインピーダンスを変更することによって設定される。これは、プログラム可能な電位差計(図示略)のインピーダンスを変更することによってなされる。これは、ADコンバータ1005の動的なスケーリングを可能にする。基準ADC_OFFSET1と抵抗器R643,646は、積分ステージからの電圧オフセットを、図9に示されたスイッチ920からのスイッチング電流が積分器出力(INTOUTA)を接地よりも低下させないような値に設定可能にし、この時点では、ADコンバータ1005は、信号電圧を正確に記録しない。このオフセット電圧は、好ましくは、プログラム可能である。ADコンバータ1005は、パイプライン変換器であり、従って、ADコンバータクロック信号のすべての立上りで連続的な値を提供する。いずれの電圧値が記録されるかは、積分時間と共に、動的に変更でき、従って、ユーザに信号の信号対雑音値を改善可能にし、その帯域幅は、中性子の場合のように広い範囲で変化する。

【0050】

図4を再び参照して、それぞれの制御フィールドプログラマブルゲートアレイからのデータは、単一のフロントエンドモジュール(FEM)に接続される。フロントエンドモジュールは、デジタル信号処理カードからの計時と制御信号を分配し、読出カード405からのデータを収集する。フロントエンドモジュールは、そのデータをデジタル信号処理カードに再送信し、それは、次に、図示の光ファイバ・リンクを介して、プリプロセッサとしても知られている外部コンピュータにそれを送信する。

【0051】

図11は、破砕中性子源1100用の典型的なデータ取得システムのためのシステム・ブロックについての模式図であり、検出器1105、プリプロセッサ1110、制御コンピュータ1125、および解析コンピュータ1130と共に、そこへの発明の検出電子機器1110の配置を示す。上述したように、検出電子機器1110は、検出器1105からのアナログ信号の信号調整、信号のアナログデジタル変換、および各々の検出された中

性子に対する固有の位置とタイムスタンプの割当を担う。検出電子機器1110は、更に、中性子事象データをプリプロセッサ・メモリ(PRM)1115に送信するのに必要な電子機器を提供する。この送信は、好ましくは、双方向の高速データリンクによって達成される。

【0052】

高速データリンク(プリプロセッサ・メモリ1115と検出電子機器1110の間の両方向矢印によって表わされる)は、好しくは、光ファイバに基づくデータリンクである。検出された中性子事象を表わすデータ・バイトは、検出電子機器1110でフォーマットされ、連続化され、データ・フレームにおける光学リンクを介して、送られる。データリンクは、更に、データがプリプロセッサ・メモリ1115から検出電子機器1110に送られるように提供される。

【0053】

プリプロセッサ・メモリ1115は、検出電子機器1110と制御コンピュータ1125の間のインタフェースとして作用する。プリプロセッサ・メモリ1115は、各機器に適切であると判断されるような生データまたは変形データの記憶を担う。データは、生事象情報からリアルタイムで変形できる。プリプロセッサ・メモリ1115におけるプリプロセッサ・メモリ記憶部は、この目的を達成するために必要なルックアップ・テーブルとプロセッサ速度を有する。プリプロセッサ・メモリ1115は、更に、制御コンピュータ1125と検出電子機器1110の間の通信リンクとして作用する。このリンクは、ルックアップ・テーブルのデータまたは弁別子設定のような適切な操作に必要な検出器電子情報に、制御コンピュータ1125がダウンロードすることを可能にする。

【0054】

プリプロセッサ・メモリ1115と制御コンピュータ1125の間の通信は、制御コンピュータ1125にリアルタイムで表示データおよび/またはヒストグラム・データを送信するのに十分な速度のデータリンクを通じて達成される。実験的なアイドル期間中に、プリプロセッサ・メモリ1115は、データの解析用の分散型コンピューティング・システムとして、解析コンピュータ1130と制御コンピュータ1125と共に使用可能である。「生」またはヒストグラム・データを解析コンピュータ1130に転送するために使用できる、プリプロセッサ・メモリ1115から解析コンピュータ1130への付加的なポイント間リンクがある。データ転送に対するこの2重の方法は、潜在的なデータ帯域幅を2倍にするだけではなく、それは、データがどのように表示され、ユーザに転送されるかについての柔軟性を持たせる。

【0055】

制御コンピュータ1125は、実験的タスクの制御とシーケンスを担う。それは、更に、チョッパ調整、サンプル温度、および他の機器の特定の変数のようなパラメータの監視を担う。それは、包括的な制御と他のサイト全体に亘る情報に関連した変数へのアクセスを機器に提供する。更に、制御コンピュータ1125は、好ましくは、サイト全体のイーサネット(登録商標)へのリンクを提供し、機器科学者の指導の下、実験的な遠隔の監視または制御に可能にする。

【0056】

上述したように、プリアンプ・モジュールは、8チャネルを備えることができ、各々は、He3チューブ用のHVバイアス・ネットワークと、トランスインピーダンス・プリアンプと、ゲインおよびフィルタリング・ステージと、差動出力バッファとからなる。更に、1個のプリアンプ・モジュールは、チューブのバンクの各端に対して使用でき、上述もしたように、チューブからのパルスは、増幅され、フィルタリングされ、読出カードに接続するケーブル内に駆動される。

【0057】

図12は、8本のチューブから信号を受信する読出カード1200についての高レベルの模式図を提供し、それは、8個の読出カードチャネル1202a,1202bによって処理される。読出カードチャネル1202a,1202bの各々は、アナログ部1204

とデジタル部1206から構成できる。読出カードは、フロントエンドモジュールを介して、デジタル信号処理カードから制御、計時、およびセットアップ信号を受信できる。代わりに、しかしながら、読出カード制御器は、デジタル信号処理機基板からの信号をエミュレートでき、従って、デジタル信号処理カードは、計時発生に対して必要ではない。読出カードは、フロントエンドモジュールを介して、デジタル信号処理カードにデータを送信する。

【0058】

図13は、読出カードのアナログ部1204の1個のチャネル1300を模式的に示すブロック図であり、プリアンプへの、およびデジタル部1206への接続を示す。先に記述したように、読出カードの各チャネルは、2個の差動受信器を有しており、1つは、チューブ(AとB)ならびに対応するプリアンプの2個の端の各々に対する。これらの2つの信号は、加算アンプ1302によって合計され、合計信号は、弁別子によって最初の範囲閾値と比較される。中性子検出の特定の状況では、パルスがこの閾値を超える場合、パルスが中性子によるもの(単なる雑音ではない)であると想定でき、パルス処理プロセスが開始される。弁別子がトリガした時刻は、事象タイムスタンプとして記録される。図14を更に参照して、この種の事象の例は、図示のタイミング図1400によって示される。合計信号もまた、積分されるかまたはローパス・フィルタリングされ、且つ、再び識別される(パルスOK弁別子)。この第2弁別子が第1弁別子の約200ナノ秒内にトリガした場合、パルスが中性子によると想定され、事象の処理を継続すべきである。第2弁別子がトリガしない場合、第1弁別子が雑音に対してトリガしたものと想定され、事象を拒絶し、処理すべきではない。

【0059】

2個の差動受信器もまた、それぞれ、長さ約400ナノ秒の遅延線を駆動する。加算アンプもまた、同様の遅延線1304を駆動する。遅延線の各々に続いて、ゲート積分器1306がある。遅延線の使用は、ゲート制御の遅延によって如何なる信号も失うことなく、パルス高弁別子が積分器のゲートをオンにすることを可能にする。タイミング図で見られるように、デジタル論理は、第1パルス弁別子からの時間を計り、約300ナノ秒後に積分器のリセット・スイッチを開く。この遅延および弁別子遅延は、遅延線の長さ未満であるべきであり、従って、パルスは、完全に積分される。パルスOK弁別子出力が300ナノ秒の遅延中に真にならない場合、積分器はリセットされ、システムは別のパルスを待つ。真になった場合、積分器は、それらがそれらのADコンバータ1005によってサンプリングされるまでリセットされない。

【0060】

十分な積分時間の後で(これは、プリアンプからのパルスの形状に依存する)、積分器は、複数のADコンバータ1005によって同時にサンプリングされる。これは、1マイクロ秒の積分時間の場合の変換開始信号によってタイミング図に示される。その変換には、典型的には約0.5マイクロ秒掛かり、変換器が終えた場合に、それは変換終了(EOC)信号を生成する。この信号は、論理に積分器をリセットさせ、読出カードは、別のパルスを処理する準備ができる。パルス検出とEOCの間で掛かる時間は、この構成に対して約2マイクロ秒である。

【0061】

ADコンバータ1005は、たとえば内蔵トラックを備えた10ビットのユニットであることができ、アンプを保持できる。この構成は、複数のサンプルおよび保持回路、マルチプレクサ、および単一の更に高速なADコンバータ1005を必要とする、従来の構成よりも更にコンパクトで安価である。トラックと保持は、積分器がもっと早くリセットされることを可能にし(ADコンバータ1005開始の直後)、これは、第1パルスが依然としてデジタル化される間であっても、第2パルスを積分することを可能にすることによって、更に高いパルス処理速度を可能にできる。

【0062】

読出カードのデジタル部1206は、読出カード制御器1500と読出カードチャネル

1202a,1202bの2つのレベルの制御を備える。読出カード制御器1500と各読出カードチャネル1202a,1202bの両方は、個々の状態と構成を有する。すべての読出カードチャネル1202a,1202bは、読出カード制御器1500からの或る計時制御と動作モード制御を除き独立してプログラム可能である。読出カード制御器1500、読出カードチャネル1202a,1202bのデジタル部1206、およびアナログ部1204からのパルスが有効になる方法が、これから更に記述される。

【0063】

図15は、読出カード制御器1500の模式概観図である。フロントエンドモジュール/デジタル信号処理機からのコマンド・パケットはすべて、コマンド・プリプロセッサ1502を通じてフィルタリングされる。コマンド・プリプロセッサは、コマンドFIFO(1024語x20ビット)にパケットを書込む前に、パケットのハードウェアIDアドレスのチェックを行なう。このプリプロセッサは、他の読出カードのためのコマンドを除去し、従って、フロントエンドモジュール/デジタル信号処理機は、すべての読出カードのコマンドFIFOをオーバーフローさせることなく多量のデータをブロードキャストできる。コマンド・インターラプタは、コマンドFIFOからの情報を解析し、ローカルのハードウェアIDに対するハードウェアIDを再確認する。読出カードのローカルの32ビットのハードウェアIDは、64ビットの通し番号から生成される。読出カード制御器1500は、コマンド・パケットをパリティとフォーマットのチェックを行なう。チェック処理中に、すべてのコマンドは、一時的なコマンド(CMDTMP)FIFO/RAMに配置される。コマンド・プロトコルの如何なる違反もホストにエラー・メッセージを生成し、コマンド・パケットは実行されない。読出カード制御器1500は、コマンドを実行できるか、または、読出カードチャネル1202a,1202bに情報を送信できる(20ビットのDIOバスを介して)。読出カード制御器1500は、読出カードコマンド・パケットに対する長さとコマンド文をチェックするだけである。同様に、読出カードチャネル1202a,1202bは、そのパケットに対する長さとコマンド文をチェックし、従って、読出カードチャネル1202a,1202bへの新しいコマンドは、読出カード制御器1500に修正を要求しない。読出カードチャネル1202a,1202bと制御器の両方は、コマンドが実行に成功した場合、ホストに肯定応答を送る。読出カード制御器1500は、読出カードチャネル1202a,1202bへ送られたパケットを了解しない。コマンド・パケットの最大長さは、255語である。

【0064】

この制御フィールドプログラマブルゲートアレイに関して、読出カード制御器1500によって使用されるすべてのパラメータは、構成RAMとシャドー・レジスタに記憶される。ローカル動作は、シャドー・レジスタを使用する。構成RAMにおけるパラメータの記憶は、効率的なデータの書込み確認を主とする。更に、周辺装置(高電圧カード、preamp1カード、preamp2カード)からのすべての応答は、構成RAMに記憶される。読出カード制御器1500は、すべての周辺装置からデータを同時に受信できる。しかしながら、読出カード制御器1500は、周辺装置にコマンドを1つずつだけ送ることができる。周辺装置の点では、読出カード制御器1500は、受動装置であり、それは情報を単に送受信する。

【0065】

読出カードチャネル1202a,1202bからのすべての情報は、チャネル・データFIFOに書込まれる。このデータは、2つの方法でポスト処理できる。第1に、ローカルのハードウェアIDは、コマンド応答に加えられることができる。第2に、ADコンバータ情報は、位置情報を演算するために使用される。読出カード制御器1500は、検出器1105における事象の位置を判断するために2つの独立した演算エンジンを有する。これらのエンジンは、並列動作し、位置に対する効率的な演算時間を減少させる。具体的には、エンジンは、演算を完了させるのに21クロック周期掛かるが、読出カードチャネル1202a,1202bからのデータは、12サイクル未満でロードできる。複数のエンジンが実行する間、データ転送時間は、演算処理におけるボトルネックになる。すべて

のポスト処理読出カード情報は、最終読出に対してFIFOに配置される。最終出力フォーマッタは、読出カード制御器1500からコマンド応答を生成し、処理されたチャネル情報を出力し、デジタル信号処理機によって使用されるパリティ情報を生成する。

【0066】

最後に、読出カード制御器1500は、チャネルが何をしているかを判断する読出カードチャネル1202a,1202bに或る制御信号を与える。DO_ACQ信号は、読出カードチャネル1202a,1202bがデータを取得できる期間を示す。これらの期間は、10MHzのクロック(TCLK)で増分される時間カウンタ(32ビット)に基づく。下側時間拒否と上側時間拒否パラメータ(32ビット)は、チャネルがいつデータを取得できるかを判断する。別のパラメータは、各読出カードチャネル1202a,1202bへのイネーブルを規定するチューブ・マスクである。読出カードチャネル1202a,1202bに対する他の制御は、読出カード制御器1500から独立する。

【0067】

図16は、読出カードチャネル1202a,1202bのデジタル構造1600を模式的に示す。読出カードチャネル1202a,1202bは、コマンドがその一時コマンドFIFOに書込まれる前に、コマンドのチャネル・アドレスをチェックし、有効にする。コマンドの長さが正しい場合、そのコマンドは、良いものとしてマークを付けられ、また、コマンドは、復号化され、実行される。肯定応答(失敗または成功)は、ホストに送り返される。読出カード制御器1500のように、構成データは、シャドー・レジスタと構成RAMに書込まれる。パルス事象をエミュレートするための偽データが、構成RAMに記憶される。

【0068】

A/D変換処理は、チューブ(A,B)の各端に対する10ビットの結果と合計を生成する。各チャネルで使用されるADコンバータ1005は、パイプライン化されており、従って、データ取得は、パルス検出後の7つのADコンバータクロック周期である。能動パルス検出は、INIT_DISC_POS信号の立上りで開始する。この時点で、チャネルは、2個のカウンタを開始させ、タイムスタンプをラッチする。1つのカウンタは、ADコンバータクロック速度のサンプル基準であり、他のカウンタは、固定された40MHzのパルス基準である。或る取得パラメータは、サンプル基準カウンタに基づく。一方、他のパラメータは、パルス基準カウンタに基づく。ADコンバータ1005のパイプライン化のために、サンプル基準は、0〜FFFの代わりにFFA〜FF9に及んでいる。各読出カードチャネル1202a,1202bでは、時間カウンタ(32ビット)は、10MHzのクロック(TCLK)で増分される。読出カードチャネル1202a,1202bにおける様々な時間カウンタは、TSYNCの立上りで同期される。

【0069】

パルス確認中に、取得処理は、非標準のADコンバータ FIFO構造に情報を書込む。このADコンバータ FIFOは、パルスが有効でない場合に書込まれたデータを廃棄できるので、非標準である。一旦パルスが有効になれば、ADコンバータ FIFOからのタイムスタンプとデータは、出力FIFOに、そして次に、出力キャッシュに移動される。すべてのデータ応答は、ユーザ定義可能な32ビットの位置インデックス(ポジション・スタンプ)を必要とする。従って、位置インデックスは、読出カードチャネル1202a,1202bがデータを取得する前に定義されなければならない。コマンド応答は、読出カード制御器1500内のハードウェアIDを使用する(ポスト処理が読出カードハードウェアIDを加える)。チャネルにおけるキャッシュは、読出カード制御器1500による高速データ・アクセス、および生成情報に対する大きなデータ記憶領域を可能にする。

【0070】

チャネルは、入力信号が有効であるか否かを判断するための様々なパラメータを有する。読出カードチャネル1202a,1202bは、本発明の実施形態によれば、有効パルス判断をするために3つの信号と3つの値を使用する:

・INIT_DISC_POS:初期弁別子が正。この信号は、良いパルス・シーケンスを開始させる。

【0071】

・MIN_DISC_POS:最小弁別子が正。この信号は、INIT_DISC_POS信号が有効であったことを示す。

・INIT_DISC_NEG:初期弁別子が負。この信号は、初期弁別子パルスがアナログ閾値未満に低下したことを示す。恐らくは、そのチャネルは、偽のトリガを得た。

【0072】

・ADC_A:SUMのA部分に対するADコンバータ出力。

・ADC_B:SUMのB部分に対するADコンバータ出力。

・ADC_S:AとBの積分SUMに対するADコンバータ出力。

【0073】

次のものは、パルスが有効であるか否かを判断する際になされた判断を概略する(それぞれ拒否と有効なパルス取得の計時詳細を示す図17と図18のタイミング図):

・有効なパルス時間窓:有効なパルス時間窓は、時間拒否が低と、時間拒否が高とによって定義される。時間拒否が低に先立ち、時間拒否が高の後に生じるすべてのパルスは無効であり、拒否されるものと考えられる。図9におけるパルス#1と#5は、時間拒否のために無視される。

【0074】

・負のパルス拒否:イネーブルにされた場合に、INIT_DISC_NEG信号は、潜在的に有効なパルスを拒否する。負の信号の立上りは、有効なパルスシーケンスを終了させ、信号の立下りの後の或る期間(負の初期弁別子タイムアウト)から将来の有効なパルスの検出を防止する。図9では、パルス#3と#4は、負のパルス・タイムアウト特徴のために拒否される。第2パラメータ(拒否禁止時間)は、初期弁別子の後でパルス拒否を可能にする時間の長さを判断する。この後では、パルスは、拒否できない。

【0075】

・最小弁別子チェック・ポイント:最小弁別子(MIN_DISC_POS)信号は、図10に示すような最小弁別子チェック・ポイントの前に生じなければならない。さもなければ、パルスは、最小弁別子チェック・ポイントに拒否される。最小弁別子(MIN_DISC_POS)信号は、図10に示すような最小弁別子チェック・ポイントの前に生じなければならない。さもなければ、パルスは拒否される。

【0076】

或るチェック・ポイント判断は、INIT_DISC_POS(立上り)が40MHzのクロックに対していつ生じたかに基づく。チャネルに対する他の計時パラメータは、サンプリング時間(サンプル1,2,3,4)と積分器リセット時間(INT_RST)のようなADコンバータ計時にリンクされたパルス基準タイマに基づく。ここでは、計時制約の定義上、幾つかの制限がある:

・Sample1時間<Sample2時間<Sample3時間<Sample4時間。

【0077】

・「最小弁別子チェック・ポイント」は「良いパルス・チェック・ポイント」に先立って生じなければならない。

データ及び計時と制御信号は、上述したように、低電圧差分信号リンク(LVDSリンク。LVDS:Low voltage differential signaling

)を介して、検出電子機器の様々なサブセクションに送信される。データは、データリンクを介して、送信され、ここで、データワードが連続化され、高速(240MHz超)低電圧差分信号リンクを通じて送信され、非連続化される。計時と制御信号は、低電圧差分信号ドライバと受信器を使用して送信される。使用されるチップ・セットは、様々なソースから得ることができるが、一般に、好しくは、ナショナル・セミコンダクター社の高速シリアルリンク用の部品番号DS90CR216,DS90CR215、ならびに、計時

と制御信号用のSN65LVDS32ADとSN65LVDS31NSと等価であるかまたは更に良い。

【0078】

高速送信データリンクの各々は、3つの低電圧差分信号対に連続化される21個の信号からなる。データ・クロックからなる第4低電圧差分信号もまた、データリンクの一部として送られる。受信端では、3個の低電圧差分信号データ信号が非連続化され、データ・クロックを使用して、元の21個のデータリンク信号に回復される。図19は、送信1900のこの特定の方式を示す。矢印の方向を反転させることによって、および、連続化器を非連続化器に置換することによって、受信側の等価図が容易に得られる。

【0079】

高速データリンクは、読出カード、フロントエンドモジュール、およびデジタル信号処理機基板の間でデータを送信するポイント間リンクである。次の信号は、高速データリンクに対して定義される(注:DVは、アクティブが低である):

・CLK(クロック):この信号は、21データ・ビットを連続化器にクロックさせるために使用される。

【0080】

・D0−D15:データワード。

・EPB(偶数パリティ・ビット):すべてのリンクが、偶数パリティを使用する(D20は、パリティ・チェックに対して考慮されない)。

【0081】

・FW(第1語):データワードがデータまたはコマンドのシーケンスの第1語であることを示す。

・LW(最終語)は、データワードがデータまたはコマンドのシーケンスの最終語であることを示す。

【0082】

・DV(データ有効・アクティブ低):アサートされた場合に(アクティブ低!)データワードが有効であることを示す。

・CMD(コマンド):アサートされた場合にデータワードがコマンドであることを示し、アサートされない場合にはデータワードがデータであることを示す(注:当業者には容易に理解されるように、データはリトル・エンディアンのフォーマットで送られる)。

【0083】

セットアップと時間保持は、ナショナル・セミコンダクター社のチップ・セットと互換性があるべきである。実際には、これは、DVがアサートされる場合には常に(既に注記したように、アクティブ低)、ナショナル・セミコンダクター社のチップを駆動するクロック立上りでデータのクロック・インとアウトすることによって容易に実施できる。図20は、典型的なインタフェースを模式的に示し、従って、データリンクは、第1語失敗モードで動作する2個のFIFO間の直接通信を可能にする。送信FIFOのORピンは、クロック信号の立上り後の数ナノ秒で低になる。その後、この信号と利用可能なデータは、次の立上りでCR215にラッチされる。受信端上で、D20が低になる場合には常に、そのデータは、回復されたクロック信号(RXCLK)のクロック立上りで第2FIFOにラッチされる。

【0084】

FIFOからFIFOへのデータ・フローは、低電圧差分信号高速リンクを介してのものである。制御信号は、読出カード基板上のタイムスタンプから使用される計時クロック(10MHz)、リセット信号(アクティブ低)、タイムスタンプ・カウンタをリセットする同期パルス、および送信イネーブル(アクティブ低)である。次のものは、図21に模式的に示された計時と制御信号に対する信号定義である:

RST*(リセット):フロントエンドモジュールと読出カード基板を既知の状態に設定するが、その構成要素の本構成は、リセットされることがある。リセット・パルスは、少なくとも25.6usecの長さが必要とされる。その信号は、アクティブ低である。

【0085】

TCLK(計時クロック):それは、グローバルな10MHzの計時クロックである。立上りの各々は、タイムスタンプ・カウンタを1だけ増分する。

TSYNC(計時クロック同期):タイムスタンプ・カウンタは、この信号の立上りで0にリセットされる。公称で、このパルスは、16.7ミリ秒毎に見られる(60Hz)。

【0086】

TXEN*(送信イネーブル):データ送信をイネーブルにする。この信号は、アクティブ低である。この信号は、更に高いレベルの構成要素がその情報を扱うことができない場合に、更に低いレベルの構成要素がデータを送信するのを防止する。

【0087】

図示のように、読出カード基板上に3つのRJ−45通信リンクがあり、これらは、データ・イン、データ・アウト、ならびに計時と制御インである。3つのリンクはすべて、特定の実施形態によれば、8個の接触シールドRJ−45ジャックを使用する。通信リンクに加えて、3つのRJ−11リンクがあり、2つはプリアンプ基板へ、そして、1つは高電圧基板へのものである。RJ−45ジャックは、当業者には容易に理解されるように、好しくは、Cat5eに互換性がある。図示の構成では、データ通信リンクに対するピン・アウトは、1=D0−、2=D0+、3=D1−、6=D1+、4=D2−、5=D2+、7=CLK−、8=CLK+である。計時と制御リンクに対するピン・アウトは、1=10MHz+、2=10MHz−、3=TSYNC+、4=RESET+、5=RESET−、6=TSYNC−である(ピン7と8は不確定であるが、既知の状態にされるべきである(たとえば7を接地へ、8をVccへ))。特にこの実施形態については、プリアンプ・リンクに対するピン・アウトは、1=試験パルス・トリガ、2=I2Cクロック、3=I2Cデータ、4=スペアである。高電圧基板リンクに対するピン・アウトは、この実施形態によれば、再び、1=リセット、2=I2Cクロック、3=I2Cデータ、4=スペアである。

【0088】

読出カード通信に関して、一実施形態によれば、すべてのコマンドは、ブロードキャスト・モードで発行され、約1Kの量のコマンド語は、入力コマンドFIFOがオーバーフローする前に、特定の読出カードによって受信できる。本システムにおける各20ビット語に対する一般的なフォーマットが表1に示される。

【0089】

【表1】

【0090】

すべての語は、パケットの一部として送られる。このシステムでのパケットはすべて、

第1と最終語インジケータを使用することによって変数長を定義する。各パケットは、開始と停止インジケータを有するか、または、パケットは処理されない。コマンド・ビットは、アップロード(デジタル信号処理機へ)とダウンロード(読出カードへ)で異なって使用される。ダウンロード・パケットでは、第1語だけがコマンドとして示す。コマンド・パケットにおけるすべての他の語は、データとしてマークを付けられる。アップロード・パケットでは、検出器からの測定値がデータとして示す。コマンドに対するすべての他の応答は、それらと通常のデータから区別するためにコマンドとしてマークを付けられる。更に、偶数パリティ・ビット・インジケータがある。残りの16ビットは、データまたはコマンドに使用される。すべての構造は、リトル・エンディアンのフォーマットで送られる。つまり、LSWが最初に送られる。本システムに対するコマンド・セットは、表2に定義される。

【0091】

【表2】

【0092】

【0093】

コマンド語の一部は、読出カード構造をプログラムするためのアドレス定義であることができる。他の構成要素の種類(フロントエンドモジュール、デジタル信号処理機)は、アドレス仕様を無視する。アップロード構成要素の定義は、特定の構成要素の種類に対して同一のアドレス・ビットを使用できる。表2では、アドレスはXXで示され、構成要素の種類の定義は、ZZで示される。

【0094】

表3は、読出カードの特定の要素にアクセスし、構成要素の種類ZZを定義するためのXXの値を指定する。WRITE構成コマンドについては、4ビットの変数Yは、ローカルとグローバルの制約で構成サブ定義を可能とするように定義される。WRITE_CNFGコマンド用のY定義上の制約は、表3に定義される。構成情報のこの区分は、構成要素における解析とコマンド・エラー論理を最小限にし、構成要素の更に汎用で、更に包括的なプログラミングを可能にするようになされた。

【0095】

【表3】

【0096】

【0097】

プログラミング処理を開始するために、本システムは、まず初期化される。初期化手順は、実施形態によれば、次の必要条件とオプションのステップを含む:

1. デジタル信号処理機は、DISCOVERコマンドを発行する。このコマンドは、デジタル信号処理機に本システムでの構成要素を知らしめる(必要条件)。

【0098】

2. デジタル信号処理機は、すべての読出カード基板に構成情報をダウンロードする。読出カードは、すべての構成情報が書込まれた場合に限り構成される(必要条件)。

3. 適切なダウンロードを確実にするために各構成要素の構成を読込む(オプション)。

【0099】

4. 各構成要素の状態を読込む(オプション)。

5. 周辺装置(高電圧モジュール、preamp1とpreamp2基番)に情報を書込む(オプション)。

【0100】

6. 周辺装置の状態をチェックする(オプション)。

7. データ取得を開始するためにSTARTコマンドを発行する。ステップ2が読出カードチャネル1202a,1202bに対して行われなければ、取得処理は読出カードで止められる。ERROR応答は、構成されていない各イネーブル・チャネルによってデジタル信号処理機に送られる。

【0101】

次の段落は、本発明の実施形態に係る、典型的なコマンド・セットについて記述する。なお、或るコマンドは、この実施形態によれば、HID(ハードウェアID)なしで送られる。或る単一語のグローバル・コマンドもまた、ハードウェアIDを必要としない。

【0102】

[ACKNOWLEDGE<ハードウェアID>]

アップロード(デジタル信号処理機へ):コマンドが読出カードまたは読出カードチャネル1202a,1202bによって受信され、実行に成功したという本システムへの応答コマンド。ERRORコマンドは、エラーが発生し、コマンドが処理されない場合に生成される。

【0103】

【表4】

【0104】

[ERROR<ハードウェアID>]

アップロード(デジタル信号処理機へ):エラーが発生し、コマンドが処理されないという本システムへの応答コマンド。本システムは、読出カードまたは読出カードチャネル1202a,1202bの状態レジスタにおけるエラーをクリアするのを担う。ACKNOWLEDGEコマンドは、コマンド実行の成功の際に送られる。

【0105】

【表5】

【0106】

[DISCOVER]

この一般的なコマンドは、本システムの初期化処理を開始させる。特に、すべての読出カードに対して、本システムは、それらのハードウェアIDで応答する。そのコマンドは、下記のようなものである。

【0107】

【表6】

【0108】

読出カードに対する特定の応答は、下記のようなものである。

【0109】

【表7】

【0110】

[HV UPLOAD]

高電圧カードは、一実施形態によれば、RS232(9600ボー)インタフェースを使用して情報を本システムにアップロードする。各バイトは、個々に送られることができる。

【0111】

【表8】

【0112】

[HV DOWNLOAD]

最大128バイトのRS232(9600ボー)インタフェースを使用して高電圧基板にコマンドとデータを送る。

【0113】

【表9】

【0114】

[READ_STATUS<ハードウェアID>]

構成要素は、その状態を本システムにアップロードする。このコマンドを受信した後で、構成要素中の或るフラグがクリアされる(*)。各構成要素の状態は異なる。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、コマンド語の停止ビットが設定されなければならない。

【0115】

【表10】

【0116】

[読出カード状態]

【0117】

【表11】

【0118】

【0119】

【0120】

[読出カードチャネル状態]

【0121】

【表12】

【0122】

[READ_TEMPERATURES<ハードウェアID>]

読出カード基板は、その温度と2個のプリアンプ基板(AとB端)の温度を本システムにアップロードする。

【0123】

【表13】

【0124】

その応答は、下記のようなものである。

【0125】

【表14】

【0126】

温度値は、その出力を0.25℃で乗じることによって決定される。

[READ_VERSION<アドレス>]

構成要素は、そのバージョンを本システムにアップロードする。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、最初のコマンド語の停止ビットが設定されなければならない。

【0127】

【表15】

【0128】

殆どの構成要素については、応答は、基板とファームウェア情報を含む。

【0129】

【表16】

【0130】

しかしながら、制御器読出カードバージョン情報が基板情報を含むので、読出カードチャネル1202a,1202bは、ファームウェア仕様を必要とするだけである。読出カードチャネル応答は、次のようなものである。

【0131】

【表17】

【0132】

[RESET]

RESETコマンドは、すべての構成要素をそれらのデフォルト状態(パワー上昇)に戻す。具体的には、すべての制御フィールドプログラマブルゲートアレイは、それらのPROM情報を再びロードする。

【0133】

【表18】

【0134】

[START]

すべての適切なプロトコルが充足されたと想定してデータの取得を開始する。適切に構成されていない構成要素には、ERRORコマンドで応答する。STARTは、エラーを発生させずに複数回送られることができる。更に、STARTコマンドは、TSYNC選択ビットが読出カード制御器1500に設定される場合に、TSYNCを生成する。

【0135】

【表19】

【0136】

[停止]

データの取得を止める。

【0137】

【表20】

【0138】

[READ_CNFG]

構成要素は、その構成を本システムにアップロードする。各構成要素に対する応答は異

なる。本システムにおけるデータワードに対する十分な定義は、WRITE_CNFGコマンドに定義される。構成情報は返されて、Y=0から始まり、Y=15−で終わる。異なるサブ構成は、単一シーケンスに共にスタックされる。グローバル・フォーマットで使用される場合には、ハードウェアIDは必要ではないが、コマンド語の停止ビットは設定されなければならない。

【0139】

【表21】

【0140】

構成要素に書込まれる情報と、構成要素から返される情報との間の唯一の差は、COMMANDビットが、それを取得データから区別するために、返された情報で送られることである。たとえば読出カード構成READからの応答は、次のようなものである。

【0141】

【表22】

【0142】

[WRITE_CNFG]

構成要素の構成をダウンロードする。構成要素の構成はそれぞれ異なる。Yの定義は、情報量とその情報がどのくらいグローバルに一般的かに基づく。一般の規定では、構成0〜7は、特定の構成要素に特有である。一方、構成F〜8は、グローバルに定義可能である。一般的なコマンドは、下記のようなものである。

【0143】

【表23】

【0144】

このコマンドは、取得中に発行できないか、または、エラーが生成される。一旦取得が開始すれば、読出カードの構成は、変更できない。読出カード構成バッチ(Y=0)は、1つのコマンドでY=8、Y=14、およびY=15の構成情報を書込む。各種類のデータを、つまり、Y=8データ、Y=14データ、Y=15データの順に連鎖させる。

【0145】

[読出カード演算パラメータ(Y=8)]

これらのパラメータは、AとB入力に基づきパルスの位置の演算するために使用される変数を定義する。範囲値は、固定小数点12ビット値であり、オフセットは、固定小数点12ビット値である。これらのパラメータは、以下のように読出カード制御器1500における位置を演算するために使用される。オフセットは、偽のトリガ・モードで多くの読取結果の平均を取り、次に、その数値に64を乗じることによって決定され、最終値を整数として割当ている。従って、LSBは、=1/64のカウントである。範囲は、2048が1.0として定義され、従って、範囲=1/2048のLSBをなすことを注記することによって決定される。あるいは、範囲に0.0005の分解能を提供する。

【0146】

【表24】

【0147】

【0148】

【0149】

操作パラメータ(Y=14)

【0150】

【表25】

【0151】

【0152】

モード・パラメータ(Y=15)

【0153】

【表26】

【0154】

【0155】

読出カードチャネル構成(WRITE)Y=0は、Y=1、Y=8の順に連鎖させたすべてのチャネル情報を送る。

[固有の情報(Y=1)]

読出カードチャネル1202a,1202bの構成Y=1情報は、限定された定義によるものである。位置インデックスは、各チャネルに対して固有でなければならず、各チャネルに対するアナログ情報は、典型的には、様々な検出器とプリアンプに対して異なる。これらのパラメータは、チャネルがデータを取得する前に構成されなければならない。v変数は、電圧と抵抗の電位差計値を表わす。p変数は、固定位置値を表わす。x変数は、パリティを意味するか、または、条件に依存しない。

【0156】

【表27】

【0157】

【0158】

チャネルのアナログ部1204に対するデフォルト値が下に定義され、従って、チャネルのアナログ部1204は、一次に機能するべきである。

【0159】

【表28】

【0160】

[判断パラメータ(Y=8)]

読出カードチャネル1202a,1202b用の判断パラメータは、本システムに亘って包括的且つ一般的であるべきである。これらのパラメータの変化は、様々な検出器の種類または様々な読出カードアナログ電子機器においてのみ生じる。s変数は、ADコンバータサンプリング・レートに基づく。p変数は、40MHz(25ナノ秒周期)の読出カ

ード基板クロック基づく。x変数は、パリティを意味するか、または、条件に依存しない。

【0161】

【表29】

【0162】

【0163】

デフォルト・パラメータ値は、次のようなものである。

【0164】

【表30】

【0165】

[DATA_MODES]

構成要素の構成をダウンロードする。構成要素の構成は、それぞれ異なる。Yの定義は、情報量とその情報がどのくらいグローバルに一般的かに基づく。一般の規定では、構成0〜7は、特定の構成要素に特有なものである。

【0166】

[事象モード]

すべてのサンプリング情報は、位置を演算するために使用される(cで示す)。

【0167】

【表31】

【0168】

[詳細データ・モード]

詳細モードと名付けられたこのモードでは、チャネルは、情報を出力する前に、検出される入力信号を待つ。有効時間窓判断だけが、このモードで使用される。チャネル情報は、sample4時間に達するまで出力される。詳細パケットの長さは、ハードウェア限定を有し、それらは、イネーブルになったチャネルの数、パルスがどのくらいの頻度で生じているか、サンプリング・レート、およびサンプリング時間に依存する。詳細データ・パケットの長さは、任意の内部データFIFOがオーバーフローする場合に変わることがある。

【0169】

【表32】

【0170】

[生データ・モード]

生データ・モードとして示すこのモードでは、読出カードは、事象中に測定されたA/D変換値を出力する。

【0171】

【表33】

【0172】

[拡張生データ・モード]

別のモード、拡張生データ・モードでは、読出カードは、事象中に測定されたA/D変換値を出力する。加えて、位置についての制御フィールドプログラマブルゲートアレイ演算が報告される。

【0173】

【表34】

【0174】

[POSITON_CALCULATION]

位置演算は、以下のように行なわれる。AとBに対する生カウントが左に6つシフトされる。次に、AとBのオフセットは、その結果から減じられる。次に、各々のオフセット訂正値は、AとBの範囲で乗じられる。次に、(A−B)/(A+B)+1が演算され、ここでは、その区分は、少なくとも28ビットの分解能を維持される。結果として生じる数は、0〜2の間にある。この数は、高分解能モードの場合に128を乗じられ、さもなければ64を乗じられる。整数である際に統計的に正しいビンを生成するために、0.5に等しい適切な固定小数点がその数に加算される。次に、その数は、チューブの位置インデックスに加算される整数になり、これは、報告されるピクセルIDである。

【0175】

次の典型的なxmlリストは、32型の検出器に対する要求されたデフォルト構成ファイルを提供する。

【0176】

【表35】

【0177】

【0178】

本発明がその好ましい特定の実施形態に関連して記述されるが、先の記述とそれに続く例が本発明の範囲を例示し、且つ、それを限定しないように意図されることが理解されるべきである。本発明の範囲内の他の態様、利点、および修正は、本発明が関連する当業者には明白であろう。

【特許請求の範囲】

【請求項1】

線形位置センサアレイとプリアンプ回路とを有する放射線検出器であって、

前記線形位置センサアレイは、真空チャンバで中性子を捕獲するように、かつ前記中性子の捕獲に基づき電流信号を生成するように構成され、

前記プリアンプ回路は、

前記放射線検出器の第1位置と第2位置とから前記電流信号を受信するように接続された第1および第2トランスインピーダンス・アンプであって、前記第1および第2トランスインピーダンス・アンプは出力で第1および第2電圧信号を生成することと;

第1および第2増幅電圧信号を提供すべく、前記第1および第2電圧信号を増幅するために前記トランスインピーダンス・アンプの出力に接続される入力を有する第2増幅ステージと;

前記第2増幅ステージに接続される差動出力ステージであって、前記差動出力ステージは前記第1および第2増幅電圧信号を受信し、前記第1および第2増幅電圧信号それぞれからの一対の出力を提供することと;

前記一対の出力の両方を受信するように接続された入力を有する読出回路であって、前記読出回路は前記一対の出力のそれぞれを処理する処理構造を有し、前記読出回路はタイムスタンプされた単一のデジタル出力を提供することと

を有する、放射線検出器。

【請求項2】

前記処理構造は、

前記一対の出力を、AとBの単一の出力に変換する差動アンプのシリアル接続と;

前記単一の出力を合計出力に合計する合計ステージと;

集積回路と;および

ADコンバータと

を有する、請求項1記載の放射線検出器。

【請求項3】

前記合計ステージはさらに、前記合計出力の信号レベルを平衡させるためにプログラム可能なゲイン平衡/加算回路を有する、

請求項2記載の放射線検出器。

【請求項4】

前記放射線検出器は更に、前記合計ステージと前記集積回路とにそれぞれ接続された弁別子回路を有し、

前記弁別子回路は、

信号検出のための前記合計出力を受信する一つのチャネルである信号検出チャネルと;

雑音検出のための前記合計出力の負つまり反転を受信する一つのチャネルである雑音検出チャネルと

を有し、

前記信号検出チャネルでの論理「1」の検出は、前記集積回路の計時を開始させる、

請求項2記載の放射線検出器。

【請求項5】

前記信号検出チャネルと前記雑音検出チャネルとは、それぞれ比較器を有する、

請求項4記載の放射線検出器。

【請求項6】

前記第1および第2電圧信号は、前記電流信号を積分せずに、前記電流信号に比例する、

請求項1記載の放射線検出器。

【請求項7】

前記第2増幅ステージは、第2オペアンプとコンデンサとを有し、前記コンデンサは前記第2オペアンプと並列であり、かつ前記第2オペアンプを安定化させるように構成され

る、

請求項1記載の放射線検出器。

【請求項8】

前記第1および第2トランスインピーダンス・アンプは、それぞれ100KΩ以下の抵抗を伴うフィードバックループを有する、

請求項6記載の放射線検出器。

【請求項1】

線形位置センサアレイとプリアンプ回路とを有する放射線検出器であって、

前記線形位置センサアレイは、真空チャンバで中性子を捕獲するように、かつ前記中性子の捕獲に基づき電流信号を生成するように構成され、

前記プリアンプ回路は、

前記放射線検出器の第1位置と第2位置とから前記電流信号を受信するように接続された第1および第2トランスインピーダンス・アンプであって、前記第1および第2トランスインピーダンス・アンプは出力で第1および第2電圧信号を生成することと;

第1および第2増幅電圧信号を提供すべく、前記第1および第2電圧信号を増幅するために前記トランスインピーダンス・アンプの出力に接続される入力を有する第2増幅ステージと;

前記第2増幅ステージに接続される差動出力ステージであって、前記差動出力ステージは前記第1および第2増幅電圧信号を受信し、前記第1および第2増幅電圧信号それぞれからの一対の出力を提供することと;

前記一対の出力の両方を受信するように接続された入力を有する読出回路であって、前記読出回路は前記一対の出力のそれぞれを処理する処理構造を有し、前記読出回路はタイムスタンプされた単一のデジタル出力を提供することと

を有する、放射線検出器。

【請求項2】

前記処理構造は、

前記一対の出力を、AとBの単一の出力に変換する差動アンプのシリアル接続と;

前記単一の出力を合計出力に合計する合計ステージと;

集積回路と;および

ADコンバータと

を有する、請求項1記載の放射線検出器。

【請求項3】

前記合計ステージはさらに、前記合計出力の信号レベルを平衡させるためにプログラム可能なゲイン平衡/加算回路を有する、

請求項2記載の放射線検出器。

【請求項4】

前記放射線検出器は更に、前記合計ステージと前記集積回路とにそれぞれ接続された弁別子回路を有し、

前記弁別子回路は、

信号検出のための前記合計出力を受信する一つのチャネルである信号検出チャネルと;

雑音検出のための前記合計出力の負つまり反転を受信する一つのチャネルである雑音検出チャネルと

を有し、

前記信号検出チャネルでの論理「1」の検出は、前記集積回路の計時を開始させる、

請求項2記載の放射線検出器。

【請求項5】

前記信号検出チャネルと前記雑音検出チャネルとは、それぞれ比較器を有する、

請求項4記載の放射線検出器。

【請求項6】

前記第1および第2電圧信号は、前記電流信号を積分せずに、前記電流信号に比例する、

請求項1記載の放射線検出器。

【請求項7】

前記第2増幅ステージは、第2オペアンプとコンデンサとを有し、前記コンデンサは前記第2オペアンプと並列であり、かつ前記第2オペアンプを安定化させるように構成され

る、

請求項1記載の放射線検出器。

【請求項8】

前記第1および第2トランスインピーダンス・アンプは、それぞれ100KΩ以下の抵抗を伴うフィードバックループを有する、

請求項6記載の放射線検出器。

【図1】

【図2】

【図2A】

【図2B】

【図2C】

【図3】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図16】

【図17】

【図12】

【図13】

【図18】

【図19】

【図20】

【図21】

【図2】

【図2A】

【図2B】

【図2C】

【図3】

【図3A】

【図3B】

【図3C】

【図3D】

【図3E】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図14】

【図15】

【図16】

【図17】

【図12】

【図13】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−57676(P2013−57676A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2012−236597(P2012−236597)

【出願日】平成24年10月26日(2012.10.26)

【分割の表示】特願2009−534923(P2009−534923)の分割

【原出願日】平成19年10月29日(2007.10.29)

【出願人】(301027074)ユーティ―バテル エルエルシー (19)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成24年10月26日(2012.10.26)

【分割の表示】特願2009−534923(P2009−534923)の分割

【原出願日】平成19年10月29日(2007.10.29)

【出願人】(301027074)ユーティ―バテル エルエルシー (19)

【Fターム(参考)】

[ Back to top ]