高速量子化器

【課題】高速量子化器および最適化された時間遅延を提供する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

【解決手段】高速量子化器コンパレータの装置と方法は、3部を含む:プリアンプ部、再生ラッチ部、およびデータラッチ部。時間遅延は、再生ラッチ出力の最初の電圧を変えることによって減少される。電流源はコンパレータの底部に提供され、時間遅延最適化を可能にする。PMOS同等化スイッチが停止されたとき、クロック信号をフィードスルーにし、出力に電荷の注入を提供する。これらの電荷によって、コンパレータの時間遅延が可変となる。リセット時間が比較時間より長いために、非常に低い電流が出力電圧を決定する。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願の相互参照)

本出願は、参照により本明細書に組み込まれている、2010年11月18日に出願した米国特許仮出願第61/415,041号の利益を主張する。

【0002】

本発明は、低歪みデルタシグマ変調器のためのアーキテクチャに関し、特に高速量子化器および最適化された時間遅延を提供する方法に関する。

【背景技術】

【0003】

幅広い製品が、アナログデジタルコンバータ(ADC)およびデジタルアナログコンバータ(DAC)を形成する高速回路を組み込んでいる。これらはデルタシグマ(ΔΣ)変調器を含む。これら製品の性能予想は、常に、電力消費を制限または減少させながら、より良い線形性およびバンド幅を達成するように推進されている。信号処理の領域は通常、強化された仕様を要求する。これら要求は、サイズ、コスト、複雑性、電力、速度、信号バンド幅、ノイズおよび安定性などの相反する特性を伴う。この増加された性能を要求する製品は、オーディオ、ビデオ、およびRFの応用における、データおよび信号の送受信機を含む。

【0004】

変調器の性能を向上させる方法は、高次の、低歪みのアーキテクチャを使用することを含んでいる。これは加算器の入力の数の増加および係数の増加を伴う。加算器の入力の増加によって効率的なフィードバックが得られる一方、不安定性も増加する。不安定性は、回路遅延、特にループ遅延の結果であることもある。

【0005】

図1は、量子化器155を含む、既知の3次の変調器のブロック図100である。言及したように、加算器の入力の数および係数が増加するにつれて、加算器フィードバック因子βは小さくなり、よって広いバンド幅または良い位相マージンを得るには電力消費が高くなる。図1の回路において、入力U110は加算ノード105および115に入力される。加算ノード115の出力は積算器120の入力に入力される。積算器120の出力は、フィードフォーワード経路125の入力および加算ノード130の入力に入力される。加算ノード130の出力は積算器135の入力に入力される。積算器135の出力は、フィードフォーワード経路140の入力および積算器145の入力に入力される。積算器145の出力は、フィードバック経路150の入力に入力され、この出力は加算ノード130に入力される。積算器145の出力も、加算ノード105に入力され、この出力は量子化器155に入力される。量子化器の出力は、DAC160とデジタル出力フィードバック経路によって加算ノード115に戻り、また出力V165を提供する。

【0006】

電力消費が増加することなく、安定性を維持しながら、低歪みおよび広いバンド幅を提供する技術が必要である。

【発明の概要】

【0007】

実施形態は、低歪みアーキテクチャと減少されたループ遅延を提供し、安定性を制御する。ダブルサンプリング、量子化、およびダイナミックエレメントマッチング(DEM)がオーバーラップ時間なしで遂行される。時間遅延を減少させることで、アナログ加算器の電力を節約することができる。

【0008】

本発明の一実施形態は、遅延時間を最適化する高速量子化器コンパレータデバイスであり、少なくとも第1部のプリアンプと、少なくとも第2部の再生ラッチとを含み、再生ラッチの後部に電流源と、少なくとも第3部のデータラッチとを含み、時間遅延は、最初の電圧を通じて減少され、最適化される。

【0009】

他の実施形態は、変調器ループ遅延時間を最適化するための高速量子化器コンパレータのための方法であり、この方法は、PMOS同等化スイッチを停止することと、PMOS同等化スイッチの停止からクロック信号を送り込むことと、PMOS同等化スイッチの停止から電荷を少なくとも再生ラッチ出力Aと再生ラッチ出力Bに注入することとのステップを備え、時間遅延は、少なくとも再生ラッチ出力Aと再生ラッチ出力Bへの電荷の注入に基づき、変化する。

【0010】

ここに記述されている特長と利点は、包括的なものではなく、特に、多くの付加的な特徴と利点は、図、明細書および特許請求の範囲を見ることにより、当業者には明らかであろう。さらに、明細書内で使用されている言語は原則的に読みやすさと教授の目的で選択されており、発明の主題の範囲を限定するために選択されているのではない。

【図面の簡単な説明】

【0011】

【図1】量子化器を含む既知の3次の変調器のブロック図である。

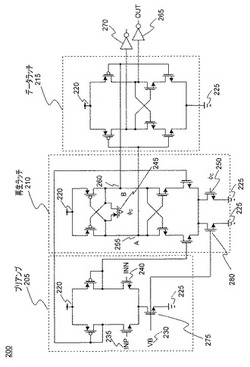

【図2】本発明の一実施形態に従って構築された高速量子化器コンパレータを示す回路図である。

【図3】本発明の一実施形態に従って構築された高速量子化器コンパレータの方法を示すフローチャートである。

【発明を実施するための形態】

【0012】

以下の詳細な記述は、添付の図を参照しながら、現在主張している発明の例示の実施形態を提供する。記述は実例となるよう意図され、本発明の範囲を限定するものではない。実施形態は、当業者が主題の発明を実施することができるように十分詳細に記述されている。他の実施形態は、主題の発明の精神または範囲を逸脱することなくある程度の変更とともに実施されることができる。

【0013】

図2は高速量子化器コンパレータ回路の実施形態200を示す。回路は3ステージを含む:第1のプリアンプ部205、第2の再生ラッチ部210、および第3のデータラッチ部215。接続はVDD供給接続220および接地接続225を含む。入力はVB230、INP235、およびINN240を含む。スイッチはΦcスイッチ245および250を含む。出力は再生ラッチ出力A255、再生ラッチ出力B260、OUT265および270を含む。

【0014】

第2の再生ラッチ部210は、再生ラッチ出力A255と再生ラッチ出力B260との間にPMOS同等化スイッチ245を含む。第2の再生ラッチ部210は、コンパレータ再生ラッチ210の底部に、接地に接続されているNMOS比較スイッチ250を含む。PMOS同等化スイッチ245とNMOS比較スイッチ250とは、交互に作動、または停止される。

【0015】

第1のプリアンプ部205はトランジスタ275を電流源として含む。

【0016】

第2の再生ラッチ部210はトランジスタ280を電流源として含む。電流源280がコンパレータ再生ラッチ210の底部に位置することから、時間遅延を最適化することができる。

【0017】

第1の期間は、信号Φc=「H」のとき、比較時間である。第2の期間は、信号Φc=「L」のとき、リセット時間である。

【0018】

第1の期間において、PMOS同等化スイッチ245は、停止しているとき(NMOS比較スイッチ250が作動しているとき)再生ラッチ出力A255および再生ラッチ出力B260に電荷を注入する。次に、第2の期間において、PMOS同等化スイッチ245は、作動しているとき(NMOS比較スイッチ250が停止しているとき)出力Aおよび出力Bの電圧をリセットする。出力Aおよび出力Bのリセット電圧は、ラッチ値を変更することができる。出力Aおよび出力Bの同等化電圧は、PMOS同等化スイッチ245が作動しているときの再生ラッチの論理閾値と等しいため、注入された電荷の効果は減少されることができる。

【0019】

第2の期間において、コンパレータ再生ラッチ210の底部に位置する電流源280は、NMOS比較スイッチ250が停止しているとき、低DC電流を提供することができる。リセット時間が比較時間より長いため、出力A255および出力B260の電圧を設定するために低DC電流のみが必要である。

【0020】

図3は高速量子化器コンパレータの方法を示すフローチャート300である。方法のステップは、再生ラッチにバイアスをかけること305、出力Aおよび出力Bに電荷を注入すること310、および出力Aおよび出力Bのイニシャライズ時間を縮小することを備える。時間遅延は、再生ラッチ出力(AおよびB)の初期の電圧を変更することで減少し、よって提案されているコンパレータの遅延は最適化されることができる。リセット時間が比較時間より長いため、AおよびBの電圧を設定するために非常に低い直流電流(DC)のみが必要である。

【0021】

本発明の実施形態の上述の記述は実例と説明の目的で提供された。本提案のそれぞれおよびすべてのページと、この中のすべてのコンテンツは、特長付けられ、定義され、番号を付けられているが、すべての目的に対する本願の実質的な部分とみなされ、形式または本願内での位置に関わらない。本明細書は、包括的なものまたは本発明を開示された厳密な形式に限定することを意図していない。多くの変更および変形が、本開示を踏まえて可能である。

【技術分野】

【0001】

(関連出願の相互参照)

本出願は、参照により本明細書に組み込まれている、2010年11月18日に出願した米国特許仮出願第61/415,041号の利益を主張する。

【0002】

本発明は、低歪みデルタシグマ変調器のためのアーキテクチャに関し、特に高速量子化器および最適化された時間遅延を提供する方法に関する。

【背景技術】

【0003】

幅広い製品が、アナログデジタルコンバータ(ADC)およびデジタルアナログコンバータ(DAC)を形成する高速回路を組み込んでいる。これらはデルタシグマ(ΔΣ)変調器を含む。これら製品の性能予想は、常に、電力消費を制限または減少させながら、より良い線形性およびバンド幅を達成するように推進されている。信号処理の領域は通常、強化された仕様を要求する。これら要求は、サイズ、コスト、複雑性、電力、速度、信号バンド幅、ノイズおよび安定性などの相反する特性を伴う。この増加された性能を要求する製品は、オーディオ、ビデオ、およびRFの応用における、データおよび信号の送受信機を含む。

【0004】

変調器の性能を向上させる方法は、高次の、低歪みのアーキテクチャを使用することを含んでいる。これは加算器の入力の数の増加および係数の増加を伴う。加算器の入力の増加によって効率的なフィードバックが得られる一方、不安定性も増加する。不安定性は、回路遅延、特にループ遅延の結果であることもある。

【0005】

図1は、量子化器155を含む、既知の3次の変調器のブロック図100である。言及したように、加算器の入力の数および係数が増加するにつれて、加算器フィードバック因子βは小さくなり、よって広いバンド幅または良い位相マージンを得るには電力消費が高くなる。図1の回路において、入力U110は加算ノード105および115に入力される。加算ノード115の出力は積算器120の入力に入力される。積算器120の出力は、フィードフォーワード経路125の入力および加算ノード130の入力に入力される。加算ノード130の出力は積算器135の入力に入力される。積算器135の出力は、フィードフォーワード経路140の入力および積算器145の入力に入力される。積算器145の出力は、フィードバック経路150の入力に入力され、この出力は加算ノード130に入力される。積算器145の出力も、加算ノード105に入力され、この出力は量子化器155に入力される。量子化器の出力は、DAC160とデジタル出力フィードバック経路によって加算ノード115に戻り、また出力V165を提供する。

【0006】

電力消費が増加することなく、安定性を維持しながら、低歪みおよび広いバンド幅を提供する技術が必要である。

【発明の概要】

【0007】

実施形態は、低歪みアーキテクチャと減少されたループ遅延を提供し、安定性を制御する。ダブルサンプリング、量子化、およびダイナミックエレメントマッチング(DEM)がオーバーラップ時間なしで遂行される。時間遅延を減少させることで、アナログ加算器の電力を節約することができる。

【0008】

本発明の一実施形態は、遅延時間を最適化する高速量子化器コンパレータデバイスであり、少なくとも第1部のプリアンプと、少なくとも第2部の再生ラッチとを含み、再生ラッチの後部に電流源と、少なくとも第3部のデータラッチとを含み、時間遅延は、最初の電圧を通じて減少され、最適化される。

【0009】

他の実施形態は、変調器ループ遅延時間を最適化するための高速量子化器コンパレータのための方法であり、この方法は、PMOS同等化スイッチを停止することと、PMOS同等化スイッチの停止からクロック信号を送り込むことと、PMOS同等化スイッチの停止から電荷を少なくとも再生ラッチ出力Aと再生ラッチ出力Bに注入することとのステップを備え、時間遅延は、少なくとも再生ラッチ出力Aと再生ラッチ出力Bへの電荷の注入に基づき、変化する。

【0010】

ここに記述されている特長と利点は、包括的なものではなく、特に、多くの付加的な特徴と利点は、図、明細書および特許請求の範囲を見ることにより、当業者には明らかであろう。さらに、明細書内で使用されている言語は原則的に読みやすさと教授の目的で選択されており、発明の主題の範囲を限定するために選択されているのではない。

【図面の簡単な説明】

【0011】

【図1】量子化器を含む既知の3次の変調器のブロック図である。

【図2】本発明の一実施形態に従って構築された高速量子化器コンパレータを示す回路図である。

【図3】本発明の一実施形態に従って構築された高速量子化器コンパレータの方法を示すフローチャートである。

【発明を実施するための形態】

【0012】

以下の詳細な記述は、添付の図を参照しながら、現在主張している発明の例示の実施形態を提供する。記述は実例となるよう意図され、本発明の範囲を限定するものではない。実施形態は、当業者が主題の発明を実施することができるように十分詳細に記述されている。他の実施形態は、主題の発明の精神または範囲を逸脱することなくある程度の変更とともに実施されることができる。

【0013】

図2は高速量子化器コンパレータ回路の実施形態200を示す。回路は3ステージを含む:第1のプリアンプ部205、第2の再生ラッチ部210、および第3のデータラッチ部215。接続はVDD供給接続220および接地接続225を含む。入力はVB230、INP235、およびINN240を含む。スイッチはΦcスイッチ245および250を含む。出力は再生ラッチ出力A255、再生ラッチ出力B260、OUT265および270を含む。

【0014】

第2の再生ラッチ部210は、再生ラッチ出力A255と再生ラッチ出力B260との間にPMOS同等化スイッチ245を含む。第2の再生ラッチ部210は、コンパレータ再生ラッチ210の底部に、接地に接続されているNMOS比較スイッチ250を含む。PMOS同等化スイッチ245とNMOS比較スイッチ250とは、交互に作動、または停止される。

【0015】

第1のプリアンプ部205はトランジスタ275を電流源として含む。

【0016】

第2の再生ラッチ部210はトランジスタ280を電流源として含む。電流源280がコンパレータ再生ラッチ210の底部に位置することから、時間遅延を最適化することができる。

【0017】

第1の期間は、信号Φc=「H」のとき、比較時間である。第2の期間は、信号Φc=「L」のとき、リセット時間である。

【0018】

第1の期間において、PMOS同等化スイッチ245は、停止しているとき(NMOS比較スイッチ250が作動しているとき)再生ラッチ出力A255および再生ラッチ出力B260に電荷を注入する。次に、第2の期間において、PMOS同等化スイッチ245は、作動しているとき(NMOS比較スイッチ250が停止しているとき)出力Aおよび出力Bの電圧をリセットする。出力Aおよび出力Bのリセット電圧は、ラッチ値を変更することができる。出力Aおよび出力Bの同等化電圧は、PMOS同等化スイッチ245が作動しているときの再生ラッチの論理閾値と等しいため、注入された電荷の効果は減少されることができる。

【0019】

第2の期間において、コンパレータ再生ラッチ210の底部に位置する電流源280は、NMOS比較スイッチ250が停止しているとき、低DC電流を提供することができる。リセット時間が比較時間より長いため、出力A255および出力B260の電圧を設定するために低DC電流のみが必要である。

【0020】

図3は高速量子化器コンパレータの方法を示すフローチャート300である。方法のステップは、再生ラッチにバイアスをかけること305、出力Aおよび出力Bに電荷を注入すること310、および出力Aおよび出力Bのイニシャライズ時間を縮小することを備える。時間遅延は、再生ラッチ出力(AおよびB)の初期の電圧を変更することで減少し、よって提案されているコンパレータの遅延は最適化されることができる。リセット時間が比較時間より長いため、AおよびBの電圧を設定するために非常に低い直流電流(DC)のみが必要である。

【0021】

本発明の実施形態の上述の記述は実例と説明の目的で提供された。本提案のそれぞれおよびすべてのページと、この中のすべてのコンテンツは、特長付けられ、定義され、番号を付けられているが、すべての目的に対する本願の実質的な部分とみなされ、形式または本願内での位置に関わらない。本明細書は、包括的なものまたは本発明を開示された厳密な形式に限定することを意図していない。多くの変更および変形が、本開示を踏まえて可能である。

【特許請求の範囲】

【請求項1】

遅延時間を最適化するための高速量子化器コンパレータであって、

少なくとも再生ラッチであって、第1の再生ラッチ出力と第2の再生ラッチ出力との間に同等化スイッチを含む、再生ラッチと、

前記再生ラッチの底部に位置する電流源であって、リセット時間の間に、前記同等化スイッチが作動する、電流源と

を含むことを特徴とする高速量子化器コンパレータ。

【請求項2】

前記電流源は低DC電流を提供することを特徴とする請求項1に記載の高速量子化器コンパレータ。

【請求項3】

前記再生ラッチは、前記再生ラッチの底部に比較スイッチを含み、比較時間の間に、前記比較スイッチが作動することを特徴とする請求項1または2に記載の高速量子化器コンパレータ。

【請求項4】

前記再生ラッチの前方に接続された少なくともプリアンプと、

前記再生ラッチの次に接続された少なくともデータラッチと

をさらに含むことを特徴とする請求項1乃至3のいずれかに記載の高速量子化器コンパレータ。

【請求項5】

時間遅延は、前記プリアンプによって前記再生ラッチの再生ラッチ出力へ提供される最初の電圧を通じて減少され、最適化されることを特徴とする請求項4に記載の高速量子化器コンパレータ。

【請求項6】

変調器ループ遅延時間を最適化するための高速量子化器コンパレータのための方法であって、

DC電流によって再生ラッチの出力にバイアスをかけることと、

同等化スイッチを停止することと、

前記同等化スイッチの前記停止からクロック信号を送り込むことと、

前記同等化スイッチの前記停止から電荷を少なくとも第1の再生ラッチ出力と第2の再生ラッチ出力に注入することであって、時間遅延は少なくとも前記第1の再生ラッチ出力と前記第2の再生ラッチ出力への電荷の注入に基づき変化する、電荷を注入することと

を備えたことを特徴とする方法。

【請求項1】

遅延時間を最適化するための高速量子化器コンパレータであって、

少なくとも再生ラッチであって、第1の再生ラッチ出力と第2の再生ラッチ出力との間に同等化スイッチを含む、再生ラッチと、

前記再生ラッチの底部に位置する電流源であって、リセット時間の間に、前記同等化スイッチが作動する、電流源と

を含むことを特徴とする高速量子化器コンパレータ。

【請求項2】

前記電流源は低DC電流を提供することを特徴とする請求項1に記載の高速量子化器コンパレータ。

【請求項3】

前記再生ラッチは、前記再生ラッチの底部に比較スイッチを含み、比較時間の間に、前記比較スイッチが作動することを特徴とする請求項1または2に記載の高速量子化器コンパレータ。

【請求項4】

前記再生ラッチの前方に接続された少なくともプリアンプと、

前記再生ラッチの次に接続された少なくともデータラッチと

をさらに含むことを特徴とする請求項1乃至3のいずれかに記載の高速量子化器コンパレータ。

【請求項5】

時間遅延は、前記プリアンプによって前記再生ラッチの再生ラッチ出力へ提供される最初の電圧を通じて減少され、最適化されることを特徴とする請求項4に記載の高速量子化器コンパレータ。

【請求項6】

変調器ループ遅延時間を最適化するための高速量子化器コンパレータのための方法であって、

DC電流によって再生ラッチの出力にバイアスをかけることと、

同等化スイッチを停止することと、

前記同等化スイッチの前記停止からクロック信号を送り込むことと、

前記同等化スイッチの前記停止から電荷を少なくとも第1の再生ラッチ出力と第2の再生ラッチ出力に注入することであって、時間遅延は少なくとも前記第1の再生ラッチ出力と前記第2の再生ラッチ出力への電荷の注入に基づき変化する、電荷を注入することと

を備えたことを特徴とする方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2012−109971(P2012−109971A)

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願番号】特願2011−250645(P2011−250645)

【出願日】平成23年11月16日(2011.11.16)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願日】平成23年11月16日(2011.11.16)

【出願人】(303046277)旭化成エレクトロニクス株式会社 (840)

【Fターム(参考)】

[ Back to top ]