2つのタイプの減結合コンデンサを備えた集積回路および方法

【課題】デュアル電圧パワーアイランドアーキテクチャにおいて、低いオフ状態リークを実現する事が可能な最適な減結合キャパシタンスのための方法およびシステムを提供する。

【解決手段】チップの低電圧領域において、誘電体膜厚の異なる2つの異なるタイプのコンデンサが使用される。膜厚の薄いコンデンサは常時オン状態の領域で使用され、膜厚の厚いコンデンサーは条件付きで起動される領域で使用される。これによって低いオフ状態リークをで減結合コンデンサーを使用できる。

【解決手段】チップの低電圧領域において、誘電体膜厚の異なる2つの異なるタイプのコンデンサが使用される。膜厚の薄いコンデンサは常時オン状態の領域で使用され、膜厚の厚いコンデンサーは条件付きで起動される領域で使用される。これによって低いオフ状態リークをで減結合コンデンサーを使用できる。

【発明の詳細な説明】

【技術分野】

【0001】

本願は、パワーアイランドを使用する低電力集積回路に関し、より詳細には、そのような回路における減結合キャパシタンスの実装に関する。

【0002】

他の出願への相互参照

2007年1月1日に出願された米国仮特許出願第60/921,508号(元は第11/618,912号と番号がつけられている)(特許文献1)および米国仮特許出願第60/934,937号(元は第11/618,913号と番号がつけられている)(特許文献2)の優先権を主張し、両者は、本願明細書において参照により援用されている。

【背景技術】

【0003】

減結合コンデンサは、チップの設計において頻繁に使用され、スイッチング中のノイズを低減する。電源と接地の間に接続されたコンデンサを含むフィラーセルが、ロジック領域において一般的に使用されている。電圧スケーリングが進歩し、デバイスが一時的過電圧により敏感になっているので、スイッチングノイズの制御がより望まれている。

しかし、矛盾する傾向は、低いオフ状態リークに対する要求である。減結合コンデンサは、簡単な蓄積コンデンサとして一般的に実装されている。深くスケーリングされたプロセスによってもたらされたゲート酸化物は、非常に高い固有のキャパシタンスを可能としながら、比較的高いリーク電流密度をもたらす。

ゲート酸化物のリーク密度は、現在好ましくないことに増加している。このように、プロセスがより小さな大きさにスケーリングし続けるので、減結合コンデンサへの従来のアプローチは、許容することができないリーク電流密度をもたらす。

【0004】

多くの携帯電子システムが、電池寿命によって決定的に制限されている。例えば、ユーザは、重い携帯電話を好まないが、ユーザは、電力を使い果たし、シャットダウンする携帯電話も好まない。電池寿命を改善する1つの方法は、携帯システムにおいて電子部品のエネルギー効率を増大させることである。携帯システムが動作中の場合の電力消費量は、電池寿命の重要な要素であるが、システムが待機している場合の電力消費量もやはり重要な要素である。

パワーアイランドは、低電力設計における共通の技術である。パワーアイランドは、停止動作または待機動作の間に必要な回路部分だけを起動しておくことによって、待機電流を低減するのに役立つ。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願第11/618,912号

【特許文献2】米国特許出願第11/618,913号

【特許文献3】米国仮特許出願第60/934,936号

【特許文献4】米国仮特許出願第60/921,507号

【特許文献5】米国仮特許出願第60/934,918号

【特許文献6】米国仮特許出願第60/934,917号

【特許文献7】米国仮特許出願第60/999,760号

【特許文献8】米国仮特許出願第60/934,923号

【特許文献9】米国特許出願第11/618,849号

【特許文献10】米国特許出願第11/618,852号

【特許文献11】米国特許出願第11/618,865号

【特許文献12】米国特許出願第11/618,867号

【特許文献13】米国特許出願第11/649,325号

【特許文献14】米国特許出願第11/649,326号

【特許文献15】米国特許出願第11/965,943号

【特許文献16】米国特許出願第11/966,012号

【特許文献17】米国特許出願第11/966,147号

【発明の概要】

【0006】

本発明者らは、チップの常時オン状態の部分と時々オン状態の部分との違いを考慮することにより、減結合コンデンサの最適化を実現することができることに気付いた。

本願は、減結合コンデンサに対する新しいアプローチを開示し、それは、特に、2つ(またはそれ以上)の酸化物の厚みが使用される集積回路に適用可能である(普通の高くスケーリングされた製品のままで)。例えば、より薄い有効なゲート酸化物は、一般的に、周辺回路よりコアロジックに使用され、これは、周辺回路にいくらかローバスト性を加えながら、コアロジックが最適にスケーリングされることを可能にする。

【0007】

本願は、パワーアイランドアーキテクチャが減結合コンデンサに新しい可能性を開くことを教示する。実施形態の1つの種類によれば、最も薄いゲート酸化物は、常に起動される位置ではなく条件付きで起動される位置でのみ、最低電圧領域内で減結合コンデンサに使用される。別の種類の実施形態によれば、条件付きで起動される位置の減結合コンデンサの一部またはすべてが密度最適化される一方で、常に起動される位置の減結合コンデンサは、リーク最適化される。別の種類の実施形態によれば、条件付きで起動される位置の減結合コンデンサの一部またはすべてが最低電圧ゲート酸化物層から形成される一方で、常に起動される位置の減結合コンデンサは、より高い電圧ゲート酸化物層から形成される。

【0008】

コアゲート酸化物の厚みは、一般的に、I/Oゲート酸化物の厚みよりも薄く、したがって、I/Oゲート酸化物の厚みよりも領域比に対してより良好なキャパシタンスをもたらす。しかし、ディープサブミクロン技術について、大量の電流が、ゲート酸化物を流れてもよい(直接トンネル)。より厚いI/Oゲート酸化物は、領域比に対して低いキャパシタンスを有するだけでなく、はるかに少ないゲート電流を使用する。桁違いのゲートリーク電流は、サブミクロン技術には珍しいことではない。

したがって、コア酸化物の厚みを有するコンデンサは、領域比に対してより良好なキャパシタンスを有するが、より高いゲートリーク電流を有する。I/O酸化物の厚みで形成されたコンデンサは、領域比に対してより低いキャパシタンスを有するがはるかに低いゲートリーク電流を有する。

【0009】

開示された革新は、様々な実施形態において、少なくとも次の利点の1つ以上をもたらす。

・低減された電力消費量

・より大きな密度

・より良好なノイズ抑制

・蓄積コンデンサを今もなお使用することができる

・特別のデバイス構造は減結合コンデンサに必要ではない

・より良好な信頼性

【0010】

開示された発明は、添付の図面を参照して説明され、発明の重要なサンプルの実施形態を示し、本願明細書において参照により援用されている。

【図面の簡単な説明】

【0011】

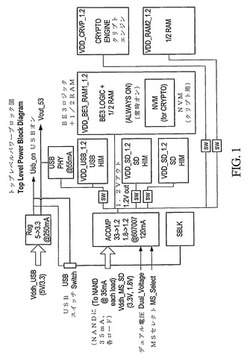

【図1】好ましい実施形態による異なる種類の蓄積コンデンサを使用する異なる領域を含む集積回路の例を示す。

【図2】以下に検討される異なる位置で、2つの異なるバージョンで使用することができる蓄積コンデンサの構造の一例を示す。

【発明を実施するための形態】

【0012】

本願の多数の革新的な教示が、この好ましい実施形態を特別に参照して記載される(例を目的とし限定を目的としない)。

【0013】

減結合コンデンサが、チップの設計において頻繁に使用され、スイッチング中にノイズを低減する。電源と接地の間に接続されたコンデンサを含むフィラーセルが、ロジック領域において一般的に使用される。

少なくとも2つの酸化物の厚みが、サブミクロン製品を製造するために一般的に使用される。コアに使用される酸化物の厚みとIO回路用の酸化物の厚みである。減結合コンデンサは、異なる特性を生じる一方の酸化物の厚みから生成することができる。

コアゲート酸化物の厚みは、IOゲート酸化物の厚みよりも一般的に薄く、このようにして、IOの厚みより領域比に対してより良好なキャパシタンスをもたらす。しかし、ディープサブミクロン技術について、大量の電流が、ゲート酸化物を通って流れる可能性がある(直接トンネル)。

【0014】

トンネル電流が、障壁高さにかかわらず障壁厚みの減少とともに指数関数的であることに留意することが重要である。したがって、ゲート電流密度は、さらなるスケーリングとともに過度に悪化する可能性がある。

IO回路で使用されるより厚いゲート酸化物は、領域比で低いキャパシタンスを有するだけでなく、はるかに少ないゲート電流を使用する。桁違いのゲートリーク電流は、サブミクロン技術に珍しいことではない。

【0015】

多くの現代の低電力設計は、パワーアイランドを使用する。パワーアイランドの目的の1つは、停止動作または待機動作の間に必要な回路部のみが起動された状態とすることによって待機電流を低減することである。

ゲート電流、したがって、パワーアイランドを使用する所定の製品の待機電流を最小限にするために、より厚いゲート酸化物を使用して、待機動作中に起動される回路部分に減結合コンデンサを形成する。より薄いゲート酸化物コンデンサは、待機中に電源が切られる回路部分で使用することができる。この戦略は、ASIC設計者が、待機中に電源が切られる部分におけるチップ領域当たりのキャパシタンスを最も効率的に使用しながら、待機中に電源が入れられる部分におけるリーク電流を最小限にすることを可能にする。

【0016】

これらの減結合コンデンサのサンプル実施例を、本願明細書で「トリポリ」と称するチップ設計との関連で以下に説明する。0.13μmのトランジスタ技術を使用するトリポリ実施例では、N−ウェル蓄積コンデンサが使用された(n−ウェルの内側のN+がドープされたポリおよびソースおよびドレイン)。

I/O酸化物コンデンサについて、1nFは、5.1nAのみのゲートリーク電流で約300Kμm2 の領域を使用する。コア酸化物コンデンサについて、1nFは、2.25μAのゲートリーク電流を使用しながら、約150Kμm2 の領域を使用する。領域が半分だけ低減されるが、リーク電流は、約400の係数を掛けられることに留意するべきである。

【0017】

様々な領域のフィラーセルは、キャパシタンス内蔵で作成された。コア設計およびI/O酸化物コンデンサ設計の両方は、これらのフィラーセル内で作成された。CADソフトウェアは、次いで、チップまわりで減結合キャパシタンスフィラーセルを分配するために使用された。

特定のフィラーセルの位置は、それらの位置が設計者にとって重要なことではないため説明されない。すなわち、フィラーセルは、低レベルの仕様書に挿入され、人間の設計者

の決定とは強い関係がない。同様の理由で、いかなるコンデンサも従来の蓄積コンデンサと同じであるので、任意の個々のコンデンサのデバイスレベルの詳細は特に重要ではない。同様に、個々のフィラーセルは、従来のセルと大きく異ならず、前述したように、セルタイプとセル位置との関連性が、驚くべき利点をもたらす。

【0018】

図1は、好ましい実施形態による、異なる種類の蓄積コンデンサを使用する異なる領域を含む集積回路の例を示す。この図では、個々のブロックの回路動作は、詳細に検討されないが、電源接続は、開示された概念の適用を示すことに有用である。

この図において、「クリプトエンジン」と称する右端の最上部のブロックは、条件付きのみで起動される低電圧コアブロックの例である。図に示されたASICでは、クリプトエンジンは、大量の領域を消費し、さらに、多くのゲートを含み、迅速な計算を可能にする。このブロックは、必要に応じてのみ起動され、チップの合計領域の大部分を消費するので、このブロックは、最も密度の高い結合コンデンサを使用する。

【0019】

「USB PHY」と称する中央上部ブロックは、最も薄いゲート酸化物を使用しないIO(周辺)ブロックである。したがって、このブロックは、いかなる場合にも最も薄い結合コンデンサに適切ではない。

下側中心部の小さな白いブロックは、より大きな灰色ブロック内に埋め込まれ、「クリプト1用のNVM」と称され、常時オンの低電圧コアブロックの例である。このブロックは、条件付きで起動されないので、より薄い酸化物(密度最適化)コンデンサを受けないが、その代りにより厚い酸化物リーク最適化コンデンサを受ける。

したがって、これらの3つのブロックは、ともに、適切なキャパシタンスが好ましい実施形態によって選択される方法を説明する。

【0020】

図2は、以下に検討される異なる位置で、2つの異なるバージョンで使用することができる蓄積コンデンサの構造の一例を示す。ゲート30(例えば、ポリシリコン上のシリサイド)は、ゲート誘電体28(例えば、SiO2 、またはその代わりに、higher−k誘電体)を覆い、ゲート誘電体28は、n−ウェル117を覆う。N+拡散20は、他の位置でNMOSソース/ドレイン拡散をもたらし、ここで、ウェルが接地に結合されることを可能にする。ゲート30が正の供給電圧Vddに結合される場合、キャリアは、ゲート誘電体28とn−ウェル17との界面に蓄積する。この構造は、前に検討したように、誘電体28の有効な厚みに反比例して変化する(誘電体28の)単位領域あたりのキャパシタンスをもたらす。誘電体28に異なる材料を使用すると、リークと固有のキャパシタンスとの正確な関係を変化する可能性があるが、所定の薄膜構造タイプについて、誘電体28のより薄いバージョンは、より高いキャパシタンスおよびより高いリークをもたらす。

【0021】

様々な実施形態によれば、条件付きのみで起動される能動回路領域の第1の部分と、チップが起動される場合は常に起動される能動回路領域の他の部分と、を含み、第1の部分は、主に第1のタイプである減結合コンデンサを含むが、他の部分はこれを含まず、他の部分は、主に第2のタイプである減結合コンデンサを含むが、第1の部分はこれを含まず、第1のタイプのコンデンサは、第2のタイプのコンデンサより高い固有のキャパシタンスおよび領域当たりより高いリーク電流を有する集積回路が提供される。

【0022】

様々な実施形態によれば、条件付きのみで起動される能動回路領域の第1の部分と、チップが起動される場合は常に起動される能動回路領域の他の部分と、を含み、第1の部分は、主に領域最適化された減結合コンデンサを含むが、他の部分はこれを含まず、他の部分は、リーク最適化された減結合コンデンサを主に含むが、第1の部分はこれを含まない集積回路が提供される。

【0023】

様々な実施形態によれば、条件付きのみで起動される第1の部分と、電源遮断状態からチップが起動される場合は常に、起動される能動回路領域の他の部分と、を含み、第1の部分および他の部分は、実質的に同一のゲート構造を有する対応する電界効果トランジスタを含み、第1の部分は、主に蓄積コンデンサでありゲート構造と実質的に同じ薄膜層を使用する減結合コンデンサを含むが、他の部分はこれを含まない集積回路が提供される。

【0024】

様々な実施形態によれば、ゲート電圧の第1の範囲用に最適化された第1の絶縁ゲートトランジスタを含む第1の領域と、第1の範囲のいずれの部分より高い数電圧を含む作動電圧の第2の範囲用に最適化された第2の絶縁ゲートトランジスタを含む第2の領域と、を含み、第1の領域は、条件付きのみで起動されるいくつかの部分と、第1の領域が起動される場合は常に起動される他の部分と、を含み、条件付きで起動される部分は、主に第1のタイプであり、第1のトランジスタと同じプロセスによって形成された減結合コンデンサを含み、他の部分は、主に、第1のタイプではない減結合コンデンサを含む集積回路が提供される。

【0025】

様々な実施形態によれば、チップ内の利用可能な場所に位置する複数のコンデンサを電源ラインに搭載するアクションを含み、コンデンサが条件付きのみで起動される領域に位置しないならば、最低電圧領域に位置するコンデンサのいくつかは、リーク最適化される集積回路において電気的ノイズを低減する方法が提供される。

【0026】

様々な実施形態によれば、チップ内の利用可能な場所に位置する複数のコンデンサを電源ラインに搭載するアクションを含み、コンデンサが条件付きのみで起動される領域に位置しないならば、最低電圧領域に位置するコンデンサのいくつかは、最も薄いゲート酸化物を使用せず、最低電圧領域に位置するコンデンサの少なくともいくつかは、チップ上で最低電圧絶縁ゲートトランジスタと同じゲート酸化物を使用する集積回路において電気的ノイズを低減する方法が提供される。

【0027】

様々な実施形態によれば、デュアル電圧パワーアイランドアーキテクチャにおける最適な減結合キャパシタンスのための方法およびシステムが提供される。2つの異なるタイプの蓄積コンデンサは、チップの低電圧領域において、コンデンサが常時オン状態の領域または条件付きで起動される領域に位置するかどうかに依存して、減結合に使用される。

【0028】

修正および変更

当業者に認識されるように、本願に記載された革新的概念は、出願の多大な範囲にわたって修正し変更することができ、従って、特許されるべき主題の範囲は、論じた特定の例示の教示のいずれによっても限定されない。それは、添付の特許請求の範囲の精神および広い範囲内にある代案、修正例および変更例をすべて包含することが意図される。

例えば、開示された発明は、3つ以上のゲート酸化物の厚みが利用可能なプロセスにおいてさらに有利とさえすることができ、そのような場合、前述したトレードオフは、指数関数的により改良することができる。

【0029】

以下の共同所有された同時係属米国特許出願も参照し、それらの特許出願のそれぞれおよび全ては、その全体が本願明細書において参照により援用されている。それらの特許出願とは、2006年12月31日に出願された米国仮特許出願第60/934,936号(特許文献3)、2006年12月31日に出願された米国仮特許出願第60/921,507号(特許文献4)、2006年12月31日に出願された米国仮特許出願第60/934,918号(特許文献5)、2006年12月31日に出願された米国仮特許出願第60/934,917号(特許文献6)、2006年12月31日に出願された第60/999,760号(特許文献7)、2006年12月31日に出願された米国仮特許出願第60/934,923号(特許文献8)、2007年1月1日に出願された米国仮特許出願第60/934,937号(特許文献2)、2007年1月1日に出願された米国仮特許出願第60/921,508号(特許文献1)、2006年12月31日に出願された米国特許出願第11/618,849号(特許文献9)、2006年12月31日に出願された米国特許出願第11/618,852号(特許文献10)、2006年12月31日に出願された米国特許出願第11/618,865号(特許文献11)、2006年12月31日に出願された米国特許出願第11/618,867号(特許文献12)、2006年12月31日に出願された米国特許出願第11/649,325号(特許文献13)、2006年12月31日に出願された米国特許出願第11/649,326号(特許文献14)、2007年12月28日に出願された米国特許出願第11/965,943号(特許文献15)、2007年12月28日に出願された米国特許出願第11/966,012号(特許文献16)、2007年12月28日に出願された米国特許出願第11/966,147号(特許文献17)である。これらの出願は、必ずしも本願と関係はないが、これらの多くが前述した考えと同じシステムに設計され、かつ/またはそれらの考えと相乗的に結合する特徴を示すことに役立つ。これらの同時係属出願中のいくつかは、本願と重複する発明を有している可能性があり、従って、米国特許法下で国内優先権の主張に適格である可能性があるが、優先権は現段階では必ずしも主張せず、または放棄しない。

【0030】

本願の記載のいずれも、いかなる特有の要素、工程または機能が特許請求の範囲に含まれていなければならない必須要素であることを意味することと解釈されない。特許されるべき主題の範囲は、特許登録された特許請求の範囲によってのみ定められる。さらに、「のための手段」という用語に分詞が続く場合を除いて、これらの特許請求の範囲のいずれも、米国特許法第112条6項を行使することは意図されない。

出願された特許請求の範囲は、可能な限り包括的であることが意図され、主題は、意図的に断念されたり、ゆだねられたり、放棄されない。

【技術分野】

【0001】

本願は、パワーアイランドを使用する低電力集積回路に関し、より詳細には、そのような回路における減結合キャパシタンスの実装に関する。

【0002】

他の出願への相互参照

2007年1月1日に出願された米国仮特許出願第60/921,508号(元は第11/618,912号と番号がつけられている)(特許文献1)および米国仮特許出願第60/934,937号(元は第11/618,913号と番号がつけられている)(特許文献2)の優先権を主張し、両者は、本願明細書において参照により援用されている。

【背景技術】

【0003】

減結合コンデンサは、チップの設計において頻繁に使用され、スイッチング中のノイズを低減する。電源と接地の間に接続されたコンデンサを含むフィラーセルが、ロジック領域において一般的に使用されている。電圧スケーリングが進歩し、デバイスが一時的過電圧により敏感になっているので、スイッチングノイズの制御がより望まれている。

しかし、矛盾する傾向は、低いオフ状態リークに対する要求である。減結合コンデンサは、簡単な蓄積コンデンサとして一般的に実装されている。深くスケーリングされたプロセスによってもたらされたゲート酸化物は、非常に高い固有のキャパシタンスを可能としながら、比較的高いリーク電流密度をもたらす。

ゲート酸化物のリーク密度は、現在好ましくないことに増加している。このように、プロセスがより小さな大きさにスケーリングし続けるので、減結合コンデンサへの従来のアプローチは、許容することができないリーク電流密度をもたらす。

【0004】

多くの携帯電子システムが、電池寿命によって決定的に制限されている。例えば、ユーザは、重い携帯電話を好まないが、ユーザは、電力を使い果たし、シャットダウンする携帯電話も好まない。電池寿命を改善する1つの方法は、携帯システムにおいて電子部品のエネルギー効率を増大させることである。携帯システムが動作中の場合の電力消費量は、電池寿命の重要な要素であるが、システムが待機している場合の電力消費量もやはり重要な要素である。

パワーアイランドは、低電力設計における共通の技術である。パワーアイランドは、停止動作または待機動作の間に必要な回路部分だけを起動しておくことによって、待機電流を低減するのに役立つ。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願第11/618,912号

【特許文献2】米国特許出願第11/618,913号

【特許文献3】米国仮特許出願第60/934,936号

【特許文献4】米国仮特許出願第60/921,507号

【特許文献5】米国仮特許出願第60/934,918号

【特許文献6】米国仮特許出願第60/934,917号

【特許文献7】米国仮特許出願第60/999,760号

【特許文献8】米国仮特許出願第60/934,923号

【特許文献9】米国特許出願第11/618,849号

【特許文献10】米国特許出願第11/618,852号

【特許文献11】米国特許出願第11/618,865号

【特許文献12】米国特許出願第11/618,867号

【特許文献13】米国特許出願第11/649,325号

【特許文献14】米国特許出願第11/649,326号

【特許文献15】米国特許出願第11/965,943号

【特許文献16】米国特許出願第11/966,012号

【特許文献17】米国特許出願第11/966,147号

【発明の概要】

【0006】

本発明者らは、チップの常時オン状態の部分と時々オン状態の部分との違いを考慮することにより、減結合コンデンサの最適化を実現することができることに気付いた。

本願は、減結合コンデンサに対する新しいアプローチを開示し、それは、特に、2つ(またはそれ以上)の酸化物の厚みが使用される集積回路に適用可能である(普通の高くスケーリングされた製品のままで)。例えば、より薄い有効なゲート酸化物は、一般的に、周辺回路よりコアロジックに使用され、これは、周辺回路にいくらかローバスト性を加えながら、コアロジックが最適にスケーリングされることを可能にする。

【0007】

本願は、パワーアイランドアーキテクチャが減結合コンデンサに新しい可能性を開くことを教示する。実施形態の1つの種類によれば、最も薄いゲート酸化物は、常に起動される位置ではなく条件付きで起動される位置でのみ、最低電圧領域内で減結合コンデンサに使用される。別の種類の実施形態によれば、条件付きで起動される位置の減結合コンデンサの一部またはすべてが密度最適化される一方で、常に起動される位置の減結合コンデンサは、リーク最適化される。別の種類の実施形態によれば、条件付きで起動される位置の減結合コンデンサの一部またはすべてが最低電圧ゲート酸化物層から形成される一方で、常に起動される位置の減結合コンデンサは、より高い電圧ゲート酸化物層から形成される。

【0008】

コアゲート酸化物の厚みは、一般的に、I/Oゲート酸化物の厚みよりも薄く、したがって、I/Oゲート酸化物の厚みよりも領域比に対してより良好なキャパシタンスをもたらす。しかし、ディープサブミクロン技術について、大量の電流が、ゲート酸化物を流れてもよい(直接トンネル)。より厚いI/Oゲート酸化物は、領域比に対して低いキャパシタンスを有するだけでなく、はるかに少ないゲート電流を使用する。桁違いのゲートリーク電流は、サブミクロン技術には珍しいことではない。

したがって、コア酸化物の厚みを有するコンデンサは、領域比に対してより良好なキャパシタンスを有するが、より高いゲートリーク電流を有する。I/O酸化物の厚みで形成されたコンデンサは、領域比に対してより低いキャパシタンスを有するがはるかに低いゲートリーク電流を有する。

【0009】

開示された革新は、様々な実施形態において、少なくとも次の利点の1つ以上をもたらす。

・低減された電力消費量

・より大きな密度

・より良好なノイズ抑制

・蓄積コンデンサを今もなお使用することができる

・特別のデバイス構造は減結合コンデンサに必要ではない

・より良好な信頼性

【0010】

開示された発明は、添付の図面を参照して説明され、発明の重要なサンプルの実施形態を示し、本願明細書において参照により援用されている。

【図面の簡単な説明】

【0011】

【図1】好ましい実施形態による異なる種類の蓄積コンデンサを使用する異なる領域を含む集積回路の例を示す。

【図2】以下に検討される異なる位置で、2つの異なるバージョンで使用することができる蓄積コンデンサの構造の一例を示す。

【発明を実施するための形態】

【0012】

本願の多数の革新的な教示が、この好ましい実施形態を特別に参照して記載される(例を目的とし限定を目的としない)。

【0013】

減結合コンデンサが、チップの設計において頻繁に使用され、スイッチング中にノイズを低減する。電源と接地の間に接続されたコンデンサを含むフィラーセルが、ロジック領域において一般的に使用される。

少なくとも2つの酸化物の厚みが、サブミクロン製品を製造するために一般的に使用される。コアに使用される酸化物の厚みとIO回路用の酸化物の厚みである。減結合コンデンサは、異なる特性を生じる一方の酸化物の厚みから生成することができる。

コアゲート酸化物の厚みは、IOゲート酸化物の厚みよりも一般的に薄く、このようにして、IOの厚みより領域比に対してより良好なキャパシタンスをもたらす。しかし、ディープサブミクロン技術について、大量の電流が、ゲート酸化物を通って流れる可能性がある(直接トンネル)。

【0014】

トンネル電流が、障壁高さにかかわらず障壁厚みの減少とともに指数関数的であることに留意することが重要である。したがって、ゲート電流密度は、さらなるスケーリングとともに過度に悪化する可能性がある。

IO回路で使用されるより厚いゲート酸化物は、領域比で低いキャパシタンスを有するだけでなく、はるかに少ないゲート電流を使用する。桁違いのゲートリーク電流は、サブミクロン技術に珍しいことではない。

【0015】

多くの現代の低電力設計は、パワーアイランドを使用する。パワーアイランドの目的の1つは、停止動作または待機動作の間に必要な回路部のみが起動された状態とすることによって待機電流を低減することである。

ゲート電流、したがって、パワーアイランドを使用する所定の製品の待機電流を最小限にするために、より厚いゲート酸化物を使用して、待機動作中に起動される回路部分に減結合コンデンサを形成する。より薄いゲート酸化物コンデンサは、待機中に電源が切られる回路部分で使用することができる。この戦略は、ASIC設計者が、待機中に電源が切られる部分におけるチップ領域当たりのキャパシタンスを最も効率的に使用しながら、待機中に電源が入れられる部分におけるリーク電流を最小限にすることを可能にする。

【0016】

これらの減結合コンデンサのサンプル実施例を、本願明細書で「トリポリ」と称するチップ設計との関連で以下に説明する。0.13μmのトランジスタ技術を使用するトリポリ実施例では、N−ウェル蓄積コンデンサが使用された(n−ウェルの内側のN+がドープされたポリおよびソースおよびドレイン)。

I/O酸化物コンデンサについて、1nFは、5.1nAのみのゲートリーク電流で約300Kμm2 の領域を使用する。コア酸化物コンデンサについて、1nFは、2.25μAのゲートリーク電流を使用しながら、約150Kμm2 の領域を使用する。領域が半分だけ低減されるが、リーク電流は、約400の係数を掛けられることに留意するべきである。

【0017】

様々な領域のフィラーセルは、キャパシタンス内蔵で作成された。コア設計およびI/O酸化物コンデンサ設計の両方は、これらのフィラーセル内で作成された。CADソフトウェアは、次いで、チップまわりで減結合キャパシタンスフィラーセルを分配するために使用された。

特定のフィラーセルの位置は、それらの位置が設計者にとって重要なことではないため説明されない。すなわち、フィラーセルは、低レベルの仕様書に挿入され、人間の設計者

の決定とは強い関係がない。同様の理由で、いかなるコンデンサも従来の蓄積コンデンサと同じであるので、任意の個々のコンデンサのデバイスレベルの詳細は特に重要ではない。同様に、個々のフィラーセルは、従来のセルと大きく異ならず、前述したように、セルタイプとセル位置との関連性が、驚くべき利点をもたらす。

【0018】

図1は、好ましい実施形態による、異なる種類の蓄積コンデンサを使用する異なる領域を含む集積回路の例を示す。この図では、個々のブロックの回路動作は、詳細に検討されないが、電源接続は、開示された概念の適用を示すことに有用である。

この図において、「クリプトエンジン」と称する右端の最上部のブロックは、条件付きのみで起動される低電圧コアブロックの例である。図に示されたASICでは、クリプトエンジンは、大量の領域を消費し、さらに、多くのゲートを含み、迅速な計算を可能にする。このブロックは、必要に応じてのみ起動され、チップの合計領域の大部分を消費するので、このブロックは、最も密度の高い結合コンデンサを使用する。

【0019】

「USB PHY」と称する中央上部ブロックは、最も薄いゲート酸化物を使用しないIO(周辺)ブロックである。したがって、このブロックは、いかなる場合にも最も薄い結合コンデンサに適切ではない。

下側中心部の小さな白いブロックは、より大きな灰色ブロック内に埋め込まれ、「クリプト1用のNVM」と称され、常時オンの低電圧コアブロックの例である。このブロックは、条件付きで起動されないので、より薄い酸化物(密度最適化)コンデンサを受けないが、その代りにより厚い酸化物リーク最適化コンデンサを受ける。

したがって、これらの3つのブロックは、ともに、適切なキャパシタンスが好ましい実施形態によって選択される方法を説明する。

【0020】

図2は、以下に検討される異なる位置で、2つの異なるバージョンで使用することができる蓄積コンデンサの構造の一例を示す。ゲート30(例えば、ポリシリコン上のシリサイド)は、ゲート誘電体28(例えば、SiO2 、またはその代わりに、higher−k誘電体)を覆い、ゲート誘電体28は、n−ウェル117を覆う。N+拡散20は、他の位置でNMOSソース/ドレイン拡散をもたらし、ここで、ウェルが接地に結合されることを可能にする。ゲート30が正の供給電圧Vddに結合される場合、キャリアは、ゲート誘電体28とn−ウェル17との界面に蓄積する。この構造は、前に検討したように、誘電体28の有効な厚みに反比例して変化する(誘電体28の)単位領域あたりのキャパシタンスをもたらす。誘電体28に異なる材料を使用すると、リークと固有のキャパシタンスとの正確な関係を変化する可能性があるが、所定の薄膜構造タイプについて、誘電体28のより薄いバージョンは、より高いキャパシタンスおよびより高いリークをもたらす。

【0021】

様々な実施形態によれば、条件付きのみで起動される能動回路領域の第1の部分と、チップが起動される場合は常に起動される能動回路領域の他の部分と、を含み、第1の部分は、主に第1のタイプである減結合コンデンサを含むが、他の部分はこれを含まず、他の部分は、主に第2のタイプである減結合コンデンサを含むが、第1の部分はこれを含まず、第1のタイプのコンデンサは、第2のタイプのコンデンサより高い固有のキャパシタンスおよび領域当たりより高いリーク電流を有する集積回路が提供される。

【0022】

様々な実施形態によれば、条件付きのみで起動される能動回路領域の第1の部分と、チップが起動される場合は常に起動される能動回路領域の他の部分と、を含み、第1の部分は、主に領域最適化された減結合コンデンサを含むが、他の部分はこれを含まず、他の部分は、リーク最適化された減結合コンデンサを主に含むが、第1の部分はこれを含まない集積回路が提供される。

【0023】

様々な実施形態によれば、条件付きのみで起動される第1の部分と、電源遮断状態からチップが起動される場合は常に、起動される能動回路領域の他の部分と、を含み、第1の部分および他の部分は、実質的に同一のゲート構造を有する対応する電界効果トランジスタを含み、第1の部分は、主に蓄積コンデンサでありゲート構造と実質的に同じ薄膜層を使用する減結合コンデンサを含むが、他の部分はこれを含まない集積回路が提供される。

【0024】

様々な実施形態によれば、ゲート電圧の第1の範囲用に最適化された第1の絶縁ゲートトランジスタを含む第1の領域と、第1の範囲のいずれの部分より高い数電圧を含む作動電圧の第2の範囲用に最適化された第2の絶縁ゲートトランジスタを含む第2の領域と、を含み、第1の領域は、条件付きのみで起動されるいくつかの部分と、第1の領域が起動される場合は常に起動される他の部分と、を含み、条件付きで起動される部分は、主に第1のタイプであり、第1のトランジスタと同じプロセスによって形成された減結合コンデンサを含み、他の部分は、主に、第1のタイプではない減結合コンデンサを含む集積回路が提供される。

【0025】

様々な実施形態によれば、チップ内の利用可能な場所に位置する複数のコンデンサを電源ラインに搭載するアクションを含み、コンデンサが条件付きのみで起動される領域に位置しないならば、最低電圧領域に位置するコンデンサのいくつかは、リーク最適化される集積回路において電気的ノイズを低減する方法が提供される。

【0026】

様々な実施形態によれば、チップ内の利用可能な場所に位置する複数のコンデンサを電源ラインに搭載するアクションを含み、コンデンサが条件付きのみで起動される領域に位置しないならば、最低電圧領域に位置するコンデンサのいくつかは、最も薄いゲート酸化物を使用せず、最低電圧領域に位置するコンデンサの少なくともいくつかは、チップ上で最低電圧絶縁ゲートトランジスタと同じゲート酸化物を使用する集積回路において電気的ノイズを低減する方法が提供される。

【0027】

様々な実施形態によれば、デュアル電圧パワーアイランドアーキテクチャにおける最適な減結合キャパシタンスのための方法およびシステムが提供される。2つの異なるタイプの蓄積コンデンサは、チップの低電圧領域において、コンデンサが常時オン状態の領域または条件付きで起動される領域に位置するかどうかに依存して、減結合に使用される。

【0028】

修正および変更

当業者に認識されるように、本願に記載された革新的概念は、出願の多大な範囲にわたって修正し変更することができ、従って、特許されるべき主題の範囲は、論じた特定の例示の教示のいずれによっても限定されない。それは、添付の特許請求の範囲の精神および広い範囲内にある代案、修正例および変更例をすべて包含することが意図される。

例えば、開示された発明は、3つ以上のゲート酸化物の厚みが利用可能なプロセスにおいてさらに有利とさえすることができ、そのような場合、前述したトレードオフは、指数関数的により改良することができる。

【0029】

以下の共同所有された同時係属米国特許出願も参照し、それらの特許出願のそれぞれおよび全ては、その全体が本願明細書において参照により援用されている。それらの特許出願とは、2006年12月31日に出願された米国仮特許出願第60/934,936号(特許文献3)、2006年12月31日に出願された米国仮特許出願第60/921,507号(特許文献4)、2006年12月31日に出願された米国仮特許出願第60/934,918号(特許文献5)、2006年12月31日に出願された米国仮特許出願第60/934,917号(特許文献6)、2006年12月31日に出願された第60/999,760号(特許文献7)、2006年12月31日に出願された米国仮特許出願第60/934,923号(特許文献8)、2007年1月1日に出願された米国仮特許出願第60/934,937号(特許文献2)、2007年1月1日に出願された米国仮特許出願第60/921,508号(特許文献1)、2006年12月31日に出願された米国特許出願第11/618,849号(特許文献9)、2006年12月31日に出願された米国特許出願第11/618,852号(特許文献10)、2006年12月31日に出願された米国特許出願第11/618,865号(特許文献11)、2006年12月31日に出願された米国特許出願第11/618,867号(特許文献12)、2006年12月31日に出願された米国特許出願第11/649,325号(特許文献13)、2006年12月31日に出願された米国特許出願第11/649,326号(特許文献14)、2007年12月28日に出願された米国特許出願第11/965,943号(特許文献15)、2007年12月28日に出願された米国特許出願第11/966,012号(特許文献16)、2007年12月28日に出願された米国特許出願第11/966,147号(特許文献17)である。これらの出願は、必ずしも本願と関係はないが、これらの多くが前述した考えと同じシステムに設計され、かつ/またはそれらの考えと相乗的に結合する特徴を示すことに役立つ。これらの同時係属出願中のいくつかは、本願と重複する発明を有している可能性があり、従って、米国特許法下で国内優先権の主張に適格である可能性があるが、優先権は現段階では必ずしも主張せず、または放棄しない。

【0030】

本願の記載のいずれも、いかなる特有の要素、工程または機能が特許請求の範囲に含まれていなければならない必須要素であることを意味することと解釈されない。特許されるべき主題の範囲は、特許登録された特許請求の範囲によってのみ定められる。さらに、「のための手段」という用語に分詞が続く場合を除いて、これらの特許請求の範囲のいずれも、米国特許法第112条6項を行使することは意図されない。

出願された特許請求の範囲は、可能な限り包括的であることが意図され、主題は、意図的に断念されたり、ゆだねられたり、放棄されない。

【特許請求の範囲】

【請求項1】

集積回路であって、

条件付きのみで起動される能動回路領域の第1の部分と、

集積回路が起動される場合は常に起動される能動回路領域の他の部分と、を備え、

前記第1の部分は、主に第1のタイプである減結合コンデンサを含むが、前記他の部分はそのような減結合コンデンサを含まず、

前記他の部分は、主に第2のタイプである減結合コンデンサを含むが、前記第1の部分はそのような減結合コンデンサを含まず、

前記第1のタイプのコンデンサは、前記第2のタイプのコンデンサよりも高い固有のキャパシタンスおよび領域当たりより高いリーク電流を有する集積回路。

【請求項2】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともに半導体領域を覆う導体および絶縁層を有し、

前記第1のタイプのコンデンサは、前記第2のタイプのコンデンサよりも薄い絶縁層を有する集積回路。

【請求項3】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともにMOSコンデンサである集積回路。

【請求項4】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともに蓄積コンデンサである集積回路。

【請求項5】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともにn−ウェルに対するMOSコンデンサである集積回路。

【請求項6】

集積回路であって、

条件付きのみで起動される能動回路領域の第1の部分と、

集積回路が起動される場合は常に起動される能動回路領域の他の部分と、を備え、

前記第1の部分は、主に領域最適化された減結合コンデンサを含むが、前記他の部分はそのような減結合コンデンサを含まず、

前記他の部分は、リーク最適化された減結合コンデンサを主に含むが、前記第1の部分はそのような減結合コンデンサを含まない集積回路。

【請求項7】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともに半導体領域を覆う導体および絶縁層を有し、

前記領域最適化されたコンデンサは、前記リーク最適化されたコンデンサよりも薄い絶縁層を有する集積回路。

【請求項8】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともにMOSコンデンサである集積回路。

【請求項9】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともにn−ウェルに対するMOSコンデンサである集積回路。

【請求項1】

集積回路であって、

条件付きのみで起動される能動回路領域の第1の部分と、

集積回路が起動される場合は常に起動される能動回路領域の他の部分と、を備え、

前記第1の部分は、主に第1のタイプである減結合コンデンサを含むが、前記他の部分はそのような減結合コンデンサを含まず、

前記他の部分は、主に第2のタイプである減結合コンデンサを含むが、前記第1の部分はそのような減結合コンデンサを含まず、

前記第1のタイプのコンデンサは、前記第2のタイプのコンデンサよりも高い固有のキャパシタンスおよび領域当たりより高いリーク電流を有する集積回路。

【請求項2】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともに半導体領域を覆う導体および絶縁層を有し、

前記第1のタイプのコンデンサは、前記第2のタイプのコンデンサよりも薄い絶縁層を有する集積回路。

【請求項3】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともにMOSコンデンサである集積回路。

【請求項4】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともに蓄積コンデンサである集積回路。

【請求項5】

請求項1記載の集積回路において、

前記第1のタイプのコンデンサおよび前記第2のタイプのコンデンサは、ともにn−ウェルに対するMOSコンデンサである集積回路。

【請求項6】

集積回路であって、

条件付きのみで起動される能動回路領域の第1の部分と、

集積回路が起動される場合は常に起動される能動回路領域の他の部分と、を備え、

前記第1の部分は、主に領域最適化された減結合コンデンサを含むが、前記他の部分はそのような減結合コンデンサを含まず、

前記他の部分は、リーク最適化された減結合コンデンサを主に含むが、前記第1の部分はそのような減結合コンデンサを含まない集積回路。

【請求項7】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともに半導体領域を覆う導体および絶縁層を有し、

前記領域最適化されたコンデンサは、前記リーク最適化されたコンデンサよりも薄い絶縁層を有する集積回路。

【請求項8】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともにMOSコンデンサである集積回路。

【請求項9】

請求項6記載の集積回路において、

前記領域最適化されたコンデンサおよび前記リーク最適化されたコンデンサは、ともにn−ウェルに対するMOSコンデンサである集積回路。

【図1】

【図2】

【図2】

【公開番号】特開2012−119702(P2012−119702A)

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願番号】特願2012−5216(P2012−5216)

【出願日】平成24年1月13日(2012.1.13)

【分割の表示】特願2009−544322(P2009−544322)の分割

【原出願日】平成19年12月31日(2007.12.31)

【出願人】(506197901)サンディスク コーポレイション (175)

【Fターム(参考)】

【公開日】平成24年6月21日(2012.6.21)

【国際特許分類】

【出願日】平成24年1月13日(2012.1.13)

【分割の表示】特願2009−544322(P2009−544322)の分割

【原出願日】平成19年12月31日(2007.12.31)

【出願人】(506197901)サンディスク コーポレイション (175)

【Fターム(参考)】

[ Back to top ]