2つの自己整合型独立ゲートを有するメモリの製作

【課題】並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法を提供する。

【解決手段】支持体上にある、少なくとも1つの第1のゲート材料に基づく層内に、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階aと、前記所与のスペース内に、少なくとも1つの絶縁層および少なくとも1つの第2のゲート材料を含むスタックを形成する段階であって、前記スペース内に位置する前記ゲート材料が、第1のブロックから前記絶縁層だけ隔たった第2のゲートブロックを形成するように意図されている段階bと、前記犠牲ブロックを除去する段階cとを含む方法。

【解決手段】支持体上にある、少なくとも1つの第1のゲート材料に基づく層内に、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階aと、前記所与のスペース内に、少なくとも1つの絶縁層および少なくとも1つの第2のゲート材料を含むスタックを形成する段階であって、前記スペース内に位置する前記ゲート材料が、第1のブロックから前記絶縁層だけ隔たった第2のゲートブロックを形成するように意図されている段階bと、前記犠牲ブロックを除去する段階cとを含む方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、マイクロエレクトロニクスの分野に関し、詳細にはメモリの分野に関する。

【0002】

本発明は、並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクスデバイスを製作する方法に関する。本方法は、不揮発性メモリデバイスの製造に顕著に適用される。

【0003】

本発明は、並置されたゲートの位置決め精度の向上をもたらす。このことは、こうしたゲートを備えた不揮発性メモリの電気的性能の向上として表される。

【背景技術】

【0004】

電力供給なしに情報を保持する能力がある消去可能なメモリデバイスは、不揮発性メモリと呼ばれている。

【0005】

理想的には、次の特徴、すなわち電気的書込みおよび消去の可能性、ビット当たりの低嵩高性および低コスト、ランダムアクセス、短い書込みおよび読出し時間、良好な耐久性、さらに低消費電力および低電源電圧を兼ね備えることになる不揮発性メモリの適用が求められる。

【0006】

フラッシュメモリを用いると、上記基準のすべての間で良い妥協を得ることが可能である。

【0007】

フラッシュメモリは、「ブロック」、「セクタ」または、「ページ」と呼ばれる多数のメモリセルを電気的に同時に消去しうる一方、メモリセルを個別に電気的にプログラムしうる不揮発性メモリである。

【0008】

フラッシュメモリは、EPROMメモリの低嵩高性要件およびEEPROMメモリの電気的に消去可能であるという要件の両方を兼ね備えている。

【0009】

大部分の不揮発性メモリは、浮遊ゲートと呼ばれる、電荷を蓄積する場所を含む構造を備える。

【0010】

MONOS(MONOSは「Metal Oxide Nitride Oxide Silicon(金属 酸化物 窒化物 酸化物 シリコン)」の略)タイプの不揮発性メモリデバイスが出現し、ポリシリコン中の従来の浮遊ゲート構造に取って代わっている。MONOSタイプのメモリでは、電荷は窒化シリコン電荷トラップ層内に蓄積される。

【0011】

メモリトランジスタおよび選択トランジスタの両方を備える「分離ゲート」と呼ばれるメモリ構造もまた出現している。「分離ゲート」タイプのメモリは、一般に、選択トランジスタの適用を必要とする機構によってプログラムされる。なお、選択トランジスタのゲートは、メモリトランジスタのゲートに隣接して置かれている。

【0012】

こうした構造により、プログラミングレートの向上および消費電力の低減を得ることが可能である。

【0013】

これらのメモリを適用する上での困難の1つは、ゲート相互の位置決め精度に関連する。ゲートは、一般に連続フォトリソグラフィで作られる。並置されたゲート相互の位置の制御が不十分であると、メモリトランジスタの電気特性の制御が不十分になり、したがってメモリの性能の制御が不十分になることが生じる。

【0014】

「分離ゲート」と呼ばれるメモリ構造を適用するときは、並置されたゲートの位置の正確な制御が必要になる。

【0015】

米国特許第7,130,233号では、スペーサの形状に類似の丸みのある形状を有し、他のゲートに隣接して置かれた平行六面体ゲートを備えるトランジスタメモリ記憶デバイスを作る方法が開示されている。

【0016】

丸みのあるプロファイルを有するこうしたゲートを備えるデバイスを作ると、コンタクトを画定する際に著しく、ゲート寸法精度の問題が生じる。

【0017】

ゲートの正確な位置決めおよびゲートパターンの正確な画定を伴って、並置されたゲートを有するトランジスタを備えるメモリデバイスを作る、新規な方法を見つけるという問題がもたらされる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許第7,130,223号

【発明の概要】

【課題を解決するための手段】

【0019】

本発明は、並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法に関し、その方法は、

a)支持体上に置かれた第1のゲート材料に基づく層内に、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階と、

b)絶縁層および第2のゲート材料を含むスタックで前記の所与のスペースを埋め、前記スペース内の前記第2のゲート材料が、前記絶縁層により第1のブロックから隔てられた他のゲートブロックを形成する段階と、

c)前記犠牲ブロックを除去する段階と、を含む。

【0020】

それによって、制御された寸法を有する2つの独立なゲートを備えるメモリを作りうる。

【0021】

ゲートブロックおよび犠牲ブロックは、段階a)で作り、この段階でこれらのブロック間の空きのスペースの寸法を制御することが可能であり、段階b)でこの空きスペース内に他のゲートのブロックを形成する。

【0022】

本発明によれば、本方法は、段階a)の前に、

−前記第1のゲート材料に基づく層の上にジブロック共重合体に基づくマスキング層を形成する段階と、

−ジブロック共重合体に基づくマスキング層において、少なくとも1つの所与のマスキングパターン、および前記所与のパターンの所与の距離だけ隔たれた少なくとも1つの他の所与のマスキングパターンを保持するために、前記ジブロック共重合体を形成するポリマーに基づくブロックを選択的に除去する段階であって、前記マスキングパターンは前記ジブロック共重合体を形成する他のポリマーに基づいている段階と、をさらに含み、

前記第1のゲートブロックおよび前記犠牲ブロックは、前記所与のパターンおよび前記他の所与のパターンを介して、前記第1のゲート材料の前記層をエッチングすることにより、段階a)で形成される。

【0023】

それを介して第1のゲート材料をエッチングすることになるマスクキングパターンを形成するためにジブロック共重合体を用いることにより、前記第1のゲートブロックの位置決めは、前記第1のゲート材料内に形成された前記犠牲ブロックおよび前記他のゲートブロックに対して正確に制御しうる。それによって、前記所与のスペースは、正確に制御され、したがって、前記所与のスペースを埋めることによって形成されるゲートの寸法決めは正確に制御される。

【0024】

また、第1のゲート材料内に形成される犠牲ブロックの位置決めを正確に制御する。

【0025】

犠牲ブロックの精密な位置決めにより、本方法の後の段階で、このマスクの位置決めへの制約をより少なく保ちながら、マスクを介してエッチングすることで、これらのブロックを除去することが可能となりうる。

【0026】

ジブロック共重合体を用いると、小さいサイズの、例えば15nm程度のゲートを作ることもまた可能である。

【0027】

所与のパターンおよび前記他の所与のパターンは、平行六面体の形状を有しうる。

【0028】

ジブロック共重合体は、次の材料、PS−b−PMMAまたはPS−b−PIまたはPS−b−PBのうちから1つ選ばれうる。

【0029】

可能な適用例によれば、絶縁層は、少なくとも1つの誘電体層および少なくとも1つの電荷蓄積層を含む層のスタックで形成されうる。

【0030】

スタックは、例えば、

−少なくとも1つの第1の誘電材料層、

−前記第1の誘電材料層上に形成された少なくとも1つの電荷蓄積層、

−前記電荷蓄積層上に形成された少なくとも1つの第2の誘電材料層で形成された3層でありうる。

【0031】

段階b)は、

−前記第1のゲート材料の前記ブロック上への前記絶縁層のコンフォーマブルな堆積段階と、

−前記所与のスペースを埋めるための、前記第2のゲート材料の堆積段階と、を含む。

【0032】

可能な一実施例では、本方法は、段階b)と段階c)との間に、

−前記第1のゲートブロックおよび前記第2のゲートブロックを覆う少なくとも1つのマスクを、第1のゲートブロックのある側の犠牲ブロックの一部を覆い、前記所与の距離l2未満の所定の距離Δだけ第1のゲートブロックの他の側を越えて延在するように形成する段階と、

−マスクを介して、第2のゲート材料、絶縁層、および場合によりハードマスク層の連続エッチング段階と、を含むことができる。

【0033】

次いで犠牲ブロックは、段階c)で前記マスクを介してのエッチングで除去されうる。

【0034】

このようなマスクを用いると、ずれ公差は従来技術の方法よりも大きくなる。この公差は、形成を望むゲートの寸法に依存する。

【0035】

本方法の可能な一実施例では、第1のゲート材料に基づく層は、前記支持体上に形成されたゲート誘電体層上に形成しうる。次いでジブロック共重合体層は、前記第1のゲート材料層上に形成されたハードマスク層上に形成しうる。

【0036】

段階a)でのエッチングは、ハードマスクを介して実現され、本方法は、段階a)と段階b)との間に、前記ハードマスクを介してのエッチングによる、第1のブロックと前記犠牲ブロックとの間のゲート誘電体層の除去をさらに含む。

【0037】

ハードマスク層は、段階a)で第1のゲート材料ブロックを保護するためと、エッチングマスクとしての両方で役立つことができる。

【0038】

可能な適用例によれば、本方法は、段階b)と段階c)との間に、

−前記第2のゲートブロックを覆った状態で、前記第1のゲートブロック上に、および犠牲ブロックの一部上にある、少なくとも1つのマスクの形成と、

−マスクを介して、第2のゲート材料、絶縁層、およびハードマスク層の連続エッチングと、を含み、

犠牲ブロックが、段階c)で前記マスクを介するエッチングにより除去される。

【0039】

本方法は、段階c)後に、

−前記マスクを除去する段階と、

−絶縁層を、前記第1のブロックと前記他のゲートブロックとの間および前記他のゲートブロックの下にそのまま残して、部分的に除去する段階と、をさらに含みうる。

【0040】

1つの可能性によれば、段階a)は、前記支持体上にある前記第1のゲート材料に基づく前記層内への、少なくとも1つの第2のトランジスタゲートブロックの形成を含みうる。ここで、前記第2のブロックおよび前記犠牲ブロックは、他の所与のスペースだけ隔てられ、前記犠牲ブロックは、前記第1のブロックと前記第2のゲートブロックとの間に位置している。この場合、段階b)は、前記他の所与のスペース内への、前記絶縁層および前記第2のゲート材料を含む前記スタックの形成を含みうる。ここで、前記他のスペース内に位置している前記ゲート材料は、前記第2のブロックに隣接して配置され、前記第2のブロックから前記絶縁層だけ隔てられたゲートブロックを形成する。

【0041】

本方法の可能な適用例によれば、第1のゲートブロックに隣接して配置された前記他のゲートブロックは、第1のメモリ記憶トランジスタのゲートブロックであり、第2のゲートブロックに隣接して配置された前記ゲートブロックは、第2のメモリ記憶トランジスタのゲートブロックであり、前記他のゲートブロックに並置される。本方法は、第1のメモリ記憶トランジスタと前記第2のメモリ記憶トランジスタとの間への共通コンタクト領域の形成をさらに含む。

【0042】

それによって、ソース線が2つの隣接するメモリトランジスタのソースに共通であるデバイス、例えばNORフラッシュメモリセルなどが作られうる。

【0043】

本発明は、添付の図面を参照して、純粋に指示のためであり、決して制限するものではないが、所与の例示的な実施形態の説明を読むと、より良く理解されよう。

【図面の簡単な説明】

【0044】

【図1A】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1B】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1C】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1D】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1E】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1F】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1G】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1H】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1I】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1J】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1K】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1L】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1M】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1N】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1O】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1P】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図2A】並置されたゲートを有するトランジスタのいくつかの対が、同時に作られる代替の実施形態を示す図である。

【図2B】並置されたゲートを有するトランジスタのいくつかの対が、同時に作られる代替の実施形態を示す図である。

【図3A】並置されたゲートを有するトランジスタのいくつかの対が作られ、トランジスタの各対がメモリトランジスタを備え、メモリトランジスタが配置され、共通ソース電位に設定されうるように対が配置されている、例示的な方法の代替方法を示す図である。

【図3B】並置されたゲートを有するトランジスタのいくつかの対が作られ、トランジスタの各対がメモリトランジスタを備え、メモリトランジスタが配置され、共通ソース電位に設定されうるように対が配置されている、例示的な方法の代替方法を示す図である。

【図4A】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図4B】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図4C】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図5A】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5B】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5C】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5D】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5E】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【0045】

別々の図の同一、類似または等価の部分は、ある図から他の図への移行を容易にするために、同じ参照番号を有する。

【0046】

図面の中に示されている別々の部分は、図面をより読みやすくするために、必ずしも均一の尺度で図示しているわけではない。

【発明を実施するための形態】

【0047】

ここで、並置されたゲートを備えるトランジスタを有するマイクロエレクトロニクスデバイスを作る、本発明による例示的な方法を図1A〜図1Pと関連付けて提示する。マイクロエレクトロニクスデバイスは、不揮発性メモリセル、例えばフラッシュメモリなどでありうる。

【0048】

第一に、支持体100上にその支持体100上にある絶縁層102中に窪み103を作る。窪み103は、例えば矩形の形状を有してよく、例えば通例「浅いトレンチ分離」と呼ばれている方法で作りうる。絶縁層102は、例えばSiO2に基づきうる。窪み103は、例えば1μm程度の限界寸法dcで作りうる。(ここで、寸法は、支持体100および図1A中で定義された直交基準系

【0049】

【数1】

【0050】

のベクトル

【0051】

【数2】

【0052】

に平行な方向に測る。)「限界寸法」とは、1つの層または層のスタック内に作られたパターンの、高さすなわち厚さを除く最小寸法を指す。窪み103は、そこに1つまたは複数の活性トランジスタ領域を作ることを意図した半導体領域101に面して形成する(図1A)。

【0053】

次に(図1B)、第1のタイプのトランジスタ、例えばメモリセルを選択またはアクセスするためのトランジスタの1つまたは複数のゲートを作るためにゲートスタックを形成する。ゲートスタックは、誘電体ゲート層107を含む。この誘電体ゲート層107は、例えば半導体領域101の熱酸化で作りうる。誘電体ゲート層107は、例えば5nm程度の厚さを有しうる。また、ゲートスタックは、誘電体層107上にゲート材料109の層、例えば、N型ドーピングによりドープされうるポリシリコンの層を含む。ゲート材料109の層は、例えば100ナノメートルの厚さを有しうる(図1B)。

【0054】

次いで(図1C)、例えば、SiO2または、HfO2または、Al2O3に基づくハードマスク層113をゲート材料109の層上に形成する。

【0055】

ハードマスク層113は、ゲート材料109の層に対するその後のエッチング中にゲート材料109の層を保護するために使いうる。

【0056】

ハードマスク層113上にOHサイトを作り出すようにハードマスク層113の表面を下処理する段階は、例えば、ハードマスク層113がSiO2から成るときには、HFで処理することにより達成することができる。

【0057】

次いで、第1のポリマー115に基づく限界寸法l1の複数のブロック114および他のポリマー117に基づく限界寸法l2の複数のブロック116を含むマスキング層を窪み103中に作る(それぞれの限界寸法l1、l2は、図1D中で定義された直交基準系

【0058】

【数3】

【0059】

のベクトル

【0060】

【数4】

【0061】

に平行な方向に測る)。ブロック114および116の寸法l1、l2は、メモリデバイスのゲートを形成することが望ましい寸法に応じて与え、それぞれ、メモリデバイスの少なくとも1つの第1のゲートおよび少なくとも1つの第2のゲートに与えられた寸法に等しくなりうる。寸法l1、l2は、例えば15ナノメートルから40ナノメートルの間に含まれうる。

【0062】

マスキング層は、ブロック共重合体材料に基づいてよく、具体的にはジブロック共重合体材料を使用する。ジブロック共重合体材料は、相互結合した、異なる化学的性質の2つのポリマー115および117の組合せを含む材料であり、それらの分布は、規則的な周期構造に応じて作られる。

【0063】

この規則的な周期分布は、規則的な分布を有するマスクのパターンを形成するために使用する。

【0064】

可能な適用例によれば、ブロック114、116は、平行六面体の形状を有し、相互に平行であるように作りうる。

【0065】

ハードマスク層113の表面処理により、共重合体ブロックの組織化を容易にすることができる。

【0066】

平行六面体ブロックを得るために、ジブロック共重合体の組成を制御しうる。例えば、その組成が、50%程度のポリマーブロック115および50%程度のポリマーブロック117から成ると、図1Dに示すように、平行六面体ラメラへと共重合体の組織化を導く。

【0067】

ジブロック共重合体材料は、例えばPS−b−PMMA(ポリスチレン−b−ポリメチルメタクリレート)またはPS−b−PI(ポリスチレン−b−ポリイソプレン)またはPS−b−PB(ポリスチレン−b−ポリブタジエン)でありうる。

【0068】

ジブロック共重合体材料がPS−b−PMMAである場合、PS−b−PMMAは0.3程度の体積分率、67,100gmol−1程度の重量モル質量、および1.09の多分子性指数を有しうる。ジブロック共重合体鎖は、例えば1重量%程度の濃度を得るためにトルエンの溶液中に希釈しうる。次いでスピンナを用いて、例えば3,000rpm(回転数/分)程度の速度、1,000(回転数/分)s−1の加速度、および例えば30s程度の継続時間で堆積させうる。したがって、例えば35nm程度のPS−b−PMMAの一様な厚さの層を得ることが可能である。次いで、得られた層は、真空中に例えば48時間程度の継続時間の間、例えば170℃程度の温度に置いておく。

【0069】

共重合体層内のPMMAブロックの配向は、異なるブロックと絶縁層との間の表面相互作用効果により、具体的には絶縁層が酸化シリコンに基づくとき、支配される。

【0070】

この相互作用は、図1Dに示すように、平行六面体ブロックの交代配置を形成するように、例えばランダムPS−PMMA共重合体を堆積させることにより中性化されうる。

【0071】

次いで、特定のマスクパターンを残すように、マスキング層の部分の除去を行う。

【0072】

例えば共重合体がPS−PMMAである場合、除去する材料はPMMAである。このため、第2のポリマー117に基づくブロック116の除去において、第1のポリマー115に対する選択的が適用されうる(図1E)。

【0073】

他の実施例によれば、PS−b−PI系の場合、この選択的除去は、オゾンによる処理を使用して行いうる。なお、オゾンにより、ポリイソプレン(PI)ブロックは、ポリブタジエン(PB)ブロックに対して選択的に分解されうる。

【0074】

PS−b−PMMA系の場合、PMMAブロックに対してPSブロックを選択的にエッチングすることもまた可能である。そのためには、CF4プラズマ、次にO2プラズマを用いる2段階のプラズマエッチング方法を使用しうる。

【0075】

共重合体がPS−PMMAである場合、PS−b−PMMAタイプのジブロック共重合体内のPMMAブロックの選択的除去を、UV放射を用いて進めることがまた可能である。これらのUV放射は、PMMA鎖の優先的な分裂を引き起こす。PMMAブロックの除去は、例えば共重合体層を、例えば1.2Jcm−2程度の線量で例えば15分程度の継続時間の間HgXe紫外線照明にさらし、10分間酢酸浴中へ浸漬し、次いで脱イオン水でリンスして、行いうる。ポリマー117のブロック116の残留成分を除去する目的で、プラズマ、具体的には、例えば4.2mTorrであり、50sccm(「標準立方センチメートル毎分」)のArおよび5sccmのO2に基づいており、例えば70W程度でありうる供給源電力で、照射が例えば15秒程度の継続時間でありうる誘導結合プラズマ(ICP)中でエッチングを行いうる。

【0076】

この選択的除去の最後に、ゲートスタック上に規則的に分布した、ポリマー115の平行六面体ブロック114(図1E)を得る。

【0077】

代替の実施形態(図4A〜図4C)によれば、非対称共重合体を使用することもまた可能である。非対称共重合体では、ポリマー115およびポリマー117の割合は、50/50とは異なっている。

【0078】

こうした共重合体を用いると、第1のポリマー115に基づく層214内に円筒形の、または円形もしくは長円形の断面を有する、第2のポリマー117に基づく複数のブロック216を形成することが可能であり、これらの複数のブロック216は、支持体に平行に延在する(図4A)。PS−PMMA共重合体の場合、こうした配置は、例えば30%のPMMAおよび70%のPSで得られうる。

【0079】

次いでPMMAブロック216は、酢酸に基づく処理とAr、O2プラズマエッチングに基づく処理とを結合させて、除去しうる(図4B)。

【0080】

例えばAr、O2を用いた異方性エッチングで、残ったPS層214を薄くし、ゲートスタック上に規則的に分布した、ポリマー115の平行六面体ブロック214を得る(図4C)。

【0081】

その後、エッチングマスクとしてポリマー115のブロック114または214を用いて、ゲート材料109のエッチングを行う。

【0082】

ポリシリコンゲートの場合、このエッチングは、例えばエッチングマスクとしてポリマー115のブロック114または214を、エッチング停止層としてゲート誘電体107を用いて、ポリシリコンのドライエッチで行いうる。したがって、ゲート材料109の層をエッチングし、第1のタイプのトランジスタ用のゲートブロック110、例えばメモリセルを選択またはアクセスするためのトランジスタのゲートを形成する(図1F)。

【0083】

このエッチングの間、ポリマー115のブロック114または214は、部分的に消費されうる(図1F)。

【0084】

代替の一実施形態(図示せず)によれば、エッチングの終了時点では、ポリマー115のブロック114が完全に消費されているように、このエッチングを行いうる。ハードマスク113を用いれば、エッチングの間、第1のゲート材料109に基づくブロック110を保護することが可能である。

【0085】

エッチングの終了時点でブロック114が完全に消費されてはいない場合、ポリマー115の除去は、例えばO2プラズマを用いて行う。

【0086】

いったんエッチングを行い終えると、空きスペース119だけ相互に隔たり、誘電体層107上に規則的なピッチで分布した、第1のゲート材料109に基づく複数の独特なブロック110を得る。第1のゲート材料109に基づく、これらの複数の独特なブロック110の中で、少なくとも1つのブロック110aは、トランジスタゲートを形成することを意図し、他方、1つまたは複数のブロックは後で除去されることを意図する。

【0087】

誘電体層107は、ゲートブロック110の下にだけ残るように、前記ハードマスクを介してエッチングしうる(図1G)。

【0088】

その後、第2のタイプのトランジスタの1つまたは複数のゲート、例えばメモリ記憶トランジスタを作る。

【0089】

そのため、第一にONOスタックなど3層絶縁スタック121、122、123を窪み103内に形成する。

【0090】

3層絶縁スタック121、122、123は、ブロック110を覆うようにコンフォーマブルな堆積で作りうる。

【0091】

そのために、例えば酸化シリコンに基づき、例えば6ナノメートル程度の厚さの誘電材料層121を第一に堆積させる。次いで、電荷トラップ層を形成する。この電荷トラップ層は、例えば6ナノメートル程度の厚さの、例えば窒化シリコンなど誘電材料122に基づきうる。

【0092】

さらに、例えば8ナノメートル程度厚い他の酸化シリコン層123を作る。

【0093】

ゲートブロック110間の誘電体ゲート層107を除去して、第2のゲート用に特定の高品質なゲート誘電材料を形成できる。

【0094】

次いで、ゲート材料129を窪み103内に堆積させる。ゲート材料129は、ゲートブロック110を隔てているスペース119を埋めるように、非コンフォーマブルな堆積により堆積されうる。材料129は、ONOスタック121−122−123で覆われたゲートブロック110を覆うように、堆積させうる。材料129は、例えばポリシリコン、具体的にはN型ドーパントでドープされたポリシリコンでありうる(図1I)。

【0095】

その後、ゲート材料129の部分的除去は、異方性エッチングで行う。

【0096】

このエッチングは、例えばHBr−Clを用いて達成されるドライエッチングまたは、例えばTMAH(水酸化テトラメチルアンモニウム)を用いるウエットエッチングでありうる。除去は、選択トランジスタのゲートのブロック110のいずれか一方の側でゲート材料129のブロック130を保存するように行う。除去は、ゲート材料129のブロック130がブロック110の高さに等しい、または実質的に等しい、または近い高さを有するように行いうる(図1J)。

【0097】

次いで、例えばレジンに基づいたマスク133を作成する。そのマスクは、選択トランジスタのゲートブロック110のうちの少なくとも第1の所与のブロック110aおよびメモリ記憶トランジスタのゲートブロック130のうちの少なくとも1つの他のブロック130aを覆う。前記他のブロック130aは、前記第1の所与のブロックに隣接し、前記第1の所与のブロックからONOスタックで隔てられている。レジンマスク133は、フォトリソグラフィで作りうる。この例示的な実施形態では、第1のブロック110aおよび第2のブロック130aとの、レジンマスク133の厳密な位置合わせは、不可欠ではない。したがって、マスク133は、ブロック130のうちの他のブロックを垂直下方に部分的に突き出させるように、任意に形成されてよく、また前記ブロック110のうちの少なくとも1つの他の所与のブロックの上にあってもよい。ブロック110および130の精密な位置決めのおかげで、マスク133の位置決め制約が軽減される。ブロック130のうちの前記ブロックを越える、マスク133の突出長さΔは、限界寸法l2未満でありうる(図1K)。

【0098】

マスクを生産するフォトリソグラフィ法では、従来技術による方法よりも大きなずれ公差がもたらされうる。これは、形成が所望されているゲートの寸法に依存する。

【0099】

次いで、メモリデバイスのゲート材料129の除去は、例えばTMAHを用いてレジンマスク133で保護された領域の外で実行する。エッチングの停止は、層121−122−123のスタックの上層上で実施する(図1L)。層121−122−123のスタックの除去は、第一に、誘電体層123がSiO2に基づくとき、誘電体層123を除去するために例えばHFを用いるエッチングで達成しうる。次いで、層122を除去するために、層122がSi3N4に基づくとき、酸H3PO4を用いたエッチングを行うことが可能である。その後、層121の除去は、層121がSiO2に基づくとき、例えばHFを用いるエッチングで達成しうる。層121の除去は、半導体領域101上の誘電体ゲート層107の少なくとも一部分を保持するように行いうる。

【0100】

この除去の終了時点で、第1のブロック110aおよび第2のブロック130aは、頂面および側面がONOスタック121−122−123で覆われている。

【0101】

次いで、誘電体107から第1のゲート材料109に基づくブロック110bの除去は、レジンマスク133で保護された領域の外で行う。そのため、TMAHに基づく選択的で等方的な化学エッチングを、半導体領域101が誘電体層107で保護されている部分であって、マスク133で完全に覆われておらず、層121−122−123のスタックで完全に覆われてもいないゲートブロック110bのエッチングのために使用されうる。また、ハードマスク113もこのエッチングの間に除去する(図1N)。

【0102】

次いで、レジンマスク133の除去を行う。

【0103】

さらに、レジンマスク133で保護されていたゲートブロック110a、130a上の層121−122−123のスタックの除去を行う。

【0104】

例えば、ONOすなわち「酸化物」、「窒化物」、「酸化物」スタックに対しては、酸化シリコン層123を除去するのにHF酸を、その後、窒化シリコン層122を除去するのにH3PO4酸を、さらに酸化シリコン層121を除去するのにHF酸を、使用することが可能である(図1O)。

【0105】

また、第1のブロック110a上のハードマスク113の除去を達成する。ハードマスク層113がAl2O3またはHfO2に基づいている場合、ハードマスクを除去するのにBCl3−Clを用いうる。ハードマスク層113がSiO2に基づいて形成されている場合、この除去は、例えば酸化シリコン層121の除去と同時に行いうる。

【0106】

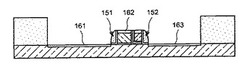

トランジスタの活性領域のドーピングは、例えば注入で、それから、隣接するゲートブロック110a、130aのどちらの側にもスペーサ151、152を作成することで実行されうる。

【0107】

そこで、活性領域への注入のための他の段階を行う。

【0108】

ゲートのコンタクトポイントおよび活性領域のための領域161、162、163を形成するために、ゲートおよび活性領域のシリサイド化が行われうる(図1P)。

【0109】

次に、トランジスタの1つまたは複数の相互接続レベルを達成しうる。

【0110】

図2Aおよび図2Bに、図1Jに関連する前述の段階の後、マスク133のタイプのいくつかのレジンマスク233a、233bを形成する代替の実施形態を示す。

【0111】

マスク233a、233bは、ポリマー117のブロック116の限界寸法l1およびポリマー115の他のブロック114の限界寸法l2の和に等しい距離だけ隔てうる。マスク233aは、ゲート材料109に基づいて形成されたゲートブロック210a上、および第1のゲート材料109に基づく他のブロック上にあり、除去されることが意図されている。マスク233bは、第1のゲート材料109に基づいて形成されたゲートブロック210b上、および第1のゲート材料109に基づく他のブロック上にあり、除去されることが意図されている。

【0112】

次いで、これらのマスク233a、233bを介して連続エッチングを行い、マスクの外の、ゲート材料129、層121−122−123のスタック、およびゲート材料109を除去する。

【0113】

前述の方法の他の代替方法を図3Aおよび図3B中に提示する。この代替方法のために、第1のマスク333aを材料209の第1のブロック210a上、およびゲート材料229の第2のブロック230aの上方に形成する。また、マスク333aは、ゲート材料209の犠牲ブロック211の一部の上にある。第2のマスク333bを材料209のブロック210b上、およびゲート材料229のブロック230bの上方に形成する。また、マスク333bは、犠牲ブロック211の一部の上にある。なお、犠牲ブロック211は、ゲート材料229に基づくブロック230aと230bとを隔てている。

【0114】

その後、これらのマスク333a、333bを介して連続エッチングを行い、マスクの外の、ゲート材料129、層121−122−123のスタック、およびゲート材料109を除去する。

【0115】

このようにして、隣接するゲート310aおよび330aを有する1対のトランジスタT11およびT12を作りうる。それらのトランジスタは、隣接するゲート310bおよび330bを有する他の対のトランジスタT21およびT22と共通電極を共有することになる。トランジスタの各対は、アクセストランジスタT11もしくはT22およびメモリ記憶トランジスタT12もしくはT21を備え、メモリ記憶トランジスタ同士が、隣接し、共通コンタクト350およびこのコンタクト350が接続される共通ソース領域を共有するように形成されている。

【0116】

図(図5A〜図5D)に関連して説明される作成方法の代替方法によれば、ゲートブロック110aおよび130aを作る順序は、逆にされてもよい。

【0117】

したがって、第一に、窪み103内に3層スタック121、122、123を作り、それからゲート材料129の堆積を行う(図5A)。

【0118】

次いで、ハードマスク113を形成し、それからポリマー115のブロック114およびポリマー117のブロック116の交代配置を有するジブロック共重合体層を形成する(図5B)。

【0119】

規則的に分布したゲートブロック130は、ポリマーパターン115を介してゲート材料129および3層121−122−123をエッチングして作られる。

【0120】

その後、これらのポリマーパターン115を除去する(図5C)。

【0121】

規則的に分布したブロック130の間に誘電体107およびゲート材料109で形成されたゲートスタックを作る(図5D)。

【0122】

次にブロック130aに隣接してゲートブロック110aを作るため、および犠牲ゲートブロックを除去するために、レジンマスクを介してエッチングを行う(図5E)。

【符号の説明】

【0123】

100 支持体

101 半導体領域

102 絶縁層

103 窪み

107 誘電体ゲート層、ゲート誘電体(層)

109、209 第1のゲート材料

110、210a、210b ゲートブロック

113 ハードマスク層

114、116、130、216、230a、230b ブロック

115 第1のポリマー

117 他のポリマー

119 空いたスペース

121 第1の誘電材料層

122 電荷蓄積層

123 第2の誘電材料層

129、229 第2のゲート材料

133、233a、233b、333a、333b マスク、レジンマスク

211 犠牲ブロック

310a、310b、330a、330b ゲート

350 共通コンタクト

T11、T22 アクセストランジスタ

T12、T21 メモリ記憶トランジスタ

【技術分野】

【0001】

本発明は、マイクロエレクトロニクスの分野に関し、詳細にはメモリの分野に関する。

【0002】

本発明は、並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクスデバイスを製作する方法に関する。本方法は、不揮発性メモリデバイスの製造に顕著に適用される。

【0003】

本発明は、並置されたゲートの位置決め精度の向上をもたらす。このことは、こうしたゲートを備えた不揮発性メモリの電気的性能の向上として表される。

【背景技術】

【0004】

電力供給なしに情報を保持する能力がある消去可能なメモリデバイスは、不揮発性メモリと呼ばれている。

【0005】

理想的には、次の特徴、すなわち電気的書込みおよび消去の可能性、ビット当たりの低嵩高性および低コスト、ランダムアクセス、短い書込みおよび読出し時間、良好な耐久性、さらに低消費電力および低電源電圧を兼ね備えることになる不揮発性メモリの適用が求められる。

【0006】

フラッシュメモリを用いると、上記基準のすべての間で良い妥協を得ることが可能である。

【0007】

フラッシュメモリは、「ブロック」、「セクタ」または、「ページ」と呼ばれる多数のメモリセルを電気的に同時に消去しうる一方、メモリセルを個別に電気的にプログラムしうる不揮発性メモリである。

【0008】

フラッシュメモリは、EPROMメモリの低嵩高性要件およびEEPROMメモリの電気的に消去可能であるという要件の両方を兼ね備えている。

【0009】

大部分の不揮発性メモリは、浮遊ゲートと呼ばれる、電荷を蓄積する場所を含む構造を備える。

【0010】

MONOS(MONOSは「Metal Oxide Nitride Oxide Silicon(金属 酸化物 窒化物 酸化物 シリコン)」の略)タイプの不揮発性メモリデバイスが出現し、ポリシリコン中の従来の浮遊ゲート構造に取って代わっている。MONOSタイプのメモリでは、電荷は窒化シリコン電荷トラップ層内に蓄積される。

【0011】

メモリトランジスタおよび選択トランジスタの両方を備える「分離ゲート」と呼ばれるメモリ構造もまた出現している。「分離ゲート」タイプのメモリは、一般に、選択トランジスタの適用を必要とする機構によってプログラムされる。なお、選択トランジスタのゲートは、メモリトランジスタのゲートに隣接して置かれている。

【0012】

こうした構造により、プログラミングレートの向上および消費電力の低減を得ることが可能である。

【0013】

これらのメモリを適用する上での困難の1つは、ゲート相互の位置決め精度に関連する。ゲートは、一般に連続フォトリソグラフィで作られる。並置されたゲート相互の位置の制御が不十分であると、メモリトランジスタの電気特性の制御が不十分になり、したがってメモリの性能の制御が不十分になることが生じる。

【0014】

「分離ゲート」と呼ばれるメモリ構造を適用するときは、並置されたゲートの位置の正確な制御が必要になる。

【0015】

米国特許第7,130,233号では、スペーサの形状に類似の丸みのある形状を有し、他のゲートに隣接して置かれた平行六面体ゲートを備えるトランジスタメモリ記憶デバイスを作る方法が開示されている。

【0016】

丸みのあるプロファイルを有するこうしたゲートを備えるデバイスを作ると、コンタクトを画定する際に著しく、ゲート寸法精度の問題が生じる。

【0017】

ゲートの正確な位置決めおよびゲートパターンの正確な画定を伴って、並置されたゲートを有するトランジスタを備えるメモリデバイスを作る、新規な方法を見つけるという問題がもたらされる。

【先行技術文献】

【特許文献】

【0018】

【特許文献1】米国特許第7,130,223号

【発明の概要】

【課題を解決するための手段】

【0019】

本発明は、並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法に関し、その方法は、

a)支持体上に置かれた第1のゲート材料に基づく層内に、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階と、

b)絶縁層および第2のゲート材料を含むスタックで前記の所与のスペースを埋め、前記スペース内の前記第2のゲート材料が、前記絶縁層により第1のブロックから隔てられた他のゲートブロックを形成する段階と、

c)前記犠牲ブロックを除去する段階と、を含む。

【0020】

それによって、制御された寸法を有する2つの独立なゲートを備えるメモリを作りうる。

【0021】

ゲートブロックおよび犠牲ブロックは、段階a)で作り、この段階でこれらのブロック間の空きのスペースの寸法を制御することが可能であり、段階b)でこの空きスペース内に他のゲートのブロックを形成する。

【0022】

本発明によれば、本方法は、段階a)の前に、

−前記第1のゲート材料に基づく層の上にジブロック共重合体に基づくマスキング層を形成する段階と、

−ジブロック共重合体に基づくマスキング層において、少なくとも1つの所与のマスキングパターン、および前記所与のパターンの所与の距離だけ隔たれた少なくとも1つの他の所与のマスキングパターンを保持するために、前記ジブロック共重合体を形成するポリマーに基づくブロックを選択的に除去する段階であって、前記マスキングパターンは前記ジブロック共重合体を形成する他のポリマーに基づいている段階と、をさらに含み、

前記第1のゲートブロックおよび前記犠牲ブロックは、前記所与のパターンおよび前記他の所与のパターンを介して、前記第1のゲート材料の前記層をエッチングすることにより、段階a)で形成される。

【0023】

それを介して第1のゲート材料をエッチングすることになるマスクキングパターンを形成するためにジブロック共重合体を用いることにより、前記第1のゲートブロックの位置決めは、前記第1のゲート材料内に形成された前記犠牲ブロックおよび前記他のゲートブロックに対して正確に制御しうる。それによって、前記所与のスペースは、正確に制御され、したがって、前記所与のスペースを埋めることによって形成されるゲートの寸法決めは正確に制御される。

【0024】

また、第1のゲート材料内に形成される犠牲ブロックの位置決めを正確に制御する。

【0025】

犠牲ブロックの精密な位置決めにより、本方法の後の段階で、このマスクの位置決めへの制約をより少なく保ちながら、マスクを介してエッチングすることで、これらのブロックを除去することが可能となりうる。

【0026】

ジブロック共重合体を用いると、小さいサイズの、例えば15nm程度のゲートを作ることもまた可能である。

【0027】

所与のパターンおよび前記他の所与のパターンは、平行六面体の形状を有しうる。

【0028】

ジブロック共重合体は、次の材料、PS−b−PMMAまたはPS−b−PIまたはPS−b−PBのうちから1つ選ばれうる。

【0029】

可能な適用例によれば、絶縁層は、少なくとも1つの誘電体層および少なくとも1つの電荷蓄積層を含む層のスタックで形成されうる。

【0030】

スタックは、例えば、

−少なくとも1つの第1の誘電材料層、

−前記第1の誘電材料層上に形成された少なくとも1つの電荷蓄積層、

−前記電荷蓄積層上に形成された少なくとも1つの第2の誘電材料層で形成された3層でありうる。

【0031】

段階b)は、

−前記第1のゲート材料の前記ブロック上への前記絶縁層のコンフォーマブルな堆積段階と、

−前記所与のスペースを埋めるための、前記第2のゲート材料の堆積段階と、を含む。

【0032】

可能な一実施例では、本方法は、段階b)と段階c)との間に、

−前記第1のゲートブロックおよび前記第2のゲートブロックを覆う少なくとも1つのマスクを、第1のゲートブロックのある側の犠牲ブロックの一部を覆い、前記所与の距離l2未満の所定の距離Δだけ第1のゲートブロックの他の側を越えて延在するように形成する段階と、

−マスクを介して、第2のゲート材料、絶縁層、および場合によりハードマスク層の連続エッチング段階と、を含むことができる。

【0033】

次いで犠牲ブロックは、段階c)で前記マスクを介してのエッチングで除去されうる。

【0034】

このようなマスクを用いると、ずれ公差は従来技術の方法よりも大きくなる。この公差は、形成を望むゲートの寸法に依存する。

【0035】

本方法の可能な一実施例では、第1のゲート材料に基づく層は、前記支持体上に形成されたゲート誘電体層上に形成しうる。次いでジブロック共重合体層は、前記第1のゲート材料層上に形成されたハードマスク層上に形成しうる。

【0036】

段階a)でのエッチングは、ハードマスクを介して実現され、本方法は、段階a)と段階b)との間に、前記ハードマスクを介してのエッチングによる、第1のブロックと前記犠牲ブロックとの間のゲート誘電体層の除去をさらに含む。

【0037】

ハードマスク層は、段階a)で第1のゲート材料ブロックを保護するためと、エッチングマスクとしての両方で役立つことができる。

【0038】

可能な適用例によれば、本方法は、段階b)と段階c)との間に、

−前記第2のゲートブロックを覆った状態で、前記第1のゲートブロック上に、および犠牲ブロックの一部上にある、少なくとも1つのマスクの形成と、

−マスクを介して、第2のゲート材料、絶縁層、およびハードマスク層の連続エッチングと、を含み、

犠牲ブロックが、段階c)で前記マスクを介するエッチングにより除去される。

【0039】

本方法は、段階c)後に、

−前記マスクを除去する段階と、

−絶縁層を、前記第1のブロックと前記他のゲートブロックとの間および前記他のゲートブロックの下にそのまま残して、部分的に除去する段階と、をさらに含みうる。

【0040】

1つの可能性によれば、段階a)は、前記支持体上にある前記第1のゲート材料に基づく前記層内への、少なくとも1つの第2のトランジスタゲートブロックの形成を含みうる。ここで、前記第2のブロックおよび前記犠牲ブロックは、他の所与のスペースだけ隔てられ、前記犠牲ブロックは、前記第1のブロックと前記第2のゲートブロックとの間に位置している。この場合、段階b)は、前記他の所与のスペース内への、前記絶縁層および前記第2のゲート材料を含む前記スタックの形成を含みうる。ここで、前記他のスペース内に位置している前記ゲート材料は、前記第2のブロックに隣接して配置され、前記第2のブロックから前記絶縁層だけ隔てられたゲートブロックを形成する。

【0041】

本方法の可能な適用例によれば、第1のゲートブロックに隣接して配置された前記他のゲートブロックは、第1のメモリ記憶トランジスタのゲートブロックであり、第2のゲートブロックに隣接して配置された前記ゲートブロックは、第2のメモリ記憶トランジスタのゲートブロックであり、前記他のゲートブロックに並置される。本方法は、第1のメモリ記憶トランジスタと前記第2のメモリ記憶トランジスタとの間への共通コンタクト領域の形成をさらに含む。

【0042】

それによって、ソース線が2つの隣接するメモリトランジスタのソースに共通であるデバイス、例えばNORフラッシュメモリセルなどが作られうる。

【0043】

本発明は、添付の図面を参照して、純粋に指示のためであり、決して制限するものではないが、所与の例示的な実施形態の説明を読むと、より良く理解されよう。

【図面の簡単な説明】

【0044】

【図1A】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1B】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1C】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1D】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1E】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1F】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1G】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1H】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1I】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1J】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1K】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1L】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1M】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1N】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1O】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図1P】並置されたゲートを備えたトランジスタを有するマイクロエレクトロニクス不揮発性メモリデバイスを作る、本発明による第1の例示的な方法を示す図である。

【図2A】並置されたゲートを有するトランジスタのいくつかの対が、同時に作られる代替の実施形態を示す図である。

【図2B】並置されたゲートを有するトランジスタのいくつかの対が、同時に作られる代替の実施形態を示す図である。

【図3A】並置されたゲートを有するトランジスタのいくつかの対が作られ、トランジスタの各対がメモリトランジスタを備え、メモリトランジスタが配置され、共通ソース電位に設定されうるように対が配置されている、例示的な方法の代替方法を示す図である。

【図3B】並置されたゲートを有するトランジスタのいくつかの対が作られ、トランジスタの各対がメモリトランジスタを備え、メモリトランジスタが配置され、共通ソース電位に設定されうるように対が配置されている、例示的な方法の代替方法を示す図である。

【図4A】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図4B】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図4C】本発明による方法において適用されるマスキングパターンの代替の実施形態を示す図である。

【図5A】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5B】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5C】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5D】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【図5E】トランジスタのゲートを作る順序において著しく、第1の実施例とは異なる、本発明による他の例示的な方法を示す図である。

【0045】

別々の図の同一、類似または等価の部分は、ある図から他の図への移行を容易にするために、同じ参照番号を有する。

【0046】

図面の中に示されている別々の部分は、図面をより読みやすくするために、必ずしも均一の尺度で図示しているわけではない。

【発明を実施するための形態】

【0047】

ここで、並置されたゲートを備えるトランジスタを有するマイクロエレクトロニクスデバイスを作る、本発明による例示的な方法を図1A〜図1Pと関連付けて提示する。マイクロエレクトロニクスデバイスは、不揮発性メモリセル、例えばフラッシュメモリなどでありうる。

【0048】

第一に、支持体100上にその支持体100上にある絶縁層102中に窪み103を作る。窪み103は、例えば矩形の形状を有してよく、例えば通例「浅いトレンチ分離」と呼ばれている方法で作りうる。絶縁層102は、例えばSiO2に基づきうる。窪み103は、例えば1μm程度の限界寸法dcで作りうる。(ここで、寸法は、支持体100および図1A中で定義された直交基準系

【0049】

【数1】

【0050】

のベクトル

【0051】

【数2】

【0052】

に平行な方向に測る。)「限界寸法」とは、1つの層または層のスタック内に作られたパターンの、高さすなわち厚さを除く最小寸法を指す。窪み103は、そこに1つまたは複数の活性トランジスタ領域を作ることを意図した半導体領域101に面して形成する(図1A)。

【0053】

次に(図1B)、第1のタイプのトランジスタ、例えばメモリセルを選択またはアクセスするためのトランジスタの1つまたは複数のゲートを作るためにゲートスタックを形成する。ゲートスタックは、誘電体ゲート層107を含む。この誘電体ゲート層107は、例えば半導体領域101の熱酸化で作りうる。誘電体ゲート層107は、例えば5nm程度の厚さを有しうる。また、ゲートスタックは、誘電体層107上にゲート材料109の層、例えば、N型ドーピングによりドープされうるポリシリコンの層を含む。ゲート材料109の層は、例えば100ナノメートルの厚さを有しうる(図1B)。

【0054】

次いで(図1C)、例えば、SiO2または、HfO2または、Al2O3に基づくハードマスク層113をゲート材料109の層上に形成する。

【0055】

ハードマスク層113は、ゲート材料109の層に対するその後のエッチング中にゲート材料109の層を保護するために使いうる。

【0056】

ハードマスク層113上にOHサイトを作り出すようにハードマスク層113の表面を下処理する段階は、例えば、ハードマスク層113がSiO2から成るときには、HFで処理することにより達成することができる。

【0057】

次いで、第1のポリマー115に基づく限界寸法l1の複数のブロック114および他のポリマー117に基づく限界寸法l2の複数のブロック116を含むマスキング層を窪み103中に作る(それぞれの限界寸法l1、l2は、図1D中で定義された直交基準系

【0058】

【数3】

【0059】

のベクトル

【0060】

【数4】

【0061】

に平行な方向に測る)。ブロック114および116の寸法l1、l2は、メモリデバイスのゲートを形成することが望ましい寸法に応じて与え、それぞれ、メモリデバイスの少なくとも1つの第1のゲートおよび少なくとも1つの第2のゲートに与えられた寸法に等しくなりうる。寸法l1、l2は、例えば15ナノメートルから40ナノメートルの間に含まれうる。

【0062】

マスキング層は、ブロック共重合体材料に基づいてよく、具体的にはジブロック共重合体材料を使用する。ジブロック共重合体材料は、相互結合した、異なる化学的性質の2つのポリマー115および117の組合せを含む材料であり、それらの分布は、規則的な周期構造に応じて作られる。

【0063】

この規則的な周期分布は、規則的な分布を有するマスクのパターンを形成するために使用する。

【0064】

可能な適用例によれば、ブロック114、116は、平行六面体の形状を有し、相互に平行であるように作りうる。

【0065】

ハードマスク層113の表面処理により、共重合体ブロックの組織化を容易にすることができる。

【0066】

平行六面体ブロックを得るために、ジブロック共重合体の組成を制御しうる。例えば、その組成が、50%程度のポリマーブロック115および50%程度のポリマーブロック117から成ると、図1Dに示すように、平行六面体ラメラへと共重合体の組織化を導く。

【0067】

ジブロック共重合体材料は、例えばPS−b−PMMA(ポリスチレン−b−ポリメチルメタクリレート)またはPS−b−PI(ポリスチレン−b−ポリイソプレン)またはPS−b−PB(ポリスチレン−b−ポリブタジエン)でありうる。

【0068】

ジブロック共重合体材料がPS−b−PMMAである場合、PS−b−PMMAは0.3程度の体積分率、67,100gmol−1程度の重量モル質量、および1.09の多分子性指数を有しうる。ジブロック共重合体鎖は、例えば1重量%程度の濃度を得るためにトルエンの溶液中に希釈しうる。次いでスピンナを用いて、例えば3,000rpm(回転数/分)程度の速度、1,000(回転数/分)s−1の加速度、および例えば30s程度の継続時間で堆積させうる。したがって、例えば35nm程度のPS−b−PMMAの一様な厚さの層を得ることが可能である。次いで、得られた層は、真空中に例えば48時間程度の継続時間の間、例えば170℃程度の温度に置いておく。

【0069】

共重合体層内のPMMAブロックの配向は、異なるブロックと絶縁層との間の表面相互作用効果により、具体的には絶縁層が酸化シリコンに基づくとき、支配される。

【0070】

この相互作用は、図1Dに示すように、平行六面体ブロックの交代配置を形成するように、例えばランダムPS−PMMA共重合体を堆積させることにより中性化されうる。

【0071】

次いで、特定のマスクパターンを残すように、マスキング層の部分の除去を行う。

【0072】

例えば共重合体がPS−PMMAである場合、除去する材料はPMMAである。このため、第2のポリマー117に基づくブロック116の除去において、第1のポリマー115に対する選択的が適用されうる(図1E)。

【0073】

他の実施例によれば、PS−b−PI系の場合、この選択的除去は、オゾンによる処理を使用して行いうる。なお、オゾンにより、ポリイソプレン(PI)ブロックは、ポリブタジエン(PB)ブロックに対して選択的に分解されうる。

【0074】

PS−b−PMMA系の場合、PMMAブロックに対してPSブロックを選択的にエッチングすることもまた可能である。そのためには、CF4プラズマ、次にO2プラズマを用いる2段階のプラズマエッチング方法を使用しうる。

【0075】

共重合体がPS−PMMAである場合、PS−b−PMMAタイプのジブロック共重合体内のPMMAブロックの選択的除去を、UV放射を用いて進めることがまた可能である。これらのUV放射は、PMMA鎖の優先的な分裂を引き起こす。PMMAブロックの除去は、例えば共重合体層を、例えば1.2Jcm−2程度の線量で例えば15分程度の継続時間の間HgXe紫外線照明にさらし、10分間酢酸浴中へ浸漬し、次いで脱イオン水でリンスして、行いうる。ポリマー117のブロック116の残留成分を除去する目的で、プラズマ、具体的には、例えば4.2mTorrであり、50sccm(「標準立方センチメートル毎分」)のArおよび5sccmのO2に基づいており、例えば70W程度でありうる供給源電力で、照射が例えば15秒程度の継続時間でありうる誘導結合プラズマ(ICP)中でエッチングを行いうる。

【0076】

この選択的除去の最後に、ゲートスタック上に規則的に分布した、ポリマー115の平行六面体ブロック114(図1E)を得る。

【0077】

代替の実施形態(図4A〜図4C)によれば、非対称共重合体を使用することもまた可能である。非対称共重合体では、ポリマー115およびポリマー117の割合は、50/50とは異なっている。

【0078】

こうした共重合体を用いると、第1のポリマー115に基づく層214内に円筒形の、または円形もしくは長円形の断面を有する、第2のポリマー117に基づく複数のブロック216を形成することが可能であり、これらの複数のブロック216は、支持体に平行に延在する(図4A)。PS−PMMA共重合体の場合、こうした配置は、例えば30%のPMMAおよび70%のPSで得られうる。

【0079】

次いでPMMAブロック216は、酢酸に基づく処理とAr、O2プラズマエッチングに基づく処理とを結合させて、除去しうる(図4B)。

【0080】

例えばAr、O2を用いた異方性エッチングで、残ったPS層214を薄くし、ゲートスタック上に規則的に分布した、ポリマー115の平行六面体ブロック214を得る(図4C)。

【0081】

その後、エッチングマスクとしてポリマー115のブロック114または214を用いて、ゲート材料109のエッチングを行う。

【0082】

ポリシリコンゲートの場合、このエッチングは、例えばエッチングマスクとしてポリマー115のブロック114または214を、エッチング停止層としてゲート誘電体107を用いて、ポリシリコンのドライエッチで行いうる。したがって、ゲート材料109の層をエッチングし、第1のタイプのトランジスタ用のゲートブロック110、例えばメモリセルを選択またはアクセスするためのトランジスタのゲートを形成する(図1F)。

【0083】

このエッチングの間、ポリマー115のブロック114または214は、部分的に消費されうる(図1F)。

【0084】

代替の一実施形態(図示せず)によれば、エッチングの終了時点では、ポリマー115のブロック114が完全に消費されているように、このエッチングを行いうる。ハードマスク113を用いれば、エッチングの間、第1のゲート材料109に基づくブロック110を保護することが可能である。

【0085】

エッチングの終了時点でブロック114が完全に消費されてはいない場合、ポリマー115の除去は、例えばO2プラズマを用いて行う。

【0086】

いったんエッチングを行い終えると、空きスペース119だけ相互に隔たり、誘電体層107上に規則的なピッチで分布した、第1のゲート材料109に基づく複数の独特なブロック110を得る。第1のゲート材料109に基づく、これらの複数の独特なブロック110の中で、少なくとも1つのブロック110aは、トランジスタゲートを形成することを意図し、他方、1つまたは複数のブロックは後で除去されることを意図する。

【0087】

誘電体層107は、ゲートブロック110の下にだけ残るように、前記ハードマスクを介してエッチングしうる(図1G)。

【0088】

その後、第2のタイプのトランジスタの1つまたは複数のゲート、例えばメモリ記憶トランジスタを作る。

【0089】

そのため、第一にONOスタックなど3層絶縁スタック121、122、123を窪み103内に形成する。

【0090】

3層絶縁スタック121、122、123は、ブロック110を覆うようにコンフォーマブルな堆積で作りうる。

【0091】

そのために、例えば酸化シリコンに基づき、例えば6ナノメートル程度の厚さの誘電材料層121を第一に堆積させる。次いで、電荷トラップ層を形成する。この電荷トラップ層は、例えば6ナノメートル程度の厚さの、例えば窒化シリコンなど誘電材料122に基づきうる。

【0092】

さらに、例えば8ナノメートル程度厚い他の酸化シリコン層123を作る。

【0093】

ゲートブロック110間の誘電体ゲート層107を除去して、第2のゲート用に特定の高品質なゲート誘電材料を形成できる。

【0094】

次いで、ゲート材料129を窪み103内に堆積させる。ゲート材料129は、ゲートブロック110を隔てているスペース119を埋めるように、非コンフォーマブルな堆積により堆積されうる。材料129は、ONOスタック121−122−123で覆われたゲートブロック110を覆うように、堆積させうる。材料129は、例えばポリシリコン、具体的にはN型ドーパントでドープされたポリシリコンでありうる(図1I)。

【0095】

その後、ゲート材料129の部分的除去は、異方性エッチングで行う。

【0096】

このエッチングは、例えばHBr−Clを用いて達成されるドライエッチングまたは、例えばTMAH(水酸化テトラメチルアンモニウム)を用いるウエットエッチングでありうる。除去は、選択トランジスタのゲートのブロック110のいずれか一方の側でゲート材料129のブロック130を保存するように行う。除去は、ゲート材料129のブロック130がブロック110の高さに等しい、または実質的に等しい、または近い高さを有するように行いうる(図1J)。

【0097】

次いで、例えばレジンに基づいたマスク133を作成する。そのマスクは、選択トランジスタのゲートブロック110のうちの少なくとも第1の所与のブロック110aおよびメモリ記憶トランジスタのゲートブロック130のうちの少なくとも1つの他のブロック130aを覆う。前記他のブロック130aは、前記第1の所与のブロックに隣接し、前記第1の所与のブロックからONOスタックで隔てられている。レジンマスク133は、フォトリソグラフィで作りうる。この例示的な実施形態では、第1のブロック110aおよび第2のブロック130aとの、レジンマスク133の厳密な位置合わせは、不可欠ではない。したがって、マスク133は、ブロック130のうちの他のブロックを垂直下方に部分的に突き出させるように、任意に形成されてよく、また前記ブロック110のうちの少なくとも1つの他の所与のブロックの上にあってもよい。ブロック110および130の精密な位置決めのおかげで、マスク133の位置決め制約が軽減される。ブロック130のうちの前記ブロックを越える、マスク133の突出長さΔは、限界寸法l2未満でありうる(図1K)。

【0098】

マスクを生産するフォトリソグラフィ法では、従来技術による方法よりも大きなずれ公差がもたらされうる。これは、形成が所望されているゲートの寸法に依存する。

【0099】

次いで、メモリデバイスのゲート材料129の除去は、例えばTMAHを用いてレジンマスク133で保護された領域の外で実行する。エッチングの停止は、層121−122−123のスタックの上層上で実施する(図1L)。層121−122−123のスタックの除去は、第一に、誘電体層123がSiO2に基づくとき、誘電体層123を除去するために例えばHFを用いるエッチングで達成しうる。次いで、層122を除去するために、層122がSi3N4に基づくとき、酸H3PO4を用いたエッチングを行うことが可能である。その後、層121の除去は、層121がSiO2に基づくとき、例えばHFを用いるエッチングで達成しうる。層121の除去は、半導体領域101上の誘電体ゲート層107の少なくとも一部分を保持するように行いうる。

【0100】

この除去の終了時点で、第1のブロック110aおよび第2のブロック130aは、頂面および側面がONOスタック121−122−123で覆われている。

【0101】

次いで、誘電体107から第1のゲート材料109に基づくブロック110bの除去は、レジンマスク133で保護された領域の外で行う。そのため、TMAHに基づく選択的で等方的な化学エッチングを、半導体領域101が誘電体層107で保護されている部分であって、マスク133で完全に覆われておらず、層121−122−123のスタックで完全に覆われてもいないゲートブロック110bのエッチングのために使用されうる。また、ハードマスク113もこのエッチングの間に除去する(図1N)。

【0102】

次いで、レジンマスク133の除去を行う。

【0103】

さらに、レジンマスク133で保護されていたゲートブロック110a、130a上の層121−122−123のスタックの除去を行う。

【0104】

例えば、ONOすなわち「酸化物」、「窒化物」、「酸化物」スタックに対しては、酸化シリコン層123を除去するのにHF酸を、その後、窒化シリコン層122を除去するのにH3PO4酸を、さらに酸化シリコン層121を除去するのにHF酸を、使用することが可能である(図1O)。

【0105】

また、第1のブロック110a上のハードマスク113の除去を達成する。ハードマスク層113がAl2O3またはHfO2に基づいている場合、ハードマスクを除去するのにBCl3−Clを用いうる。ハードマスク層113がSiO2に基づいて形成されている場合、この除去は、例えば酸化シリコン層121の除去と同時に行いうる。

【0106】

トランジスタの活性領域のドーピングは、例えば注入で、それから、隣接するゲートブロック110a、130aのどちらの側にもスペーサ151、152を作成することで実行されうる。

【0107】

そこで、活性領域への注入のための他の段階を行う。

【0108】

ゲートのコンタクトポイントおよび活性領域のための領域161、162、163を形成するために、ゲートおよび活性領域のシリサイド化が行われうる(図1P)。

【0109】

次に、トランジスタの1つまたは複数の相互接続レベルを達成しうる。

【0110】

図2Aおよび図2Bに、図1Jに関連する前述の段階の後、マスク133のタイプのいくつかのレジンマスク233a、233bを形成する代替の実施形態を示す。

【0111】

マスク233a、233bは、ポリマー117のブロック116の限界寸法l1およびポリマー115の他のブロック114の限界寸法l2の和に等しい距離だけ隔てうる。マスク233aは、ゲート材料109に基づいて形成されたゲートブロック210a上、および第1のゲート材料109に基づく他のブロック上にあり、除去されることが意図されている。マスク233bは、第1のゲート材料109に基づいて形成されたゲートブロック210b上、および第1のゲート材料109に基づく他のブロック上にあり、除去されることが意図されている。

【0112】

次いで、これらのマスク233a、233bを介して連続エッチングを行い、マスクの外の、ゲート材料129、層121−122−123のスタック、およびゲート材料109を除去する。

【0113】

前述の方法の他の代替方法を図3Aおよび図3B中に提示する。この代替方法のために、第1のマスク333aを材料209の第1のブロック210a上、およびゲート材料229の第2のブロック230aの上方に形成する。また、マスク333aは、ゲート材料209の犠牲ブロック211の一部の上にある。第2のマスク333bを材料209のブロック210b上、およびゲート材料229のブロック230bの上方に形成する。また、マスク333bは、犠牲ブロック211の一部の上にある。なお、犠牲ブロック211は、ゲート材料229に基づくブロック230aと230bとを隔てている。

【0114】

その後、これらのマスク333a、333bを介して連続エッチングを行い、マスクの外の、ゲート材料129、層121−122−123のスタック、およびゲート材料109を除去する。

【0115】

このようにして、隣接するゲート310aおよび330aを有する1対のトランジスタT11およびT12を作りうる。それらのトランジスタは、隣接するゲート310bおよび330bを有する他の対のトランジスタT21およびT22と共通電極を共有することになる。トランジスタの各対は、アクセストランジスタT11もしくはT22およびメモリ記憶トランジスタT12もしくはT21を備え、メモリ記憶トランジスタ同士が、隣接し、共通コンタクト350およびこのコンタクト350が接続される共通ソース領域を共有するように形成されている。

【0116】

図(図5A〜図5D)に関連して説明される作成方法の代替方法によれば、ゲートブロック110aおよび130aを作る順序は、逆にされてもよい。

【0117】

したがって、第一に、窪み103内に3層スタック121、122、123を作り、それからゲート材料129の堆積を行う(図5A)。

【0118】

次いで、ハードマスク113を形成し、それからポリマー115のブロック114およびポリマー117のブロック116の交代配置を有するジブロック共重合体層を形成する(図5B)。

【0119】

規則的に分布したゲートブロック130は、ポリマーパターン115を介してゲート材料129および3層121−122−123をエッチングして作られる。

【0120】

その後、これらのポリマーパターン115を除去する(図5C)。

【0121】

規則的に分布したブロック130の間に誘電体107およびゲート材料109で形成されたゲートスタックを作る(図5D)。

【0122】

次にブロック130aに隣接してゲートブロック110aを作るため、および犠牲ゲートブロックを除去するために、レジンマスクを介してエッチングを行う(図5E)。

【符号の説明】

【0123】

100 支持体

101 半導体領域

102 絶縁層

103 窪み

107 誘電体ゲート層、ゲート誘電体(層)

109、209 第1のゲート材料

110、210a、210b ゲートブロック

113 ハードマスク層

114、116、130、216、230a、230b ブロック

115 第1のポリマー

117 他のポリマー

119 空いたスペース

121 第1の誘電材料層

122 電荷蓄積層

123 第2の誘電材料層

129、229 第2のゲート材料

133、233a、233b、333a、333b マスク、レジンマスク

211 犠牲ブロック

310a、310b、330a、330b ゲート

350 共通コンタクト

T11、T22 アクセストランジスタ

T12、T21 メモリ記憶トランジスタ

【特許請求の範囲】

【請求項1】

並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法であって、

−第1のゲート材料に基づく層の上にジブロック共重合体層を形成する段階と、

−前記ジブロック共重合体層から前記共重合体のポリマーに基づくブロックを選択的に除去して、前記共重合体の他のポリマーに基づく、少なくとも1つの所与のパターンおよび前記所与のパターンから所与の距離だけ隔たった少なくとも1つの他の所与のパターンを保持する段階と、を含み、

a)前記所与のパターンおよび前記他の所与のパターンを介して前記第1のゲート材料をエッチングすることにより、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階と、

b)前記所与のスペース内に少なくとも1つの絶縁層および第2のゲート材料を形成する段階であって、前記スペース内の前記第2のゲート材料が、前記絶縁層により前記第1のブロックから隔てられた他のゲートブロックを形成する段階と、

c)前記犠牲ブロックを除去する段階と、をさらに含む方法。

【請求項2】

段階b)と段階c)との間に、

−前記第1のゲートブロックおよび前記他のゲートブロックを覆う少なくとも1つのマスクを形成する段階であって、前記マスクは、前記第1のゲートブロックの一方の側の前記犠牲ブロックの一部を覆い、且つ前記第1のゲートブロックの他方の側を越えて延在している段階と、

−前記マスクを介して、前記第2のゲート材料および前記絶縁層を連続エッチングする段階と、をさらに含み、段階c)で前記マスクを介してエッチングすることにより前記犠牲ブロックを除去する、請求項1に記載の方法。

【請求項3】

前記第1のゲート材料に基づいた層を、支持体上に形成されたゲート誘電体層上に形成してもよく、前記ジブロック共重合体層を、前記第1のゲート材料層上に形成されたハードマスク層上に形成し、段階a)での前記エッチングを、前記ハードマスクを介して実現し、

段階a)と段階b)との間に、前記ハードマスクを介してエッチングすることによる、前記第1のブロックと前記犠牲ブロックとの間の前記ゲート誘電体層の除去をさらに含む、請求項1または2に記載の方法。

【請求項4】

前記所与のパターンおよび前記他の所与のパターンが平行六面体である、請求項1から3のいずれかに記載の方法。

【請求項5】

前記ジブロック共重合体は次の材料、PS−b−PMMA、PS−b−PIのうち1つから選択される、請求項1から4のいずれかに記載の方法。

【請求項6】

前記絶縁層は、

−少なくとも1つの第1の誘電材料層と、

−前記第1の誘電材料層上に形成された、電荷を蓄積するための少なくとも1つの層と、

−前記電荷蓄積層上に形成された少なくとも1つの第2の誘電材料層と、を含むスタックで形成されている、請求項1から5のいずれかに記載の方法。

【請求項7】

段階b)は、

−前記第1のゲート材料の前記ブロック上への前記絶縁層のコンフォーマブルな堆積と、

−前記所与のスペースを埋めるような前記第2のゲート材料の堆積と、のための段階を含む、請求項6に記載の方法。

【請求項8】

段階c)の後に、

−前記マスクを除去する段階と、

−前記絶縁層を部分的に除去する段階であって、前記絶縁層は前記第1のゲートブロックと前記他のゲートブロックとの間および前記他のゲートブロックの下に残されている段階と、をさらに含む、請求項2に記載の方法。

【請求項9】

前記支持体が、前記トランジスタのチャネルが設けられる半導体領域を含み、前記半導体領域はゲート誘電体領域で覆われ、次いで前記第1のゲート材料の前記層で覆われる、請求項1から8のいずれかに記載の方法。

【請求項10】

前記誘電体ゲート領域および前記第1のゲート材料の前記層を、前記支持体上にある絶縁層内に作られた空洞内に形成する、請求項9に記載の方法。

【請求項11】

段階a)は、前記支持体上にある前記第1のゲート材料に基づく前記層内に、少なくとも1つの第2のトランジスタゲートブロックの形成を含み、前記第2のブロックと前記犠牲ブロックとが他の所与のスペースにより隔てられ、前記犠牲ブロックが前記第1のブロックと前記第2のゲートブロックとの間に位置し、

段階b)は、前記他の所与のスペース内に、前記絶縁層および前記第2のゲート材料を含む前記スタックの形成を含み、前記他のスペース内に位置する前記ゲート材料が、前記第2のブロックに隣接し前記第2のブロックから前記絶縁層だけ隔たれたゲートブロックを形成する、請求項1から10のいずれかに記載の方法。

【請求項12】

前記第1のゲートブロックに隣接する前記他のゲートブロックが第1のメモリ記憶トランジスタのゲートブロックであり、前記第2のゲートブロックに隣接する前記ゲートブロックが第2のメモリ記憶トランジスタのゲートブロックであって、前記他のゲートブロックと並置されており、前記第1のメモリ記憶トランジスタと前記第2のメモリ記憶トランジスタとの間への共通コンタクト領域の形成をさらに含む、請求項1から11のいずれかに記載の方法。

【請求項1】

並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法であって、

−第1のゲート材料に基づく層の上にジブロック共重合体層を形成する段階と、

−前記ジブロック共重合体層から前記共重合体のポリマーに基づくブロックを選択的に除去して、前記共重合体の他のポリマーに基づく、少なくとも1つの所与のパターンおよび前記所与のパターンから所与の距離だけ隔たった少なくとも1つの他の所与のパターンを保持する段階と、を含み、

a)前記所与のパターンおよび前記他の所与のパターンを介して前記第1のゲート材料をエッチングすることにより、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階と、

b)前記所与のスペース内に少なくとも1つの絶縁層および第2のゲート材料を形成する段階であって、前記スペース内の前記第2のゲート材料が、前記絶縁層により前記第1のブロックから隔てられた他のゲートブロックを形成する段階と、

c)前記犠牲ブロックを除去する段階と、をさらに含む方法。

【請求項2】

段階b)と段階c)との間に、

−前記第1のゲートブロックおよび前記他のゲートブロックを覆う少なくとも1つのマスクを形成する段階であって、前記マスクは、前記第1のゲートブロックの一方の側の前記犠牲ブロックの一部を覆い、且つ前記第1のゲートブロックの他方の側を越えて延在している段階と、

−前記マスクを介して、前記第2のゲート材料および前記絶縁層を連続エッチングする段階と、をさらに含み、段階c)で前記マスクを介してエッチングすることにより前記犠牲ブロックを除去する、請求項1に記載の方法。

【請求項3】

前記第1のゲート材料に基づいた層を、支持体上に形成されたゲート誘電体層上に形成してもよく、前記ジブロック共重合体層を、前記第1のゲート材料層上に形成されたハードマスク層上に形成し、段階a)での前記エッチングを、前記ハードマスクを介して実現し、

段階a)と段階b)との間に、前記ハードマスクを介してエッチングすることによる、前記第1のブロックと前記犠牲ブロックとの間の前記ゲート誘電体層の除去をさらに含む、請求項1または2に記載の方法。

【請求項4】

前記所与のパターンおよび前記他の所与のパターンが平行六面体である、請求項1から3のいずれかに記載の方法。

【請求項5】

前記ジブロック共重合体は次の材料、PS−b−PMMA、PS−b−PIのうち1つから選択される、請求項1から4のいずれかに記載の方法。

【請求項6】

前記絶縁層は、

−少なくとも1つの第1の誘電材料層と、

−前記第1の誘電材料層上に形成された、電荷を蓄積するための少なくとも1つの層と、

−前記電荷蓄積層上に形成された少なくとも1つの第2の誘電材料層と、を含むスタックで形成されている、請求項1から5のいずれかに記載の方法。

【請求項7】

段階b)は、

−前記第1のゲート材料の前記ブロック上への前記絶縁層のコンフォーマブルな堆積と、

−前記所与のスペースを埋めるような前記第2のゲート材料の堆積と、のための段階を含む、請求項6に記載の方法。

【請求項8】

段階c)の後に、

−前記マスクを除去する段階と、

−前記絶縁層を部分的に除去する段階であって、前記絶縁層は前記第1のゲートブロックと前記他のゲートブロックとの間および前記他のゲートブロックの下に残されている段階と、をさらに含む、請求項2に記載の方法。

【請求項9】

前記支持体が、前記トランジスタのチャネルが設けられる半導体領域を含み、前記半導体領域はゲート誘電体領域で覆われ、次いで前記第1のゲート材料の前記層で覆われる、請求項1から8のいずれかに記載の方法。

【請求項10】

前記誘電体ゲート領域および前記第1のゲート材料の前記層を、前記支持体上にある絶縁層内に作られた空洞内に形成する、請求項9に記載の方法。

【請求項11】

段階a)は、前記支持体上にある前記第1のゲート材料に基づく前記層内に、少なくとも1つの第2のトランジスタゲートブロックの形成を含み、前記第2のブロックと前記犠牲ブロックとが他の所与のスペースにより隔てられ、前記犠牲ブロックが前記第1のブロックと前記第2のゲートブロックとの間に位置し、

段階b)は、前記他の所与のスペース内に、前記絶縁層および前記第2のゲート材料を含む前記スタックの形成を含み、前記他のスペース内に位置する前記ゲート材料が、前記第2のブロックに隣接し前記第2のブロックから前記絶縁層だけ隔たれたゲートブロックを形成する、請求項1から10のいずれかに記載の方法。

【請求項12】

前記第1のゲートブロックに隣接する前記他のゲートブロックが第1のメモリ記憶トランジスタのゲートブロックであり、前記第2のゲートブロックに隣接する前記ゲートブロックが第2のメモリ記憶トランジスタのゲートブロックであって、前記他のゲートブロックと並置されており、前記第1のメモリ記憶トランジスタと前記第2のメモリ記憶トランジスタとの間への共通コンタクト領域の形成をさらに含む、請求項1から11のいずれかに記載の方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図1P】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図1J】

【図1K】

【図1L】

【図1M】

【図1N】

【図1O】

【図1P】

【図2A】

【図2B】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【公開番号】特開2011−228713(P2011−228713A)

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【外国語出願】

【出願番号】特願2011−94901(P2011−94901)

【出願日】平成23年4月21日(2011.4.21)

【出願人】(502124444)コミッサリア ア レネルジー アトミーク エ オ ゼネルジ ザルタナテイヴ (383)

【出願人】(500531141)セントレ・ナショナル・デ・ラ・レシェルシェ・サイエンティフィーク (84)

【Fターム(参考)】

【公開日】平成23年11月10日(2011.11.10)

【国際特許分類】

【出願番号】特願2011−94901(P2011−94901)

【出願日】平成23年4月21日(2011.4.21)

【出願人】(502124444)コミッサリア ア レネルジー アトミーク エ オ ゼネルジ ザルタナテイヴ (383)

【出願人】(500531141)セントレ・ナショナル・デ・ラ・レシェルシェ・サイエンティフィーク (84)

【Fターム(参考)】

[ Back to top ]