2軸測定信号の和差値出力装置

【課題】2軸測定信号の和差値を、コスト負担が少ない小さな回路規模で高速に算出する。

【解決手段】2軸分の変位検出器(10A、10B)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、2軸測定信号の和又は差を計数するためのカウンタ32と、2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路30とを備える。

【解決手段】2軸分の変位検出器(10A、10B)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、2軸測定信号の和又は差を計数するためのカウンタ32と、2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路30とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、2軸分の変位検出器(測定ゲージやエンコーダ)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置に係り、特に、2つの測定ゲージを使用した厚さ測定や段差測定に用いるのに好適な、2軸測定信号の和差値出力装置に関する。

【背景技術】

【0002】

図1(A)に示すような、ワーク8の板厚/肉厚測定や外径/内径測定、図1(B)に示すような、ワーク8の段差測定では、2つの測定ゲージ10A、10Bを使用し、それらの出力の和A+B(図1(A))や差A−B(図1(B))を求めることが行なわれている。そのため、リニアゲージカウンタ等2軸の測定ゲージや測定ヘッドを接続する装置には、2軸間の和差値を算出する機能を搭載したものが存在する。例えば、出願人は特許文献1で、板厚測定における感度校正方法を提案している。

【0003】

このような装置においては、従来、図2に示す如く、測定ゲージ10A、10B毎に独立した計数回路20を設けて、2軸の計数を独立で行ない、2軸の計数値A、Bをそれぞれ取得した後、マイコン40で加算A+Bあるいは減算A−Bを行なうことで、和差値の算出や、そのピーク検出を行なう方法を採用している。

【0004】

図において、12は、測定ゲージの出力を分割し90°位相差の2相方形波信号に変換するための分割IC、22は、該分割IC12の出力を例えば4分割して方向を弁別するための4分割方向弁別回路、24はバイナリカウンタ、26はマイコンインタフェース(I/F)である。

【0005】

【特許文献1】特開平11−72351号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、図2の方法では、マイコン40のソフトウェア処理で加減算を行ない、その結果についてピーク検出等を行なうため、処理時間が長くなり、ピーク値の取りこぼしが発生する等の問題点があった。特に、マイコン40による表示値作成に際しては、ミリ・インチ変換や定数の加算・乗算等も行なわれるため、表示更新の周期は数十ミリ秒オーダとなる。この周期で和差値算出やピーク検出を実行すると、和差値のピーク検出周期も数十ミリ秒と長くなってしまう。

【0007】

このような問題点を解決するべく、図3に示す如く、和差値算出とピーク検出をハードウェアで処理することも考えられる。図3において、22A、22Bは、それぞれ測定ゲージ10A、10Bに対応して設けられた4分割方向弁別回路、24A、24Bは、同じくバイナリカウンタ、28は、該バイナリカウンタ24A、24Bの出力によりピーク検出と和差値演算をハードウェアで行なうピーク検出・和差演算回路である。

【0008】

しかしながら、加減算回路を使用すると回路規模が大きくなり、又、ハードウェアと言えども演算時間が発生する。更に、一つの計数回路20が2軸分の回路を含むことになるため、数量の少ない2軸商品にはコストメリットがあるが、2軸測定が不要な1軸商品にそのまま用いると、数量の多い1軸商品に対してコスト負担が過大となるという問題点を有していた。

【0009】

本発明は、前記従来の問題点を解決するべくなされたもので、コスト負担が少ない小さな回路規模で、和差値を高速で算出できるようにすることを課題とする。

【課題を解決するための手段】

【0010】

本発明は、2軸分の変位検出器(測定ゲージやエンコーダ)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、2軸測定信号の和又は差を計数するためのカウンタと、2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路と、を備えることにより、前記課題を解決したものである。

【0011】

又、前記カウンタの出力側にピーク検出回路を備えて、和差値のピーク検出の高速化も可能としたものである。

【発明の効果】

【0012】

本発明によれば、2軸分の変位検出器から出力される計数パルスを入力し、2軸間の和差値を1つのカウンタで直接計数するものであるため、計数パルスに応じてリアルタイムで和差値を得ることができ、回路規模が小さく低価格で、且つ、極めて高速な動作が可能となる。又、1つの計数回路は1軸分のカウンタしか含まないため、大半を占める1軸商品に過大なコスト負担をかけることがない。

【0013】

更に、ピーク検出もハードウェアで実行し易い構成であるため、ピーク検出周期も短くなり、確実なピーク値取得が可能となる。

【発明を実施するための最良の形態】

【0014】

以下図面を参照して、本発明の実施形態を詳細に説明する。

【0015】

本発明の第1実施形態は、図4に示す如く、計数回路20を、各測定軸用の4分割方向弁別回路22A、22Bと、これらの出力により、カウンタ制御信号を生成する和差計数制御回路30と、ラッチ回路を含む1進/2進/停止切換式のバイナリカウンタ32と、ハードウェアのピーク検出回路34と、マイコンI/F26とを用いて構成したものである。

【0016】

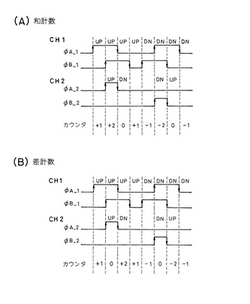

図5に和差計数例、図6に和差計数部分のブロック図、図7に該和差計数ブロック内の和差計数制御回路30の真理値表、図8に同じくバイナリカウンタ32の真理値表を示す。

【0017】

図5は、測定ゲージから出力される2軸分(CH1とCH2)の2相方形波信号φA_1、φB_1、φA_2、φB_2と、バイナリカウンタ32で行なう和差計数の関係を示している。例えば、和はCH1+CH2、差はCH1−CH2とすると、CH1がUP計数(A相がB相よりも進相)、CH2がカウント停止(A相とB相が同相)の場合、図5(A)に示す和計数においては、カウンタ32が+1カウント、図5(B)に示す差計数においても、カウンタ32が+1カウントすることになる。同様に、CH1がUP計数、CH2がUP計数の場合、和計数においてはカウンタ32が+2カウント、差計数においてはカウント停止(0)となる。CH1、CH2共にUP計数、DN計数(B相がA相より進相)、停止の3つのケースが存在するため、CH1とCH2の組合せは9通り存在することになり、これらについてもカウンタ32のカウント数を定義することができる。

【0018】

図7は、和差計数制御回路30の真理値表であり、上記9つのケースについて、カウンタ32でカウント数を制御するための信号を示している。ここで、2カウントイネーブルを示す2EN、1カウントイネーブルを示す1EN、アップ/ダウンを示すU/DBについては、/の左が和計数時、/の右が差計数時の真理値を示している。又、Xはドントケアを意味する。

【0019】

又、図8は、カウンタ計数の真理値表であり、和差計数制御回路30からの信号によりカウント数が制御されることを示している。このカウンタ32は、1進/2進/停止切換式になっており、1進時には0→1→2→3・・・、2進時には0→2→4→6・・・のように計数を行なう。1進/2進/停止は、前記のように和差計数制御回路30からの信号で切換えられる。

【0020】

和差計数制御回路30とカウンタ32部分の詳細回路は省略するが、上記動作を行なうように構成すれば、細部の回路構成については問わない。又、真理値表の信号名や信号数も、数通りの変形例が考えられるが、動作として等価であればよい。なお、4分割方向弁別回路22A、22Bについては、従来通りの構成である。

【0021】

このようにして、加減算等の演算を行なわなくても、直接、和差計数が可能であり、極めて高速(計数パルスに対してリアルタイム)で和差値を得ることができる。

【0022】

又、カウンタ32で直接和差値が得られるため、最大値、最小値、振れ等のピーク検出も、ピーク検出回路34により、ハードウェアで実行することが容易である。図2に示した従来例のようにマイコン40で和差値を算出する場合、ハードウェアでピーク検出を行なおうとしても、一度、計数値をマイコン40に渡し、和差値をマイコン40からハードウェアに戻す必要があったが、本発明の構成においては、カウンタ32の次段にピーク検出回路34を設け、ピーク検出値まで算出した後、マイコン40にデータを送ればよい。

【0023】

なお、本発明では、1つのカウンタ32で直接和差値を計数するため、和差値だけでなく、CH1、CH2の単独計数値A、Bが必要である場合には、図9に示す第2実施形態のように、第1実施形態と同じ計数回路20をもう1個設けて、そのカウンタ32で一方の計数値(図9の例ではB)を計数すれば良い。但し、和差値とどちらか一方の計数値があれば、他方の計数値を求めることができるため、カウンタ数は計2つでよい。図2に示したように、マイコン40で和差値を求める場合も、バイナリカウンタ24の数は2つ必要であるから、本発明によりカウント数が増加することはない。

【0024】

なお、図10に示す第3実施形態のように、計数回路20を3個設けて、CH1、CH2の単独計数値A、B及び和差値A+B又はA−Bが全て直接得られるように構成することも可能である。

【0025】

又、ピーク検出が不要な時は、ピーク検出回路34を省略することができる。

【0026】

前記実施形態においては、本発明が、光電式検出器を使用したリニアゲージのカウンタに適用されていたが、本発明の適用対象は、これに限定されず、図11に示す如く、4分割方向弁別回路22の代わりに計数パルス生成部50を組み合わせて和差計数制御回路に入力する信号(EN、U/DB)を作ることによって、静電容量式センサや電磁誘導式センサにも同様に適用できる。又、リニアゲージ以外の、検出ヘッドを2つ備えたタイプのエンコーダ(リニアエンコーダやロータリエンコーダ)にも、同様に適用できる。

【図面の簡単な説明】

【0027】

【図1】和差測定の代表的な例を示す概略図

【図2】従来の和差演算の方法を説明するためのブロック図

【図3】和差演算をハードウェアで実行する構成の例を示すブロック図

【図4】本発明の第1実施形態の構成を示すブロック図

【図5】同じく和差計数例を示すタイムチャート

【図6】同じく和差計数部分の動作を説明するためのブロック図

【図7】同じく和差計数制御回路の真理値表を示す図

【図8】同じくカウンタの真理値表を示す図

【図9】本発明の第2実施形態の構成を示すブロック図

【図10】同じく第3実施形態の構成を示すブロック図

【図11】同じく変形例の構成を示す要部構成を示すブロック図

【符号の説明】

【0028】

8…ワーク

10A、10B…測定ゲージ

12…分割IC

20…計数回路

22A、22B…4分割方向弁別回路

26…マイコンI/F

30…和差計数制御回路

32…バイナリカウンタ

34…ピーク検出回路

40…マイコン

50…計数パルス生成部

【技術分野】

【0001】

本発明は、2軸分の変位検出器(測定ゲージやエンコーダ)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置に係り、特に、2つの測定ゲージを使用した厚さ測定や段差測定に用いるのに好適な、2軸測定信号の和差値出力装置に関する。

【背景技術】

【0002】

図1(A)に示すような、ワーク8の板厚/肉厚測定や外径/内径測定、図1(B)に示すような、ワーク8の段差測定では、2つの測定ゲージ10A、10Bを使用し、それらの出力の和A+B(図1(A))や差A−B(図1(B))を求めることが行なわれている。そのため、リニアゲージカウンタ等2軸の測定ゲージや測定ヘッドを接続する装置には、2軸間の和差値を算出する機能を搭載したものが存在する。例えば、出願人は特許文献1で、板厚測定における感度校正方法を提案している。

【0003】

このような装置においては、従来、図2に示す如く、測定ゲージ10A、10B毎に独立した計数回路20を設けて、2軸の計数を独立で行ない、2軸の計数値A、Bをそれぞれ取得した後、マイコン40で加算A+Bあるいは減算A−Bを行なうことで、和差値の算出や、そのピーク検出を行なう方法を採用している。

【0004】

図において、12は、測定ゲージの出力を分割し90°位相差の2相方形波信号に変換するための分割IC、22は、該分割IC12の出力を例えば4分割して方向を弁別するための4分割方向弁別回路、24はバイナリカウンタ、26はマイコンインタフェース(I/F)である。

【0005】

【特許文献1】特開平11−72351号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

しかしながら、図2の方法では、マイコン40のソフトウェア処理で加減算を行ない、その結果についてピーク検出等を行なうため、処理時間が長くなり、ピーク値の取りこぼしが発生する等の問題点があった。特に、マイコン40による表示値作成に際しては、ミリ・インチ変換や定数の加算・乗算等も行なわれるため、表示更新の周期は数十ミリ秒オーダとなる。この周期で和差値算出やピーク検出を実行すると、和差値のピーク検出周期も数十ミリ秒と長くなってしまう。

【0007】

このような問題点を解決するべく、図3に示す如く、和差値算出とピーク検出をハードウェアで処理することも考えられる。図3において、22A、22Bは、それぞれ測定ゲージ10A、10Bに対応して設けられた4分割方向弁別回路、24A、24Bは、同じくバイナリカウンタ、28は、該バイナリカウンタ24A、24Bの出力によりピーク検出と和差値演算をハードウェアで行なうピーク検出・和差演算回路である。

【0008】

しかしながら、加減算回路を使用すると回路規模が大きくなり、又、ハードウェアと言えども演算時間が発生する。更に、一つの計数回路20が2軸分の回路を含むことになるため、数量の少ない2軸商品にはコストメリットがあるが、2軸測定が不要な1軸商品にそのまま用いると、数量の多い1軸商品に対してコスト負担が過大となるという問題点を有していた。

【0009】

本発明は、前記従来の問題点を解決するべくなされたもので、コスト負担が少ない小さな回路規模で、和差値を高速で算出できるようにすることを課題とする。

【課題を解決するための手段】

【0010】

本発明は、2軸分の変位検出器(測定ゲージやエンコーダ)からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、2軸測定信号の和又は差を計数するためのカウンタと、2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路と、を備えることにより、前記課題を解決したものである。

【0011】

又、前記カウンタの出力側にピーク検出回路を備えて、和差値のピーク検出の高速化も可能としたものである。

【発明の効果】

【0012】

本発明によれば、2軸分の変位検出器から出力される計数パルスを入力し、2軸間の和差値を1つのカウンタで直接計数するものであるため、計数パルスに応じてリアルタイムで和差値を得ることができ、回路規模が小さく低価格で、且つ、極めて高速な動作が可能となる。又、1つの計数回路は1軸分のカウンタしか含まないため、大半を占める1軸商品に過大なコスト負担をかけることがない。

【0013】

更に、ピーク検出もハードウェアで実行し易い構成であるため、ピーク検出周期も短くなり、確実なピーク値取得が可能となる。

【発明を実施するための最良の形態】

【0014】

以下図面を参照して、本発明の実施形態を詳細に説明する。

【0015】

本発明の第1実施形態は、図4に示す如く、計数回路20を、各測定軸用の4分割方向弁別回路22A、22Bと、これらの出力により、カウンタ制御信号を生成する和差計数制御回路30と、ラッチ回路を含む1進/2進/停止切換式のバイナリカウンタ32と、ハードウェアのピーク検出回路34と、マイコンI/F26とを用いて構成したものである。

【0016】

図5に和差計数例、図6に和差計数部分のブロック図、図7に該和差計数ブロック内の和差計数制御回路30の真理値表、図8に同じくバイナリカウンタ32の真理値表を示す。

【0017】

図5は、測定ゲージから出力される2軸分(CH1とCH2)の2相方形波信号φA_1、φB_1、φA_2、φB_2と、バイナリカウンタ32で行なう和差計数の関係を示している。例えば、和はCH1+CH2、差はCH1−CH2とすると、CH1がUP計数(A相がB相よりも進相)、CH2がカウント停止(A相とB相が同相)の場合、図5(A)に示す和計数においては、カウンタ32が+1カウント、図5(B)に示す差計数においても、カウンタ32が+1カウントすることになる。同様に、CH1がUP計数、CH2がUP計数の場合、和計数においてはカウンタ32が+2カウント、差計数においてはカウント停止(0)となる。CH1、CH2共にUP計数、DN計数(B相がA相より進相)、停止の3つのケースが存在するため、CH1とCH2の組合せは9通り存在することになり、これらについてもカウンタ32のカウント数を定義することができる。

【0018】

図7は、和差計数制御回路30の真理値表であり、上記9つのケースについて、カウンタ32でカウント数を制御するための信号を示している。ここで、2カウントイネーブルを示す2EN、1カウントイネーブルを示す1EN、アップ/ダウンを示すU/DBについては、/の左が和計数時、/の右が差計数時の真理値を示している。又、Xはドントケアを意味する。

【0019】

又、図8は、カウンタ計数の真理値表であり、和差計数制御回路30からの信号によりカウント数が制御されることを示している。このカウンタ32は、1進/2進/停止切換式になっており、1進時には0→1→2→3・・・、2進時には0→2→4→6・・・のように計数を行なう。1進/2進/停止は、前記のように和差計数制御回路30からの信号で切換えられる。

【0020】

和差計数制御回路30とカウンタ32部分の詳細回路は省略するが、上記動作を行なうように構成すれば、細部の回路構成については問わない。又、真理値表の信号名や信号数も、数通りの変形例が考えられるが、動作として等価であればよい。なお、4分割方向弁別回路22A、22Bについては、従来通りの構成である。

【0021】

このようにして、加減算等の演算を行なわなくても、直接、和差計数が可能であり、極めて高速(計数パルスに対してリアルタイム)で和差値を得ることができる。

【0022】

又、カウンタ32で直接和差値が得られるため、最大値、最小値、振れ等のピーク検出も、ピーク検出回路34により、ハードウェアで実行することが容易である。図2に示した従来例のようにマイコン40で和差値を算出する場合、ハードウェアでピーク検出を行なおうとしても、一度、計数値をマイコン40に渡し、和差値をマイコン40からハードウェアに戻す必要があったが、本発明の構成においては、カウンタ32の次段にピーク検出回路34を設け、ピーク検出値まで算出した後、マイコン40にデータを送ればよい。

【0023】

なお、本発明では、1つのカウンタ32で直接和差値を計数するため、和差値だけでなく、CH1、CH2の単独計数値A、Bが必要である場合には、図9に示す第2実施形態のように、第1実施形態と同じ計数回路20をもう1個設けて、そのカウンタ32で一方の計数値(図9の例ではB)を計数すれば良い。但し、和差値とどちらか一方の計数値があれば、他方の計数値を求めることができるため、カウンタ数は計2つでよい。図2に示したように、マイコン40で和差値を求める場合も、バイナリカウンタ24の数は2つ必要であるから、本発明によりカウント数が増加することはない。

【0024】

なお、図10に示す第3実施形態のように、計数回路20を3個設けて、CH1、CH2の単独計数値A、B及び和差値A+B又はA−Bが全て直接得られるように構成することも可能である。

【0025】

又、ピーク検出が不要な時は、ピーク検出回路34を省略することができる。

【0026】

前記実施形態においては、本発明が、光電式検出器を使用したリニアゲージのカウンタに適用されていたが、本発明の適用対象は、これに限定されず、図11に示す如く、4分割方向弁別回路22の代わりに計数パルス生成部50を組み合わせて和差計数制御回路に入力する信号(EN、U/DB)を作ることによって、静電容量式センサや電磁誘導式センサにも同様に適用できる。又、リニアゲージ以外の、検出ヘッドを2つ備えたタイプのエンコーダ(リニアエンコーダやロータリエンコーダ)にも、同様に適用できる。

【図面の簡単な説明】

【0027】

【図1】和差測定の代表的な例を示す概略図

【図2】従来の和差演算の方法を説明するためのブロック図

【図3】和差演算をハードウェアで実行する構成の例を示すブロック図

【図4】本発明の第1実施形態の構成を示すブロック図

【図5】同じく和差計数例を示すタイムチャート

【図6】同じく和差計数部分の動作を説明するためのブロック図

【図7】同じく和差計数制御回路の真理値表を示す図

【図8】同じくカウンタの真理値表を示す図

【図9】本発明の第2実施形態の構成を示すブロック図

【図10】同じく第3実施形態の構成を示すブロック図

【図11】同じく変形例の構成を示す要部構成を示すブロック図

【符号の説明】

【0028】

8…ワーク

10A、10B…測定ゲージ

12…分割IC

20…計数回路

22A、22B…4分割方向弁別回路

26…マイコンI/F

30…和差計数制御回路

32…バイナリカウンタ

34…ピーク検出回路

40…マイコン

50…計数パルス生成部

【特許請求の範囲】

【請求項1】

2軸分の変位検出器からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、

2軸測定信号の和又は差を計数するためのカウンタと、

2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路と、

を備えたことを特徴とする2軸測定信号の和差値出力装置。

【請求項2】

前記カウンタの出力側にピーク検出回路が備えられていることを特徴とする請求項1に記載の2軸測定信号の和差値出力装置。

【請求項1】

2軸分の変位検出器からの計数パルスを入力し、2軸間の和又は差を出力するための2軸測定信号の和差値出力装置であって、

2軸測定信号の和又は差を計数するためのカウンタと、

2軸測定信号の状態に応じて、該カウンタの計数モードを制御する和差計数制御回路と、

を備えたことを特徴とする2軸測定信号の和差値出力装置。

【請求項2】

前記カウンタの出力側にピーク検出回路が備えられていることを特徴とする請求項1に記載の2軸測定信号の和差値出力装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2006−47173(P2006−47173A)

【公開日】平成18年2月16日(2006.2.16)

【国際特許分類】

【出願番号】特願2004−230390(P2004−230390)

【出願日】平成16年8月6日(2004.8.6)

【出願人】(000137694)株式会社ミツトヨ (979)

【Fターム(参考)】

【公開日】平成18年2月16日(2006.2.16)

【国際特許分類】

【出願日】平成16年8月6日(2004.8.6)

【出願人】(000137694)株式会社ミツトヨ (979)

【Fターム(参考)】

[ Back to top ]