3次元半導体装置

【課題】増加された集積度を有し且つ高密度で高速の3次元(抵抗性)半導体(メモリ)装置を、最小限のマスク工程数で提供する。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

【解決手段】チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時,前記選択ラインは平面形状及び平面位置において、前記水平電極の各々と実質的に同一であり得る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は3次元半導体装置に係り、より具体的には3次元的に配列された抵抗性メモリセルを含む半導体メモリ装置に関する。

【背景技術】

【0002】

3D−ICメモリ技術はメモリ容量を増大させるための技術として、メモリセルを3次元的に配列することに関連された諸般技術を意味する。メモリ容量は、3D−ICメモリ技術以外にも、(1)パターン微細化技術及び(2)多重レベルセル(MLC)技術を通じても増大できる。しかし、パターン微細化技術は高費用の問題を随伴し、MLC技術はセル当たりの増加させ得るビット数で制限される。このような理由で、3D−IC技術はメモリ容量を増大させるための必然的な方法であるように見える。勿論、パターン微細化及びMLS技術を3D−IC技術と組み合わせた場合、メモリ容量のさらなる増加を具現できる点で、これらパターン微細化及びMLS技術も3D−IC技術とは独立に発展することが期待される。

【0003】

3D−IC技術の1つとして、パンチ−アンド−プラグ(punch−and−plug)技術が最近提案されている。パンチ−アンド−プラグ技術は多層の薄膜を基板の上に順に形成した後、その薄膜を貫通するプラグを形成する段階を含む。この技術を利用すれば、製造費用を大きく増加すること無く3Dメモリ素子のメモリ容量を大きく増加できるので、この技術は最近大きく注目を浴びている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】韓国特許公開第10−2009−0130180号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は増加された集積度を有する3次元半導体メモリ装置を提供することにある。

【課題を解決するための手段】

【0006】

本発明による3次元半導体装置は、チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時、前記選択ラインは平面(planar)形状及び平面位置において、前記水平電極の各々と実質的に同一である。

【0007】

一実施形態で、前記選択ラインと前記垂直電極との間の水平距離は前記水平電極と前記垂直電極との間の水平距離と実質的に同一であり得る。

一実施形態で、前記ビットラインと前記第1不純物領域とを連結するビットラインプラグをさらに包含でき、前記選択ラインと前記ビットラインプラグとの間の水平距離は前記水平電極と前記ビットラインプラグとの間の水平距離と実質的に同一であり得る。

前記ビットラインは前記水平電極を横切り、前記選択ライン及び前記積層体は前記チャンネル領域を横切ることができる。

一実施形態で、前記選択ラインと重畳される水平的幅において、前記第1及び第2不純物領域は互に異なり得る。

一実施形態で、前記選択ラインは前記水平電極の各々と実質的に同一であり得る。

一実施形態で、前記積層体は垂直的な方向で前記水平電極の間に介在される鋳型膜をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記水平電極と前記垂直電極との間の間隔より大きくなり得る。

一実施形態で、前記水平電極と前記垂直電極との間に介在されるメモリパターンをさらに包含できる。

また、前記水平電極の高さにおける前記メモリパターンの水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの水平厚さより薄いことがあり得る。

一実施形態で、前記積層体は、前記水平電極の垂直方向において前記水平電極の間に介在する鋳型膜、及び前記水平電極と前記垂直電極との間に介在する整流要素(rectifying element)をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記整流要素と前記垂直電極との間の間隔と異なり得る。

一実施形態で,前記水平電極と前記垂直電極との間に介在するメモリパターンをさらに包含し、前記メモリパターンはカルコゲン化合物,磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを包含できる。

【0008】

本発明による3次元半導体装置は、互いに連結されて選択ライングループを構成する第1及び第2選択ライン、前記選択ラインの各々の上方に順に積層される複数のワードライン、前記第1及び第2選択ラインの間に一列に配列される垂直電極、前記選択ライングループの両側に各々一列に配列される複数のビットラインプラグ、及び前記ワードラインを横切りながら、前記ビットラインプラグを連結するビットラインを含む。

【0009】

一実施形態で、前記ワードラインは互いに電気的に分離されて、互いに異なる電圧を有するように構成され得る。

一実施形態で、前記ワードラインは前記垂直電極が配置される第1トレンチ及び前記ビットラインプラグが配置される第2トレンチを定義し、前記第2トレンチの各々は複数の前記ビットラインを横切る長さを有することができる。

一実施形態で、前記第1トレンチは複数の前記ビットラインを横切る長さを有することができる。

一実施形態で、前記第1及び第2選択ラインの各々はその上方に位置する前記ワードラインと平面(planar)形状及び平面位置において、実質的に同一であり得る。

一実施形態で、前記第1及び第2選択ラインと前記垂直電極との間の水平距離は前記ワードラインと前記垂直電極との間の水平距離と実質的に同一であり得る。

一実施形態で、前記第1及び第2選択ラインと前記ビットラインプラグとの間の水平距離は前記ワードラインと前記ビットラインプラグとの間の水平距離と実質的に同一であり得る。

一実施形態で、前記選択ライングループの下に配置される複数の活性パターンをさらに包含でき、前記活性パターンの各々は互いに離隔された一対のドレーン領域、前記ドレーン領域の間に位置するソース領域、前記ドレーン領域と前記ソース領域との間に位置する一対のチャンネル領域を含み、前記垂直電極は前記ソース領域に接続され、前記ビットラインプラグは前記ドレーン領域に接続され、前記第1及び第2選択ラインは前記一対のチャンネル領域と各々対向して前記一対のチャンネル領域の上に配置され得る。

一実施形態で、前記第1及び第2選択ラインと重畳される水平方向の幅において、前記ドレーン領域は前記ソース領域と異なり得る。

一実施形態で、前記第1及び第2選択ラインは前記ワードラインと実質的に同一の物質で形成され得る。

一実施形態で、垂直方向において前記ワードラインの間に介在する鋳型膜をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記ワードラインと前記垂直電極との間の間隔より大きくなり得る。

一実施形態で、前記ワードラインと前記垂直電極との間に介在されるメモリパターンをさらに包含でき、前記ワードラインの高さにおける前記メモリパターンの水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの水平厚さより薄いことがあり得る。

一実施形態で、前記ワードラインと前記垂直電極との間に介在するメモリパターンをさらに包含できる。前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことができる。

【0010】

本発明による3次元半導体装置は、基板の上に配列された複数の積層体を含む電極構造体、前記電極構造体の上に配置されて前記積層体を横切る複数のビットライン、前記電極構造体を貫通する垂直電極、及び前記電極構造体を貫通し、その各々は前記ビットラインの中の対応する1つに連結されるビットラインプラグを含むことができる。前記積層体の各々は選択ライン及び前記選択ラインの上に順に積層された複数のワードラインを含み、同一の高さに配置される、奇数番目積層体のワードライン及び偶数番目積層体のワードラインは、各々、互いに連結され、前記奇数番目積層体の各々の選択ラインはそれの右側に位置する偶数番目積層体の選択ラインに連結されて選択ライングループを構成し、前記垂直電極は前記選択ライングループの各々の内部に位置し、前記ビットラインプラグは前記選択ライングループの間に位置することができる。

【0011】

本発明による3次元半導体装置は、基板内に第1方向にチャンネル領域によって互に離隔された第1不純物領域及び第2不純物領域、及び前記第1方向を横切る第2方向に前記チャンネル領域を横切って延長する選択ラインを含む選択トランジスターと、前記選択トランジスターの上に積層された複数のワードラインと、を含み、前記選択トランジスターは前記基板の第1不純物領域に連結されたビットラインと前記基板の第2不純物領域の上の垂直電極との間の電気的連結をコントロールするように配置され、前記複数のワードラインは前記選択ラインの前記第1方向に延長する幅と実質的に同一である、前記第1方向に延長する幅を有する。

【0012】

一実施形態で、前記選択トランジスターは前記チャンネル領域及び前記選択ラインの間にゲート絶縁膜をさらに含み得る。

一実施形態で、前記垂直電極及び前記少なくとも1つの選択トランジスター及び前記ワードラインの間にメモリパターンをさらに含み、前記垂直電極及び前記選択トランジスターの間の前記第1方向における距離がと前記垂直電極及び前記少なくとも1つのワードラインの間の前記第1方向における距離と同一であり得る。

一実施形態で、前記複数のワードラインの各々の少なくとも2つの面及び前記選択ラインの少なくとも2つの面を覆うメモリパターンをさらに含み得る。

一実施形態で、前記基板の上に、前記第1方向に延長し、前記第2方向に離隔された複数の活性領域を限定する複数の素子分離パターンと、前記複数の素子分離パターンを横切る複数のビットラインと、をさらに含み、

前記アクティブパターンの各々は、前記第1方向に沿って交互に配列された複数の第1不純物領域、チャンネル領域、及び第2不純物領域を含み、前記3次元半導体装置は、前記第2不純物領域の各々の上に複数の垂直電極と、前記複数のビットラインを前記第1不純物領域に各々連結させる複数のビットラインプラグと、前記基板の第1不純物領域の中1つに連結された前記複数のビットラインの中の1つと、前記基板の前記第2不純物領域の上の複数の垂直電極の中の1つとの間の電気的連結をコントロールするように各々配置された複数の選択トランジスターをさらに含み得る。

【発明の効果】

【0013】

本発明によれば、3次元的に配列された抵抗性メモリセルを含む半導体メモリ装置が提供される。この装置は3次元的に配列された抵抗性メモリセルへの電気的連結を制御するスイッチングトランジスターを具備できる。前記スイッチングトランジスターはその上方に位置する複数のワードラインの各々と実質的に同一の平面形状及び平面位置を有するように形成される。これによって前記スイッチングトランジスターは最大化されたチャンネル長さを有することができる。従って、増加された集積度を有し且つ高密度で高速の3次元抵抗性メモリ装置を、最小限のマスク工程数で提供できる。

【0014】

これに加えて、前記ワードラインはメモリパターンを形成した以後に金属性物質で形成され得る。これによって、前記半導体メモリ装置は増加された動作速度を具現することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の例示的実施形態による3次元半導体装置のセルアレイの一部を示す回路図である。

【図2】本発明の第1実施形態による3次元半導体装置の、第1の製造段階を示す斜視図である。

【図3】図2の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図4】本発明の第1実施形態による3次元半導体装置の、第2の製造段階を示す斜視図である。

【図5】図4の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図6】本発明の第1実施形態による3次元半導体装置の、第3の製造段階を示す斜視図である。

【図7】図6の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図8】本発明の第1実施形態による3次元半導体装置の、第4の製造段階を示す斜視図である。

【図9】図8の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図10】本発明の第1実施形態による3次元半導体装置の、第5の製造段階を示す斜視図である。

【図11】図10の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0016】

【図12】本発明の第1実施形態による3次元半導体装置の、第6の製造段階を示す斜視図である。

【図13】図12の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図14】本発明の第1実施形態による3次元半導体装置の、第7の製造段階を示す斜視図である。

【図15】図14の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図16】本発明の第1実施形態による3次元半導体装置の、第8の製造段階を示す斜視図である。

【図17】図16の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図18】本発明の第1実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図19】図18の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図20】本発明の第1実施形態による3次元半導体装置の、第10の製造段階を示す斜視図である。

【図21】図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0017】

【図22】本発明の第2実施形態による3次元半導体装置の、第8の製造段階を示す斜視図である。

【図23】図22の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図24】本発明の第2実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図25】図24の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図26】本発明の第3実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図27】図26の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

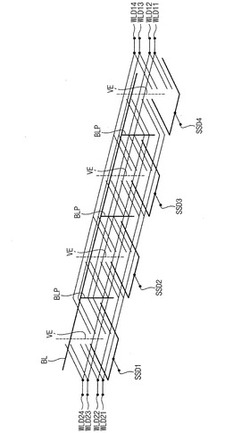

【図28】本発明の例示的実施形態による3次元半導体装置のセルアレイを示す回路図である。

【図29】本発明の第2実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図30】本発明の第1実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図31】本発明の第3実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【0018】

【図32】本発明の第4実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図33】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域のワードラインWLの配線構造を概略的に説明するための図面である。

【図34】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の選択ラインSLの配線構造を概略的に説明するための図面である。

【図35】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の3次元的配線構造を概略的に説明するための図面である。

【図36】本発明の例示的実施形態による3次元半導体装置で特定のメモリセルを選択する方法を示す図面である。

【図37】本発明の第5実施形態に従う3次元半導体装置を示す断面図である。

【図38】本発明の第6実施形態に従う3次元半導体装置を示す断面図である。

【図39】本発明の第7実施形態に従う3次元半導体装置を示す断面図である。

【図40】本発明の第8実施形態に従う3次元半導体装置を示す断面図である。

【図41】本発明の第9実施形態に従う3次元半導体装置を示す断面図である。

【0019】

【図42】本発明の第10実施形態に従う3次元半導体装置を示す断面図である。

【図43】本発明の第11実施形態に従う3次元半導体装置を示す断面図である。

【図44】本発明の第12実施形態に従う3次元半導体装置を示す断面図である。

【図45】本発明の第13実施形態に従う3次元半導体装置を示す断面図である。

【図46】本発明による3次元半導体装置を含む電子装置を図式的に説明するための図面である。

【図47】本発明による3次元半導体装置を含む電子装置を図式的に説明するための図面である。

【発明を実施するための形態】

【0020】

本発明の長所及び特徴、そしてそれらを達成する方法は、添付される図面と共に詳細に後述した実施形態を参照すれば明確になるであろう。しかし、本発明は以下で開示される実施形態に限定されず、互に異なる多様な形態に具現できる。従って、本実施形態は単に、本発明の開示が完全になるように本発明が属する技術分野で通常の知識を有する者に発明の範疇を完全に説明するために提供され、本発明は請求項の範疇によってのみ定義される。明細書の全文に亘って同一参照符号は同一構成要素を意味する。

【0021】

本明細書で使用された用語は本発明の実施形態を説明するためにのみ使用され、本発明を制限しない。本明細書で、単数形は特別に明言しない限り複数形も含む。明細書で使用される‘含む(comprises)’及び/又は‘包含する(comprising)’は、言及された構成要素、構成段階、動作及び/又は素子に対して、1つ以上の他の構成要素、構成段階、動作及び/又は素子が存在する、又は追加される場合を排除しない。また、本明細書で、或る膜が他の膜又は基板の「上方」にあると言及される場合、その膜が他の膜又は基板上に直接存在するか、又はこれらの間に第3の膜が介在することを意味する。

【0022】

また、本明細書で記述する実施形態は、本発明の理想的な例示図である断面図及び/又は平面図を参照して説明される。図面において、膜及び領域の厚さは技術的内容の効果的な説明のために誇張され得る。従って、製造技術及び/又は許容誤差等によって例示図の形態が変形され得る。従って、本発明の実施形態は図示された特定形態に制限されず、製造工程によって生成される形態の変化も含む。例えば、直角に図示された蝕刻領域の角部の境界線はラウンドされるか、或いは所定曲率を有する形態であり得る。従って、図面で例示された領域は概略的な属性を有し、図面で例示された領域の形状は単に、素子の領域の典型的な形態を例示するためであって、発明の範疇を制限しない。

【0023】

図1は本発明の例示的実施形態による3次元半導体装置のセルアレイの一部を示す回路図である。

【0024】

図1を参照すれば、第1ノードN1と第2ノードN2とを連結する選択トランジスターSSTが提供される。選択トランジスターSSTの上方にはビットラインBLが配置され、ビットラインBLはビットラインプラグBLPを通じて第1ノードN1に連結される。

【0025】

複数のワードラインWLがビットラインBLと選択トランジスターSSTとの間に配置され、垂直電極VEが第2ノードN2に連結される。複数のメモリ要素MEが垂直電極VEに並列に連結される。メモリ要素MEの各々はワードラインWLの対応する1つに連結される。即ち、ワードラインWLの各々は、メモリ要素MEの対応する1つを介して、垂直電極VEに並列に連結される。

【0026】

選択トランジスターSSTは、そのゲート電極として機能する、選択ラインSLを具備する。一実施形態で、選択ラインSLはワードラインWLと平行に設けられる。

【0027】

図1の3次元半導体装置は、次に説明する本発明の実施形態を利用して具現され得る。

[第1実施形態]

【0028】

図2、4、6、8、10、12、14、16、乃至図18は、本発明の一実施形態による3次元半導体装置の、製造段階を順次示す斜視図であり、図3、5、7、9、11、13、15、17、乃至図19は、各々、図2、4、6、8、10、12、14、16、乃至図18の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

図20は、本発明の一実施形態による3次元半導体装置の斜視図であり、図21は、図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0029】

図2及び図3を参照すれば、基板100の上部領域に、複数の活性領域120を定義する複数の素子分離パターン110が形成される。基板100は半導体、絶縁体、導電体、及びこれらの組み合わせの中での1つを包含するように構成される。一実施形態によれば、基板100はシリコンウエハー又は(これを加工した結果物として提供される)シリコン基板を包含できるが、本発明の実施形態はこれに限定されない。

【0030】

素子分離パターン110の各々は、所定の方向(例えば、x方向)と平行な長軸を有するライン形態のパターンをとる。これに加えて、素子分離パターン110は互に平行であり、従って、活性領域120もやはり互に平行であり、その各々はライン形態のパターンをとる。素子分離パターン110はシリコン酸化物のような少なくとも1つの絶縁物で形成できるが、本実施形態はこれに限定されない。

【0031】

図4及び図5を参照すれば、活性領域120の上部に不純物領域130を形成する。不純物領域130は基板100の上に2次元的に形成され得る。例えば、不純物領域130の複数の領域が、活性領域120毎に、素子分離パターン110の長軸に沿って互に離隔されて形成され得る。不純物領域130は図1を参照して説明した第1ノードN1として機能する第2不純物領域132、及び第2ノードN2として機能する第1不純物領域131を含む。

【0032】

第1及び第2不純物領域131、132は、素子分離パターン110の長軸に沿って交互に配列される。第1及び第2不純物領域131、132はその内部に注入された、ホウ素、アルミニウム、燐、及び/又は砒素のようなn形又はp形不純物を包含するが、本実施形態はこれに限定されない。

【0033】

不純物領域130を形成する段階は、素子分離パターン110の上に活性領域120を横切るマスクパターン(図示せず)を形成する段階及びマスクパターンをイオンマスクとして使用するイオン注入工程を実施する段階を含む。

【0034】

変形された実施形態で、不純物領域130は素子分離パターン110を形成する前に形成される。これに加えて、活性領域120又は基板100内に不純物を注入する少なくとも1回のイオン注入工程が選択的に実施される。例えば、選択トランジスターSSTの閾値電圧を調節するために、活性領域120の内に不純物を注入するイオン注入工程が選択的に実施される。又は、基板100の内にウェル領域(well region)を形成するイオン注入工程が選択的に実施される。このような追加的なイオン注入工程は素子分離パターン110を形成する前又は後に実施される。

【0035】

図6及び図7を参照すれば、ゲート絶縁膜210が、不純物領域130が形成された結果物の上に形成され、薄膜構造体200がゲート絶縁膜210の上に形成される。薄膜構造体200は、交互に積層された、複数の犠牲膜220及び複数の鋳型膜230を含む。

【0036】

ゲート絶縁膜210はシリコン酸化膜及び高誘電膜の中の少なくとも1つを含む。高誘電膜はハフニウム酸化物、アルミニウム酸化物、ジルコニウム酸化物のような物質からなるが、本実施形態はこれに限定されない。一実施形態で、ゲート絶縁膜210は活性領域120の上部面を熱酸化して形成される。他の実施形態で、ゲート絶縁膜210は蒸着技術を使用して形成される蒸着膜である。

【0037】

犠牲膜220は鋳型膜230に対して蝕刻選択性(etch selectivity)を有しながら蝕刻され得る物質で形成される。即ち、所定の蝕刻レシピーを使用して犠牲膜220を蝕刻する工程で、犠牲膜220は鋳型膜230の蝕刻を制限しながら(及び/又は、防止しながら)蝕刻され得る物質で形成される。公知のように、このような蝕刻選択性は鋳型膜230の蝕刻速度に対する犠牲膜220の蝕刻速度の比率として定量的に表現される。一実施形態によれば、犠牲膜220は鋳型膜230に対して1:10乃至1:200(さらに限定的には、1:30乃至1:100)の蝕刻選択比を有する物質の1つである。例えば、鋳型膜230はシリコン酸化膜及びシリコン窒化膜の中の少なくとも1つであり、犠牲膜220はシリコン膜、シリコン酸化膜、シリコンカーバイド、及びシリコン窒化膜の中から選択される鋳型膜230と異なる物質である。以下では、本発明の技術的思想に対する理解を容易にするために、鋳型膜230はシリコン酸化膜であり、犠牲膜220はシリコン窒化膜である実施形態を例示的に説明する。

【0038】

図8及び図9を参照すれば、薄膜構造体200をパターニングして第1トレンチ240を形成した後、第1埋め込み膜250を形成して第1トレンチ240を満たす。

【0039】

第1トレンチ240は不純物領域130の一部を露出するように形成され、その各々は素子分離パターン110を横切るように形成される。第1トレンチ240は、素子分離パターン110の長軸に沿って配列される第1不純物領域131を露出する。

【0040】

第1埋め込み膜250は絶縁性物質を少なくとも1つを含む。例えば、第1埋め込み膜250はSOG物質及びシリコン酸化物の中の少なくとも1つを含む。一実施形態で、第1埋め込み膜250は犠牲膜220及び鋳型膜230に対して蝕刻選択性を有する物質で形成される。

【0041】

図10及び図11を参照すれば、第1トレンチ240の下に位置する第1不純物領域131を露出する複数の垂直ホール260を形成する。以後、垂直ホール260の内側壁を覆うメモリパターン270及び垂直ホール260の残りの空間を満たす第1プラグ280を形成する。

【0042】

垂直ホール260の形成は、薄膜構造体200の上にマスクパターンを形成する段階と、その後、これを蝕刻マスクとして使用して第1埋め込み膜250をパターニングする段階とを含む。一部の実施形態によれば、示したように、垂直ホール260の各々は第1トレンチ240より広い幅を有するように形成される。

【0043】

メモリパターン270は情報を格納できるようにする物性を有する物質を少なくとも1つ含む。例えば、メモリパターン270はそれを通過する電流によってその抵抗が選択的に変化する物質(即ち、可変抵抗特性を有する物質)を少なくとも1つ含む。

【0044】

一実施形態によれば、メモリパターン270はそれに印加される熱によってその電気的抵抗が変化する物質(例えば、カルコゲン化合物(chalcogenide))を少なくとも1つ含む。カルコゲン化合物はアンチモン(antimony、Sb)、テルル(tellurium、Te)、及びセレン(selenium、Se)の中の少なくとも1つを含む。例えば、メモリパターン270は、テルルTeは約20原子%乃至約80原子%の濃度を有し、アンチモンSbは約5原子%乃至約50原子%の濃度を有し、残りはゲルマニウムGeであるカルコゲン化合物を含む。これに加えて、メモリパターン270のためのカルコゲン化合物は、不純物として、N、O、C、Bi、In、B、Sn、Si、Ti、Al、Ni、Fe、Dy、及びLaの中の少なくとも1つを含むことができる。又は、メモリパターン270はGeBiTe、InSb、GeSb、及びGaSbの中の1つで形成されることもあり得る。

【0045】

他の実施形態によれば、メモリパターン270はペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含む。例えば、メモリパターン270は、酸化ニオブ(niobium oxide)、酸化チタン(titanium oxide)、酸化ニッケル(nikel oxide)、酸化ジルコニウム(zirconium oxide)、酸化バナジウム(vanadium oxide)、PCMO((Pr、Ca)MnO3)、ストロンチウム−チタニウム酸化物(strontium−titanium oxide)、バリウム−ストロンチウム−チタニウム酸化物(barium−strontium−titanium oxide)、ストロンチウム−ジルコニウム酸化物(strontium−zirconium oxide)、バリウム−ジルコニウム酸化物(barium−zirconium oxide)、又はバリウム−ストロンチウム−ジルコニウム酸化物(barium−strontium−zirconium oxide)等の少なくとも1つを含む。これに加えて、本発明の一実施形態によれば、メモリパターン270は、情報を格納できるようにする物性に加えて、自己整流特性(self−rectifying property)又は非線形の電流−電圧特性を示す物質の中の少なくとも1つで形成される。

【0046】

第1プラグ280の各々は、導電性物質(例えば、ドーピングされた半導体、金属、導電性金属窒化物、シリサイド、及び、炭素ナノチューブ又はグラフェン等のナノ構造体の中の少なくとも1つを含む。

【0047】

この実施形態によれば、メモリパターン270の各々は図1を参照して説明されたメモリ要素MEとして使用され、第1プラグ280の各々は図1を参照して説明された垂直電極VEとして使用される。

【0048】

図12及び図13を参照すれば、薄膜構造体200をパターニングして、不純物領域130の中の他の一部を露出させる第2トレンチ310を形成する。一実施形態で、第2トレンチ310を形成する段階は第1プラグ280が形成された結果物を覆うキャッピングマスクパターン300を形成した後、これを蝕刻マスクとして使用して薄膜構造体200を異方的に蝕刻する段階を含む。

【0049】

第2トレンチ310の各々は素子分離パターン110を横切るように形成される。第2トレンチ310は、素子分離パターン110の長軸に沿って配列される第2不純物領域132を露出する。また、第2トレンチ310によって、犠牲膜220及び鋳型膜230の側壁が露出される。

【0050】

一部の実施形態によれば、図12に示したように、第2トレンチ310の各々は、狭い領域及び該狭い領域より広い幅を有する広い領域311を含む。1つの第2トレンチ310において、前記狭い領域及び広い領域311は交互に配列されて互に連結される。広い領域311の各々は第2不純物領域132の対応する1つを露出するように形成され、前記狭い領域の各々は素子分離パターン110の対応する1つを横切るように形成される。一実施形態において、第2トレンチ310はキャッピングマスクパターン300をハードマスクとして使用してパターニングされる。

【0051】

図14及び図15を参照すれば、犠牲膜220を選択的に除去して鋳型膜230の間にリセス領域320を形成する。リセス領域320を形成する段階は第2トレンチ310によって露出される犠牲膜220を側方向に蝕刻(例えば、等方的に蝕刻)する段階を含む。

【0052】

第2トレンチ310が複数の素子分離パターン110を横切るライン形態であるので、上述した犠牲膜220の選択的除去が遂行できる。即ち、ライン形態の第2トレンチ310が存在するので、エッチャントが犠牲膜220まで供給される。

【0053】

リセス領域320は第1トレンチ240の境界まで拡張される。例えば、リセス領域320は第1埋め込み膜250及びメモリパターン270の外側壁を露出するように形成される。

【0054】

図16及び図17を参照すれば、リセス領域320を満たす水平電極330を形成する。水平電極330の各々はリセス領域320の中の対応する1つを満たすように形成される。この実施形態によれば、水平電極330は図1を参照して説明したワードラインWL及び選択ラインSLとして使用される。

【0055】

水平電極330を形成する段階は、リセス領域320を満たす導電膜を形成する段階、及び第2トレンチ310から導電膜を除去して導電膜をリセス領域320の内部空間に局所化させる段階を含む。一実施形態では、導電膜は第2トレンチ310を完全に満たさず、第2トレンチ310の内壁をコンフォーマルに覆うように形成される。この場合、導電膜を除去する段階は等方性蝕刻工程(例えば、湿式蝕刻工程)を通じて遂行できる。

【0056】

水平電極330は導電性物質を少なくとも1つ含む。例えば、水平電極330はドーピングされた半導体、金属物質又は金属窒化物の中の少なくとも1つで形成される。水平電極330が金属物質又は金属窒化物で形成される場合、本発明による半導体メモリ装置の動作速度特性は改善できる。

【0057】

図18及び図19を参照すれば、第2不純物領域132に各々接続する第2プラグ350が形成される。この実施形態によれば、第2プラグ350は図1を参照して説明されたビットラインプラグBLPとして使用される。第2プラグ350を形成する段階は、第2トレンチ310を満たす第2埋め込み膜340を形成する段階と、その後、第2埋め込み膜340を貫通する第2プラグ350を形成する段階を含む。

【0058】

一実施形態において、第2埋め込み膜340は蒸着技術の中の1つを使用して形成され、その蒸着厚さは第2トレンチ310の狭い領域の幅の1/2より大きく、且つ第2トレンチ310の広い領域311の幅の1/2より小さい。この場合、第2埋め込み膜340は第2トレンチ310の狭い領域を完全に満たすが、広い領域311を完全に満たさない。即ち、上述した蒸着厚さ条件が充足される場合、第2埋め込み膜340は広い領域311に自己整列的に形成される開口部を有する。

【0059】

第2埋め込み膜340が蒸着技術を使用して形成される場合、第2埋め込み膜340は広い領域311の底を覆う。従って、第2プラグ350を形成する前に、広い領域311の底から第2埋め込み膜340を除去する異方性蝕刻工程が実施される。

【0060】

第2プラグ350は、異方性蝕刻工程が実施された結果物の上に導電膜を形成した後、所定のノード分離工程を実施することによって形成される。導電膜は広い領域311に形成される開口部を満たすように形成されて、第2不純物領域132に連結される。ノード分離工程の結果として、広い領域311の内に局所化され、2次元的に分離された第2プラグ350が得られる。

【0061】

図20は、本実施形態による3次元半導体装置の、第10の製造段階を示す斜視図であり、図21は、図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

図20及び図21を参照すれば、キャッピングマスクパターン300の上に上部配線360を形成する。上部配線360は第1及び第2トレンチ240、310、及び水平電極330を横切るように形成され、上部配線360の各々はその下に配置される第2プラグ350の中の複数個と連結される。この実施形態によれば、上部配線360は図1を参照して説明したビットラインBLとして使用される。

[第2実施形態]

【0062】

図22及び図24は本発明の第2実施形態による3次元半導体装置の、第8、第9の製造段階を示す斜視図であり、図23及び図25は、各々、図22及び図24の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

説明を簡単にするために、図2乃至図21を参照して説明した先述の第1実施形態と実質的に同一の構成要素に対する説明は省略する。この実施形態は少なくとも2つの点で図16乃至図19を参照して説明した先述の実施形態と区別される。

【0063】

第1点としては、図22及び図23に示したように、第2トレンチ310はその長軸方向に沿って計測された幅が均一である。即ち、第2トレンチ310の幅は素子分離パターン110及び第2不純物領域132の上で実質的に同一である。

第2点としては、水平電極330は第2トレンチ310の形成後に形成されるのではなく、薄膜構造体200の一部として提供される。即ち、この実施形態によれば、薄膜構造体200は順に積層される複数の導電膜及び複数の絶縁膜を含む。この場合、第2トレンチ310の形成によって、薄膜構造体200の導電膜及び絶縁膜は各々先の実施形態の水平電極330及び鋳型膜230として機能する。

【0064】

一方、第2トレンチ310の幅が均一であるので、第2プラグ350は図18を参照して説明したように自己整列的に形成されることが困難になる。この実施形態によれば、図24及び図25に示したように、第2プラグ350を形成する段階は第2トレンチ310を完全に満たす第2埋め込み膜340を形成した後、所定のパターニング工程を実施して第2不純物領域132を露出させる開口部を形成する段階、及び開口部を導電性物質で満たす段階を含む。第2プラグ350と水平電極330との間を電気的に分離するために、第2プラグ350の各々の側壁を覆う絶縁スペーサー345がさらに形成される。

【0065】

上で説明されなかった他の工程段階は図2乃至図20を参照して説明した先述の第1実施形態の工程段階と同一である。

[第3実施形態]

【0066】

図26は本発明の第3実施形態による3次元半導体装置の、第9の製造段階を示す斜視図であり、図27は図26の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。説明を簡単にするために、図2乃至図21を参照して説明した先述の第1実施形態と実質的に同一の構成要素に対する説明は省略される。

【0067】

図10及び図11を再び参照すれば、第1埋め込み膜250を選択的に除去して第1トレンチ240を通じてメモリパターン270の側壁を露出する。続いて、メモリパターン270の露出された側壁を蝕刻して第1プラグ280の側壁を露出する。これによって、図26及び図27に示したように、メモリパターン270の各々は第1トレンチ240によって水平方向に分離された2つの部分を有する。第1トレンチ240の両側に位置するメモリパターン270の2つの部分は互に異なるデータ格納箇所として機能するので、このような分離工程は格納されたデータ間の攪乱問題を解決できる。

【0068】

以後、第1埋め込み膜250が除去されることによって、形成される空間は絶縁膜(例えば、キャッピングマスクパターン300)で満たされる。上で説明されなかった他の工程段階は図2乃至図21を参照して説明した先述の第1実施形態の工程段階と同一である。

【0069】

図28は本発明の例示的実施形態による3次元半導体装置のセルアレイを示す回路図であり、図29乃至図32は本発明の例示的実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。以下、説明を簡単にするために、図1及び、図2乃至図26を参照して説明した第1乃至第3実施形態と実質的に同一の構成要素に対する説明は省略する。また、図29乃至図32においては理解の便のため、キャッピングマスクパターン300及び鋳型膜230の全てを省略し、水平電極330の一部を切欠いてある。

【0070】

図28を参照すれば、複数の選択トランジスターSSTが複数のビットラインプラグBLPを通じてビットラインBLに並列に連結される。ビットラインプラグBLPの各々はそれに隣接する一対の選択トランジスターSSTに共通に連結される。

【0071】

複数のワードラインWL及び複数の垂直電極VEがビットラインBLと選択トランジスターSSTとの間に配置される。垂直電極VEはビットラインプラグBLPの間に配置される。例えば、垂直電極VE及びビットラインプラグBLPはビットラインBLと平行な方向に沿って交互に配列される。これに加えて、垂直電極VEの各々はそれに隣接する一対の選択トランジスターSSTに共通に連結される。

【0072】

複数のメモリ要素MEが垂直電極VEの各々に並列に連結される。メモリ要素MEの各々はワードラインWLの対応する1つに連結される。即ち、ワードラインWLの各々は、メモリ要素MEの対応する1つを通じて、垂直電極VEの対応する1つに連結される。

【0073】

選択トランジスターSSTの各々は、そのゲート電極として機能する、選択ラインSLを具備する。一実施形態において、選択ラインSLはワードラインWLと平行である。

【0074】

図29乃至図32を参照すれば、図28のビットラインBLとして機能する複数の上部配線360が基板100の上に配置される。基板100は上部配線360と平行な複数の活性領域120を有する。活性領域120は基板100の上部領域に形成される複数の素子分離パターン110によって定義される。平面(planar)図において、即ち上方から垂直方向に見る時、素子分離パターン110は上部配線360の間に位置し、上部配線360と平行な長軸を有するように形成される。なお図29乃至図32で、参照符号Cはチャンネルを示す。

【0075】

活性領域120の各々には、上部配線360と平行な方向に沿って一列に配列される複数の不純物領域130が形成される。不純物領域130は互に離隔されてチャンネル領域を定義する。不純物領域130は複数の第1不純物領域131及び複数の第2不純物領域132を包含し、第1不純物領域131及び第2不純物領域132は互に交互に配列される。

【0076】

基板100の上には2次元的に配列される複数の第1プラグ280が配列される。第1プラグ280は図28の垂直電極VEとして機能し、その各々は第1不純物領域131の対応する1つに連結される。

【0077】

基板100の上には2次元的に配列される複数の第2プラグ350が配列される。第2プラグ350は図28のビットラインプラグBLPとして機能し、その各々は第2不純物領域132の対応する1つに連結される。

【0078】

チャンネル領域の上には素子分離パターン110を横切る複数の水平電極330が配置される。水平電極330は図28のワードラインWL及び選択ラインSLとして機能する。水平電極330の中の複数の電極がチャンネル領域の各々の上方に順に積層される。一実施形態において、水平電極330の中の最下部の電極は選択ラインSLとして機能し、残りはワードラインWLとして機能する。

【0079】

水平電極330は第1及び第2プラグ280、350から水平方向に離隔される。例えば、水平電極330と第1プラグ280との間には図28のメモリ要素MEとして機能するメモリパターン270が介在し、水平電極330と第2プラグ350との間には絶縁膜(例えば、図18及び図19に示した第2埋め込み膜340)が介在する。

【0080】

第1プラグ280の各々は第1不純物領域131の中の対応する1つとワードラインWLとして使用される水平電極330の中の1つの間の導電経路として使用される。これによって、第1プラグ280は第1不純物領域131には連結されるが、上部配線360からは離隔される。第2プラグ350の各々は第2不純物領域132の中の対応する1つとビットラインBLの中の対応する1つとの間の導電経路として使用される。この時、第2プラグ350の各々は上述したように絶縁膜によって水平電極330から離隔される。

【0081】

一方、図2乃至図21を参照して説明した第1実施形態によれば、図30に示したように、第2プラグ350の各々は円柱に近い形状を有するように形成される。反面、図22及び図24を参照して説明した第2実施形態によれば、図29に示したように、第2プラグ350の各々は直方体柱形状を有するように形成される。

【0082】

また、図26を参照して説明した第3実施形態によれば、図31に示したように、メモリパターン270の各々は水平的に分離された2つの部分を有する。即ち、メモリパターン270の各々は第1プラグ280の左側壁を覆う部分とこれから離隔されて右側壁を覆う部分とを含む。

[第4実施形態]

【0083】

本発明の第4実施形態によれば、図32に示したように、第1プラグ280の下には導電パターン99が各々配置され、メモリパターン270の下には下部絶縁パターン215が各々配置される。このような実施形態は図40及び図41を参照して後でより詳細に説明する

【0084】

図33乃至図35は本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の配線構造を概略的に説明するための図面である。より具体的に、図33はワードラインWLの連結構造を示し、図34は選択ラインSLの連結構造を示し、図35はセルアレイ領域の配線の相対的配置を3次元的に示す。説明を簡単にするために、図1及び図28を参照して説明した例示的実施形態と実質的に同一又は類似の構成要素に対する説明は省略する。

【0085】

図33及び図34を参照すれば、ビットラインBLの各々の下にはビットラインプラグBLP及び垂直電極VEが交互に配列される。ビットラインBLはビットラインドライバーBLDに各々連結される。

【0086】

図33を参照すると、ワードラインWL1乃至WL16がビットラインBLを横切るように配置される。ワードラインWL1乃至WL16の各々はビットラインプラグBLPの1列及び垂直電極VEの1列の間に配置される。また、ワードラインWL1乃至WL16の各々は第1又は第2ワードラインドライバーWLD1又はWLD2の中の1つに連結される。例えば、ワードラインWL1乃至WL16の中の奇数番目のものは第1ワードラインドライバーWLD1に連結され、ワードラインWL1乃至WL16の中の偶数番目のものは第2ワードラインドライバーWLD2に連結される。ビットラインBLを含むセルアレイ領域は第1ワードラインドライバーWLD1と第2ワードラインドライバーWLD2との間に配置され得る。これによって、図33に示したように、第1及び第2ワードラインドライバーWLD1、WLD2の各々に連結されるワードラインWL1乃至WL16はフィンガー構造を形成する。

【0087】

一方、図34を参照すると、選択ラインSL1乃至SL14がビットラインBLを横切るように配置される。ワードラインWL1乃至WL16と同様に、選択ラインSL1乃至SL14の各々はビットラインプラグBLPの1列及び垂直電極VEの1列の間に配置される。例えば、図29乃至図32に示したように、選択ラインSL1乃至SL14の各々の上方には複数のワードラインWLが積層される。

【0088】

選択ラインSL1乃至SL14は複数の選択ライングループを構成し、選択ライングループの各々は互に連結された隣接する一対の選択ラインを含む。一実施形態によれば、選択ライングループの各々はビットラインBLを横切る方向に沿って配列される垂直電極VEの両側に位置する一対の選択ラインSL1乃至SL14で構成される。即ち、垂直電極VEは選択ライングループの各々の内部に位置し、ビットラインプラグBLPは選択ライングループの間に位置する。

【0089】

選択ライングループは、図34に示すように、複数の選択ラインドライバーSSD1乃至SSD7に各々連結される。選択ラインドライバーSSD1乃至SSD7は独立的に動作するように構成される。

【0090】

一方、図33では、特定の高さ、即ち薄膜構造体200の特定の層に配列されたワードラインの配置構造を示したが、本実施形態による3次元半導体装置は複数の層の各々で図33の配置構造を有するように配列されたワードラインを含む場合もある。例えば、図35に示したように、ワードラインドライバーWLD11乃至WLD14、WLD21乃至24は各々の層に配列されるワードラインを独立的に制御するように構成され、これらの中の一部WLD11乃至WLD14はワードラインの中で偶数番目のものを制御し、他の一部WLD21乃至24はワードラインの中で奇数番目のものを制御するように構成される。

【0091】

図36は本発明の一実施形態による3次元半導体装置で特定のメモリセルを選択する方法を示す図面である。

【0092】

図36に示したように、ビットラインドライバーBLDの中の1つ、選択ドライバーSSD1乃至SSD3の中の1つ、そしてワードラインドライバーWLD1、WLD2の中の1つを選択すれば、3次元的に配列されるメモリセルの中の1つが一意的に選択される。

【0093】

例えば、ビットラインドライバーBLDの中の1つを選択し、選択ドライバーSSD1乃至SSD3の中の1つを選択すれば、これらに連結された導電ラインの交差点に位置する一対の選択トランジスターSSTが選択される。しかし、これらの選択トランジスターSSTは1つの垂直電極VEを共有するので、このような選択は1つの垂直電極VEを選択することが可能である。これに加えて、図35に示したように、1つの垂直電極VEの両側に配列される複数のワードラインWLは全て電気的に分離されるので、これらの中の1つを選択すれば、1つのワードライン、1つのビットライン及びこれらの間に介在される1つのメモリセルを連結する一意的な経路を形成できる。

【0094】

図37乃至図45は各々、本発明の第5乃至第13実施形態に従う3次元半導体装置を示す断面図である。上述した実施形態による3次元半導体装置は以下で説明する本発明の技術的特徴の中の少なくとも1つを有するように構成される。

【0095】

一実施形態によれば、図29乃至図32に示したように、選択ラインSLの各々は、少なくとも所定の領域の内で、その上方に位置するワードラインWLと実質的に同一の平面(planar)形状及び同一の平面配置を有する。例えば、図37乃至図39、図42、及び図43に例示的に示したように、選択ラインSLとワードラインWLとは垂直に互いに整列された側壁を有する。即ち、選択ラインSLと垂直電極VEの側壁との間の距離は、ワードラインWLと垂直電極VEの側壁との間の距離と実質的に同一である。同様に、選択ラインSLとビットラインプラグBLPの側壁との間の距離は、ワードラインWLとビットラインプラグBLPの側壁との間の距離と実質的に同一である。

【0096】

一実施形態によれば、選択ラインSLとワードラインWLとは実質的に同一の物質で形成される。一方、他の実施形態によれば、選択ラインSLとワードラインWLとは互に異なる物質で形成されるか、或いは互に整列されない場合もある。例えば、選択ラインSLとして使用される水平電極330はワードラインWLとして使用される水平電極330を形成する以前に形成される。即ち、図6を参照して説明された薄膜構造体200を形成する以前に、選択ラインSLを形成するための別の工程がさらに実施される。

【0097】

これに加えて一実施形態によれば、薄膜構造体200を形成する以前に、選択ラインSLをパターニングして第1不純物領域131を露出させる開口部を形成する段階がさらに実施される。一実施形態によれば、後述する図41に示すように、開口部は層間絶縁膜225及びこれを貫通する連結電極282によって満たされる。他の実施形態によれば、後述する図40に示すように、開口部は下部絶縁スペーサー215及び導電パターン99によって満たされる。

【0098】

一方、本発明の一実施形態によれば、図2乃至図6を参照して説明したように、不純物領域130は薄膜構造体200を形成する以前に形成され、第1及び第2トレンチ240、310の形成は薄膜構造体200の形成以後に遂行される。この場合、水平電極330は不純物領域130を形成するためのマスクとしては使用されない。その結果として、選択ラインSLと第1及び第2不純物領域131、132との間の相対的配置は、水平電極330が第1及び第2不純物領域131、132を形成するためのマスクとして使用される場合に比べて異なることがあり得る。

例えば、第1及び第2不純物領域131、132とこれら各々に隣接する選択ラインSLとの間の重畳幅は互いに異なり得る。具体的には、

図37乃至図40に示したように、第1不純物領域131の左側及び右側領域とこれらに隣接する選択ラインSLとの間の重畳幅L1、L2とし、第2不純物領域132の左側及び右側領域とこれらに隣接する選択ラインSLとの間の重畳幅をL3、L4とする。そしてL1とL2の差をD(L1,L2)と表現すると仮定する場合、これと同一の表記法(notation)の下で、D(L1、L2)、D(L1、L3)、D(L1、L4)、D(L2、L3)、D(L2、L4)又はD(L3、L4)の中の少なくとも1つは実質的に0ではないことがあり得る。

【0099】

第5、第8乃至第11実施形態によれば、図37、図40乃至図43に示したように、メモリパターン270はパイプ形態の側壁部及び側壁部の底から内側に延長される底部を含む場合がある。この時、垂直電極VEはパイプ形態を有しながら、メモリパターン270の底部の上に配置されるスペーサー電極281及びスペーサー電極281を貫通する連結電極282を含む。連結電極282は図37、図42及び図43に示したように、第1不純物領域131に接続されるか、図40に示したように、第1不純物領域131とメモリパターン270との間に介在する導電パターン99に連結される。

【0100】

第6実施形態によれば、図38に示したように、メモリパターン270は、水平方向から見ると垂直電極VEと水平電極330との間にあり、垂直方向から見ると鋳型膜230の間にある局在された空間内に配置される。

【0101】

第7実施形態によれば、図39に示したように、メモリパターン270は水平電極330の上部面及び下部面を覆う部分を含む。これに加えて、メモリパターン270は垂直電極VEと水平電極330との間に配置されて上記の水平電極330の上部面を覆う部分及び下部面を覆う部分を連結する連結領域をさらに包む。一方、この実施形態によれば、ビットラインプラグBLPに隣接する水平電極330の一側壁はメモリパターン270によって覆われない。メモリパターン270が図16を参照して説明された水平電極330を形成する前にリセス領域320を覆うように形成される場合、メモリパターン270は図39に示す構造に形成される。

【0102】

第2プラグ350、即ちビットラインプラグBLPは、図37乃至図43に示したように、基板100又は第2不純物領域132に所定の深さに挿入される。一実施形態によれば、第2埋め込み膜340もやはり基板100又は第2不純物領域132に所定の深さに挿入される。一実施形態によれば、第2プラグ350は第2埋め込み膜340より大きい挿入深さを有するように形成される。同様に、図38乃至図41に例示的に示したように、第1プラグ280、即ち垂直電極VEもやはりその下に位置するパターン(例えば、第1不純物領域131又は導電パターン99)に所定の深さに挿入される。

【0103】

第10、第11実施形態によれば、図42及び図43に示したように、鋳型膜230と垂直電極VEとの間の水平方向の間隔W1は水平電極330と垂直電極VEとの間の水平方向の間隔W2より大きい。例えば、図14を参照して説明したリセス領域320を形成する間に、メモリパターン270の露出された外側壁が蝕刻される。図42の構造はこのような追加的な蝕刻の結果であり得る。変形された実施形態によれば、図43に示したように、メモリパターン270と鋳型膜230の側壁との間に保護パターン272が形成される。保護パターン272はメモリパターン270の上述した側壁リセスを限定する(及び/又は防止する)ために形成された蝕刻停止層の残存物であり得る。

【0104】

第12実施形態によれば、図44に示したように、水平電極330とメモリパターン270との間に整流素子を具現するための追加パターン(整流要素)400がさらに配置され得る。

【0105】

また第13実施形態によれば、図45に示したように、メモリパターン270は水平方向から見て垂直電極VE及び追加パターン400の間の空間に配置されるように提供される。メモリパターン270は垂直方向から見てモールド膜230の間に介在する。その結果として、モールド膜230及び垂直電極280の間の空間は追加的なパターン400及び垂直電極280の間の空間とは異なる。

[応用例]

【0106】

図46及び図47は本発明の実施形態による半導体装置を含む電子装置を図式的に説明するための図面である。

【0107】

図46を参照すれば、本発明の実施形態による半導体装置を含む電子装置1300はPDA、ラップトップ(laptop)コンピューター、携帯用コンピューター、ウェブタブレット(web tablet)、無線電話機、携帯電話、デジタル音楽再生器(digital music player)、有無線電子機器、又はこれらの中で少なくとも2つを含む複合電子装置の中の1つであり得る。電子装置1300はバス1350を通じて互に結合した制御器1310、キーパッド、キーボード、画面(display)のような入出力装置1320、メモリ1330、無線インターフェイス1340を含む。制御器1310は、例えば1つ以上のマイクロプロセッサー、デジタル信号プロセッサー、マイクロコントローラ、又はこれと類似なものを含む。メモリ1330は、例えば制御器1310によって実行される命令語を格納するのに使用される。メモリ1330は使用者データを格納するのにも使用でき、上述した本発明の実施形態による3次元半導体装置を含む。電子装置1300はRF信号を用いて無線通信ネットワークにデータを伝送するか、或いはネットワークからデータを受信するために無線インターフェイス1340を使用する。例えば無線インターフェイス1340はアンテナ、無線トランシーバー等を含む。電子装置1300はCDMA、GSM(登録商標)、NADC、E−TDMA、WCDMA、CDMA2000、Wi−Fi(登録商標)、Muni Wi−Fi、Bluetooth(登録商標)、DECT、Wireless USB(登録商標)、Flash−OFDM、IEEE 802.20、GPRS、iBurst、WiBro(登録商標)、WiMAX(登録商標)、WiMAX−Advanced(登録商標)、UMTS−TDD、HSPA、EVDO、LTE−Advanced、MMDS等のような通信システムの通信インターフェイスプロトコルを具現するのに利用される。

【0108】

図47を参照すれば、本発明の実施形態による3次元半導体装置はメモリシステム(memory system)を具現するために使用される。メモリシステム1400は大容量のデータを格納するためのメモリ装置1410及びメモリコントローラ1420を含むことができる。メモリコントローラ1420はホスト1430の読出し/書込み要請に応答してメモリ装置1410から格納されたデータを読出し又は書き込まれるようにメモリ装置1410を制御する。メモリコントローラ1420はホスト1430、例えばモバイル機器又はコンピューターシステムから提供されるアドレスをメモリ装置1410の物理的なアドレスにマッピングするためのアドレスマッピングテーブル(Address mapping table)を構成する。メモリ装置1410は上述した本発明の実施形態による3次元半導体装置を含む。

【0109】

上述された実施形態で開示された半導体装置は多様な形態の半導体パッケージ(semiconductor package)で具現される。例えば、本発明の実施形態による半導体装置はPoP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In−Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In−Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer−level Fabricated Package(WFP)、Wafer−Level Processed Stack Package(WSP)等の方式を用いてパッケージングされる。

【0110】

本発明の実施形態による3次元半導体装置が実装されたパッケージは該3次元半導体装置を制御するコントローラ及び/又は論理素子等をさらに包含することもあり得る。

【0111】

以上、添付された図面を参照して本発明の実施形態を説明したが、本発明が属する技術分野で通常の知識を有する者ならば、本発明がその技術的思想や必須的な特徴を変形しなくとも、他の具体的な形態で実施できることを理解できよう。従って、以上で記述した実施形態は全ての面で例示的であって、限定的ではないことを理解しなければならない。

【符号の説明】

【0112】

99 導電パターン

100 基板

110 素子分離パターン

120 活性領域

130 不純物領域

131 第1不純物領域

132 第2不純物領域

200 薄膜構造体

210 ゲート絶縁膜

215 下部絶縁スペーサー(下部絶縁パターン)

220 犠牲膜

225 層間絶縁膜

230 鋳型膜(モールド膜)

240 第1トレンチ

250 第1埋め込み膜

260 垂直ホール

270 メモリパターン

272 保護パターン

280 第1プラグ(垂直電極VE)

281 スペーサー電極

282 連結電極

300 キャッピングマスクパターン

310 第2トレンチ

311 広い領域

320 リセス領域

330 水平電極(ワードラインWL、又は、選択ラインSL)

340 第2埋め込み膜

345 絶縁スペーサー

350 第2プラグ(ビットラインプラグBLP)

360 上部配線(ビットラインBL)

400 追加パターン(整流要素)

1300 電子装置

1310 制御器

1320 入出力装置

1330 メモリ

1340 無線インターフェイス

1350 バス

1400 メモリシステム

1410 メモリ装置

1420 メモリコントローラ

1430 ホスト

WL ワードライン

ME メモリ要素

BL ビットライン

BLP ビットラインプラグ

VE 垂直電極

SL 選択ライン

SST 選択トランジスター

WLD ワードラインドライバー

BLD ビットラインドライバー

SSD 選択ドライバー

【技術分野】

【0001】

本発明は3次元半導体装置に係り、より具体的には3次元的に配列された抵抗性メモリセルを含む半導体メモリ装置に関する。

【背景技術】

【0002】

3D−ICメモリ技術はメモリ容量を増大させるための技術として、メモリセルを3次元的に配列することに関連された諸般技術を意味する。メモリ容量は、3D−ICメモリ技術以外にも、(1)パターン微細化技術及び(2)多重レベルセル(MLC)技術を通じても増大できる。しかし、パターン微細化技術は高費用の問題を随伴し、MLC技術はセル当たりの増加させ得るビット数で制限される。このような理由で、3D−IC技術はメモリ容量を増大させるための必然的な方法であるように見える。勿論、パターン微細化及びMLS技術を3D−IC技術と組み合わせた場合、メモリ容量のさらなる増加を具現できる点で、これらパターン微細化及びMLS技術も3D−IC技術とは独立に発展することが期待される。

【0003】

3D−IC技術の1つとして、パンチ−アンド−プラグ(punch−and−plug)技術が最近提案されている。パンチ−アンド−プラグ技術は多層の薄膜を基板の上に順に形成した後、その薄膜を貫通するプラグを形成する段階を含む。この技術を利用すれば、製造費用を大きく増加すること無く3Dメモリ素子のメモリ容量を大きく増加できるので、この技術は最近大きく注目を浴びている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】韓国特許公開第10−2009−0130180号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明の目的は増加された集積度を有する3次元半導体メモリ装置を提供することにある。

【課題を解決するための手段】

【0006】

本発明による3次元半導体装置は、チャンネル領域によって分離された第1及び第2不純物領域を含む基板、前記第1不純物領域に接続するビットライン、前記第2不純物領域に接続する垂直電極、前記基板と前記ビットラインとの間に配置される水平電極の積層体、及び、前記積層体と前記基板との間に配置される選択ラインを含む。この時、前記選択ラインは平面(planar)形状及び平面位置において、前記水平電極の各々と実質的に同一である。

【0007】

一実施形態で、前記選択ラインと前記垂直電極との間の水平距離は前記水平電極と前記垂直電極との間の水平距離と実質的に同一であり得る。

一実施形態で、前記ビットラインと前記第1不純物領域とを連結するビットラインプラグをさらに包含でき、前記選択ラインと前記ビットラインプラグとの間の水平距離は前記水平電極と前記ビットラインプラグとの間の水平距離と実質的に同一であり得る。

前記ビットラインは前記水平電極を横切り、前記選択ライン及び前記積層体は前記チャンネル領域を横切ることができる。

一実施形態で、前記選択ラインと重畳される水平的幅において、前記第1及び第2不純物領域は互に異なり得る。

一実施形態で、前記選択ラインは前記水平電極の各々と実質的に同一であり得る。

一実施形態で、前記積層体は垂直的な方向で前記水平電極の間に介在される鋳型膜をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記水平電極と前記垂直電極との間の間隔より大きくなり得る。

一実施形態で、前記水平電極と前記垂直電極との間に介在されるメモリパターンをさらに包含できる。

また、前記水平電極の高さにおける前記メモリパターンの水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの水平厚さより薄いことがあり得る。

一実施形態で、前記積層体は、前記水平電極の垂直方向において前記水平電極の間に介在する鋳型膜、及び前記水平電極と前記垂直電極との間に介在する整流要素(rectifying element)をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記整流要素と前記垂直電極との間の間隔と異なり得る。

一実施形態で,前記水平電極と前記垂直電極との間に介在するメモリパターンをさらに包含し、前記メモリパターンはカルコゲン化合物,磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを包含できる。

【0008】

本発明による3次元半導体装置は、互いに連結されて選択ライングループを構成する第1及び第2選択ライン、前記選択ラインの各々の上方に順に積層される複数のワードライン、前記第1及び第2選択ラインの間に一列に配列される垂直電極、前記選択ライングループの両側に各々一列に配列される複数のビットラインプラグ、及び前記ワードラインを横切りながら、前記ビットラインプラグを連結するビットラインを含む。

【0009】

一実施形態で、前記ワードラインは互いに電気的に分離されて、互いに異なる電圧を有するように構成され得る。

一実施形態で、前記ワードラインは前記垂直電極が配置される第1トレンチ及び前記ビットラインプラグが配置される第2トレンチを定義し、前記第2トレンチの各々は複数の前記ビットラインを横切る長さを有することができる。

一実施形態で、前記第1トレンチは複数の前記ビットラインを横切る長さを有することができる。

一実施形態で、前記第1及び第2選択ラインの各々はその上方に位置する前記ワードラインと平面(planar)形状及び平面位置において、実質的に同一であり得る。

一実施形態で、前記第1及び第2選択ラインと前記垂直電極との間の水平距離は前記ワードラインと前記垂直電極との間の水平距離と実質的に同一であり得る。

一実施形態で、前記第1及び第2選択ラインと前記ビットラインプラグとの間の水平距離は前記ワードラインと前記ビットラインプラグとの間の水平距離と実質的に同一であり得る。

一実施形態で、前記選択ライングループの下に配置される複数の活性パターンをさらに包含でき、前記活性パターンの各々は互いに離隔された一対のドレーン領域、前記ドレーン領域の間に位置するソース領域、前記ドレーン領域と前記ソース領域との間に位置する一対のチャンネル領域を含み、前記垂直電極は前記ソース領域に接続され、前記ビットラインプラグは前記ドレーン領域に接続され、前記第1及び第2選択ラインは前記一対のチャンネル領域と各々対向して前記一対のチャンネル領域の上に配置され得る。

一実施形態で、前記第1及び第2選択ラインと重畳される水平方向の幅において、前記ドレーン領域は前記ソース領域と異なり得る。

一実施形態で、前記第1及び第2選択ラインは前記ワードラインと実質的に同一の物質で形成され得る。

一実施形態で、垂直方向において前記ワードラインの間に介在する鋳型膜をさらに包含できる。前記鋳型膜と前記垂直電極との間の間隔は前記ワードラインと前記垂直電極との間の間隔より大きくなり得る。

一実施形態で、前記ワードラインと前記垂直電極との間に介在されるメモリパターンをさらに包含でき、前記ワードラインの高さにおける前記メモリパターンの水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの水平厚さより薄いことがあり得る。

一実施形態で、前記ワードラインと前記垂直電極との間に介在するメモリパターンをさらに包含できる。前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことができる。

【0010】

本発明による3次元半導体装置は、基板の上に配列された複数の積層体を含む電極構造体、前記電極構造体の上に配置されて前記積層体を横切る複数のビットライン、前記電極構造体を貫通する垂直電極、及び前記電極構造体を貫通し、その各々は前記ビットラインの中の対応する1つに連結されるビットラインプラグを含むことができる。前記積層体の各々は選択ライン及び前記選択ラインの上に順に積層された複数のワードラインを含み、同一の高さに配置される、奇数番目積層体のワードライン及び偶数番目積層体のワードラインは、各々、互いに連結され、前記奇数番目積層体の各々の選択ラインはそれの右側に位置する偶数番目積層体の選択ラインに連結されて選択ライングループを構成し、前記垂直電極は前記選択ライングループの各々の内部に位置し、前記ビットラインプラグは前記選択ライングループの間に位置することができる。

【0011】

本発明による3次元半導体装置は、基板内に第1方向にチャンネル領域によって互に離隔された第1不純物領域及び第2不純物領域、及び前記第1方向を横切る第2方向に前記チャンネル領域を横切って延長する選択ラインを含む選択トランジスターと、前記選択トランジスターの上に積層された複数のワードラインと、を含み、前記選択トランジスターは前記基板の第1不純物領域に連結されたビットラインと前記基板の第2不純物領域の上の垂直電極との間の電気的連結をコントロールするように配置され、前記複数のワードラインは前記選択ラインの前記第1方向に延長する幅と実質的に同一である、前記第1方向に延長する幅を有する。

【0012】

一実施形態で、前記選択トランジスターは前記チャンネル領域及び前記選択ラインの間にゲート絶縁膜をさらに含み得る。

一実施形態で、前記垂直電極及び前記少なくとも1つの選択トランジスター及び前記ワードラインの間にメモリパターンをさらに含み、前記垂直電極及び前記選択トランジスターの間の前記第1方向における距離がと前記垂直電極及び前記少なくとも1つのワードラインの間の前記第1方向における距離と同一であり得る。

一実施形態で、前記複数のワードラインの各々の少なくとも2つの面及び前記選択ラインの少なくとも2つの面を覆うメモリパターンをさらに含み得る。

一実施形態で、前記基板の上に、前記第1方向に延長し、前記第2方向に離隔された複数の活性領域を限定する複数の素子分離パターンと、前記複数の素子分離パターンを横切る複数のビットラインと、をさらに含み、

前記アクティブパターンの各々は、前記第1方向に沿って交互に配列された複数の第1不純物領域、チャンネル領域、及び第2不純物領域を含み、前記3次元半導体装置は、前記第2不純物領域の各々の上に複数の垂直電極と、前記複数のビットラインを前記第1不純物領域に各々連結させる複数のビットラインプラグと、前記基板の第1不純物領域の中1つに連結された前記複数のビットラインの中の1つと、前記基板の前記第2不純物領域の上の複数の垂直電極の中の1つとの間の電気的連結をコントロールするように各々配置された複数の選択トランジスターをさらに含み得る。

【発明の効果】

【0013】

本発明によれば、3次元的に配列された抵抗性メモリセルを含む半導体メモリ装置が提供される。この装置は3次元的に配列された抵抗性メモリセルへの電気的連結を制御するスイッチングトランジスターを具備できる。前記スイッチングトランジスターはその上方に位置する複数のワードラインの各々と実質的に同一の平面形状及び平面位置を有するように形成される。これによって前記スイッチングトランジスターは最大化されたチャンネル長さを有することができる。従って、増加された集積度を有し且つ高密度で高速の3次元抵抗性メモリ装置を、最小限のマスク工程数で提供できる。

【0014】

これに加えて、前記ワードラインはメモリパターンを形成した以後に金属性物質で形成され得る。これによって、前記半導体メモリ装置は増加された動作速度を具現することができる。

【図面の簡単な説明】

【0015】

【図1】本発明の例示的実施形態による3次元半導体装置のセルアレイの一部を示す回路図である。

【図2】本発明の第1実施形態による3次元半導体装置の、第1の製造段階を示す斜視図である。

【図3】図2の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図4】本発明の第1実施形態による3次元半導体装置の、第2の製造段階を示す斜視図である。

【図5】図4の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図6】本発明の第1実施形態による3次元半導体装置の、第3の製造段階を示す斜視図である。

【図7】図6の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図8】本発明の第1実施形態による3次元半導体装置の、第4の製造段階を示す斜視図である。

【図9】図8の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図10】本発明の第1実施形態による3次元半導体装置の、第5の製造段階を示す斜視図である。

【図11】図10の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0016】

【図12】本発明の第1実施形態による3次元半導体装置の、第6の製造段階を示す斜視図である。

【図13】図12の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図14】本発明の第1実施形態による3次元半導体装置の、第7の製造段階を示す斜視図である。

【図15】図14の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図16】本発明の第1実施形態による3次元半導体装置の、第8の製造段階を示す斜視図である。

【図17】図16の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図18】本発明の第1実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図19】図18の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図20】本発明の第1実施形態による3次元半導体装置の、第10の製造段階を示す斜視図である。

【図21】図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0017】

【図22】本発明の第2実施形態による3次元半導体装置の、第8の製造段階を示す斜視図である。

【図23】図22の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図24】本発明の第2実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図25】図24の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図26】本発明の第3実施形態による3次元半導体装置の、第9の製造段階を示す斜視図である。

【図27】図26の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【図28】本発明の例示的実施形態による3次元半導体装置のセルアレイを示す回路図である。

【図29】本発明の第2実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図30】本発明の第1実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図31】本発明の第3実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【0018】

【図32】本発明の第4実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。

【図33】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域のワードラインWLの配線構造を概略的に説明するための図面である。

【図34】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の選択ラインSLの配線構造を概略的に説明するための図面である。

【図35】本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の3次元的配線構造を概略的に説明するための図面である。

【図36】本発明の例示的実施形態による3次元半導体装置で特定のメモリセルを選択する方法を示す図面である。

【図37】本発明の第5実施形態に従う3次元半導体装置を示す断面図である。

【図38】本発明の第6実施形態に従う3次元半導体装置を示す断面図である。

【図39】本発明の第7実施形態に従う3次元半導体装置を示す断面図である。

【図40】本発明の第8実施形態に従う3次元半導体装置を示す断面図である。

【図41】本発明の第9実施形態に従う3次元半導体装置を示す断面図である。

【0019】

【図42】本発明の第10実施形態に従う3次元半導体装置を示す断面図である。

【図43】本発明の第11実施形態に従う3次元半導体装置を示す断面図である。

【図44】本発明の第12実施形態に従う3次元半導体装置を示す断面図である。

【図45】本発明の第13実施形態に従う3次元半導体装置を示す断面図である。

【図46】本発明による3次元半導体装置を含む電子装置を図式的に説明するための図面である。

【図47】本発明による3次元半導体装置を含む電子装置を図式的に説明するための図面である。

【発明を実施するための形態】

【0020】

本発明の長所及び特徴、そしてそれらを達成する方法は、添付される図面と共に詳細に後述した実施形態を参照すれば明確になるであろう。しかし、本発明は以下で開示される実施形態に限定されず、互に異なる多様な形態に具現できる。従って、本実施形態は単に、本発明の開示が完全になるように本発明が属する技術分野で通常の知識を有する者に発明の範疇を完全に説明するために提供され、本発明は請求項の範疇によってのみ定義される。明細書の全文に亘って同一参照符号は同一構成要素を意味する。

【0021】

本明細書で使用された用語は本発明の実施形態を説明するためにのみ使用され、本発明を制限しない。本明細書で、単数形は特別に明言しない限り複数形も含む。明細書で使用される‘含む(comprises)’及び/又は‘包含する(comprising)’は、言及された構成要素、構成段階、動作及び/又は素子に対して、1つ以上の他の構成要素、構成段階、動作及び/又は素子が存在する、又は追加される場合を排除しない。また、本明細書で、或る膜が他の膜又は基板の「上方」にあると言及される場合、その膜が他の膜又は基板上に直接存在するか、又はこれらの間に第3の膜が介在することを意味する。

【0022】

また、本明細書で記述する実施形態は、本発明の理想的な例示図である断面図及び/又は平面図を参照して説明される。図面において、膜及び領域の厚さは技術的内容の効果的な説明のために誇張され得る。従って、製造技術及び/又は許容誤差等によって例示図の形態が変形され得る。従って、本発明の実施形態は図示された特定形態に制限されず、製造工程によって生成される形態の変化も含む。例えば、直角に図示された蝕刻領域の角部の境界線はラウンドされるか、或いは所定曲率を有する形態であり得る。従って、図面で例示された領域は概略的な属性を有し、図面で例示された領域の形状は単に、素子の領域の典型的な形態を例示するためであって、発明の範疇を制限しない。

【0023】

図1は本発明の例示的実施形態による3次元半導体装置のセルアレイの一部を示す回路図である。

【0024】

図1を参照すれば、第1ノードN1と第2ノードN2とを連結する選択トランジスターSSTが提供される。選択トランジスターSSTの上方にはビットラインBLが配置され、ビットラインBLはビットラインプラグBLPを通じて第1ノードN1に連結される。

【0025】

複数のワードラインWLがビットラインBLと選択トランジスターSSTとの間に配置され、垂直電極VEが第2ノードN2に連結される。複数のメモリ要素MEが垂直電極VEに並列に連結される。メモリ要素MEの各々はワードラインWLの対応する1つに連結される。即ち、ワードラインWLの各々は、メモリ要素MEの対応する1つを介して、垂直電極VEに並列に連結される。

【0026】

選択トランジスターSSTは、そのゲート電極として機能する、選択ラインSLを具備する。一実施形態で、選択ラインSLはワードラインWLと平行に設けられる。

【0027】

図1の3次元半導体装置は、次に説明する本発明の実施形態を利用して具現され得る。

[第1実施形態]

【0028】

図2、4、6、8、10、12、14、16、乃至図18は、本発明の一実施形態による3次元半導体装置の、製造段階を順次示す斜視図であり、図3、5、7、9、11、13、15、17、乃至図19は、各々、図2、4、6、8、10、12、14、16、乃至図18の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

図20は、本発明の一実施形態による3次元半導体装置の斜視図であり、図21は、図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

【0029】

図2及び図3を参照すれば、基板100の上部領域に、複数の活性領域120を定義する複数の素子分離パターン110が形成される。基板100は半導体、絶縁体、導電体、及びこれらの組み合わせの中での1つを包含するように構成される。一実施形態によれば、基板100はシリコンウエハー又は(これを加工した結果物として提供される)シリコン基板を包含できるが、本発明の実施形態はこれに限定されない。

【0030】

素子分離パターン110の各々は、所定の方向(例えば、x方向)と平行な長軸を有するライン形態のパターンをとる。これに加えて、素子分離パターン110は互に平行であり、従って、活性領域120もやはり互に平行であり、その各々はライン形態のパターンをとる。素子分離パターン110はシリコン酸化物のような少なくとも1つの絶縁物で形成できるが、本実施形態はこれに限定されない。

【0031】

図4及び図5を参照すれば、活性領域120の上部に不純物領域130を形成する。不純物領域130は基板100の上に2次元的に形成され得る。例えば、不純物領域130の複数の領域が、活性領域120毎に、素子分離パターン110の長軸に沿って互に離隔されて形成され得る。不純物領域130は図1を参照して説明した第1ノードN1として機能する第2不純物領域132、及び第2ノードN2として機能する第1不純物領域131を含む。

【0032】

第1及び第2不純物領域131、132は、素子分離パターン110の長軸に沿って交互に配列される。第1及び第2不純物領域131、132はその内部に注入された、ホウ素、アルミニウム、燐、及び/又は砒素のようなn形又はp形不純物を包含するが、本実施形態はこれに限定されない。

【0033】

不純物領域130を形成する段階は、素子分離パターン110の上に活性領域120を横切るマスクパターン(図示せず)を形成する段階及びマスクパターンをイオンマスクとして使用するイオン注入工程を実施する段階を含む。

【0034】

変形された実施形態で、不純物領域130は素子分離パターン110を形成する前に形成される。これに加えて、活性領域120又は基板100内に不純物を注入する少なくとも1回のイオン注入工程が選択的に実施される。例えば、選択トランジスターSSTの閾値電圧を調節するために、活性領域120の内に不純物を注入するイオン注入工程が選択的に実施される。又は、基板100の内にウェル領域(well region)を形成するイオン注入工程が選択的に実施される。このような追加的なイオン注入工程は素子分離パターン110を形成する前又は後に実施される。

【0035】

図6及び図7を参照すれば、ゲート絶縁膜210が、不純物領域130が形成された結果物の上に形成され、薄膜構造体200がゲート絶縁膜210の上に形成される。薄膜構造体200は、交互に積層された、複数の犠牲膜220及び複数の鋳型膜230を含む。

【0036】

ゲート絶縁膜210はシリコン酸化膜及び高誘電膜の中の少なくとも1つを含む。高誘電膜はハフニウム酸化物、アルミニウム酸化物、ジルコニウム酸化物のような物質からなるが、本実施形態はこれに限定されない。一実施形態で、ゲート絶縁膜210は活性領域120の上部面を熱酸化して形成される。他の実施形態で、ゲート絶縁膜210は蒸着技術を使用して形成される蒸着膜である。

【0037】

犠牲膜220は鋳型膜230に対して蝕刻選択性(etch selectivity)を有しながら蝕刻され得る物質で形成される。即ち、所定の蝕刻レシピーを使用して犠牲膜220を蝕刻する工程で、犠牲膜220は鋳型膜230の蝕刻を制限しながら(及び/又は、防止しながら)蝕刻され得る物質で形成される。公知のように、このような蝕刻選択性は鋳型膜230の蝕刻速度に対する犠牲膜220の蝕刻速度の比率として定量的に表現される。一実施形態によれば、犠牲膜220は鋳型膜230に対して1:10乃至1:200(さらに限定的には、1:30乃至1:100)の蝕刻選択比を有する物質の1つである。例えば、鋳型膜230はシリコン酸化膜及びシリコン窒化膜の中の少なくとも1つであり、犠牲膜220はシリコン膜、シリコン酸化膜、シリコンカーバイド、及びシリコン窒化膜の中から選択される鋳型膜230と異なる物質である。以下では、本発明の技術的思想に対する理解を容易にするために、鋳型膜230はシリコン酸化膜であり、犠牲膜220はシリコン窒化膜である実施形態を例示的に説明する。

【0038】

図8及び図9を参照すれば、薄膜構造体200をパターニングして第1トレンチ240を形成した後、第1埋め込み膜250を形成して第1トレンチ240を満たす。

【0039】

第1トレンチ240は不純物領域130の一部を露出するように形成され、その各々は素子分離パターン110を横切るように形成される。第1トレンチ240は、素子分離パターン110の長軸に沿って配列される第1不純物領域131を露出する。

【0040】

第1埋め込み膜250は絶縁性物質を少なくとも1つを含む。例えば、第1埋め込み膜250はSOG物質及びシリコン酸化物の中の少なくとも1つを含む。一実施形態で、第1埋め込み膜250は犠牲膜220及び鋳型膜230に対して蝕刻選択性を有する物質で形成される。

【0041】

図10及び図11を参照すれば、第1トレンチ240の下に位置する第1不純物領域131を露出する複数の垂直ホール260を形成する。以後、垂直ホール260の内側壁を覆うメモリパターン270及び垂直ホール260の残りの空間を満たす第1プラグ280を形成する。

【0042】

垂直ホール260の形成は、薄膜構造体200の上にマスクパターンを形成する段階と、その後、これを蝕刻マスクとして使用して第1埋め込み膜250をパターニングする段階とを含む。一部の実施形態によれば、示したように、垂直ホール260の各々は第1トレンチ240より広い幅を有するように形成される。

【0043】

メモリパターン270は情報を格納できるようにする物性を有する物質を少なくとも1つ含む。例えば、メモリパターン270はそれを通過する電流によってその抵抗が選択的に変化する物質(即ち、可変抵抗特性を有する物質)を少なくとも1つ含む。

【0044】

一実施形態によれば、メモリパターン270はそれに印加される熱によってその電気的抵抗が変化する物質(例えば、カルコゲン化合物(chalcogenide))を少なくとも1つ含む。カルコゲン化合物はアンチモン(antimony、Sb)、テルル(tellurium、Te)、及びセレン(selenium、Se)の中の少なくとも1つを含む。例えば、メモリパターン270は、テルルTeは約20原子%乃至約80原子%の濃度を有し、アンチモンSbは約5原子%乃至約50原子%の濃度を有し、残りはゲルマニウムGeであるカルコゲン化合物を含む。これに加えて、メモリパターン270のためのカルコゲン化合物は、不純物として、N、O、C、Bi、In、B、Sn、Si、Ti、Al、Ni、Fe、Dy、及びLaの中の少なくとも1つを含むことができる。又は、メモリパターン270はGeBiTe、InSb、GeSb、及びGaSbの中の1つで形成されることもあり得る。

【0045】

他の実施形態によれば、メモリパターン270はペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含む。例えば、メモリパターン270は、酸化ニオブ(niobium oxide)、酸化チタン(titanium oxide)、酸化ニッケル(nikel oxide)、酸化ジルコニウム(zirconium oxide)、酸化バナジウム(vanadium oxide)、PCMO((Pr、Ca)MnO3)、ストロンチウム−チタニウム酸化物(strontium−titanium oxide)、バリウム−ストロンチウム−チタニウム酸化物(barium−strontium−titanium oxide)、ストロンチウム−ジルコニウム酸化物(strontium−zirconium oxide)、バリウム−ジルコニウム酸化物(barium−zirconium oxide)、又はバリウム−ストロンチウム−ジルコニウム酸化物(barium−strontium−zirconium oxide)等の少なくとも1つを含む。これに加えて、本発明の一実施形態によれば、メモリパターン270は、情報を格納できるようにする物性に加えて、自己整流特性(self−rectifying property)又は非線形の電流−電圧特性を示す物質の中の少なくとも1つで形成される。

【0046】

第1プラグ280の各々は、導電性物質(例えば、ドーピングされた半導体、金属、導電性金属窒化物、シリサイド、及び、炭素ナノチューブ又はグラフェン等のナノ構造体の中の少なくとも1つを含む。

【0047】

この実施形態によれば、メモリパターン270の各々は図1を参照して説明されたメモリ要素MEとして使用され、第1プラグ280の各々は図1を参照して説明された垂直電極VEとして使用される。

【0048】

図12及び図13を参照すれば、薄膜構造体200をパターニングして、不純物領域130の中の他の一部を露出させる第2トレンチ310を形成する。一実施形態で、第2トレンチ310を形成する段階は第1プラグ280が形成された結果物を覆うキャッピングマスクパターン300を形成した後、これを蝕刻マスクとして使用して薄膜構造体200を異方的に蝕刻する段階を含む。

【0049】

第2トレンチ310の各々は素子分離パターン110を横切るように形成される。第2トレンチ310は、素子分離パターン110の長軸に沿って配列される第2不純物領域132を露出する。また、第2トレンチ310によって、犠牲膜220及び鋳型膜230の側壁が露出される。

【0050】

一部の実施形態によれば、図12に示したように、第2トレンチ310の各々は、狭い領域及び該狭い領域より広い幅を有する広い領域311を含む。1つの第2トレンチ310において、前記狭い領域及び広い領域311は交互に配列されて互に連結される。広い領域311の各々は第2不純物領域132の対応する1つを露出するように形成され、前記狭い領域の各々は素子分離パターン110の対応する1つを横切るように形成される。一実施形態において、第2トレンチ310はキャッピングマスクパターン300をハードマスクとして使用してパターニングされる。

【0051】

図14及び図15を参照すれば、犠牲膜220を選択的に除去して鋳型膜230の間にリセス領域320を形成する。リセス領域320を形成する段階は第2トレンチ310によって露出される犠牲膜220を側方向に蝕刻(例えば、等方的に蝕刻)する段階を含む。

【0052】

第2トレンチ310が複数の素子分離パターン110を横切るライン形態であるので、上述した犠牲膜220の選択的除去が遂行できる。即ち、ライン形態の第2トレンチ310が存在するので、エッチャントが犠牲膜220まで供給される。

【0053】

リセス領域320は第1トレンチ240の境界まで拡張される。例えば、リセス領域320は第1埋め込み膜250及びメモリパターン270の外側壁を露出するように形成される。

【0054】

図16及び図17を参照すれば、リセス領域320を満たす水平電極330を形成する。水平電極330の各々はリセス領域320の中の対応する1つを満たすように形成される。この実施形態によれば、水平電極330は図1を参照して説明したワードラインWL及び選択ラインSLとして使用される。

【0055】

水平電極330を形成する段階は、リセス領域320を満たす導電膜を形成する段階、及び第2トレンチ310から導電膜を除去して導電膜をリセス領域320の内部空間に局所化させる段階を含む。一実施形態では、導電膜は第2トレンチ310を完全に満たさず、第2トレンチ310の内壁をコンフォーマルに覆うように形成される。この場合、導電膜を除去する段階は等方性蝕刻工程(例えば、湿式蝕刻工程)を通じて遂行できる。

【0056】

水平電極330は導電性物質を少なくとも1つ含む。例えば、水平電極330はドーピングされた半導体、金属物質又は金属窒化物の中の少なくとも1つで形成される。水平電極330が金属物質又は金属窒化物で形成される場合、本発明による半導体メモリ装置の動作速度特性は改善できる。

【0057】

図18及び図19を参照すれば、第2不純物領域132に各々接続する第2プラグ350が形成される。この実施形態によれば、第2プラグ350は図1を参照して説明されたビットラインプラグBLPとして使用される。第2プラグ350を形成する段階は、第2トレンチ310を満たす第2埋め込み膜340を形成する段階と、その後、第2埋め込み膜340を貫通する第2プラグ350を形成する段階を含む。

【0058】

一実施形態において、第2埋め込み膜340は蒸着技術の中の1つを使用して形成され、その蒸着厚さは第2トレンチ310の狭い領域の幅の1/2より大きく、且つ第2トレンチ310の広い領域311の幅の1/2より小さい。この場合、第2埋め込み膜340は第2トレンチ310の狭い領域を完全に満たすが、広い領域311を完全に満たさない。即ち、上述した蒸着厚さ条件が充足される場合、第2埋め込み膜340は広い領域311に自己整列的に形成される開口部を有する。

【0059】

第2埋め込み膜340が蒸着技術を使用して形成される場合、第2埋め込み膜340は広い領域311の底を覆う。従って、第2プラグ350を形成する前に、広い領域311の底から第2埋め込み膜340を除去する異方性蝕刻工程が実施される。

【0060】

第2プラグ350は、異方性蝕刻工程が実施された結果物の上に導電膜を形成した後、所定のノード分離工程を実施することによって形成される。導電膜は広い領域311に形成される開口部を満たすように形成されて、第2不純物領域132に連結される。ノード分離工程の結果として、広い領域311の内に局所化され、2次元的に分離された第2プラグ350が得られる。

【0061】

図20は、本実施形態による3次元半導体装置の、第10の製造段階を示す斜視図であり、図21は、図20の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

図20及び図21を参照すれば、キャッピングマスクパターン300の上に上部配線360を形成する。上部配線360は第1及び第2トレンチ240、310、及び水平電極330を横切るように形成され、上部配線360の各々はその下に配置される第2プラグ350の中の複数個と連結される。この実施形態によれば、上部配線360は図1を参照して説明したビットラインBLとして使用される。

[第2実施形態]

【0062】

図22及び図24は本発明の第2実施形態による3次元半導体装置の、第8、第9の製造段階を示す斜視図であり、図23及び図25は、各々、図22及び図24の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。

説明を簡単にするために、図2乃至図21を参照して説明した先述の第1実施形態と実質的に同一の構成要素に対する説明は省略する。この実施形態は少なくとも2つの点で図16乃至図19を参照して説明した先述の実施形態と区別される。

【0063】

第1点としては、図22及び図23に示したように、第2トレンチ310はその長軸方向に沿って計測された幅が均一である。即ち、第2トレンチ310の幅は素子分離パターン110及び第2不純物領域132の上で実質的に同一である。

第2点としては、水平電極330は第2トレンチ310の形成後に形成されるのではなく、薄膜構造体200の一部として提供される。即ち、この実施形態によれば、薄膜構造体200は順に積層される複数の導電膜及び複数の絶縁膜を含む。この場合、第2トレンチ310の形成によって、薄膜構造体200の導電膜及び絶縁膜は各々先の実施形態の水平電極330及び鋳型膜230として機能する。

【0064】

一方、第2トレンチ310の幅が均一であるので、第2プラグ350は図18を参照して説明したように自己整列的に形成されることが困難になる。この実施形態によれば、図24及び図25に示したように、第2プラグ350を形成する段階は第2トレンチ310を完全に満たす第2埋め込み膜340を形成した後、所定のパターニング工程を実施して第2不純物領域132を露出させる開口部を形成する段階、及び開口部を導電性物質で満たす段階を含む。第2プラグ350と水平電極330との間を電気的に分離するために、第2プラグ350の各々の側壁を覆う絶縁スペーサー345がさらに形成される。

【0065】

上で説明されなかった他の工程段階は図2乃至図20を参照して説明した先述の第1実施形態の工程段階と同一である。

[第3実施形態]

【0066】

図26は本発明の第3実施形態による3次元半導体装置の、第9の製造段階を示す斜視図であり、図27は図26の一点鎖線I−I’及びII−II’線に沿って切断した断面を示す断面図である。説明を簡単にするために、図2乃至図21を参照して説明した先述の第1実施形態と実質的に同一の構成要素に対する説明は省略される。

【0067】

図10及び図11を再び参照すれば、第1埋め込み膜250を選択的に除去して第1トレンチ240を通じてメモリパターン270の側壁を露出する。続いて、メモリパターン270の露出された側壁を蝕刻して第1プラグ280の側壁を露出する。これによって、図26及び図27に示したように、メモリパターン270の各々は第1トレンチ240によって水平方向に分離された2つの部分を有する。第1トレンチ240の両側に位置するメモリパターン270の2つの部分は互に異なるデータ格納箇所として機能するので、このような分離工程は格納されたデータ間の攪乱問題を解決できる。

【0068】

以後、第1埋め込み膜250が除去されることによって、形成される空間は絶縁膜(例えば、キャッピングマスクパターン300)で満たされる。上で説明されなかった他の工程段階は図2乃至図21を参照して説明した先述の第1実施形態の工程段階と同一である。

【0069】

図28は本発明の例示的実施形態による3次元半導体装置のセルアレイを示す回路図であり、図29乃至図32は本発明の例示的実施形態による3次元半導体装置のセルアレイ領域を概略的に示す斜視図である。以下、説明を簡単にするために、図1及び、図2乃至図26を参照して説明した第1乃至第3実施形態と実質的に同一の構成要素に対する説明は省略する。また、図29乃至図32においては理解の便のため、キャッピングマスクパターン300及び鋳型膜230の全てを省略し、水平電極330の一部を切欠いてある。

【0070】

図28を参照すれば、複数の選択トランジスターSSTが複数のビットラインプラグBLPを通じてビットラインBLに並列に連結される。ビットラインプラグBLPの各々はそれに隣接する一対の選択トランジスターSSTに共通に連結される。

【0071】

複数のワードラインWL及び複数の垂直電極VEがビットラインBLと選択トランジスターSSTとの間に配置される。垂直電極VEはビットラインプラグBLPの間に配置される。例えば、垂直電極VE及びビットラインプラグBLPはビットラインBLと平行な方向に沿って交互に配列される。これに加えて、垂直電極VEの各々はそれに隣接する一対の選択トランジスターSSTに共通に連結される。

【0072】

複数のメモリ要素MEが垂直電極VEの各々に並列に連結される。メモリ要素MEの各々はワードラインWLの対応する1つに連結される。即ち、ワードラインWLの各々は、メモリ要素MEの対応する1つを通じて、垂直電極VEの対応する1つに連結される。

【0073】

選択トランジスターSSTの各々は、そのゲート電極として機能する、選択ラインSLを具備する。一実施形態において、選択ラインSLはワードラインWLと平行である。

【0074】

図29乃至図32を参照すれば、図28のビットラインBLとして機能する複数の上部配線360が基板100の上に配置される。基板100は上部配線360と平行な複数の活性領域120を有する。活性領域120は基板100の上部領域に形成される複数の素子分離パターン110によって定義される。平面(planar)図において、即ち上方から垂直方向に見る時、素子分離パターン110は上部配線360の間に位置し、上部配線360と平行な長軸を有するように形成される。なお図29乃至図32で、参照符号Cはチャンネルを示す。

【0075】

活性領域120の各々には、上部配線360と平行な方向に沿って一列に配列される複数の不純物領域130が形成される。不純物領域130は互に離隔されてチャンネル領域を定義する。不純物領域130は複数の第1不純物領域131及び複数の第2不純物領域132を包含し、第1不純物領域131及び第2不純物領域132は互に交互に配列される。

【0076】

基板100の上には2次元的に配列される複数の第1プラグ280が配列される。第1プラグ280は図28の垂直電極VEとして機能し、その各々は第1不純物領域131の対応する1つに連結される。

【0077】

基板100の上には2次元的に配列される複数の第2プラグ350が配列される。第2プラグ350は図28のビットラインプラグBLPとして機能し、その各々は第2不純物領域132の対応する1つに連結される。

【0078】

チャンネル領域の上には素子分離パターン110を横切る複数の水平電極330が配置される。水平電極330は図28のワードラインWL及び選択ラインSLとして機能する。水平電極330の中の複数の電極がチャンネル領域の各々の上方に順に積層される。一実施形態において、水平電極330の中の最下部の電極は選択ラインSLとして機能し、残りはワードラインWLとして機能する。

【0079】

水平電極330は第1及び第2プラグ280、350から水平方向に離隔される。例えば、水平電極330と第1プラグ280との間には図28のメモリ要素MEとして機能するメモリパターン270が介在し、水平電極330と第2プラグ350との間には絶縁膜(例えば、図18及び図19に示した第2埋め込み膜340)が介在する。

【0080】

第1プラグ280の各々は第1不純物領域131の中の対応する1つとワードラインWLとして使用される水平電極330の中の1つの間の導電経路として使用される。これによって、第1プラグ280は第1不純物領域131には連結されるが、上部配線360からは離隔される。第2プラグ350の各々は第2不純物領域132の中の対応する1つとビットラインBLの中の対応する1つとの間の導電経路として使用される。この時、第2プラグ350の各々は上述したように絶縁膜によって水平電極330から離隔される。

【0081】

一方、図2乃至図21を参照して説明した第1実施形態によれば、図30に示したように、第2プラグ350の各々は円柱に近い形状を有するように形成される。反面、図22及び図24を参照して説明した第2実施形態によれば、図29に示したように、第2プラグ350の各々は直方体柱形状を有するように形成される。

【0082】

また、図26を参照して説明した第3実施形態によれば、図31に示したように、メモリパターン270の各々は水平的に分離された2つの部分を有する。即ち、メモリパターン270の各々は第1プラグ280の左側壁を覆う部分とこれから離隔されて右側壁を覆う部分とを含む。

[第4実施形態]

【0083】

本発明の第4実施形態によれば、図32に示したように、第1プラグ280の下には導電パターン99が各々配置され、メモリパターン270の下には下部絶縁パターン215が各々配置される。このような実施形態は図40及び図41を参照して後でより詳細に説明する

【0084】

図33乃至図35は本発明の例示的実施形態による3次元半導体装置のセルアレイ領域の配線構造を概略的に説明するための図面である。より具体的に、図33はワードラインWLの連結構造を示し、図34は選択ラインSLの連結構造を示し、図35はセルアレイ領域の配線の相対的配置を3次元的に示す。説明を簡単にするために、図1及び図28を参照して説明した例示的実施形態と実質的に同一又は類似の構成要素に対する説明は省略する。

【0085】

図33及び図34を参照すれば、ビットラインBLの各々の下にはビットラインプラグBLP及び垂直電極VEが交互に配列される。ビットラインBLはビットラインドライバーBLDに各々連結される。

【0086】

図33を参照すると、ワードラインWL1乃至WL16がビットラインBLを横切るように配置される。ワードラインWL1乃至WL16の各々はビットラインプラグBLPの1列及び垂直電極VEの1列の間に配置される。また、ワードラインWL1乃至WL16の各々は第1又は第2ワードラインドライバーWLD1又はWLD2の中の1つに連結される。例えば、ワードラインWL1乃至WL16の中の奇数番目のものは第1ワードラインドライバーWLD1に連結され、ワードラインWL1乃至WL16の中の偶数番目のものは第2ワードラインドライバーWLD2に連結される。ビットラインBLを含むセルアレイ領域は第1ワードラインドライバーWLD1と第2ワードラインドライバーWLD2との間に配置され得る。これによって、図33に示したように、第1及び第2ワードラインドライバーWLD1、WLD2の各々に連結されるワードラインWL1乃至WL16はフィンガー構造を形成する。

【0087】

一方、図34を参照すると、選択ラインSL1乃至SL14がビットラインBLを横切るように配置される。ワードラインWL1乃至WL16と同様に、選択ラインSL1乃至SL14の各々はビットラインプラグBLPの1列及び垂直電極VEの1列の間に配置される。例えば、図29乃至図32に示したように、選択ラインSL1乃至SL14の各々の上方には複数のワードラインWLが積層される。

【0088】

選択ラインSL1乃至SL14は複数の選択ライングループを構成し、選択ライングループの各々は互に連結された隣接する一対の選択ラインを含む。一実施形態によれば、選択ライングループの各々はビットラインBLを横切る方向に沿って配列される垂直電極VEの両側に位置する一対の選択ラインSL1乃至SL14で構成される。即ち、垂直電極VEは選択ライングループの各々の内部に位置し、ビットラインプラグBLPは選択ライングループの間に位置する。

【0089】

選択ライングループは、図34に示すように、複数の選択ラインドライバーSSD1乃至SSD7に各々連結される。選択ラインドライバーSSD1乃至SSD7は独立的に動作するように構成される。

【0090】

一方、図33では、特定の高さ、即ち薄膜構造体200の特定の層に配列されたワードラインの配置構造を示したが、本実施形態による3次元半導体装置は複数の層の各々で図33の配置構造を有するように配列されたワードラインを含む場合もある。例えば、図35に示したように、ワードラインドライバーWLD11乃至WLD14、WLD21乃至24は各々の層に配列されるワードラインを独立的に制御するように構成され、これらの中の一部WLD11乃至WLD14はワードラインの中で偶数番目のものを制御し、他の一部WLD21乃至24はワードラインの中で奇数番目のものを制御するように構成される。

【0091】

図36は本発明の一実施形態による3次元半導体装置で特定のメモリセルを選択する方法を示す図面である。

【0092】

図36に示したように、ビットラインドライバーBLDの中の1つ、選択ドライバーSSD1乃至SSD3の中の1つ、そしてワードラインドライバーWLD1、WLD2の中の1つを選択すれば、3次元的に配列されるメモリセルの中の1つが一意的に選択される。

【0093】

例えば、ビットラインドライバーBLDの中の1つを選択し、選択ドライバーSSD1乃至SSD3の中の1つを選択すれば、これらに連結された導電ラインの交差点に位置する一対の選択トランジスターSSTが選択される。しかし、これらの選択トランジスターSSTは1つの垂直電極VEを共有するので、このような選択は1つの垂直電極VEを選択することが可能である。これに加えて、図35に示したように、1つの垂直電極VEの両側に配列される複数のワードラインWLは全て電気的に分離されるので、これらの中の1つを選択すれば、1つのワードライン、1つのビットライン及びこれらの間に介在される1つのメモリセルを連結する一意的な経路を形成できる。

【0094】

図37乃至図45は各々、本発明の第5乃至第13実施形態に従う3次元半導体装置を示す断面図である。上述した実施形態による3次元半導体装置は以下で説明する本発明の技術的特徴の中の少なくとも1つを有するように構成される。

【0095】

一実施形態によれば、図29乃至図32に示したように、選択ラインSLの各々は、少なくとも所定の領域の内で、その上方に位置するワードラインWLと実質的に同一の平面(planar)形状及び同一の平面配置を有する。例えば、図37乃至図39、図42、及び図43に例示的に示したように、選択ラインSLとワードラインWLとは垂直に互いに整列された側壁を有する。即ち、選択ラインSLと垂直電極VEの側壁との間の距離は、ワードラインWLと垂直電極VEの側壁との間の距離と実質的に同一である。同様に、選択ラインSLとビットラインプラグBLPの側壁との間の距離は、ワードラインWLとビットラインプラグBLPの側壁との間の距離と実質的に同一である。

【0096】

一実施形態によれば、選択ラインSLとワードラインWLとは実質的に同一の物質で形成される。一方、他の実施形態によれば、選択ラインSLとワードラインWLとは互に異なる物質で形成されるか、或いは互に整列されない場合もある。例えば、選択ラインSLとして使用される水平電極330はワードラインWLとして使用される水平電極330を形成する以前に形成される。即ち、図6を参照して説明された薄膜構造体200を形成する以前に、選択ラインSLを形成するための別の工程がさらに実施される。

【0097】

これに加えて一実施形態によれば、薄膜構造体200を形成する以前に、選択ラインSLをパターニングして第1不純物領域131を露出させる開口部を形成する段階がさらに実施される。一実施形態によれば、後述する図41に示すように、開口部は層間絶縁膜225及びこれを貫通する連結電極282によって満たされる。他の実施形態によれば、後述する図40に示すように、開口部は下部絶縁スペーサー215及び導電パターン99によって満たされる。

【0098】

一方、本発明の一実施形態によれば、図2乃至図6を参照して説明したように、不純物領域130は薄膜構造体200を形成する以前に形成され、第1及び第2トレンチ240、310の形成は薄膜構造体200の形成以後に遂行される。この場合、水平電極330は不純物領域130を形成するためのマスクとしては使用されない。その結果として、選択ラインSLと第1及び第2不純物領域131、132との間の相対的配置は、水平電極330が第1及び第2不純物領域131、132を形成するためのマスクとして使用される場合に比べて異なることがあり得る。

例えば、第1及び第2不純物領域131、132とこれら各々に隣接する選択ラインSLとの間の重畳幅は互いに異なり得る。具体的には、

図37乃至図40に示したように、第1不純物領域131の左側及び右側領域とこれらに隣接する選択ラインSLとの間の重畳幅L1、L2とし、第2不純物領域132の左側及び右側領域とこれらに隣接する選択ラインSLとの間の重畳幅をL3、L4とする。そしてL1とL2の差をD(L1,L2)と表現すると仮定する場合、これと同一の表記法(notation)の下で、D(L1、L2)、D(L1、L3)、D(L1、L4)、D(L2、L3)、D(L2、L4)又はD(L3、L4)の中の少なくとも1つは実質的に0ではないことがあり得る。

【0099】

第5、第8乃至第11実施形態によれば、図37、図40乃至図43に示したように、メモリパターン270はパイプ形態の側壁部及び側壁部の底から内側に延長される底部を含む場合がある。この時、垂直電極VEはパイプ形態を有しながら、メモリパターン270の底部の上に配置されるスペーサー電極281及びスペーサー電極281を貫通する連結電極282を含む。連結電極282は図37、図42及び図43に示したように、第1不純物領域131に接続されるか、図40に示したように、第1不純物領域131とメモリパターン270との間に介在する導電パターン99に連結される。

【0100】

第6実施形態によれば、図38に示したように、メモリパターン270は、水平方向から見ると垂直電極VEと水平電極330との間にあり、垂直方向から見ると鋳型膜230の間にある局在された空間内に配置される。

【0101】

第7実施形態によれば、図39に示したように、メモリパターン270は水平電極330の上部面及び下部面を覆う部分を含む。これに加えて、メモリパターン270は垂直電極VEと水平電極330との間に配置されて上記の水平電極330の上部面を覆う部分及び下部面を覆う部分を連結する連結領域をさらに包む。一方、この実施形態によれば、ビットラインプラグBLPに隣接する水平電極330の一側壁はメモリパターン270によって覆われない。メモリパターン270が図16を参照して説明された水平電極330を形成する前にリセス領域320を覆うように形成される場合、メモリパターン270は図39に示す構造に形成される。

【0102】

第2プラグ350、即ちビットラインプラグBLPは、図37乃至図43に示したように、基板100又は第2不純物領域132に所定の深さに挿入される。一実施形態によれば、第2埋め込み膜340もやはり基板100又は第2不純物領域132に所定の深さに挿入される。一実施形態によれば、第2プラグ350は第2埋め込み膜340より大きい挿入深さを有するように形成される。同様に、図38乃至図41に例示的に示したように、第1プラグ280、即ち垂直電極VEもやはりその下に位置するパターン(例えば、第1不純物領域131又は導電パターン99)に所定の深さに挿入される。

【0103】

第10、第11実施形態によれば、図42及び図43に示したように、鋳型膜230と垂直電極VEとの間の水平方向の間隔W1は水平電極330と垂直電極VEとの間の水平方向の間隔W2より大きい。例えば、図14を参照して説明したリセス領域320を形成する間に、メモリパターン270の露出された外側壁が蝕刻される。図42の構造はこのような追加的な蝕刻の結果であり得る。変形された実施形態によれば、図43に示したように、メモリパターン270と鋳型膜230の側壁との間に保護パターン272が形成される。保護パターン272はメモリパターン270の上述した側壁リセスを限定する(及び/又は防止する)ために形成された蝕刻停止層の残存物であり得る。

【0104】

第12実施形態によれば、図44に示したように、水平電極330とメモリパターン270との間に整流素子を具現するための追加パターン(整流要素)400がさらに配置され得る。

【0105】

また第13実施形態によれば、図45に示したように、メモリパターン270は水平方向から見て垂直電極VE及び追加パターン400の間の空間に配置されるように提供される。メモリパターン270は垂直方向から見てモールド膜230の間に介在する。その結果として、モールド膜230及び垂直電極280の間の空間は追加的なパターン400及び垂直電極280の間の空間とは異なる。

[応用例]

【0106】

図46及び図47は本発明の実施形態による半導体装置を含む電子装置を図式的に説明するための図面である。

【0107】

図46を参照すれば、本発明の実施形態による半導体装置を含む電子装置1300はPDA、ラップトップ(laptop)コンピューター、携帯用コンピューター、ウェブタブレット(web tablet)、無線電話機、携帯電話、デジタル音楽再生器(digital music player)、有無線電子機器、又はこれらの中で少なくとも2つを含む複合電子装置の中の1つであり得る。電子装置1300はバス1350を通じて互に結合した制御器1310、キーパッド、キーボード、画面(display)のような入出力装置1320、メモリ1330、無線インターフェイス1340を含む。制御器1310は、例えば1つ以上のマイクロプロセッサー、デジタル信号プロセッサー、マイクロコントローラ、又はこれと類似なものを含む。メモリ1330は、例えば制御器1310によって実行される命令語を格納するのに使用される。メモリ1330は使用者データを格納するのにも使用でき、上述した本発明の実施形態による3次元半導体装置を含む。電子装置1300はRF信号を用いて無線通信ネットワークにデータを伝送するか、或いはネットワークからデータを受信するために無線インターフェイス1340を使用する。例えば無線インターフェイス1340はアンテナ、無線トランシーバー等を含む。電子装置1300はCDMA、GSM(登録商標)、NADC、E−TDMA、WCDMA、CDMA2000、Wi−Fi(登録商標)、Muni Wi−Fi、Bluetooth(登録商標)、DECT、Wireless USB(登録商標)、Flash−OFDM、IEEE 802.20、GPRS、iBurst、WiBro(登録商標)、WiMAX(登録商標)、WiMAX−Advanced(登録商標)、UMTS−TDD、HSPA、EVDO、LTE−Advanced、MMDS等のような通信システムの通信インターフェイスプロトコルを具現するのに利用される。

【0108】

図47を参照すれば、本発明の実施形態による3次元半導体装置はメモリシステム(memory system)を具現するために使用される。メモリシステム1400は大容量のデータを格納するためのメモリ装置1410及びメモリコントローラ1420を含むことができる。メモリコントローラ1420はホスト1430の読出し/書込み要請に応答してメモリ装置1410から格納されたデータを読出し又は書き込まれるようにメモリ装置1410を制御する。メモリコントローラ1420はホスト1430、例えばモバイル機器又はコンピューターシステムから提供されるアドレスをメモリ装置1410の物理的なアドレスにマッピングするためのアドレスマッピングテーブル(Address mapping table)を構成する。メモリ装置1410は上述した本発明の実施形態による3次元半導体装置を含む。

【0109】

上述された実施形態で開示された半導体装置は多様な形態の半導体パッケージ(semiconductor package)で具現される。例えば、本発明の実施形態による半導体装置はPoP(Package on Package)、Ball grid arrays(BGAs)、Chip scale packages(CSPs)、Plastic Leaded Chip Carrier(PLCC)、Plastic Dual In−Line Package(PDIP)、Die in Waffle Pack、Die in Wafer Form、Chip On Board(COB)、Ceramic Dual In−Line Package(CERDIP)、Plastic Metric Quad Flat Pack(MQFP)、Thin Quad Flatpack(TQFP)、Small Outline(SOIC)、Shrink Small Outline Package(SSOP)、Thin Small Outline(TSOP)、Thin Quad Flatpack(TQFP)、System In Package(SIP)、Multi Chip Package(MCP)、Wafer−level Fabricated Package(WFP)、Wafer−Level Processed Stack Package(WSP)等の方式を用いてパッケージングされる。

【0110】

本発明の実施形態による3次元半導体装置が実装されたパッケージは該3次元半導体装置を制御するコントローラ及び/又は論理素子等をさらに包含することもあり得る。

【0111】

以上、添付された図面を参照して本発明の実施形態を説明したが、本発明が属する技術分野で通常の知識を有する者ならば、本発明がその技術的思想や必須的な特徴を変形しなくとも、他の具体的な形態で実施できることを理解できよう。従って、以上で記述した実施形態は全ての面で例示的であって、限定的ではないことを理解しなければならない。

【符号の説明】

【0112】

99 導電パターン

100 基板

110 素子分離パターン

120 活性領域

130 不純物領域

131 第1不純物領域

132 第2不純物領域

200 薄膜構造体

210 ゲート絶縁膜

215 下部絶縁スペーサー(下部絶縁パターン)

220 犠牲膜

225 層間絶縁膜

230 鋳型膜(モールド膜)

240 第1トレンチ

250 第1埋め込み膜

260 垂直ホール

270 メモリパターン

272 保護パターン

280 第1プラグ(垂直電極VE)

281 スペーサー電極

282 連結電極

300 キャッピングマスクパターン

310 第2トレンチ

311 広い領域

320 リセス領域

330 水平電極(ワードラインWL、又は、選択ラインSL)

340 第2埋め込み膜

345 絶縁スペーサー

350 第2プラグ(ビットラインプラグBLP)

360 上部配線(ビットラインBL)

400 追加パターン(整流要素)

1300 電子装置

1310 制御器

1320 入出力装置

1330 メモリ

1340 無線インターフェイス

1350 バス

1400 メモリシステム

1410 メモリ装置

1420 メモリコントローラ

1430 ホスト

WL ワードライン

ME メモリ要素

BL ビットライン

BLP ビットラインプラグ

VE 垂直電極

SL 選択ライン

SST 選択トランジスター

WLD ワードラインドライバー

BLD ビットラインドライバー

SSD 選択ドライバー

【特許請求の範囲】

【請求項1】

チャンネル領域によって分離された第1及び第2不純物領域を含む基板と、

前記第1不純物領域に接続するビットラインと、

前記第2不純物領域に接続する垂直電極と、

前記基板と前記ビットラインとの間に水平電極の積層体と、

前記水平電極の積層体と前記基板との間に選択ラインと、を含み、

前記選択ラインは前記水平電極の平面形状及び平面位置と実質的に同一の平面形状及び平面位置を有することを特徴とする3次元半導体装置。

【請求項2】

前記選択ラインと前記垂直電極との間の水平距離は前記水平電極と前記垂直電極との間の水平距離と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項3】

前記ビットラインと前記第1不純物領域とを連結するビットラインプラグをさらに含み、

前記選択ラインと前記ビットラインプラグとの間の水平距離は前記水平電極と前記ビットラインプラグとの間の水平距離と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項4】

前記ビットラインは前記水平電極を横切り、

前記選択ライン及び前記積層体は前記チャンネル領域を横切ることを特徴とする請求項1に記載の3次元半導体装置。

【請求項5】

前記選択ラインは前記第1不純物領域の第1部分に重畳され、

前記選択ラインは前記第2不純物領域の第2部分に重畳され、

前記第1不純物領域の第1部分の幅は前記第2不純物領域の第1部分の幅と異なることを特徴とする請求項1に記載の3次元半導体装置。

【請求項6】

前記選択ラインの物質は前記水平電極の物質と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項7】

前記積層体は前記水平電極の垂直方向の間に鋳型膜をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記水平電極と前記垂直電極との間の間隔より大きいことを特徴とする請求項1に記載の3次元半導体装置。

【請求項8】

前記水平電極と前記垂直電極との間にメモリパターンをさらに含み、前記少なくとも1つの水平電極の高さにおける前記メモリパターンの第1水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの第2水平厚さより小さいことを特徴とする請求項7に記載の3次元半導体装置。

【請求項9】

前記積層体は

前記水平電極の垂直方向の間に介在する鋳型膜と、

前記水平電極と前記垂直電極との間に介在する整流要素(rectifying element)をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記整流要素と前記垂直電極との間の間隔と異なることを特徴とする請求項1に記載の3次元半導体装置。

【請求項10】

前記水平電極と前記垂直電極との間に介在するメモリパターンをさらに含み、前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことを特徴とする請求項1に記載の3次元半導体装置。

【請求項11】

互いに連結されて選択ライングループを構成する第1及び第2選択ラインを含む選択ライングループと、

前記選択ラインの各々の上方に順に積層される複数のワードラインと、

前記第1及び第2選択ラインの間に一列に配列される垂直電極と、

前記選択ライングループの両側に各々一列に配列される複数のビットラインプラグと、

前記ワードラインを横切りながら、前記ビットラインプラグを連結するビットラインを含むことを特徴とする3次元半導体装置。

【請求項12】

前記ワードラインは互いに電気的に分離されて、互いに異なる電圧を有するように構成されることを特徴とする請求項11に記載の3次元半導体装置。

【請求項13】

前記ワードラインは第1トレンチを限定し、

前記垂直電極は前記第1トレンチ内にあり、

前記ワードラインは第2トレンチを限定し、

前記ビットラインプラグは前記第2トレンチ内にあり、

前記第2トレンチの各々は複数の前記ビットラインを横切る長さを有することを特徴とする請求項11に記載の3次元半導体装置。

【請求項14】

前記第1トレンチは複数の前記ビットラインを横切る長さを有することを特徴とする請求項13に記載の3次元半導体装置。

【請求項15】

前記第1及び第2選択ラインの各々は前記第1及び第2選択ラインの上の前記複数のワードラインの平面(planar)形状及び平面位置と実質的に同一の平面形状及び平面位置を有することを特徴とする請求項11に記載の3次元半導体装置。

【請求項16】

前記第1及び第2選択ラインと前記垂直電極との間の水平距離は前記複数のワードラインと前記垂直電極との間の水平距離と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項17】

前記第1及び第2選択ラインと前記ビットラインプラグとの間の水平距離は前記ワードラインと前記ビットラインプラグとの間の水平距離と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項18】

前記選択ライングループの下に複数の活性パターンをさらに含み、

前記活性パターンの各々は互いに離隔された一対のドレーン領域、前記ドレーン領域の間に位置するソース領域、前記ドレーン領域と前記ソース領域との間に位置する一対のチャンネル領域を含み、

前記垂直電極は前記ソース領域に接続され、前記ビットラインプラグは前記ドレーン領域に接続され、前記第1及び第2選択ラインは前記一対のチャンネル領域と各々対向して前記一対のチャンネル領域の上に配置されることを特徴とする請求項11に記載の3次元半導体装置。

【請求項19】

前記ドレーン領域の一部は前記第1及び第2選択ラインの中の1つと重畳され、前記ソース領域の一部は前記第1及び第2選択ラインの中の他の1つと重畳され、

前記第1及び第2選択ラインの中の1つと重畳される前記ドレーン領域の一部の幅は、前記第1選択ラインに重畳された前記ソース領域の一部の第1幅及び前記第2選択ラインと重畳された前記ソース領域の一部の第2幅の中少なくとも1つと異なることを特徴とする請求項18に記載の3次元半導体装置。

【請求項20】

前記第1及び第2選択ラインの物質は前記ワードラインの物質と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項21】

垂直方向において前記ワードラインの間に鋳型膜をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記複数のワードラインの少なくとも1つと前記垂直電極との間の間隔より大きいことを特徴とする請求項11に記載の3次元半導体装置。

【請求項22】

前記ワードラインと前記垂直電極との間にメモリパターンをさらに含み、

前記複数のワードラインの少なくとも1つの高さで前記メモリパターンの第1水平厚さは、前記モールド膜の少なくとも1つの高さで前記メモリパターンの第2水平厚さより小さいことを特徴とする請求項21に記載の3次元半導体装置。

【請求項23】

前記ワードラインと前記垂直電極との間に介在するメモリパターンをさらに含み、前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことを特徴とする請求項11に記載の3次元半導体装置。

【請求項24】

基板の上に複数の積層体を含む電極構造体と、

前記電極構造体の上に前記積層体を横切る複数のビットラインと、

前記電極構造体を貫通する垂直電極と、

前記電極構造体を貫通し、その各々は前記ビットラインの中の対応する1つに連結される、ビットラインプラグと、を含み、

前記積層体の各々は選択ライン及び前記選択ラインの上に順に積層された複数のワードラインを含み、

同一の高さに配置される、奇数番目積層体のワードライン及び偶数番目積層体のワードラインは、各々互いに連結され、

前記奇数番目積層体の各々の選択ラインはその右側に位置する偶数番目積層体の選択ラインに連結されて選択ライングループを構成し、

前記垂直電極は前記選択ライングループの各々の内部に位置し、前記ビットラインプラグは前記選択ライングループの間に位置することを特徴とする3次元半導体装置。

【請求項25】

基板内に第1方向にチャンネル領域によって互に離隔された第1不純物領域及び第2不純物領域、及び前記第1方向を横切る第2方向に前記チャンネル領域を横切って延長する選択ラインを含む選択トランジスターと、

前記選択トランジスターの上に積層された複数のワードラインと、を含み、

前記選択トランジスターは前記基板の第1不純物領域に連結されたビットラインと前記基板の第2不純物領域の上の垂直電極との間の電気的連結をコントロールするように配置され、

前記複数のワードラインは前記選択ラインの前記第1方向に延長する幅と実質的に同一である、前記第1方向に延長する幅を有することを特徴とする3次元半導体装置。

【請求項26】

前記選択トランジスターは前記チャンネル領域及び前記選択ラインの間にゲート絶縁膜をさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【請求項27】

前記垂直電極及び前記少なくとも1つの選択トランジスター及び前記ワードラインの間にメモリパターンをさらに含み、

前記垂直電極及び前記選択トランジスターの間の前記第1方向における距離が、前記垂直電極及び前記少なくとも1つのワードラインの間の前記第1方向における距離と同一であることを特徴とする請求項25に記載の3次元半導体装置。

【請求項28】

前記複数のワードラインの各々の少なくとも2つの面及び前記選択ラインの少なくとも2つの面を覆うメモリパターンをさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【請求項29】

前記基板の上に、前記第1方向に延長し、前記第2方向に離隔された複数の活性領域を限定する複数の素子分離パターンと、

前記複数の素子分離パターンを横切る複数のビットラインと、をさらに含み、

前記アクティブパターンの各々は、前記第1方向に沿って交互に配列された複数の第1不純物領域、チャンネル領域、及び第2不純物領域を含み、

前記3次元半導体装置は、

前記第2不純物領域の各々の上に複数の垂直電極と、

前記複数のビットラインを前記第1不純物領域に各々連結させる複数のビットラインプラグと、

前記基板の第1不純物領域の中1つに連結された前記複数のビットラインの中の1つと、前記基板の前記第2不純物領域の上の複数の垂直電極の中の1つとの間の電気的連結をコントロールするように各々配置された複数の選択トランジスターをさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【請求項1】

チャンネル領域によって分離された第1及び第2不純物領域を含む基板と、

前記第1不純物領域に接続するビットラインと、

前記第2不純物領域に接続する垂直電極と、

前記基板と前記ビットラインとの間に水平電極の積層体と、

前記水平電極の積層体と前記基板との間に選択ラインと、を含み、

前記選択ラインは前記水平電極の平面形状及び平面位置と実質的に同一の平面形状及び平面位置を有することを特徴とする3次元半導体装置。

【請求項2】

前記選択ラインと前記垂直電極との間の水平距離は前記水平電極と前記垂直電極との間の水平距離と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項3】

前記ビットラインと前記第1不純物領域とを連結するビットラインプラグをさらに含み、

前記選択ラインと前記ビットラインプラグとの間の水平距離は前記水平電極と前記ビットラインプラグとの間の水平距離と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項4】

前記ビットラインは前記水平電極を横切り、

前記選択ライン及び前記積層体は前記チャンネル領域を横切ることを特徴とする請求項1に記載の3次元半導体装置。

【請求項5】

前記選択ラインは前記第1不純物領域の第1部分に重畳され、

前記選択ラインは前記第2不純物領域の第2部分に重畳され、

前記第1不純物領域の第1部分の幅は前記第2不純物領域の第1部分の幅と異なることを特徴とする請求項1に記載の3次元半導体装置。

【請求項6】

前記選択ラインの物質は前記水平電極の物質と実質的に同一であることを特徴とする請求項1に記載の3次元半導体装置。

【請求項7】

前記積層体は前記水平電極の垂直方向の間に鋳型膜をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記水平電極と前記垂直電極との間の間隔より大きいことを特徴とする請求項1に記載の3次元半導体装置。

【請求項8】

前記水平電極と前記垂直電極との間にメモリパターンをさらに含み、前記少なくとも1つの水平電極の高さにおける前記メモリパターンの第1水平厚さは、前記鋳型膜の高さにおける前記メモリパターンの第2水平厚さより小さいことを特徴とする請求項7に記載の3次元半導体装置。

【請求項9】

前記積層体は

前記水平電極の垂直方向の間に介在する鋳型膜と、

前記水平電極と前記垂直電極との間に介在する整流要素(rectifying element)をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記整流要素と前記垂直電極との間の間隔と異なることを特徴とする請求項1に記載の3次元半導体装置。

【請求項10】

前記水平電極と前記垂直電極との間に介在するメモリパターンをさらに含み、前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことを特徴とする請求項1に記載の3次元半導体装置。

【請求項11】

互いに連結されて選択ライングループを構成する第1及び第2選択ラインを含む選択ライングループと、

前記選択ラインの各々の上方に順に積層される複数のワードラインと、

前記第1及び第2選択ラインの間に一列に配列される垂直電極と、

前記選択ライングループの両側に各々一列に配列される複数のビットラインプラグと、

前記ワードラインを横切りながら、前記ビットラインプラグを連結するビットラインを含むことを特徴とする3次元半導体装置。

【請求項12】

前記ワードラインは互いに電気的に分離されて、互いに異なる電圧を有するように構成されることを特徴とする請求項11に記載の3次元半導体装置。

【請求項13】

前記ワードラインは第1トレンチを限定し、

前記垂直電極は前記第1トレンチ内にあり、

前記ワードラインは第2トレンチを限定し、

前記ビットラインプラグは前記第2トレンチ内にあり、

前記第2トレンチの各々は複数の前記ビットラインを横切る長さを有することを特徴とする請求項11に記載の3次元半導体装置。

【請求項14】

前記第1トレンチは複数の前記ビットラインを横切る長さを有することを特徴とする請求項13に記載の3次元半導体装置。

【請求項15】

前記第1及び第2選択ラインの各々は前記第1及び第2選択ラインの上の前記複数のワードラインの平面(planar)形状及び平面位置と実質的に同一の平面形状及び平面位置を有することを特徴とする請求項11に記載の3次元半導体装置。

【請求項16】

前記第1及び第2選択ラインと前記垂直電極との間の水平距離は前記複数のワードラインと前記垂直電極との間の水平距離と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項17】

前記第1及び第2選択ラインと前記ビットラインプラグとの間の水平距離は前記ワードラインと前記ビットラインプラグとの間の水平距離と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項18】

前記選択ライングループの下に複数の活性パターンをさらに含み、

前記活性パターンの各々は互いに離隔された一対のドレーン領域、前記ドレーン領域の間に位置するソース領域、前記ドレーン領域と前記ソース領域との間に位置する一対のチャンネル領域を含み、

前記垂直電極は前記ソース領域に接続され、前記ビットラインプラグは前記ドレーン領域に接続され、前記第1及び第2選択ラインは前記一対のチャンネル領域と各々対向して前記一対のチャンネル領域の上に配置されることを特徴とする請求項11に記載の3次元半導体装置。

【請求項19】

前記ドレーン領域の一部は前記第1及び第2選択ラインの中の1つと重畳され、前記ソース領域の一部は前記第1及び第2選択ラインの中の他の1つと重畳され、

前記第1及び第2選択ラインの中の1つと重畳される前記ドレーン領域の一部の幅は、前記第1選択ラインに重畳された前記ソース領域の一部の第1幅及び前記第2選択ラインと重畳された前記ソース領域の一部の第2幅の中少なくとも1つと異なることを特徴とする請求項18に記載の3次元半導体装置。

【請求項20】

前記第1及び第2選択ラインの物質は前記ワードラインの物質と実質的に同一であることを特徴とする請求項11に記載の3次元半導体装置。

【請求項21】

垂直方向において前記ワードラインの間に鋳型膜をさらに含み、

前記鋳型膜と前記垂直電極との間の間隔は前記複数のワードラインの少なくとも1つと前記垂直電極との間の間隔より大きいことを特徴とする請求項11に記載の3次元半導体装置。

【請求項22】

前記ワードラインと前記垂直電極との間にメモリパターンをさらに含み、

前記複数のワードラインの少なくとも1つの高さで前記メモリパターンの第1水平厚さは、前記モールド膜の少なくとも1つの高さで前記メモリパターンの第2水平厚さより小さいことを特徴とする請求項21に記載の3次元半導体装置。

【請求項23】

前記ワードラインと前記垂直電極との間に介在するメモリパターンをさらに含み、前記メモリパターンはカルコゲン化合物、磁気−抵抗(magnetoresistance)特性を示すように構成される薄膜構造、ペロブスカイト(perovskite)化合物又は遷移金属酸化物の中の少なくとも1つを含むことを特徴とする請求項11に記載の3次元半導体装置。

【請求項24】

基板の上に複数の積層体を含む電極構造体と、

前記電極構造体の上に前記積層体を横切る複数のビットラインと、

前記電極構造体を貫通する垂直電極と、

前記電極構造体を貫通し、その各々は前記ビットラインの中の対応する1つに連結される、ビットラインプラグと、を含み、

前記積層体の各々は選択ライン及び前記選択ラインの上に順に積層された複数のワードラインを含み、

同一の高さに配置される、奇数番目積層体のワードライン及び偶数番目積層体のワードラインは、各々互いに連結され、

前記奇数番目積層体の各々の選択ラインはその右側に位置する偶数番目積層体の選択ラインに連結されて選択ライングループを構成し、

前記垂直電極は前記選択ライングループの各々の内部に位置し、前記ビットラインプラグは前記選択ライングループの間に位置することを特徴とする3次元半導体装置。

【請求項25】

基板内に第1方向にチャンネル領域によって互に離隔された第1不純物領域及び第2不純物領域、及び前記第1方向を横切る第2方向に前記チャンネル領域を横切って延長する選択ラインを含む選択トランジスターと、

前記選択トランジスターの上に積層された複数のワードラインと、を含み、

前記選択トランジスターは前記基板の第1不純物領域に連結されたビットラインと前記基板の第2不純物領域の上の垂直電極との間の電気的連結をコントロールするように配置され、

前記複数のワードラインは前記選択ラインの前記第1方向に延長する幅と実質的に同一である、前記第1方向に延長する幅を有することを特徴とする3次元半導体装置。

【請求項26】

前記選択トランジスターは前記チャンネル領域及び前記選択ラインの間にゲート絶縁膜をさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【請求項27】

前記垂直電極及び前記少なくとも1つの選択トランジスター及び前記ワードラインの間にメモリパターンをさらに含み、

前記垂直電極及び前記選択トランジスターの間の前記第1方向における距離が、前記垂直電極及び前記少なくとも1つのワードラインの間の前記第1方向における距離と同一であることを特徴とする請求項25に記載の3次元半導体装置。

【請求項28】

前記複数のワードラインの各々の少なくとも2つの面及び前記選択ラインの少なくとも2つの面を覆うメモリパターンをさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【請求項29】

前記基板の上に、前記第1方向に延長し、前記第2方向に離隔された複数の活性領域を限定する複数の素子分離パターンと、

前記複数の素子分離パターンを横切る複数のビットラインと、をさらに含み、

前記アクティブパターンの各々は、前記第1方向に沿って交互に配列された複数の第1不純物領域、チャンネル領域、及び第2不純物領域を含み、

前記3次元半導体装置は、

前記第2不純物領域の各々の上に複数の垂直電極と、

前記複数のビットラインを前記第1不純物領域に各々連結させる複数のビットラインプラグと、

前記基板の第1不純物領域の中1つに連結された前記複数のビットラインの中の1つと、前記基板の前記第2不純物領域の上の複数の垂直電極の中の1つとの間の電気的連結をコントロールするように各々配置された複数の選択トランジスターをさらに含むことを特徴とする請求項25に記載の3次元半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【公開番号】特開2013−115436(P2013−115436A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2012−257685(P2012−257685)

【出願日】平成24年11月26日(2012.11.26)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.WCDMA

2.LTE

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成24年11月26日(2012.11.26)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.WCDMA

2.LTE

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]